(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第6853252号

(P6853252)

(45) 発行日 令和3年3月31日(2021.3.31)

(24) 登録日 令和3年3月15日(2021.3.15)

(51) Int.Cl.

H01L 23/12 (2006.01)

H05K 1/02 (2006.01)

F 1

H01L 23/12

H01L 23/12

H01L 23/12

H05K 1/02

H05K 1/02N

E

Q

A

J

請求項の数 9 (全 16 頁) 最終頁に続く

(21) 出願番号 特願2018-529863 (P2018-529863)

(86) (22) 出願日 平成29年7月24日 (2017.7.24)

(86) 国際出願番号 PCT/JP2017/026604

(87) 国際公開番号 WO2018/021209

(87) 国際公開日 平成30年2月1日 (2018.2.1)

審査請求日 平成31年1月17日 (2019.1.17)

(31) 優先権主張番号 特願2016-148006 (P2016-148006)

(32) 優先日 平成28年7月28日 (2016.7.28)

(33) 優先権主張国・地域又は機関

日本国 (JP)

(73) 特許権者 000006633

京セラ株式会社

京都府京都市伏見区竹田鳥羽殿町 6 番地

(72) 発明者 木村 泰人

京都府京都市伏見区竹田鳥羽殿町 6 番地

京セラ株式会社内

(72) 発明者 白崎 隆行

京都府京都市伏見区竹田鳥羽殿町 6 番地

京セラ株式会社内

審査官 古川 哲也

最終頁に続く

(54) 【発明の名称】半導体素子実装用基板および半導体装置

## (57) 【特許請求の範囲】

## 【請求項 1】

上面に位置する半導体素子を実装する実装領域と、該実装領域以外の周辺領域とを有する第1基板と、

該第1基板の前記周辺領域に位置するとともに前記第1基板の外縁と重なって位置した、前記実装領域を囲む枠状の第2基板と、

該第2基板の上面において前記第2基板の内縁から外縁にかけて位置した、信号線路と、前記第1基板の側面であって、前記第1基板の下面から前記第1基板の上面にかけて位置するとともに、前記第2基板の外縁よりも内側に位置した溝部と、

前記第2基板の内部に位置した、前記信号線路と接続された貫通導体と、

前記溝部の内面に位置しているとともに、前記貫通導体と電気的に接続された側面導体と、を備えており、

前記第1基板および前記第2基板は、前記第1基板および前記第2基板の側面に位置し、かつ、前記溝部の両側において前記溝部と間をあけて位置した凹部を有することを特徴とする半導体素子実装用基板。

## 【請求項 2】

上面に位置する半導体素子を実装する実装領域と、該実装領域以外の周辺領域とを有する第1基板と、

該第1基板の前記周辺領域に位置するとともに前記第1基板の外縁と重なって位置した、前記実装領域を囲む枠状の第2基板と、

10

20

該第2基板の上面において前記第2基板の内縁から外縁にかけて位置した、信号線路と、前記第1基板の側面であって、前記第1基板の下面から前記第1基板の上面にかけて位置するとともに、前記第2基板の外縁よりも内側に位置した溝部と、

前記第2基板の内部に位置した、前記信号線路と接続された貫通導体と、

前記溝部の内面に位置しているとともに、前記貫通導体と電気的に接続された側面導体と、

前記第2基板の上面に位置するとともに、前記実装領域を囲む枠状の第3基板とを備えており、

該第3基板は、前記第3基板の側面に位置するとともに、側面視において前記第2基板を挟んで前記溝部と対向する切欠き部を有することを特徴とする半導体素子実装用基板。 10

### 【請求項3】

上面に位置する半導体素子を実装する実装領域と、該実装領域以外の周辺領域とを有する第1基板と、

該第1基板の前記周辺領域に位置するとともに前記第1基板の外縁と重なって位置した、前記実装領域を囲む枠状の第2基板と、

該第2基板の上面において前記第2基板の内縁から外縁にかけて位置した、信号線路と、前記第1基板の側面であって、前記第1基板の下面から前記第1基板の上面にかけて位置するとともに、前記第2基板の外縁よりも内側に位置した溝部と、

前記第2基板の内部に位置した、前記信号線路と接続された貫通導体と、

前記溝部の内面に位置しているとともに、前記貫通導体と電気的に接続された側面導体と、を備えており、 20

前記第2基板は、下面視において、前記第2基板の外縁が、前記第1基板の外縁よりも外側に位置していることを特徴とする半導体素子実装用基板。

### 【請求項4】

下面視において、前記第2基板の外縁は、前記第1基板の外縁よりも外側に位置していることを特徴とする請求項1または請求項2に記載の半導体素子実装用基板。

### 【請求項5】

前記第2基板の下面に位置するとともに、前記側面導体と前記貫通導体とを接続する電極をさらに備え、

下面視において、前記電極の外縁は前記側面導体の外縁よりも内側に位置していることを特徴とする請求項1乃至請求項4のいずれか1つに記載の半導体素子実装用基板。 30

### 【請求項6】

前記第1基板と前記第2基板の間に位置するとともに、前記電極と間をあけて位置した、第1接地導体層と、

前記第2基板の上面かつ、前記信号線路の両側に前記信号線路と間をあけて位置する接地導体層と、をさらに備えていることを特徴とする請求項5に記載の半導体素子実装用基板。 。

### 【請求項7】

前記第1基板および前記第2基板は、前記第1基板および前記第2基板の側面に位置し、かつ、前記溝部の両側において前記溝部と間をあけて位置した、凹部をさらに備えていることを特徴とする請求項2または請求項3に記載の半導体素子実装用基板。 40

### 【請求項8】

請求項1乃至請求項7のいずれか1つに記載の半導体素子実装用基板と、

前記実装領域に実装された、前記信号線路と電気的に接続された半導体素子とを備えていることを特徴とする半導体装置。

### 【請求項9】

前記第1基板の下面であって、前記第1基板の下面と接合された実装基板をさらに備えており、前記実装基板は内部に接地導体の形成領域および接地導体の非形成領域を有しているとともに、前記接地導体の非形成領域は、前記側面導体と重なっていることを特徴とする請求項8に記載の半導体装置。 50

**【発明の詳細な説明】****【技術分野】****【0001】**

本発明は、半導体素子を実装するための半導体素子実装用基板に関するものである。

**【背景技術】****【0002】**

近年、半導体素子には高い周波数特性が求められており、半導体素子の周波数特性を向上させることができる、高性能な半導体素子実装用基板および半導体装置の必要性が高まっている。半導体装置の製造においては、半導体素子実装用基板上の実装領域に半導体素子を実装して、ボンディングワイヤ等で半導体素子の電極と信号線路とを電気的に接続することによって、半導体素子実装用基板に半導体素子を実装し、製品としての半導体装置となる（例えば、特開2012-156428号公報参照）。この場合、半導体素子と外部の回路基板とを電気的に導通するために側面に側面導体を設けることが知られている。10

**【0003】**

しかしながら、特開2012-156428号公報に開示された技術では、半導体素子実装用基板の側面に設けられた側面導体が露出しているために、外部からの影響で導体部分が損傷する場合があった。また、他の電極と接触しやすくなる場合があった。

**【発明の概要】****【0004】**

本発明の一実施形態に係る半導体素子実装用基板は、第1基板と、第2基板と、信号線路と、溝部と、貫通導体と、側面導体とを備えている。第1基板は、実装領域と実装領域以外の周辺領域とを有する。第2基板は、第1基板の周辺領域に位置するとともに第1基板の外縁と重なって位置した、実装領域を囲む枠状である。信号線路は、第2基板の上面において、第2基板の内縁から外縁にかけて位置している。溝部は、第1基板の側面に、第1基板の下面から第1基板の上面にかけて位置するとともに、第2基板の外縁よりも内側に位置している。貫通導体は、第2基板の内部に位置し、信号線路と接続されている。側面導体は、溝部の内面に位置し、第1基板の上面に形成された電極および貫通導体と電気的に接続されている。そして、第1基板および第2基板は、第1基板および第2基板の側面に位置し、かつ、溝部の両側において溝部と間をあけて位置した凹部を有する。本発明の一実施形態に係る半導体素子実装用基板は、第1基板と、第2基板と、信号線路と、溝部と、貫通導体と、側面導体と、第3基体とを備えている。第1基板は、実装領域と実装領域以外の周辺領域とを有する。第2基板は、第1基板の周辺領域に位置するとともに第1基板の外縁と重なって位置した、実装領域を囲む枠状である。信号線路は、第2基板の上面において、第2基板の内縁から外縁にかけて位置している。溝部は、第1基板の側面に、第1基板の下面から第1基板の上面にかけて位置するとともに、第2基板の外縁よりも内側に位置している。貫通導体は、第2基板の内部に位置し、信号線路と接続されている。側面導体は、溝部の内面に位置し、第1基板の上面に形成された電極および貫通導体と電気的に接続されている。第3基体は、第2基板の上面に位置するとともに、実装領域を囲む枠状である。そして、第3基板は、第3基板の側面に位置するとともに、側面視において第2基板を挟んで溝部と対向する切欠き部を有する。本発明の一実施形態に係る半導体素子実装用基板は、第1基板と、第2基板と、信号線路と、溝部と、貫通導体と、側面導体とを備えている。第1基板は、実装領域と実装領域以外の周辺領域とを有する。第2基板は、第1基板の周辺領域に位置するとともに第1基板の外縁と重なって位置した、実装領域を囲む枠状である。信号線路は、第2基板の上面において、第2基板の内縁から外縁にかけて位置している。溝部は、第1基板の側面に、第1基板の下面から第1基板の上面にかけて位置するとともに、第2基板の外縁よりも内側に位置している。貫通導体は、第2基板の内部に位置し、信号線路と接続されている。側面導体は、溝部の内面に位置し、第1基板の上面に形成された電極および貫通導体と電気的に接続されている。そして、第2基板は、下面視において、第2基板の外縁が、第1基板の外縁よりも外側に位置している。4050

**【0005】**

本発明の一実施形態に係る半導体装置は、上述した半導体素子実装用基板と、半導体素子とを備えている。半導体素子は、実装領域に実装された、信号線路と電気的に接続されている。

**【図面の簡単な説明】****【0006】**

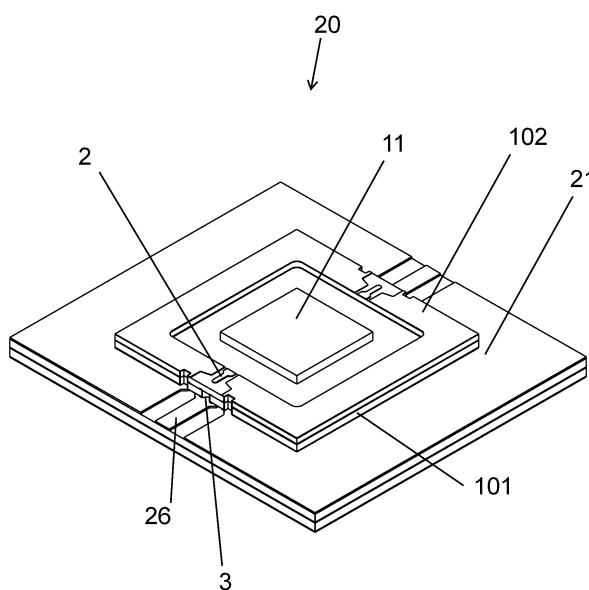

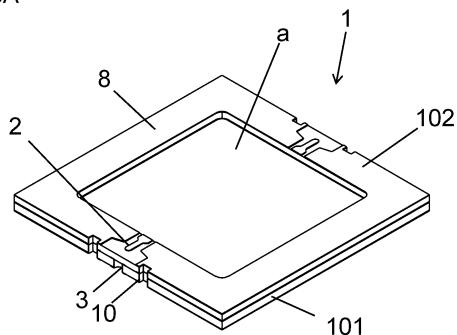

【図1】本発明の一実施形態に係る半導体装置の斜視図である。

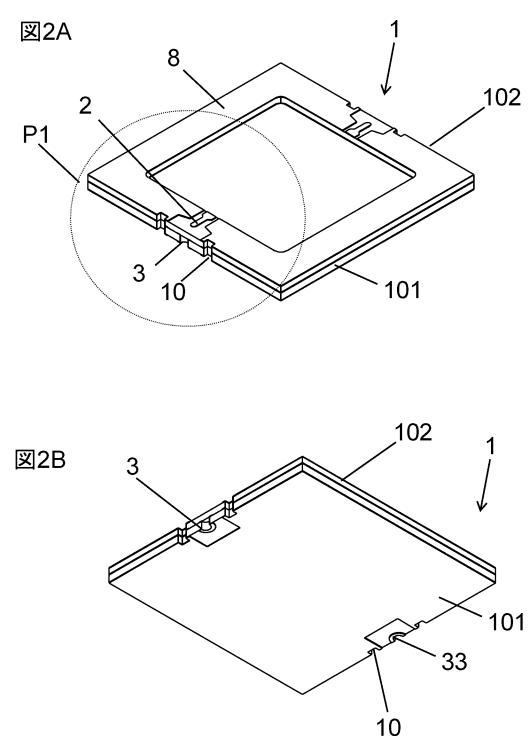

【図2】本発明の一実施形態に係る半導体素子実装用基板の斜視図であって、図2Aは、上面からの斜視図であり、図2Bは下面からの斜視図である。

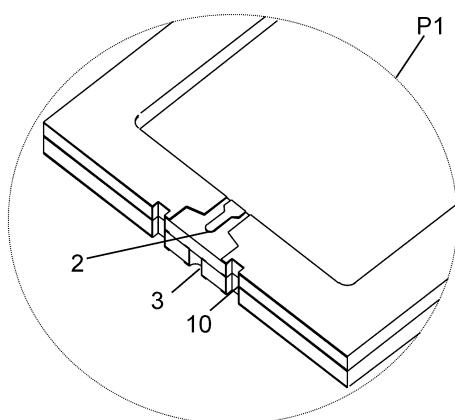

【図3】図2Aに示した本発明の一実施形態に係る半導体素子実装用基板のP1領域の拡大図である。

10

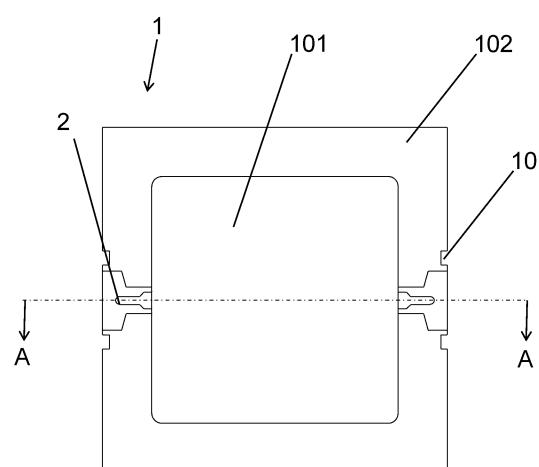

【図4】本発明の一実施形態に係る半導体素子実装用基板の平面図である。

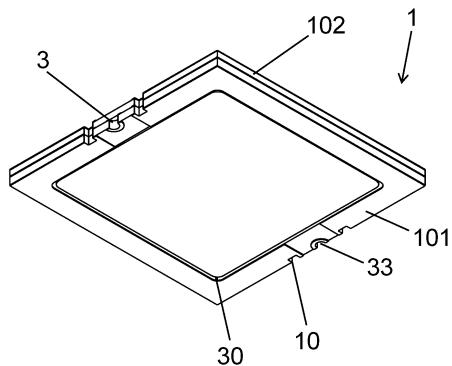

【図5】本発明の他の実施形態に係る半導体素子実装用基板の斜視図であって、図5Aは、上面からの斜視図であり、図5Bは下面からの斜視図である。

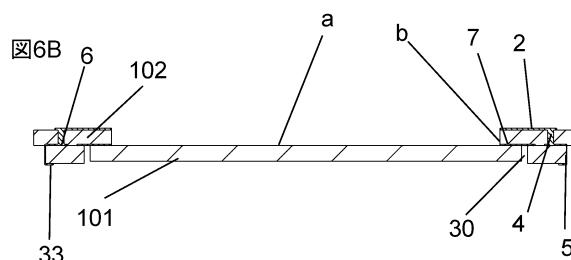

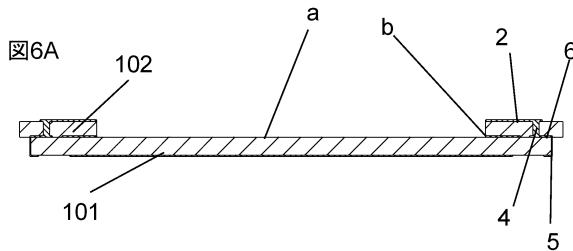

【図6】図4に示した本発明の実施形態に係る半導体素子実装用基板のA-A線での断面図であって、図6Aは本発明の一実施形態に係る半導体素子実装用基板の断面図であり、図6Bは本発明の他の実施形態に係る半導体素子実装用基板の断面図である。

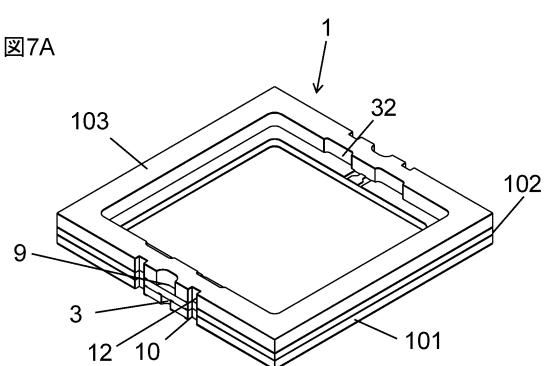

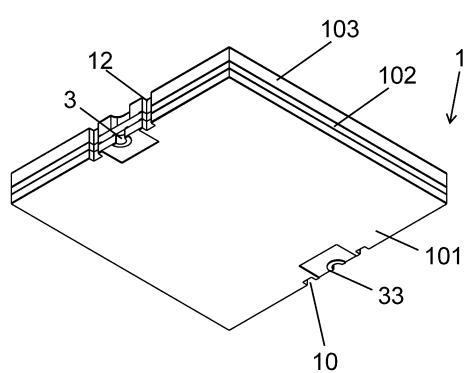

【図7】本発明の他の実施形態に係る半導体素子実装用基板の斜視図であって、図7Aは、上面からの斜視図であり、図7Bは下面からの斜視図である。

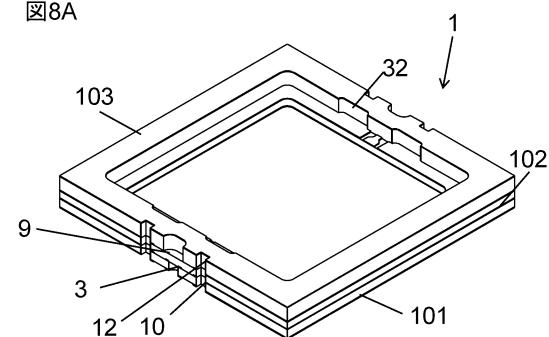

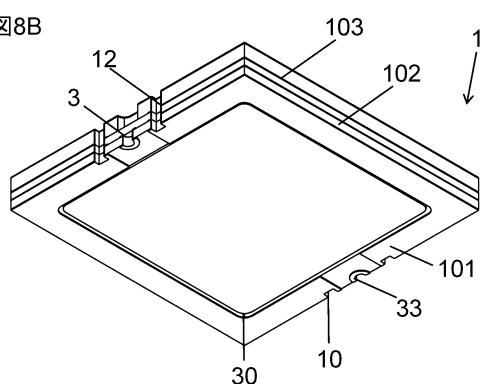

【図8】本発明の他の実施形態に係る半導体素子実装用基板の斜視図であって、図8Aは、上面からの斜視図であり、図8Bは下面からの斜視図である。

20

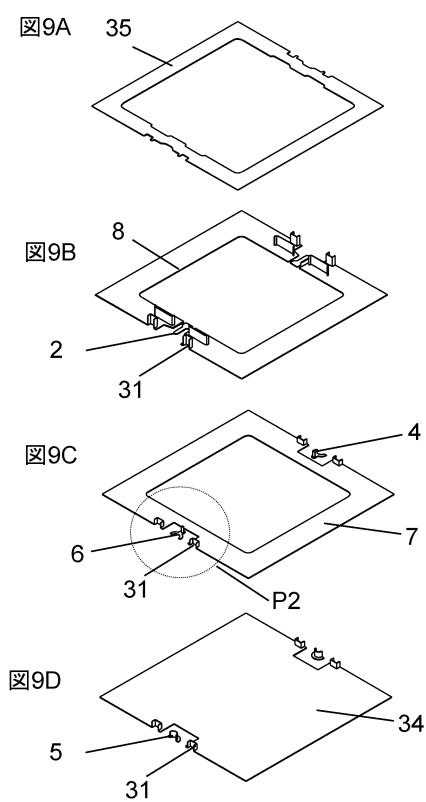

【図9】本発明の他の実施形態に係る半導体素子実装用基板のうち、導体部分のみを示した分解斜視図であって、図9Aは、第3基板の上面の金属層であり、図9Bは、第2基板の上面の信号線路および接地導体層であり、図9Cは、第1基板の上面の第1接地導体層および電極であり、図9Dは、第1基板の下面の金属層である。

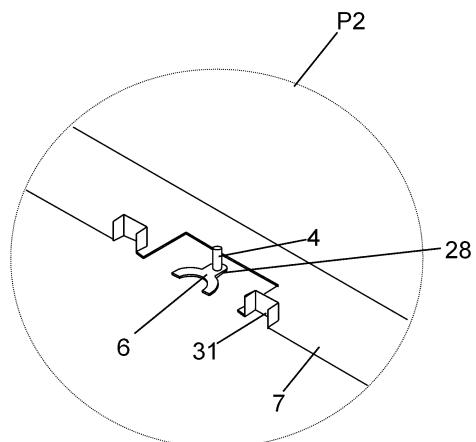

【図10】図9Cに示した第1基板の上面の第1接地導体層および電極のP2領域の拡大図である。

【図11】本発明の一実施形態に係る半導体装置の分解斜視図である。

【図12】本発明の一実施形態に係る半導体装置を実装する実装基板の分解斜視図である。

30

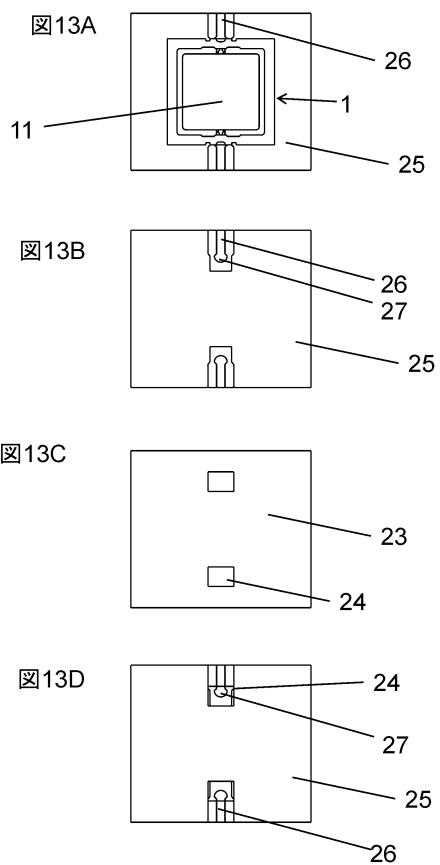

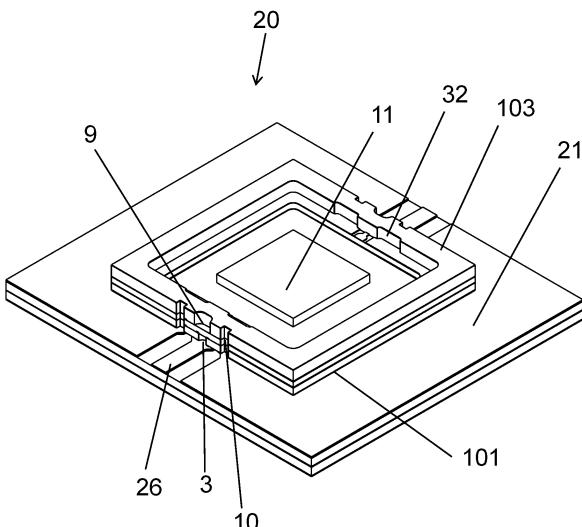

【図13】本発明の他の実施形態に係る半導体装置であって、図13Aは、半導体装置の平面図であり、図13Bは、実装基板の平面図、図13Cは、実装基板の2層目の平面図、図13Dは、実装基板の平面透視図である。

【図14】本発明の他の実施形態に係る半導体装置の分解斜視図である。

**【発明を実施するための形態】****【0007】**

以下、本発明の実施形態に係る半導体素子実装用基板1について、図面に基づき詳細に説明する。なお、以降の図において同一の構成については同一の参照符号を用いて説明する。

**【0008】****<半導体素子実装用基板の構成>**

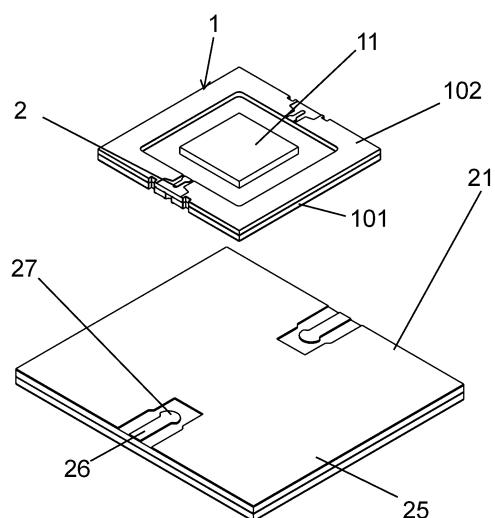

図1は、本発明の一実施形態に係る半導体装置20の斜視図であり、図2は本発明の一実施形態に係る半導体素子実装用基板1の斜視図であって、図2Aは、上面からの斜視図であり、図2Bは下面からの斜視図である。また、図3は図2Aに示した本発明の一実施形態に係る半導体素子実装用基板1のP1領域の拡大図である。図4は本発明の一実施形態に係る半導体素子実装用基板1の平面図である。図5は本発明の他の実施形態に係る半導体素子実装用基板1の斜視図であって、図5Aは、上面からの斜視図であり、図5Bは下面からの斜視図である。図6は図4に示した本発明の実施形態に係る半導体素子実装用基板1のA-A線での断面図であって、図6Aは本発明の一実施形態に係る半導体素子実装用基板1の断面図であり、図6Bは本発明の他の実施形態に係る半導体素子実装用基板1の断面図である。

40

断面図である。これらの図において、半導体装置 20 および半導体素子実装用基板 1 は、第 1 基板 101、第 2 基板 102、信号線路 2、溝部 3、貫通導体 4 および側面導体 5 を備えている。

#### 【 0 0 0 9 】

また、本発明の他の実施形態として、図 7 ~ 図 9 に示すように、半導体素子実装用基板 1 は、第 3 基板 103 をさらに備えていてもよい。図 7 は本発明の他の実施形態に係る半導体素子実装用基板 1 の斜視図であって、図 7 A は、上面からの斜視図であり、図 7 B は下面からの斜視図である。図 8 は本発明の他の実施形態に係る半導体素子実装用基板 1 の斜視図であって、図 8 A は、上面からの斜視図であり、図 8 B は下面からの斜視図である。そして、図 9 は本発明の他の実施形態に係る半導体素子実装用基板 1 のうち、導体部分のみを示した分解斜視図であって、図 9 A は、第 3 基板 103 の上面の金属層 35 であり、図 9 B は、第 2 基板 102 の上面の信号線路 2 および第 2 接地導体層 8 であり、図 9 C は、第 1 基板 101 の上面の第 1 接地導体層 7、貫通導体 4 および電極 6 であり、図 9 D は、第 1 基板 101 の下面の金属層 34 および側面導体 5 である。また、図 10 は図 9 C に示した第 1 基板の上面の第 1 接地導体層 7、貫通導体 4 および電極 6 の P2 領域の拡大図である。

10

#### 【 0 0 1 0 】

半導体素子実装用基板 1 は、第 1 基板 101 および第 2 基板 102 を有している。第 1 基板 101 の上面には、半導体素子 11 を実装する実装領域 a と実装領域 a を取り囲んだ周辺領域 b とを有している。第 1 基板 101 は、たとえばアルミナ ( $\text{Al}_2\text{O}_3$ ) 質焼結体 (アルミナセラミックス) 等のセラミックスから成る。

20

#### 【 0 0 1 1 】

第 2 基板 102 は、第 1 基板 101 の周辺領域 b に位置している。このとき、半導体素子実装用基板 1 の平面視において、第 2 基板 102 の外縁は、第 1 基板 101 の外縁と重なっている。また、第 2 基板 102 は、実装領域 a を取り囲んだ枠状である。第 2 基板 102 は、第 1 基板 101 と同様に、たとえばアルミナ ( $\text{Al}_2\text{O}_3$ ) 質焼結体 (アルミナセラミックス) 等のセラミックスから成る。

#### 【 0 0 1 2 】

また、第 2 基板 102 の上面に、信号線路 2 を備えている。信号線路 2 は、第 2 基板 102 の内縁側の一方の端部から外縁側の他方の端部に向かって形成され、たとえば、鉄、銅、ニッケル、金、クロム、コバルト、モリブデン、マンガンまたはタンゲステン等から成る。または、これらの材料の合金から成る。信号線路 2 は、半導体素子 11 と接続される。

30

#### 【 0 0 1 3 】

また、第 1 基板 101 の側面には、第 1 基板 101 の下面から上面にかけて形成された溝部 3 と、溝部 3 の内面に形成されるとともに、信号線路 2、後述する電極 6 および貫通導体 4 と接続された側面導体 5 と、を有している。溝部 3 は、半導体素子実装用基板 1 の平面視において、第 2 基板 102 の外縁よりも内側に位置している。側面導体 5 は、たとえば、鉄、銅、ニッケル、金、クロム、コバルト、モリブデン、マンガンまたはタンゲステン等から成る。または、これらの材料の合金から成る。

40

#### 【 0 0 1 4 】

また、第 2 基板 102 の内部には、信号線路 2 と電気的に接続された、第 2 基板 102 の上面から下面にかけて貫通する貫通導体 4 が設けられる。貫通導体 4 は、さらに、第 1 基板 101 の上面で溝部 3 の上端部の周囲に設けられる電極 6 を介して側面導体 5 と電気的に接続される。貫通導体 4 は、信号線路 2 の他方の端部と重なる位置にあり、電気的に接続される。この場合には、高周波の電気信号をより確実に貫通導体 4 から信号線路 2 に伝送させることができるとともに、伝送される高周波の電気信号の伝送損失や反射損失を低減させることができる。

#### 【 0 0 1 5 】

溝部 3 は、平面視において、第 2 基板 102 の外縁よりも内側に位置している。つまり

50

、溝部3がある箇所において、第2基板102が出っ張った状態になる。このため、溝部3に形成された側面導体5は、電気的な導通を良好に維持した状態とすることができます。つまり、外部からの影響によって、導体に傷がついたり、損傷したり、ショートするおそれを低減させることができる。

#### 【0016】

また、平面視において、第2基板102の外縁は、第1基板101の外縁よりも外側に位置していてもよい。このことによって、溝部3の上面にある第2基板102は、より外側に出っ張っていることになる。つまり、溝部3に形成された側面導体5は、外部からの影響を受けにくく、電気的な導通を良好に維持した状態とすることができます。外部からの影響によって、導体に傷がついたり、損傷したり、ショートするおそれをより低減させることができる。10

#### 【0017】

さらに、図6および図10に示すように、半導体素子実装基板1は、第1基板101の上面、もしくは第2基板102の下面であって、第1基板101と第2基板102の間に位置し、側面導体5と電気的に接続された電極6と、電極6と間をあけて位置した、第1接地導体層7とをさらに有している。つまり、電極6および第1接地導体層7は、半導体素子実装基板1の内部に位置した信号導体層および接地導体層である。このような構成によって、半導体素子実装用基板1の内部において、電極6が第1接地導体層7によって取り囲まれるように位置することによって、側面導体5および電極6における特性インピーダンスを低減することができる。さらに、電極6を介した、側面導体5から貫通導体4に至る信号伝送部分に生じる電界が意図しない範囲に広がる可能性を抑制することができ、電極6と第1接地導体層7との間に結合させることができる。このことによって、この信号伝送部分の電界分布の拡がりを抑制することができる。また、高周波の電気信号が電極6と第1接地導体層7との間で電界結合しながら伝送することができる。また、信号伝送部分における特性インピーダンスを安定化させることができます。20

#### 【0018】

すなわち、半導体素子実装用基板1は、信号伝送部分が接地電位部分に取り囲まれる構成となり、信号伝送部分の電界分布の拡がりを抑制できる。このことから、半導体素子実装用基板1の信号伝送部分における特性インピーダンスの変動を抑制することができる。また、周波数特性を向上させることができ、高性能な半導体素子実装用基板1および半導体装置20を提供することが可能となる。30

#### 【0019】

さらに、はんだ等の導電性の接合材を介して側面導体5を外部の実装基板に電気的に接続する際に、接合材によるメニスカスが溝部3の内面の下端に形成される。このような構成であることによって、側面導体5は、外部の実装基板と電気的に安定して接続される。つまり、半導体素子実装用基板1は、信号伝送部分における特性インピーダンスの変動を抑制することができ、周波数特性を向上させることができる。

#### 【0020】

また、半導体素子実装用基板1は、第2基板102の上面に、信号線路2を挟むようにして、第2接地導体層8をさらに備えていてもよい。このような構成によって、第2基板102の上面において、信号伝送部分が接地電位部分に挟まれる、いわゆるコプレーナ線路の構成とすることができます。この結果、半導体素子実装用基板1の信号伝送部分における周波数特性をさらに向上させることができる。さらに、第1基板101と第2基板102の間に位置し、電極6と間をあけて位置した第1接地導体層7が信号線路2および第2接地導体層8と重なる箇所に設けられる。この場合には、いわゆるグランド付きコプレーナ線路の構成となり、半導体素子実装用基板1の信号伝送部分における周波数特性をさらに向上させることができる。40

#### 【0021】

また、図6および図10に示すように、電極6は、第1基板101の上面、もしくは第2基板102の下面に側面導体5が延びる方向と直交する方向で、溝部3の上端部（第250

基板 102 側の端部) の周囲に設けられ、側面導体 5 に電気的に接続される。このとき、下面視において電極 6 の外縁は、側面導体 5 の外縁よりも半導体素子実装用基板 1 の内側に位置している。つまり、電極 6 は、下面視において、第 2 基板 102 の下面に露出しない。電極 6 が第 2 基板 102 の下面に露出していない場合には、半導体装置 20 をはんだ等の導電性の接合材を介して実装基板に電気的に接続する際に、接合材が側面導体 5 を介して電極 6 に濡れ広がることを低減させることができる。その結果、第 2 基板 102 と接合材との熱膨張係数差に起因して生じる応力を低減できる。また、接合材の濡れ広がり方によって特性インピーダンスが不安定に変動する可能性を低減することができる。その結果、信号伝送部分となる側面導体 5 および電極 6 における周波数特性をさらに良好に維持することができる。

10

#### 【0022】

また、電極 6 は、図 10 に示すように、溝部 3 と反対方向に突出するように内層の接続端子である第 2 接続端子 28 が設けられ、第 2 接続端子 28 の第 2 基板 102 側の面に貫通導体 4 が接続される。これにより、電極 6 は、第 2 接続端子 28 および貫通導体 4 を介して信号線路 2 に電気的に接続される。その結果、半導体素子実装用基板 1 は、電極 6 および第 2 接続端子 28 と第 1 接地導体層 7 との間に生じる静電容量が大きくなる。また、特性インピーダンスが小さくなることを緩和することができる。よって、電極 6 および第 2 接続端子 28 による信号伝送部分の特性インピーダンスを所望の値にすることが容易となり、半導体素子実装用基板 1 の小型化を実現できる。また、信号伝送部分における周波数特性をさらに向上させることができる。

20

#### 【0023】

第 2 接続端子 28 は、平面視において、電極 6 の外縁の中央部から溝部 3 と反対方向に直線状に設けられ、第 2 基板 102 側の面に貫通導体 4 が接続される。その結果、半導体素子実装用基板 1 は、電極 6 および第 2 接続端子 28 による信号伝送部分の長さを短くすることができ、信号伝送部分における周波数特性をさらに向上させることができる。

#### 【0024】

また、半導体素子実装用基板 1 は、第 1 基板 101 の側面から第 2 基板 102 の側面にかけて、溝部 3 を挟むようにして形成された側面接地導体 31 をさらに備えている。このような構成によって、側面においても、信号伝送部分が接地電位部分に挟まれる構成となり、半導体素子実装用基板 1 の信号伝送部分に生じる電界分布の不要かつ不安定な拡がりと特性インピーダンスの変動を抑制することができる。この結果、半導体素子実装用基板 1 の周波数特性をさらに向上させることができ。また、側面接地導体 31 は、第 1 基板 101 の側面から第 2 基板 102 の側面にかけて、溝部 3 を挟むように連続して設けられてもよい。これにより、半導体素子実装用基板 1 は、側面接地導体 31 の電位を安定化させることができる。さらに、側面接地導体 31 は、平面視において、第 1 基板 101 の側面に設けられる側面接地導体 31 と、第 2 基板 102 の側面に設けられる側面接地導体 31 とが重なるように設けられてもよい。この結果、半導体素子実装用基板 1 は、半導体素子実装用基板 1 の信号伝送部分に生じる電界分布の不要かつ不安定な拡がりと特性インピーダンスの変動をより安定して抑制することができる。

30

#### 【0025】

また、図 10 に示すように、電極 6 は平面視したときの外形状が略半円形状である。このような構成によって、半導体素子実装用基板 1 の製造工程において、電極 6 を容易に設けることができるとともに、電極 6 の外形部分に応力が局所的に生じる可能性を低減できる。さらに、半導体素子実装用基板 1 は、電極 6 の外形部分における電界分布の拡がりが偏ることを抑制することができる。この結果、半導体素子実装用基板 1 は、電極 6 の外形部分に生じる応力によって電極 6 が剥がれたり、第 1 基板 101 や第 2 基板 102 にクラックが生じたりするおそれを低減できるとともに、信号伝送部分の周波数特性をさらに向上させることができる。また、下面の信号電極 33 は、平面視したときの外形状が略半円形状である。このような構成によって、上述と同様の作用効果により、半導体素子 11 と外部の実装基板との間の電気的な接続を安定させることができ、周波数特性を改善するこ

40

50

とができる。また、下面の信号電極 3 3 を介して半導体装置 2 0 を外部の実装基板にはんだ等の接続部材で実装する際に、下面の信号電極 3 3 および接続部材の周辺に生じる応力が一部に集中することを低減することができる。

#### 【 0 0 2 6 】

また、実装領域 a を取り囲む第 2 基板 1 0 2 の周縁の内壁に、半導体素子実装用基板 1 の平面視にて信号線路 2 を間に挟むように内面溝 3 2 が設けられていてもよく、この内面溝 3 2 の内面にも接地電位となる内面接地導体が形成されている。その結果、このような構成である半導体素子実装用基板 1 は、信号線路 2 の実装領域 a 側の端部における電界分布の不要かつ不安定な拡がりと特性インピーダンスの変動を抑制することができ、半導体素子実装用基板 1 の周波数特性をさらに向上させることができる。

10

#### 【 0 0 2 7 】

また、図 5 B、図 6 B および図 8 B に示すように、本発明の他の実施形態に係る半導体素子実装用基板 1 には、第 1 基板 1 0 1 の一部であって、平面視で実装領域 a を取り囲むように、第 1 接地導体層 7 よりも下面の信号電極 3 3 側に、空隙部 3 0 が設けられていてもよい。半導体素子実装用基板 1 または半導体装置 2 0 の製造工程や、半導体装置 2 0 を作動させる際の半導体素子 1 1 の発熱によって半導体素子実装用基板 1 内に温度変化や温度勾配が発生する。この結果、半導体素子実装用基板 1 や半導体素子 1 1 の熱膨張や熱収縮に起因した応力が生じる場合がある。このような場合であっても、空隙部 3 0 が存在することによって半導体素子実装用基板 1 に生じる応力を緩和することができるので、半導体素子実装用基板 1 の破損やクラックの発生を抑制することが可能となる。また、基板 2 の変形や反りに伴って生じる実装領域 a の変形や反りを抑制することができるため、半導体素子 1 1 を実装領域 a に安定して実装することができる。また、実装領域 a の変形や反りに伴って生じる半導体素子 1 1 の破損を抑制することができる。

20

#### 【 0 0 2 8 】

さらに、半導体素子実装用基板 1 の小型化において、側面導体 5 、下面の信号電極 3 3 および電極 6 と第 1 接地導体層 7 との間隔が狭くなり、信号伝送部分と接地電位部分との間に生じる静電容量が大きくなるとともに特性インピーダンスが小さくなることを、空隙部 3 0 が存在することによって緩和することができる。よって、信号伝送部分の特性インピーダンスを所望の値にすることが容易となり、半導体素子実装用基板 1 の小型化を実現できるとともに、信号伝送部分における周波数特性をさらに向上させることができる。

30

#### 【 0 0 2 9 】

また、半導体素子実装用基板 1 は実装領域 a が金属材料であってもよい。このとき実装領域 a は、鉄、銅、ニッケル、クロム、コバルトまたはタンクステンのような金属材料を用いることができる。あるいは、これらの金属からなる合金を用いることができる。また、実装領域 a は第 1 接地導体層 7 とはんだやろう材等の導電性の接合材で電気的に接続されている。このような構成によって、半導体素子実装用基板 1 の放熱性が向上するとともに実装領域 a 、第 1 接地導体層 7 、接地導体 2 2 、側面接地導体 3 1 が外部の実装基板に設けられる後述するグランド層 2 5 に実装領域 a を介して接続され、それぞれの接地電位が安定する。また、半導体素子実装用基板 1 の接地電位となる実装領域 a と外部の実装基板に設けられる接地導体との接合面積を大きくすることができることから、実装領域 a を含む半導体素子実装用基板 1 の接地電位がさらに安定する。

40

#### 【 0 0 3 0 】

この結果、半導体素子実装用基板 1 の信号伝送部分における周波数特性をさらに向上させることができる。さらに、半導体素子実装用基板 1 には、第 1 基板 1 0 1 に空隙部 3 0 が設けられていると、前述と同様の作用効果によって半導体素子実装用基板 1 の破損やクラックの発生、さらに、半導体素子 1 1 の破損を抑制することが可能となる。また、半導体素子実装用基板 1 の信号伝送部分における周波数特性をさらに向上させることができること。

#### 【 0 0 3 1 】

また、溝部 3 は、平面視において、例えば半楕円形状または円形状である。また、溝部

50

3が曲線部を有している。半導体素子実装用基板1または半導体装置20の製造工程や、半導体装置20を作動させる際の半導体素子11の発熱によって半導体素子実装用基板1内に温度変化や温度勾配が発生する。これによって、半導体素子実装用基板1の熱膨張や熱収縮に起因した応力が生じる場合がある。このような場合にも、溝部3が曲線部を有することによって、溝部3の局所に応力が集中することを抑制することができ、第1基板101、側面導体5、電極6、下面の信号電極33および側面接地導体31の破損やクラックの発生を抑制することが可能となる。また、溝部3は、平面視において、電極6の外形状と同じである。これにより、半導体素子実装用基板1は、上述と同様の作用効果によって溝部3および電極6の局所に応力が集中することを抑制することができる。

## 【0032】

10

また、図3に示すように、側面視において第1基板101および第2基板102の側面に凹部10をさらに備えていてもよい。凹部10は、溝部3の両側に、溝部3と間を開けて、第1基板101の下面から第2基板102の上面にかけて設けられている。この凹部10は、内周面に側面接地導体31が設けられているのがよい。このことによって、接地導体となる側面接地導体31の面積を大きくすることができますから、半導体素子実装用基板1の接地電位をより安定させることができる。また、側面導体5の周囲に生じる電界分布の不要かつ不安定な拡がりと特性インピーダンスの変動をより安定して抑制することができる。

## 【0033】

20

また、図7～図9に示すように、半導体素子実装用基板1は、第2基板102の上面に第3基板103をさらに備えている。第3基板103は、例えば第1基板101および第2基板102を構成する材料と同じであり、平面視で外周の形状が同じである。例えば、第3基板103は、側面に、平面視において溝部3と重なる位置に切欠き部9、第2の凹部12を有しており、切欠き部9の内面には接地導体が設けられておらず、第2の凹部12の内面には側面接地導体31が連続して設けられている。第3基板103は、内面に接地導体が設けられていない切欠き部9が設けられていることにより、半導体素子実装用基板1の小型化において、信号線路2と接地導体22との間隔が狭くなる。このことによって、信号伝送部分と接地電位部分との間に生じる静電容量が大きくなるとともに特性インピーダンスが小さくなることを、切欠き部9が存在することによって緩和することができる。また、切欠き部9は、平面視において、外形が溝部3より大きくなる。これにより、半導体素子実装用基板1は、溝部3と切欠き部9との間に位置する第2基板102に応力が集中することを抑制できる。このことから、第2基板102にクラックや割れが生じる可能性を低減することができる。さらに、平面視において、凹部10と第2の凹部12の形状を同じにするのがよい。その結果、凹部10と第2の凹部12との間に生じる応力が凹部10と第2の凹部12との界面において局所的に集中することを抑制できる。また、半導体素子実装用基板1の信号伝送部分となる側面導体5の周囲に生じる電界分布の不要かつ不安定な拡がりと特性インピーダンスの変動を抑制することができる。この結果、半導体素子実装用基板1は、信号伝送部分の周波数特性をさらに向上させることができる。

## 【0034】

30

図9に示すように、第1基板101の下面には下面の金属層34、第3基板103の上面には、上面の金属層35が形成されていてもよい。下面に金属層34があることによって、実装基板との電気的な接続がしやすくなる。また、金属層34を介した半導体素子実装用基板1の放熱性が向上する。また、上面の金属層35があることによって、信号線路2に高周波の電気信号が伝送する際に生じる電界が上面の金属層35に結合されることにより、信号線路2の周囲における不要かつ不安定な電界分布の拡がりを抑制することができる。その結果、半導体素子実装用基板1は、信号伝送部分の周波数特性をさらに向上させることができる。

## 【0035】

40

半導体素子実装用基板1または半導体装置20の製造工程や、半導体装置20を作動させる際の半導体素子11の発熱によって熱応力が生じる。このとき、溝部3および凹部1

50

0と切欠き部9および第2の凹部12の形状が同じであれば、上記のとおり溝部3および凹部10と切欠き部9および第2の凹部12との接合界面に局所的に集中することを抑制することができる。さらに、第3基板103は、第2の凹部12が設けられているとともに内面に側面接地導体31が設けられている。このことにより、信号線路2の溝部3側の端部における電界分布の不要かつ不安定な拡がりと特性インピーダンスの変動を抑制することができる。この結果、半導体素子実装用基板1の周波数特性をさらに向上させることができる。

#### 【0036】

##### <半導体装置の構成>

図11は、発明の一実施形態に係る半導体装置20の分解斜視図である。半導体装置20を組み立てる場合、基板2の実装領域aに半導体素子11を載置して基板2に接着剤等を介して接着固定し、半導体素子11と信号線路2とをポンディングワイヤ等を介して電気的に接続する。このようにして、半導体素子実装用基板1に半導体素子11を実装することによって製品としての半導体装置20が完成する。

10

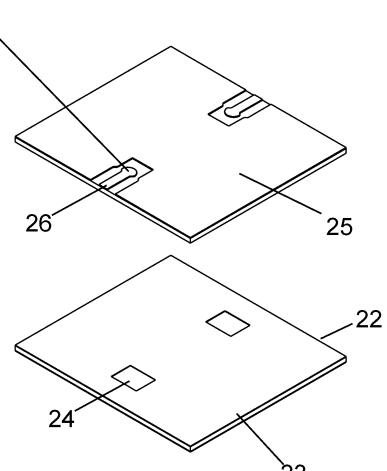

#### 【0037】

半導体装置20の他の実施形態として、図12～図14に基づいて説明する。図12は、本発明の一実施形態に係る半導体装置20を実装する実装基板21の分解斜視図であり、図13は本発明の他の実施形態に係る半導体装置20であって、図13Aは、半導体装置20の平面図であり、図13Bは、実装基板21の平面図、図13Cは、実装基板の2層目の平面図、図13Dは、実装基板21の平面透視図である。また、図14は本発明の他の実施形態に係る半導体装置20の分解斜視図である。

20

#### 【0038】

実装基板21は、例えば複数の絶縁層で構成されており、上層の上面には、はんだ等の導電性の接合材を介して側面導体5および下面の信号電極33が電気的に接続されるとともに高周波の電気信号が伝送される、銅箔等の金属材料から成る信号導体26および接続端子27が設けられる。さらに、実装基板21は、上層の上面に信号導体26を間に挟み、接続端子27を取り囲むように、所定の間隔が設けられた銅箔等の金属材料から成り、接地電位となるグランド層25が形成されている。

#### 【0039】

このグランド層25と、半導体素子実装用基板1の下面に設けられた金属層34や側面接地導体31、金属材料からなる実装領域aの下面とが、はんだ等の接合材を介して接合される。実装基板21は、上面に前述の接続端子27、信号導体26およびグランド層25が設けられることにより、平面伝送線路の1つである、いわゆる、コブレーナ線路が構成される。グランド層25は、平面視において、電極6および下面の信号電極33と重なる位置に設けられず、さらに、信号線路2の信号伝送方向、すなわち、信号線路2から半導体素子11の方向と直交する方向において、信号線路2と重なる位置に設けられていない。

30

#### 【0040】

また、実装基板21は、内層に接地導体22が形成されている。接地導体22は、接地導体22が形成される形成領域23および接地導体22が形成されない非形成領域24を有している。接地導体層の非形成領域24は、平面視において、少なくとも下面の信号電極33および接続端子27と重なる位置に設けられない。このことによって、半導体装置20を実装基板21に実装した際に、所望の特性インピーダンスの範囲に調整し難くなることを緩和することができる。なぜならば、下面の信号電極33と接続端子27とを電気的に接続するはんだ等の導電性の接合材や、この接合材によって側面導体5の側面に形成されるメニスカスにより、信号導体26と側面導体5との間の信号伝送部分において、接地電位部分との間に生じる静電容量が大きくなるとともに特性インピーダンスが小さくなるためである。

40

#### 【0041】

また、非形成領域24は、平面視において、信号線路2の信号伝送方向、すなわち、信

50

号線路 2 から半導体素子 1 1 の方向と直交する方向において、側面導体 5 を間に挟む一対の側面接地導体 3 1 よりも内側（側面導体 5 側）に設けられることがよい。これにより、信号導体 2 6 と側面導体 5 との間の信号伝送部分における電界分布の不要かつ不安定な拡がりと特性インピーダンスの変動を抑制することができる。この結果、半導体素子実装用基板 1 は、信号伝送部分の周波数特性をさらに向上させることができる。

#### 【 0 0 4 2 】

以上に説明した、本発明は上述の実施形態に限定されるものではなく、本発明の要旨を逸脱しない範囲において種々の変更等が可能である。

#### 【 符号の説明 】

#### 【 0 0 4 3 】

|       |            |    |

|-------|------------|----|

| 1     | 半導体素子実装用基板 | 10 |

| 1 0 1 | 第 1 基板     |    |

| 1 0 2 | 第 2 基板     |    |

| 1 0 3 | 第 3 基板     |    |

| a     | 実装領域       |    |

| b     | 周辺領域       |    |

| 2     | 信号線路       |    |

| 3     | 溝部         |    |

| 4     | 貫通導体       |    |

| 5     | 側面導体       | 20 |

| 6     | 電極         |    |

| 7     | 第 1 接地導体層  |    |

| 8     | 第 2 接地導体層  |    |

| 9     | 切欠き部       |    |

| 1 0   | 凹部         |    |

| 1 1   | 半導体素子      |    |

| 1 2   | 第 2 の凹部    |    |

| 2 0   | 半導体装置      |    |

| 2 1   | 実装基板       |    |

| 2 2   | 接地導体       | 30 |

| 2 3   | 形成領域       |    |

| 2 4   | 非形成領域      |    |

| 2 5   | グランド層      |    |

| 2 6   | 信号導体       |    |

| 2 7   | 接続端子       |    |

| 2 8   | 第 2 接続端子   |    |

| 3 0   | 空隙部        |    |

| 3 1   | 側面接地導体     |    |

| 3 2   | 内面溝        |    |

| 3 3   | 下面の信号電極    | 40 |

| 3 4   | 下面の金属層     |    |

| 3 5   | 上面の金属層     |    |

【図1】

【図2】

【図3】

【図4】

【図5】

図5A

図5B

【図6】

【図7】

図7A

図7B

【図8】

図8A

図8B

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

---

フロントページの続き

(51)Int.Cl.

F I

H 0 5 K      1/02

P

- (56)参考文献 特開2009-266905(JP,A)

特開平09-293826(JP,A)

特開平11-312760(JP,A)

国際公開第2012/165434(WO,A1)

特開2004-247627(JP,A)

特開2004-179338(JP,A)

特開平11-097736(JP,A)

(58)調査した分野(Int.Cl., DB名)

H 0 1 L      2 3 / 1 2

H 0 5 K      1 / 0 2

H 0 5 K      3 / 4 6