# (19) 대한민국특허청(KR)

## (12) 등록특허공보(B1)

(51)Int. Cl.

**H01J 17/49** (2006.01) **H01J 17/04** (2006.01)

(21) 출원번호

10-2006-0093670

(22) 출원일자

2006년09월26일

심사청구일자 2006년09월26일

(56) 선행기술조사문헌 JP15031133 A JP15308791 A

(45) 공고일자

2008년02월20일

(11) 등록번호 10-0804531

(24) 등록일자 2008년02월12일

(73) 특허권자

삼성에스디아이 주식회사

경기 수원시 영통구 신동 575

(72) 발명자

강태경

경기 용인시 기흥구 공세동428-5

(74) 대리인

리앤목특허법인

전체 청구항 수 : 총 10 항

심사관 : 최훈영

## (54) 플라즈마 디스플레이 패널

## (57) 요 약

전극들의 단자부 불량을 방지할 수 있도록 본 발명은 서로 마주보는 전면 기판 및 배면 기판, 상기 전면 기판과 배면 기판 사이의 공간을 복수 개의 방전셀들로 한정하는 격벽, 상기 전면 기판 및 배면 기판 사이에 배치되는 전극들 및 상기 전극들과 전기적으로 연결되는 전극 단자부들을 포함하고, 상기 전극 단자부는 상기 각 전극들의 일 측단을 덮도록 형성되는 플라즈마 디스플레이 패널을 제공한다.

### **대표도** - 도4

#### 특허청구의 범위

#### 청구항 1

서로 마주보는 전면 기판 및 배면 기판;

상기 전면 기판과 배면 기판 사이의 공간을 복수 개의 방전셀들로 한정하는 격벽;

상기 전면 기판 및 배면 기판 사이에 배치되는 전극들 및

상기 전극들과 전기적으로 연결되는 전극 단자부들을 포함하고,

상기 전극 단자부들은 상기 각 전극들의 일 측단을 덮도록 형성되며, 상기 전극들은 상기 전극 단자부들에 의해 덮이는 제1 부분과, 상기 전극 단자부들에 의해 덮이지 않는 제2 부분을 포함하고, 상기 제1 부분은 상기 전극 단자부를 향하는 방향으로 갈수록 두께가 감소하도록 그 종단면이 테이퍼형인 플라즈마 디스플레이 패널.

#### 청구항 2

제1 항에 있어서,

상기 전극 단자부들의 두께가 상기 전극들의 두께보다 큰 플라즈마 디스플레이 패널.

#### 청구항 3

제2 항에 있어서,

상기 전극 단자부들의 두께는 상기 전극들의 두께의 2배 이내인 플라즈마 디스플레이 패널.

#### 청구항 4

제1 항에 있어서,

상기 전극 단자부들의 폭이 상기 전극들의 폭보다 큰 플라즈마 디스플레이 패널.

#### 청구항 5

삭제

#### 청구항 6

서로 마주보는 전면 기판 및 배면 기판;

상기 전면 기판과 배면 기판 사이의 공간을 복수 개의 방전셀들로 한정하는 격벽;

상기 전면 기판 및 배면 기판 사이에 배치되는 전극들 및

상기 전극들과 전기적으로 연결되는 전극 단자부들을 포함하고,

상기 전극 단자부들은 상기 각 전극들의 일 측단을 덮도록 형성되고, 상기 전극들은 상기 전극 단자부들에 의해 덮이는 제1 부분과, 상기 전극 단자부들에 의해 덮이지 않는 제2 부분을 포함하고,

상기 제1 부분의 폭이 상기 제2 부분의 폭보다 큰 플라즈마 디스플레이 패널.

#### 청구항 7

제1 항에 있어서,

상기 전극 단자부들은 옵셋 인쇄방법에 의해 형성된 플라즈마 디스플레이 패널.

### 청구항 8

제1 항, 제2 항, 제3 항, 제4 항, 제6 항 또는 제7 항 중 어느 하나의 항에 있어서,

상기 전극 단자부들과 전기적으로 연결되는 신호 전달 수단 및

상기 방전셀들내에 배치되는 형광체를 더 포함하는 플라즈마 디스플레이 패널.

#### 청구항 9

기판 상에 복수 개의 방전셀을 구획하는 격벽을 형성하는 단계;

상기 방전셀에 전극들을 형성하는 단계; 및

상기 전극들과 전기적으로 연결되는 전극 단자부들을 형성하는 단계를 포함하고,

상기 전극 단자부들은 상기 각 전극들의 일 측단을 덮도록 형성하며, 상기 전극들은 상기 전극 단자부들에 의해 덮이는 제1 부분과, 상기 전극 단자부들에 의해 덮이지 않는 제2 부분을 포함하고, 상기 제1 부분은 상기 전극 단자부를 향하는 방향으로 갈수록 두께가 감소하도록 그 종단면을 테이퍼형으로 형성하는 플라즈마 디스플레이패널의 제조 방법.

#### 청구항 10

제9 항에 있어서,

상기 전극 단자부들은 옵셋 인쇄 방법으로 형성하는 플라즈마 디스플레이 패널의 제조 방법.

#### 청구항 11

기판 상에 복수 개의 방전셀을 구획하는 격벽을 형성하는 단계;

상기 방전셀에 전극들을 형성하는 단계; 및

상기 전극들과 전기적으로 연결되는 전극 단자부들을 형성하는 단계를 포함하고,

상기 전극 단자부들은 상기 각 전극들의 일 측단을 덮도록 형성하며, 상기 전극들은 상기 전극 단자부들에 의해 덮이는 제1 부분과, 상기 전극 단자부들에 의해 덮이지 않는 제2 부분을 포함하고, 상기 제1 부분의 폭을 상기 제2 부분의 폭보다 크게 형성하는 플라즈마 디스플레이 패널의 제조 방법.

#### 명 세 서

### 발명의 상세한 설명

#### 발명의 목적

#### 발명이 속하는 기술 및 그 분야의 종래기술

- <17> 본 발명은 플라즈마 디스플레이 패널에 관한 것으로서, 더욱 상세하게는 전극 단자부의 불량을 방지하는 플라즈 마 디스플레이 패널에 관한 것이다.

- <18> 플라즈마 디스플레이 패널을 이용하는 플라즈마 디스플레이 장치는 기체 방전현상을 이용하여 화상을 표시하는 평판 디스플레이 장치로서, 휘도, 콘트라스트, 잔상 및 시야각 등의 각종 표시 능력이 우수하며, 박형이고 대화 면 표시가 가능하여 차세대 대형 평판 디스플레이 장치로서 각광을 받고 있다.

- <19> 통상적으로 플라즈마 디스플레이 장치는, 서로 대향되어 배치된 전면기판, 배면기판 및 상기 기판들의 사이에 위치한 복수의 전극들을 구비하는 플라즈마 디스플레이 패널과, 상기 플라즈마 디스플레이 패널을 구동하는 회로기판을 포함하고 있다.

- <20> 종래의 플라즈마 디스플레이 패널에서는, 전면 유리 기판의 내부 표면에는 디스플레이 전극에 해당하는 방전 전 극이 형성되고, 배면 유리 기판의 내부 표면에는 어드레스 전극이 형성된다. 방전 전극은 한 쌍을 이루게 되며, 그 사이에서는 작동 시에 유지 방전이 발생한다. 각 전극들은 신호 전달 수단에 의해 회로 기판과 전기적으로 연결된다. 이 때 각 전극들은 단자부를 포함하고 단자부가 신호 전달 수단과 전기적으로 연결되는데 다수의 단자부를 단일의 신호 전달 수단에 접속하기 힘들다. 이는 신호 전달 수단을 대형화하기 어렵기 때문이다. 각각의 신호 전달 수단에 복수의 단자부를 연결하기 위하여 단자부를 몇 개의 그룹으로 나누어 각 그룹별로 신호 전달 수단에 연결한다. 이 때 각 전극은 단자부를 포함하여 1개로 형성하는데 단자부에서 각 단자들이 단선되는 문제점이 있었다. 또한 신호 전달 수단과의 접촉이 불량한 문제점이 있었다.

#### 발명이 이루고자 하는 기술적 과제

<21> 본 발명은 전극의 단자부 불량을 방지하는 플라즈마 디스플레이 패널을 제공한다.

### 발명의 구성 및 작용

- <22> 본 발명은 서로 마주보는 전면 기판 및 배면 기판, 상기 전면 기판과 배면 기판 사이의 공간을 복수 개의 방전 셀들로 한정하는 격벽, 상기 전면 기판 및 배면 기판 사이에 배치되는 전극들 및 상기 전극들과 전기적으로 연결되는 전극 단자부들을 포함하고, 상기 전극 단자부는 상기 각 전극들의 일 측단을 덮도록 형성되는 플라즈마디스플레이 패널을 개시한다.

- <23> 본 발명에 있어서 상기 전극 단자부들의 두께가 상기 전극들의 두께보다 클 수 있고, 상기 전극 단자부들의 두 께는 상기 전극들의 두께의 2배 이내일 수 있으며, 상기 전극 단자부들의 폭이 상기 전극들의 폭보다 클 수 있다.

- <24> 본 발명에 있어서 상기 전극들은 상기 전극 단자부들에 의해 덮이는 제1 부분과, 상기 전극 단자부들에 의해 덮이지 않는 제2 부분을 포함하고, 상기 제1 부분은 전극 단자부를 향하는 방향으로 갈수록 두께가 감소하도록 그종단면이 테이퍼 형일 수 있다.

- <25> 본 발명에 있어서 상기 전극들은 상기 전극 단자부들에 의해 덮이는 제1 부분과, 상기 전극 단자부들에 의해 덮이지 않는 제2 부분을 포함하고, 상기 제1 부분의 폭이 상기 제2 부분의 폭보다 클 수 있다.

- <26> 본 발명에 있어서 상기 전극 단자부들과 전기적으로 연결되는 신호 전달 수단 및 상기 방전셀들내에 배치되는 형광체를 더 포함할 수 있다.

- <27> 본 발명의 다른 측면에 따르면 기판 상에 복수 개의 방전셀을 구획하는 격벽을 형성하는 단계, 상기 방전셀에 전극들을 형성하는 단계 및 상기 전극들과 전기적으로 연결되는 전극 단자부들을 형성하는 단계를 포함하고, 상 기 전극 단자부들은 상기 각 전극들의 일 측단을 덮도록 형성하는 플라즈마 디스플레이 패널의 제조 방법을 개시한다.

- <28> 본 발명에 있어서 상기 전극 단자부는 옵셋 인쇄법에 의해 형성할 수 있다.

- <29> 이하, 첨부된 도면들에 도시된 본 발명에 관한 실시예를 참조하여 본 발명의 구성 및 작용을 상세히 설명한다.

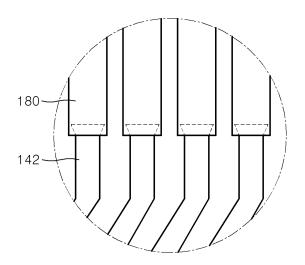

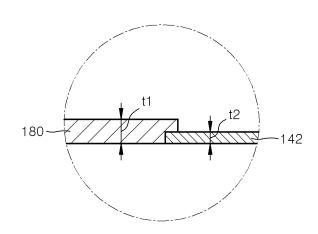

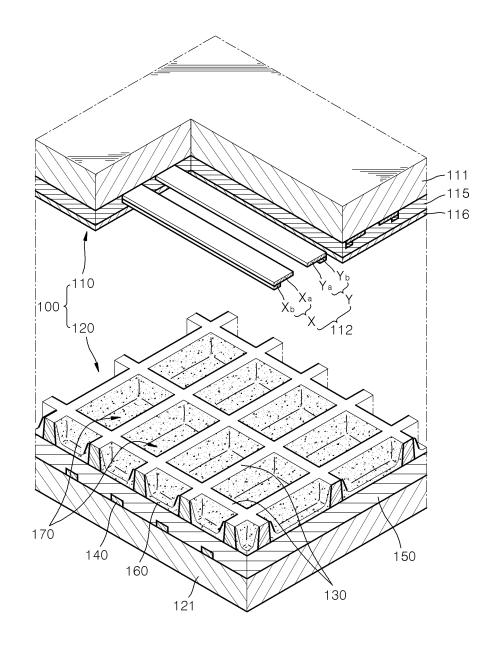

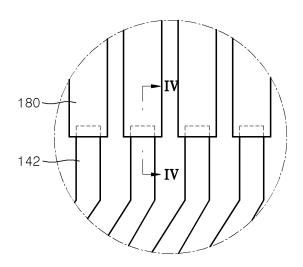

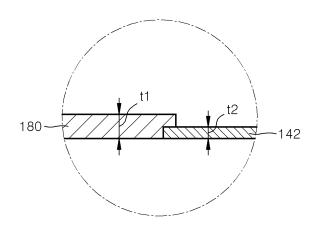

- <30> 도 1은 본 발명의 일 실시예에 관한 플라즈마 디스플레이 패널의 개략적인 분리 사시도이고, 도 2는 본 발명의일 실시예에 관한 플라즈마 디스플레이 패널의 가장자리에 배치된 전극들을 개략적으로 도시한 평면도이다. 도 3은 도 2의 A를 확대한 부분 평면도이고, 도 4는 도 3의 IV-IV선을 따라 절취한 부분 단면도이다.

- <31> 도 1 및 도 2에 도시된 본 발명의 일 실시예에 관한 플라즈마 디스플레이 패널(100)은 크게 서로 대향되어 결합되는 전면 패널(110) 및 배면 패널(120)을 포함한다. 전면 패널(110)은 전면 기판(111), 방전 전극(112)들 및 전면 유전체층(115)을 포함하고, 배면 패널(120)은 배면 기판(121), 어드레스 전극(140), 배면 유전체층(150), 격벽(130) 및 형광체(160)를 포함하며 전면 패널(110)과 배면 패널(120) 사이의 공간에는 방전 기체가 채워져있다. 이하 상세하게 살펴보도록 한다.

- <32> 전면 기판(111)은 일반적으로 가시광의 투과율이 높은 유리를 포함한 재료로 이루어질 수 있다. 그러나 명실 콘트라스트를 향상시키기 위하여 착색될 수도 있다.

- <33> 배면 기판(121)은 전면 기판(111)으로부터 소정의 간격으로 이격되어 대향되도록 배치되는데 유리를 포함한 재료로 이루어질 수 있고 전면 기판(111)과 마찬가지로 명실 콘트라스트 향상을 위하여 착색될 수도 있다. 전면 기판(111)과 배면 기판(121) 사이에는 격벽(130)이 배치되어 있다.

- <34> 격벽(130)은 전면 기판(111)과 배면 기판(121) 사이에 배치되어 방전 공간을 복수 개의 방전셀(170)들로 구획하며, 방전셀(170)들 사이의 광학적/전기적 크로스토크를 방지하는 기능을 한다. 격벽(130)은 직사각형의 횡단면을 가지고 매트릭스형태로 방전셀(170)들을 구획할 수 있다. 보다 상세하게는 방전셀(170)들은 복수 개의 행들과 복수 개의 열들로 구성되어 있다. 그러나 격벽(130)은 이에 한정되지 않고 방전셀(170)을 한정할 수 있는 구조라면 어떠한 모양도 가능하다. 이에 방전셀(170)의 횡단면이 다각형, 원형 또는 타원형 등이 될 수도 있다.

- <35> 전면 기판(111)상에는 방전 전극(112)들이 배치되어 있다. 방전 전극(112)들은 X 전극(X), Y 전극(Y)으로 이루어지고 각각은 서로 이격되어 평행하게 배치되어 있다. X 전극(X), Y 전극(Y)들은 전압이 인가되면 방전을 일으키며 X 전극(X), Y 전극(Y)들은 각각 투명 전극(Xa, Ya)과 버스 전극(Xb, Yb)을 포함한다. 투명 전극(Xa, Ya)은 방전을 일으킬 수 있는 도전체이면서 형광체(160)로부터 방출되는 빛이 전면 기판(111)으로 나아가는 것을

방해하지 않는 투명한 재료로 형성되는데 ITO(indium tin oxide)를 포함하는 투명한 물질로 형성될 수 있다. 그런데 ITO와 같은 투명한 도전성 물질은 일반적으로 저항이 크므로 투명 전극(Xa, Ya)으로만 방전 전극(X, Y)을 형성하면 투명 전극(Xa, Ya)의 길이가 길어짐에 따라 길이방향으로 전압강하가 커서 구동전력이 많이 소비되고 응답속도가 늦어진다. 그래서 이러한 문제점을 해결하기 위하여 투명 전극(Xa, Ya)상에 각각 금속재질로 이루어지고 좁은 폭으로 형성되는 버스 전극(Xb, Yb)이 배치된다. 투명 전극(Xa, Ya)들 및 버스 전극(Xb, Yb)들은 포토 에칭법, 포토 리소그래피법 등을 이용하여 형성한다. 이때 투명 전극(Xa, Ya)들은 길게 연장된 구조로 형성될 수도 있고 직사각형으로 형성될 수 있으며 다양한 형태로 형성이 가능하다.

- <36> 전면 기판(111)상에 방전 전극(X, Y)들을 덮도록 전면 유전체층(115)이 형성된다. 전면 유전체층(115)은 인접한투명 전극(X, Y)들이 서로 통전되는 것을 방지함과 동시에 전자들이 방전 전극(X, Y)에 직접 충돌하여 방전 전극(X, Y)을 손상 시키는 것을 방지하기 위해 형성한다. 또한 전하를 유도하는 기능을 하여 벽전하 생성을 용이하게 한다. 이러한 전면 유전체층(115)은 절연성이 우수한 SiO<sub>2</sub>, PbO 또는 Al<sub>2</sub>O<sub>3</sub> 계열의 세라믹 재료가 혼합된 재료 등으로 이루어진다.

- <37> 전면 기판(111)의 전면 유전체층(115)상에 보호층(116)이 형성될 수 있다. 보호층(116)은 플라즈마 디스플레이 패널(100)의 방전 시 양이온과 전자가 전면 유전체층(115)에 충돌하여 전면 유전체층(115)이 손상되는 것을 방지하며 방전셀(170)내에서 2차 전자의 방출을 증가시키기 위한 목적으로 형성한다. 보호층(116)은 내전압 성질이 우수한 강유전체인 MgO 등을 포함한 재료로 형성될 수 있고 주로 스퍼터링, 전자빔 증착법 등을 이용하여 박막으로 형성된다.

- <38> 전면 기판(111)과 대향하여 결합하는 배면 기판(121)상에는 소정의 패턴으로 형성되는 어드레스 전극(140)을 형성한다. 어드레스 전극(140)들은 전면 기판(111)의 방전 전극(X, Y)들과 교차하도록 방전셀(170)들을 가로질 러 연장되어 형성된다. 어드레스 전극(140)들은 방전 전극(X, Y)간의 유지 방전을 보다 용이하게 하기 위한 어 드레스 방전을 일으키기 위한 것으로서 구체적으로는 유지 방전이 일어나기 위한 전압을 낮추는 역할을 한다.

- <39> 한편, 방전 전극(112)들 및 어드레스 전극(140)들은 방전부 및 연결부를 포함한다. 방전부는 방전을 직접 수행하는 부분이다. 연결부는 방전부와 연결되고 전극의 끝단을 포함한다. 전극들(112,140)의 이러한 구조는 종류에 관계없이 유사하므로 본 발명의 실시예에서는 어드레스 전극(140)에 대해서만 설명하기로 한다.

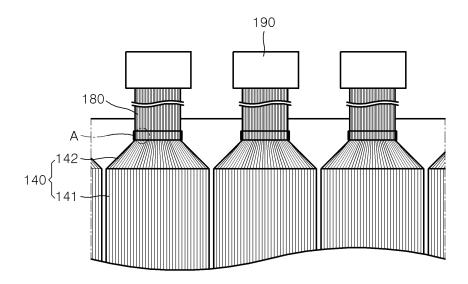

- <40> 어드레스 전극 단자부(180)가 어드레스 전극(140)의 일측단을 덮도록 어드레스 전극(140)과 별도로 형성된다. 어드레스 전극 단자부(180)는 어드레스 전극(140)의 연결부(142)의 끝단을 덮게 된다. 또한 어드레스 전극 단자부(180)는 배면 기판(121)에 배치되며 신호 전달 수단(190)과 전기적으로 연결되는 부분이다. 어드레스 전극 단자부(180)를 통하여 어드레스 전극(140)과 신호 전달 수단(190)이 전기적으로 연결된다.

- <41> 어드레스 전극(140)의 방전부(141)는 배면 기판(121)의 안쪽 면에 배치되어 방전 전극(112)의 방전부와 함께 어드레스 방전을 수행하는데, 스트라이프 형상으로 형성된다. 본 실시예의 방전부(141)는 스트라이프 형상으로 형성되어 방전셀(170)들의 하부 중앙을 가로지르도록 배치되나, 본 발명은 이에 한정하지 않는다. 즉, 본 발명의 방전부(141)는 방전셀(170)의 적어도 일부를 둘러싸도록 배치될 수 있다.

- <42> 어드레스 전극 단자부(180)는 배면 기판(121)의 각 가장자리에 배치되며, 신호 전달 수단(190)과 연결되기 위하여 외부로 노출이 되어 있다. 싱글 스캔 방식에서는 한 방향으로만 스캔하므로, 어드레스 전극(140)의 일 측에만 전극 단자가 형성되어 신호 전달 수단(190)과 연결되고 더블 스캔 방식의 경우에는 일 측 및 타 측에 신호 전달 수단(190)이 연결된다. 어드레스 전극 단자부(180)는 어드레스 전극(140)과 전기적으로 연결되도록 어드레스 전극의 연결부(142)의 일 측단을 덮도록 형성한다. 본 발명은 어드레스 전극(140)을 전극 단자부(180)를 포함하여 1개의 구조로 형성하지 않고 어드레스 전극 단자부(180)와 어드레스 전극(140)을 별도로 형성한다. 이를통하여 어드레스 전극 단자부(180)에서 생기는 단선 등의 문제를 줄일 수 있다. 즉 가늘고 긴 어드레스 전극(140)을 단자부(180)를 포함하여 한 번에 1개의 구조로 형성할 경우 어드레스 전극 단자부(180)에서 단선의 우려가 있었고 특히 신호 전달 수단(190)과 접촉하는 부위 근방에서 이러한 단선의 문제점이 컸었다. 그러나 어드레스 전극(140)을 형성하여 어드레스 전극 단자부(180)에서의 단선을 줄일 수 있다.

- <43> 어드레스 전극 단자부(180)의 폭은 어드레스 전극(140)의 폭보다 크게 형성한다. 어드레스 전극(140)과 어드레스 전극 단자부(180)를 따로 형성할 경우에 어드레스 전극 단자부(180)의 패터닝이 부정확할 경우에 어드레스 전극 단자부(180)와 어드레스 전극(140)의 전기적 연결의 신뢰성이 감소할 가능성이 있다. 어드레스 전극 단자부(180)의 폭을 어드레스 전극(140)의 폭보다 크게 하여 어드레스 전극 단자부(180)와 어드레스 전극(140)의 전

기적 연결을 더 용이하게 할 수 있다. 결과적으로 어드레스 전극(140)과 어드레스 전극 단자부(180)의 전기적 연결의 신뢰성이 향상된다. 또한 어드레스 전극 단자부(180)의 폭이 늘어남에 따라 신호 전달 수단(190)과 전기적으로 연결되는 면이 넓어져 신호 전달 수단(190)과의 전기적 연결의 신뢰성도 향상된다. 나아가 어드레스 전극 단자부(180)의 폭이 늘어나 단면적이 커지므로 어드레스 전극 단자부(180)의 저항 특성도 향상된다.

- <44> 어드레스 전극 단자부(180)의 두께(t1)는 어드레스 전극(140)의 두께(t2)보다 크게 형성한다. 이를 통하여 어드레스 전극 단자부(180)와 어드레스 전극(140)과의 전기적 연결 및 어드레스 전극 단자부(180)와 신호 전달 수단 (190)과의 전기적 연결의 신뢰성을 향상시킬 수 있다. 또한 어드레스 전극 단자부(180)의 저항 특성이 향상될수 있고 방전 특성 또한 향상될수 있다. 그러나 어드레스 전극 단자부(180)가 지나치게 두꺼우면 방전 특성이 저하되고, 어드레스 전극 단자부(180)에서 메탈 마이그레이션, 수증기 흡착 또는 황부식을 통한 단락이 일어나기 쉽다. 어드레스 전극 단자부(180)의 두께(t1)는 어드레스 전극(140)의 두께(t2)의 2배 이내로 형성할수 있다. 즉 t1<2\*t2식이 성립한다.</p>

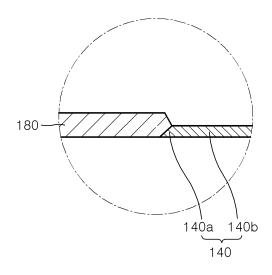

- <45> 도 5는 본 발명의 일 실시예에 관한 플라즈마 디스플레이 패널의 전극 단자부의 다른 변형예를 도시한 단면도이다.도 5를 참조하면 어드레스 전극(140)은 어드레스 전극 단자부(180)와 전기적으로 연결되는 일 측으로 갈수록 그 두께가 감소하여 테이퍼형으로 형성된다.즉 어드레스 전극(140)은 어드레스 전극 단자부(180)로 덮이는 부분인 제1 부분(140a)과 어드레스 전극 단자부(180)로 덮이지 않는 제2 부분(140b)을 포함한다.제1 부분(140a)은 어드레스 전극 단자부(180)를 향하는 방향으로 갈수록 두께가 감소하도록 형성하여 테이퍼 형상을 가진다.어드레스 전극(140)의 제1 부분(140a)이 테이퍼 형상으로 형성되어 어드레스 전극 단자부(180)를 형성할때,어드레스 전극(140)가 어드레스 전극(140)가 어드레스 전극(140)의 일 측단을 쉽게 덮을 수 있다.결과적으로 어드레스 전극(140)과 어드레스 전극 단자부(180)의 전기적 연결의 신뢰성을 더 향상시킬 수 있다.또한 어드레스 전극(140)을 형성한 후에 어드레스 전극 단자부(180)를 어드레스 전극(140)보다 두껍게 형성하게 되면 어드레스 전극 단자부(180)의 하중에 의하여 어드레스 전극(140)이 눌려 변형되어 어드레스 전극(140)의 제1 부분(140a)이 자연스럽게 테이퍼 형상을 가지게 될 수도 있다.이 경우 어드레스 전극 단자부(180)의 끝단도 자연스럽게 약간의 경사를 가지도록 형성되기도 한다.

- <46> 도 6은 본 발명의 일 실시예에 관한 플라즈마 디스플레이 패널의 전국 단자부의 또 다른 변형예를 도시한 평면 도이다. 도 6을 참조하면 어드레스 전극(140)들은 어드레스 전극 단자부(180)들에 의해 덮이는 제1 부분(140a)과, 어드레스 전극 단자부(180)들에 의해 덮이지 않는 제2 부분(140b)을 포함한다. 어드레스 전극(140)은 제1 부분(140a)의 폭이 제2 부분(140b)의 폭보다 크도록 형성할 수 있다. 이를 통하여 어드레스 전극(140)과 어드레스 전극 단자부(180)의 전기적 연결의 신뢰성을 향상시킬 수 있다. 또한 어드레스 전극(140)을 형성한 후에 어드레스 전극 단자부(180)를 어드레스 전극(140)보다 두껍게 형성하게 되면 어드레스 전극 단자부(180)의 하중에 의하여 어드레스 전극(140)이 눌려 변형되어 자연스럽게 어드레스 전극(140)의 제1 부분(140a)의 폭이 제2 부분 (140b)의 폭보다 크게 형성될 수도 있다. 도 6에서는 제1 부분(140a)을 사다리꼴로 도시하고 있으나 이에 한정되지 않는다. 즉 제1 부분(140a)은 제2 부분(140b)보다 폭이 크면 되므로 직사각형 등 다양한 형상이 가능하다.

- <47> 어드레스 전극(140)은 스크린 인쇄법, 포토 리소그래피법 또는 리프트 오프법 등 다양한 방법으로 형성할 수 있다.

- <48> 어드레스 전극 단자부(180)는 어드레스 전극(140)을 형성한 후에 옵셋(offset) 인쇄 방법을 이용하여 형성할 수 있다. 옵셋 인쇄법을 이용하여 어드레스 전극 단자부(180)의 폭 및 두께를 용이하게 조절할 수 있다. 그리고 스크린 인쇄법과 달리 소성 공정이 불필요하여 원하는 모양의 어드레스 전극 단자부(180)의 모양을 형성하기 용이하다. 그러나 기타 다양한 방법을 사용하여 어드레스 전극 단자부(180)를 형성할 수 있다.

- <49> 신호 전달 수단(190)은 플라즈마 디스플레이 패널(100)을 구동하는 구동회로기판(미도시)과 전기적으로 연결되어 있는데, 신호 전달 수단(190)으로는 플렉시블 프린티드 케이블(flexible printed cable: FPC)이나, 테이프 캐리어 패키지(tape carrier package: TCP) 등이 사용된다. 신호 전달 수단(190)은 전기적 신호를 전달하는 각 각의 도선들을 포함하고 있는데, 각각의 도선들은 어드레스 전극 단자부(180)에 전기적으로 연결되어 있다. 신호 전달 수단(190)의 도선과 어드레스 전극 단자부(180)사이의 연결은 이방성 도전 필름(anisotropic conductive film)에 의해 이루어질 수 있다.

- <50> 배면 기판(121)상에는 어드레스 전극(140)을 덮도록 배면 유전체층(150)이 형성될 수 있다. 배면 유전체층(150)은 방전 시 전자 등이 어드레스 전극(140)들에 충돌하여 어드레스 전극(140)을 손상시키는 것을 방지하고 전하를 유도하는 기능을 한다. 배면 유전체층(150)은 Pb0, ₽0₃, Si0₂ 등으로 형성할 수 있다.

- <51> 배면 기판(121)에 형성된 배면 유전체층(150)상에 형광체(160)가 도포된다. 형광체(160)는 적색, 녹색, 청색발 광 형광체(160)로 도포될 수 있다. 형광체(160)는 진공 자외선을 받아 가시광선을 발생하는 성분을 가지는데 적색 발광 형광체(160)는 Y(V, P)O<sub>4</sub>:Eu 등과 같은 형광체를 포함하고, 녹색발광 형광체(160)는 Zn<sub>2</sub>SiO<sub>4</sub>:Mn, YBO<sub>3</sub>:Tb 등과 같은 형광체를 포함하며, 청색발광 형광체(160)는 BAM:Eu 등과 같은 형광체를 포함한다.

- <52> 방전셀(170) 내에는 네온(Ne), 제논(Xe) 등이 혼합된 방전 기체가 채워지며 방전 기체가 채워진 상태에서 전면 기판(111) 및 배면 기판(121)의 가장 자리에 형성된 프릿트 글라스(frit glass)와 같은 밀봉 부재에 의해 전면 기판(111) 및 배면 기판(121)이 서로 봉합되어 결합된다.

- <53> 상술한 바와 같이 구성된 본 발명의 일 실시예에 관한 플라즈마 디스플레이 패널(100)의 작동을 설명하면 다음 과 같다.

- <54> 어드레스 전극(140)과 Y 전극(Y)들 간에 어드레스 전압이 인가됨으로써 어드레스 방전이 일어나고 이 어드레스 방전의 결과로 유지방전이 일어나게 될 방전셀(170)을 선택한다. 그 후 상기 선택된 방전셀(170)들의 X 전극(X)과 Y 전극(Y)들 사이에 유지 전압이 인가되면 유지 방전이 발생한다.

- <55> 이렇게 유지 방전이 발생할 때 여기된 방전 기체의 에너지 준위가 낮아지면서 자외선이 방출된다. 그리고 이 자외선이 방전셀(170) 내에 도포된 형광체(160)를 여기 시키는데 이 때 여기된 형광체(160)의 에너지 준위가 낮아지면서 가시광이 방출되며 이 방출된 가시광이 화상을 구현하게 된다. 이 때 방출된 가시광은 전면 패널(100)을 통과하여 사람의 눈으로 인식하게 된다. 이 때 어드레스 전극 단자부(180)는 어드레스 전극(140)과 별도로 형성한다. 어드레스 전극 단자부(180)를 어드레스 전극(140)의 일 측을 덮도록 형성하여 어드레스 전극(140)과 어드레스 전극 단자부(180)와의 전기적 연결의 신뢰성을 향상시킨다. 또한 어드레스 전극 단자부(180)의 폭과 두께를 크게 하여 어드레스 전극(140)과 어드레스 전극 단자부(180)와의 전기적 연결 및 어드레스 전극 단자부(180)와 신호 전달 수단(190)과의 전기적 연결의 신뢰성도 향상시키며 어드레스 전극 단자부(180)의 저항 특성도개선된다.

#### 발명의 효과

- <56> 본 발명에 관한 플라즈마 디스플레이 패널은 전극 단자부 불량을 방지할 수 있는 효과를 갖는다.

- <57> 본 발명은 도면에 도시된 실시예를 참고로 설명되었으나 이는 예시적인 것에 불과하며, 본 기술 분야의 통상의 지식을 가진 자라면 이로부터 다양한 변형 및 균등한 다른 실시예가 가능하다는 점을 이해할 것이다. 따라서, 본 발명의 진정한 기술적 보호 범위는 첨부된 특허청구범위의 기술적 사상에 의하여 정해져야 할 것이다.

### 도면의 간단한 설명

- <!> 도 1은 본 발명의 일 실시예에 관한 플라즈마 디스플레이 패널의 개략적인 분리 사시도이다.

- <2> 도 2는 본 발명의 일 실시예에 관한 플라즈마 디스플레이 패널의 가장자리에 배치된 전극들을 개략적으로 도시한 평면도이다.

- <3> 도 3은 도 2의 A를 확대한 부분 평면도이다.

- <4> 도 4는 도 3의 IV-IV선을 따라 절취한 부분 단면도이다.

- <5> 도 5는 본 발명의 일 실시예에 관한 플라즈마 디스플레이 패널의 전극 단자부의 다른 변형예를 도시한 단면도이다.

- <6> 도 6은 본 발명의 일 실시예에 관한 플라즈마 디스플레이 패널의 전극 단자부의 또 다른 변형예를 도시한 평면 도이다.

- <7> <도면의 주요 부분에 대한 부호의 간단한 설명>

- <8> 100: 플라즈마 디스플레이 패널 110: 전면 패널

- <9> 111: 전면 기판 112: 방전 전극

- <10> 115: 전면 유전체층 116: 보호층

- <11> 120: 배면 패널 121: 배면 기판

<12> 130: 격벽 140: 어드레스 전극

<13> 141: 어드레스 전극의 방전부 142: 어드레스 전극의 연결부

<14> 150: 배면 유전체층 160: 형광체

<15> 170: 방전셀 180: 어드레스 전극 단자부

<16> 190: 신호 전달 수단

## 도면

## 도면1

## 도면2

## 도면3

## 도면4

## 도면5

## 도면6