(19) 日本国特許庁(JP)

## (12) 公開特許公報(A)

(11) 特許出願公開番号

特開2016-181696

(P2016-181696A)

(43) 公開日 平成28年10月13日(2016.10.13)

| (51) Int.Cl.                  | F 1        | テーマコード (参考) |       |  |

|-------------------------------|------------|-------------|-------|--|

| <b>HO1L 21/336 (2006.01)</b>  | HO1L 29/78 | 616L        | 2H192 |  |

| <b>HO1L 29/786 (2006.01)</b>  | HO1L 29/78 | 618B        | 5C094 |  |

| <b>HO1L 21/8234 (2006.01)</b> | HO1L 29/78 | 616V        | 5F048 |  |

| <b>HO1L 27/088 (2006.01)</b>  | HO1L 29/78 | 627Z        | 5F083 |  |

| <b>HO1L 21/322 (2006.01)</b>  | HO1L 27/08 | 102E        | 5F110 |  |

審査請求 未請求 請求項の数 8 O L (全 114 頁) 最終頁に続く

|              |                            |            |                                |

|--------------|----------------------------|------------|--------------------------------|

| (21) 出願番号    | 特願2016-58188 (P2016-58188) | (71) 出願人   | 000153878                      |

| (22) 出願日     | 平成28年3月23日 (2016.3.23)     |            | 株式会社半導体エネルギー研究所                |

| (31) 優先権主張番号 | 特願2015-60420 (P2015-60420) |            | 神奈川県厚木市長谷398番地                 |

| (32) 優先日     | 平成27年3月24日 (2015.3.24)     | (72) 発明者   | 山崎 舜平                          |

| (33) 優先権主張国  | 日本国 (JP)                   |            | 神奈川県厚木市長谷398番地 株式会社            |

| (31) 優先権主張番号 | 特願2015-60421 (P2015-60421) |            | 半導体エネルギー研究所内                   |

| (32) 優先日     | 平成27年3月24日 (2015.3.24)     | F ターム (参考) | 2H192 AA24 BC31 CB05 CB08 CB37 |

| (33) 優先権主張国  | 日本国 (JP)                   |            | CB53 DA12 DA42 EA67 FB02       |

| (31) 優先権主張番号 | 特願2015-66943 (P2015-66943) |            | 5C094 AA21 AA25 BA03 BA27 BA43 |

| (32) 優先日     | 平成27年3月27日 (2015.3.27)     |            | CA19 DA13 DA15 FA02 FB02       |

| (33) 優先権主張国  | 日本国 (JP)                   |            | FB05 FB14 FB15 GB01 HA05       |

|              |                            |            | HA07 HA08 JA01 JA09            |

最終頁に続く

(54) 【発明の名称】半導体装置の作製方法

## (57) 【要約】

【課題】安定した電気特性を有するトランジスタを提供する。

【解決手段】基板上、酸化物半導体と、第1の導電体と、第1の絶縁体と、第2の絶縁体と、第3の絶縁体と、を有し、酸化物半導体は第1の絶縁体上に配置され、第2の絶縁体は酸化物半導体上に配置され、第3の絶縁体は第2の絶縁体上に配置され、第1の導電体は第3の絶縁体上に配置される半導体装置の作製方法であって、酸化物半導体は、第1の領域と、第2の領域と、を有し、第1の領域は、第1の導電体をマスクとして、酸化物半導体にイオン注入を行った後、第1の導電体をマスクとして、酸化物半導体に水素の添加を行うことによって形成することを特徴とする半導体装置の作製方法である。

【選択図】図 1

**【特許請求の範囲】****【請求項 1】**

基板上の、酸化物半導体と、第1の導電体と、第1の絶縁体と、第2の絶縁体と、第3の絶縁体と、を有し、前記酸化物半導体は前記第1の絶縁体上に配置され、前記第2の絶縁体は前記酸化物半導体上に配置され、前記第3の絶縁体は前記第2の絶縁体上に配置され、前記第1の導電体は前記第3の絶縁体上に配置される半導体装置の作製方法であって、

前記酸化物半導体は、第1の領域と、第2の領域と、を有し、

前記第1の領域は、前記第1の導電体をマスクとして、前記酸化物半導体にイオン注入を行った後、前記第1の導電体をマスクとして、前記酸化物半導体に水素の添加を行うことによって形成することを特徴とする半導体装置の作製方法。 10

**【請求項 2】**

基板上の、酸化物半導体と、第1の導電体と、第1の絶縁体と、第2の絶縁体と、第3の絶縁体と、を有し、前記酸化物半導体は前記第1の絶縁体上に配置され、前記第2の絶縁体は前記酸化物半導体上に配置され、前記第3の絶縁体は前記第2の絶縁体上に配置され、前記第1の導電体は前記第3の絶縁体上に配置される半導体装置の作製方法であって、

前記酸化物半導体は、第1の領域と、第2の領域と、を有し、

前記第1の領域は、前記第1の導電体をマスクとして、前記酸化物半導体にイオン注入を行った後、加熱処理を行うことで前記第2の領域にある水素をゲッタリングさせることによって形成することを特徴とする半導体装置の作製方法。 20

**【請求項 3】**

基板上の、酸化物半導体と、第1の導電体と、第1の絶縁体と、第2の絶縁体と、第3の絶縁体と、を有し、前記酸化物半導体は前記第1の絶縁体上に配置され、前記第2の絶縁体は前記酸化物半導体上に配置され、前記第3の絶縁体は前記第2の絶縁体上に配置され、前記第1の導電体は前記第3の絶縁体上に配置される半導体装置の作製方法であって、

前記酸化物半導体は、第1の領域と、第2の領域と、を有し、

前記第1の領域は、前記第1の導電体をマスクとして、前記酸化物半導体にイオン注入を行った後、前記第1の導電体の側面に接して第4の絶縁体を形成し、前記第1の導電体と前記第4の絶縁体をマスクとして、前記酸化物半導体に水素の添加を行うことによって形成することを特徴とする半導体装置の作製方法。 30

**【請求項 4】**

請求項1乃至請求項3のいずれか一において、

前記イオン注入によって、少なくとも前記酸化物半導体に酸素欠損を形成することを特徴とする半導体装置の作製方法。

**【請求項 5】**

請求項1乃至請求項4のいずれか一において、

前記イオン注入によって、ヘリウムイオン、ネオンイオン、アルゴンイオン、クリプトンイオンまたはキセノンイオンを注入することを特徴とする半導体装置の作製方法。 40

**【請求項 6】**

請求項1乃至請求項5のいずれか一において、

前記イオン注入は、前記基板面の法線に対して  $10^{\circ}$  以上  $60^{\circ}$  以下の入射角となるように注入する第1のステップと、 $-60^{\circ}$  以上  $-10^{\circ}$  以下の入射角となるように注入する第2のステップと、を有することを特徴とする半導体装置の作製方法。

**【請求項 7】**

請求項1乃至請求項6のいずれか一において、

前記第2の領域は、キャリア密度が  $1 \times 10^9$  個 /  $\text{cm}^3$  未満である領域を有することを特徴とする半導体装置の作製方法。

**【請求項 8】**

10

20

30

40

50

請求項 1 乃至 請求項 7 のいずれか一において、

前記第 1 の絶縁体、前記第 2 の絶縁体および前記酸化物半導体は、ガリウムを有することを特徴とする半導体装置の作製方法。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、例えば、トランジスタおよび半導体装置に関する。または、本発明は、例えば、トランジスタおよび半導体装置の製造方法に関する。または、本発明は、例えば、表示装置、発光装置、照明装置、蓄電装置、記憶装置、プロセッサ、電子機器に関する。または、表示装置、液晶表示装置、発光装置、記憶装置、電子機器の製造方法に関する。または、表示装置、液晶表示装置、発光装置、記憶装置、電子機器の駆動方法に関する。

10

【0002】

なお、本発明の一態様は、上記の技術分野に限定されない。本明細書等で開示する発明の一態様の技術分野は、物、方法、または、製造方法に関するものである。または、本発明の一態様は、プロセス、マシン、マニュファクチャ、または、組成物（コンポジション・オブ・マター）に関するものである。

【0003】

なお、本明細書等において半導体装置とは、半導体特性を利用して機能しうる装置全般を指す。表示装置、発光装置、照明装置、電気光学装置、半導体回路および電子機器は、半導体装置を有する場合がある。

20

【背景技術】

【0004】

絶縁表面を有する基板上の半導体を用いて、トランジスタを構成する技術が注目されている。当該トランジスタは集積回路や表示装置のような半導体装置に広く応用されている。トランジスタに適用可能な半導体としてシリコンが知られている。

【0005】

トランジスタの半導体に用いられるシリコンは、用途によって非晶質シリコンと多結晶シリコンとが使い分けられている。例えば、大型の表示装置を構成するトランジスタに適用する場合、大面積基板への成膜技術が確立されている非晶質シリコンを用いると好適である。一方、駆動回路を一体形成した高機能の表示装置を構成するトランジスタに適用する場合、高い電界効果移動度を有するトランジスタを作製可能な多結晶シリコンを用いると好適である。多結晶シリコンは、非晶質シリコンに対し高温での熱処理、またはレーザ光処理を行うことで形成する方法が知られる。

30

【0006】

近年では、酸化物半導体（代表的には  $In - Ga - Zn$  酸化物）を用いたトランジスタの開発が活発化している。酸化物半導体の歴史は古く、1988年には、結晶  $In - Ga - Zn$  酸化物を半導体素子へ利用することが開示されている（特許文献 1 参照。）。また、1995年には、酸化物半導体を用いたトランジスタが発明されており、その電気特性が開示されている（特許文献 2 参照。）。

40

【0007】

2010年には、非晶質  $In - Ga - Zn$  酸化物を用いたトランジスタと比べ、優れた電気特性および信頼性を有する、結晶性  $In - Ga - Zn$  酸化物を用いたトランジスタが開発された（特許文献 3 参照。）。該結晶性  $In - Ga - Zn$  酸化物は、c 軸配向性を有することから、CAAC-OS（C-Axis-Aligned Crystalline Oxide Semiconductor）などとも呼ばれている。

【0008】

CAAC-OS を用いたトランジスタは、その発見以降、優れた電気特性を有することが報告されてきた。CAAC-OS を用いたトランジスタは、例えば、以下のような点においては、シリコンを用いたトランジスタよりも優れた特性を有している。

50

【0009】

CAAC-OSを用いたトランジスタは、短チャネルであってもフォノン散乱の影響が小さいため、電界効果移動度の低下が起こりにくいことが報告されている（非特許文献1参照。）。また、CAAC-OSを用い、surrounded channel(s-channel)構造を有するトランジスタは、短チャネルにおいても良好なスイッチング特性を有することが報告されている（非特許文献2参照。）。また、CAAC-OSを用いたトランジスタは高い動作速度を有する。例えば、20GHzの遮断周波数が報告されている（非特許文献3参照。）。また、CAAC-OSを用いたトランジスタは、高い耐圧特性を有することが報告されている（特許文献4参照。）。また、CAAC-OSを用いたトランジスタは、温度による特性の変動が小さいことが報告されている（特許文献5参照。）。

10

## 【0010】

また、酸化物半導体を用いたトランジスタは、非晶質シリコンを用いたトランジスタ、および多結晶シリコンを用いたトランジスタとは異なる特徴を有する。例えば、酸化物半導体を用いたトランジスタを適用した表示装置は、消費電力が低いことが知られている。酸化物半導体は、スパッタリング法などを用いて成膜できるため、大型の表示装置を構成するトランジスタに用いることができる。また、酸化物半導体を用いたトランジスタは、高い電界効果移動度を有するため、駆動回路を一体形成した高機能の表示装置を実現できる。また、非晶質シリコンを用いたトランジスタの生産設備の一部を改良して利用することが可能であるため、設備投資を抑えられるメリットもある。

20

## 【先行技術文献】

## 【特許文献】

## 【0011】

【特許文献1】特開昭63-239117

【特許文献2】特表平11-505377

【特許文献3】特開2011-86923

【特許文献4】特開2012-256838

【特許文献5】特開2013-250262

## 【0012】

【非特許文献1】S. Matsuda et al. : Extended Abstracts International Conference on Solid State Devices and Materials, 2014, pp 138-139

30

【非特許文献2】Y. Kobayashi et al. : IEEE ELECTRON DEVICE LETTERS, April 2015, Vol. 36, No. 4, pp 309-311

【非特許文献3】Y. Yakubo et al. : Extended Abstracts International Conference on Solid State Devices and Materials, 2014, pp 648-649

## 【発明の概要】

## 【発明が解決しようとする課題】

## 【0013】

安定した電気特性を有するトランジスタを提供することを課題の一とする。または、非導通時のリーク電流の小さいトランジスタを提供することを課題の一とする。または、オン電流の大きいトランジスタを提供することを課題の一とする。または、ノーマリーオフの電気特性を有するトランジスタを提供することを課題の一とする。または、サブスレッショルドスイッチング値の小さいトランジスタを提供することを課題の一とする。または、信頼性の高いトランジスタを提供することを課題の一とする。

## 【0014】

または、該トランジスタを有する半導体装置を提供することを課題の一とする。または

40

50

、該半導体装置を有するモジュールを提供することを課題の一とする。または、該半導体装置、または該モジュールを有する電子機器を提供することを課題の一とする。または、新規な半導体装置を提供することを課題の一とする。または、新規なモジュールを提供することを課題の一とする。または、新規な電子機器を提供することを課題の一とする。

#### 【0015】

なお、これらの課題の記載は、他の課題の存在を妨げるものではない。なお、本発明の一態様は、これらの課題の全てを解決する必要はないものとする。なお、これら以外の課題は、明細書、図面、請求項などの記載から、自ずと明らかとなるものであり、明細書、図面、請求項などの記載から、これら以外の課題を抽出することが可能である。

#### 【課題を解決するための手段】

#### 【0016】

(1) 本発明の一態様は、基板上の、酸化物半導体と、第1の導電体と、第1の絶縁体と、第2の絶縁体と、第3の絶縁体と、を有し、酸化物半導体は第1の絶縁体上に配置され、第2の絶縁体は酸化物半導体上に配置され、第3の絶縁体は第2の絶縁体上に配置され、第1の導電体は第3の絶縁体上に配置される半導体装置の作製方法であって、酸化物半導体は、第1の領域と、第2の領域と、を有し、第1の領域は、第1の導電体をマスクとして、酸化物半導体にイオン注入を行った後、第1の導電体をマスクとして、酸化物半導体に水素の添加を行うことによって形成することを特徴とする半導体装置の作製方法である。

#### 【0017】

(2) 本発明の一態様は、基板上の、酸化物半導体と、第1の導電体と、第1の絶縁体と、第2の絶縁体と、第3の絶縁体と、を有し、酸化物半導体は第1の絶縁体上に配置され、第2の絶縁体は酸化物半導体上に配置され、第3の絶縁体は第2の絶縁体上に配置され、第1の導電体は第3の絶縁体上に配置される半導体装置の作製方法であって、酸化物半導体は、第1の領域と、第2の領域と、を有し、第1の領域は、第1の導電体をマスクとして、酸化物半導体にイオン注入を行った後、加熱処理を行うことで第2の領域にある水素をゲッタリングさせることによって形成することを特徴とする半導体装置の作製方法である。

#### 【0018】

(3) 本発明の一態様は、基板上の、酸化物半導体と、第1の導電体と、第1の絶縁体と、第2の絶縁体と、第3の絶縁体と、を有し、酸化物半導体は第1の絶縁体上に配置され、第2の絶縁体は酸化物半導体上に配置され、第3の絶縁体は第2の絶縁体上に配置され、第1の導電体は第3の絶縁体上に配置される半導体装置の作製方法であって、酸化物半導体は、第1の領域と、第2の領域と、を有し、第1の領域は、第1の導電体をマスクとして、酸化物半導体にイオン注入を行った後、第1の導電体の側面に接して第4の絶縁体を形成し、第1の導電体と第4の絶縁体をマスクとして、酸化物半導体に水素の添加を行うことによって形成することを特徴とする半導体装置の作製方法である。

#### 【0019】

上述の半導体装置の作製方法においてイオン注入によって、少なくとも酸化物半導体に酸素欠損を形成することが好ましい。

#### 【0020】

上述の半導体装置の作製方法においてイオン注入によって、ヘリウムイオン、ネオンイオン、アルゴンイオン、クリプトンイオンまたはキセノンイオンを注入することが好ましい。

#### 【0021】

上述の半導体装置の作製方法においてイオン注入は、基板面の法線に対して  $10^{\circ}$  以上  $60^{\circ}$  以下の入射角となるように注入する第1のステップと、 $-60^{\circ}$  以上  $-10^{\circ}$  以下の入射角となるように注入する第2のステップと、を有することが好ましい。

#### 【0022】

上述の半導体装置の作製方法において第2の領域は、キャリア密度が  $1 \times 10^9$  個 /  $\text{cm}^2$

10

20

30

40

50

$m^3$  未満である領域を有することが好ましい。

【0023】

上述の半導体装置の作製方法において第1の絶縁体、第2の絶縁体および酸化物半導体は、酸素およびガリウムを有していてもよい。

【発明の効果】

【0024】

安定した電気特性を有するトランジスタを提供することができる。または、非導通時のリーコンデンサーの小さいトランジスタを提供することができる。または、オン電流の大きいトランジスタを提供することができる。または、ノーマリーオフの電気特性を有するトランジスタを提供することができる。または、サブスレッショルドスイング値の小さいトランジスタを提供することができる。または、信頼性の高いトランジスタを提供することができる。

10

【0025】

または、該トランジスタを有する半導体装置を提供することができる。または、該半導体装置を有するモジュールを提供することができる。または、該半導体装置、または該モジュールを有する電子機器を提供することができる。または、新規な半導体装置を提供することができる。または、新規なモジュールを提供することができる。または、新規な電子機器を提供することができる。

【0026】

なお、これらの効果の記載は、他の効果の存在を妨げるものではない。なお、本発明の一態様は、これらの効果の全てを有する必要はない。なお、これら以外の効果は、明細書、図面、請求項などの記載から、自ずと明らかとなるものであり、明細書、図面、請求項などの記載から、これら以外の効果を抽出することが可能である。

20

【図面の簡単な説明】

【0027】

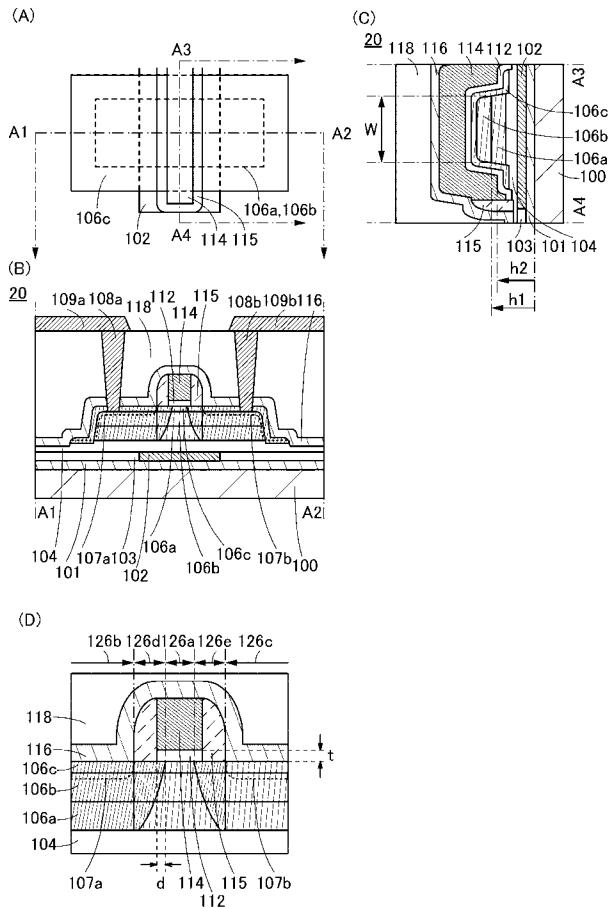

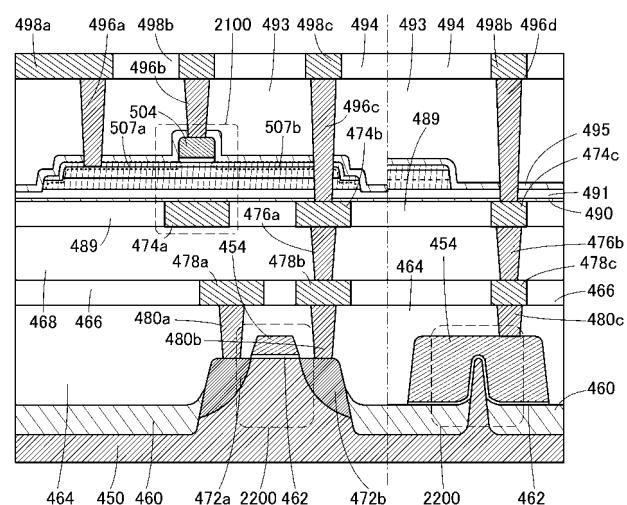

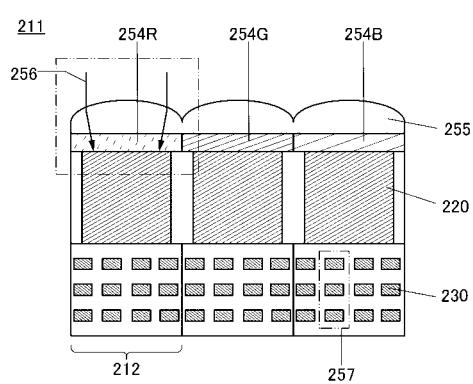

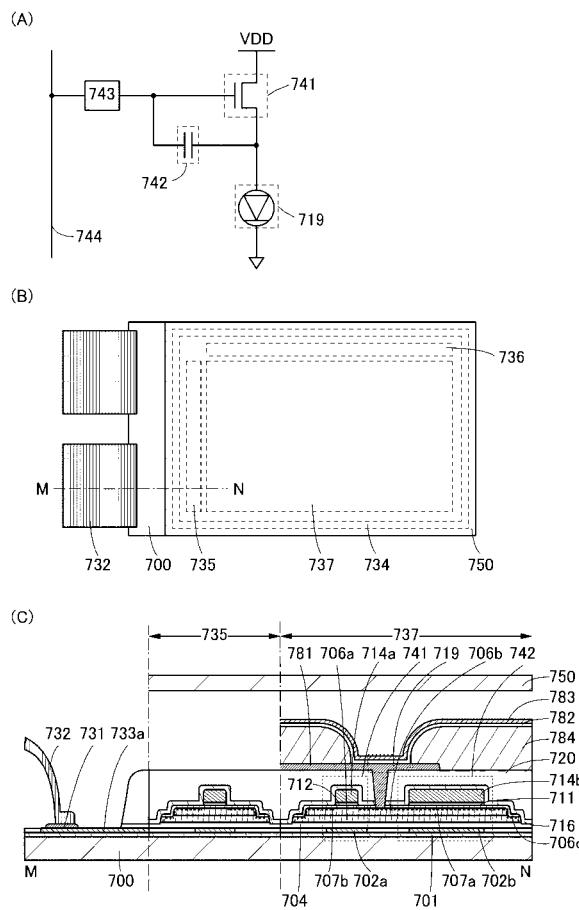

【図1】本発明の一態様に係るトランジスタを説明する上面図および断面図。

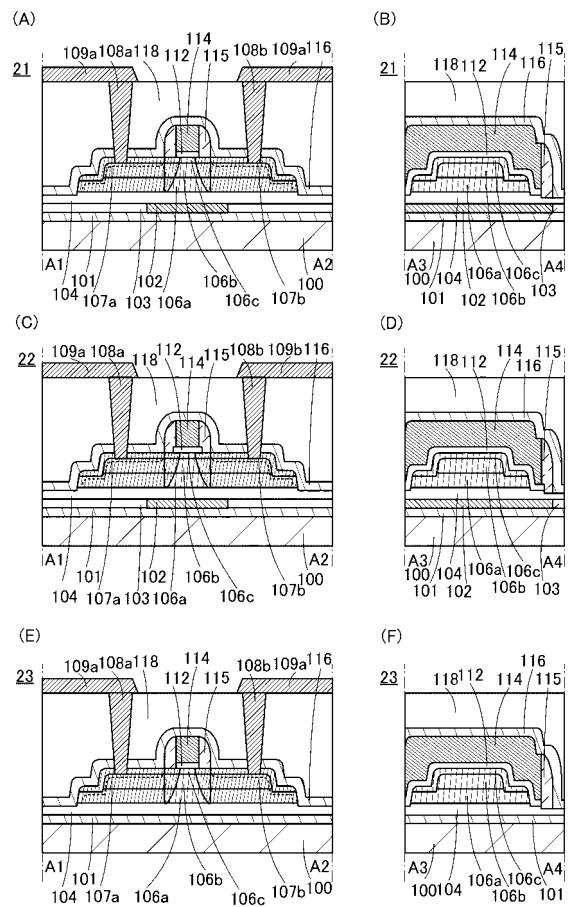

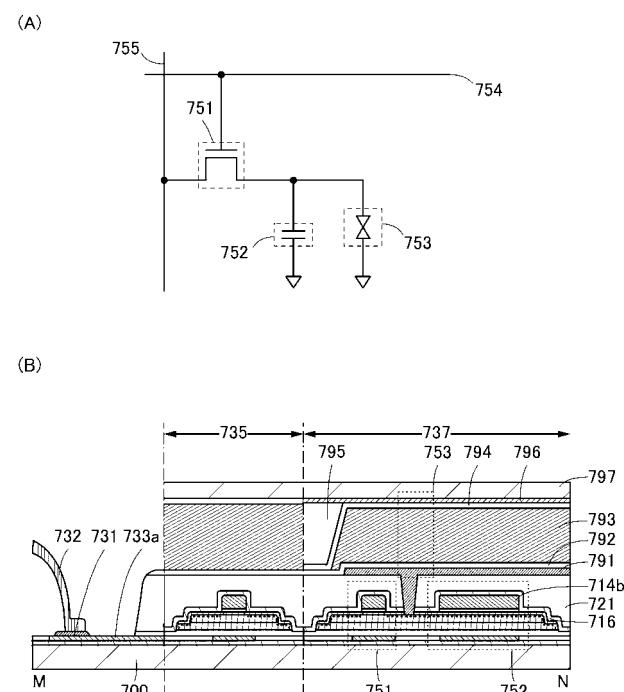

【図2】本発明の一態様に係るトランジスタを説明する断面図。

【図3】本発明の一態様に係るトランジスタを説明する断面図。

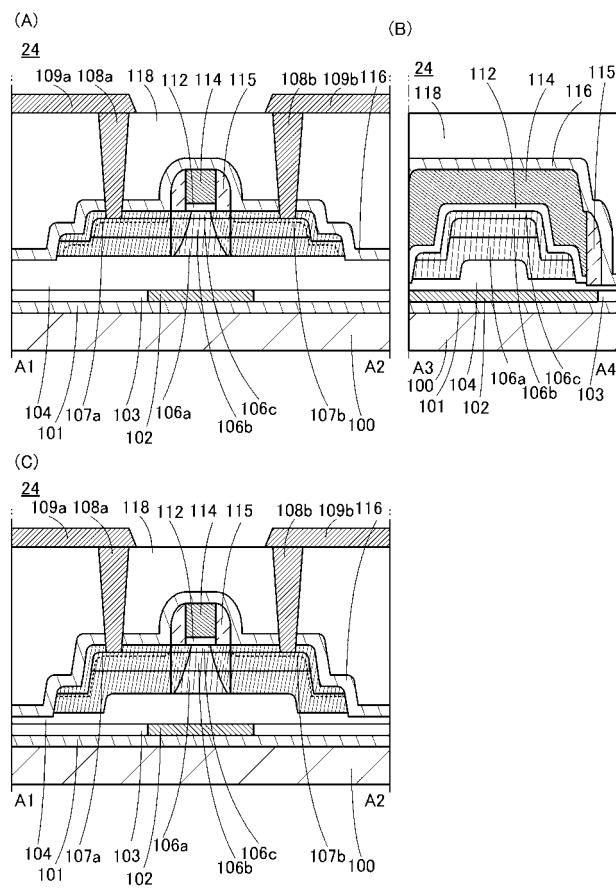

【図4】本発明の一態様に係るトランジスタの作製方法を説明する断面図。

【図5】本発明の一態様に係るトランジスタの作製方法を説明する断面図。

30

【図6】本発明の一態様に係るトランジスタの作製方法を説明する断面図。

【図7】イオンの入射を説明する図。

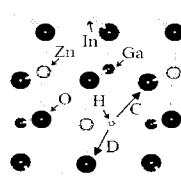

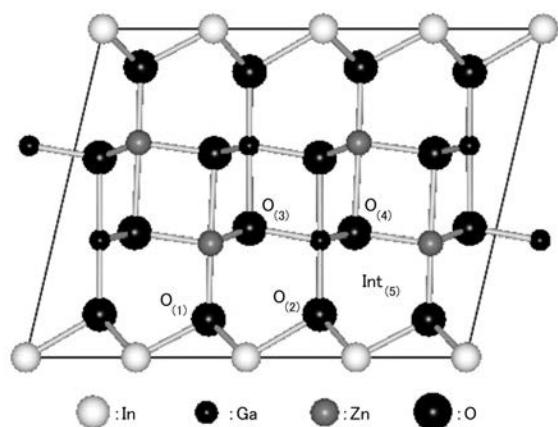

【図8】InGaN<sub>0.4</sub>O<sub>4</sub>結晶構造を説明する図。

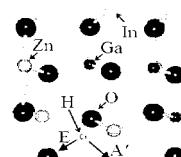

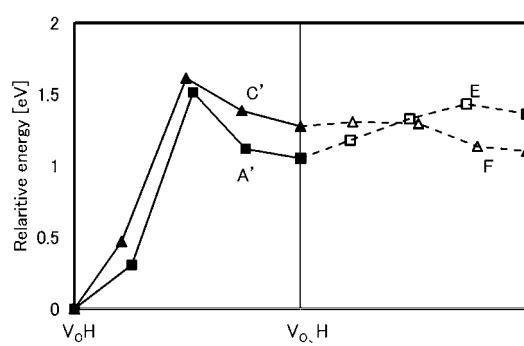

【図9】水素に関する欠陥の形成エネルギーを説明する図。

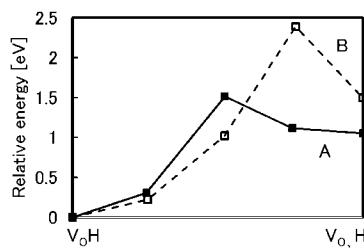

【図10】V<sub>0</sub>-H間距離に対する相対エネルギーを説明する図。

【図11】水素に関する欠陥の形成エネルギーを説明する図。

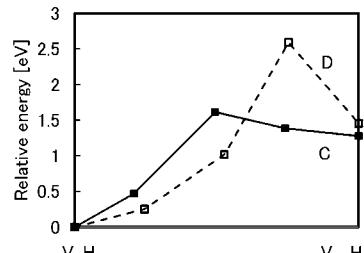

【図12】V<sub>0</sub>内から水素が抜け出す経路およびエネルギー変化を説明する図。

【図13】水素の拡散経路およびエネルギー変化を説明する図。

【図14】本発明の一態様に係るトランジスタを説明する上面図および断面図。

40

【図15】本発明の一態様に係るトランジスタを説明する断面図。

【図16】本発明の一態様に係るトランジスタを説明する断面図。

【図17】本発明の一態様に係るトランジスタを説明する断面図。

【図18】本発明の一態様に係るトランジスタの作製方法を説明する断面図。

【図19】本発明の一態様に係るトランジスタの作製方法を説明する断面図。

【図20】本発明の一態様に係るトランジスタの作製方法を説明する断面図。

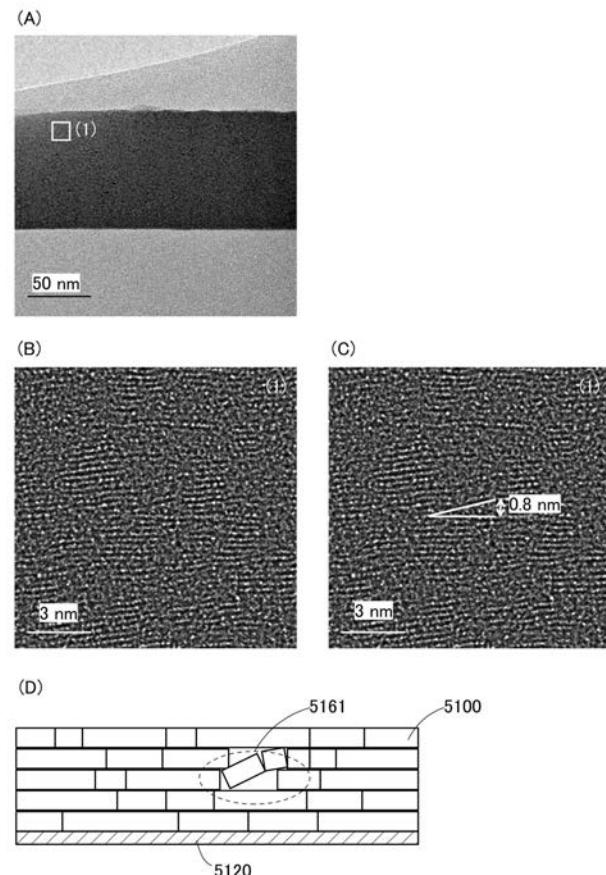

【図21】CAAC-OSの断面におけるCs補正高分解能TEM像、およびCAAC-OSの断面模式図。

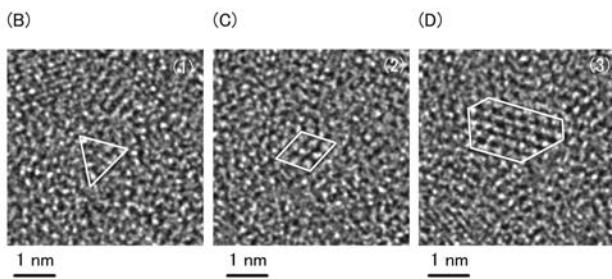

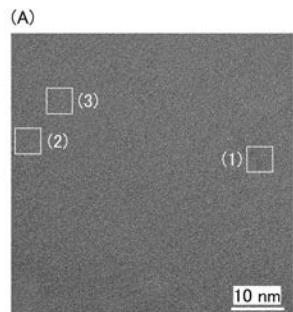

【図22】CAAC-OSの平面におけるCs補正高分解能TEM像。

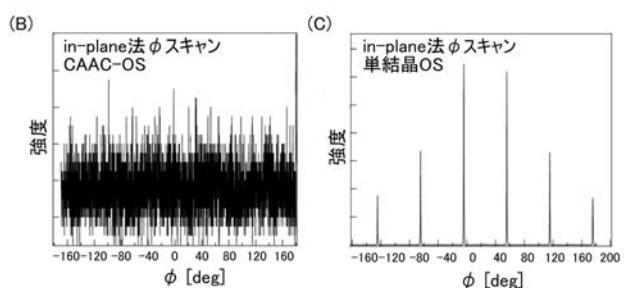

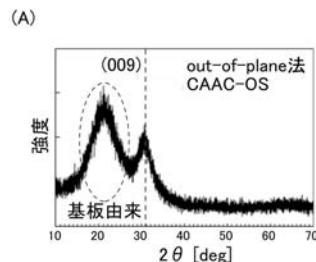

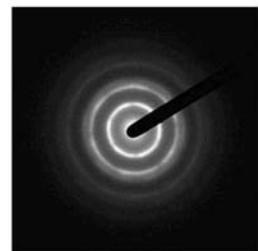

【図23】CAAC-OSおよび単結晶酸化物半導体のXRDによる構造解析を説明する図。

50

- 【図 2 4】C A A C - O S の電子回折パターンを示す図。

- 【図 2 5】In - Ga - Zn 酸化物の電子照射による結晶部の変化を示す図。

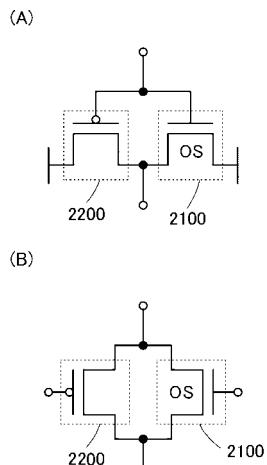

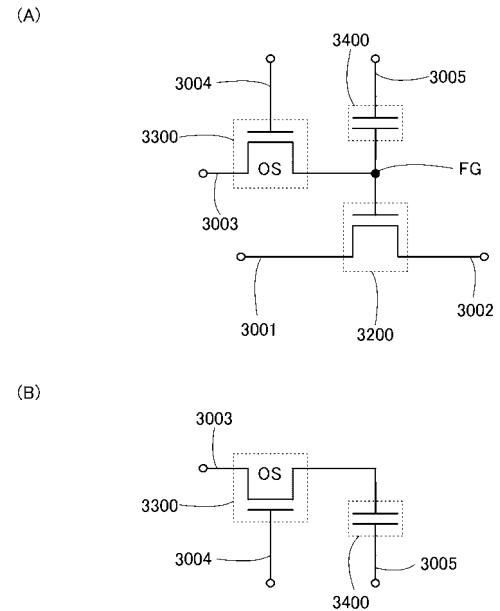

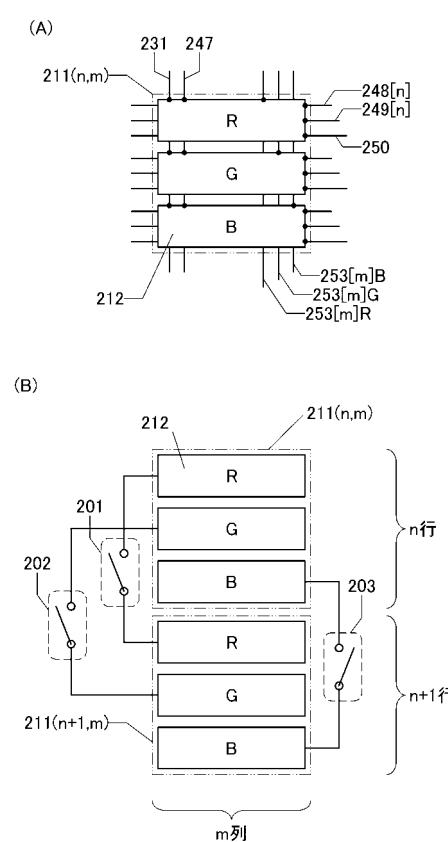

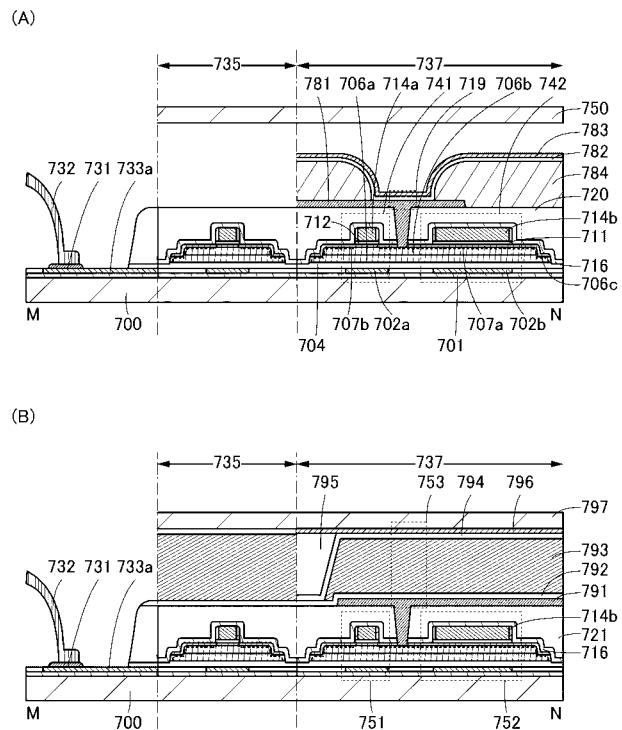

- 【図 2 6】本発明の一態様に係る半導体装置を示す回路図。

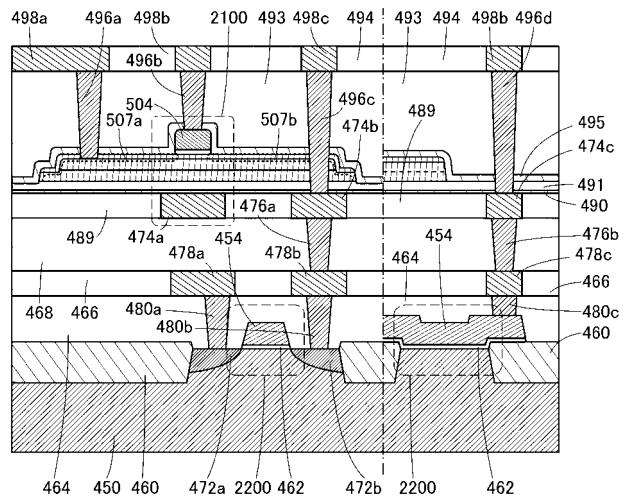

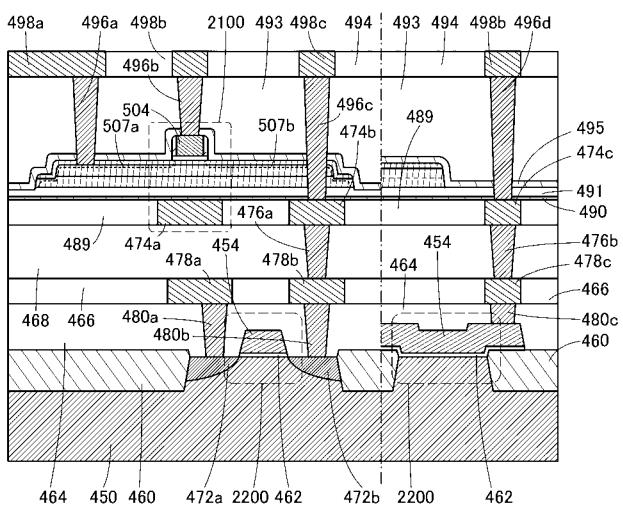

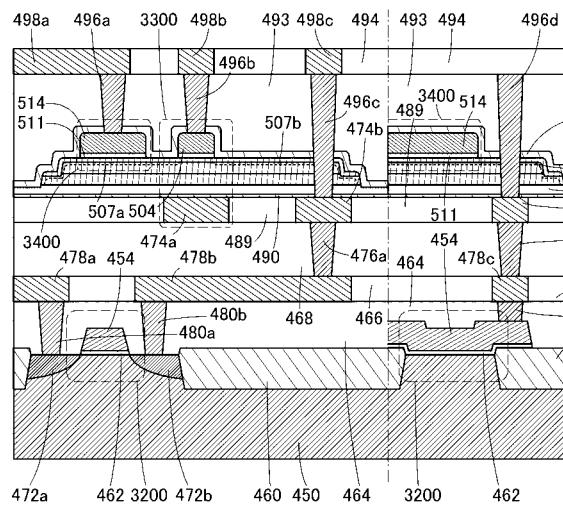

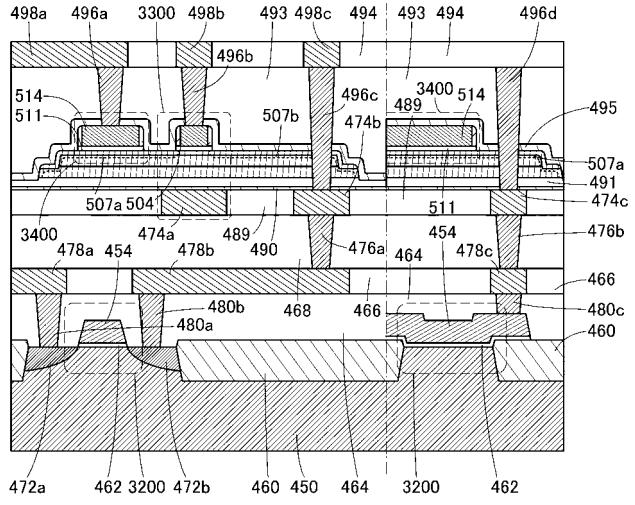

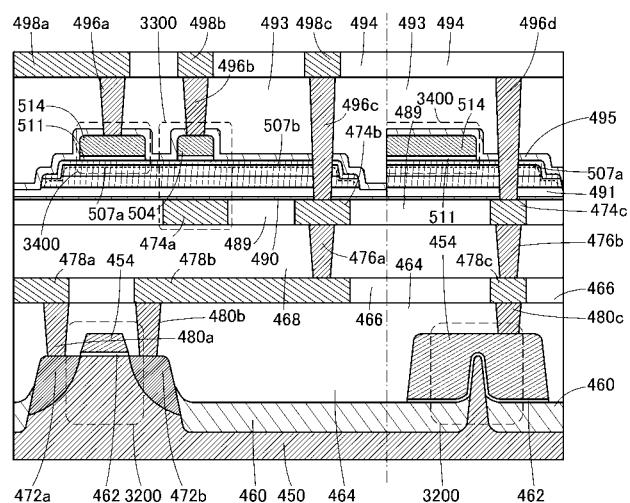

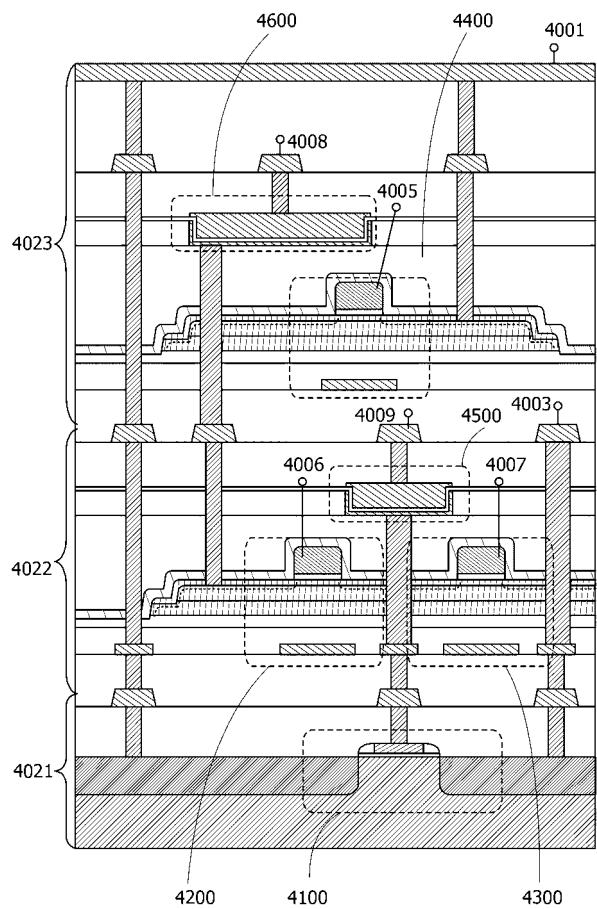

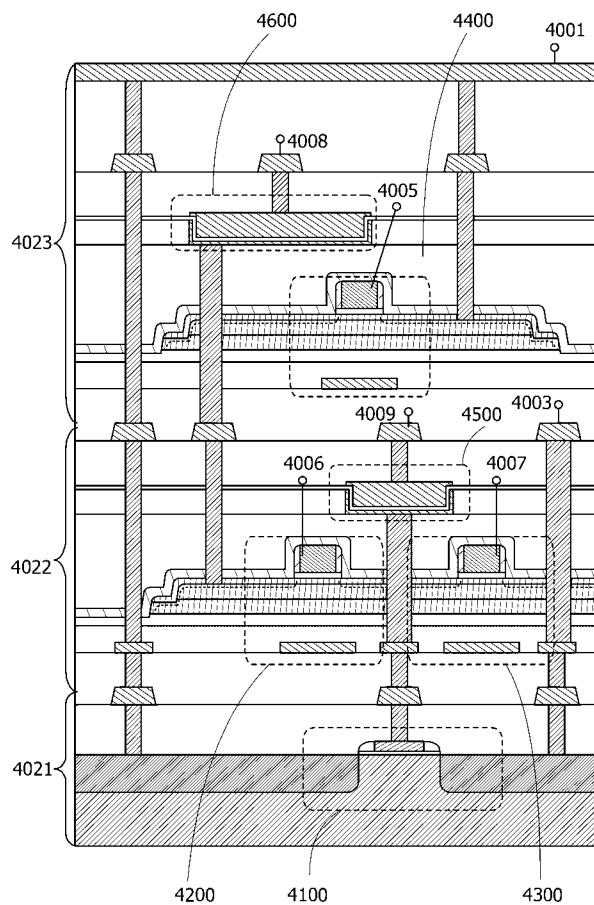

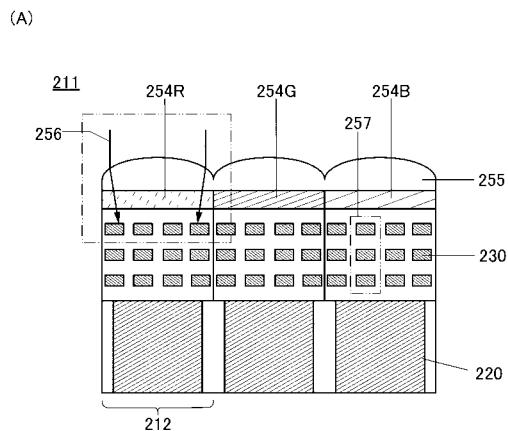

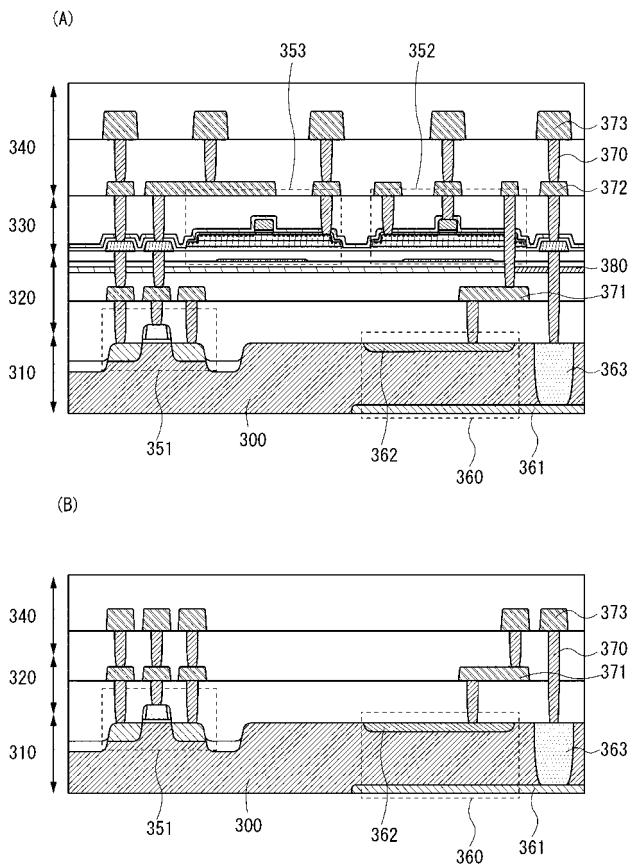

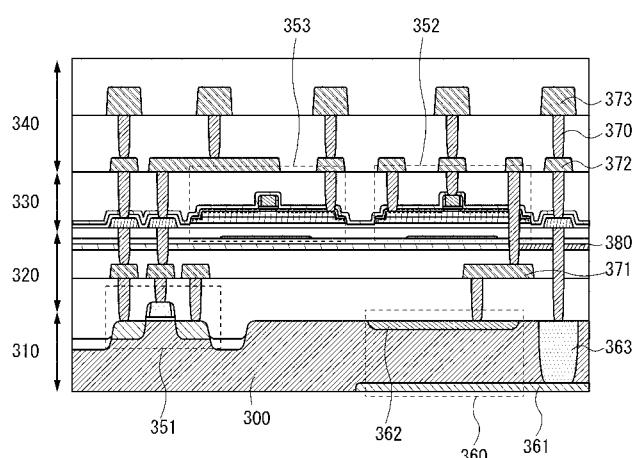

- 【図 2 7】本発明の一態様に係る半導体装置を示す断面図。

- 【図 2 8】本発明の一態様に係る半導体装置を示す断面図。

- 【図 2 9】本発明の一態様に係る半導体装置を示す断面図。

- 【図 3 0】本発明の一態様に係る半導体装置を示す断面図。

- 【図 3 1】本発明の一態様に係る半導体装置を示す断面図。

- 【図 3 2】本発明の一態様に係る半導体装置を示す断面図。

- 【図 3 3】本発明の一態様に係る記憶装置を示す回路図。 10

- 【図 3 4】本発明の一態様に係る半導体装置を示す断面図。

- 【図 3 5】本発明の一態様に係る半導体装置を示す断面図。

- 【図 3 6】本発明の一態様に係る半導体装置を示す断面図。

- 【図 3 7】本発明の一態様に係る半導体装置を示す断面図。

- 【図 3 8】本発明の一態様に係る半導体装置を示す断面図。

- 【図 3 9】本発明の一態様に係る半導体装置を示す断面図。

- 【図 4 0】本発明の一態様に係る半導体装置を示す回路図。

- 【図 4 1】本発明の一態様に係る半導体装置を示す断面図。

- 【図 4 2】本発明の一態様に係る半導体装置を示す断面図。

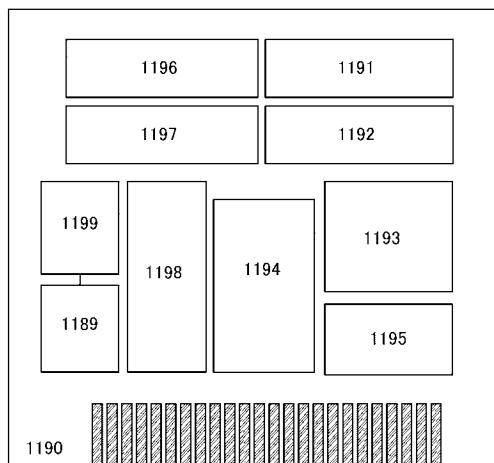

- 【図 4 3】本発明の一態様に係る半導体装置を示す回路図。 20

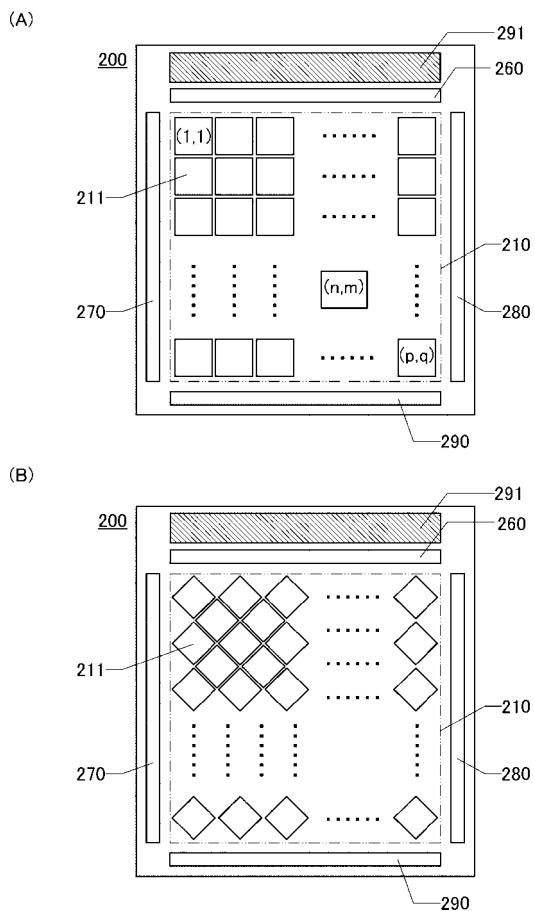

- 【図 4 4】本発明の一態様に係る半導体装置を示す上面図。

- 【図 4 5】本発明の一態様に係る半導体装置を示すブロック図。

- 【図 4 6】本発明の一態様に係る半導体装置を示す断面図。

- 【図 4 7】本発明の一態様に係る半導体装置を示す断面図。

- 【図 4 8】本発明の一態様に係る半導体装置を示す断面図。

- 【図 4 9】本発明の一態様に係る半導体装置を示す斜視図および断面図。

- 【図 5 0】本発明の一態様に係る半導体装置を示すブロック図。 30

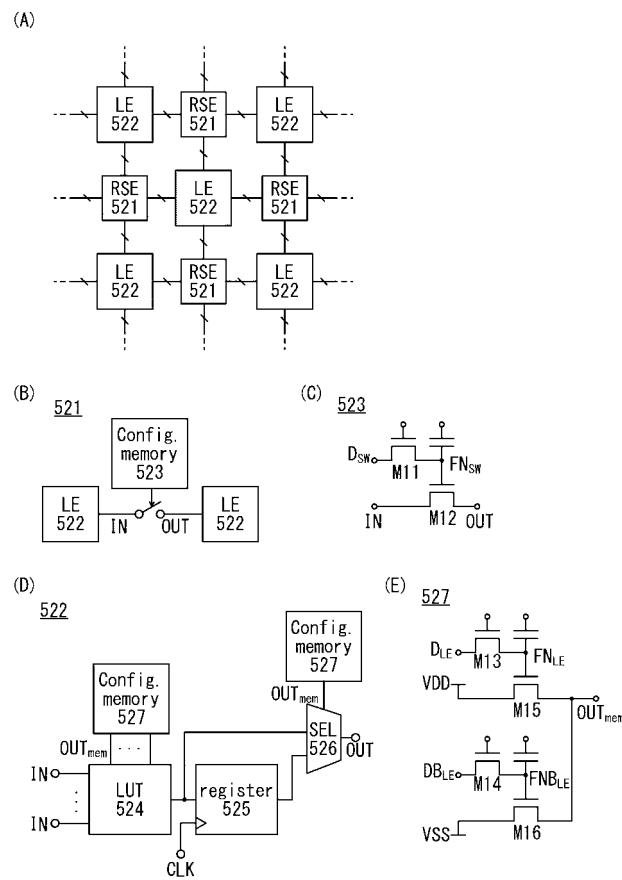

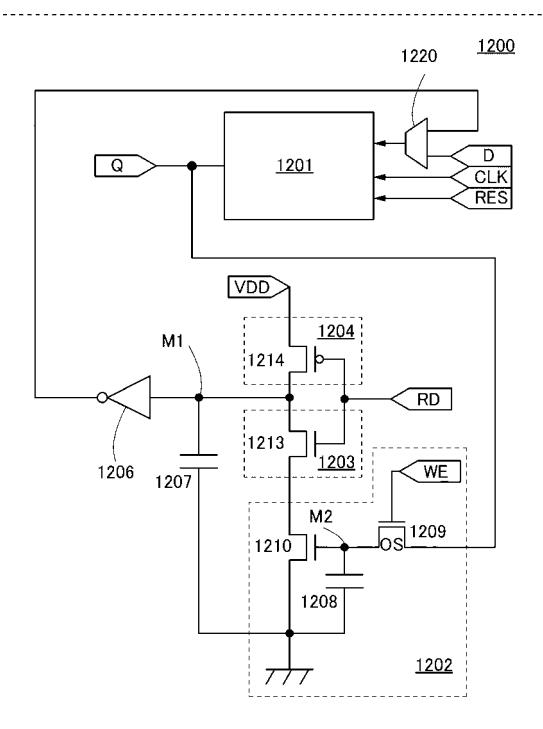

- 【図 5 1】本発明の一態様に係る半導体装置を示す回路図。

- 【図 5 2】本発明の一態様に係る半導体装置を示す回路図、上面図および断面図。

- 【図 5 3】本発明の一態様に係る半導体装置を示す回路図および断面図。

- 【図 5 4】本発明の一態様に係る半導体装置を示す断面図。

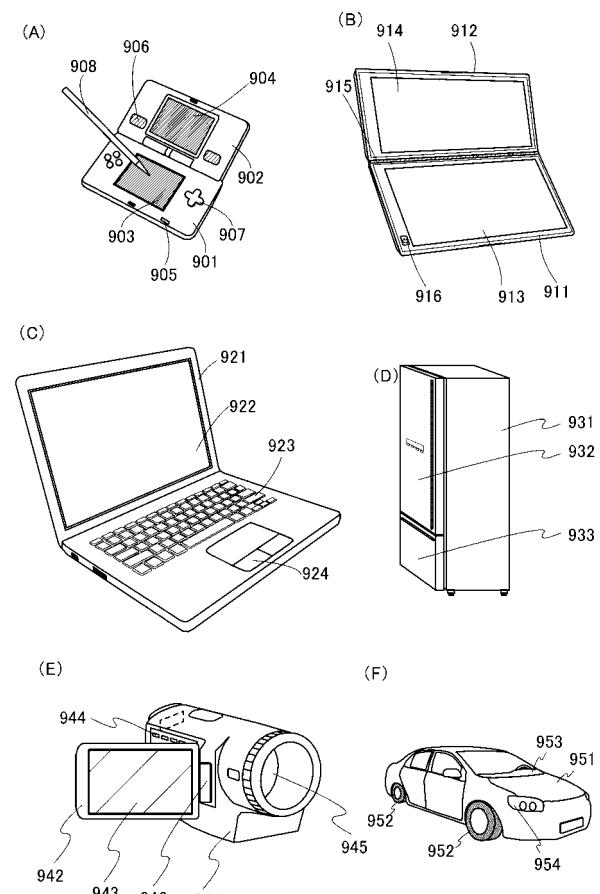

- 【図 5 5】本発明の一態様に係る電子機器を示す斜視図。

【発明を実施するための形態】

【0 0 2 8】

本発明の実施の形態について、図面を用いて詳細に説明する。ただし、本発明は以下の説明に限定されず、その形態および詳細を様々に変更し得ることは、当業者であれば容易に理解される。また、本発明は以下に示す実施の形態の記載内容に限定して解釈されるものではない。なお、図面を用いて発明の構成を説明するにあたり、同じものを指す符号は異なる図面間でも共通して用いる。なお、同様のものを指す際にはハッチパターンを同じくし、特に符号を付さない場合がある。 40

【0 0 2 9】

以下の実施の形態に示す構成は、実施の形態に示す他の構成に対して適宜、適用、組み合わせ、又は置き換えなどを行って、本発明の一態様とすることができます。

【0 0 3 0】

なお、図において、大きさ、膜（層）の厚さ、または領域は、明瞭化のために誇張されている場合がある。

【0 0 3 1】

なお、本明細書において、「膜」という表記と、「層」という表記と、を互いに入れ替えることが可能である。

【0 0 3 2】

10

20

30

40

50

また、電圧は、ある電位と、基準の電位（例えば接地電位（GND）またはソース電位）との電位差のことを示す場合が多い。よって、電圧を電位と言い換えることが可能である。一般的に、電位（電圧）は、相対的なものであり、基準の電位からの相対的な大きさによって決定される。したがって、「接地電位」などと記載されている場合であっても、電位が0Vであるとは限らない。例えば、回路で最も低い電位が、「接地電位」となる場合もある。または、回路で中間くらいの電位が、「接地電位」となる場合もある。その場合には、その電位を基準として、正の電位と負の電位が規定される。

#### 【0033】

なお、第1、第2として付される序数詞は便宜的に用いるものであり、工程順または積層順を示すものではない。そのため、例えば、「第1の」を「第2の」または「第3の」などと適宜置き換えて説明することができる。また、本明細書などに記載されている序数詞と、本発明の一態様を特定するために用いられる序数詞は一致しない場合がある。

#### 【0034】

なお、半導体の不純物とは、例えば、半導体を構成する主成分以外をいう。例えば、濃度が0.1原子%未満の元素は不純物である。不純物が含まれることにより、例えば、半導体にDOS (Density of State) が形成されることや、キャリア移動度が低下することや、結晶性が低下することなどが起こる場合がある。半導体が酸化物半導体である場合、半導体の特性を変化させる不純物としては、例えば、第1族元素、第2族元素、第13族元素、第14族元素、第15族元素、主成分以外の遷移金属などがあり、特に、例えば、水素（水にも含まれる）、リチウム、ナトリウム、シリコン、ホウ素、リン、炭素、窒素などがある。酸化物半導体の場合、例えば水素などの不純物の混入によって酸素欠損を形成する場合がある。また、半導体がシリコンである場合、半導体の特性を変化させる不純物としては、例えば、酸素、水素を除く第1族元素、第2族元素、第13族元素、第15族元素などがある。

#### 【0035】

なお、チャネル長とは、例えば、トランジスタの上面図において、半導体（またはトランジスタがオン状態のときに半導体の中で電流の流れる部分）とゲート電極とが互いに重なる領域、またはチャネルが形成される領域における、ソース（ソース領域またはソース電極）とドレイン（ドレイン領域またはドレイン電極）との間の距離をいう。なお、一つのトランジスタにおいて、チャネル長が全ての領域で同じ値をとるとは限らない。即ち、一つのトランジスタのチャネル長は、一つの値に定まらない場合がある。そのため、本明細書では、チャネル長は、チャネルの形成される領域における、いずれか一の値、最大値、最小値または平均値とする。

#### 【0036】

チャネル幅とは、例えば、半導体（またはトランジスタがオン状態のときに半導体の中で電流の流れる部分）とゲート電極とが互いに重なる領域、またはチャネルが形成される領域における、ソースとドレインとが向かい合っている部分の長さをいう。なお、一つのトランジスタにおいて、チャネル幅がすべての領域で同じ値をとるとは限らない。即ち、一つのトランジスタのチャネル幅は、一つの値に定まらない場合がある。そのため、本明細書では、チャネル幅は、チャネルの形成される領域における、いずれか一の値、最大値、最小値または平均値とする。

#### 【0037】

なお、トランジスタの構造によっては、実際にチャネルの形成される領域におけるチャネル幅（以下、実効的なチャネル幅と呼ぶ。）と、トランジスタの上面図において示されるチャネル幅（以下、見かけ上のチャネル幅と呼ぶ。）と、が異なる場合がある。例えば、立体的な構造を有するトランジスタでは、実効的なチャネル幅が、トランジスタの上面図において示される見かけ上のチャネル幅よりも大きくなり、その影響が無視できなくなる場合がある。例えば、微細かつ立体的な構造を有するトランジスタでは、半導体の側面に形成されるチャネル領域の割合が大きくなる場合がある。その場合は、上面図において示される見かけ上のチャネル幅よりも、実際にチャネルの形成される実効的なチャネル幅

10

20

30

40

50

の方が大きくなる。

【0038】

ところで、立体的な構造を有するトランジスタにおいては、実効的なチャネル幅の、実測による見積もりが困難となる場合がある。例えば、設計値から実効的なチャネル幅を見積もるために、半導体の形状が既知という仮定が必要である。したがって、半導体の形状が正確にわからない場合には、実効的なチャネル幅を正確に測定することは困難である。

【0039】

そこで、本明細書では、トランジスタの上面図において、半導体とゲート電極とが互いに重なる領域における、ソースとドレインとが向かい合っている部分の長さである見かけ上のチャネル幅を、「囲い込みチャネル幅 (SCW: Surrounded Channel Width)」と呼ぶ場合がある。また、本明細書では、単にチャネル幅と記載した場合には、囲い込みチャネル幅または見かけ上のチャネル幅を指す場合がある。または、本明細書では、単にチャネル幅と記載した場合には、実効的なチャネル幅を指す場合がある。なお、チャネル長、チャネル幅、実効的なチャネル幅、見かけ上のチャネル幅、囲い込みチャネル幅などは、断面TEM像などを取得して、その画像を解析することなどによって、値を決定することができる。

【0040】

なお、トランジスタの電界効果移動度や、チャネル幅当たりの電流値などを計算して求める場合、囲い込みチャネル幅を用いて計算する場合がある。その場合には、実効的なチャネル幅を用いて計算する場合とは異なる値をとる場合がある。

【0041】

本明細書において、「平行」とは、二つの直線が -10° 以上 10° 以下の角度で配置されている状態をいう。したがって、-5° 以上 5° 以下の場合も含まれる。また、「略平行」とは、二つの直線が -30° 以上 30° 以下の角度で配置されている状態をいう。また、「垂直」とは、二つの直線が 80° 以上 100° 以下の角度で配置されている状態をいう。したがって、85° 以上 95° 以下の場合も含まれる。また、「略垂直」とは、二つの直線が 60° 以上 120° 以下の角度で配置されている状態をいう。

【0042】

また、本明細書において、結晶が三方晶または菱面体晶である場合、六方晶系として表す。

【0043】

(実施の形態 1)

本実施の形態では、本発明の一態様に係る半導体装置の構成について、図1乃至図3を用いて説明する。

【0044】

<トランジスタの構成 1>

以下では、本発明の一態様に係る半導体装置の一例としてトランジスタの構成について説明する。

【0045】

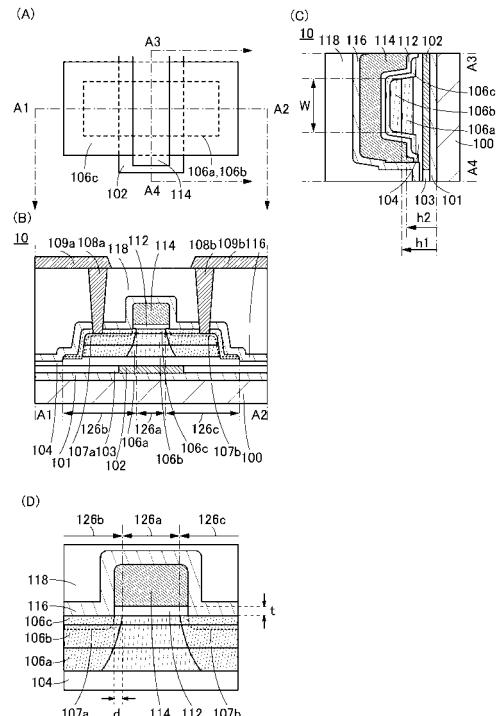

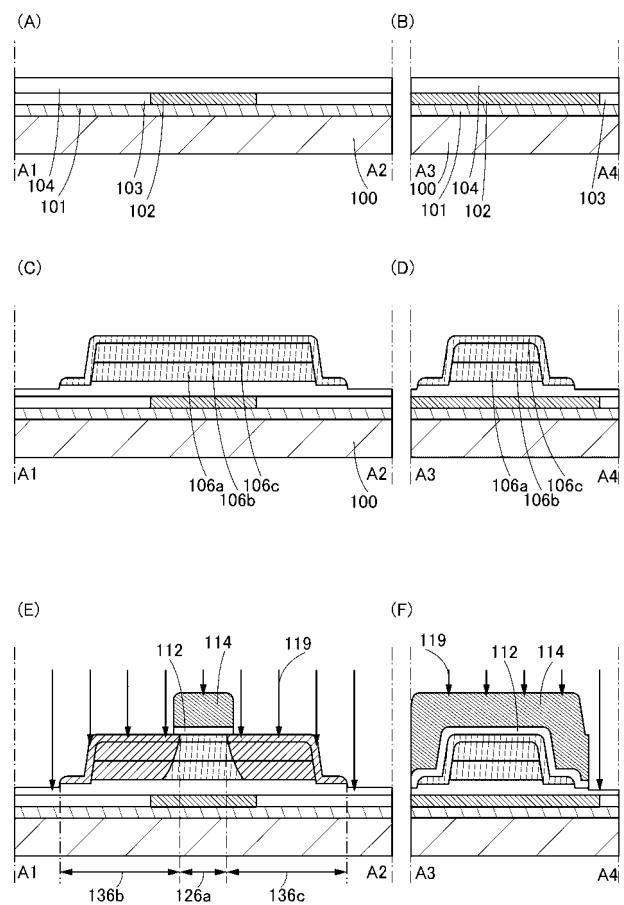

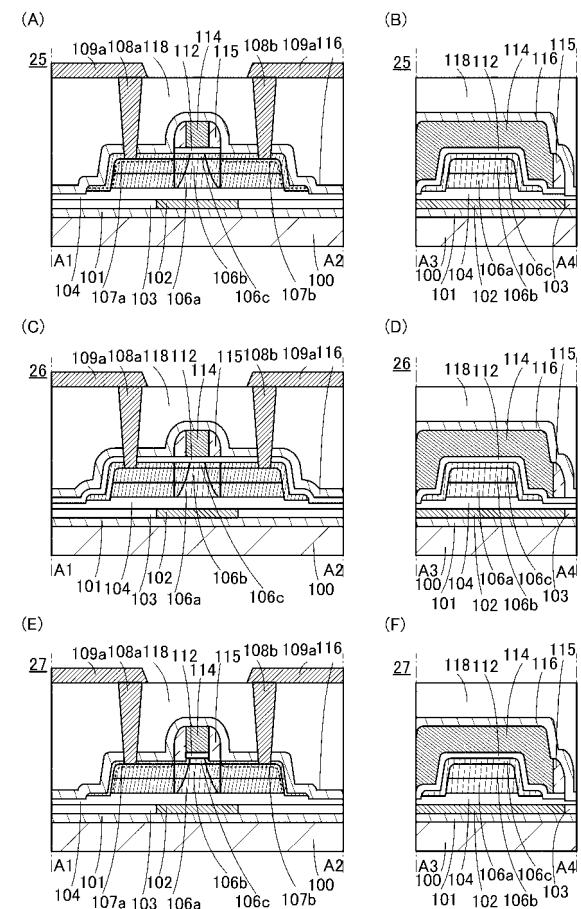

図1(A)乃至(C)を用いてトランジスタ10の構成について説明する。図1(A)はトランジスタ10の上面図である。図1(B)は図1(A)の一点鎖線A1-A2に対応する断面図である。図1(C)は図1(A)の一点鎖線A3-A4に対応する断面図である。なお、一点鎖線A1-A2で示す領域では、トランジスタ10のチャネル長方向における構造を示しており、一点鎖線A3-A4で示す領域では、トランジスタ10のチャネル幅方向における構造を示している。なお、トランジスタのチャネル長方向とは、ソース(ソース領域またはソース電極)及びドレイン(ドレイン領域またはドレイン電極)間において、キャリアが移動する方向を意味し、チャネル幅方向は、基板と水平な面において、チャネル長方向に対して垂直の方向を意味する。なお、図1(A)において、煩雑になることを避けるため、トランジスタ10の構成要素の一部(保護絶縁膜として機能す

る絶縁膜等)を省略して図示している。なお、トランジスタの上面図においては、以降の図面においても図1(A)と同様に、構成要素の一部を省略して図示する場合がある。

【0046】

トランジスタ10は、半導体106bと、導電体114と、絶縁体106aと、絶縁体106cと、絶縁体112と、絶縁体116と、を有する。半導体106bは、絶縁体106a上に配置され、絶縁体106cは、半導体106b上に配置され、絶縁体112は、絶縁体106c上に配置され、導電体114は、絶縁体112上に配置される。絶縁体116は、導電体114上に配置され、絶縁体116は、絶縁体106cの上面と接する領域を有し、半導体106bは、絶縁体106cおよび絶縁体112を介して導電体114と重なる領域を有する。図1(A)に示すように上面から見たとき、絶縁体106aの外周が半導体106bの外周と概略一致し、絶縁体106cの外周が絶縁体106a及び半導体106bの外周よりも外側に位置することが好ましい。

10

【0047】

例えば、図1(A)乃至(C)に示すように、トランジスタ10は、基板100の上に形成された絶縁体101、導電体102、絶縁体103及び絶縁体104と、絶縁体104の上に形成された絶縁体106a、半導体106b及び絶縁体106cと、絶縁体106cの上に形成された絶縁体112、導電体114と、導電体114の上に形成された絶縁体116、絶縁体118、導電体108a、導電体108b、導電体109a及び導電体109bと、を有する。

20

【0048】

ここで、絶縁体101、絶縁体103、絶縁体104、絶縁体106a、絶縁体106c、絶縁体112、絶縁体116及び絶縁体118は、絶縁膜又は絶縁層ということもできる。また、導電体102、導電体108a、導電体108b、導電体109a、導電体109b及び導電体114は、導電膜又は導電層ということもできる。また、半導体106bは、半導体膜又は半導体層ということもできる。

30

【0049】

基板100上に形成された絶縁体101の上に絶縁体103が形成され、絶縁体103に埋め込まれるように導電体102が形成されている。絶縁体103及び導電体102上に絶縁体104が形成されている。ここで、絶縁体101は酸素、水素、水等に対してプロッキング効果を有する絶縁体を用いることが好ましい。また、絶縁体104は酸素を含む絶縁体を用いることが好ましい。

30

【0050】

絶縁体104の上に絶縁体106aが形成され、絶縁体106aの上面に接して半導体106bが形成され、絶縁体106aの側面と半導体106bの上面に接して絶縁体106cが形成される。ここで、半導体106bは少なくとも一部が、導電体102と重なるように形成されることが好ましい。絶縁体106aの側面端部、特にチャネル幅方向の側面端部と、半導体106bの側面端部、特にチャネル幅方向の側面端部と、が概略一致する形状となっている。さらに、半導体106bの側面端部、特にチャネル幅方向の側面端部が、絶縁体106cと接して設けられている。このように本実施の形態に示すトランジスタ10は、半導体106bが絶縁体106a及び絶縁体106cに包み込まれるように設けられている。

40

【0051】

なお、図1(B)(C)では、絶縁体106cの外周が絶縁体106aの外周より外側に位置する形状となっているが、本実施の形態に示すトランジスタはこれに限られるものではない。例えば、絶縁体106aの外周が絶縁体106cの外周より外側に位置してもよいし、絶縁体106aの側面端部と、絶縁体106cの側面端部とが概略一致する形状としてもよい。

【0052】

本実施の形態に示すトランジスタ10の、絶縁体106a、半導体106b及び絶縁体106cは、領域126a、領域126b及び領域126cが形成されており、領域12

50

6 b 及び領域 126 c は領域 126 a と比較してドーパントの濃度が高く、低抵抗化されている。例えば、領域 126 a は、領域 126 b または領域 126 c のドーパントの最大濃度に対して、5 % 以下の濃度の領域、2 % 以下の濃度の領域、または 1 % 以下の濃度の領域とすればよい。なお、ドーパントを、ドナー、アクセプター、不純物または元素といい換えてよい。

【0053】

ここで、図 1 (D) に図 1 (B) に示すトランジスタ 10 の導電体 114 近傍の拡大図を示す。図 1 (D) に示すように、絶縁体 106 a、半導体 106 b 及び絶縁体 106 c において、領域 126 a は導電体 114 と概ね重なる領域であり、領域 126 b 及び領域 126 c は、領域 126 a を除いた領域である。ここで、領域 126 b 及び領域 126 c の一部が、半導体 106 b の導電体 114 と重なる領域（チャネル形成領域）の一部と重なることが好ましい。例えば、領域 126 b 及び領域 126 c のチャネル長方向の側面端部は、導電体 114 の側面端部より距離 d だけ導電体 114 の内側に位置することが好ましい。このとき、距離 d は絶縁体 112 の膜厚 t に対して、 $0.25t < d < t$  を満たすことが好ましい。

10

【0054】

このように、絶縁体 106 a、半導体 106 b および絶縁体 106 c の、導電体 114 と重なる領域の一部に領域 126 b 及び領域 126 c が形成される。これにより、トランジスタ 10 のチャネル形成領域と低抵抗化された領域 126 b 及び領域 126 c が接し、領域 126 b および領域 126 c と、領域 126 a との間に、高抵抗のオフセット領域が形成されないため、トランジスタ 10 のオン電流を増大させることができる。さらに、領域 126 b 及び領域 126 c のチャネル長方向の側面端部が上記の範囲を満たして形成されることで、領域 126 b 及び領域 126 c がチャネル形成領域に対して深く形成されすぎて常に導通状態になってしまふことも防ぐことができる。

20

【0055】

なお、詳細は後述するが、領域 126 b 及び領域 126 c は、イオン注入法などのイオンドーピング処理を用いて形成される。このため、図 1 (D) に示すように、領域 126 b 及び領域 126 c のチャネル長方向の側面端部の位置が、絶縁体 106 c 上面から深くなるに従って、絶縁体 106 a、半導体 106 b および絶縁体 106 c のチャネル長方向の側面端部側にシフトする場合がある。このとき、距離 d は、最も導電体 114 の内側の近くに位置する、領域 126 b 及び領域 126 c のチャネル長方向の側面端部と導電体 114 のチャネル長方向の側面端部との距離とする。

30

【0056】

この場合、例えば、絶縁体 106 a 中に形成される領域 126 b 及び領域 126 c が導電体 114 と重なる領域に形成されない場合がある。この場合、半導体 106 b に形成される領域 126 b 及び領域 126 c の少なくとも一部が導電体 114 と重なる領域に形成されることが好ましい。

【0057】

また、絶縁体 106 a、半導体 106 b 及び絶縁体 106 c の絶縁体 116 との界面近傍（図 1 (B) では点線で表示）に低抵抗領域 107 a 及び低抵抗領域 107 b が形成されることが好ましい。低抵抗領域 107 a 及び低抵抗領域 107 b は、絶縁体 116 に含まれる元素の少なくとも一が含まれる。低抵抗領域 107 a 及び低抵抗領域 107 b の一部が、半導体 106 b の導電体 114 と重なる領域（チャネル形成領域）と概略接するか、当該領域の一部と重なることが好ましい。

40

【0058】

また、絶縁体 106 c は絶縁体 116 と接する領域が大きいため、低抵抗領域 107 a 及び低抵抗領域 107 b は絶縁体 106 c に形成されやすい。絶縁体 106 c における低抵抗領域 107 a と低抵抗領域 107 b は、絶縁体 106 c の低抵抗領域 107 a 及び低抵抗領域 107 b ではない領域（例えば、絶縁体 106 c の導電体 114 と重なる領域）より、絶縁体 116 に含まれる元素の濃度が高い。

50

## 【0059】

領域126b中に低抵抗領域107aが形成され、領域126c中に低抵抗領域107bが形成される。ここで、理想的には、低抵抗領域107a及び低抵抗領域107bが添加元素濃度が最も高く、領域126b及び領域126cの低抵抗領域107a及び低抵抗領域107bを除く領域が添加元素濃度が次に高く、領域126aが添加元素濃度が最も低くなる。ここで、添加元素とは、領域126b及び領域126cを形成するドーパントと、低抵抗領域107a及び低抵抗領域107bに絶縁体116から添加される元素を合わせたものである。

## 【0060】

このような領域126b、領域126c、低抵抗領域107a及び低抵抗領域107bが形成されることにより、導電体108a又は導電体108bと絶縁体106a、半導体106b又は絶縁体106cとの接触抵抗を低減することが可能となるのでトランジスタ10のオン電流を増大させることができる。

10

## 【0061】

なお、図1(A)乃至(D)に示すトランジスタ10では低抵抗領域107a及び低抵抗領域107bが形成される構成としているが、本実施の形態に示す半導体装置は、必ずしもこれに限られるものではない。例えば、領域126b及び領域126cの抵抗が十分低い場合、低抵抗領域107a及び低抵抗領域107bを形成する必要はない。

## 【0062】

絶縁体106cの上に絶縁体112が形成され、絶縁体112の上に導電体114が形成される。絶縁体112及び導電体114は、少なくとも一部が導電体102及び半導体106bと重なる。導電体114のチャネル長方向の側面端部と絶縁体112のチャネル長方向の側面端部は概略一致していることが好ましい。ここで、絶縁体112はトランジスタ10のゲート絶縁膜として機能し、導電体114はトランジスタ10のゲート電極として機能する。

20

## 【0063】

導電体114、絶縁体106c及び絶縁体104の上に絶縁体116が形成される。絶縁体116は、絶縁体106cの絶縁体112と重なっていない領域と接していることが好ましい。また、絶縁体116は、絶縁体104の少なくとも一部と接していてもよい。絶縁体116の上に絶縁体118が形成される。ここで、絶縁体116はトランジスタ10の保護絶縁膜として機能し、絶縁体118は、トランジスタ10の層間絶縁膜として機能する。絶縁体116は、酸素に対してブロッキング効果を有する絶縁体を用いることが好ましい。

30

## 【0064】

また、絶縁体106aの膜厚が、絶縁体106cと絶縁体112の膜厚の和より大きいことが好ましい。別言すると、基板100の上面から半導体106bの下面までの高さh1と、絶縁体106cと重なる領域における基板100の上面から導電体114の下面までの高さh2との関係が、 $h_1 = h_2$ または $h_1 > h_2$ であることが好ましい。例えば、h1を、h2よりもトランジスタ10の見かけ上のチャネル幅Wの5%以上、好ましくは10%以上、さらに好ましくは20%以上、より好ましくは50%以上高くすればよい。このような構成とすることにより、半導体106bのチャネル幅方向の側面の概略全体を、絶縁体106cと絶縁体112を介して、導電体114と対向させることができる。

40

## 【0065】

これにより、図1(C)に示すように、導電体114の電界によって、半導体106bを電気的に取り囲むことができる(導電体から生じる電界によって、半導体を電気的に取り囲むトランジスタの構造を、surrounded channel(s-channel)構造とよぶ。)。そのため、半導体106bの全体にチャネルが形成される場合がある。s-channel構造では、トランジスタのソース-ドレイン間に大電流を流すことができ、オン電流を高くすることができる。

## 【0066】

50

なお、トランジスタが s - channel 構造を有する場合、半導体 106b の側面にもチャネルが形成される。したがって、半導体 106b が厚いほどチャネル領域は大きくなる。即ち、半導体 106b が厚いほど、トランジスタのオン電流を高くすることができる。また、半導体 106b が厚いほど、キャリアの制御性の高い領域の割合が増えるため、サブスレッショルドスイング値を小さくすることができる。例えば、10 nm 以上、好ましくは 20 nm 以上、さらに好ましくは 30 nm 以上、より好ましくは 50 nm 以上の厚さの領域を有する半導体 106b とすればよい。ただし、半導体装置の生産性が低下する場合があるため、例えば、300 nm 以下、好ましくは 200 nm 以下、さらに好ましくは 150 nm 以下の厚さの領域を有する半導体 106b とすればよい。なお、チャネル形成領域が縮小していくと、半導体 106b が薄いほうがトランジスタの電気特性が向上する場合もある。よって、半導体 106b の厚さが 10 nm 未満であってもよい。

10

## 【0067】

高いオン電流が得られるため、s - channel 構造は、微細化されたトランジスタに適した構造といえる。トランジスタを微細化できるため、該トランジスタを有する半導体装置は、集積度の高い、高密度化された半導体装置とすることが可能となる。例えば、トランジスタは、チャネル長が好ましくは 40 nm 以下、さらに好ましくは 30 nm 以下、より好ましくは 20 nm 以下の領域を有し、かつ、トランジスタは、チャネル幅が好ましくは 40 nm 以下、さらに好ましくは 30 nm 以下、より好ましくは 20 nm 以下の領域を有する。

20

## 【0068】

絶縁体 118、絶縁体 116 及び絶縁体 106c に設けられた開口に導電体 108a 及び導電体 108b が形成され、低抵抗領域 107a または低抵抗領域 107b に接している。さらに絶縁体 118 の上に、導電体 108a の上面に接して導電体 109a が形成され、導電体 108b の上面に接して導電体 109b が形成されている。導電体 108a と導電体 108b は離間して形成されており、図 1 (B) に示すように導電体 114 を挟んで対向して形成されていることが好ましい。ここで、導電体 108a は、トランジスタ 10 のソース電極またはドレイン電極の一方として機能し、導電体 108b は、トランジスタ 10 のソース電極またはドレイン電極の他方として機能する。また、導電体 109a は、トランジスタ 10 のソース電極またはドレイン電極の一方と接続される配線として機能し、導電体 109b は、トランジスタ 10 のソース電極またはドレイン電極の他方と接続される配線として機能する。なお、図 1 (B) では、導電体 108a 及び導電体 108b は半導体 106b に接して設けられているが、本実施の形態はこれに限られるものではない。低抵抗領域 107a 及び低抵抗領域 107b との接触抵抗が十分低いなら、導電体 108a 及び導電体 108b と絶縁体 106c が接する構成としてもよい。

30

## 【0069】

<半導体>

以下、半導体 106b の詳細な構成について説明する。

## 【0070】

なお、本項目においては、半導体 106b とともに絶縁体 106a、絶縁体 106c の詳細な構成についても説明する。

40

## 【0071】

半導体 106b は、例えば、インジウムを含む酸化物半導体である。半導体 106b は、インジウムを含むと、キャリア移動度（電子移動度）が高くなる。また、半導体 106b は、元素 M を含むと好ましい。元素 M は、好ましくは、Ti、Ga、Y、Zr、La、Ce、Nd、Sn または Hf を表すとする。ただし、元素 M として、前述の元素を複数組み合わせても構わない場合がある。元素 M は、例えば、酸素との結合エネルギーが高い元素である。例えば、酸素との結合エネルギーがインジウムよりも高い元素である。または、元素 M は、例えば、酸化物半導体のエネルギーギャップを大きくする機能を有する元素である。また、半導体 106b は、亜鉛を含むと好ましい。酸化物半導体は、亜鉛を含むと結晶化しやすくなる場合がある。

50

## 【0072】

ただし、半導体106bは、インジウムを含む酸化物半導体に限定されない。半導体106bは、例えば、亜鉛スズ酸化物、ガリウムスズ酸化物などの、インジウムを含まず、亜鉛を含む酸化物半導体、ガリウムを含む酸化物半導体、スズを含む酸化物半導体などであっても構わない。

## 【0073】

絶縁体106a及び絶縁体106cは、半導体106bを構成する酸素以外の元素一種以上、または二種以上から構成される。半導体106bを構成する酸素以外の元素一種以上、または二種以上から絶縁体106a及び絶縁体106cが構成されるため、絶縁体106aと半導体106bとの界面、及び半導体106bと絶縁体106cとの界面において、欠陥準位が形成されにくい。10

## 【0074】

絶縁体106a、半導体106b及び絶縁体106cは、少なくともインジウムを含むと好ましい。なお、絶縁体106aがIn-M-Zn酸化物のとき、InおよびMの和を100atomic%としたとき、好ましくはInが50atomic%未満、Mが50atomic%より高く、さらに好ましくはInが25atomic%未満、Mが75atomic%より高いとする。また、半導体106bがIn-M-Zn酸化物のとき、InおよびMの和を100atomic%としたとき、好ましくはInが25atomic%より高く、Mが75atomic%未満、さらに好ましくはInが34atomic%より高く、Mが66atomic%未満とする。また、絶縁体106cがIn-M-Zn酸化物のとき、InおよびMの和を100atomic%としたとき、好ましくはInが50atomic%未満、Mが50atomic%より高く、さらに好ましくはInが25atomic%未満、Mが75atomic%より高いとする。ただし、絶縁体106aまたは絶縁体106cがインジウムを含まなくても構わない場合がある。例えば絶縁体106aまたは絶縁体106cが酸化ガリウムまたはGa-Zn酸化物であっても構わない。なお、絶縁体106a、半導体106b及び絶縁体106cに含まれる各元素の原子数が、簡単な整数比にならなくても構わない。20

## 【0075】

例えば、スパッタリング法を用いて成膜する場合、絶縁体106aまたは絶縁体106cに用いるターゲットの金属元素の原子数比の代表例としては、In:M:Zn = 1:2:4、In:M:Zn = 1:3:2、In:M:Zn = 1:3:4、In:M:Zn = 1:3:6、In:M:Zn = 1:3:8、In:M:Zn = 1:4:3、In:M:Zn = 1:4:4、In:M:Zn = 1:4:5、In:M:Zn = 1:4:6、In:M:Zn = 1:6:3、In:M:Zn = 1:6:4、In:M:Zn = 1:6:5、In:M:Zn = 1:6:6、In:M:Zn = 1:6:7、In:M:Zn = 1:6:8、In:M:Zn = 1:6:9等がある。また、絶縁体106aに用いるターゲットの金属元素の原子数比をM:Zn = 10:1としてもよい。30

## 【0076】

また、例えば、スパッタリング法を用いて成膜する場合、半導体106bに用いるターゲットの金属元素の原子数比の代表例としては、In:M:Zn = 1:1:1、In:M:Zn = 1:1:1.2、In:M:Zn = 2:1:1.5、In:M:Zn = 2:1:2.3、In:M:Zn = 2:1:3、In:M:Zn = 3:1:2、In:M:Zn = 4:2:4.1等がある。特に、スパッタリングターゲットとして、原子数比がIn:Ga:Zn = 4:2:4.1を用いる場合、成膜される半導体106bの原子数比は、In:Ga:Zn = 4:2:3近傍となる場合がある。40

## 【0077】

なお、インジウムガリウム酸化物は、小さい電子親和力と、高い酸素プロック性を有する。そのため、絶縁体106cがインジウムガリウム酸化物を含むと好ましい。ガリウム原子割合[Ga/(In+Ga)]は、例えば、70%以上、好ましくは80%以上、さらに好ましくは90%以上とする。50

## 【0078】

半導体106bは、例えば、エネルギーギャップが大きい酸化物を用いる。半導体106bのエネルギーギャップは、例えば、2.5eV以上4.2eV以下、好ましくは2.8eV以上3.8eV以下、さらに好ましくは3eV以上3.5eV以下とする。ここで、絶縁体106aのエネルギーギャップは、半導体106bのエネルギーギャップより大きい。また、絶縁体106cのエネルギーギャップは、半導体106bのエネルギーギャップより大きい。

## 【0079】

半導体106bは、絶縁体106aまたは絶縁体106cよりも電子親和力の大きい酸化物を用いる。例えば、半導体106bとして、絶縁体106aまたは絶縁体106cよりも電子親和力の0.07eV以上1.3eV以下、好ましくは0.1eV以上0.7eV以下、さらに好ましくは0.15eV以上0.4eV以下大きい酸化物を用いる。なお、電子親和力は、真空準位と伝導帯下端のエネルギーとの差である。言い換えると、絶縁体106aまたは絶縁体106cの伝導帯下端のエネルギー準位は、半導体106bの伝導帯下端のエネルギー準位より真空準位に近い。

10

## 【0080】

このとき、ゲート電圧を印加すると、絶縁体106aまたは絶縁体106cではなく、より電子親和力の大きい半導体106bにチャネルが形成される。

## 【0081】

上記の通り、絶縁体106aおよび絶縁体106cは、単独で用いる場合、導電体、半導体または絶縁体として機能させることができる物質からなる。しかしながら、半導体106bと積層させてトランジスタを形成する場合、電子は半導体106b、半導体106bと絶縁体106aの界面近傍、および半導体106bと絶縁体106cの界面近傍を流れ、絶縁体106aおよび絶縁体106cは当該トランジスタのチャネルとして機能しない領域を有する。このため、本明細書などにおいては、絶縁体106aおよび絶縁体106cを半導体と記載せず、絶縁体と記載するものとする。なお、絶縁体106aおよび絶縁体106cを絶縁体と記載するのは、あくまで半導体106bと比較してトランジスタの機能上絶縁体に近い機能を有するためなので、絶縁体106aまたは絶縁体106cとして、半導体106bに用いることができる物質を用いる場合もある。

20

## 【0082】

30

ここで、絶縁体106aと半導体106bとの間には、絶縁体106aと半導体106bとの混合領域を有する場合がある。また、絶縁体106cと半導体106bとの間には、絶縁体106cと半導体106bとの混合領域を有する場合がある。混合領域は、欠陥準位密度が低くなる。そのため、絶縁体106a、半導体106bおよび絶縁体106cの積層体は、それぞれの界面近傍において、エネルギーが連続的に変化する（連続接合ともいう。）バンド図となる。なお、絶縁体106aと半導体106b、または絶縁体106cと半導体106bは、それぞれの界面を明確に判別できない場合がある。

## 【0083】

このとき、電子は、絶縁体106a及び絶縁体106c中ではなく、半導体106b中を主として移動する。上述したように、絶縁体106aと半導体106bとの界面、および絶縁体106cと半導体106bとの界面における欠陥準位密度を低くすることによって、半導体106b中で電子の移動が阻害されることが少なく、トランジスタのオン電流を高くすることができる。

40

## 【0084】

また、トランジスタのオン電流は、電子の移動を阻害する要因を低減するほど、高くすることができる。例えば、電子の移動を阻害する要因のない場合、効率よく電子が移動すると推定される。電子の移動は、例えば、チャネル形成領域の物理的な凹凸が大きい場合にも阻害される。

## 【0085】

トランジスタのオン電流を高くするためには、例えば、半導体106bの上面または下

50

面（被形成面、ここでは絶縁体106aの上面）の、 $1\text{ }\mu\text{m} \times 1\text{ }\mu\text{m}$ の範囲における二乗平均平方根（RMS：Root Mean Square）粗さが $1\text{ nm}$ 未満、好ましくは $0.6\text{ nm}$ 未満、さらに好ましくは $0.5\text{ nm}$ 未満、より好ましくは $0.4\text{ nm}$ 未満とすればよい。また、 $1\text{ }\mu\text{m} \times 1\text{ }\mu\text{m}$ の範囲における平均面粗さ（Raともいう。）が $1\text{ nm}$ 未満、好ましくは $0.6\text{ nm}$ 未満、さらに好ましくは $0.5\text{ nm}$ 未満、より好ましくは $0.4\text{ nm}$ 未満とすればよい。また、 $1\text{ }\mu\text{m} \times 1\text{ }\mu\text{m}$ の範囲における最大高低差（P-Vともいう。）が $10\text{ nm}$ 未満、好ましくは $9\text{ nm}$ 未満、さらに好ましくは $8\text{ nm}$ 未満、より好ましくは $7\text{ nm}$ 未満とすればよい。RMS粗さ、RaおよびP-Vは、エスアイアイ・ナノテクノロジー株式会社製走査型プローブ顕微鏡システムSPA-500などを用いて測定することができる。

10

#### 【0086】

また、トランジスタのオン電流を高くするためには、絶縁体106cの厚さは小さいほど好ましい。絶縁体106cの厚さは、絶縁体106aの厚さより小さく、半導体106bの厚さより小さいことが好ましい。例えば、 $10\text{ nm}$ 未満、好ましくは $5\text{ nm}$ 以下、さらに好ましくは $3\text{ nm}$ 以下の領域を有する絶縁体106cとすればよい。一方、絶縁体106cは、チャネルの形成される半導体106bへ、隣接する絶縁体を構成する酸素以外の元素（水素、シリコンなど）が入り込まないようブロックする機能を有する。そのため、絶縁体106cは、ある程度の厚さを有することが好ましい。例えば、 $0.3\text{ nm}$ 以上、好ましくは $1\text{ nm}$ 以上、さらに好ましくは $2\text{ nm}$ 以上の厚さの領域を有する絶縁体106cとすればよい。

20

#### 【0087】

また、信頼性を高くするためには、絶縁体106aは厚いことが好ましい。例えば、 $10\text{ nm}$ 以上、好ましくは $20\text{ nm}$ 以上、さらに好ましくは $40\text{ nm}$ 以上、より好ましくは $60\text{ nm}$ 以上の厚さの領域を有する絶縁体106aとすればよい。絶縁体106aの厚さを、厚くすることで、隣接する絶縁体と絶縁体106aとの界面からチャネルの形成される半導体106bまでの距離を離すことができる。ただし、半導体装置の生産性が低下する場合があるため、例えば、 $200\text{ nm}$ 以下、好ましくは $120\text{ nm}$ 以下、さらに好ましくは $80\text{ nm}$ 以下の厚さの領域を有する絶縁体106aとすればよい。

#### 【0088】

例えば、酸化物半導体中のシリコンは、キャリアトラップやキャリア発生源となる場合がある。したがって、半導体106bのシリコン濃度は低いほど好ましい。例えば、半導体106bと絶縁体106aとの間に、二次イオン質量分析法（SIMS：Secondary Ion Mass Spectrometry）において、 $1 \times 10^{16}\text{ atoms/cm}^3$ 以上 $1 \times 10^{19}\text{ atoms/cm}^3$ 以下、好ましくは $1 \times 10^{16}\text{ atoms/cm}^3$ 以上 $5 \times 10^{18}\text{ atoms/cm}^3$ 以下、さらに好ましくは $1 \times 10^{16}\text{ atoms/cm}^3$ 以上 $2 \times 10^{18}\text{ atoms/cm}^3$ 以下のシリコン濃度となる領域を有する。また、半導体106bと絶縁体106cとの間に、SIMSにおいて、 $1 \times 10^{16}\text{ atoms/cm}^3$ 以上 $1 \times 10^{19}\text{ atoms/cm}^3$ 以下、好ましくは $1 \times 10^{16}\text{ atoms/cm}^3$ 以上 $5 \times 10^{18}\text{ atoms/cm}^3$ 以下、さらに好ましくは $1 \times 10^{16}\text{ atoms/cm}^3$ 以上 $2 \times 10^{18}\text{ atoms/cm}^3$ 以下のシリコン濃度となる領域を有する。

30

#### 【0089】

また、半導体106bの水素濃度を低減するために、絶縁体106a及び絶縁体106cの水素濃度を低減すると好ましい。絶縁体106a及び絶縁体106cは、SIMSにおいて、 $1 \times 10^{16}\text{ atoms/cm}^3$ 以上 $2 \times 10^{20}\text{ atoms/cm}^3$ 以下、好ましくは $1 \times 10^{16}\text{ atoms/cm}^3$ 以上 $5 \times 10^{19}\text{ atoms/cm}^3$ 以下、より好ましくは $1 \times 10^{16}\text{ atoms/cm}^3$ 以上 $1 \times 10^{19}\text{ atoms/cm}^3$ 以下、さらに好ましくは $1 \times 10^{16}\text{ atoms/cm}^3$ 以上 $5 \times 10^{18}\text{ atoms/cm}^3$ 以下の水素濃度となる領域を有する。また、半導体106bの窒素濃度を低減するために、絶縁体106a及び絶縁体106cの窒素濃度を低減すると好ましい。絶縁体106

40

50

a 及び絶縁体 106c は、S I M Sにおいて、 $1 \times 10^{15}$  atoms / cm<sup>3</sup> 以上  $5 \times 10^{19}$  atoms / cm<sup>3</sup> 以下、好ましくは  $1 \times 10^{15}$  atoms / cm<sup>3</sup> 以上  $5 \times 10^{18}$  atoms / cm<sup>3</sup> 以下、より好ましくは  $1 \times 10^{15}$  atoms / cm<sup>3</sup> 以上  $1 \times 10^{18}$  atoms / cm<sup>3</sup> 以下、さらに好ましくは  $1 \times 10^{15}$  atoms / cm<sup>3</sup> 以上  $5 \times 10^{17}$  atoms / cm<sup>3</sup> 以下の窒素濃度となる領域を有する。

#### 【0090】

本実施の形態に示す絶縁体 106a、半導体 106b 及び絶縁体 106c、特に半導体 106b は、不純物濃度が低く、欠陥準位密度の低い（酸素欠損の少ない）酸化物半導体であり、高純度真性または実質的に高純度真性な酸化物半導体と呼ぶことができる。高純度真性または実質的に高純度真性である酸化物半導体は、キャリア発生源が少ないため、キャリア密度を低くすることができる。従って、該酸化物半導体にチャネル領域が形成されるトランジスタは、しきい値電圧がマイナスとなる電気特性（ノーマリーオンともいう。）になることが少ない。また、高純度真性または実質的に高純度真性である酸化物半導体は、欠陥準位密度が低いため、トラップ準位密度も低くなる場合がある。また、高純度真性または実質的に高純度真性である酸化物半導体は、オフ電流が著しく小さく、チャネル幅 W が  $1 \times 10^6$  μm でチャネル長 L が  $10$  μm の素子であっても、ソース電極とドレイン電極間の電圧（ドレイン電圧）が  $1$  V から  $10$  V の範囲において、オフ電流が、半導体パラメータアナライザの測定限界以下、すなわち  $1 \times 10^{-13}$  A 以下という特性を得ることができる。

#### 【0091】

したがって、上記高純度真性、または実質的に高純度真性の酸化物半導体にチャネル領域が形成されるトランジスタは、電気特性の変動が小さく、信頼性の高いトランジスタとすることができます。なお、酸化物半導体のトラップ準位に捕獲された電荷は、消失するまでに要する時間が長く、あたかも固定電荷のように振る舞うことがある。そのため、トラップ準位密度の高い酸化物半導体にチャネル領域が形成されるトランジスタは、電気特性が不安定となる場合がある。不純物としては、水素、窒素、アルカリ金属、またはアルカリ土類金属等がある。

#### 【0092】

絶縁体 106a、半導体 106b 及び絶縁体 106c に含まれる水素は、金属原子と結合する酸素と反応して水になると共に、酸素が脱離した格子（または酸素が脱離した部分）に酸素欠損を形成する。該酸素欠損に水素が入ることで、キャリアである電子が生成される場合がある。また、水素の一部が金属原子と結合する酸素と結合して、キャリアである電子を生成することがある。特に酸素欠損にトラップされた水素は、半導体のバンド構造に対して浅いドナー準位を形成することがある。従って、水素が含まれている酸化物半導体を用いたトランジスタはノーマリーオン特性となりやすい。このため、絶縁体 106a、半導体 106b 及び絶縁体 106c は水素ができる限り低減されていることが好ましい。具体的には、絶縁体 106a、半導体 106b 及び絶縁体 106c において、S I M S 分析により得られる水素濃度を、 $2 \times 10^{20}$  atoms / cm<sup>3</sup> 以下、好ましくは  $5 \times 10^{19}$  atoms / cm<sup>3</sup> 以下、より好ましくは  $1 \times 10^{19}$  atoms / cm<sup>3</sup> 以下、 $5 \times 10^{18}$  atoms / cm<sup>3</sup> 以下、好ましくは  $1 \times 10^{18}$  atoms / cm<sup>3</sup> 以下、より好ましくは  $5 \times 10^{17}$  atoms / cm<sup>3</sup> 以下、さらに好ましくは  $1 \times 10^{16}$  atoms / cm<sup>3</sup> 以下とする。

#### 【0093】

絶縁体 106a、半導体 106b 及び絶縁体 106c において、第 14 族元素の一つであるシリコンや炭素が含まれると、絶縁体 106a、半導体 106b 及び絶縁体 106c において酸素欠損が増加し、n 型化してしまう。このため、絶縁体 106a、半導体 106b 及び絶縁体 106c におけるシリコンや炭素の濃度と、絶縁体 106a、半導体 106b 及び絶縁体 106c との界面近傍のシリコンや炭素の濃度（S I M S 分析により得られる濃度）を、 $2 \times 10^{18}$  atoms / cm<sup>3</sup> 以下、好ましくは  $2 \times 10^{17}$  atoms / cm<sup>3</sup> 以下とする。

10

20

30

40

50

## 【0094】

また、絶縁体106a、半導体106b及び絶縁体106cにおいて、SIMS分析により得られるアルカリ金属またはアルカリ土類金属の濃度を、 $1 \times 10^{-8}$  atoms/cm<sup>3</sup>以下、好ましくは $2 \times 10^{-6}$  atoms/cm<sup>3</sup>以下にする。アルカリ金属及びアルカリ土類金属は、酸化物半導体と結合するとキャリアを生成する場合があり、トランジスタのオフ電流が増大してしまうことがある。このため、絶縁体106a、半導体106b及び絶縁体106cのアルカリ金属またはアルカリ土類金属の濃度を低減することが好ましい。

## 【0095】

また、絶縁体106a、半導体106b及び絶縁体106cに窒素が含まれていると、キャリアである電子が生じ、キャリア密度が増加し、n型化しやすい。この結果、窒素が含まれている酸化物半導体膜を用いたトランジスタはノーマリーオン特性となりやすい。従って、該酸化物半導体膜において、窒素はできる限り低減されていることが好ましい、例えば、SIMS分析により得られる窒素濃度は、 $5 \times 10^{-8}$  atoms/cm<sup>3</sup>以下にすることが好ましい。

10

## 【0096】

上述の通り、本実施の形態に示す絶縁体106a、半導体106b及び絶縁体106cは、不純物濃度が低く、欠陥準位密度の低い（酸素欠損の少ない）酸化物であり、キャリア密度が低い。このため、ソース電極またはドレイン電極として機能する導電体108a及び導電体108bとの間で接触抵抗が大きくなりやすい。そこで、本実施の形態に示すトランジスタ10では、導電体108aまたは導電体108bと、絶縁体106a、半導体106bまたは絶縁体106cと、が領域126b中の低抵抗領域107aまたは領域126c中の低抵抗領域107bを介して接続されることにより、接触抵抗の抑制を図っている。

20

## 【0097】

上述の通り、絶縁体106a、半導体106b及び絶縁体106cには、領域126a、領域126b及び領域126cが形成されており、領域126b及び領域126cは領域126aと比較してドーパントの濃度が高く、低抵抗化されている。ここで、絶縁体106a、半導体106b及び絶縁体106cにおいて、領域126aは導電体114と概ね重なる領域であり、領域126b及び領域126cは、領域126aを除いた領域である。ただし、領域126b及び領域126cの一部が、半導体106bの導電体114と重なる領域（チャネル形成領域）の一部と重なることが好ましい。

30

## 【0098】

さらに、絶縁体106a、半導体106b及び絶縁体106cの絶縁体116との界面近傍には、低抵抗領域107a及び低抵抗領域107bが形成されることが好ましい。領域126b、領域126c、低抵抗領域107a及び低抵抗領域107bでは、ドーパントや絶縁体116に含まれる元素が添加され、当該元素によって欠陥が形成される。このような欠陥は、例えば、添加されたドーパントや絶縁体116から添加された元素によって、酸素が引き抜かれて酸素欠損が形成される、またはドーパントや絶縁体116から添加された元素自体がキャリア発生源となることによって形成される。このような欠陥によってドナー準位が形成され、キャリア密度が増加するため、ドーパントや絶縁体116に含まれる元素が添加された領域が、領域126b、領域126c、低抵抗領域107a及び低抵抗領域107bとして機能することになる。

40

## 【0099】

領域126b、領域126c、特に低抵抗領域107a及び低抵抗領域107bは、酸素欠損が多く形成されているため、領域126aよりも、SIMS分析により得られる酸素濃度が低くなる。また、領域126b、領域126c、特に低抵抗領域107a及び低抵抗領域107bは、欠陥が多く形成されているため、領域126aよりも結晶性が低くなっている。

## 【0100】

50

また、詳細は後述するが、領域 126b 及び領域 126c はドーパントを添加して形成される。このため、領域 126b 及び領域 126c は領域 126a より、SIMS 分析により得られる当該ドーパントの濃度が高くなる。

#### 【0101】

領域 126b 及び領域 126c に添加されるドーパントとしては、例えば、水素、ヘリウム、ネオン、アルゴン、クリプトン、キセノン、窒素、フッ素、リン、塩素、ヒ素、ホウ素、マグネシウム、アルミニウム、シリコン、チタン、バナジウム、クロム、ニッケル、亜鉛、ガリウム、ゲルマニウム、イットリウム、ジルコニウム、ニオブ、モリブデン、インジウム、スズ、ランタン、セリウム、ネオジム、ハフニウム、タンタルまたはタンゲスタンなどが挙げられる。これらの元素の中でも、ヘリウム、ネオン、アルゴン、クリプトン、キセノン、窒素、フッ素、リン、塩素、ヒ素またはホウ素は、イオン注入法、イオンドーピング法、プラズマイマージョンイオンインプランテーション法などを用いて比較的容易に添加することができるため、好適である。

10

#### 【0102】

また、低抵抗領域 107a 及び低抵抗領域 107b は、絶縁体 116 に含まれる元素が添加されているため、半導体 106b の低抵抗領域 107a 及び低抵抗領域 107b を除く領域（例えば、半導体 106b の導電体 114 と重なる領域）よりも、SIMS 分析により得られる当該元素の濃度が高くなる。

#### 【0103】

低抵抗領域 107a 及び低抵抗領域 107b に添加される元素としては、例えば、ホウ素、マグネシウム、アルミニウム、シリコン、チタン、バナジウム、クロム、ニッケル、亜鉛、ガリウム、ゲルマニウム、イットリウム、ジルコニウム、ニオブ、モリブデン、インジウム、スズ、ランタン、セリウム、ネオジム、ハフニウム、タンタルまたはタンゲスタンなどが好ましい。これらの元素は、比較的酸化物を形成しやすく、当該酸化物は半導体または絶縁体として機能しうるため、絶縁体 106a、半導体 106b または絶縁体 106c の添加元素として好適である。例えば、低抵抗領域 107a 及び低抵抗領域 107b に上記の元素が  $1 \times 10^{14} / \text{cm}^2$  以上  $2 \times 10^{16} / \text{cm}^2$  以下含まれることが好ましい。また、絶縁体 106c における低抵抗領域 107a と低抵抗領域 107b は、絶縁体 106c の低抵抗領域 107a 及び低抵抗領域 107b ではない領域（例えば、絶縁体 106c の導電体 114 と重なる領域）よりも、上述の元素の濃度が高い。

20

#### 【0104】

また、低抵抗領域 107a 及び低抵抗領域 107b は、窒素を含ませることにより n 型化させることができるので、半導体 106b の低抵抗領域 107a 及び低抵抗領域 107b を除く領域（例えば、半導体 106b の導電体 114 と重なる領域）よりも、SIMS 分析により得られる窒素濃度が高くなる。

30

#### 【0105】

このような低抵抗領域 107a 及び低抵抗領域 107b が形成されることにより、導電体 108a 又は導電体 108b と絶縁体 106a、半導体 106b 又は絶縁体 106c との接触抵抗を低減することができるためトランジスタ 10 のオン電流を増大させることができる。

40

#### 【0106】

また、図 1 (B) に示すように、導電体 114 のチャネル長方向の側面端部と絶縁体 112 のチャネル長方向の側面端部は概略一致していることが好ましい。このような構成とすることにより、低抵抗領域 107a 及び低抵抗領域 107b と、半導体 106b の導電体 114 と重なる領域（チャネル形成領域）とが概略接するため、オン電流の向上を図ることができる。

#### 【0107】

また、トランジスタ 10 では、半導体 106b が絶縁体 106a 及び絶縁体 106c によって包み込まれるように設けられている。よって、半導体 106b の側面端部、特にチャネル幅方向の側面端部近傍が、絶縁体 106a 及び絶縁体 106c と接して設けられて

50

いる。これにより、半導体 106b の側面端部近傍において、絶縁体 106a 又は絶縁体 106c との間に連続接合が形成され、欠陥準位密度が低減される。よって、領域 126b、領域 126c、低抵抗領域 107a 及び低抵抗領域 107b を設けることによりオン電流が流れやすくなても、半導体 106b のチャネル幅方向の側面端部が寄生チャネルとならず、安定した電気特性を得ることができる。

#### 【0108】

なお、上述の絶縁体 106a、半導体 106b 及び絶縁体 106c の 3 層構造は一例である。例えば、絶縁体 106a または絶縁体 106c のいずれか一方を設けない 2 層構造としてもよい。また、絶縁体 106a または絶縁体 106c の両方を設けない単層構造としてもよい。または、絶縁体 106a、半導体 106b または絶縁体 106c として例示した絶縁体、半導体又は導電体のいずれかを有する n 層構造 (n は 4 以上の整数) としても構わない。

10

#### 【0109】

なお、絶縁体 106a、半導体 106b 及び絶縁体 106c に用いることのできる酸化物半導体の詳細については、実施の形態 5 で詳細に説明する。

#### 【0110】

<基板、絶縁体、導電体>

以下に、トランジスタ 10 の半導体以外の各構成要素について詳細な説明を行う。

#### 【0111】

基板 100 は、例えば、絶縁体基板、半導体基板または導電体基板を用いればよい。絶縁体基板としては、例えば、ガラス基板、石英基板、サファイア基板、安定化ジルコニア基板 (イットリア安定化ジルコニア基板など)、樹脂基板などがある。また、半導体基板としては、例えば、シリコン、ゲルマニウムなどの単体半導体基板、または炭化シリコン、シリコンゲルマニウム、ヒ化ガリウム、リン化インジウム、酸化亜鉛、酸化ガリウムなどの半導体基板などがある。さらには、前述の半導体基板内部に絶縁体領域を有する半導体基板、例えば SOI (Silicon On Insulator) 基板などがある。導電体基板としては、黒鉛基板、金属基板、合金基板、導電性樹脂基板などがある。または、金属の窒化物を有する基板、金属の酸化物を有する基板などがある。さらには、絶縁体基板に導電体または半導体が設けられた基板、半導体基板に導電体または絶縁体が設けられた基板、導電体基板に半導体または絶縁体が設けられた基板などがある。または、これらの基板に素子が設けられたものを用いてよい。基板に設けられる素子としては、容量素子、抵抗素子、スイッチ素子、発光素子、記憶素子などがある。

20

#### 【0112】

また、基板 100 として、トランジスタ作製時の加熱処理に耐えうる可とう性基板を用いてよい。なお、可とう性基板上にトランジスタを設ける方法としては、非可とう性の基板上にトランジスタを作製した後、トランジスタを剥離し、可とう性基板である基板 100 に転置する方法もある。その場合には、非可とう性基板とトランジスタとの間に剥離層を設けるとよい。なお、基板 100 として、繊維を編みこんだシート、フィルムまたは箔などを用いてよい。また、基板 100 が伸縮性を有してもよい。また、基板 100 は、折り曲げや引っ張りをやめた際に、元の形状に戻る性質を有してもよい。または、元の形状に戻らない性質を有してもよい。基板 100 の厚さは、例えば、5 μm 以上 700 μm 以下、好ましくは 10 μm 以上 500 μm 以下、さらに好ましくは 15 μm 以上 300 μm 以下とする。基板 100 を薄くすると、半導体装置を軽量化することができる。また、基板 100 を薄くすることで、ガラスなどを用いた場合にも伸縮性を有する場合や、折り曲げや引っ張りをやめた際に、元の形状に戻る性質を有する場合がある。そのため、落下などによって基板 100 上の半導体装置に加わる衝撃などを緩和することができる。即ち、丈夫な半導体装置を提供することができる。

30

#### 【0113】

可とう性基板である基板 100 としては、例えば、金属、合金、樹脂もしくはガラス、またはそれらの繊維などを用いることができる。可とう性基板である基板 100 は、線膨

40

50

張率が低いほど環境による変形が抑制されて好ましい。可とう性基板である基板100としては、例えば、線膨張率が $1 \times 10^{-3}$  / K以下、 $5 \times 10^{-5}$  / K以下、または $1 \times 10^{-5}$  / K以下である材質を用いればよい。樹脂としては、例えば、ポリエステル、ポリオレフィン、ポリアミド（ナイロン、アラミドなど）、ポリイミド、ポリカーボネート、アクリルなどがある。特に、アラミドは、線膨張率が低いため、可とう性基板である基板100として好適である。

#### 【0114】

絶縁体101は、水素又は水をロックする機能を有する絶縁体を用いる。絶縁体106a、半導体106b及び絶縁体106c近傍に設けられる絶縁体中の水素や水は、酸化物半導体を含む絶縁体106a、半導体106b及び絶縁体106c中にキャリアを生成する要因の一つとなる。これによりトランジスタ10の信頼性が低下するおそれがある。特に基板100としてスイッチ素子などのシリコン系半導体素子を設けた基板を用いる場合、当該半導体素子のダングリングボンドを終端するために水素が用いられ、当該水素がトランジスタ10まで拡散するおそれがある。これに対して水素又は水をロックする機能を有する絶縁体101を設けることによりトランジスタ10の下層から水素又は水が拡散するのを抑制し、トランジスタ10の信頼性を向上させることができる。

#### 【0115】

また、絶縁体101は酸素をロックする機能も有することが好ましい。絶縁体101が絶縁体104から拡散する酸素をロックすることにより、絶縁体104から絶縁体106a、半導体106b及び絶縁体106cに効果的に酸素を供給することができる。

#### 【0116】

絶縁体101としては、例えば、酸化アルミニウム、酸化窒化アルミニウム、酸化ガリウム、酸化窒化ガリウム、酸化イットリウム、酸化窒化イットリウム、酸化ハフニウム、酸化窒化ハフニウム等を用いることができる。これらを絶縁体101として用いることにより、酸素、水素又は水の拡散をロックする効果を示す絶縁膜として機能することができる。また、絶縁体101としては、例えば、窒化シリコン、窒化酸化シリコン等を用いることができる。これらを絶縁体101として用いることにより、水素、水の拡散をロックする効果を示す絶縁膜として機能することができる。

#### 【0117】

導電体102は、少なくとも一部が導電体108aと導電体108bに挟まれる領域において半導体106bと重なることが好ましい。導電体102は、トランジスタ10のバックゲートとして機能する。このような導電体102を設けることにより、トランジスタ10のしきい値電圧の制御を行うことができる。しきい値電圧の制御を行うことによって、トランジスタ10のゲート（導電体114）に印加された電圧が低い、例えば印加された電圧が0V以下のときに、トランジスタ10が導通状態となることを防ぐことができる。つまり、トランジスタ10の電気特性を、よりノーマリーオフの方向にシフトさせることができ容易になる。

#### 【0118】

また、導電体102は、絶縁体104、絶縁体116に設けられた開口を介してトランジスタ10のゲートとして機能する導電体114と接続される構成としてもよい。

#### 【0119】

導電体102としては、例えば、ホウ素、窒素、酸素、フッ素、シリコン、リン、アルミニウム、チタン、クロム、マンガン、コバルト、ニッケル、銅、亜鉛、ガリウム、イットリウム、ジルコニア、モリブデン、ルテニウム、銀、インジウム、スズ、タンタルおよびタンゲステンを一種以上含む導電体を、単層で、または積層で用いればよい。例えば、合金や化合物であってもよく、アルミニウムを含む導電体、銅およびチタンを含む導電体、銅およびマンガンを含む導電体、インジウム、スズおよび酸素を含む導電体、チタンおよび窒素を含む導電体などを用いてもよい。

#### 【0120】

なお、トランジスタ10において導電体102及び絶縁体103が形成されているが、

10

20

30

40

50

本実施の形態に示す半導体装置の構成はこれに限られるものではなく、例えば、導電体102及び絶縁体103を設けない構成としてもよい。

【0121】

絶縁体103としては、例えば、ホウ素、炭素、窒素、酸素、フッ素、マグネシウム、アルミニウム、シリコン、リン、塩素、アルゴン、ガリウム、ゲルマニウム、イットリウム、ジルコニウム、ランタン、ネオジム、ハフニウムまたはタンタルを含む絶縁体を、単層で、または積層で用いればよい。例えば、酸化シリコンまたは酸化窒化シリコンを有することが好ましい。

【0122】

図1(B)に示すように、絶縁体103と導電体102の上面は、化学機械研磨(CMP: Chemical Mechanical Polishing)法などによって平坦化処理を行って平坦性の向上を図ることが好ましい。これにより、バックゲートとして機能する導電体102を設けても、半導体106bを形成する面の平坦性が損なわれないため、キャリアの移動度を向上させ、トランジスタ10のオン電流を増大させることができる。

【0123】

また、導電体102は、絶縁体103中に埋め込まれるように設けられているが、本実施の形態に示す半導体装置の構成はこれに限られるものではなく、例えば、導電体102を覆うように絶縁体103を設ける構成としてもよい。その場合、絶縁体103は、酸素をロックする機能を有することが好ましい。このような絶縁体103を設けることにより、導電体102の酸化を防ぐ、言い換えると絶縁体104から導電体102が酸素を引き抜くことを防ぐことができる。これにより、絶縁体104から絶縁体106a、半導体106b及び絶縁体106cに効果的に酸素を供給することができる。

【0124】

絶縁体104は酸素を含む絶縁体であり、過剰酸素を有することが好ましい。また、絶縁体104は絶縁体101より酸素を透過させやすいことが好ましい。このような絶縁体104を設けることにより、絶縁体104から絶縁体106a、半導体106b及び絶縁体106cに酸素を供給することができる。当該酸素により、酸化物半導体である半導体106bの欠陥となる酸素欠損を低減することができる。これにより、半導体106bの欠陥準位密度を低減し、半導体106bを安定な特性を有する酸化物半導体とすることができる。

【0125】

なお、本明細書などにおいて、過剰酸素とは、例えば、化学量論的組成を超えて含まれる酸素をいう。または、過剰酸素とは、例えば、加熱することで当該過剰酸素が含まれる膜又は層から放出される酸素をいう。過剰酸素は、例えば、膜や層の内部を移動することができる。過剰酸素の移動は、膜や層の原子間を移動する場合や、膜や層を構成する酸素と置き換わりながら玉突き的に移動する場合などがある。

【0126】

絶縁体104としては、例えば、ホウ素、炭素、窒素、酸素、フッ素、マグネシウム、アルミニウム、シリコン、リン、塩素、アルゴン、ガリウム、ゲルマニウム、イットリウム、ジルコニウム、ランタン、ネオジム、ハフニウムまたはタンタルを含む絶縁体を、単層で、または積層で用いればよい。例えば、酸化シリコンまたは酸化窒化シリコンを有することが好ましい。

【0127】

過剰酸素を有する絶縁体104は、昇温脱離ガス分光法(TDS: Thermal Desorption Spectroscopy)分析にて、100以上700以下または100以上500以下の表面温度の範囲で、酸素分子の脱離量が $1.0 \times 10^{14}$  molecules/cm<sup>2</sup>以上 $1.0 \times 10^{16}$  molecules/cm<sup>2</sup>以下、より好ましくは、 $1.0 \times 10^{15}$  molecules/cm<sup>2</sup>以上 $5.0 \times 10^{15}$  molecules/cm<sup>2</sup>以下となる領域を有することが好ましい。

10

20

30

40

50

## 【0128】

TDS分析を用いた酸素の放出量の測定方法について、以下に説明する。

## 【0129】

測定試料をTDS分析したときの気体の全放出量は、放出ガスのイオン強度の積分値に比例する。そして標準試料との比較により、気体の全放出量を計算することができる。

## 【0130】

例えば、標準試料である所定の密度の水素を含むシリコン基板のTDS分析結果、および測定試料のTDS分析結果から、測定試料の酸素分子の放出量( $N_{O_2}$ )は、下に示す式で求めることができる。ここで、TDS分析で得られる質量電荷比32で検出されるガスの全てが酸素分子由来と仮定する。 $CH_3OH$ の質量電荷比は32であるが、存在する可能性が低いものとしてここでは考慮しない。また、酸素原子の同位体である質量数17の酸素原子および質量数18の酸素原子を含む酸素分子についても、自然界における存在比率が極微量であるため考慮しない。

10

## 【0131】

$$N_{O_2} = N_{H_2} / S_{H_2} \times S_{O_2} \times$$

## 【0132】

$N_{H_2}$ は、標準試料から脱離した水素分子を密度で換算した値である。 $S_{H_2}$ は、標準試料をTDS分析したときのイオン強度の積分値である。ここで、標準試料の基準値を、 $N_{H_2} / S_{H_2}$ とする。 $S_{O_2}$ は、測定試料をTDS分析したときのイオン強度の積分値である。は、TDS分析におけるイオン強度に影響する係数である。上に示す式の詳細に関しては、特開平6-275697公報を参照する。なお、上記酸素の放出量は、電子科学株式会社製の昇温脱離分析装置EMD-WA1000S/Wを用い、標準試料として一定量の水素原子を含むシリコン基板を用いて測定する。

20

## 【0133】

また、TDS分析において、酸素の一部は酸素原子として検出される。酸素分子と酸素原子の比率は、酸素分子のイオン化率から算出することができる。なお、上述のは酸素分子のイオン化率を含むため、酸素分子の放出量を評価することで、酸素原子の放出量についても見積もることができる。

## 【0134】

なお、 $N_{O_2}$ は酸素分子の放出量である。酸素原子に換算したときの放出量は、酸素分子の放出量の2倍となる。

30

## 【0135】

または、過剰酸素を有する絶縁体104は、過酸化ラジカルを含むこともある。具体的には、過酸化ラジカルに起因するスピン密度が、 $5 \times 10^{17} \text{ spins/cm}^3$ 以上であることをいう。なお、過酸化ラジカルを含む絶縁体は、電子スピン共鳴法(ESR: Electron Spin Resonance)にて、g値が2.01近傍に非対称の信号を有することもある。

## 【0136】

また、絶縁体104は、基板100からの不純物の拡散を防止する機能を有してもよい。また、絶縁体104は、水素トラップを有する絶縁体としてもよい。

40

## 【0137】

また、上述の通り半導体106bの上面又は下面是平坦性が高いことが好ましい。このため、絶縁体104の上面にCMP法などによって平坦化処理を行って平坦性の向上を図ってもよい。

## 【0138】

絶縁体112は、トランジスタ10のゲート絶縁膜として機能する。絶縁体112は、絶縁体104と同様に過剰酸素を有する絶縁体としてもよい。このような絶縁体112を設けることにより、絶縁体112から絶縁体106a、半導体106b及び絶縁体106cに酸素を供給することができる。これにより、半導体106bの欠陥準位密度を低減し、半導体106bを安定な特性を有する酸化物半導体とすることができます。

50

## 【0139】

絶縁体112としては、例えば、ホウ素、炭素、窒素、酸素、フッ素、マグネシウム、アルミニウム、シリコン、リン、塩素、アルゴン、ガリウム、ゲルマニウム、イットリウム、ジルコニウム、ランタン、ネオジム、ハフニウムまたはタンタルを含む絶縁体を、単層で、または積層で用いればよい。例えば、絶縁体112としては、酸化アルミニウム、酸化マグネシウム、酸化シリコン、酸化窒化シリコン、窒化酸化シリコン、窒化シリコン、酸化ガリウム、酸化ゲルマニウム、酸化イットリウム、酸化ジルコニウム、酸化ランタン、酸化ネオジム、酸化ハフニウムまたは酸化タンタルを用いればよい。

## 【0140】

導電体114はトランジスタ10のゲート電極として機能する。導電体114としては、例えば、ホウ素、窒素、酸素、フッ素、シリコン、リン、アルミニウム、チタン、クロム、マンガン、コバルト、ニッケル、銅、亜鉛、ガリウム、イットリウム、ジルコニウム、モリブデン、ルテニウム、銀、インジウム、スズ、タンタルおよびタンゲステンを一種以上含む導電体を、単層で、または積層で用いればよい。例えば、合金や化合物であってもよく、アルミニウムを含む導電体、銅およびチタンを含む導電体、銅およびマンガンを含む導電体、インジウム、スズおよび酸素を含む導電体、チタンおよび窒素を含む導電体などを用いてもよい。

10

## 【0141】

導電体114のチャネル長方向の側面端部と絶縁体112のチャネル長方向の側面端部は概略一致していることが好ましい。このような構造とすることにより、低抵抗領域107a及び低抵抗領域107bと、半導体106bの導電体114と重なる領域（チャネル形成領域）とが概略接する、もしくは一部が重なるため、オン電流の向上ができる。

20

## 【0142】

絶縁体116は、トランジスタ10の保護絶縁膜として機能し、且つ絶縁体106a、半導体106b及び絶縁体106cに元素を添加する機能を有する。上述の通り、絶縁体116は、絶縁体106a、半導体106b及び絶縁体106cの界面近傍に元素を添加し、低抵抗領域107a及び低抵抗領域107bを形成する。これにより、導電体108a又は導電体108bと絶縁体106a、半導体106b又は絶縁体106cとの接触抵抗を低減することができるトランジスタ10のオン電流を増大させることができる。

30

## 【0143】

また、絶縁体116は、酸素をロックする機能を有することが好ましい。このような絶縁体118を設けることにより、絶縁体104から絶縁体106a、半導体106b及び絶縁体106cに酸素を供給する際に、当該酸素が絶縁体104の上方に外部放出されてしまうことを防ぐことができる。これにより、絶縁体104から絶縁体106a、半導体106b及び絶縁体106cに効果的に酸素を供給することができる。ここで絶縁体116の膜厚としては、例えば5nm以上、又は20nm以上とすることができる。また、絶縁体116は、スパッタリング法などを用いて成膜することが好ましい。

40

## 【0144】

絶縁体116としては、例えば、ホウ素、マグネシウム、アルミニウム、シリコン、チタン、バナジウム、クロム、ニッケル、亜鉛、ガリウム、ゲルマニウム、イットリウム、ジルコニウム、ニオブ、モリブデン、インジウム、スズ、ランタン、セリウム、ネオジム、ハフニウム、タンタルまたはタンゲステンなどの元素のうち一または複数を含む、酸化物、酸化窒化物、窒化酸化物または窒化物を用いることができる。なお、本明細書において、酸化窒化物とは、その組成として窒素よりも酸素の含有量が多い材料を指し、窒化酸化物とは、その組成として、酸素よりも窒素の含有量が多い材料を示す。

## 【0145】

これらの元素は、比較的酸化物を形成しやすく、当該酸化物は半導体または絶縁体として機能しうるため、絶縁体106a、半導体106bまたは絶縁体106cの添加元素と

50

して好適である。

【0146】

また、絶縁体116を窒化物または窒化酸化物とする場合、アルミニウム、シリコン、チタン、ニッケル、亜鉛、ガリウム、モリブデン、インジウム、スズ、タンゲステンなどは窒化物または窒化酸化物が物性または構造が安定になりやすいため好適である。

【0147】

また、絶縁体116は、酸素とアルミニウムを含む絶縁体、例えば、酸化アルミニウムを用いることが好ましい。酸化アルミニウムは、酸素、および水素、水分などの不純物の両方に対して膜を透過させない遮断効果が高いので絶縁体116として用いるのに好適である。

10

【0148】

また、絶縁体116は酸素、水素、水、アルカリ金属、アルカリ土類金属、銅等をブロックする効果を有することが好ましい。このような絶縁体としては、例えば、窒化物絶縁膜を用いることができる。該窒化物絶縁膜としては、窒化シリコン、窒化酸化シリコン、窒化アルミニウム、窒化酸化アルミニウム等がある。なお、窒化物絶縁膜の代わりに、酸素、水素、水等のブロッキング効果を有する酸化物絶縁膜を設けてもよい。酸化物絶縁膜としては、酸化アルミニウム、酸化窒化アルミニウム、酸化ガリウム、酸化窒化ガリウム、酸化イットリウム、酸化窒化イットリウム、酸化ハフニウム、酸化窒化ハフニウム等がある。

【0149】

また、絶縁体116は、上述の絶縁体106aまたは絶縁体106cとして用いることができる酸化物を用いることもできる。このような絶縁体116としては、Inを含む酸化絶縁物を用いることが好ましく、例えば、In-A1酸化物、In-Ga酸化物、In-Ga-Zn酸化物を用いればよい。Inを含む酸化絶縁物はスパッタリング法で成膜する際に発生するパーティクル数が少ないので、絶縁体116として用いるのに好適である。

20

【0150】

絶縁体118は、層間絶縁膜として機能する。絶縁体118としては、例えば、ホウ素、炭素、窒素、酸素、フッ素、マグネシウム、アルミニウム、シリコン、リン、塩素、アルゴン、ガリウム、ゲルマニウム、イットリウム、ジルコニウム、ランタン、ネオジム、ハフニウムまたはタンタルを含む絶縁体を、単層で、または積層で用いてもよい。

30

【0151】

導電体108a及び導電体108bは、それぞれトランジスタ10のソース電極またはドレイン電極のいずれかとして機能する。

【0152】

導電体108a及び導電体108bとしては、例えば、ホウ素、窒素、酸素、フッ素、シリコン、リン、アルミニウム、チタン、クロム、マンガン、コバルト、ニッケル、銅、亜鉛、ガリウム、イットリウム、ジルコニウム、モリブデン、ルテニウム、銀、インジウム、スズ、タンタルおよびタンゲステンを一種以上含む導電体を、単層で、または積層で用いればよい。例えば、合金や化合物であってもよく、アルミニウムを含む導電体、銅およびチタンを含む導電体、銅およびマンガンを含む導電体、インジウム、スズおよび酸素を含む導電体、チタンおよび窒素を含む導電体などを用いてもよい。

40

【0153】

また、導電体108a及び導電体108bを、絶縁体118に埋め込むように形成し、絶縁体118上の導電体109a及び導電体109bと接続させる構成とする場合、絶縁体118、導電体108a及び導電体108bの上面を、CMP法などを用いて平坦化処理し、平坦性を向上させることが好ましい。

【0154】

導電体109a及び導電体109bは、それぞれトランジスタ10のソース電極またはドレイン電極のいずれかと接続する配線として機能する。導電体109a及び導電体10

50

9 b としては、導電体 108 a 及び導電体 108 b として用いることができる導電体を用いればよい。

【0155】

以上のような構成とすることにより、安定した電気特性を有するトランジスタを提供することができる。または、非導通時のリーク電流の小さいトランジスタを提供することができる。または、オン電流の大きいトランジスタを提供することができる。または、ノーマリーオフの電気特性を有するトランジスタを提供することができる。または、サブスレッショルドスイング値の小さいトランジスタを提供することができる。または、信頼性の高いトランジスタを提供することができる。

【0156】

10

<トランジスタの変形例 1 >

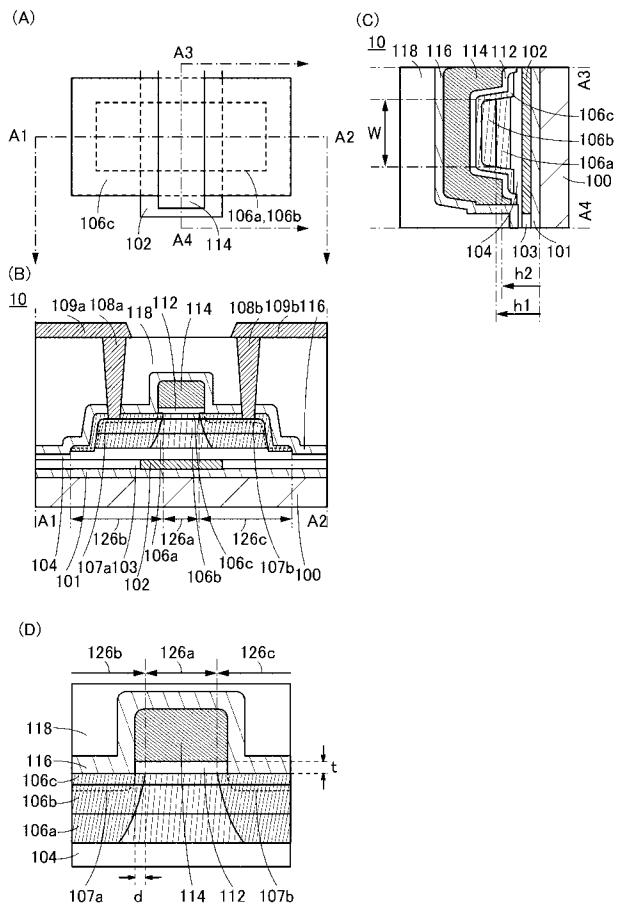

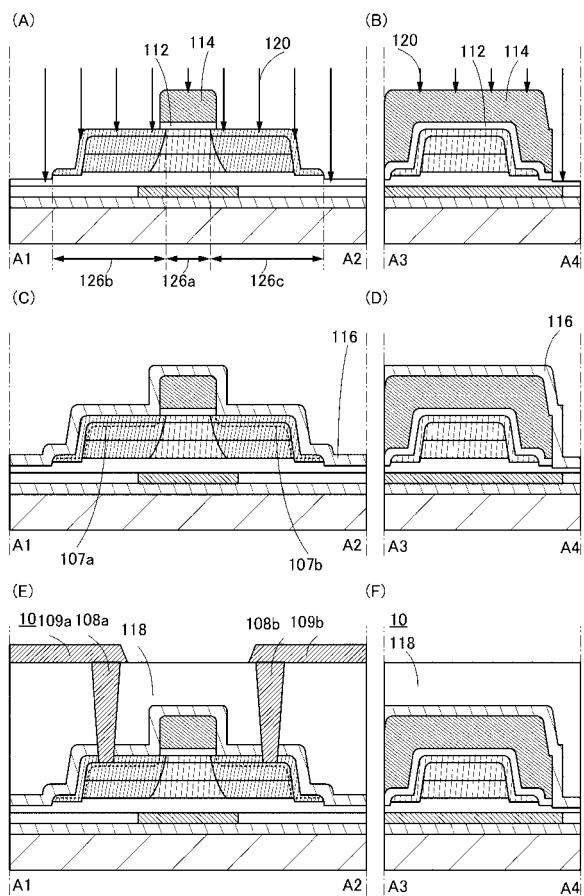

以下、トランジスタ 10 の変形例について図 2 及び図 3 を用いて説明する。なお、図 2 及び図 3 は、図 1 (B) (C) と同様に、トランジスタのチャネル長方向の断面図とトランジスタのチャネル幅方向の断面図になる。なお、以下に示すトランジスタ 10 の変形例の各構成は互いに適宜組み合わせて用いることができる。

【0157】

図 2 (A) (B) に示すトランジスタ 11 は、半導体 106 b の側面端部が絶縁体 106 a の側面端部より内側に形成されている点において、トランジスタ 10 と異なる。つまり、トランジスタ 11 では、絶縁体 106 a 及び絶縁体 106 c の外周が半導体 106 b の外周より外側に位置しており、半導体 106 b は絶縁体 106 a 及び絶縁体 106 c に包み込まれるように設けられる。また、絶縁体 106 a の側面端部、特にチャネル幅方向の側面端部と、絶縁体 106 c の側面端部、特にチャネル幅方向の側面端部と、が概略一致する形状となっていることが好ましい。

20

【0158】

図 2 (A) (B) に示すトランジスタ 11 のように、半導体 106 b の側面端部が絶縁体 106 a の側面端部より内側に位置するようにパターン形成することにより、絶縁体 104 が絶縁体 106 a または半導体 106 b のエッチングとともにエッチングされる回数を削減することができる。また、絶縁体 104 表面のエッチング箇所を導電体 102 から遠くにすることができるので、トランジスタ 11 の耐圧性の向上にもつながる。

30

【0159】

図 2 (A) (B) に示すトランジスタ 11 などでは、導電体 114 のチャネル長方向の側面端部と絶縁体 112 のチャネル長方向の側面端部は概略一致しているが、本実施の形態に示す半導体装置の構成はこれに限られるものではない。例えば、図 2 (C) (D) に示すトランジスタ 12 のように、導電体 114 のチャネル長方向の幅が絶縁体 112 のチャネル長方向の幅より小さい構成としてもよい。

【0160】

40

また、図 2 (A) (B) に示すトランジスタ 11 などでは、導電体 102 及び絶縁体 103 が形成されているが、本実施の形態に示す半導体装置の構成はこれに限られるものではない。例えば、図 2 (E) (F) に示すトランジスタ 13 のように、導電体 102 及び絶縁体 103 を設けない構成としてもよい。

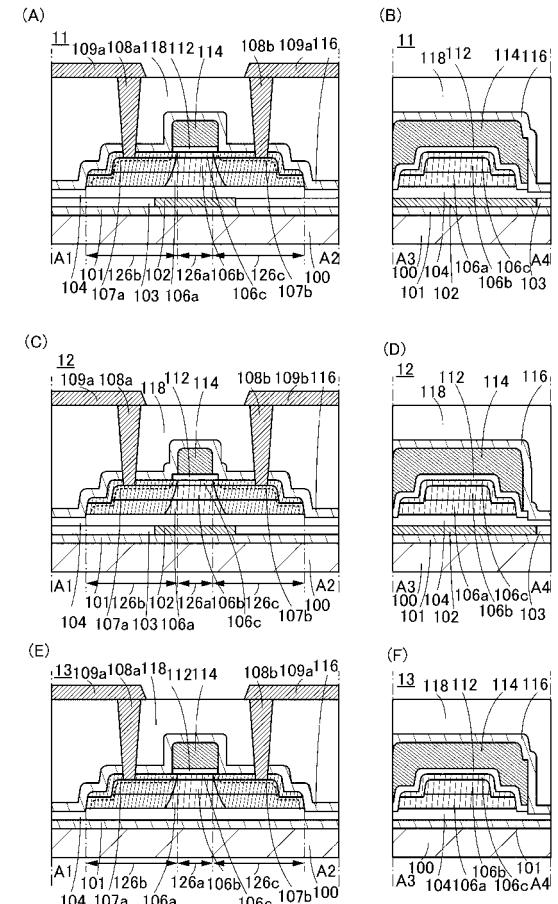

【0161】

図 3 (A) (B) に示すトランジスタ 14 は、絶縁体 104 の一部に膜厚が大きい領域が形成されている点において、トランジスタ 11 と異なる。絶縁体 104 の膜厚が大きい領域のチャネル幅方向の側面端部は、半導体 106 b のチャネル幅方向の側面端部より内側に位置することが好ましい。言い換えると、絶縁体 104 は凸部を有しており、上面から見たとき当該凸部の外周は、半導体 106 b の外周よりも内側に位置する。また、絶縁体 104 の膜厚が大きい領域のチャネル幅方向の側面端部は、絶縁体 106 a の膜厚と同程度、半導体 106 b のチャネル幅方向の側面端部より内側に位置することがより好ましい。ここで、絶縁体 104 の膜厚の大きい領域と膜厚の小さい領域の膜厚の差が、絶縁体 106 c と絶縁体 112 の膜厚の和より大きいことが好ましい。このような構成とすること

50

とにより、半導体 106b のチャネル幅方向の側面の概略全体を、絶縁体 106c と絶縁体 112 を介して、導電体 114 と対向させることができる。

【0162】

このような構成とすることにより、トランジスタ 14 を上記トランジスタ 10 と同様に、s-channel 構造とすることができます。よって、トランジスタ 14 でソース - ドレイン間に大電流を流すことができ、オン電流を高くすることができる。

【0163】

なお、図 3 (A) に示すトランジスタ 14 では、絶縁体 104 の膜厚が大きい領域は、チャネル長方向に伸長されて設けられているが、本実施の形態に示す構成はこれに限られるものではない。例えば、図 3 (C) に示すように、絶縁体 104 の膜厚が大きい領域のチャネル長方向の側面端部が、半導体 106b のチャネル長方向の側面端部より内側に位置する構成としてもよい。

【0164】

以上、本実施の形態で示す構成、方法は、他の実施の形態で示す構成、方法と適宜組み合わせて用いることができる。

【0165】

(実施の形態 2)

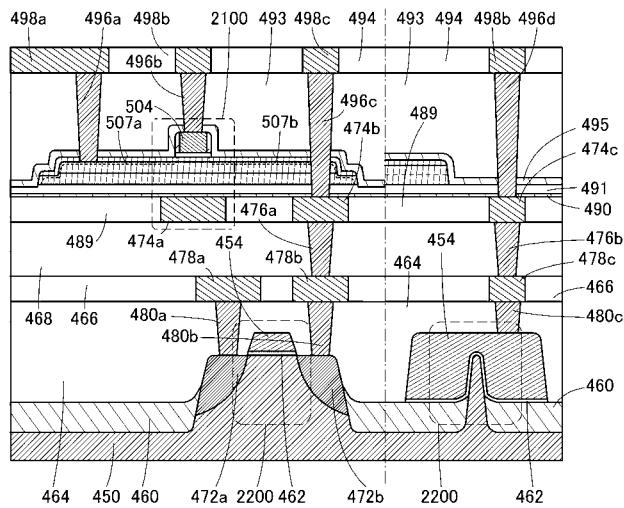

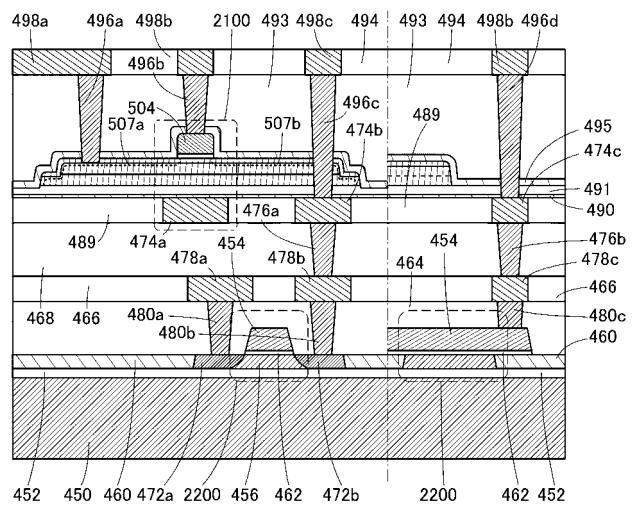

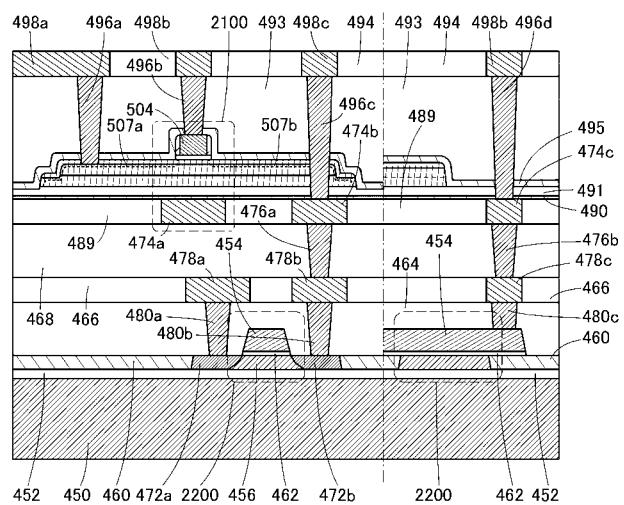

本実施の形態では、本発明の一態様に係る半導体装置の作製方法について、図 4 及び図 5 を用いて説明する。

【0166】

<トランジスタの作製方法 1>

以下において、図 1 に示すトランジスタ 10 の作製方法について説明する。

【0167】

まずは、基板 100 を準備する。基板 100 に用いる基板としては上述の基板を用いればよい。

【0168】

次に、絶縁体 101 を成膜する。絶縁体 101 としては上述の絶縁体を用いればよい。

【0169】

絶縁体 101 の成膜は、スパッタリング法、化学気相成長 (CVD : Chemical Vapor Deposition) 法、分子線エピタキシー (MBE : Molecular Beam Epitaxy) 法またはパルスレーザ堆積 (PLD : Pulsed Laser Deposition) 法、原子層堆積 (ALD : Atomic Layer Deposition) 法などを用いて行うことができる。

【0170】

なお、CVD 法は、プラズマを利用するプラズマ CVD (PECVD : Plasma Enhanced CVD) 法、熱を利用する熱 CVD (TCVD : Thermal CVD) 法、光を利用する光 CVD (Photo CVD) 法などに分類できる。さらに用いる原料ガスによって金属 CVD (MCVD : Metal CVD) 法、有機金属 CVD (MOCVD : Metal Organic CVD) 法に分けることができる。

【0171】

PECVD 法は、比較的低温で高品質の膜が得られる。また、TCVD 法は、プラズマを用いないため、被処理物へのプラズマダメージを小さくすることが可能な成膜方法である。例えば、半導体装置に含まれる配線、電極、素子 (トランジスタ、容量素子など) などは、プラズマから電荷を受け取ることでチャージアップする場合がある。このとき、蓄積した電荷によって、半導体装置に含まれる配線、電極、素子などが破壊される場合がある。一方、プラズマを用いない TCVD 法の場合、こういったプラズマダメージが生じないため、半導体装置の歩留まりを高くすることができる。また、TCVD 法では、成膜中のプラズマダメージが生じないため、欠陥の少ない膜が得られる。

【0172】

また、ALD 法も、被処理物へのプラズマダメージを小さくすることが可能な成膜方法

10

20

30

40

50

である。よって、A L D 法を用いることにより、欠陥の少ない膜が得られる。

【 0 1 7 3 】

C V D 法および A L D 法は、ターゲットなどから放出される粒子が堆積する成膜方法とは異なり、被処理物の表面における反応により膜が形成される成膜方法である。したがって、被処理物の形状の影響を受けにくく、良好な段差被覆性を有する成膜方法である。特に、A L D 法は、優れた段差被覆性と、優れた厚さの均一性を有するため、アスペクト比の高い開口部の表面を被覆する場合などに好適である。またこれにより、成膜した膜にピンホールなどが形成されにくくなる。ただし、A L D 法は、比較的成膜速度が遅いため、成膜速度の速い C V D 法などの他の成膜方法と組み合わせて用いることが好ましい場合もある。

10

【 0 1 7 4 】

C V D 法および A L D 法は、原料ガスの流量比によって、得られる膜の組成を制御することができる。例えば、C V D 法および A L D 法では、原料ガスの流量比によって、任意の組成の膜を成膜することができる。また、例えば、C V D 法および A L D 法では、成膜しながら原料ガスの流量比を変化させることによって、組成が連続的に変化した膜を成膜することができる。原料ガスの流量比を変化させながら成膜する場合、複数の成膜室を用いて成膜する場合と比べて、搬送や圧力調整に掛かる時間の分、成膜に掛かる時間を短くすることができる。したがって、半導体装置の生産性を高めることができる場合がある。

【 0 1 7 5 】

従来の C V D 法を利用した成膜装置は、成膜の際、反応のための原料ガスの 1 種または複数種がチャンバーに同時に供給される。A L D 法を利用した成膜装置は、反応のための原料ガス（プリカーサとも呼ぶ）と反応剤として機能するガス（リアクタントとも呼ぶ）を交互にチャンバーに導入し、これらのガスの導入を繰り返すことで成膜を行う。なお、導入ガスの切り替えは、例えば、それぞれのスイッチングバルブ（高速バルブとも呼ぶ）を切り替えて行うことができる。

20

【 0 1 7 6 】

例えば、以下のような手順で成膜を行う。まず、プリカーサをチャンバーに導入し、基板表面にプリカーサを吸着させる（第 1 ステップ）。ここで、プリカーサが基板表面に吸着することにより、表面化学反応の自己停止機構が作用し、基板上のプリカーサの層の上にさらにプリカーサが吸着することはない。なお、表面化学反応の自己停止機構が作用する基板温度の適正範囲を A L D Window とも呼ぶ。A L D Window は、プリカーサの温度特性、蒸気圧、分解温度などによって決まる。次に、不活性ガス（アルゴン、或いは窒素など）などをチャンバーに導入し、余剰なプリカーサや反応生成物などをチャンバーから排出する（第 2 ステップ）。また、不活性ガスを導入する代わりに真空排気によって、余剰なプリカーサや反応生成物などをチャンバーから排出してもよい。次に、リアクタント（例えば、酸化剤（H<sub>2</sub>O、O<sub>3</sub> など））をチャンバーに導入し、基板表面吸着したプリカーサと反応させて、膜の構成分子を基板に吸着させたままプリカーサの一部を除去する（第 3 ステップ）。次に、不活性ガスの導入または真空排気によって、余剰なリアクタントや反応生成物などをチャンバーから排出する（第 4 ステップ）。

30

【 0 1 7 7 】

このようにして、基板表面に第 1 の単一層を成膜することができ、第 1 乃至第 4 ステップを再び行うことで、第 1 の単一層の上に第 2 の単一層を積層することができる。第 1 乃至第 4 ステップを、ガス導入を制御しつつ、膜が所望の厚さになるまで複数回繰り返すことで、段差被覆性に優れた薄膜を形成することができる。薄膜の厚さは、繰り返す回数によって調節することができるため、精密な膜厚調節が可能であり、微細なトランジスタを作製する場合に適している。

40

【 0 1 7 8 】

A L D 法は、熱エネルギーを用いてプリカーサを反応させて行う成膜方法である。さらに、上記のリアクタントの反応において、プラズマを用いてリアクタントをラジカル状態として処理を行う A L D 法をプラズマ A L D 法と呼ぶことがある。またこれに対して、プ

50

リカーサ及びリアクタントの反応を熱エネルギーで行う A L D 法を熱 A L D 法と呼ぶことがある。

【 0 1 7 9 】

A L D 法は、極めて薄い膜を均一な膜厚で成膜することができる。また、凹凸を有する面に対しても、表面被覆率が高い。

【 0 1 8 0 】

また、プラズマ A L D 法により成膜することで、熱 A L D 法に比べてさらに低温での成膜が可能となる。プラズマ A L D 法は、例えば、100 以下でも成膜速度を低下させずに成膜することができる。また、プラズマ A L D 法では、酸化剤だけでなく、窒素ガスなど多くのリアクタントを用いることができる。酸化物だけでなく、窒化物、フッ化物、金属など多くの種類の膜を成膜することができる。

10

【 0 1 8 1 】

また、プラズマ A L D 法を行う場合には、I C P ( I n d u c t i v e l y C o u p l e d P l a s m a ) などのように基板から離れた状態でプラズマを発生させることもできる。このようにプラズマを発生させることにより、プラズマダメージを抑えることができる。

【 0 1 8 2 】

次に、絶縁体 103 を成膜する。絶縁体 103 としては上述の絶縁体を用いればよい。絶縁体 103 の成膜は、スパッタリング法、C V D 法、M B E 法または P L D 法、A L D 法などを用いて行うことができる。

20

【 0 1 8 3 】

次に、絶縁体 103 上にレジストなどを形成し、絶縁体 103 に開口を形成する。なお、単にレジストを形成するという場合、レジストの下に反射防止層を形成する場合も含まれる。

【 0 1 8 4 】

レジストなどは、対象物をエッチングなどによって加工した後で除去する。レジストなどの除去には、プラズマ処理または / およびウェットエッチングを用いる。なお、プラズマ処理としては、プラズマアッシングが好適である。レジストなどの除去が不十分な場合、0.001 重量 % 以上 1 重量 % 以下の濃度のフッ化水素酸または / およびオゾン水などによって取り残したレジストなどを除去しても構わない。

30

【 0 1 8 5 】

次に、導電体 102 となる導電体を成膜する。導電体 102 となる導電体としては、上述の導電体を用いることができる。導電体 102 となる導電体の成膜は、スパッタリング法、C V D 法、M B E 法または P L D 法、A L D 法などを用いて行うことができる。

【 0 1 8 6 】

次に、C M P 処理を行って、絶縁体 103 上の導電体 102 となる導電体を除去する。その結果、絶縁体 103 に形成された開口の中のみに、導電体 102 が残存する。

【 0 1 8 7 】

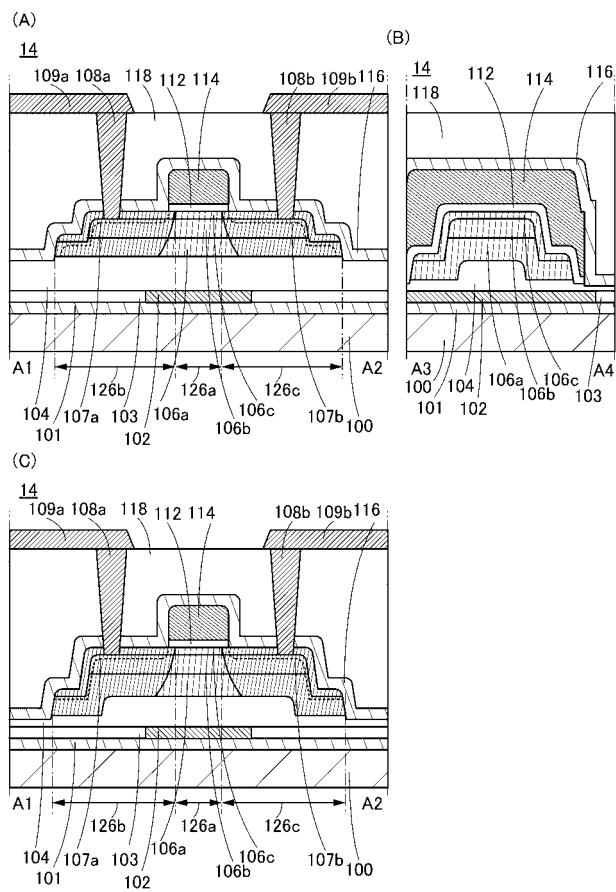

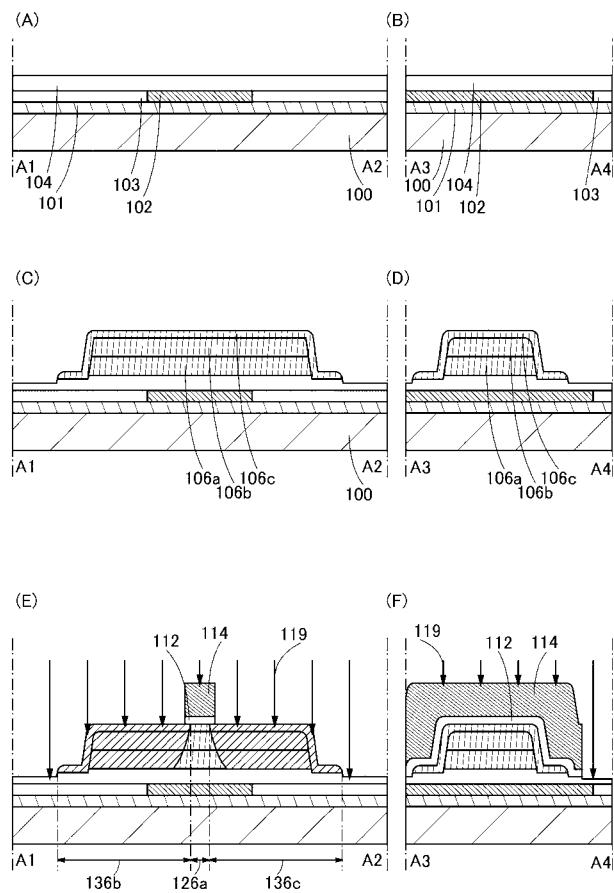

次に、絶縁体 104 を成膜する ( 図 4 ( A ) ( B ) 参照 ) 。絶縁体 104 としては上述の絶縁体を用いればよい。絶縁体 104 の成膜は、スパッタリング法、C V D 法、M B E 法または P L D 法、A L D 法などを用いて行うことができる。

40

【 0 1 8 8 】

また、後で形成する半導体 106 b の上面又は下面は平坦性が高いことが好ましい。このため、絶縁体 104 の上面に C M P 法などの平坦化処理を行って平坦性の向上を図ってもよい。

【 0 1 8 9 】

次に、後の工程で絶縁体 106 a となる絶縁体を成膜する。当該絶縁体としては上述の絶縁体 106 a として用いることができる絶縁体、半導体又は導電体を用いればよい。当該絶縁体の成膜は、スパッタリング法、C V D 法、M B E 法または P L D 法、A L D 法などを用いて行うことができる。

50

## 【0190】

また、絶縁体106aとなる絶縁体の成膜は、スパッタリング法を用いて行うことが好ましく、酸素を含む雰囲気下でスパッタリング法を用いて行うことがより好ましい。また、スパッタリング法を用いる際に、平行平板型のスパッタリング装置を用いてもよいし、対向ターゲット式のスパッタリング装置を用いてもよい。後述するが、対向ターゲット式のスパッタリング装置を用いた成膜では、被形成面へのダメージが小さくできるため、結晶性の高い膜を得やすい。よって後述するC A A C - O Sの成膜には、対向ターゲット式のスパッタリング装置を用いることが好ましい場合がある。

## 【0191】

平行平板型スパッタリング装置を用いた成膜法を、P E S P (parallel electrode sputtering)と呼ぶこともできる。また、対向ターゲット式スパッタリング装置を用いた成膜法を、V D S P (vapor deposition sputtering)と呼ぶこともできる。

10

## 【0192】

スパッタリング法で絶縁体106aとなる絶縁体の成膜を行うことにより、成膜と同時に絶縁体104の表面（絶縁体106a形成後は絶縁体106aと絶縁体104の界面）近傍に酸素が添加されることがある。ここで、酸素は、例えば、酸素ラジカルとして絶縁体104に添加されるが、酸素が添加されるときの状態はこれに限定されない。当該酸素は、酸素原子、又は酸素イオンなどの状態で絶縁体104に添加されてもよい。このように酸素を絶縁体104に添加することにより、絶縁体104に過剰酸素を含ませることができる。

20

## 【0193】

また、絶縁体104と絶縁体106aとなる絶縁体の界面近傍の領域に混合領域が形成されることがある。混合領域では、絶縁体104を構成する成分と絶縁体106aとなる絶縁体を構成する成分が含まれている。

## 【0194】

次に、後の工程で半導体106bとなる半導体を成膜する。当該半導体としては上述の半導体106bとして用いることができる半導体を用いればよい。当該半導体の成膜は、スパッタリング法、C V D法、M B E法またはP L D法、A L D法などを用いて行うことができる。また、P E S P法又はV D S P法で成膜することもできる。なお、絶縁体106aとなる絶縁体の成膜と、半導体106bとなる半導体の成膜と、を大気に暴露することなく連続で行うことで、膜中および界面への不純物の混入を低減することができる。

30

## 【0195】

また、成膜ガスはアルゴンなどの希ガス（ほかにヘリウム、ネオン、クリプトン、キセノンなど）と酸素との混合ガスを用いると好ましい。例えば、全体に占める酸素の割合を50体積%未満、好ましくは33体積%以下、さらに好ましくは20体積%以下、より好ましくは15体積%以下とすればよい。

## 【0196】

また、スパッタリング法を用いて成膜する場合、基板温度を高くしても構わない。基板温度を高くすることで、基板上面におけるスパッタ粒子のマイグレーションを助長させることができる。したがって、より密度が高く、より結晶性の高い酸化物を成膜することができる。なお、基板の温度は、例えば、100以上450以下、好ましくは150以上400以下、さらに好ましくは170以上350以下とすればよい。

40

## 【0197】

次に、加熱処理を行うことが好ましい。加熱処理を行うことで、後の工程で形成する絶縁体106aおよび半導体106bの水素濃度を低減させることができる場合がある。また、後の工程で形成する絶縁体106aおよび半導体106bの酸素欠損を低減させることができる場合がある。加熱処理は、250以上650以下、好ましくは450以上600以下、さらに好ましくは520以上570以下で行えばよい。加熱処理は、不活性ガス雰囲気、または酸化性ガスを10ppm以上、1%以上もしくは10%以上

50

含む雰囲気で行う。加熱処理は減圧状態で行ってもよい。または、加熱処理は、不活性ガス雰囲気で加熱処理した後に、脱離した酸素を補うために酸化性ガスを10 ppm以上、1%以上または10%以上含む雰囲気で加熱処理を行ってもよい。加熱処理によって、後の工程で形成する絶縁体106aおよび半導体106bの結晶性を高めることや、水素や水などの不純物を除去することなどができる。加熱処理は、ランプ加熱によるRTA装置を用いることもできる。

#### 【0198】

当該加熱処理により、絶縁体104から絶縁体106aとなる絶縁体、及び半導体106bとなる半導体に酸素を供給することができる。絶縁体104に対して加熱処理を行うことにより、極めて容易に酸素を絶縁体106aとなる絶縁体、及び半導体106bとなる半導体に供給することができる。

10

#### 【0199】

ここで、絶縁体101は、酸素をブロックするバリア膜として機能する。絶縁体101が絶縁体104の下に設けられることにより、絶縁体104中に拡散した酸素が絶縁体104より下層に拡散することを防ぐことができる。

#### 【0200】

このように絶縁体106aとなる絶縁体、及び半導体106bとなる半導体に酸素を供給し、酸素欠損を低減させることにより、欠陥準位密度の低い、高純度真性または実質的に高純度真性な酸化物半導体とすることができる。

#### 【0201】

また、高密度プラズマ処理などを行ってもよい。高密度プラズマは、マイクロ波を用いて生成すればよい。高密度プラズマ処理では、例えば、酸素、亜酸化窒素などの酸化性ガスを用いればよい。または、酸化性ガスと、He、Ar、Kr、Xeなどの希ガスと、の混合ガスを用いてもよい。高密度プラズマ処理において、基板にバイアスを印加してもよい。これにより、プラズマ中の酸素イオンなどを基板側に引き込むことができる。高密度プラズマ処理は基板を加熱しながら行ってもよい。例えば、上記加熱処理の代わりに高密度プラズマ処理を行う場合、上記加熱処理の温度より低温で同様の効果を得ることができる。高密度プラズマ処理は、絶縁体106aとなる絶縁体の成膜前に行ってもよいし、絶縁体112の成膜後に行ってもよいし、絶縁体116の成膜後などに行ってもよい。

20

#### 【0202】

次に、半導体106bとなる半導体上にレジストなどを形成し、該レジストなどを用いて加工し、絶縁体106a及び半導体106bを形成する。なお、図4(C)(D)に示すように、半導体106bの形成時に、絶縁体104の露出した表面が除去される場合がある。

30

#### 【0203】

次に、後の工程で絶縁体106cとなる絶縁体を成膜する。当該絶縁体としては上述の絶縁体、半導体又は導電体を用いればよい。当該絶縁体の成膜は、スパッタリング法、CVD法、MBE法またはPLD法、ALD法などを用いて行うことができる。また、PESP法又はVDS法で成膜することもできる。

40

#### 【0204】

次に、絶縁体106cとなる絶縁体上にレジストなどを形成し、該レジストなどを用いて加工し、絶縁体106cを形成する(図4(C)(D)参照)。なお、図4(C)(D)に示すように、絶縁体106cの形成時に、絶縁体104の露出した表面が除去される場合がある。

#### 【0205】

ここで、絶縁体106cについて、側面端部が半導体106bの側面端部の外側に位置するようにパターン形成を行う。特に、図4(D)に示すように、絶縁体106cのチャネル幅方向の側面端部が、半導体106bのチャネル幅方向の側面端部の外側に位置するようにパターン形成を行うことが好ましい。このように絶縁体106cを形成することにより、半導体106bが絶縁体106a及び絶縁体106cに包み込まれる構造となる。

50

## 【0206】

このような構造とすることにより、半導体106bの側面端部、特にチャネル幅方向の側面端部が、絶縁体106a及び絶縁体106cと接して設けられている。これにより、半導体106bの側面端部において、絶縁体106a又は絶縁体106cとの間に連続接合が形成され、欠陥準位密度が低減される。よって、低抵抗領域107a及び低抵抗領域107bを設けることによりオン電流が流れやすくなっても、半導体106bのチャネル幅方向の側面端部が寄生チャネルとならず、安定した電気特性を得ることができる。

## 【0207】

次に、後の工程で絶縁体112となる絶縁体を成膜する。当該絶縁体としては上述の絶縁体112として用いることができる絶縁体を用いればよい。当該絶縁体の成膜は、スパッタリング法、CVD法、MBE法またはPLD法、ALD法などを用いて行うことができる。例えば、ALD法を用いて成膜時の基板温度を400以上520以下、好ましくは450以上500以下に設定して絶縁体112を成膜すればよい。成膜時の基板温度を高くすることによって、絶縁体112に含まれる不純物濃度を低減することができる。例えば、成膜ガスや成膜室に含まれる炭素化合物や水などを低減することができるため、炭素濃度または/および水素濃度を低減することができる。また、成膜時の基板温度を高くすることによって、絶縁体112の密度(膜密度ともいう。)を高くすることができる。絶縁体112の密度を高くすることによって、絶縁体112の欠陥準位密度を低くすることができるため、作製するトランジスタに安定した電気特性を付与することができる。

10

20

## 【0208】

次に、後の工程で導電体114となる導電体を成膜する。当該導電体としては、上述の導電体114に用いることができる導電体を用いればよい。当該導電体の成膜は、スパッタリング法、CVD法、MBE法またはPLD法、ALD法などを用いて行うことができる。

## 【0209】

次に、導電体114となる導電体上にレジストなどを形成し、該レジストなどを用いて加工し、絶縁体112及び導電体114を形成する(図4(E)(F)参照。)。ここでは、導電体114のチャネル長方向の側面端部と絶縁体112のチャネル長方向の側面端部は概略一致するように形成した後で、同じマスクを用いてウェットエッティングなどによって、導電体114のみを選択的にエッティングしてもよい。このようにエッティングすることで、図2(C)(D)に示すトランジスタ12のように、導電体114のチャネル長方向の幅が絶縁体112のチャネル長方向の幅より小さい構成とすることができる。

30

## 【0210】

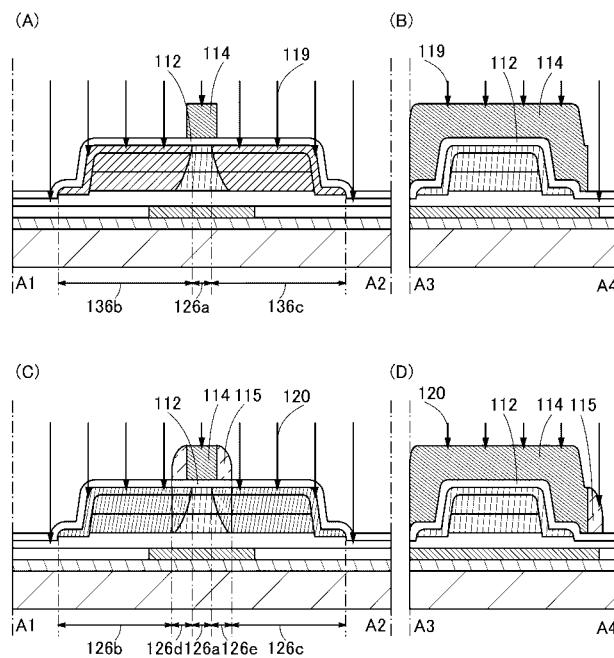

次に、導電体114及び絶縁体112をマスクとして、絶縁体106a、半導体106b及び絶縁体106cにドーパント119を添加する(図4(E)(F)参照)。これにより、絶縁体106a、半導体106b及び絶縁体106cに領域126a、領域136b及び領域136cが形成される。なお、領域136b及び領域136cは後の工程で領域126b及び領域126cとなる領域である。このため、領域136b及び領域136cは領域126aより、SIMS分析により得られるドーパント119の濃度が高くなる。ドーパント119の添加方法としては、イオン化された原料ガスを質量分離して添加するイオン注入法、イオン化された原料ガスを質量分離せずに添加するイオンドーピング法、プラズマイマージョンイオンインプランテーション法などを用いることができる。質量分離を行う場合、添加するイオン種およびその濃度を厳密に制御することができる。一方、質量分離を行わない場合、短時間で高濃度のイオンを添加することができる。また、原子または分子のクラスターを生成してイオン化するイオンドーピング法を用いてもよい。なお、ドーパントを、イオン、ドナー、アクセプター、不純物または元素と言い換えてよい。

40

## 【0211】

ドーパント119の添加工程は、加速電圧、ドーズ量などの注入条件を適宜設定して制

50

御すればよい。ドーパント119のドーズ量は、例えば、 $1 \times 10^{12}$  ions/cm<sup>2</sup>以上 $1 \times 10^{16}$  ions/cm<sup>2</sup>以下、好ましくは $1 \times 10^{13}$  ions/cm<sup>2</sup>以上 $1 \times 10^{15}$  ions/cm<sup>2</sup>以下とすればよい。ドーパント119導入時の加速電圧は2kV以上50kV以下、好ましくは5kV以上30kV以下とすればよい。

#### 【0212】

また、基板を加熱しながらドーパント119の添加を行ってもよい。基板温度は、例えば、200以上700以下、好ましくは300以上500以下、より好ましくは350以上450以下とする。

#### 【0213】

ドーパント119としては、例えば、水素、ヘリウム、ネオン、アルゴン、クリプトン、キセノン、窒素、フッ素、リン、塩素、ヒ素、ホウ素、マグネシウム、アルミニウム、シリコン、チタン、バナジウム、クロム、ニッケル、亜鉛、ガリウム、ゲルマニウム、イットリウム、ジルコニウム、ニオブ、モリブデン、インジウム、スズ、ランタン、セリウム、ネオジム、ハフニウム、タンタルまたはタンゲステンなどが挙げられる。これらの元素の中でも、ヘリウム、ネオン、アルゴン、クリプトン、キセノン、窒素、フッ素、リン、塩素、ヒ素またはホウ素は、イオン注入法、イオンドーピング法、プラズマイマージョンイオンインプランテーション法などを用いて比較的容易に添加することができるため、好適である。

#### 【0214】

また、ドーパント119の添加処理後、加熱処理を行ってもよい。加熱処理は、例えば、250以上650以下、好ましくは350以上450以下とし、窒素雰囲気下、減圧下、大気（超乾燥エア）下で加熱処理を行ってもよい。

#### 【0215】

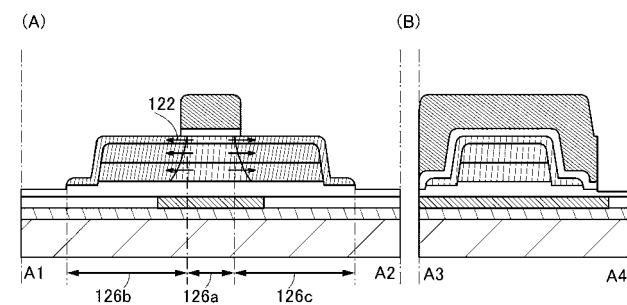

例えば、ドーパント119の添加によって領域136bおよび領域136cに酸素欠損を形成した場合、その後の加熱処理によって領域136bおよび領域136cの近傍にある水素122を酸素欠損となったサイトにゲッタリングさせることができる（図6（A）（B）参照。）。これにより、領域136b及び領域136cを低抵抗化させ、領域126b及び領域126cを形成することができる。このようにして形成されたドナー準位は安定であるため、後に高抵抗化することが少ない。なお、当該加熱処理で十分に領域126b及び領域126cを低抵抗化できる場合、下記に示すドーパント120の添加工程を省略してもよい。

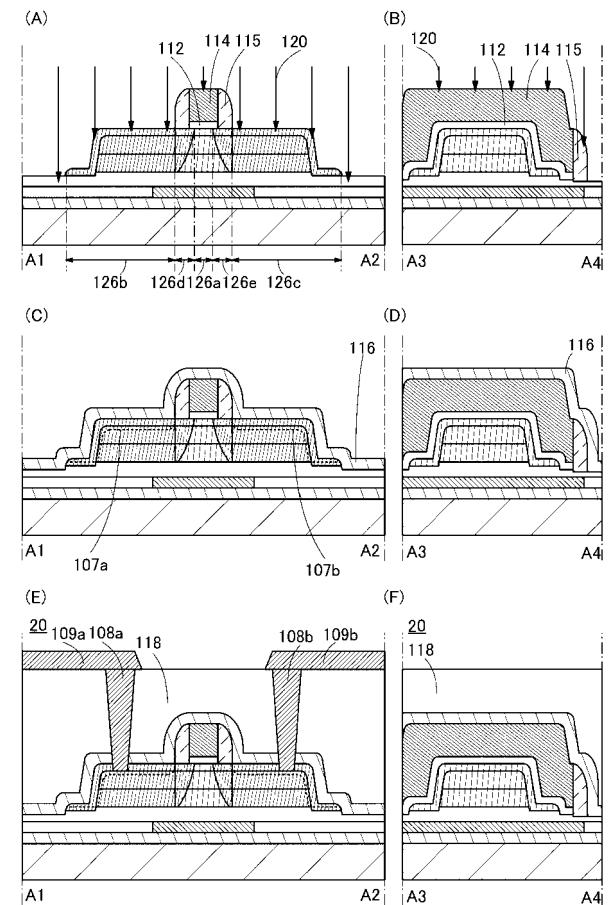

#### 【0216】

次に、導電体114及び絶縁体112をマスクとして、絶縁体106a、半導体106b及び絶縁体106cにドーパント120を添加する（図5（A）（B）参照）。これにより、領域136b及び領域136cが低抵抗化されて領域126b及び領域126cを形成することができる。このため、領域126b及び領域126cは領域126aより、SIMS分析により得られるドーパント120の濃度が高くなる。ドーパント120の添加方法としては、イオン注入法、イオンドーピング法、プラズマイマージョンイオンインプランテーション法などを用いることができる。なお、ドーパントを、イオン、ドナー、アクセプター、不純物または元素と言い換えてよい。

#### 【0217】

ドーパント120の添加工程は、加速電圧、ドーズ量などの注入条件を適宜設定して制御すればよい。ドーパント120のドーズ量は、例えば、 $1 \times 10^{12}$  ions/cm<sup>2</sup>以上 $1 \times 10^{16}$  ions/cm<sup>2</sup>以下、好ましくは $1 \times 10^{13}$  ions/cm<sup>2</sup>以上 $1 \times 10^{15}$  ions/cm<sup>2</sup>以下とすればよい。ドーパント120導入時の加速電圧は2kV以上50kV以下、好ましくは5kV以上30kV以下とすればよい。

#### 【0218】

また、基板を加熱しながらドーパント120の添加を行ってもよい。基板温度は、例えば、200以上700以下、好ましくは300以上500以下、より好ましくは350以上450以下とする。このように加熱しながらドーパント120を添加する

10

20

30

40

50

ことにより、ドーパント 120 の添加による、絶縁体 106a、半導体 106b 及び絶縁体 106c の結晶性の低下を低減することができる。

【0219】

ドーパント 120 としては、ドーパント 119 として添加したドーパント以外を添加すればよい。例えば、水素、ヘリウム、ネオン、アルゴン、クリプトン、キセノン、窒素、フッ素、リン、塩素、ヒ素、ホウ素、マグネシウム、アルミニウム、シリコン、チタン、バナジウム、クロム、ニッケル、亜鉛、ガリウム、ゲルマニウム、イットリウム、ジルコニウム、ニオブ、モリブデン、インジウム、スズ、ランタン、セリウム、ネオジム、ハフニウム、タンタルまたはタンゲステンなどが挙げられる。これらの元素の中でも、ヘリウム、ネオン、アルゴン、クリプトン、キセノン、窒素、フッ素、リン、塩素、ヒ素またはホウ素は、イオン注入法、イオンドーピング法、プラズマイマージョンイオンインプランテーション法などを用いて比較的容易に添加することができるため、好適である。

10

【0220】

また、ドーパント 120 の添加処理後、加熱処理を行ってもよい。加熱処理は、例えば、250 以上 650 以下、好ましくは 350 以上 450 以下とし、窒素雰囲気下、減圧下、大気（超乾燥エア）下で加熱処理を行ってもよい。

【0221】

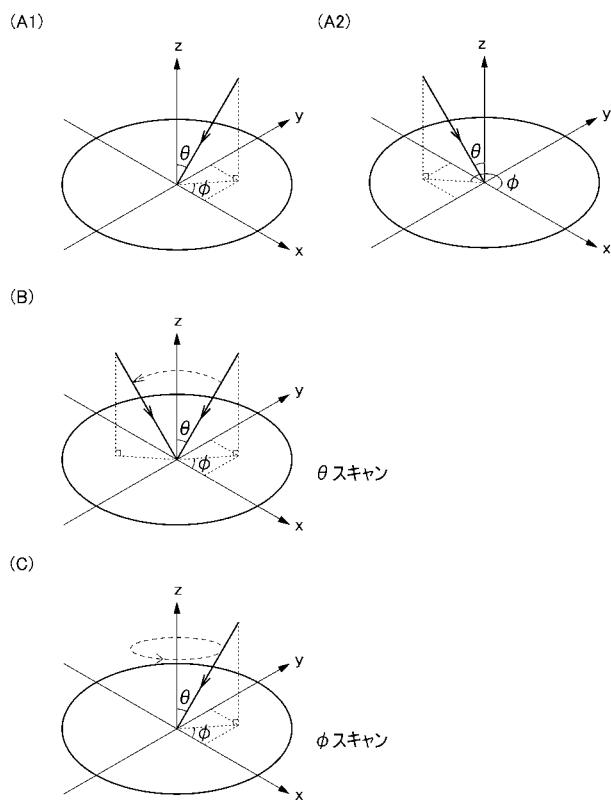

以下に、ドーパント 119 及びドーパント 120 の添加方法について図 7 を用いて説明する。なお、以下ではドーパントとしてイオンを用いるイオン注入法又はイオンドーピング法の詳細について説明する。

20

【0222】

イオンドーピング処理によるイオンの添加は、試料面に対して特定の角度（例えば、垂直な角度）から行ってもよいが、図 7 に示す方法で行うと好ましい。図 7 は、一つのイオンが、試料面に対し、角度（ ）および角度（ ）で入射する様子を簡略的に示した図である。

【0223】

図中の x 軸、y 軸および z 軸は、あるイオンの入射点で交差する直線である。x 軸は、試料面上に任意に定めた直線である。y 軸は、試料面上にあり、x 軸と直交する直線である。z 軸は、入射点における試料面の法線である。角度（ ）は、断面図において、イオンの入射方向と z 軸との為す角度である。また、角度（ ）は、上面図において、イオンの入射方向と x 軸との為す角度である。

30

【0224】

ある物体をマスクとして試料面に対して特定の角度（ ）からイオンを入射させた場合、物体の下部にある試料の一部に対してもイオンを添加することができる。

【0225】

また、試料面に対して特定の角度（ ）のみからイオンを入射させた場合、物体が高さを有することにより、イオンが入射する側と反対側にイオンの添加されない領域が生じる場合がある。イオンの添加されない領域を物体の陰と呼ぶことができる。したがって、イオンを複数の角度から入射させることにより、試料面に生じる陰の影響を低減することが好ましい。

40

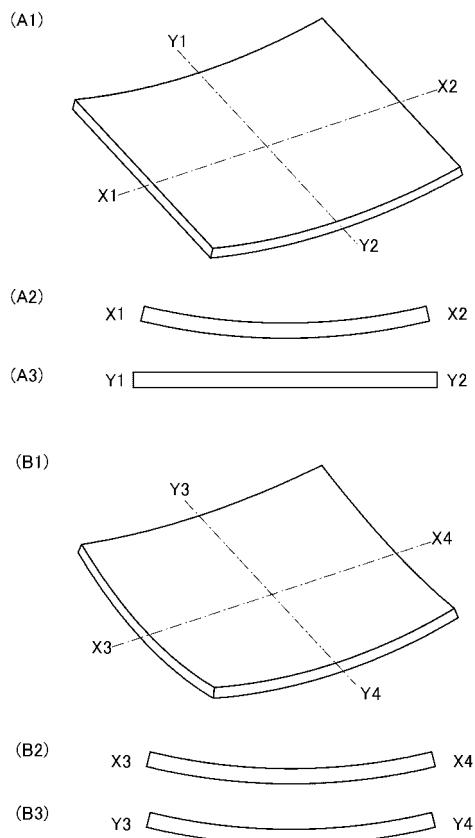

【0226】

図 7 (A1) および図 7 (A2) に示すように、イオンを試料面に対し、第 1 の角度（ ）で入射させた後、第 2 の角度（ ）で入射させればよい。ただし、第 1 の角度（ ）および第 2 の角度（ ）は、の少なくとも一方が異なる角度である。

【0227】

第 1 の角度（ ）における角度（ ）は、例えば、10° 以上 60° 以下、好ましくは 15° 以上 45° 以下、さらに好ましくは 20° 以上 40° 以下とする。第 2 の角度（ ）における角度（ ）は、例えば、10° 以上 60° 以下、好ましくは 15° 以上 45° 以下、さらに好ましくは 20° 以上 40° 以下とする。なお、第 2 の角度（ ）

50

)における角度と、第1の角度( , )における角度と、はz軸に対して対称である。よって、第2の角度( , )における角度を、負の値として表すこともできる。具体的には、第2の角度( , )における角度( )を、例えば、-60°以上-10°以下、好ましくは-45°以上-15°以下、さらに好ましくは-40°以上-20°以下と表記することもできる。

#### 【0228】

ここで、上記のように試料面に対して特定の角度でイオンを入射させる場合、図1(D)に示す絶縁体112の膜厚tと距離dとの間に相関がある。例えば、イオンが絶縁体112の側面の上端から入射する場合、絶縁体106cに当該イオンが入射する位置は、導電体114の側面端部から距離 $t \cdot \tan$ の位置になる。ここで、導電体114は金属を含んで形成されることが多く、当該イオンが入射しにくい。よって、チャネル長方向においてチャネル形成領域に侵入する長さが最も長くなるのは、イオンが絶縁体112の側面の上端から入射する場合である。よって、距離 $t \cdot \tan$ は、図1(D)に示す距離dの目安となるので、膜厚tと距離dの間に相関が見られる。例えば上記のように、イオンの入射角度( )を15°以上45°以下とすると、 $\tan 15^\circ = 0.2679$ 、 $\tan 45^\circ = 1$ なので、上記の式 $0.25t < d < t$ とよく対応している。

#### 【0229】

第2の角度( , )における角度( )は、例えば、第1の角度( , )における角度( )よりも90°以上270°以下、好ましくは135°以上225°以下大きい角度とし、代表的には180°とする。ただし、ここで示した第1の角度( , )および第2の角度( , )は一例であり、これに限定されるものではない。

#### 【0230】

なお、イオンを入射させる角度は、第1の角度( , )、第2の角度( , )の2種類に限定されない。例えば、第1乃至第n(nは2以上の自然数)の角度( , )で入射させてもよい。第1乃至第nの角度( , )は、それぞれ、の少なくとも一方が異なる角度を含む。

#### 【0231】

または、図7(B)に示すように、イオンを、試料面に対し第1の角度( , )で入射させた後、角度( )が0°を経由して第2の角度( , )まで方向にスキャン(スキャンともいう。)させてもよい。ただし、イオンを入射させる角度( )は、1種類に限定されず、第1乃至第n(nは2以上の自然数)の角度( )で入射させてもよい。

#### 【0232】

第1の角度( , )における角度( )は、例えば、10°以上60°以下、好ましくは15°以上45°以下、さらに好ましくは20°以上40°以下とする。第2の角度( , )における角度( )は、例えば、10°以上60°以下、好ましくは15°以上45°以下、さらに好ましくは20°以上40°以下とする。第1の角度( , )と第2の角度( , )とは同じ角度( )であってもよい。

#### 【0233】

なお、スキャンは、連続的にスキャンしてもよいが、例えば、0.5°、1°、2°、3°、4°、5°、6°、10°、12°、18°、20°、24°または30°ステップで段階的にスキャンしてもよい。

#### 【0234】

または、イオンは、図7(C)に示すように、試料面に対し、第1の角度( , )で入射させた後、第2の角度( , )まで方向にスキャン(スキャンともいう。)させればよい。ただし、イオンを入射させる角度( )は、1種類に限定されず、第1乃至第n(nは2以上の自然数)の角度( )で入射させてもよい。

#### 【0235】

第1の角度( , )および第2の角度( , )において、角度( )は、例えば、10°以上60°以下、好ましくは15°以上45°以下、さらに好ましくは20°以上

10

20

30

40

50

40°以下とする。第1の角度( , )と第2の角度( , )とは同じ角度( )であってもよい。

【0236】

なお、スキャンは、連続的にスキャンしてもよいが、例えば、0.5°、1°、2°、3°、4°、5°、6°、10°、12°、18°、20°、24°または30°ステップで段階的にスキャンしてもよい。

【0237】

なお、図示しないが、スキャンおよびスキャンを組み合わせて行っても構わない。

【0238】

以上のようにして、イオンの添加された領域126bおよび領域126cを形成すればよい。

10

【0239】

図7に示した方法を用いることで、領域126bおよび領域126cを、導電体114と重ならない領域に加え、一部が導電体114と重なる領域にまで形成することができる。したがって、領域126bおよび領域126cと、領域126aとの間に、高抵抗のオフセット領域が形成されないため、トランジスタのオン電流を高くすることができる。

【0240】

ドーパント119およびドーパント120の添加によって、領域126b及び領域126cを低抵抗化することができる。領域126b及び領域126cの低抵抗化のメカニズムは、ドーパント119とドーパント120との組み合わせによって異なる。

20

【0241】

例えば、ドーパント119と、ドーパント120と、で異なるドナー準位を形成することで領域126b及び領域126cを低抵抗化することができる。

【0242】

または、例えば、まずドーパント119を添加し、次にドーパント120を添加することでドナー準位を形成して領域126b及び領域126cを低抵抗化することもできる。この場合、例えば、ドーパント119の添加によって領域126b及び領域126cに酸素欠損を形成した後、ドーパント120を添加することでドナー準位を形成すればよい。または、例えば、ドーパント119を添加した後に、ドーパント120を添加することで領域126b及び領域126cに酸素欠損を形成してもよい。その後、加熱処理などによって、酸素欠損となったサイトにドーパント119またはドーパント120を移動させ、ドナー準位を形成することができる。例えば、酸素欠損となったサイトに水素が入ることでドナー準位となる場合がある。このようにして形成されたドナー準位は安定であるため、後に高抵抗化することが少ない。

30

【0243】

以下では、酸化物半導体が、酸素欠損及び水素を含むことで、抵抗率が低減することについて説明する。なお、ここでは、酸素欠損となったサイト( $V_o$ )に水素原子Hがある状態を $V_oH$ と表記する。

【0244】

<1-a 計算手法>

40

ここで、In-Ga-Zn酸化物中の $V_o$ 及び水素が同時に存在することによる影響を、第一原理計算を用いて調べた。はじめに、 $V_o$ のできやすい酸素サイト、及び水素原子の存在形態を調べた。次に、 $V_o$ の内側または外側における水素原子の安定性について調べた。最後に、安定に存在しやすい欠陥の遷移レベルを算出した。

【0245】

第一原理計算には、Vienna Ab initio Simulation Package (VASP)を使用した。また、ハイブリッド汎関数には、Heyd-Scuseria-Ernzerhof (HSE)汎関数を用い、交換相関ポテンシャルには、Perdew-Burke-Ernzerhof (PBE)型のGeneralized-Gradient-Approximation (GGA)を用い、擬ポテンシャルに

50

は projector augmented-wave (PAW) 法を用いた。V<sub>o</sub> の内側または外側における水素原子の安定性に関する計算では GGA を使用し、形成エネルギーや遷移レベルの計算ではエネルギーギャップの精度が要求されるため HSE 汎関数を使用した。GGA を用いた場合、エネルギーのカットオフは 500 eV、k-point は Monkhorst-Pack メッシュの  $2 \times 2 \times 3$  サンプリングとした。また、HSE 汎関数を用いた場合、エネルギーのカットオフは 800 eV、k-point のサンプリングは点のみとした。また、HSE 汎関数におけるスクリーニングパラメータを  $2 \text{ nm}^{-1}$ 、Hartree-Fock の交換項の比率を 0.25 とした。

## 【0246】

&lt;1-b 欠陥の形成エネルギー&gt;

欠陥濃度 c は、欠陥 D の形成エネルギー ( $E_{\text{form}}(D)$ ) 及び数式 (1) より算出される。

## 【0247】

## 【数1】

$$c = N_{\text{sites}} \exp\left\{-E_{\text{form}}(D)/k_B T\right\} \quad (1)$$

## 【0248】

ここで、 $N_{\text{sites}}$  は欠陥 D が形成されるサイトの数、 $k_B$  はボルツマン定数、T は温度である。つまり、形成エネルギーが小さいほど欠陥 D は形成されやすいといえる。そこで、形成エネルギーを、数式 (2) より算出した。

## 【0249】

## 【数2】

$$E_{\text{form}}(D) = E_{\text{tot}}(D^q) - E_{\text{tot}}(\text{bulk}) + \sum_i \Delta n_i \mu_i + q(\varepsilon_{VBM} + \Delta V_q + E_F) \quad (2)$$

## 【0250】

ここで、 $E_{\text{tot}}(D^q)$  は電荷 q の欠陥 D をもつセルの全エネルギー、 $E_{\text{tot}}(\text{bulk})$  は完全結晶の全エネルギー、 $n_i$  は原子 i の増減数、 $\mu_i$  は原子 i の化学ポテンシャル、 $\varepsilon_{VBM}$  は価電子帯上端 (VBM) のエネルギー、 $V_q$  は参照ポテンシャルに関する補正項、 $E_F$  はフェルミエネルギーである。このとき、VBM のエネルギーをフェルミエネルギーが 0 eV として表記する。化学ポテンシャルは環境に依存する。そこで、酸素の化学ポテンシャル ( $\mu_o$ ) の上限 (酸素リッチ条件) を酸素分子の全エネルギーの半分とした。この時の水素の化学ポテンシャル ( $\mu_H$ ) は、水分子の全エネルギーから酸素の化学ポテンシャルを引いた値の半分とした。

## 【0251】

なお、酸素リッチ条件とは、例えば、酸素欠損が生じたときに、該酸素欠損に酸素が入りやすい条件、即ち、酸素欠損の形成が抑制される条件である。

## 【0252】

一方、水素リッチ条件での水素の化学ポテンシャル ( $\mu_H$ ) は水素分子の全エネルギーの半分とし、この時の酸素の化学ポテンシャルは、下限 (酸素プア条件) となるが、水分子の全エネルギーから  $\mu_H$  の 2 倍を引いた値とした。

## 【0253】

なお、酸素プア条件とは、酸素欠損が生じたときに、酸素欠損の形成が促進される条件である。

## 【0254】

&lt;1-c 欠陥の遷移レベル&gt;

欠陥の種類によっては、異なる荷電状態への遷移を伴う準位 (遷移レベルともいう。) がエネルギーギャップ内に存在し、準位の深さとフェルミ準位の位置によってキャリアの捕獲や放出の要因となる。そこで、欠陥 D の遷移レベル ( $(q/q')$ ) を、以下の数

10

20

30

40

50

式(3)より算出した。

【0255】

【数3】

$$\varepsilon(q/q') = \frac{E_{form}(D^q) - E_{form}(D^{q'})}{q' - q} \quad (3)$$

【0256】

数式(3)より得られる( $q/q'$ )値は、価電子帯上端を0.0eVとした時の遷移レベルの位置を表す。言い換えると、エネルギーギャップから遷移レベルを引いた値は、伝導帯下端(CBM)からの深さに相当することになる。また、フェルミ準位が( $q/q'$ )よりも価電子帯側であれば、その欠陥は荷電状態 $q$ で安定であり、伝導帯側であれば、その欠陥は荷電状態 $q'$ で安定であるといえる。

10

【0257】

<1-d 原子の拡散>

次に、Nudged Elastic Band(NEB)法を用いて、原子の拡散過程における経路および活性障壁を調べた。NEB法とは、始状態から終状態までの経路の中で、エネルギーが最も低くなる経路を探し出す手法である。原子が受ける力が0.5eV/nm以下となるまで原子座標を緩和させる計算を行った。

20

【0258】

<1-e 計算構造>

通常、欠陥を有するセルは、完全結晶に対して1個の欠陥が存在するように作成されるが、3次元の周期境界条件を設定するため、欠陥同士の相互作用を小さくするには欠陥同士の間隔を広げる、つまり、格子サイズを大きくする必要がある。ホモロガス構造である $InGaO_3$ ( $ZnO$ )<sub>m</sub>結晶では、格子定数 $a$ (および格子定数 $b$ )は、格子定数 $c$ に対して非常に小さい。そのため、 $a$ および $b$ 軸方向の格子サイズを格子定数 $c$ と同程度にしようとする、原子数が非常に多くなってしまう。そこで、 $m=1$ において格子ベクトルを(420)、(040)、(211)とした後に、格子定数 $c$ を1/3倍にして得られる112原子のスーパーセル( $InGaZnO_4$ )を用意した(図8参照。)。これにより、欠陥同士の間隔が最短軸長の方向でも0.8nm以上となる。

30

【0259】

また、 $InGaO_3$ ( $ZnO$ )<sub>m</sub>( $m=1$ )では、 $InO_2$ 層と次の $InO_2$ 層との間には、Ga、Zn、およびOで構成されている層((Ga, Zn)O層)が2層存在する。この2層におけるGaおよびZnの配列は、エネルギーが最も低くなる配置を選んだ。このとき、酸素に対して最近接となる金属原子の組み合わせより、酸素サイトは図8のO<sub>(1)</sub>からO<sub>(4)</sub>に示す4種類存在する。具体的には、3個のInと1個のZnと結合するOサイト(O<sub>(1)</sub>)、3個のInと1個のGaと結合するOサイト(O<sub>(2)</sub>)、a-b面方向に1個のGaと2個のZnと結合するOサイト(O<sub>(3)</sub>)、a-b面方向に2個のGaと1個のZnと結合するOサイト(O<sub>(4)</sub>)である。

30

【0260】

はじめに、完全結晶に対して、格子定数および原子座標の最適化をGGAまたはHSE汎関数を用いて行った。得られた格子定数およびエネルギーギャップを下表に示す。比較のために、実験で得られた格子定数およびエネルギーギャップも併せて記載する。GGAを用いた場合、格子定数は実験値と比較すると過大評価され、エネルギーギャップは過小評価されている。一方、HSE汎関数を用いた場合、格子定数およびエネルギーギャップは実測に近い値となっている。ちなみに計算で得られた格子定数 $a$ と $b$ がわずかに異なるのは、GaおよびZnの配置によるものである。

40

【0261】

【表1】

|       | a [Å] | b [Å] | c [Å]  | energy gap [eV] |

|-------|-------|-------|--------|-----------------|

| GGA   | 3.337 | 3.372 | 26.260 | 1.10            |

| HSE   | 3.300 | 3.327 | 25.868 | 3.08            |

| 実験データ | 3.295 |       | 26.071 | 3.15            |

10

## 【0262】

<2-a V<sub>o</sub>のできやすいサイト>V<sub>o</sub>と水素が同時に存在する影響を調べる前に、V<sub>o</sub>と水素それぞれの影響を調べる。

## 【0263】

はじめに、V<sub>o</sub>のできやすいサイトについて調べた。完全結晶から1個の酸素を抜き出すことでV<sub>o</sub>を有するセルを作成し、HSE汎関数を用いて原子の配置の緩和を実施した。酸素リッチ条件で算出したV<sub>o</sub>の形成エネルギーを下表に示す。なお、n<sub>M</sub>は酸素に隣接する金属原子M(=In、Ga、Zn)の配位数を示す。

## 【0264】

【表2】

20

| 酸素サイト            | n <sub>In</sub> | n <sub>Ga</sub> | n <sub>Zn</sub> | Formation energy [eV] | ε(2+/+)[eV] | ε(+/-)[eV] | ε(2/-/0)[eV] |

|------------------|-----------------|-----------------|-----------------|-----------------------|-------------|------------|--------------|

| O <sub>(1)</sub> | 3               | 0               | 1               | 3.87                  | 2.24        | 2.28       | 2.26         |

| O <sub>(2)</sub> | 3               | 1               | 0               | 4.09                  | 2.47        | 2.69       | 2.56         |

| O <sub>(3)</sub> | 0               | 1               | 2               | 3.85                  | 2.42        | 2.17       | 2.29         |

| O <sub>(4)</sub> | 0               | 2               | 1               | 4.27                  | 2.34        | 2.14       | 2.24         |

## 【0265】

酸素サイトO<sub>(1)</sub>におけるV<sub>o</sub>の形成エネルギーは、酸素サイトO<sub>(2)</sub>よりも小さい。酸素サイトO<sub>(1)</sub>および酸素サイトO<sub>(2)</sub>の酸素は4配位であり、ともに3個のInと結合している。残りの1つの結合相手が、酸素サイトO<sub>(1)</sub>ではZnであり、酸素サイトO<sub>(2)</sub>ではGaである。この違いが形成エネルギーの差の主要因と考えるなら、Gaは、Znよりも酸素との結合が強いと推測される。また、酸素サイトO<sub>(3)</sub>におけるV<sub>o</sub>の形成エネルギーは、酸素サイトO<sub>(4)</sub>よりも小さい。酸素サイトO<sub>(3)</sub>は、a-b面方向に結合しているGaの数が酸素サイトO<sub>(4)</sub>よりも少ない。したがって、Ga-O間の結合が強いといえる。以上のことから、V<sub>o</sub>は、Gaとの配位数が少ない酸素サイトO<sub>(1)</sub>または酸素サイトO<sub>(3)</sub>で形成されやすいと考えられる。

## 【0266】

30

また、V<sub>o</sub>の遷移レベルを表2に示す。酸素サイトO<sub>(3)</sub>および酸素サイトO<sub>(4)</sub>では、V<sub>o</sub>の(2+/+)の遷移レベルは(+/-)の遷移レベルよりも伝導帯側に位置している。また、酸素サイトO<sub>(1)</sub>のV<sub>o</sub>の(2+/+)と(+/-)の遷移レベルはほぼ等しい。このことから、フェルミ準位を価電子帯側から伝導帯側へシフトさせると、V<sub>o</sub><sup>+</sup>を経ずにV<sub>o</sub><sup>2+</sup>からV<sub>o</sub><sup>0</sup>へと遷移することが分かる。すなわち、V<sub>o</sub>は、酸化亜鉛で知られる様にnegative-U挙動を示す。さらに、形成エネルギーの小さい酸素サイトO<sub>(1)</sub>と酸素サイトO<sub>(3)</sub>でのV<sub>o</sub>の(2+/0)の遷移レベルは、伝導帯下端(フェルミエネルギーが3.15eV)から約0.8eVと深い位置に存在する。このことから、In-Ga-Zn酸化物中のV<sub>o</sub>は深いドナーであることが示唆される。これは結晶性InGaO<sub>3</sub>(ZnO)<sub>m</sub>(m=3)の結果と一致する。

40

50

## 【0267】

## &lt;2-b 水素の存在形態&gt;

次に水素の存在形態について調べた。In-Ga-Zn酸化物中の水素は、格子間に水素原子または水素分子として存在する場合と、酸素と結合して存在する場合が考えられる。そこで、InO<sub>2</sub>層と(Ga, Zn)O層間の八面体格子間(図8のInt(5))に、水素原子(H<sub>0,ct</sub>)または水素分子((H<sub>2</sub>)<sub>0,ct</sub>)を配置したセルと、c軸と平行なGa-O bondの酸素において、Gaと反対側で酸素原子と結合した水素原子(bonded-H)をもつセルの計3つを用意し、それぞれ原子緩和を、HSE汎関数を用いて行った。

## 【0268】

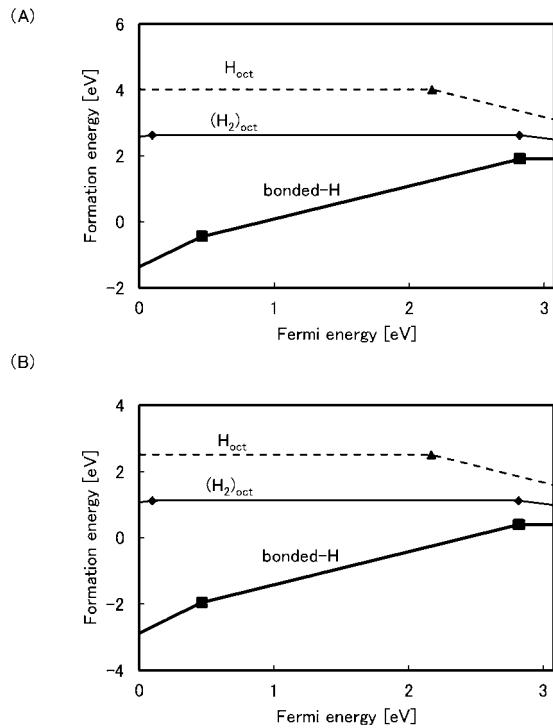

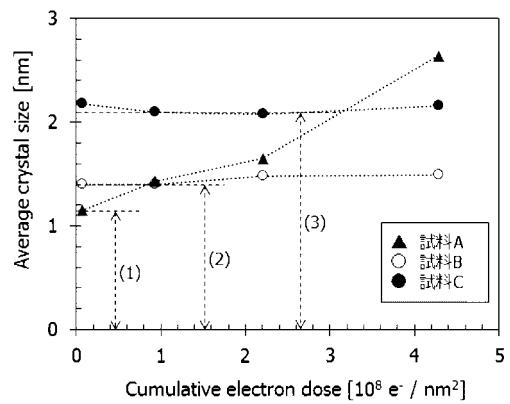

フェルミエネルギーに対する形成エネルギーの変化を図9に示す。図9(A)に、酸素リッチ条件で算出した形成エネルギーを示し、図9(B)に、酸素プア条件で算出した形成エネルギーを示す。ここでは、水素原子1個あたりの形成エネルギーで比較するために、図9中の(H<sub>2</sub>)<sub>0,ct</sub>の形成エネルギーは、半分の値で記載している。また、VBMのエネルギーをフェルミエネルギーが0eVと表記し、CBMのエネルギーをフェルミエネルギーが3.15eVと表記する。また、図9(A)及び図9(B)において、直線の傾きが0の場合、各欠陥が電荷中性の状態を示し、直線の傾きが負の場合、負の電荷を帯びた状態を示し、直線の傾きが正の場合、正の電荷を帯びた状態を示す。

## 【0269】

水素分子(H<sub>2</sub>)<sub>0,ct</sub>は、VBMから2.82eVまでは電荷中性の状態で存在し、2.82eVからCBMまでは、マイナスの電荷を帯びた状態で存在することが分かった。

## 【0270】

また、水素原子H<sub>0,ct</sub>は、VBMから2.17eVまでは、電荷中性の状態で存在し、2.17eVからCBMまでは、マイナスの電荷を帯びた状態で存在する。なお、安定なH<sub>0,ct</sub><sup>+</sup>は確認できなかった。

## 【0271】

そして、酸素原子と結合した水素原子(bonded-H)は、VBMから2.82eVまでは、プラスの電荷を帯びた状態で存在し、2.82eVからCBMまでは、中性状態で存在することが分かった。

## 【0272】

各配置の形成エネルギーを比較した結果、In-Ga-Zn酸化物中の水素は、エネルギーギャップ内の領域全てにおいて、酸素条件に関わらず、酸素原子と結合した水素原子(bonded-H)で安定に存在しやすいことが分かった。

## 【0273】

<2-c V<sub>0</sub>とHが同時に存在する時の安定な構造>

上述した<2-a>、<2-b>では、V<sub>0</sub>と水素の安定性を別々に評価した。V<sub>0</sub>と水素原子が單一セル内に存在する場合、水素原子とV<sub>0</sub>が離れて存在する状態と、V<sub>0</sub>内に水素原子が入り込んだ状態(V<sub>0</sub>H)とが考えられる。そこで、ここではどちらの状態が安定であるかを調べた。

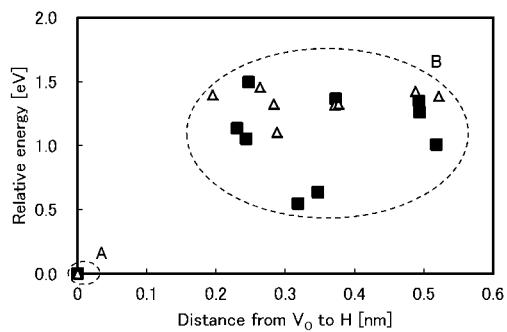

## 【0274】

V<sub>0</sub>が酸素サイトO<sub>(1)</sub>に存在し、かつ、水素原子1個が任意の位置に存在するセルと、V<sub>0</sub>が酸素サイトO<sub>(3)</sub>に存在し、かつ、水素原子1個が任意の位置に存在するセルと、を用意した。それぞれのセルに対して原子緩和を実施した。ここでは、交換相関ポテンシャルにGGAを用いた。V<sub>0</sub>の中心から水素原子までの距離に対する全エネルギーの相対値をプロットしたものを図10に示す。なお、V<sub>0</sub>の中心は、結合した酸素原子が脱離する前に存在した位置である。V<sub>0</sub>内に水素原子が入りこんだ時(V<sub>0</sub>H)を0nmとし、このときをエネルギーの基準とした。図10において、四角印は酸素サイトO<sub>(1)</sub>にV<sub>0</sub>が存在する場合、三角印は酸素サイトO<sub>(3)</sub>にV<sub>0</sub>が存在する場合である。また、破線Aは、水素原子1個をV<sub>0</sub>内に入れたセルにおけるエネルギーの相対値であり、

10

20

30

40

50

破線 B は、水素原子 1 個をさまざまな酸素の近くに配置したセルにおけるエネルギーの相対値である。計算の結果、どちらの酸素サイトでも、破線 B 内よりも破線 A 内のプロットの方のエネルギーが低いため、 $V_O$  と水素原子が離れて存在するよりも  $V_OH$  の方が安定であることが分かった。

【0275】

水素原子と  $V_O$  が離れて存在する状態と、 $V_O$  内に水素原子が入り込んだ状態 ( $V_OH$ )、該 2 つの状態のどちらが安定であるかを、上記 GGA を用いた計算とは異なる方法で調べるために、形成エネルギー ( $E_{form}$ ) から定義される結合エネルギー ( $E_b$ ) を、数式 (4) を用いて計算した。ここでは、交換相関ポテンシャルに HSE 汎関数を用いた。

10

【0276】

【数 4】

$$E_b = E_{form}(V_O) + E_{form}(bonded - H) - E_{form}(V_OH) \quad (4)$$

【0277】

なお、数式 (4) において、 $E_{form}(V_O) + E_{form}(bonded - H)$  は、水素原子と  $V_O$  が離れて存在する状態の形成エネルギーであり、 $E_{form}(V_OH)$  は、 $V_O$  内に水素原子が入り込んだ状態 ( $V_OH$ ) の形成エネルギーである。

20

【0278】

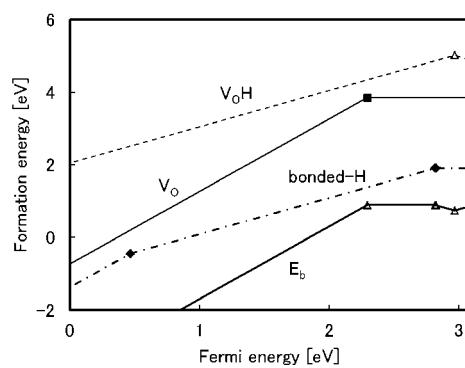

図 11 に、酸素サイト  $O_{(3)}$  に存在する  $V_O$  の形成エネルギー (細実線で示す。)、酸素原子と結合した水素原子 (bonded - H) の形成エネルギー (一点鎖線で示す。)、酸素サイト  $O_{(3)}$  に形成された  $V_OH$  の形成エネルギー (破線で示す。)、および結合エネルギー ( $E_b$ ) (太実線で示す。) を、フェルミエネルギーの関数としてプロットした結果を示す。図 11 (A) 及び図 11 (B) はそれぞれ、酸素リッチ条件、酸素プア条件での計算結果である。

【0279】

数式 (4) より、結合エネルギー  $E_b$  が正の時、 $V_O$  内に水素原子が入り込んだ状態 ( $V_OH$ ) は安定である。図 11 において、フェルミ準位が 1.85 eV 以上のとき、 $E_b$  は正である。キャリア濃度の高い場合を考えると、フェルミ準位は伝導帯下端に近く、フェルミ準位が 1.85 eV 以上である。よって、 $V_O$  内に水素原子が入り込んだ状態 ( $V_OH$ ) は、水素原子と  $V_O$  が離れて存在する状態よりも安定である。

30

【0280】

図 10 より、 $V_O$  と水素原子が存在する場合、 $V_OH$  で存在する方が安定であることが分かった。しかし、 $V_OH$  の水素原子が  $V_O$  内から容易に放出されるようであれば、水素原子は  $V_O$  内にとどまらずに  $In-Ga-Zn$  酸化物中を拡散することになる。そこで、 $V_OH$  の水素原子が  $V_O$  内から抜け出して、 $V_O$  近傍の酸素と結合するまでの水素の拡散過程およびその時の活性障壁を NEMB 法により調査した。ここでは、交換相関ポテンシャルに GGA を用いた。

40

【0281】

ここでは、始状態を、 $V_OH$  を有するセル、終状態を、 $V_O$  および  $V_O$  近傍の酸素原子と結合した水素原子を有するセル (即ち、図 10 の計算において、水素原子と  $V_O$  が離れて存在する状態のセル) とした。そして、経路内の最大エネルギーから始状態または終状態のエネルギーを引くことで、活性障壁を算出した。 $V_O$  内から水素が抜け出す経路およびエネルギー変化を図 12 に示す。酸素サイト  $O_{(1)}$  において、 $V_O$  から水素が抜け出す拡散経路として、経路 A、B を想定した (図 12 (A))。これらの経路について計算したところ、経路 A の方が活性障壁は小さく、この時の活性障壁は 1.52 eV であった。

【0282】

また、酸素サイト  $O_{(3)}$  において、 $V_O$  から水素が抜け出す拡散経路として、経路 C

50

、Dを想定した(図12(B))。これらの経路について計算したところ、経路Cの方が活性障壁は小さく、この時の活性障壁は1.61eVであった。

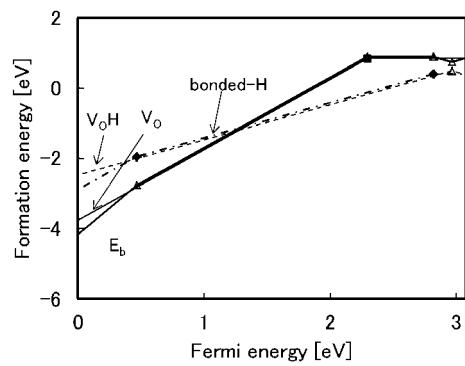

【0283】

$V_o$ から抜け出した後、水素は $V_o$ 内に戻る、または別の酸素に拡散する。水素は、AおよびCの逆方向(それぞれ、A'、C'を示す。)で $V_o$ 内に戻る。水素が、別の酸素に拡散する経路E、Fについて、経路AおよびCの終状態を始状態にセットして、NEB計算を行った。水素の拡散経路およびエネルギー変化を図13に示す。

【0284】

経路A'、C'、E、Fの活性障壁はそれぞれ0.46eV、0.34eV、0.38eV、0.03eVであった。

10

【0285】

次に、上記で得られた活性障壁より、水素拡散の起こる反応頻度 $\Gamma$ を、以下の式(5)より見積もった。

【0286】

【数5】

$$\Gamma = V \exp(-E_a/k_B T) \quad (5)$$

【0287】

ここで、 $V$ は頻度因子、 $E_a$ は活性障壁である。

20

【0288】

を $1.0 \times 10^{13} / \text{sec}$ と仮定した場合、350における $V_o$ 内の水素が抜け出す頻度、 $V_o$ 内に水素が入り込む頻度および別の酸素に拡散する頻度を下表に示す。

【0289】

【表3】

| 酸素サイト              | 水素の拡散経路          | $E_a$ [eV] | $\Gamma$ (350°C) [1/sec] |

|--------------------|------------------|------------|--------------------------|

| 酸素サイト<br>$O_{(1)}$ | $V_o$ 内から抜け出す(A) | 1.52       | $5.52 \times 10^0$       |

|                    | $V_o$ 内に入る(A')   | 0.46       | $1.82 \times 10^9$       |

|                    | 別の酸素に移る(E)       | 0.38       | $8.30 \times 10^9$       |

| 酸素サイト<br>$O_{(3)}$ | $V_o$ 内から抜け出す(C) | 1.61       | $8.77 \times 10^{-1}$    |

|                    | $V_o$ 内に入る(C')   | 0.34       | $1.89 \times 10^{10}$    |

|                    | 別の酸素に移る(F)       | 0.03       | $5.64 \times 10^{12}$    |

30

【0290】

酸素サイト $O_{(1)}$ および $O_{(3)}$ では、水素は高い頻度で $V_o$ 内に入るが、350において $V_o$ 内から水素は放出されにくいことがわかった。したがって、 $V_o$ Hは安定に存在することがわかった。

40

【0291】

即ち、 $V_o$ を有する領域は、水素を捕獲し、放出しないことがわかる。よって、 $V_o$ を有する領域を、水素をブロックする領域、またはゲッタリングする領域と呼ぶことができる。例えば、領域126bおよび領域126cが $V_o$ を有する状態で加熱処理などを行うと、領域126a中の水素が領域126bおよび領域126cにゲッタリングされる。また、領域126bおよび領域126cによって、領域126aに水素が近づきにくくなる

50

。その結果、領域 126a のキャリア密度を、 $1 \times 10^9$  個 /  $\text{cm}^3$  未満、好ましくは $1 \times 10^7$  個 /  $\text{cm}^3$  未満とすることができる場合がある。

#### 【0292】

##### < 2 - d $V_o$ H の遷移レベル >