(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第4954413号

(P4954413)

(45) 発行日 平成24年6月13日(2012.6.13)

(24) 登録日 平成24年3月23日(2012.3.23)

(51) Int.Cl.

H01L 27/04 (2006.01)

H01L 21/822 (2006.01)

F 1

H01L 27/04

H01L 27/04

H01L 27/04H

C

D

請求項の数 16 (全 13 頁)

(21) 出願番号 特願2001-547425 (P2001-547425)

(86) (22) 出願日 平成12年11月13日 (2000.11.13)

(65) 公表番号 特表2004-501501 (P2004-501501A)

(43) 公表日 平成16年1月15日 (2004.1.15)

(86) 國際出願番号 PCT/US2000/031352

(87) 國際公開番号 WO2001/046989

(87) 國際公開日 平成13年6月28日 (2001.6.28)

審査請求日 平成19年11月13日 (2007.11.13)

(31) 優先権主張番号 09/469,406

(32) 優先日 平成11年12月22日 (1999.12.22)

(33) 優先権主張国 米国(US)

(73) 特許権者 591003943

インテル・コーポレーション

アメリカ合衆国 95052 カリフォルニア州・サンタクララ・ミッション・カレッジ ブーレバード・2200

(74) 代理人 100064621

弁理士 山川 政樹

(72) 発明者 ケシャヴァルジ, アリ

アメリカ合衆国・97229・オレゴン州

・ポートランド・ノースウェスト・パークウェイ・ストリート・2341

(72) 発明者 デ, ヴィヴェック・ケイ

アメリカ合衆国・97007・オレゴン州

・ビバートン・サウスウェスト・151エスティ・アベニュー・9785

最終頁に続く

(54) 【発明の名称】薄いゲート酸化膜用デカップリング・キャパシタ

## (57) 【特許請求の範囲】

## 【請求項 1】

電源電圧を伝える第1導体と、

接地電圧を伝える第2導体と、そして

第1導体と第2導体の間でデカップリング・キャパシタンスを備えるための半導体デカップリング・キャパシタであって、空乏モードで動作するように構成された半導体デカップリング・キャパシタと

から構成されるダイにおいて、

前記半導体デカップリング・キャパシタは、

(a) 電源電圧を受けるための前記第1導体に接続されたゲート電極と、

(b) 接地電圧を受けるための前記第2導体に接続された拡散領域と、そして

(c) 前記拡散領域を通じて前記接地電圧を受け、これによって前記半導体デカップリング・キャパシタは前記空乏モードになる、ボーダーと

から成り、

前記拡散領域は第1拡散領域であり、前記半導体デカップリング・キャパシタはさらに前記接地電圧を受けるための前記第2導体に接続された第2拡散領域を有し、

前記ボーダーは前記第1および第2拡散領域を通じて前記接地電圧を受け、そして

前記半導体デカップリング・キャパシタはフラットバンド電圧を有し、かつ前記電源電圧が前記フラットバンド電圧より小さい絶対値を有する

ことを特徴とするダイ。

10

20

**【請求項 2】**

前記ゲート電極は p - t y p e であり、前記拡散領域および前記ボデーは n - t y p e であることを特徴とする請求項 1 に記載のダイ。

**【請求項 3】**

前記ゲート電極は p - t y p e であり、前記拡散領域および前記ボデーは n - t y p e であり、前記拡散領域は前記ボデーよりも高濃度でドープされていることを特徴とする請求項 1 に記載のダイ。

**【請求項 4】**

前記第 1 と第 2 の拡散領域は、ソース拡散 / ドレイン拡散領域であることを特徴とする請求項 1 に記載のダイ。 10

**【請求項 5】**

前記第 1 と第 2 の拡散領域は前記ボデーよりも高濃度でドープされていることを特徴とする請求項 1 に記載のダイ。

**【請求項 6】**

前記ゲート電極は p - t y p e で、前記拡散領域および前記ボデーは n - t y p e であり、前記拡散領域はボデー・タップ拡散であり、前記半導体デカップリング・キャパシタはさらに第 1 と第 2 の p - t y p e のソース拡散 / ドレイン拡散領域を有することを特徴とする請求項 1 に記載のダイ。

**【請求項 7】**

前記第 1 と第 2 のソース拡散 / ドレイン拡散領域は、接地電圧を受けるために前記第 2 導体に接続されていることを特徴とする請求項 6 に記載のダイ。 20

**【請求項 8】**

前記ボデー・タップ拡散領域および第 1 と第 2 のソース拡散 / ドレイン拡散領域は、前記ボデーより高濃度でドープされていることを特徴とする請求項 6 に記載のダイ。

**【請求項 9】**

電源電圧を伝える第 1 導体と、

接地電圧を伝える第 2 導体と、そして

第 1 導体と第 2 導体の間にデカップリング・キャパシタンスを備えるための半導体デカップリング・キャパシタであって、空乏モードで動作するように構成された半導体デカップリング・キャパシタと 30

から構成されるダイであって、

前記半導体デカップリング・キャパシタは、

( a ) 接地電圧を受けるための前記第 2 導体に接続されたゲート電極と、

( b ) 電源電圧を受けるための前記第 1 導体に接続された拡散領域と、

( c ) 前記拡散領域を通じて前記電源電圧を受け、これによって前記半導体デカップリング・キャパシタは前記空乏モードになる、ボデーと、

( d ) 基板と、そして

( e ) 前記基板と前記ボデーの間にある絶縁体と

から構成され、

前記拡散領域は第 1 拡散領域であり、前記半導体デカップリング・キャパシタはさらに前記電源電圧を受けるための前記第 1 導体に接続された第 2 拡散領域を有し、 40

前記ボデーは前記第 1 および第 2 拡散領域を通じて前記電源電圧を受け、そして

前記半導体デカップリング・キャパシタはフラットバンド電圧を有し、かつ前記電源電圧が前記フラットバンド電圧より小さい絶対値を有することを特徴とするダイ。

**【請求項 10】**

前記ゲート電極は n - t y p e であり、前記拡散領域および前記ボデーは p - t y p e であることを特徴とする請求項 9 に記載のダイ。

**【請求項 11】**

前記ゲート電極は n - t y p e であり、前記拡散領域および前記ボデーは p - t y p e 50

であり、前記拡散領域が前記ボデーよりも高濃度でドープされていることを特徴とする請求項9に記載のダイ。

【請求項12】

前記第1と第2の拡散領域は、ソース拡散／ドレイン拡散領域であることを特徴とする請求項9に記載のダイ。

【請求項13】

前記第1と第2の拡散は前記ボデーよりも高濃度でドープされていることを特徴とする請求項9に記載のダイ。

【請求項14】

前記ゲート電極はn-typ eで、前記拡散領域および前記ボデーはp-typ eであり、前記拡散領域はボデー・タップ拡散領域であり、前記半導体デカップリング・キャパシタはさらに第1と第2のn-typ eのソース拡散／ドレイン拡散領域を有することを特徴とする請求項9に記載のダイ。 10

【請求項15】

前記第1と第2のソース拡散／ドレイン拡散領域は前記接地電圧を受けるため前記第2導体に接続されていることを特徴とする請求項14に記載のダイ。

【請求項16】

前記ボデー・タップ拡散領域および第1と第2のソース拡散／ドレイン拡散領域は、前記ボデーより高濃度でドープされていることを特徴とする請求項14に記載のダイ。 20

【発明の詳細な説明】

【0001】

(発明の背景)

(発明の技術分野)

本発明は集積回路に関し、より具体的には、集積回路のデカップリング・キャパシタに関する。

【0002】

(背景技術)

デカップリング・キャパシタ(「デキップ」)は、雑音の遮断のために集積回路(I C)に使用されている。実際、これらは、ほぼすべてのI Cに多用されている。半導体キャパシタの一つのタイプは、MOS-Cまたは金属酸化膜半導体キャパシタと呼ばれる。MOS-Cは、(ゲート酸化膜など少なくとも絶縁体を含む)誘電体領域によって分離された2個の端子を有する。端子の1つはゲートであり、他の1つはボデー(およびおそらくソース拡散およびドレイン拡散)である。半導体キャパシタのもう一つのタイプは、n-チャネル金属酸化膜半導体FET(NMOSFET)またはp-チャネル金属酸化膜半導体FET(NMOSFET)などの電界効果トランジスタ(FET)を使用している。端子の一つはゲートであり、他の端子はソース、ドレイン、およびボデーである。端子は、(ゲート酸化膜など少なくとも絶縁体を含む)誘電体によって分離されている。MOS-CとFETキャパシタの違いは、FETでは、ソースおよびドレインがボデーと異なる極性タイプを有することである。MOS-Cでは、ソース拡散／ドレイン拡散(存在する場合)は、ボデーと同じ極性を有する。集積回路でのキャパシタの挙動は、R. Pierr e t等「Field Effect Devices」(Addison-Wesley、第2版、1990年)47~59頁、およびN. Weste等「Principles of CMOS VLSI Design」(Addison-Wesley、第2版、1993年)180~82頁に記載されている。 30 40

【0003】

高誘電率絶縁体によって2本の金属線を間に挟んだキャパシタなど、その他のデカップリング・キャパシタも可能である。しかし、今日のMOS技術での材料の課題および集積は非常に難しい。

【0004】

キャパシタのキャパシタンスCは、式 $C = \epsilon A / d$ によって与えられ、但し $\epsilon$ は誘電率、

Aは面積、dは距離である。I Cの設計では、部品の寸法を小さくすることが望ましい。したがって、数年来、キャパシタの面積Aは縮小しており、一方、電極間の距離dもまた短縮された。現在使用されているキャパシタ構造は、漏洩のない酸化膜を用いることによって概して動作は良好である。現在のデカップリング・キャパシタ構造は、MOS-Cを反転に保つように電圧を印加することによって、単位面積あたり最大のキャパシタンス値と、良好な高周波応答時間と、低い直列抵抗とを得る。プロセス技術のスケーリングに伴って、トランジスタの良好な駆動電流能力および良好な短チャネル効果を維持するために、ゲート酸化膜の厚みもスケーリングさせる。ゲート酸化膜がスケーリングを続けると（例えば、30Å未満へ）、このキャパシタ構造は酸化膜を通して著しい漏洩伝導を引き起こすことになる（例えば、高いトンネル漏洩）。

10

#### 【0005】

##### (概要)

いくつかの実施態様では、本発明は、電源電圧を伝える第1導体および接地電圧を伝える第2導体を有するダイを含む。空乏モードで動作する半導体キャパシタが第1導体と第2導体の間にデカップリング・キャパシタンスを形成するために第1導体と第2導体の間に結合される。この半導体キャパシタはゲート電圧を有する。

#### 【0006】

n-ボーデー内のn+ゲート・ポリおよびn+ソース／ドレイン領域；n-ボーデー内のp+ゲート・ポリおよびn+ソース／ドレイン領域；n-ボーデー内のp+ゲート・ポリおよびp+ソース／ドレイン領域；p-ボーデー内のp+ゲート・ポリおよびp+ソース／ドレイン領域；p-ボーデー内のn+ゲート・ポリおよびp+ソース／ドレイン領域；p-ボーデー内のn+ゲート・ポリおよびn+ソース／ドレイン領域を含めた様々な構造を用いることができる。電源電圧は、フラットバンド電圧より大きな絶対値を有することができる。

20

#### 【0007】

さらなる実施形態を説明し特許を請求する。

#### 【0008】

本発明は、下記の詳細な説明から、および本発明の実施形態に付随する図面から、さらに完全に理解されるであろう。しかし、これらは、説明した特定の実施形態に本発明を限定するものではなく単に説明および理解のためである。

#### 【0009】

30

##### (詳細な説明)

本発明は、半導体キャパシタ（トランジスタまたはMOS-C）を空乏モードで動作させて、絶縁体（例えば、ゲート酸化膜）中の漏洩を低減させることに係る。空乏モードでの動作は面積あたりのキャパシタンスを低下させるので、これは直観に反するものである。キャパシタンスのこの低下を補うために、面積を拡大することができるが、それは望ましくない。本発明を生み出す際に、本発明者らは、空乏モードで動作させることによってキャリアの数が低減し、したがってゲート酸化膜内のトンネリングの量が低減し、漏洩も低減することに気が付いた。

#### 【0010】

一般的な考え方では、反転モードで動作するMOSトランジスタ構造に由来するMOS-Cキャパシタを使用しない方向である。代替案は、空乏モードで動作する絶縁体として、ゲート酸化膜を用いたキャパシタ構造の使用である。有効キャパシタンスは約25%（概算値）低下するが、一方、約1Vの電源技術について漏洩はほぼ100分の1に低減する。キャパシタは空乏モードでバイアスするので（蓄積領域近くへ）、キャパシタンスの低下はC-V曲線で観察できる。漏洩の低減は、ゲート酸化膜下の空乏チャネルには薄いゲート酸化膜を通り抜けるキャリアが少ないという事実による。こうしたキャパシタのQファクタは、反転のMOSトランジスタ・キャップに類似しているであろう。少数キャリアの発生および再結合に依存しないで、デキャップにかさねるAC信号に応答する必要のあるキャリアを供給する場合は特にそうである。デキャップを通しての漏洩を一桁より大きく低減させる必要がある場合は、やや大きな面積のキャパシタを使用することによって、

40

50

低下したキャパシタンスをいつでも補うことができる。

#### 【0011】

n - ボデーを有するデカップリング・キャパシタ

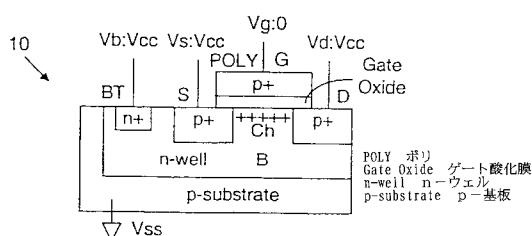

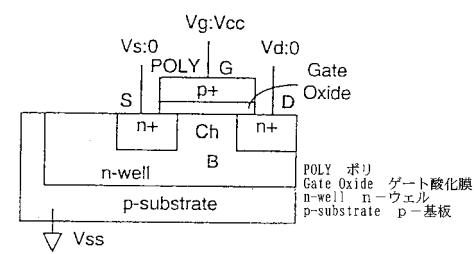

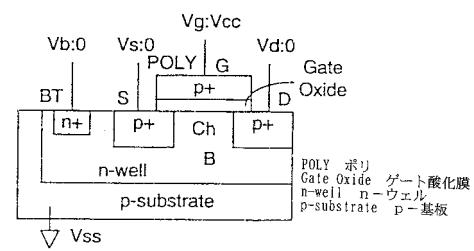

図1を参照すると、従来技術のPMOSトランジスタ・キャパシタ10は、p - 基板、n - ウェル、p + ソースS、p + ドレインD、p + ポリシリコン・ゲート電極(ポリ)G、およびボデーBのn + ボデー・タップBTを含む。本開示の専門用語によれば、トランジスタ・キャパシタ10は、n - ボデー(n - ウェル)上p + / p + キャップと呼ばれる。但し、第1のp + はポリ・タイプの意味であり、第2のp + はS / D領域のタイプを意味する。なお、キャパシタ構造の場合、1つの拡散領域をソース、他方をドレインと呼ぶことは特に意味のあることではないが、学術用語の便宜上そうしている。なお、ソース拡散/ドレイン拡散は、本発明のすべての実施形態で必要というわけではないが、しかし、これは直列抵抗を低下させてRC周波数応答に役立つこともある。ゲート酸化膜の直下が表面12である。ゲート酸化膜の表面の下がチャネルChである。本開示では、トランジスタではないMOC-C構造の場合でも、この領域をチャネルと呼ぶ。トランジスタ・キャパシタ10には以下のように電圧を印加する。ボデー電圧Vbは電源電圧Vcc(ある場合はVddと呼ぶ)であり、ソース電圧およびドレイン電圧VsおよびVdはどちらもVccであり、ゲート電圧VGとp - 基板はどちらも接地されている(Vssまたは0と呼ぶ)。基板は、下、上、またはその他から接地することができる。図1では、VgはVsに接続されている。しかし、いくつかの実施形態では、GはVssに接続されず、非ゼロおよび非Vcc値の可能性がある。

10

20

#### 【0012】

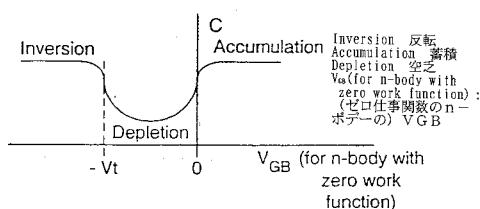

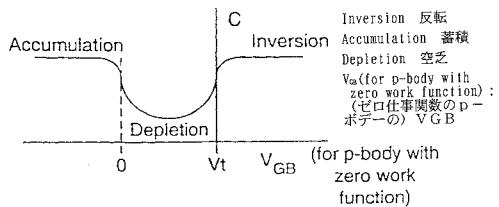

図2は、ポリとボデーが同じタイプを有するためにゼロ仕事関数のn - ボデー(例えば、n - ウェル)キャパシタ構造の、キャパシタンス対ゲート・ツー・ボデー電圧VG\_B曲線を示す。なお、ドレイン電圧とソース電圧は、ボデー電圧と同じでもよい。この曲線は、一般的な関係を示すことだけを意図しており、正確な値または形を示すものではない。実際の曲線は少し違って見えることがある。さらに、曲線の形は、異なる周波数で変化する可能性がある。明らかなように、キャパシタンスは、蓄積と反転で高く、空乏で低い。Vtがしきい値電圧である。一般に、蓄積モード、空乏モード、反転モードの境界は厳密ではないかもしれないが、蓄積モードは $0 < V_{G_B}$ の場合に起こり、空乏モードは $-V_t < V_{G_B} < 0$ の場合に起こり、反転モードは $V_{G_B} < -V_t$ の場合に起こる。

30

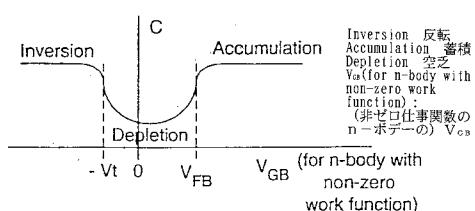

#### 【0013】

図3は、ポリとボデーが異なるタイプを有するために非ゼロ仕事関数(非ゼロ・フラット・バンド電圧VF\_B)のn - ボデーキャパシタ構造の、キャパシタンス対ゲート・ツー・ボデー電圧VG\_B曲線を示す。この曲線は、一般的な関係を示すことだけを意図しており、正確な値または形を示すものではない。実際の曲線は少し違って見えることがある。さらに、曲線の形は、異なる周波数で変化する可能性がある。明らかなように、キャパシタンスは、蓄積および反転で高く、空乏で低い。高濃度でドープされたポリのVF\_Bは約1.0ボルトである。一般に、蓄積モード、空乏モード、反転モードの境界は厳密ではないかもしれないが、蓄積モードは $V_{F_B} < V_{G_B}$ の場合に起こり、空乏モードは $-V_t < V_{G_B} < V_{F_B}$ の場合に起こり、反転モードは $V_{G_B} < -V_t$ の場合に起こる。なお、-Vtと0の間、0とVF\_Bの間、0とVtの間の相対的距離は、VB\_GまたはVtの実際の値を制約するものではなく、これらは実施形態ごとに異なる可能性がある。

40

#### 【0014】

図1の従来技術トランジスタ・キャパシタ10の場合について考えると、n - ボデーがあり、ポリおよびボデーが異なるタイプを有し、したがって非ゼロ仕事関数があるので、図3の曲線が当てはまる。この構造のフラットバンド電圧(VFB)は約1Vである。図1の場合には、 $V_{G_B} = -V_{cc}$ であり、これは $-V_t$ よりもさらに負である。したがって、トランジスタ・キャパシタ10は、反転モードである(より具体的には、チャネルがボデーの反対タイプであるホールを含むので、このチャネルは反転である)。したがって、これは、単位面積あたりキャパシタンスが非常に高く(おそらく最大)、周波数応答が非

50

常に良好で、直列抵抗が低い。しかし、これには、ゲート酸化膜を通る漏洩も見られ、特に薄いゲート酸化膜では高い（おそらく最大）。 $V_{CC}$ は、このデキップ構造では $V_t$ より高くするべきである。なお、（変位電流に対する）このキャップの、周波数および直列抵抗の関数としてのキャパシタンスが、このデキップのQファクタを表す。なお、 $p$ +ポリ・ゲートおよびn-ボーダーなので、反転のPMOSキャップのフラットバンド電圧( $V_{FB}$ )は約1V(非ゼロ)である。

#### 【0015】

図4は、本発明のいくつかの実施形態によるMOS-C40を示す。なお、用語MOS(金属酸化膜半導体)は広い解釈を意図している。すなわち、金属がどんな特別のタイプの導体にも限定されず(すなわち、ポリシリコンである必要はなく)、絶縁体が酸化膜である必要はなく、半導体部分は特別のタイプの構造に限定されない。MOS-C40は、上記の命名法によればn-ボーダー上n+/n+と示される(すなわち、ポリがn+、S/Dがn+である)。 $V_g$ は $V_{CC}$ であり、S/D/Bは0(Vss)である。n-ウェルが用いられ、ポリとボーダーが同じタイプを有するので、図2の曲線が当てはまる。MOS-C40の $V_{FB}$ は0Vである。 $V_{GB} = V_{CC}$ であり、したがってMOS-C40は蓄積モードにある(チャネルには、ボーダーと同じタイプの電子が蓄積される)。図4の構造では、デザイン・ツールでこうしたレイアウト(n-ウェル上にn-ポリを描く)にすることが望ましいかもしれない。MOS-C40はすべての $V_{CC}$ 値で動作する。これは、単位面積あたりのキャパシタンスが高く(良好)、漏洩はやや低い。これは、周波数応答が良好で、直列抵抗が低い。

10

20

#### 【0016】

図5は、本発明のいくつかの実施形態によるMOS-C50を示す。MOS-C50は、上記の命名法によればn-ボーダー上p+/n+と示される。 $V_g$ は $V_{CC}$ であり、S/D/Bは0(Vss)である。n-ウェルが用いられ、ポリとボーダーが異なるタイプを有するので、図3の曲線が当てはまる。MOS-C50の $V_{FB}$ は約1Vである。 $V_{GB} = V_{CC}$ である。 $V_{CC} > V_{FB}$ の場合は、MOS-C50は蓄積モードにあり(チャネル蓄積)、 $MOS-C < V_{FB}$ の場合は、MOS-C50は空乏モードにある(チャネル空乏)。 $V_{CC} = V_{FB}$ の場合は、モードは蓄積モードと空乏モードの間である。本発明のいくつかの実施形態では、 $V_{CC}$ は $V_{FB}$ より小さく、したがってMOS-C50は空乏モードにあり、漏洩は低減するであろう。この構造は特別のレイアウトを必要とするかもしれない。MOS-C50は、単位面積あたりのキャパシタンスが低いが、空乏モードのため(漏れるキャリアが少ない)漏洩は著しく低い。これは、周波数応答は良好であるが、直列抵抗が高い可能性がある。なお、この構造は埋め込みチャネルMOSトランジスタ構造に似ている。

30

30

#### 【0017】

図6は、本発明のいくつかの実施形態によるPMOSトランジスタ・キャパシタ60MOS-C60を示す。トランジスタ・キャパシタ60は、上記の命名法によればn-ボーダー上p+/p+と示される。 $V_g$ は $V_{CC}$ であり、S/D/Bは0(Vss)である(図1の反対)。n-ウェルが用いられ、ポリとボーダーが異なるタイプを有するので、図3の曲線が当てはまる。MOS-C50の $V_{FB}$ は約1Vである。 $V_{GB} = V_{CC}$ である。 $V_{CC} > V_{FB}$ の場合は、MOS-C60は蓄積モードにあり(チャネル蓄積)、MOS-C< $V_{FB}$ の場合は、MOS-C60は空乏モードにある(チャネル空乏)。本発明のいくつかの実施形態では、 $V_{CC}$ は $V_{FB}$ より小さく、したがってMOS-C60は空乏モードにあり、漏洩は低減するであろう。MOS-C60は、単位面積あたりのキャパシタンスが低減しているが、空乏モードのため(漏れるキャリアが少ない)漏洩は著しく低減している。しかし、周波数応答および直列抵抗が問題かもしれない。

40

#### 【0018】

p-ポリを有するデカップリング・キャパシタ

p-ボーダー(p-ウェルまたはp-基板)を有するトランジスタおよびMOS-Cキャパシタの構造の例を以下に説明する。なお、p-ウェルが示されているが、ボーダーはp-基

50

板だけのこともある。さらに、基板は、p - ウェルを有するn - タイプもありうる。

#### 【0019】

図7は、ポリとボデーが同じタイプを有するためにゼロ仕事関数を有するp - ボデー・キャパシタ構造の、キャパシタンス対ゲート・ツー・ボデー電圧 $V_{G_B}$ 曲線を示す。この曲線は、一般的な関係を示すことのみを意図しており、正確な値または形を示すものではない。実際の曲線は少し違って見えることがある。さらに、曲線の形は、異なる周波数で変化する可能性がある。明らかなように、キャパシタンスは、蓄積および反転で高く、空乏で低い。一般に、蓄積モード、空乏モード、反転モードの境界は厳密ではないかもしれないが、蓄積モードは $V_{G_B} < 0$ の場合に起こり、空乏モードは $0 < V_{G_B} < V_t$ の場合に起こり、反転モードは $V_{G_B} > V_t$ の場合に起こる。

10

#### 【0020】

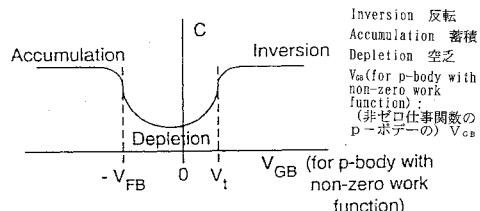

図8は、ポリとボデーが異なるタイプを有するために非ゼロ仕事関数（非ゼロ・フラット・バンド電圧 $V_{F_B}$ ）のp - ボデー・キャパシタ構造の、キャパシタンス対ゲート・ツー・ボデー電圧 $V_{G_B}$ 曲線を示す。この曲線は、一般的な関係を示すことのみを意図しており、正確な値または形を示すものではない。実際の曲線は少し違って見えることがある。さらに、曲線の形は、異なる周波数で変化する可能性がある。明らかなように、キャパシタンスは、蓄積および反転で高く、空乏で低い。高濃度でドープされたポリの $V_{F_B}$ は、約1.0ボルトである（これは、曲線の負領域にある）。一般に、蓄積モード、空乏モード、反転モードの境界は厳密ではないかもしれないが、蓄積モードは $V_{G_B} < -V_{F_B}$ （例えば、-1V）の場合に起こり、空乏モードは $-V_{F_B} < V_{G_B} < V_t$ の場合に起こり、反転モードは $V_t < V_{G_B}$ の場合に起こる。なお、- $V_{F_B}$ と0の間、および0と $V_t$ の間の相対的距離は、 $V_{F_B}$ または $V_t$ の実際の値を制約するものではなく、これらは実施形態ごとに異なる可能性がある。

20

#### 【0021】

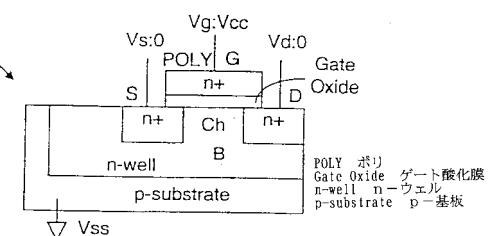

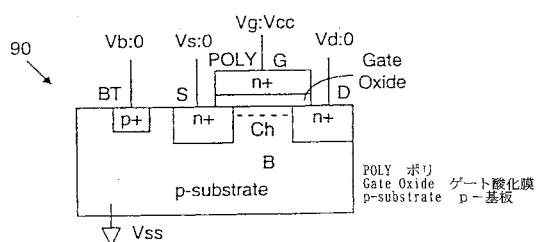

図9は、従来技術のN M O Sトランジスタ・キャパシタ90を示し、上記の命名法によれば、p - ボデー上n+/n+で示される。この場合、これはp - ボデーすなわちp - 基板であるが、n - 基板上のp - ウェルまたはp - 基板内のp - ウェルでもよい。 $V_g = V_c$ であり、S/D/Bは0(Vss)である。ポリとボデーが異なるタイプを有するので、図8の曲線が用いられる。 $V_{G_B} = V_{c c}$ である。曲線8で、 $V_{c c}$ は $V_t$ より大きく、したがって、トランジスタ・キャパシタ90は反転モード（チャネルが反転）で動作している。デキップ90は、トリプル・ウェル・プロセスを必要とせず、特別のレイアウト要求を用いない。これは、単位面積あたりのキャパシタンスが非常に高く（多分最大）、周波数応答が非常に良好で、直列抵抗が低い。主な問題は、ゲート酸化膜、特に薄いゲート酸化膜からの漏洩もまた多い（多分最大）ことである。このデキップ構造については、 $V_{c c}$ は $V_t$ より大きくするべきである。

30

#### 【0022】

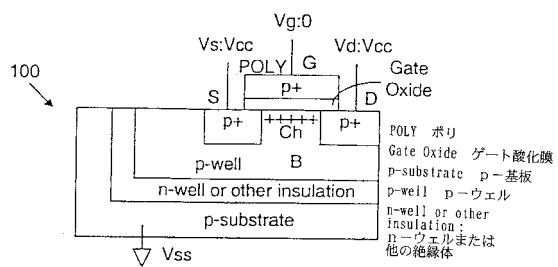

図10は、上記命名法によればp - ボデー上p+/p+を有するM O S - Cキャパシタ100を示す。p - ウェルが示されているが、これは必要ではない。 $V_g = 0$ (Vss)であり、S/D/B =  $V_{c c}$ である。ポリとボデーが同じタイプなので、図7の曲線が当てはまる。 $V_{G_B} = -V_{c c}$ であり、したがって、キャパシタ100は蓄積モードにある（チャネルに蓄積される）。いくつかの実施形態では、キャパシタ100は、p - ウェルとp - 基板の間にn - ボデーまたは他の絶縁体を含む。目的は、 $V_{c c}$ 電圧が基板または他のボデーの電圧に与える影響を防止することである。このトリプル・ウェル・プロセスは、デザイン・ツールに追加のレイアウト（P - ウェル上にP - ポリを描く）を必要とするかもしれない。デキップ100はすべての $V_{c c}$ 値で動作する。これは、単位面積あたりのキャパシタンスが高く（良好）、漏洩はやや少ない。これは、周波数応答が良好で、直列抵抗が低い。

40

#### 【0023】

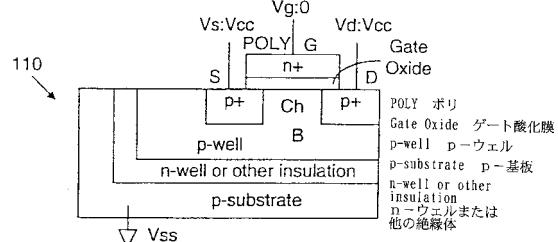

図11は、上記命名法によればp - ボデー上n+/p+を有するM O S - Cキャパシタ110を示す。p - ウェルが示されているがこれは必要ではない。 $V_g = 0$ (Vss)であ

50

り、 $S / D / B = V_{CC}$  である。ポリとボーデーが異なるタイプなので、図 8 の曲線が当てはまる。 $V_{GB} = -V_{CC}$  である。 $V_{CC} > V_{FB}$  ( $-V_{CC} < -V_{FB}$ ) の場合は、キャパシタ 110 は蓄積モードにある(チャネルに蓄積される)。 $V_{CC} < V_{FB}$  ( $-V_{CC} > -V_{FB}$ ) の場合は、キャパシタ 110 は空乏モードにある(チャネルは空乏である)。いくつかの実施形態では、漏洩の役に立つように空乏モードを用いる。いくつかの実施形態では、キャパシタ 110 は、p - ウェルと p - 基板の間に n - ボーデーまたは他の絶縁体を含む。キャパシタ 110 は、単位面積あたりのキャパシタンスが低く、かつ漏洩が著しく低い。これは、周波数応答は良好であるが、直列抵抗が高い。

#### 【0024】

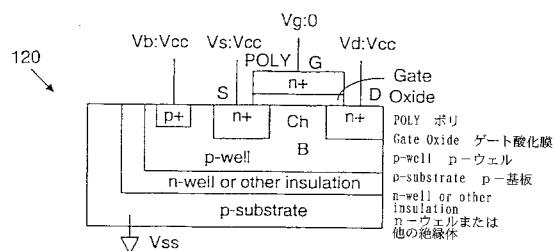

図 12 は、上記命名法によれば p - ボーデー上  $n+/n+$  を有する NMOS ドランジスタ 120 を示す。p - ウェルが示されているがこれは必要ではない。 $V_g = 0$  ( $V_{SS}$ ) であり、 $S / D / B = V_{CC}$  である。ポリとボーデーが異なるタイプなので、図 8 の曲線が当てはまる。 $V_{GB} = -V_{CC}$  である。 $V_{CC} > V_{FB}$  ( $-V_{CC} < -V_{FB}$ ) の場合は、キャパシタ 120 は蓄積モードにある(チャネルに蓄積される)。 $V_{CC} < V_{FB}$  ( $-V_{CC} > -V_{FB}$ ) の場合は、キャパシタ 120 は空乏モードにある(チャネルは空乏である)。いくつかの実施形態では、漏洩の役に立つように空乏モードを用いる。いくつかの実施形態では、キャパシタ 120 は、p - ウェルと p - 基板の間に n - ボーデーまたは他の絶縁体を含む。この構造では漏洩は良好である(低減)。しかし、周波数応答および直列抵抗が問題になるかもしれない。この構造は、トリプル・ウェル・プロセスを必要とするかもしれない。

10

#### 【0025】

下記の付録は、上記のキャパシタ、および本発明のいくつかの実施形態の範囲内の他のキャパシタの比較一覧表を提供する。

#### 【0026】

他の情報および実施形態

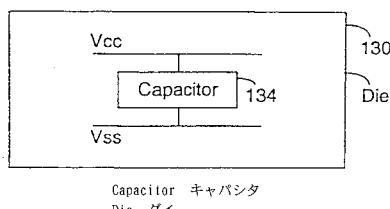

図 13 は、本明細書記載の 1 つまたは複数の構造を含めたキャパシタ(例えば、キャパシタ 134)が含まれるダイ 130 を示す。ダイ 130 は、マイクロプロセッサ、DSP(デジタル信号プロセッサ)、エンベディド・コントローラ、ASIC(特定用途向け集積回路)、およびコミュニケーション・チップを含めて、任意の様々なタイプの電気デバイスとすることができます。

30

#### 【0027】

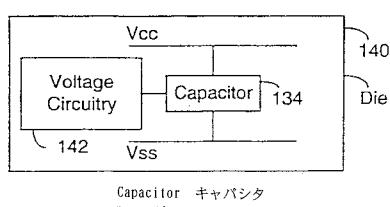

上記のように、いくつかの実施形態では、キャパシタを空乏モードとすることが望ましい。多くの状況では、キャパシタを蓄積モードまたは反転モードに接近させることも望ましいであろう。なお、図 2、3、7、8 において、空乏モードでは、蓄積モードまたは反転モードに向かって曲線は上向きである。ゲート電圧、ボーデー電圧、ソース/ドレイン電圧、しきい値電圧、および/またはドーピング濃度を調節することによって、キャパシタンスを微調整することが可能である。図 14 を参照すると、ダイ 140 は、(その中に記載された 1 つまたは複数の様々なキャパシタを表す)キャパシタ 134 を含む。ダイ 140 は電圧回路 142 を含み、これが、1 つまたは複数のボーデー、ゲート、およびソース/ドレインに電圧を供給して、所望のキャパシタンス・レベルを実現することができる。ボーデー電圧を変化させて、キャパシタに順方向または逆方向ボーデー・バイアスを持たせることができる。なお、ボーデー・バイアスが変化すると  $V_t$  が変化する。所望のキャパシタンス・レベルを得るために、フィードバック機構があつてもよい。

40

#### 【0028】

単に一例としてであるが、いくつかの実施形態では、有効キャパシタンスを約 25% 低下させることができるが、一方約 1V の電源技術について、漏洩はほぼ 100 分の 1 に低減すると思われる。キャパシタは空乏モードでバイアスするので(蓄積領域近くへ)、キャパシタンスの低下は C - V 曲線で観察できる。漏洩の低減は、ゲート酸化膜下の空乏チャネルには薄いゲート酸化膜を通り抜けるキャリアが少ないためである。こうしたキャパシタの Q ファクタは、反転の MOS ドランジスタ・キャップに類似しているであろう。少数

50

キャリアの発生および再結合に依存しないで、デキップにかさねる A C 信号に応答する必要のあるキャリアを供給する場合は特にそうである。デキップを通しての漏洩を一桁より大きく低減させる必要がある場合は、やや大きな面積のキャパシタを使用することによって、低下したキャパシタンスを補うことができる。したがって、本発明は、さらなる供給電圧のスケーリング、ならびに低電圧、高性能、および低電力 C M O S 回路用のプロセス技術の開発を支持するものである。将来、ゲート酸化膜の厚みを、既にスケーリングされたトランジスタの要求に合わせてスケーリングしても、雑音遮蔽用のデキップを、本発明者らが提案する構造を有する本発明者らの I C に継続して利用することができる。本発明者らが提案した解決法は、現在の加工技術と適合するものである。

## 【 0 0 2 9 】

10

本発明は、S O I (シリコン・オン・インシュレータ) 構造と接続して使用することができる。

## 【 0 0 3 0 】

さらに、周知のように、電源電圧および接地電圧は必ずしも一定ではなく、雑音、負荷、または他の理由で変動がある。

## 【 0 0 3 1 】

M O S F E T 以外のF E Tも使用できる。図示した実施形態はエンハンスマント・モード・トランジスタを含むが、当分野の技術者なら本開示の恩恵があれば明白な回路の改造を行うことによって、空乏モード・トランジスタも使用することができる。

## 【 0 0 3 2 】

20

本明細書で「実施形態」、「一実施形態」、「いくつかの実施形態」、または「他の実施形態」と言及した場合は、実施形態に関して説明された特定の特徴、構造、または特性が、本発明の実施形態の必ずしもすべてではないが、本発明の実施形態の少なくともいくつかに含まれていることを意味する。様々な表現「実施形態」、「一実施形態」、または「いくつかの実施形態」は、必ずしもすべてが同じ実施形態に言及するものではない。

## 【 0 0 3 3 】

本明細書が、部品、特徴、構造、または特性を含んでもよい(「m a y」、「m i g h t」、または「c o u l d」 b e i n c l u d e d)と言う場合は、その特定の部品、特徴、構造、または特性を含む必要はない。本明細書または特許請求の範囲が、「a」または「a n」要素に言及する場合は、これは唯一の要素があることを意味していない。明細書または特許請求の範囲が「追加の(a n a d d i t i o n a l)」要素に言及する場合、これは、2つ以上の追加の要素があることを排除しない。

30

## 【 0 0 3 4 】

当技術分野の技術者なら本開示の恩恵があれば、上記説明および図面から、本発明の範囲内で多くの他の変形を行うことができることを理解するであろう。したがって、本発明の範囲を定義するのは、その任意の修正を含めて頭書の特許請求の範囲である。

## 【 0 0 3 5 】

付録：いくつかの可能性を列挙した比較一覧表。これは、包括的であることを意図したものではない。他の可能性が存在する。情報のいくつかは単なる最高の推測である。

## 【表 1】

40

| タイプ               | Vcc    | モード       | キャップ | 漏洩   | 高周波数 | Rs | コメント      |

|-------------------|--------|-----------|------|------|------|----|-----------|

| n-ウェル上のデキャップ      |        |           |      |      |      |    |           |

| p+/p+ (従来技術) (図1) | >Vt    | インバージョン   | 最大   | 最大   | 良好   | 低い |           |

| n+/n+(図4)         | 全て     | アキュムレーション | ～最大  | やや低め | 良好   | 低い | No LO     |

| p+/p+(図6)         | <1V    | デフリーション   | 低め   | 低め   | OK   | 高い | No LO     |

| p+/p+             | >1V    | アキュムレーション | ～最大  | やや低め | OK   | 高い | No LO     |

| p+/n+(図5)         | <1V    | デフリーション   | 低め   | 低め   | OK   | 高い | LO        |

| p+/n+             | >1V    | アキュムレーション | ～最大  | やや低め | 良好   | 低い | LO        |

| n+/p+             | >1V+Vt | インバージョン   | 最大   | 最大   | 良好   | 低い | LO, Vcc?  |

| n+/p+             | <1V+Vt | デフリーション   | 低め   | 低め   | OK   | 高い | LO, Vcc?  |

| p-ウェル上のデキャップ      |        |           |      |      |      |    |           |

| n+/n+ (従来技術) (図9) | >Vt    | インバージョン   | 最大   | 最大   | 良好   | 低い |           |

| p+/p+(図10)        | 全て     | アキュムレーション | ～最大  | やや低め | 良好   | 低い | No LO     |

| n+/n+(図12)        | <1V    | デフリーション   | 低め   | 低め   | OK   | 高い | No LO, TW |

| n+/n+             | >1V    | アキュムレーション | ～最大  | やや低め | OK   | 高い | No LO, TW |

| n+/p+(図11)        | <1V    | デフリーション   | 低め   | 低め   | OK   | 高い | LO, TW    |

| n+/p+             | >1V    | アキュムレーション | ～最大  | やや低め | 良好   | 低い | LO, TW    |

| p+/n+             | >1V+Vt | インバージョン   | 最大   | 最大   | 良好   | 低い | LO, Vcc?  |

| p+/n+             | <1V+Vt | デフリーション   | 低め   | 低め   | OK   | 高い | LO, Vcc?  |

キー：

N-ウェル上p+/p+は、N-ウェル上のp+ポリおよびp+S/D領域を意味する。

No LO=従来の設計からのレイアウトまたはツールの変化は必要ない。

LO=従来の設計のレイアウトと比べてレイアウトの変化が必要かもしれない。

V<sub>FB</sub>=～1VをVccカラムに用いる。

TW=キャパシタのボーダーを絶縁するために、トリプル・ウェルを用いることができる。

## 【図面の簡単な説明】

【図1】 従来技術のキャパシタの概略横断面図である。

40

【図2】 ゼロ仕事関数のn-ボーダーを有するキャパシタの、キャパシタンス対ゲート・ツー・ボーダー電圧のグラフである。

【図3】 非ゼロ仕事関数のn-ボーダーを有するキャパシタの、キャパシタンス対ゲート・ツー・ボーダー電圧のグラフである。

【図4】 本発明のいくつかの実施形態によるキャパシタの概略横断面図である。

【図5】 本発明のいくつかの実施形態によるキャパシタの概略横断面図である。

【図6】 本発明のいくつかの実施形態によるキャパシタの概略横断面図である。

【図7】 ゼロ仕事関数のp-ボーダーを有するキャパシタの、キャパシタンス対ゲート・ツー・ボーダー電圧のグラフである。

【図8】 非ゼロ仕事関数のp-ボーダーを有するキャパシタの、キャパシタンス対ゲート

50

・ツー・ボデー電圧のグラフである。

【図9】従来技術のキャパシタの概略横断面図である。

【図10】本発明のいくつかの実施形態によるキャパシタの概略横断面図である。

【図11】本発明のいくつかの実施形態によるキャパシタの概略横断面図である。

【図12】本発明のいくつかの実施形態によるキャパシタの概略横断面図である。

【図13】本発明のいくつかの実施形態によるキャパシタを有するダイのブロック図である。

【図14】本発明のいくつかの実施形態によるキャパシタおよび電圧回路を有するダイのブロック図である。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

---

フロントページの続き

(72)発明者 カーニック , タナイ

アメリカ合衆国・97229・オレゴン州・ポートランド・ノースウェスト ブラックコーム ド

ライブ・3574

(72)発明者 ナイール , ラジェンドラン

アメリカ合衆国・97124・オレゴン州・ヒルズボロ・ノースウェスト エバーグリーン パー

クウェイ・19000・ナンバー 258

審査官 大嶋 洋一

(56)参考文献 特開平10-256489(JP,A)

特開平10-107235(JP,A)

特開平10-163421(JP,A)

特開平08-083887(JP,A)

特開平05-013680(JP,A)

米国特許第05883423(US,A)

米国特許第05032892(US,A)

(58)調査した分野(Int.Cl., DB名)

H01L 21/822

H01L 27/04