(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第4013432号

(P4013432)

(45) 発行日 平成19年11月28日(2007.11.28)

(24) 登録日 平成19年9月21日(2007.9.21)

(51) Int.CI.

F 1

H O 1 L 23/12 (2006.01)

H O 1 L 23/12 301C

請求項の数 4 (全 9 頁)

(21) 出願番号 特願2000-2594 (P2000-2594)

(22) 出願日 平成12年1月11日 (2000.1.11)

(65) 公開番号 特開2001-196500 (P2001-196500A)

(43) 公開日 平成13年7月19日 (2001.7.19)

審査請求日 平成18年8月30日 (2006.8.30)

(73) 特許権者 000006013

三菱電機株式会社

東京都千代田区丸の内二丁目7番3号

(74) 代理人 100113077

弁理士 高橋 省吾

(74) 代理人 100112210

弁理士 稲葉 忠彦

(74) 代理人 100108431

弁理士 村上 加奈子

(74) 代理人 100128060

弁理士 中鶴 一隆

(72) 発明者 田牧 努

東京都千代田区丸の内二丁目2番3号 三菱電機株式会社内

最終頁に続く

(54) 【発明の名称】半導体パッケージ

## (57) 【特許請求の範囲】

## 【請求項 1】

表裏導通スルーホールを有する誘電体基板を積層して形成したキャビティ内に半導体素子及び誘電体回路基板を搭載した半導体パッケージにおいて、上記キャビティを形成する複数の上記表裏導通スルーホールから上記キャビティに向かう方向に信号周波数の概略 1 / 4 伝送波長の間隔をもって、抵抗膜を形成した複数のスルーホールを配置したことを特徴とする半導体パッケージ。

## 【請求項 2】

表裏導通スルーホールを有する誘電体基板を積層して形成したキャビティ内に半導体素子及び誘電体回路基板を搭載した半導体パッケージにおいて、上記キャビティを形成する複数の上記表裏導通スルーホールから上記キャビティの周囲方向に信号周波数の概略 1 / 4 伝送波長の間隔をもって、抵抗膜を形成した複数のスルーホールを配置したことを特徴とする半導体パッケージ。

## 【請求項 3】

表裏導通スルーホールを有する誘電体基板を積層して形成したキャビティ内に半導体素子及び誘電体回路基板を搭載した半導体パッケージにおいて、上記キャビティを形成する複数の上記表裏導通スルーホールから上記キャビティに向かう方向及び上記キャビティの周囲方向に信号周波数の概略 1 / 4 伝送波長の間隔をもって、抵抗膜を形成した複数のスルーホールを配置したことを特徴とする半導体パッケージ。

## 【請求項 4】

10

20

表裏導通スルーホールを有する誘電体基板を積層して形成したキャビティ内に半導体素子及び誘電体回路基板を搭載した半導体パッケージにおいて、抵抗膜を形成した、長さの異なる複数のスルーホールを配置したことを特徴とする請求項1～3のいずれかに記載の半導体パッケージ。

【発明の詳細な説明】

【0001】

【発明の属する技術分野】

この発明は、高周波数帯で動作するマイクロ波、ミリ波集積回路を封止するパッケージに関するものである。

【0002】

10

【従来の技術】

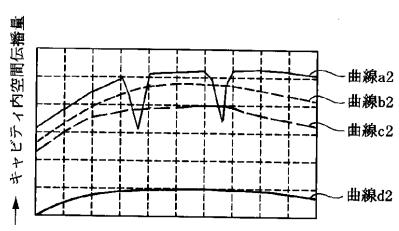

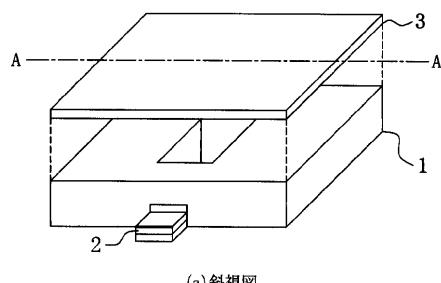

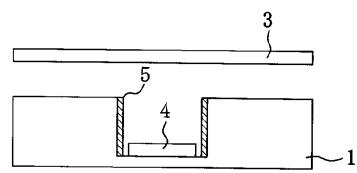

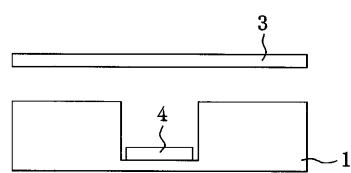

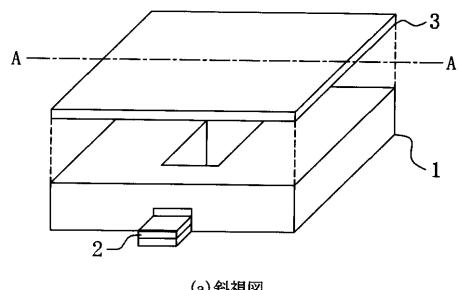

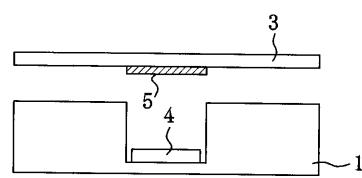

図6、図7、図8は従来の半導体パッケージを示す図である。図において、1は金属製の箱体、2は入出力端子、3はキャップ、4は半導体素子及び誘電体回路基板、5は抵抗体である。

【0003】

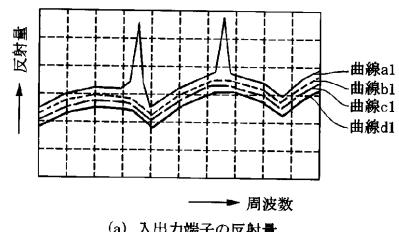

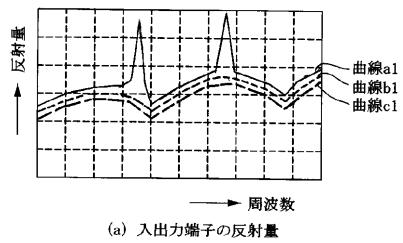

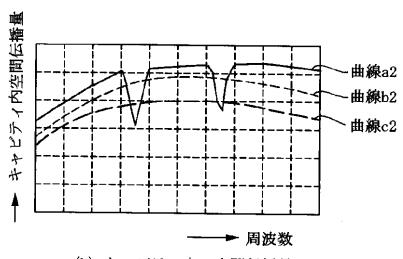

また、図9は従来の半導体パッケージの特性を示す図である。図において、曲線a1、a2は図6のようにキャビティ内に抵抗体5を設けない場合、曲線b1、b2は図7のようにキャビティ側壁に抵抗体5を設けた場合、曲線c1、c2は図8のようにキャップ3の裏面に抵抗体5を設けた場合、の入出力端子2における反射特性及びキャビティ内空間伝播特性である。

20

【0004】

次に、従来の半導体パッケージの動作及び特性について説明する。従来の半導体パッケージは、図6、図7、図8のように箱体1に形成したキャビティに半導体素子及び誘電体回路基板4を配置し、出力端子2を設けて、パッケージ内部に配置した半導体素子及び誘電体回路基板4と外部とを電気的に接続する。さらにキャップ3で封止することにより気密構造とする。このような半導体パッケージでは、キャビティ内寸法により、遮断周波数の決まる導波管伝送モード及び共振周波数の決まる導波管共振モードが存在し、この共振周波数を有する信号がこのキャビティに蓄えられる。この信号が、半導体素子及び誘電体回路基板4に結合した場合、異常発振や破壊を招き、外部の回路等にも悪影響を与える。したがって、従来のパッケージでは、図7及び図8のように、キャビティ内に抵抗体5を設けることにより、共振を抑圧していた。

30

【0005】

次に、従来の半導体パッケージの特性について補足する。従来の各半導体パッケージの入出力端子2における反射特性は、図9の曲線a1、曲線b1及び曲線c1のようになり、キャビティに抵抗体5がない場合（図6の場合、曲線a1）は共振周波数を有し、キャビティ抵抗体5がある場合（図7及び図8の場合、曲線b1及びc1）は共振を抑えることが可能になる。また、従来の各半導体パッケージの空間伝播特性は図9の曲線a2、曲線b2及び曲線c2のようになり、キャビティに抵抗体5がない場合（図6の場合、曲線a2）は異常発振が起こり、キャビティに抵抗体5がある場合（図7及び図8の場合、曲線b2及びc2）でも高い空間アイソレーションが確保できない（伝播特性の損失を大きくできない）ため、半導体素子及び誘電体回路基板4の利得が高い場合、または安定性が低い場合、空間アイソレーションの低い周波数帯と結合すると異常発振、破壊等が起こる可能性がある。このように、従来の半導体パッケージでは、キャビティ内に抵抗体5を設けることで共振を抑圧していたが、高い空間アイソレーションを確保できないため、高利得の半導体回路等を実装した場合、異常発振、破壊等が起こる可能性があり、問題となっていた。

40

【0006】

【発明が解決しようとする課題】

上記のように、従来の半導体パッケージでは、キャビティ内に抵抗体を設けることで共振を抑圧していたが、高い空間アイソレーションを確保できないため、高利得の半導体回路

50

等を実装した場合、異常発振、破壊等が起こる可能性があり、課題となっていた。

【0007】

この発明はかかる課題を解決するためになされたものであり、高利得の半導体回路等を実装した場合でも、異常発振、破壊等を抑圧することが可能な半導体パッケージを提供するものである。

【0008】

【課題を解決するための手段】

第1の発明による半導体パッケージは、積層した誘電体基板内にキャビティを形成する際に設ける複数の表裏導通スルーホールから、キャビティ方向に信号周波数の概略 $1/4$ 伝送波長の間隔をもって、抵抗膜を形成した複数のスルーホールを配置したものである。 10

【0009】

また、第2の発明による半導体パッケージは、積層した誘電体基板内にキャビティを形成する際に設ける複数の表裏導通スルーホールから、キャビティの周囲方向に信号周波数の概略 $1/4$ 伝送波長の間隔をもって、抵抗膜を形成した複数のスルーホールを配置したものである。

【0010】

第3の発明による半導体パッケージは、積層した誘電体基板内にキャビティを形成する際に設ける複数の表裏導通スルーホールから、キャビティ方向及びキャビティの周囲方向の2方向に信号周波数の概略 $1/4$ 伝送波長の間隔をもって、抵抗膜を形成した複数のスルーホールを配置したものである。 20

【0011】

また、第4の発明による半導体パッケージは、積層した誘電体基板内にキャビティを形成する際に設ける複数の表裏導通スルーホールから、キャビティ方向に信号周波数の概略 $1/4$ 伝送波長の間隔をもって、抵抗膜を形成した長さの異なる複数のスルーホールを配置したものである。

【0012】

【発明の実施の形態】

実施の形態1.

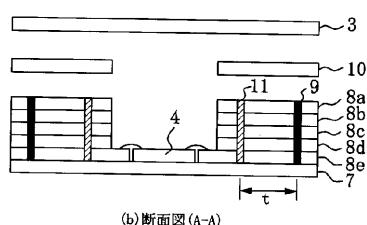

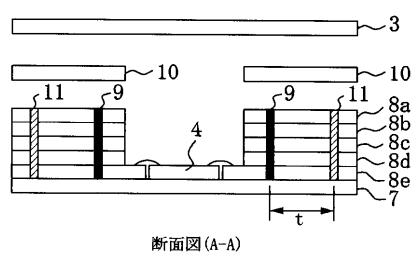

図1は、この発明の実施の形態1を示す半導体パッケージの構成図であり、図において、2は入出力端子、3はキャップ、4は半導体素子及び誘電体回路基板、7はベース、8a～8eは積層してキャビティを構成する誘電体基板、9は表裏導通スルーホール、10はシールリング、11は抵抗膜を形成したスルーホールである。 30

【0013】

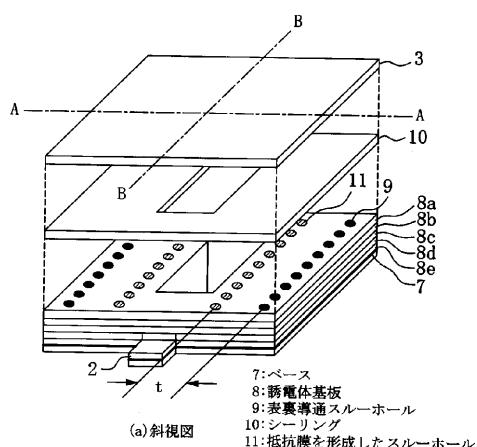

また、図2はこの発明の半導体パッケージの特性を示す図である。図において、曲線a1, a2, b1, b2, c1, c2は図9と同様であり、曲線d1, d2はこの発明の半導体パッケージの入出力端子2における反射特性及びキャビティ内空間伝播特性である。

【0014】

次に、動作及び特性について説明する。図1のようにベース7の上に誘電体基板8a～8eを積層し表裏導通スルーホール9によってキャビティを形成する。また、出力端子2を設けてパッケージ内部に配置した半導体素子及び誘電体回路基板4と外部とを電気的に接続する。さらにシールリング10とキャップ3とで封止することにより気密構造とする。抵抗膜を形成したスルーホール11は、表裏導通スルーホール9からキャビティ方向に、信号周波数F0の概略 $1/4$ 伝送波長の間隔tをもって配置され、このキャビティにおける共振を抑圧する。 40

【0015】

次に、この発明の半導体パッケージの特性について補足する。図2において、曲線a1, a2, b1, b2, c1, c2は、従来の技術(図9)にて説明したとおりである。曲線d1は、この発明の半導体パッケージの入出力端子2における反射特性であり、曲線d2はキャビティ内の空間伝播特性である。図のように、この半導体パッケージによると、キャビティ内寸法による共振を抑えることができ、空間伝播特性についても、高い空間アイ 50

ソレーションを確保することができるため、高利得の半導体回路等を実装した場合でも、異常発振、破壊等を抑圧することが可能になる。

**【0016】**

また、抵抗膜を形成した複数のスルーホール11の配置間隔により、空間伝播特性の調整が可能である。

**【0017】**

なお、ベース7及びシールリング10のない半導体パッケージにおいても、上記と同等の効果が得られる。

**【0018】**

実施の形態2.

10

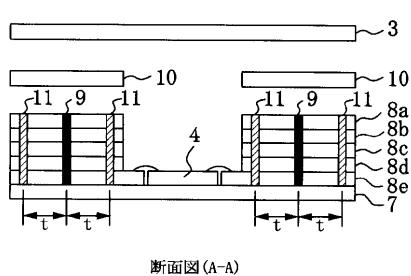

図3は、この発明の実施の形態2を示す半導体パッケージの構成図であり、図において、3はキャップ、4は半導体素子及び誘電体回路基板、7はベース、8a～8eは積層してキャビティを構成する誘電体基板、9は表裏導通スルーホール、10はシールリング、11は抵抗膜を形成したスルーホールである。

**【0019】**

次に、動作及び特性について説明する。図3のようにベース7の上に誘電体基板8a～8eを積層し表裏導通スルーホール9によってキャビティを形成する。また、出力端子(図中では省略)を設けてパッケージ内部に配置した半導体素子及び誘電体回路基板4と外部とを電気的に接続する。さらにシールリング10とキャップ3とで封止することにより気密構造とする。抵抗膜を形成したスルーホール11は、表裏導通スルーホール9からキャビティの周囲方向に、信号周波数F0の概略1/4伝送波長の間隔tをもって配置され、図2の曲線d1および曲線d2のように、このキャビティにおける共振を抑圧し、また空間伝播特性についても、高い空間アイソレーションを確保することができる。したがって、この半導体パッケージによると、キャビティ内部に高利得の半導体回路等を実装した場合でも、異常発振、破壊等を抑圧することが可能になる。

20

**【0020】**

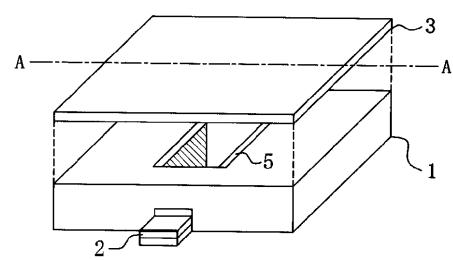

実施の形態3.

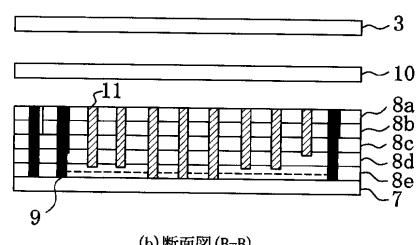

図4は、この発明の実施の形態3を示す半導体パッケージの構成図であり、図において、3はキャップ、4は半導体素子及び誘電体回路基板、7はベース、8a～8eは積層してキャビティを構成する誘電体基板、9は表裏導通スルーホール、10はシールリング、11は抵抗膜を形成したスルーホールである。

30

**【0021】**

次に、動作及び特性について説明する。図4のようにベース7の上に誘電体基板8a～8eを積層し表裏導通スルーホール9によってキャビティを形成する。また、出力端子(図中では省略)を設けてパッケージ内部に配置した半導体素子及び誘電体回路基板4と外部とを電気的に接続する。さらにシールリング10とキャップ3とで封止することにより気密構造とする。抵抗膜を形成したスルーホール11は、表裏導通スルーホール9からキャビティ方向及びキャビティの周囲方向の2方向に、信号周波数F0の概略1/4伝送波長の間隔tをもって配置され、図2の曲線d1および曲線d2のように、このキャビティにおける共振を抑圧し、また空間伝播特性についても、高い空間アイソレーションを確保することができる。したがって、この半導体パッケージによると、キャビティ内部に高利得の半導体回路等を実装した場合でも、異常発振、破壊等を抑圧することが可能になる。また、複数のキャビティが隣接した場合でも、キャビティの周囲方向に設けた、抵抗膜を形成したスルーホール11によって、隣接したキャビティへの信号の漏れ出しを抑圧することができる。

40

**【0022】**

実施の形態4.

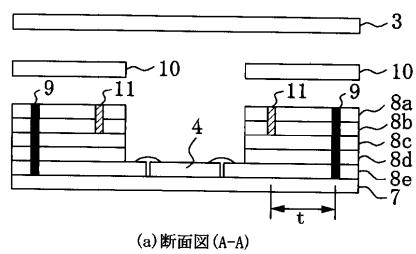

図5は、この発明の実施の形態4を示す半導体パッケージの構成図であり、3はキャップ、4は半導体素子及び誘電体回路基板、7はベース、8a～8eは積層してキャビティを構成する誘電体基板、9は表裏導通スルーホール、10はシールリング、11は抵抗膜を

50

形成したスルーホールである。

#### 【0023】

次に、動作及び特性について説明する。図5のようにベース7の上に誘電体基板8a～8eを積層し表裏導通スルーホール9によってキャビティを形成する。また、出力端子(図中では省略)を設けてパッケージ内部に配置した半導体素子及び誘電体回路基板4と外部とを電気的に接続する。さらにシールリング10とキャップ3とで封止することにより気密構造とする。

抵抗膜を形成したスルーホール11は、表裏導通スルーホール9からキャビティ方向に、信号周波数F0の概略1/4伝送波長の間隔tをもって配置され、図2の曲線d1および曲線d2のように、このキャビティにおける共振を抑圧し、また空間伝播特性についても、高い空間アイソレーションを確保することができる。したがって、この半導体パッケージによると、キャビティ内部に高利得の半導体回路等を実装した場合でも、異常発振、破壊等を抑圧することが可能になる。

#### 【0024】

また、実施の形態1～3では、抵抗膜を形成した複数のスルーホール11によって囲まれる誘電体を含む空間の寸法により、新たに導波管伝送モード及び導波管共振モードが発生するため、共振を発生する可能性がある。しかし、本実施の形態4の半導体パッケージによると、抵抗膜を形成した複数のスルーホール11の長さが異なるため、この抵抗膜を形成した複数のスルーホール11によって囲まれる空間を形成せず、新たに導波管伝送モード及び導波管共振モードが発生しない。したがって、この半導体パッケージによると、キャビティにおける共振の抑圧、高い空間アイソレーションの確保が、より効果的に達成できる。

#### 【0025】

##### 【発明の効果】

第1の発明によれば、積層した誘電体基板内にキャビティを形成するために設ける複数の表裏導通スルーホールから、キャビティ方向に信号周波数の概略1/4伝送波長の間隔をもって、抵抗膜を形成した複数のスルーホールを配置したことにより、キャビティ内寸法による共振を抑えることができ、空間伝播特性についても、高い空間アイソレーションを確保することができるため、高利得の半導体回路等を実装した場合でも、異常発振、破壊等を抑圧することが可能になる。

#### 【0026】

また、第2の発明によれば、積層した誘電体基板内にキャビティを形成するために設ける複数の表裏導通スルーホールから、キャビティの周囲方向に信号周波数の概略1/4伝送波長の間隔をもって、抵抗膜を形成した複数のスルーホールを配置したことにより、キャビティ内寸法による共振を抑えることができ、空間伝播特性についても、高い空間アイソレーションを確保することができるため、高利得の半導体回路等を実装した場合でも、異常発振、破壊等を抑圧することが可能になる。

#### 【0027】

第3の発明によれば、積層した誘電体基板内にキャビティを形成するために設ける複数の表裏導通スルーホールから、キャビティ方向及びキャビティの周囲方向の2方向に信号周波数の概略1/4伝送波長の間隔をもって、抵抗膜を形成した複数のスルーホールを配置したことにより、キャビティ内寸法による共振を抑えることができ、空間伝播特性についても、高い空間アイソレーションを確保することができるため、高利得の半導体回路等を実装した場合でも、異常発振、破壊等を抑圧することが可能になる。また、複数のキャビティが隣接した場合でも、隣接したキャビティへの信号の漏れ出しを抑圧することができる。

#### 【0028】

また、第4の発明によれば、積層した誘電体基板内にキャビティを形成するために設ける複数の表裏導通スルーホールから、キャビティ方向に信号周波数の概略1/4伝送波長の間隔をもって、抵抗膜を形成した長さの異なる複数のスルーホールを配置したことにより

10

20

30

40

50

、第1～第3の発明よりも、効果的にキャビティ内寸法による共振を抑えることができ、空間伝播特性についても、高い空間アイソレーションを確保することができるため、高利得の半導体回路等を実装した場合でも、異常発振、破壊等を抑圧することが可能になる。

**【図面の簡単な説明】**

**【図1】** この発明による半導体パッケージの実施の形態1を示す図である。

**【図2】** この発明による半導体パッケージの特性を示す図である。

**【図3】** この発明による半導体パッケージの実施の形態2を示す図である。

**【図4】** この発明による半導体パッケージの実施の形態3を示す図である。

**【図5】** この発明による半導体パッケージの実施の形態4を示す図である。

**【図6】** 従来の半導体パッケージの一例を示す図である。

10

**【図7】** 従来の半導体パッケージの一例を示す図である。

**【図8】** 従来の半導体パッケージの一例を示す図である。

**【図9】** 従来の半導体パッケージの特性を示す図である。

**【符号の説明】**

7 ベース、8a 誘電体基板、8b 誘電体基板、8c 誘電体基板、8d 誘電体基板

、8e 誘電体基板、9 表裏導通スルーホール、10 シールリング、11 抵抗膜を形成したスルーホール。

**【図1】**

**【図2】**

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

(a) 斜視図

(b) 断面図(A-A)

【図9】

(a) 入出力端子の反射量

(b) キャビティ内の空間伝播量

---

フロントページの続き

(72)発明者 古屋 輝雄

東京都千代田区丸の内二丁目2番3号 三菱電機株式会社内

(72)発明者 坪田 吉弘

東京都千代田区丸の内二丁目2番3号 三菱電機株式会社内

審査官 菅野 智子

(56)参考文献 特開平11-260966(JP,A)

特開平09-321501(JP,A)

特開平05-063432(JP,A)

特開平11-136009(JP,A)

特開平06-188322(JP,A)

特開2001-144221(JP,A)

特開2001-024100(JP,A)

特開平03-253098(JP,A)

特開2000-164766(JP,A)

特開平09-191206(JP,A)

特開2001-185918(JP,A)

特開平11-186457(JP,A)

(58)調査した分野(Int.Cl., DB名)

H01L 23/12

H01L 23/04

H05K 9/00

H05K 3/46

H01P 1/04

H01P 3/02