(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第4612450号

(P4612450)

(45) 発行日 平成23年1月12日(2011.1.12)

(24) 登録日 平成22年10月22日(2010.10.22)

(51) Int.Cl.

F 1

|             |           |            |   |

|-------------|-----------|------------|---|

| HO1L 25/065 | (2006.01) | HO1L 25/08 | Z |

| HO1L 25/07  | (2006.01) | HO1L 21/52 | E |

| HO1L 25/18  | (2006.01) |            |   |

| HO1L 21/52  | (2006.01) |            |   |

請求項の数 3 (全 13 頁)

|           |                               |

|-----------|-------------------------------|

| (21) 出願番号 | 特願2005-92595 (P2005-92595)    |

| (22) 出願日  | 平成17年3月28日 (2005.3.28)        |

| (65) 公開番号 | 特開2006-278519 (P2006-278519A) |

| (43) 公開日  | 平成18年10月12日 (2006.10.12)      |

| 審査請求日     | 平成19年4月19日 (2007.4.19)        |

|           |                                                    |

|-----------|----------------------------------------------------|

| (73) 特許権者 | 000003078<br>株式会社東芝<br>東京都港区芝浦一丁目1番1号              |

| (74) 代理人  | 110001092<br>特許業務法人サクラ国際特許事務所                      |

| (74) 代理人  | 100077849<br>弁理士 須山 佐一                             |

| (72) 発明者  | 芳村 淳<br>神奈川県川崎市幸区小向東芝町1番地 株式会社東芝 マイクロエレクトロニクスセンター内 |

| (72) 発明者  | 大久保 忠宣<br>三重県四日市市山之一色町800番地 株式会社東芝 四日市工場内          |

最終頁に続く

(54) 【発明の名称】積層型半導体装置の製造方法

## (57) 【特許請求の範囲】

## 【請求項1】

基板上に第1の半導体素子を接着する工程と、

前記基板の電極部と前記第1の半導体素子の電極パッドとをポンディングワイヤを介して電気的に接続する工程と、

第2の半導体素子となる複数の素子領域を有する半導体ウエハの裏面に、厚さが50μm以上140μm以下で常温弹性率が30MPa以上120MPa以下のダイシングフィルムと厚さが30μm以上で硬化前の常温弹性率が500MPa以上1200MPa以下の接着剤フィルムとを一体化した複合フィルムを貼り付ける工程と、

前記複合フィルムが貼り付けられた半導体ウエハを、前記接着剤フィルムと共に前記素子領域毎に分割して前記第2の半導体素子を作製する工程と、

前記第2の半導体素子を前記ダイシングフィルムからピックアップする工程と、

前記ピックアップした第2の半導体素子の裏面に貼り付けられた前記接着剤フィルムを接着剤層として、前記ポンディングワイヤの一部を前記接着剤層内に取り込みつつ、前記第2の半導体素子を前記第1の半導体素子上に接着する工程とを具備し、

前記接着剤フィルムは接着時粘度が1kPa・s以上100kPa・s未満の範囲の絶縁性樹脂層を有することを特徴とする積層型半導体装置の製造方法。

## 【請求項2】

請求項1記載の積層型半導体装置の製造方法において、

前記接着剤フィルムは、前記第1の半導体素子側に配置され、接着時粘度が1kPa・s以

10

20

上100kPa・s未満の範囲の第1の絶縁性樹脂層と、前記第2の半導体素子側に配置され、接着時粘度が100kPa・s以上の第2の絶縁性樹脂層とを有することを特徴とする積層型電子部品の製造方法。

【請求項3】

請求項1または請求項2記載の積層型半導体装置の製造方法において、

前記接着剤フィルムは60μm以上150μm以下の範囲の厚さを有することを特徴とする積層型半導体装置の製造方法。

【発明の詳細な説明】

【技術分野】

【0001】

10

本発明は複数の半導体素子を積層した積層型半導体装置の製造方法に関する。

【背景技術】

【0002】

近年、半導体装置の小型化や高密度実装化等を実現するために、1つのパッケージ内に複数の半導体素子等を積層して封止したスタック型マルチチップパッケージが実用化されている。スタック型マルチチップパッケージにおいては、複数の半導体素子が回路基板上にダイアタッチフィルム等の接着剤フィルムを介して順に積層されている。各半導体素子の電極パッドは、回路基板の電極部とボンディングワイヤを介して電気的に接続されている。そして、このような積層体を封止樹脂でパッケージングすることによって、スタック型マルチチップパッケージが構成される。

20

【0003】

このようなスタック型マルチチップパッケージにおいて、上段側の半導体素子が下段側の半導体素子より小さい場合には、下段側の半導体素子のボンディングワイヤに上段側の半導体素子が干渉することはない。しかし、このような構成では適用可能な半導体素子が大幅に制限されることから、同形状の半導体素子同士や上段側が下段側より大きい半導体素子まで適用範囲を広げることが進められている。ここで、同形状の半導体素子同士や上段側に下段側より大形状の半導体素子を積層する場合には、下段側の半導体素子のボンディングワイヤと上段側の半導体素子とが接触するおそれがある。このため、ボンディングワイヤの接触による絶縁不良やショート等の発生を防止することが重要となる。

【0004】

30

そこで、半導体素子間を接着する接着剤層の厚さを、下段側の半導体素子のボンディングワイヤと上段側の半導体素子とが接触しないように設定することが行われている（例えば特許文献1，2参照）。例えば特許文献2には、上段側の半導体素子の裏面にボンディングワイヤの接触を防止し得る厚さを有する接着剤フィルムを貼り付けた後、この接着剤フィルムを利用して下段側の半導体素子上に接着することが記載されている。さらに、半導体素子に個片化する前の半導体ウエハの裏面に接着剤フィルムとダイシングシートとを順に貼り付け、その後に半導体ウエハを分割することが記載されている。

【0005】

また、上段側の半導体素子の下面側に絶縁層を形成することによって、下段側の半導体素子のボンディングワイヤと上段側の半導体素子との接触による絶縁不良やショート等を抑制することも提案されている。例えば特許文献3には、上段側の半導体素子を個片化する前の半導体ウエハの裏面に、絶縁層と接着層とを積層した複合シートを貼り付けた後、半導体ウエハを複合シートと共に分割して半導体素子を作製し、この上段側の半導体素子の裏面側に設けられた接着層（接着剤層）を利用して下段側の半導体素子上に接着することが記載されている。ボンディングワイヤの接触による絶縁不良やショート等は、上段側の半導体素子の裏面に接着層と積層して設けられた絶縁層で防止される。

40

【特許文献1】特開2001-308262号公報

【特許文献2】特開2004-072009号公報

【特許文献3】特開2002-222913号公報

【発明の開示】

50

**【発明が解決しようとする課題】****【0006】**

上述したように、半導体素子間の接着剤層の厚さ等に基づいてボンディングワイヤの接触による絶縁不良やショート等を防止する場合には、接着剤層の厚さを十分に厚くする必要があることに加えて、下段側の半導体素子に接続されたボンディングワイヤの一部（半導体素子との接続部近傍）が接着剤層内に取り込まれることになるため、接着剤層はボンディングワイヤに変形や接続不良等を生じさせないような粘度を有する必要がある。

**【0007】**

このような接着時粘度が低粘度でかつ厚い接着剤層（接着剤フィルム）を使用する場合、従来の製造工程や構成材料等を適用しただけでは種々の問題が生じることが判明した。例えば、従来のダイシングフィルム（テープ）に低粘度でかつ厚い接着剤フィルムを積層して複合フィルムを作製した場合、この複合フィルムの剥離テープからの剥離性が低下し、半導体ウエハに貼り付ける際に不良が生じやすくなってしまう。また、この複合フィルムの貼り付け不良を単に防止しただけでは、ダイシングフィルムから半導体素子をピックアップする際に不都合が生じるおそれがある。

10

**【0008】**

本発明はこのような課題に対処するためになされたもので、複数の半導体素子を積層して積層型半導体装置を製造するにあたって、上段側の半導体素子の裏面に比較的厚い接着剤フィルムとダイシングフィルムとを積層一体化した複合フィルムを貼り付けることに起因する不良発生を抑制することを可能にした積層型半導体装置の製造方法を提供することを目的としている。

20

**【課題を解決するための手段】****【0009】**

本発明の一態様に係る積層型半導体装置の製造方法は、基板上に第1の半導体素子を接着する工程と、前記基板の電極部と前記第1の半導体素子の電極パッドとをボンディングワイヤを介して電気的に接続する工程と、第2の半導体素子となる複数の素子領域を有する半導体ウエハの裏面に、厚さが50μm以上140μm以下で常温弹性率が30MPa以上120MPa以下のダイシングフィルムと厚さが30μm以上で硬化前の常温弹性率が500MPa以上1200MPa以下の接着剤フィルムとを一体化した複合フィルムを貼り付ける工程と、前記複合フィルムが貼り付けられた半導体ウエハを、前記接着剤フィルムと共に前記素子領域毎に分割して前記第2の半導体素子を作製する工程と、前記第2の半導体素子を前記ダイシングフィルムからピックアップする工程と、前記ピックアップした第2の半導体素子の裏面に貼り付けられた前記接着剤フィルムを接着剤層として、前記ボンディングワイヤの一部を前記接着剤層内に取り込みつつ、前記第2の半導体素子を前記第1の半導体素子上に接着する工程とを具備し、前記接着剤フィルムは接着時粘度が1kPa・s以上100kPa・s未満の範囲の絶縁性樹脂層を有することを特徴としている。

30

**【発明の効果】****【0010】**

本発明の一態様に係る積層型半導体装置の製造方法においては、厚さが50μm以上140μm以下で常温弹性率(25)が30MPa以上120MPa以下のダイシングフィルムを、厚さが30μm以上の接着剤フィルムと積層一体化した複合フィルムを用いているため、フィルム貼り付け工程の成功率と素子ピックアップ工程の成功率を共に高めることができる。これによって、例えばボンディングワイヤの一部を素子間の接着剤層の内部に取り込むようにした積層型半導体装置の製造歩留りを向上させることができるとなる。

40

**【発明を実施するための最良の形態】****【0011】**

以下、本発明を実施するための形態について、図面を参照して説明する。なお、以下では本発明の実施形態を図面に基づいて述べるが、それらの図面は図解のために提供されるものであり、本発明はそれらの図面に限定されるものではない。

**【0012】**

50

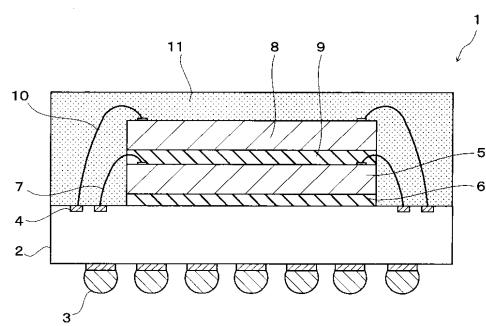

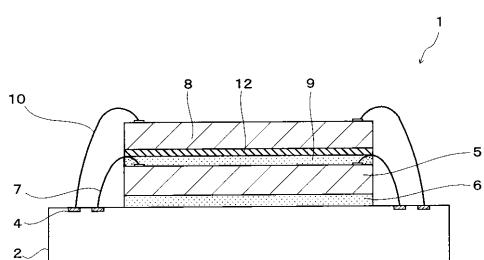

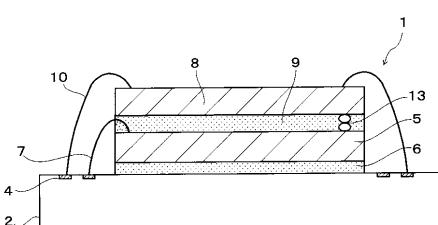

図1は本発明の一実施形態による積層型半導体装置の製造方法を適用したスタック型マルチチップ構造の半導体装置の構成を模式的に示す断面図である。同図に示す積層型半導体装置1は、素子搭載用の基板2を有している。素子搭載用基板2は半導体素子を搭載することが可能で、かつ回路を有するものであればよい。このような基板2としては、絶縁基板や半導体基板等の表面や内部に回路を形成した回路基板、あるいはリードフレームのような素子搭載部と回路部とを一体化した基板等を用いることができる。

#### 【0013】

図1に示す積層型半導体装置1は、素子搭載用基板として回路基板2を有している。回路基板2を構成する基板には、樹脂基板、セラミックス基板、ガラス基板等の絶縁基板、あるいは半導体基板等、各種の材料からなる基板を適用することができる。樹脂基板を適用した回路基板としては、一般的な多層銅張積層板（多層プリント配線板）等が挙げられる。回路基板2の下面側には、半田バンプ等の外部接続端子3が設けられている。10

#### 【0014】

回路基板2の素子搭載面となる上面側には、外部接続端子3と例えば内層配線（図示せず）を介して電気的に接続された電極部4が設けられている。電極部4はワイヤボンディング部となるものである。このような回路基板2の素子搭載面（上面）には、第1の半導体素子5が第1の接着剤層6を介して接着されている。第1の接着剤層6には一般的なダイアタッチ材（ダイアタッチフィルム等）が用いられる。第1の半導体素子5の上面側に設けられた第1の電極パッド（図示せず）は、第1のボンディングワイヤ7を介して回路基板2の電極部4と電気的に接続されている。20

#### 【0015】

第1の半導体素子5上には、第2の半導体素子8が第2の接着剤層9を介して接着されている。第2の半導体素子8は、例えば第1の半導体素子5と同形またはそれより大形の形状を有している。第2の接着剤層9は第2の半導体素子8の接着時温度で軟化または溶融し、その内部に第1のボンディングワイヤ7の一部（電極パッドとの接続部近傍）を取り込みつつ、第1の半導体素子5と第2の半導体素子8とを接着するものである。この際、第1のボンディングワイヤ7の電極パッド側端部は、第2の接着剤層9内に取り込まれることで、第2の半導体素子8との接触が防止される。20

#### 【0016】

上記した第1のボンディングワイヤ7と第2の半導体素子8との接触防止機能を得る上で、第2の接着剤層9には厚さが30μm以上の絶縁性樹脂層が適用される。第2の接着剤層9の厚さが30μm未満であると、第1のボンディングワイヤ7が第2の半導体素子8に接触しやすくなり、絶縁不良やショート等の発生率が高くなる。ワイヤ径等にもよるが、第2の接着剤層9の厚さは60μm以上とすることがより好ましい。ボンディングワイヤ7の径が25μmの場合の具体例としては、厚さが75μmや85μmの第2の接着剤層9が挙げられる。なお、第2の接着剤層9を厚くしすぎると積層型半導体装置1の薄型化が阻害されるため、第2の接着剤層9の厚さは150μm以下とすることが好ましい。30

#### 【0017】

また、接着時に第1のボンディングワイヤ7の一部を良好に取り込む上で、第2の接着剤層9は接着時温度における粘度（接着時粘度）が1kPa・s以上100kPa・s未満であることが好ましい。第2の接着剤層9の接着時粘度が1kPa・s未満であると軟らかすぎて、接着剤が素子端面からはみ出しあそれがある。一方、第2の接着剤層9の接着時粘度が100kPa・s以上であると、第1のボンディングワイヤ7に変形や接続不良等を生じさせるおそれがある。第2の接着剤層9の接着時粘度は1～50kPa・sの範囲であることがより好ましく、さらには1～20kPa・sの範囲であることが望ましい。40

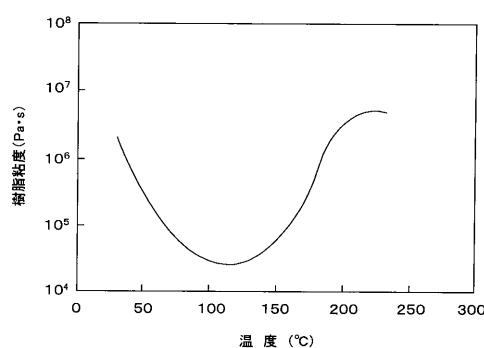

#### 【0018】

第2の接着剤層9を構成する絶縁性樹脂には、例えばエポキシ樹脂のような熱硬化性樹脂が用いられる。熱硬化性樹脂の接着時粘度は、熱硬化性樹脂組成物の組成等で調整してもよいし、また接着工程における加熱温度で調整することも可能である。図2はエポキシ樹脂からなるダイアタッチ材の硬化前の粘度特性の一例を示している。図2に示す粘度特50

性を有するダイアタッチ材は、接着時温度を約70～160 の範囲とすることで接着時粘度を100kPa・sより小さくすることができる。また、接着時温度を約80～140 の範囲とすることで接着時粘度を50kPa・s以下とすることができます。

#### 【0019】

上述したような第2の接着剤層9を介して第1の半導体素子5上に接着された第2の半導体素子8は、その上面側に設けられた第2の電極パッド(図示せず)が第2のボンディングワイヤ10を介して回路基板2の電極部4と電気的に接続されている。そして、回路基板2上に積層、配置された第1および第2の半導体素子5、8を、例えばエポキシ樹脂のような封止樹脂11を用いて封止することによって、スタック型マルチチップパッケージ構造の積層型半導体装置1が構成される。なお、図1では2個の半導体素子5、8を積層した構造について説明したが、半導体素子の積層数はこれに限られるものではなく、3個もしくはそれ以上であってもよいことは言うまでもない。10

#### 【0020】

上述した実施形態の積層型半導体装置1は、例えば以下のようにして作製される。まず、回路基板2上に第1の接着剤層6を用いて第1の半導体素子5を接着する。続いて、ワイヤボンディング工程を実施して、第1のボンディングワイヤ7で回路基板2の電極部4と第1の半導体素子5の電極パッドとを電気的に接続する。次に、第1の半導体素子5上に第2の接着剤層9を介して第2の半導体素子8を接着する。

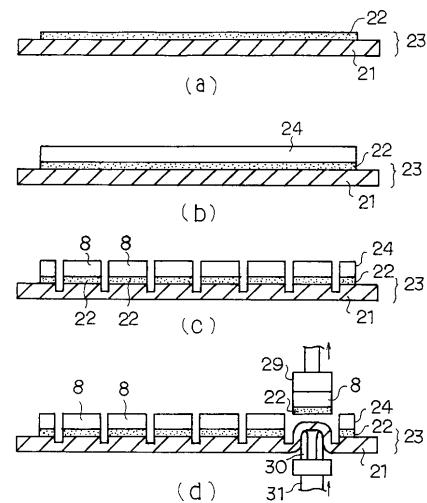

#### 【0021】

第2の半導体素子8の接着工程を実施するにあたって、第2の接着剤層9は予め半硬化させた接着剤フィルムとして第2の半導体素子8に貼り付けておく。この際、接着剤フィルムは第2の半導体素子8に分割する前の半導体ウエハの裏面に、ダイシングフィルム(テープ)と共に貼り付けるものとする。すなわち、図3(a)に示すように、ダイシングフィルム21と第2の接着剤層9となる厚さ30μm以上の接着剤フィルム22とを積層一体化して複合フィルム23を作製する。ダイシングフィルム21と接着剤フィルム22とは、例えば図示を省略した粘着層を介して一体化する。粘着層には例えば厚さが1～30μm程度の紫外線硬化型樹脂層等が用いられる。20

#### 【0022】

ここで、ダイシングフィルム21には、厚さが50μm以上140μm以下で常温弹性率(25)が30MPa以上120MPa以下の樹脂フィルム、例えばポリオレフィン樹脂フィルムのような熱可塑性樹脂フィルムが用いられる。熱可塑性樹脂等からなるダイシングフィルム21の弹性率は、フィルムを構成する樹脂組成物の組成や添加剤等により調整することが可能である。なお、ダイシングフィルム21は弹性率が異なる2層以上の樹脂層の複合体であってもよい。このような場合の弹性率は、各層による複合弹性率が30MPa以上120MPa以下であればよい。また、接着剤フィルム23には上述したように厚さが30μm以上、特に60～150μmの範囲(さらには60～100μmの範囲)のエポキシ樹脂フィルムのような熱硬化性樹脂フィルムが用いられる。熱硬化性樹脂フィルム(23)は半硬化させた状態(Bステージの状態)でダイシングフィルム21と積層一体化する。30

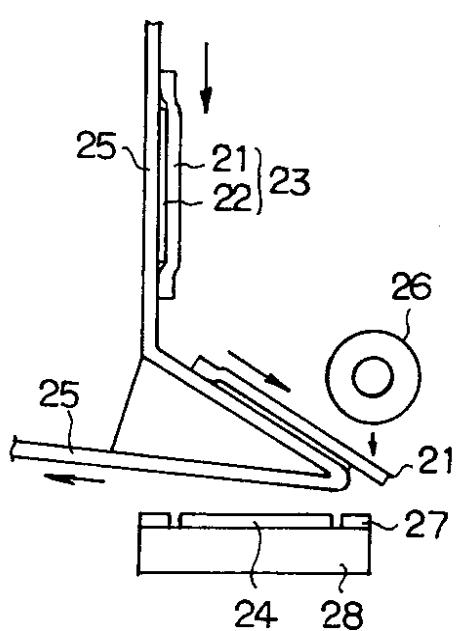

#### 【0023】

次に、図3(b)に示すように、ダイシングフィルム21と接着剤フィルム22とを積層一体化した複合フィルム23を、第2の半導体素子8となる複数の素子領域を有する半導体ウエハ24の裏面に貼り付ける。この複合フィルム23の半導体ウエハ24への貼り付け工程は、複合フィルム23の貼り付け効率の向上や貼り付けコストの削減等を図るために、図4に示すようにテープ状のセパレータ(剥離紙)25に付着させた状態で複合フィルム23を供給する。このような複合フィルム23が付着されたセパレータ25を鋭角に折り返すことによって、複合フィルム23の先端をセパレータ25から剥離させる。40

#### 【0024】

そして、このセパレータ25から剥離させた複合フィルム23の先端を、上側からローラ26で半導体ウエハ24に押し付けることによって、複合フィルム23を半導体ウエハ24の裏面に貼り付ける。また、図3では図示を省略したが、半導体ウエハ24のダイシ50

ング工程はダイシングフィルム21をフラットリング(ウェハリング)27に張設した状態で実施するため、剥離させた複合フィルム23の先端をステージ28上に半導体ウエハ24と共に配置したフラットリング27から順に押し当てて貼り付ける。

#### 【0025】

上述した複合フィルム23と半導体ウエハ24との貼り付け工程において、接着剤フィルム23の厚さが30μm以上というように厚い場合、従来のダイシングフィルムではセパレータ25を鋭角に折り返しても、複合フィルム23の先端をセパレータ25から剥離できないおそれがある。すなわち、接着剤フィルム23の厚さに対してダイシングフィルム21の厚さが薄すぎたり、また柔らかすぎる(常温弹性率が低すぎる)と、ダイシングフィルム21がセパレータ25に倣ってしまうことから、ダイシングフィルム21の先端をセパレータ25から剥離できないおそれがある。言い換えると、ダイシングフィルム21のセパレータ25からの剥離不良の発生率が上昇する。

#### 【0026】

そこで、この実施形態では厚さが50μm以上で常温弹性率が30MPa以上のダイシングフィルム21を用いている。このようなダイシングフィルム21によれば、その先端をセパレータ25から確実に剥離することができる。すなわち、複合フィルム23と半導体ウエハ24との貼り付け工程における不良発生率(複合フィルム23の貼り付け自体の失敗や貼り付け位置不良等の発生率)を低減することが可能となる。複合フィルム23の貼り付け成功率を高める上で、ダイシングフィルム21の厚さは85μm以上であることがさらに好ましく、また常温弹性率(25)は40MPa以上であることがさらに好ましい。

#### 【0027】

次に、ダイシングフィルム21と接着剤フィルム22とを一体化した複合フィルム23を貼り付けた半導体ウエハ24を、図3(c)に示すようにダイシングし、各素子領域毎に分割して第2の半導体素子8を作製する。この際、接着剤フィルム22は半導体ウエハ24と共に切断されるため、第2の半導体素子8の裏面には個片化された接着剤フィルム22が貼り付けられた状態となる。一方、ダイシングフィルム21はその表面側の一部のみが切断されるため、分割(個片化)された第2の半導体素子8はダイシングフィルム21により保持された状態が維持される。

#### 【0028】

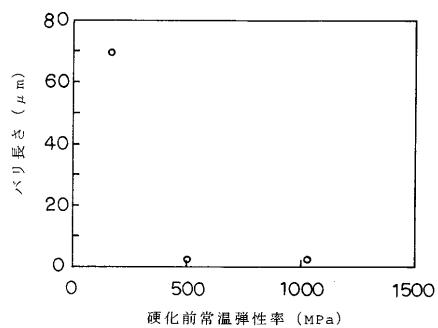

ここで、半導体ウエハ24のダイシング工程における不良発生率を抑制する上で、接着剤フィルム22は硬化前の常温弹性率(25)が500MPa以上であることが好ましい。接着剤フィルム22の常温弹性率(25)が500MPa未満であると、半導体ウエハ24のダイシング時に発生するバリ長さが長くなり、次工程のピックアップ時に半導体素子8の剥離性が低下する。図5は厚さ75μmの接着剤フィルム22の常温弹性率(25)とダイシング時におけるバリ長さとの関係の一例を示している。このように、接着剤フィルム22の常温弹性率(25)が500MPa以上であればバリ長さが短くなり、半導体素子8のピックアップ性の低下を抑制することができる。なお、接着剤フィルム22の常温弹性率が高すぎるとダイシング工程自体に悪影響を及ぼすおそれがあるため、接着剤フィルム22の常温弹性率は1200MPa以下であることが好ましい。

#### 【0029】

次いで、図3(d)に示すように、例えば吸着コレット29と数本の突き上げピン30を有する剥離機構31とを用いて、個片化した第2の半導体素子8をダイシングフィルム21からピックアップする。すなわち、吸着コレット29で吸着保持した第2の半導体素子8を上昇させつつ、その裏面側から突き上げピン30を押し当てることによって、半導体素子8をダイシングフィルム21から剥離する。なお、剥離機構31は突き上げピン30を突き上げる機構に限らず、例えば扇状に開いたバタフライ状の部材を中央に向けて閉じることで、ダイシングフィルム21の裏面を押し上げる機構等であってもよい。

#### 【0030】

上述した半導体素子8のピックアップ工程において、ダイシングフィルム21は下方から突き上げられた際に湾曲する等して、その端部に剥離基点が生じる程度の柔軟性を有し

10

20

30

40

50

ている必要がある。すなわち、ダイシングフィルム 2 1 が硬すぎるとピックアップ時に剥離し難くなり、ピックアップ不良の発生率が増加する。そこで、この実施形態では厚さが 140 μm 以下で常温弹性率 (25) が 120 MPa 以下のダイシングフィルム 2 1 を用いている。このようなダイシングフィルム 2 1 は剥離基点が生じやすいため、ピックアップ不良の発生率を低減することが可能となる。半導体素子 8 のピックアップ成功率を高める上で、ダイシングフィルム 2 1 の厚さは 120 μm 以下であることがさらに好ましく、また常温弹性率は 85 MPa 以上であることがさらに好ましい。

#### 【 0 0 3 1 】

このように、厚さが 50 μm 以上 140 μm 以下で常温弹性率 (25) が 30 MPa 以上 120 MPa 以下のダイシングフィルム 2 1 を用いることによって、相反する複合フィルム 2 3 の貼り付け成功率と半導体素子 8 のピックアップ成功率を共に高めることができる。すなわち、厚さが 30 μm 以上の接着剤フィルム 2 3 を予めダイシングフィルム 2 1 と共に半導体ウエハ 2 4 に貼り付ける場合において、複合フィルム 2 3 の貼り付け工程から半導体素子 8 のピックアップ工程までの製造歩留り（半導体素子 8 の製造歩留り）を向上させることができるとなる。半導体素子 8 の製造歩留りを高める上で、ダイシングフィルム 2 1 は厚さが 85 μm 以上 120 μm 以下であることがより好ましく、また常温弹性率 (25) は 40 MPa 以上 85 MPa 以下であることがより好ましい。

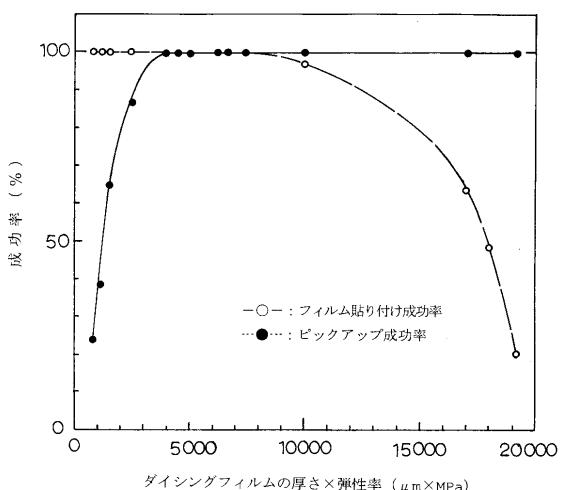

#### 【 0 0 3 2 】

表 1 および図 6 に複合フィルム 2 3 の貼り付け成功率および半導体素子 8 のピックアップ成功率とダイシングフィルム 2 1 の厚さおよび常温弹性率（厚さ × 常温弹性率 (μm × MPa)）との関係の一例を示す。ここでは、直径 8 インチ × 厚さ 60 μm の Si ウエハと厚さ 85 μm の接着剤フィルムを用いた。また、Si チップの形状は 10.71 × 7.08 × 0.06 mm とした。表 1 および図 6 から明らかなように、ダイシングフィルム 2 1 の厚さが 50 μm 以上 140 μm 以下で常温弹性率が 30 MPa 以上 120 MPa 以下、特に厚さが 85 μm 以上 120 μm 以下で常温弹性率が 40 MPa 以上 85 MPa 以下である場合に、複合フィルム 2 3 の貼り付け成功率と半導体素子 8 のピックアップ成功率を共に高めることができる。

#### 【 0 0 3 3 】

10

20

【表1】

| 試料<br>No | 厚さ<br>( $\mu\text{m}$ ) | 弾性率<br>(MPa) | 厚さ×弾性率<br>( $\mu\text{m} \times \text{MPa}$ ) | フィルム貼り付け<br>成功率 (%) | ピックアップ<br>成功率 (%) |

|----------|-------------------------|--------------|-----------------------------------------------|---------------------|-------------------|

| 1        | 30                      | 30           | 900                                           | 24                  | 100               |

| 2        | 40                      | 30           | 1200                                          | 38                  | 100               |

| 3        | 50                      | 30           | 1500                                          | 65                  | 100               |

| 4        | 50                      | 50           | 2500                                          | 87                  | 100               |

| 5        | 70                      | 57           | 3990                                          | 100                 | 100               |

| 6        | 70                      | 65           | 4550                                          | 100                 | 100               |

| 7        | 110                     | 45           | 4950                                          | 100                 | 100               |

| 8        | 110                     | 57           | 6270                                          | 100                 | 100               |

| 9        | 70                      | 94           | 6580                                          | 100                 | 100               |

| 10       | 130                     | 57           | 7410                                          | 100                 | 100               |

| 11       | 100                     | 102          | 10200                                         | 100                 | 97                |

| 12       | 140                     | 120          | 16800                                         | 100                 | 64                |

| 13       | 150                     | 120          | 18000                                         | 100                 | 48                |

| 14       | 160                     | 120          | 19200                                         | 100                 | 20                |

## 【0034】

次に、第2の半導体素子8の裏面に貼り付けられた接着剤フィルム22を接着剤層9として用いて、第2の半導体素子8を第1の半導体素子5上に接着する。第2の半導体素子8の接着工程は、例えば以下のようにして実施する。すなわち、第1の半導体素子5を接着した回路基板2を加熱ステージ上に載置する。一方、裏面側に接着剤層9(接着剤フィルム22)を形成した第2の半導体素子8を実装ツールで吸着保持する。実装ツールに保持された第2の半導体素子8を、第1の半導体素子5に対して位置合せした後に下降させ、第2の接着剤層9を第1の半導体素子5に押し当てる。この際、加熱ステージおよび実装ツールの少なくとも一方を用いて第2の接着剤層9を加熱する。

## 【0035】

第2の接着剤層9はその内部に第1のボンディングワイヤ7の一部(第2の半導体素子8との接続部近傍)を取り込むことが可能な厚さを有し、かつその接着時粘度( $1\text{kPa}\cdot\text{s}$ 以上 $100\text{kPa}\cdot\text{s}$ 未満)に基づいて第1および第2の半導体素子5、8間の間隔を保持する機能を有しているため、第1のボンディングワイヤ7と第2の半導体素子8との接触を抑制することができる。このような状態で第2の接着剤層9をさらに加熱して熱硬化させることによって、第1のボンディングワイヤ7と第2の半導体素子8との接触による絶縁不良やショート等の発生を抑制しつつ、第1の半導体素子5上にそれと同形もしくは大形の第2の半導体素子8を積層することが可能となる。

## 【0036】

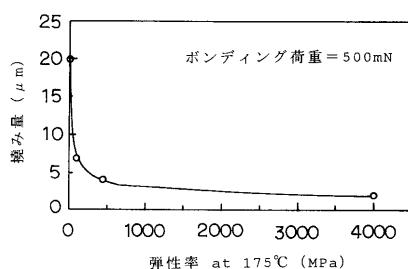

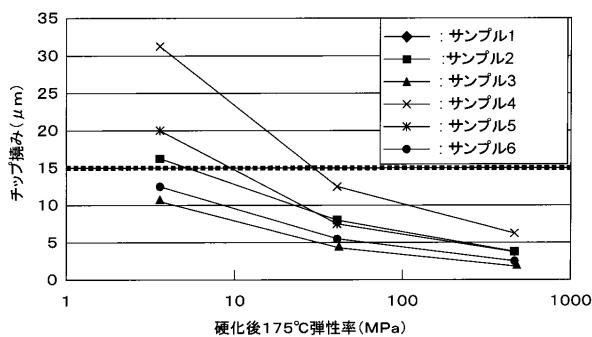

この後、第2の半導体素子8に対してワイヤボンディング工程を実施して、第2のボンディング10で回路基板2の電極部4と第2の半導体素子8の電極パッドとを電気的に接続する。この際、半導体素子8の厚さが例えば $80\mu\text{m}$ 以下になるとボンディング荷重による撓み量が大きくなり、半導体素子8にクラックや割れが発生しやすくなる。半導体素子8の撓み量は第2の接着剤層9の硬化後の弾性率に影響され、ボンディング時の温度(例えば $175^\circ\text{C}$ )による硬化後弾性率が低いと撓み量が大きくなる傾向がある。図7はS i チップ

10

20

30

40

50

の厚さが70 μm、硬化後の接着剤層9の厚さが85 μmの場合において、500mNの荷重でボンディングしたときのSiチップの撓み量を示している。

#### 【0037】

また、図8は硬化後の接着剤層9の175における弾性率と第2の半導体素子8のワイヤボンディング時における撓み量との関係を示している。図8において、サンプル1は半導体素子の厚さ(チップ厚さ)が50 μmで硬化後の接着剤層9の厚さ(接合層厚さ)が60 μmである。サンプル2はチップ厚さが70 μmで接合層厚さが60 μm、サンプル3はチップ厚さが90 μmで接合層厚さ60 μm、サンプル4はチップ厚さが50 μmで接合層厚さが85 μm、サンプル5はチップ厚さが70 μmで接合層厚さが85 μm、サンプル6はチップ厚さが90 μmで接合層厚さが85 μmである。図7および図8から、硬化後の接着剤層9の175における弾性率を40MPa以上とすることによって、ワイヤボンディング工程における第2の半導体素子8の撓みを15 μm以下とすることができます。これによって、ワイヤボンディング工程における第2の半導体素子8の撓みに起因するクラックや割れの発生を抑制することが可能となる。10

#### 【0038】

この実施形態の製造方法においては、厚さが50 μm以上140 μm以下で常温弾性率(25)が30MPa以上120MPa以下のダイシングフィルム21を、厚さが30 μm以上(特に60 μm以上)の接着剤フィルム22と積層一体化した複合フィルム23を用い、これを第2の半導体素子8に分割する前の半導体ウエハ24に貼り付けているため、複合フィルム23の貼り付け成功率と半導体素子8のピックアップ成功率を共に高めることができる。従って、第1のボンディングワイヤ7の一部を第2の接着剤層9の内部に取り込むようにした積層型半導体装置1の製造歩留りを、第1のボンディングワイヤ7と第2の半導体素子8との接触による不良発生を抑制しつつ向上させることができるとなる。すなわち、信頼性等を向上させた積層型半導体装置1を高歩留りで製造することができる。20

#### 【0039】

上述した実施形態の積層型半導体装置1は、接着時粘度が1kPa・s以上100kPa・s未満の第2の接着剤層9で第1のボンディングワイヤ7と第2の半導体素子8との接触を抑制している。これに加えて、例えば図9に示すように、第2の半導体素子8の下面に絶縁層12を形成するようにしてもよい。第2の半導体素子8の下面側に絶縁層12を設けることによって、第1のボンディングワイヤ7と第2の半導体素子8との接触に伴う絶縁不良やショート等の発生をより確実に防止することができる。絶縁層12には例えば接着時粘度が100kPa・s以上の絶縁性樹脂層が用いられる。絶縁層12の接着時粘度は130kPa・s以上、さらには200kPa・s以上であることがより好ましい。ただし、粘度があまり高すぎると接合層としての機能が損なわれるため、絶縁層12の接着時温度における粘度は1000kPa・s未満であることが好ましい。30

#### 【0040】

このような半導体素子5、8間の接合層が絶縁層12と接着剤層9との2層構造を有する積層型半導体装置1は、予め接着時温度に対して層形状を維持し得る絶縁樹脂フィルム(例えば接着時粘度が100kPa・s以上の第2の樹脂フィルム)を接着剤フィルム(例えば接着時粘度が1kPa・s以上100kPa・s未満の第1の樹脂フィルム)と積層し、このような2層構造のフィルムをダイシングフィルムと積層一体化した複合フィルムを用いることによって、上述した実施形態の製造工程を適用して作製することができる。また、第2の半導体素子8の製造歩留り、ひいては積層型半導体装置1の製造歩留りの向上効果についても、上述した実施形態と同様に得ることができる。40

#### 【0041】

上述した絶縁層12の具体的な構成材料としては、ポリイミド樹脂、シリコーン樹脂、エポキシ樹脂、アクリル樹脂等の熱硬化性樹脂が挙げられ、接着剤層9より接着時粘度が高い絶縁性樹脂が用いられる。また、樹脂フィルムを適用して絶縁層12を形成する場合、例えば接着剤フィルムと同一の絶縁性樹脂を用い、これら各樹脂フィルムの乾燥温度や乾燥時間(例えばエポキシ樹脂ワニスを塗布した後の乾燥温度や乾燥時間等)を異ならせ50

ることによって、接着剤フィルムと2層化したフィルムを得るようにしてよい。

#### 【0042】

また、第2の半導体素子8の下面に絶縁層12を設ける場合には、第1のボンディングワイヤ7を積極的に絶縁層12と当接させ、これによって第1のボンディングワイヤ7を回路基板2側に変形させるようにしてもよい。すなわち、絶縁層12は単に第1のボンディングワイヤ7と第2の半導体素子8との接触に伴うショート等を抑制するだけでなく、第1のボンディングワイヤ7を積極的に回路基板2側に変形させる層として利用することができる。このように、絶縁層12を利用して第1のボンディングワイヤ7を回路基板2側に変形させることによって、積層型半導体装置1のより一層の薄型化を実現することが可能となる。

10

#### 【0043】

すなわち、第2の接着剤層9を第1の半導体素子5に押し付ける過程で、第1のボンディングワイヤ7の少なくとも一部を絶縁層12に当接させて回路基板2側に変形させることによって、第1のボンディングワイヤ7の高さをいずれもワイヤ高さの標準値以下に揃えることができる。言い換えると、第1のボンディングワイヤ7の高さはいずれも第2の接着剤層9の厚さ以下となるため、第2の接着剤層9の厚さに基づいて半導体装置1全体をより一層薄型化することが可能となる。また、第1のボンディングワイヤ7と第2の半導体素子8との絶縁は絶縁層12により維持されるため、絶縁不良やショート等が生じることもない。これらによって、より一層の薄型化と信頼性の向上を両立させたスタック型マルチチップパッケージ構造の半導体装置1を実現することが可能となる。

20

#### 【0044】

また、第1の半導体素子5と第2の半導体素子8との間の距離は、例えば図10に示すように、第1の半導体素子5の接続に使用されていない電極パッド、すなわち非接続パッド（ノンコネクションパッド）上に、金属材料や樹脂材料等からなるスタッドパンプ13を形成して維持するようにしてもよい。スタッドパンプ13は第1のボンディングワイヤ7と第2の半導体素子8との接触に伴う絶縁不良やショート等の抑制に対して有効に機能するものである。また、スタッドパンプ13で非接続パッドやヒューズ部を埋めることで、これらに起因する気泡の発生を抑制することができる。スタッドパンプ13の設置箇所は1箇所でもよいが、第1の半導体素子5の重心を通る3箇所以上に設置することが好ましい。

30

#### 【0045】

なお、本発明は上記した各実施形態に限定されるものではなく、複数の半導体素子を積層して搭載した各種の積層型半導体装置に適用することができる。そのような積層型半導体装置についても、本発明に含まれるものである。また、本発明の実施形態は本発明の技術的思想の範囲内で拡張もしくは変更することができ、この拡張、変更した実施形態も本発明の技術的範囲に含まれるものである。

#### 【図面の簡単な説明】

#### 【0046】

【図1】本発明の一実施形態による製造方法を適用して作製した積層型半導体装置の構成を模式的に示す断面図である。

40

【図2】本発明の実施形態に適用した接着剤樹脂の粘度特性の一例を示す図である。

【図3】本発明の一実施形態による積層型半導体装置の要部製造工程を示す断面図である。

【図4】図3に示す積層型半導体装置の製造工程における複合フィルムの貼り付け工程を示す図である。

【図5】本発明の一実施形態に適用した接着剤フィルムの硬化前常温弹性率とダイシング工程におけるバリ長さとの関係の一例を示す図である。

【図6】本発明の一実施形態における複合フィルムの貼り付け成功率および半導体素子のピックアップ成功率とダイシングフィルムの厚さおよび常温弹性率（厚さ×常温弹性率）との関係の一例を示す図である。

50

【図7】本発明の一実施形態に適用した接着剤層の硬化後弾性率(175 )とポンディング時における半導体素子の撓み量との関係の一例を示す図である。

【図8】本発明の実施形態における接着剤層の硬化後弾性率(175 )とポンディング時における半導体素子の撓み量との関係を示す図である。

【図9】図1に示す積層型半導体装置の一変形例を示す断面図である。

【図10】図1に示す積層型半導体装置の他の変形例を示す断面図である。

【符号の説明】

【0047】

1 ... 積層型半導体装置、2 ... 回路基板、4 ... 電極部、5 ... 第1の半導体素子、6 ... 第1の接着剤層、7 ... 第1のポンディングワイヤ、8 ... 第2の半導体素子、9 ... 第2の接着剤層、10 ... 第2のポンディングワイヤ、11 ... 封止樹脂、12 ... 絶縁層、13 ... スタッドバンプ。

10

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図9】

【図8】

【図10】

---

フロントページの続き

審査官 市川 裕司

(56)参考文献 特開2004-072009(JP,A)

特開2003-041209(JP,A)

特開2004-253476(JP,A)

特開2002-222913(JP,A)

特開2004-186429(JP,A)

特開2005-327789(JP,A)

(58)調査した分野(Int.Cl., DB名)

H01L 25/065

H01L 21/52

H01L 25/07

H01L 25/18