(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第4008152号

(P4008152)

(45) 発行日 平成19年11月14日(2007.11.14)

(24) 登録日 平成19年9月7日(2007.9.7)

(51) Int.C1.

F 1

H01L 21/339 (2006.01)

H01L 29/76 301A

H01L 29/762 (2006.01)

H04N 5/335 F

H04N 5/335 (2006.01)

請求項の数 2 (全 6 頁)

(21) 出願番号

特願平11-134679

(22) 出願日

平成11年5月14日(1999.5.14)

(65) 公開番号

特開2000-323703(P2000-323703A)

(43) 公開日

平成12年11月24日(2000.11.24)

審査請求日

平成17年3月7日(2005.3.7)

(73) 特許権者 000191238

新日本無線株式会社

東京都中央区日本橋横山町3番10号

(72) 発明者 熊田 貴夫

埼玉県上福岡市福岡二丁目1番1号 新日本無線株式会社川越製作所内

審査官 柴山 将隆

(56) 参考文献 特開昭61-128568 (JP, A)

特開平10-041322 (JP, A)

(58) 調査した分野(Int.C1., DB名)

H01L 21/339

H01L 29/762

H04N 5/335

(54) 【発明の名称】電荷結合素子およびその製造方法

## (57) 【特許請求の範囲】

## 【請求項1】

半絶縁性基板と、該半絶縁性基板上に設けられる導電性半導体層と、該導電性半導体層上に設けられる非導電性半導体層と、該非導電性半導体層上に一定間隔で設けられ、前記非導電性半導体層と反応すると共に前記導電性半導体層とショットキー接合をする金属からなるゲート電極と、該ゲート電極の下の前記非導電性半導体層に、該ゲート電極の幅より広い幅になるように形成される前記ゲート電極の金属と前記非導電性半導体層との合金層とからなることを特徴とするショットキー接合型の電荷結合素子。

## 【請求項2】

半絶縁性基板上に導電性半導体層を設け、該導電性半導体層上に非導電性半導体層を介して、該非導電性半導体層と反応すると共に、前記導電性半導体層とショットキー接合をする金属からなるゲート電極を一定間隔で形成し、熱処理をすることにより、前記ゲート電極の金属と前記非導電性半導体層との合金層を、前記ゲート電極の間隔より合金層の間隔が小さくなるように形成する際、

前記熱処理を前記ゲート電極間のリーク電流を監視しながら行うことを特徴とするショットキー接合型の電荷結合素子の製造方法。

## 【発明の詳細な説明】

## 【0001】

## 【発明の属する技術分野】

本発明は、ショットキーゲート電極を有する電荷結合素子およびその製造方法に関する。

さらに詳しくは、ゲート間ギャップを狭く形成することができる電荷結合素子およびその製造方法に関する。

### 【0002】

#### 【従来の技術】

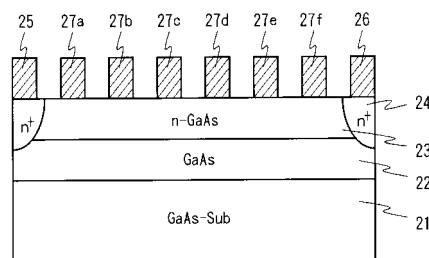

従来の GaAs - 4 相駆動電荷結合素子は、たとえば図 4 に断面構造図が示されるような構造に形成されている。すなわち、半絶縁性の GaAs 化合物半導体基板 21 上に、アンドープ GaAs 層 22 を成長し、その表面に Si がドープされた n 形 GaAs 層 23 が形成されている。そして、さらに高濃度の  $n^+$  形領域 24 の表面に電荷入力用のオーミック電極 25 と電荷出力用のオーミック電極 26 がリフトオフ法により設けられ、その間に、たとえばリフトオフ法などにより、Ti / Pt / Au からなるショットキーゲート電極 27a ~ 27f が設けられることにより、電荷結合素子が形成されている。なお、図 4 において、ゲート電極の両端の電極 27a および 27f は、それぞれ電荷出入力制御用電極で、27b ~ 27e が 4 相転送ゲート電極に対応する。10

### 【0003】

#### 【発明が解決しようとする課題】

前述の構造の電荷結合素子は、ショットキーゲート電極の間隔が広いと電荷転送効率を考慮した場合、電荷トラップ源となり、電荷転送効率が低下する。従って、ゲート間ギャップは可能な限り狭いほうが望ましい。しかし、従来の構造では、ゲート電極のギャップはリフトオフ工程またはドライエッキングやミーリングの微細化能力により制限され、そのギャップは数千 程度が限度となっている。そのため電荷転送効率を向上させるため、さらなる微細化が望まれている。20

### 【0004】

本発明は、このような状況に鑑みてなされたもので、ゲート間ギャップの小さいショットキー接合型の電荷結合素子およびその製造方法を提供することを目的とする。

### 【0005】

本発明の他の目的は、ゲート電極用の金属と半導体層との合金層を形成する際に、その合金層のギャップを非常に精度よく制御することができる電荷結合素子の製造方法を提供することにある。

### 【0006】

本発明のさらに他の目的は、ゲート電極用の金属と半導体層との合金層を形成する際に、均一に固相反応が進みバラツキが生じないで均一な合金層を形成することができる電荷結合素子の製造方法を提供することにある。30

### 【0007】

#### 【課題を解決するための手段】

本発明のショットキー接合型の電荷結合素子は、半絶縁性基板と、該半絶縁性基板上に設けられる導電性半導体層と、該導電性半導体層上に設けられる非導電性半導体層と、該非導電性半導体層上に一定間隔で設けられ、前記非導電性半導体層と反応すると共に前記導電性半導体層とショットキー接合をする金属からなるゲート電極と、該ゲート電極の下の前記非導電性半導体層に、該ゲート電極の幅より広い幅になるように形成される前記ゲート電極の金属と前記非導電性半導体層との合金層とからなることを特徴とする。40

### 【0008】

この構造にすることにより、合金層もゲート電極の一部となり、その合金層間のギャップがゲート電極間のギャップとなり、ゲート電極間のギャップを小さくすることができる。また、その反応界面の導電性半導体層の深さ方向（半導体層の表面から基板側）への反応の進行により、電荷井戸の深さも変化し、その深さを制御することもできる。そして、電荷井戸の深さとゲート電極間のギャップを独立して制御することができる。その結果、電荷転送効率が向上し、高性能な電荷結合素子が得られる。

### 【0011】

本発明のショットキー接合型の電荷結合素子の製造方法は、半絶縁性基板上に導電性半導体層を設け、該導電性半導体層上に非導電性半導体層を介して、該非導電性半導体層と

反応と共に、前記導電性半導体層とショットキー接合をする金属からなるゲート電極を一定間隔で形成し、熱処理することにより、前記ゲート電極の金属と前記非導電性半導体層との合金層を、前記ゲート電極の間隔より合金層の間隔が小さくなるように形成する際、前記熱処理を前記ゲート電極間のリーケ電流を監視しながら行うことの特徴とする。

### 【0012】

この構成にすることにより、合金層のギャップを非常に精度よく狭くすることができる。

### 【0015】

#### 【発明の実施の形態】

つぎに、図面を参照しながら本発明の電荷結合素子およびその製造方法について説明をする。

### 【0016】

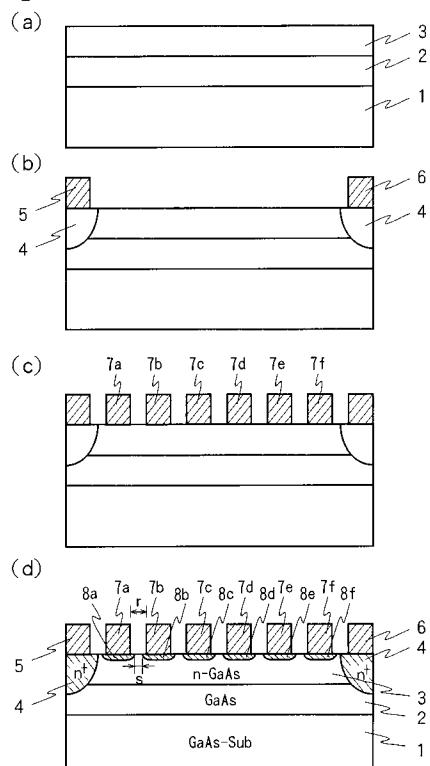

本発明の参考例のショットキー接合型の電荷結合素子は、図1(d)にその一実施形態の断面説明図が示されるように、たとえばGaAsからなる半絶縁性基板1上に、アンドープのGaAsからなるバッファ層2を介して、たとえばSiがドープされたn形のGaAsからなる導電性半導体層3が設けられ、そのn形半導体層3上に一定間隔でゲート電極7(7a～7f)が設けられている。このゲート電極7は、前述の導電性半導体層3と反応と共に、導電性半導体層3とショットキー接合をする金属、たとえばPtやPdなどの白金族の元素が好ましく用いられる。そして、このゲート電極7の下の導電性半導体層3に、ゲート電極7の金属と導電性半導体層3とが固相反応をして合金層8(8a～8f)が、それぞれゲート電極7a～7fの幅より広い幅になるように形成されている。

### 【0017】

半絶縁性基板1は、前述のように、不純物がドープされていないGaAsなどの化合物半導体が用いられる。その上に設けられるアンドープのGaAs層2は、半絶縁性基板1から導電性半導体層3への影響をなくするためにバッファ層として設けられるもので、500程度の厚さに低温で形成される。

### 【0018】

導電性半導体層3は、たとえばSiドープのn形に形成され、電荷を転送するための動作領域となるものである。この厚さが余り厚すぎると素子間分離が大となり、薄すぎると表面準位により常に空乏化するため、好ましくは2000～10000程度に、さらに好ましくは5000程度に設けられる。

### 【0019】

この導電性半導体層3の動作領域の両端部には、さらにSiなどの不純物を高濃度にドーピングした高不純物濃度領域4がバッファ層2に達する深さで形成され、その表面に電荷入力用および電荷出力用のオーミック電極5、6がそれぞれ設けられている。このオーミック電極5、6は、たとえばリフトオフ法などにより、Au-Ge/Ni/Auの積層構造により形成される。

### 【0020】

電荷入力用および出力用のオーミック電極5、6の間の動作領域である導電性半導体層3上には、ゲート電極7(7a～7f)が等間隔、たとえば間隔r=3000になるように設けられている。なお、両端の電極7aおよび7fは、それぞれ電荷入出力制御用ゲート電極に、真ん中の4個の電極7b～7eが4相転送電極にそれぞれ対応する。このゲート電極7は、半導体層3と反応して合金化し、かつ、ショットキーバリアを形成する金属材料、たとえばPt層をリフトオフ法により成膜することにより形成されている。この金属としては、Ptのほかに、Pd、Ru、Rh、Os、Irなどの白金族を使用しても、同様に半導体層と固相反応をし、ショットキー接合を形成することができる。

### 【0021】

そして、その後熱処理することにより、ゲート電極7の金属と半導体層3とを固相反応させ、合金層8(8a～8f)を形成する。この固相反応をさせると、半導体層の面方向

(横方向) および深さ方向(基板1側)のそれぞれに順次反応が広がり合金層8が広がる。そのため、合金層8の幅が、それぞれゲート電極7の幅より広くなるように熱処理の時間を制御し、合金層8のギャップsがゲート電極7のギャップrより狭くなるように形成され、たとえばs=1000程度になるように合金層8が形成されている。このギャップのコントロールは、たとえば隣接するゲート電極間のリーク電流を測定しながら熱処理をすることにより、精度よく制御することができる。このリーク電流の測定は、TEGパターンとして作られた隣接するゲート電極のそれぞれに測定端子を接触させ、隣接するゲート電極間の電流電圧測定を行うことによりなされ、予め作成しておいたリーク電流とギャップsの相関表によりリーク電流を制御することにより、合金層8のギャップsを非常に精度よく形成することができる。合金層8の成長は、横方向(電極の並ぶ方向)と深さ(縦)方向(基板1側)がほぼ同程度に進むため、横方向への成長を前述のリーク電流により監視することにより、縦方向への形成深さも制御することができる。10

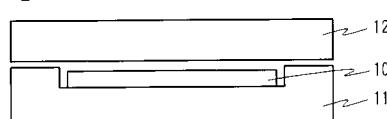

#### 【0022】

さらに、前述の熱処理をランプ加熱などのRTA処理により行うことにより、均一加熱をすることができると共に、合金化の制御を正確に行うことができる。この急速加熱処理の際、図2に示されるように、窒化ガリウム、窒化アルミニウム、もしくは窒化ホウ素またはこれらの混合物からなる保持台11を用いて、ランプ加熱などにより行うことが温度制御をしやすく加熱操作との連動性がよいと共に、効率よく均一に加熱することができるため好ましい。この保持台11は、図2に示されるように、ウェハ10(図1の半導体層の積層および電極の形成されたもの)の側面を覆うように形成されると共に、さらに上面を同様の材料により形成された保護板12により蓋することができる構造にしたほうが一層効率よく加熱することができるため好ましい。また、この保持台11や保護板12は、その表面またはその内部に、たとえばカーボンの膜や粉末などの赤外線吸収材を設けたものを使用することが、より一層熱の吸収効率を向上させることができるため好ましい。このような窒化ガリウムなどの前述の化合物からなる保持台11や保護板12を用いることにより、GaAsなどの化合物半導体は赤外線を吸収しにくいが、保持台11などの材料が加熱されて温度が上昇し、これらの材料の高い熱伝導率により即座にウェハ10の温度を上昇させ、しかもこれらの材料は高温に対して安定で、熱変形などが生じないため、ウェハ10(GaAs基板1)などと常に一定の位置関係を保持し、均一な加熱をすることができる。20

#### 【0023】

この電荷結合素子を製造するには、まず、図1(a)に示されるように、たとえばGaAsからなる半絶縁性基板1に、たとえばMOCVD法により、アンドープのGaAsからなるバッファ層2を5000程度成長する。そして、さらにSiドープのn形GaAs層3を5000程度成長する。

#### 【0024】

つぎに、図1(b)に示されるように、動作領域の両端部側に、n形不純物であるたとえばSiをイオン注入し、RTA処理によりバッファ層2に達する程度に拡散し、n<sup>+</sup>形の高不純物濃度領域4を形成する。そして、その高不純物濃度領域4上にAu-Ge/Ni/Auをリフトオフ法により順次積層し、電荷入力用および出力用のオーミック電極5、6を形成する。このRTA処理は、前述のように、図2に示されるような保持台11に入れてランプ加熱などにより行なうことが、不要部分への不純物の拡散を防止することができると共に、短時間で高精度に合金化反応を制御することができるため好ましい。40

#### 【0025】

つぎに、図1(c)に示されるように、n形半導体層3上にゲート電極7とするPt層をリフトオフ法により形成する。このゲート電極7は、前述のようにリフトオフ法またはドライエッチングもしくはミーリングなどにより行われる。そのため、ゲート電極7のそれぞれの間隔rは、1800程度が限度となる。

#### 【0026】

その後、図1(d)に示されるように、ランプ加熱などの急速加熱(RTA)処理を行い50

ゲート電極 7 の金属と半導体層 3との固相反応により合金層 8 を形成する。この方法は、前述のように、窒化ガリウムなどからなる保持台に入れて行うと共に、ゲート電極 7 間のリーク電流を測定しながら行うことにより、合金層 8 間のギャップ s を非常に精度よく制御することができる。また、深さ方向への反応深さも制御することができ、深さ方向への固相反応部である合金層 8 の深さを制御することにより、電荷井戸の深さを制御することができ、ピンチオフ電圧をコントロールすることができる。

#### 【0027】

本発明の参考例によれば、蒸着などにより設けられるゲート電極の間隔が製造プロセスの関係で一定間隔以下にすることができないくとも、その後半導体層内に合金層を形成して、合金層のギャップを狭くしているため、非常にゲート電極間ギャップを小さくすることができ、電荷転送効率の優れたショットキー接合型の電荷結合素子が得られる。

10

#### 【0028】

しかも、本発明の参考例の製造方法によれば、ゲート電極間のリーク電流を監視しながら合金層の形成をすることができるため、非常にゲート間のギャップを狭くしながら、ゲート間の接触の直前で熱処理を停止することができ、固相反応の過剰な進行によるゲート間ショートを防止することができる。

10

#### 【0029】

さらに、RTA 处理により合金層の形成を行うことにより、その制御を高精度に行うことができると共に、均一加熱をすることができ、各ゲート電極間のギャップを均一に形成することができ、特性の優れた電荷結合素子を得ることができる。

20

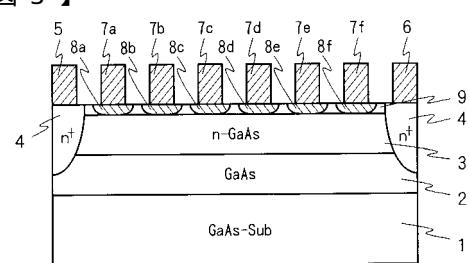

#### 【0030】

図 3 は、本発明の一実施形態の断面説明図である。この例は、図 1 に示される例の n 形 GaAs からなる導電性半導体層 3 の上に、さらにアンドープの GaAs からなる非導電性半導体層 9 が 1000 ~ 5000 程度の厚さに設けられていることがある。すなわち、この非導電性半導体層 9 の表面上に前述の参考例と同様にゲート電極 7 ( 7a ~ 7f ) を設け、非導電性半導体層との間で合金層 8 ( 8a ~ 8f ) が形成されている。この合金層 8 は、一例として丁度導電性半導体層 3 に接する程度になるように形成されている。その他の部分は前述の図 1 に示される例と同じで、同じ符号を付してその説明を省略する。このような非導電性半導体層が設けられることにより、電荷井戸の深さをゲート電極 7 ( 合金層 8 ) のギャップと独立に調整することができる。

30

#### 【0031】

前述の各例では、GaAs 半導体層を用いたが、他の半導体層、たとえばヘテロ構造を利用した HEMT 構造のもので、最上層が GaAs 、 AlGaAs または InGaAs などで形成される構造のものでもよい。

#### 【0032】

##### 【発明の効果】

本発明によれば、ゲート電極用の金属と半導体層とを固相反応させて合金層を形成しているため、ショットキーバリア型の電荷結合素子のゲート電極を非常に狭くすることができ、非常に高特性の電荷結合素子を得ることができる。

#### 【0033】

40

しかも、本発明のゲート電極間のリーク電流を監視しながらゲート電極の金属と半導体層との固相反応を制御したり、RTA 处理により固相反応をさせる製造方法によれば、非常に精度よくゲート電極間のギャップを形成することができ、非常に高精度で信頼性の高い電荷結合素子を得ることができます。

##### 【図面の簡単な説明】

【図 1】 本発明の参考例の電荷結合素子の一実施形態の製造工程を示す図である。

【図 2】 本発明の参考例の電荷結合素子の製造方法の一実施形態の熱処理を行う際の RTA 处理の保持台の説明図である。

【図 3】 本発明の電荷結合素子の一実施形態の断面説明図である。

【図 4】 従来の電荷結合素子の一例の断面説明図である。

50

## 【符号の説明】

- 1 半絶縁性基板

- 3 導電性半導体層

- 7 ゲート電極

- 8 合金層

- 9 非導電性半導体層

【図1】

- |           |            |

|-----------|------------|

| 1 半絶縁性基板  | 8 合金層      |

| 3 導電性半導体層 | 9 非導電性半導体層 |

| 7 ゲート電極   |            |

【図2】

【図3】

【図4】