(12)发明专利

(10)授权公告号 CN 104716183 B

(45)授权公告日 2020.05.01

(21)申请号 201410776936.3

(74)专利代理机构 北京林达刘知识产权代理事

(22)申请日 2014.12.15

务所(普通合伙) 11277

(65)同一申请的已公布的文献号

代理人 刘新宇

申请公布号 CN 104716183 A

(51)Int.Cl.

H01L 29/78(2006.01)

(43)申请公布日 2015.06.17

H01L 29/06(2006.01)

(30)优先权数据

H01L 29/41(2006.01)

61/915,772 2013.12.13 US

(56)对比文件

14/520,527 2014.10.22 US

US 2006/0145230 A1,2006.07.06,

(73)专利权人 电力集成公司

US 2006/0145230 A1,2006.07.06,

地址 美国加利福尼亚州

US 2005/0167749 A1,2005.08.04,

(72)发明人 S · S · 吉奥吉斯库

CN 101246906 A,2008.08.20,

W · B · 格拉博斯基

审查员 韩婷

K · R · 瓦拉达拉延 L · 朱

K-C · R · 杨

权利要求书2页 说明书6页 附图7页

(54)发明名称

具有圆柱形区域的纵向晶体管器件结构

(57)摘要

本发明涉及具有圆柱形区域的纵向晶体管器件结构。一种纵向功率晶体管器件包括第一导电类型的半导体层，具有位于所述半导体层中的多个圆柱形电介质区域。所述圆柱形电介质区域在纵向方向上从所述半导体层的顶部表面向下延伸。相邻的圆柱形电介质区域沿着一个公共直轴线被半导体层的具有第一宽度的窄区域横向隔开。每个电介质区域具有位于其中央的圆柱形导电场板构件，所述圆柱形导电场板构件在所述纵向方向上从所述顶部表面向下延伸至所述电介质区域的底部附近。所述电介质区域将所述圆柱形导电场板构件与所述窄区域横向隔开。一个源极区域位于所述顶部表面，一个漏极区域位于所述半导体层的底部。

1. 一种纵向功率晶体管器件,包括:

第一导电类型的半导体层;

多个圆柱形电介质区域,位于所述半导体层中,所述圆柱形电介质区域在纵向方向上从所述半导体层的顶部表面向下延伸,相邻的圆柱形电介质区域沿着一个公共直径轴线被所述半导体层的具有第一宽度的窄区域横向隔开;

每个圆柱形电介质区域具有位于其中央的圆柱形导电场板构件,所述圆柱形导电场板构件在所述纵向方向上从所述顶部表面向下延伸至所述圆柱形电介质区域的底部附近,所述圆柱形电介质区域将所述圆柱形导电场板构件与所述窄区域横向隔开;

所述第一导电类型的源极区域,位于所述窄区域的顶部表面处;以及

所述第一导电类型的漏极区域,位于所述半导体层下方,

其中,所述纵向功率晶体管器件的一个单元包括等边三角形布置的三个一组的相邻的圆柱形电介质区域,并且填充有电介质的沟槽形成在三个一组的相邻的圆柱形电介质区域之间。

2. 根据权利要求1所述的纵向功率晶体管器件,其中,所述圆柱形电介质区域的横向宽度将所述圆柱形导电场板构件与所述窄区域隔开,所述横向宽度在沿着所述圆柱形导电场板构件的厚度的所有点处是相同的。

3. 根据权利要求1所述的纵向功率晶体管器件,还包括第二导电类型的体区,所述体区将所述源极与所述窄区域的下部隔开,所述下部包括一个漂移区域。

4. 根据权利要求3所述的纵向功率晶体管器件,其中,每个圆柱形电介质区域还包括位于其中在所述窄区域和所述圆柱形导电场板构件之间的栅极构件。

5. 根据权利要求3所述的纵向功率晶体管器件,还包括作为平面栅极构件的栅极构件。

6. 根据权利要求1所述的纵向功率晶体管器件,其中,每个圆柱形导电场板构件均包括多晶硅。

7. 根据权利要求1所述的纵向功率晶体管器件,还包括一个衬底,所述半导体层包括位于所述衬底上的外延层。

8. 根据权利要求7所述的纵向功率晶体管器件,其中,所述衬底是所述第一导电类型。

9. 根据权利要求7所述的纵向功率晶体管器件,其中,所述衬底是第二导电类型。

10. 根据权利要求1所述的纵向功率晶体管器件,其中,所述第一导电类型包括n型。

11. 根据权利要求1所述的纵向功率晶体管器件,其中,所述圆柱形电介质区域中的每一个向下延伸到所述漏极区域中。

12. 根据权利要求3所述的纵向功率晶体管器件,其中,所述漂移区域具有从所述体区附近向下到所述漂移区域的底部附近变化的掺杂浓度。

13. 根据权利要求3所述的纵向功率晶体管器件,其中,所述漂移区域包括具有分级掺杂分布的外延层。

14. 根据权利要求12所述的纵向功率晶体管器件,其中,所述掺杂浓度在所述漂移区域的底部附近是最高的。

15. 一种高电压晶体管,包括:

一个衬底;

一个阵列的相邻的圆柱形电介质区域,位于所述衬底中并且其中相邻三个被布置成等

边三角形布局,每个圆柱形电介质区域在纵向方向上从所述衬底的顶部表面向下延伸,相邻的圆柱形电介质区域沿着一个公共直径轴线被所述衬底的具有第一宽度的窄区域横向隔开,其中,电介质填充的沟槽形成在被布置成所述等边三角形布局的相邻三个圆柱形电介质区域之间;

每个圆柱形电介质区域具有位于其中央的圆柱形导电场板构件,所述圆柱形导电场板构件在所述纵向方向上从所述顶部表面向下延伸至所述圆柱形电介质区域的底部附近,所述圆柱形电介质区域将所述圆柱形导电场板构件与所述窄区域横向隔开;

一个源极,位于所述窄区域的顶部表面处;以及

一个漏极,位于所述衬底的底部处。

16. 根据权利要求15所述的高压晶体管,还包括将所述源极与所述窄区域的下部隔开的体区,所述下部包括漂移区域。

17. 根据权利要求15所述的高压晶体管,其中,每个圆柱形电介质区域还包括位于其中在所述窄区域和所述圆柱形导电场板构件之间的栅极构件。

18. 根据权利要求15所述的高压晶体管,还包括作为平面栅极构件的栅极构件。

19. 根据权利要求15所述的高压晶体管,其中,每个圆柱形电介质区域均包括氧化物。

20. 根据权利要求15所述的高压晶体管,其中,所述第一宽度在约1微米-2微米宽的范围内。

21. 根据权利要求15所述的高压晶体管,其中,所述窄区域的掺杂浓度在大约 $1 \times 10^{15}/\text{cm}^3$ 到大约 $1 \times 10^{17}/\text{cm}^3$ 的范围内。

22. 根据权利要求15所述的高压晶体管,其中,每个圆柱形电介质区域向下延伸到所述漏极中。

## 具有圆柱形区域的纵向晶体管器件结构

[0001] 相关申请的交叉参引

[0002] 本申请要求享有于2013年12月13日提交的标题为“Vertical Transistor Device Structure With Cylindrically-Shaped Regions”的美国临时专利申请序列号No.61/915,772的优先权和权益,该美国临时专利申请以整体引用的方式纳入本文。

### 技术领域

[0003] 本公开内容涉及制造在硅衬底中的半导体器件。更具体地,本发明涉及能够承受高电压的纵向场效应晶体管器件结构。

### 背景技术

[0004] 高电压场效应晶体管(HVFET)也被称作功率晶体管,在半导体领域是众所周知的。通常,HVFET包括纵向晶体管器件结构,该纵向晶体管器件结构包括一个延伸的漏极区域,当该器件处于“断开(off)”状态时该延伸的漏极区域支持施加的高电压。此类型的HVFET通常被用在功率转换应用中,诸如,用于离线电源、马达控制等的AC/DC转换器。这些功率晶体管器件可以在高电压下被切换,并能够在“断开”状态实现高阻塞电压,同时使得在“导通(on)”状态时漏极和源极之间的电流流动的阻力最小,该阻力通常被称作特定导通电阻( $R_{DSon}$ )。

### 发明内容

[0005] 根据本发明的第一方面,提供一种纵向功率晶体管器件,包括:

[0006] 第一导电类型的半导体层;

[0007] 多个圆柱形电介质区域,位于所述半导体层中,所述圆柱形电介质区域在纵向方向上从所述半导体层的顶部表面向下延伸,相邻的圆柱形电介质区域沿着一个公共直径轴线被所述半导体层的具有第一宽度的窄区域横向隔开;

[0008] 每个圆柱形电介质区域具有位于其中央的圆柱形导电场板构件,所述圆柱形导电场板构件在所述纵向方向上从所述顶部表面向下延伸至所述圆柱形电介质区域的底部附近,所述圆柱形电介质区域将所述圆柱形导电场板构件与所述窄区域横向隔开;

[0009] 所述第一导电类型的源极区域,位于所述窄区域的顶部表面处;以及

[0010] 所述第一导电类型的漏极区域,位于所述半导体层下方。

[0011] 根据本发明的第二方面,提供一种高电压晶体管,包括:

[0012] 一个衬底;

[0013] 一个阵列的圆柱形电介质区域,位于所述衬底中并被布置成三角形布局,每个圆柱形电介质区域在纵向方向上从所述半导体层的顶部表面向下延伸,相邻的圆柱形电介质区域沿着一个公共直径轴线被所述衬底的具有第一宽度的窄区域横向隔开;

[0014] 每个圆柱形电介质区域具有位于其中央的圆柱形导电场板构件,所述圆柱形导电场板构件在所述纵向方向上从所述顶部表面向下延伸至所述圆柱形电介质区域的底部附

近,所述圆柱形电介质区域将所述圆柱形导电场板构件与所述窄区域横向隔开;

[0015] 一个源极,位于所述窄区域的顶部表面处;以及

[0016] 一个漏极,位于所述衬底的底部处。

[0017] 根据本发明的第三方面,提供一种方法,包括:

[0018] 在第一导电类型的半导体衬底中形成被所述半导体衬底的窄区域横向隔开的多个第一圆柱形沟槽和多个第二圆柱形沟槽,每个所述圆柱形沟槽在纵向方向上从所述半导体衬底的顶部表面向下延伸;

[0019] 用电介质材料填充每个所述圆柱形沟槽的至少一部分;

[0020] 在所述第一圆柱形沟槽的所述电介质材料中形成导电材料的第一圆柱形场板,在所述第二圆柱形沟槽的所述电介质材料中形成导电材料的第二圆柱形场板,所述第一场板位于所述第一圆柱形沟槽中央,所述第二场板位于所述第二圆柱形沟槽中央,所述第一场板从所述半导体衬底的顶部表面附近纵向向下延伸到所述第一圆柱形沟槽的底部附近,所述第二场板从所述半导体衬底的顶部表面附近纵向向下延伸到所述第二圆柱形沟槽的底部附近;

[0021] 在所述窄区域的上部中形成源极区域和体区,所述源极区域是所述第一导电类型并且所述体区是所述第一导电类型相对 (opposite) 的第二导电类型,所述体区将所述源极与所述窄区域的下部隔开,所述窄区域的所述下部包括漂移区域;以及

[0022] 形成嵌入在所述电介质材料中、邻近所述体区的栅极,所述栅极与所述体区、所述第一场板和所述第二场板绝缘 (insulate)。

## 附图说明

[0023] 参照附图描述本发明的非限制性和非穷举性实施方案,其中,除非另有指定,否则在所有多种附图中相同的参考数字指代相同的部分。

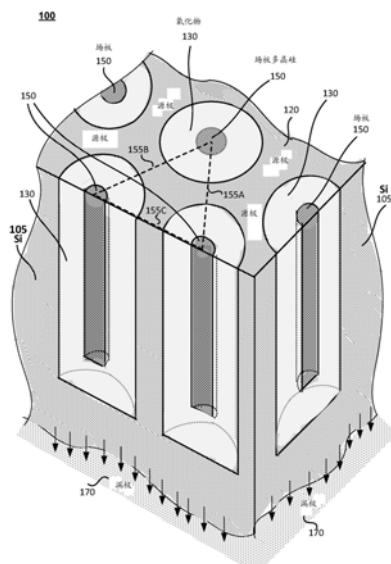

[0024] 图1是具有圆柱形区域的示例纵向晶体管器件结构的截面立体视图。

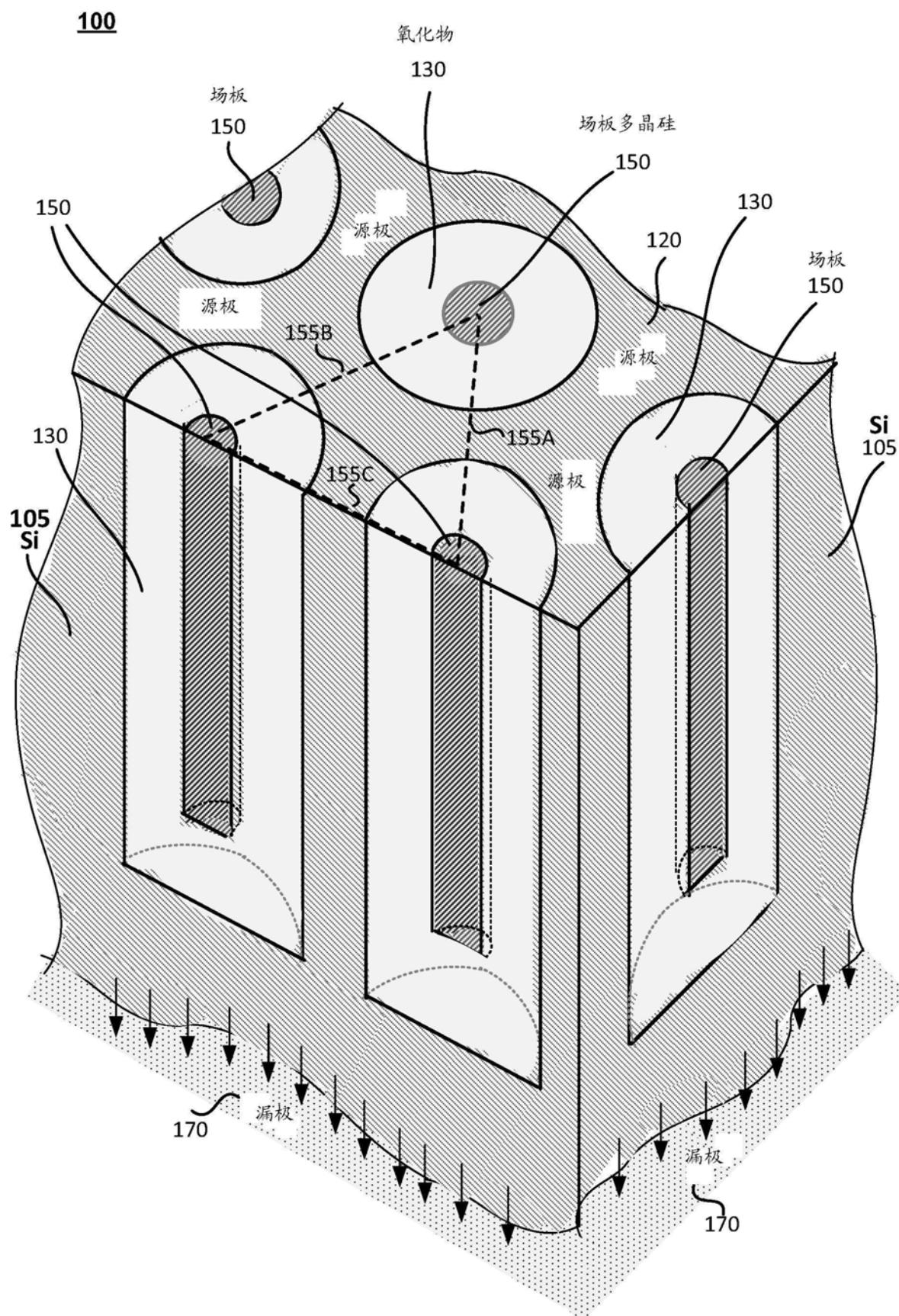

[0025] 图2是图1中示出的纵向晶体管器件结构的示例布局的俯视图。

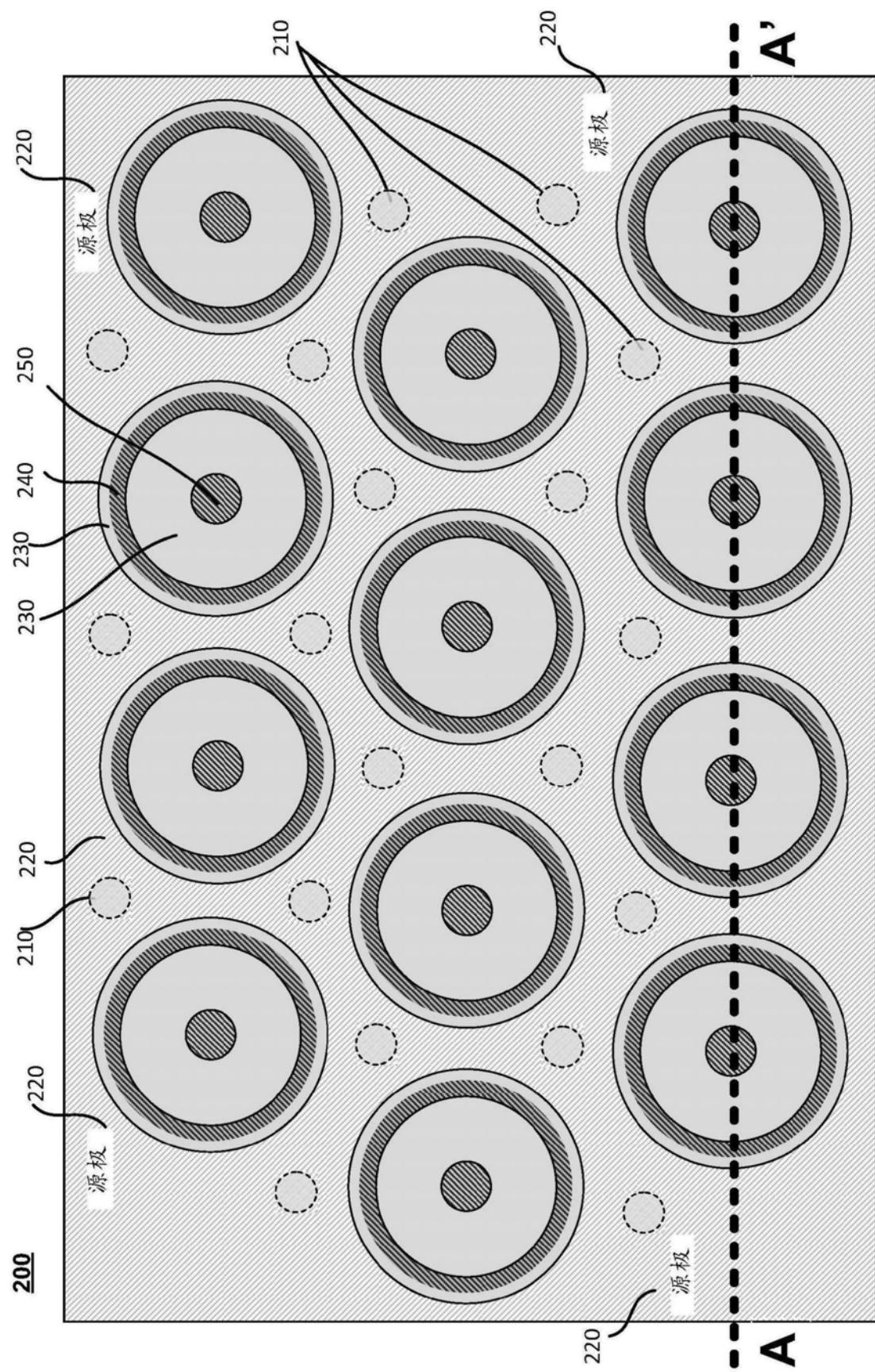

[0026] 图3A是沿切割线A-A' 截取的图2中示出的纵向晶体管器件结构布局的一个实施方案的示例截面侧视图。

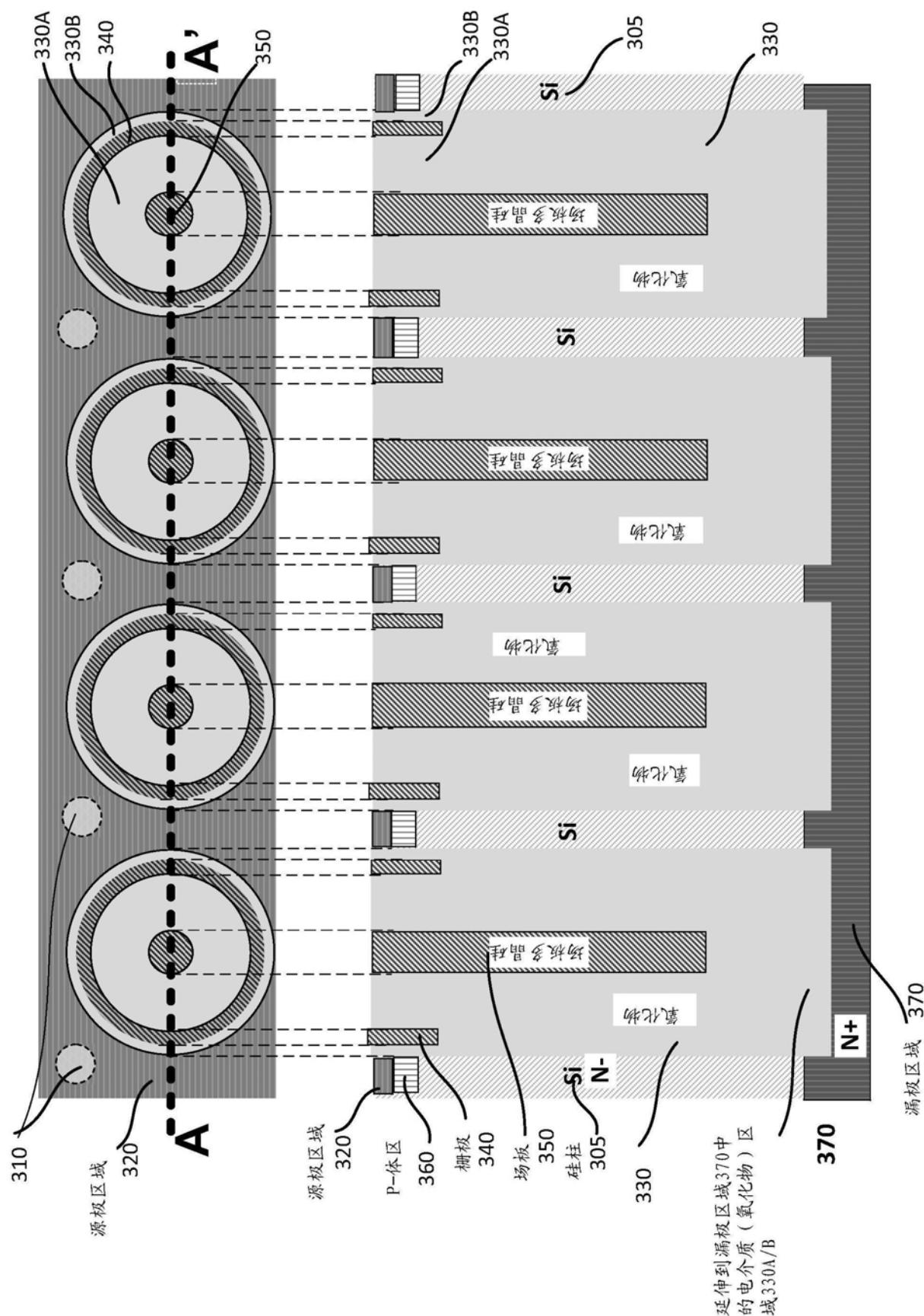

[0027] 图3B是沿切割线A-A' 截取的图2中示出的纵向晶体管器件结构布局的另一个实施方案的示例截面侧视图。

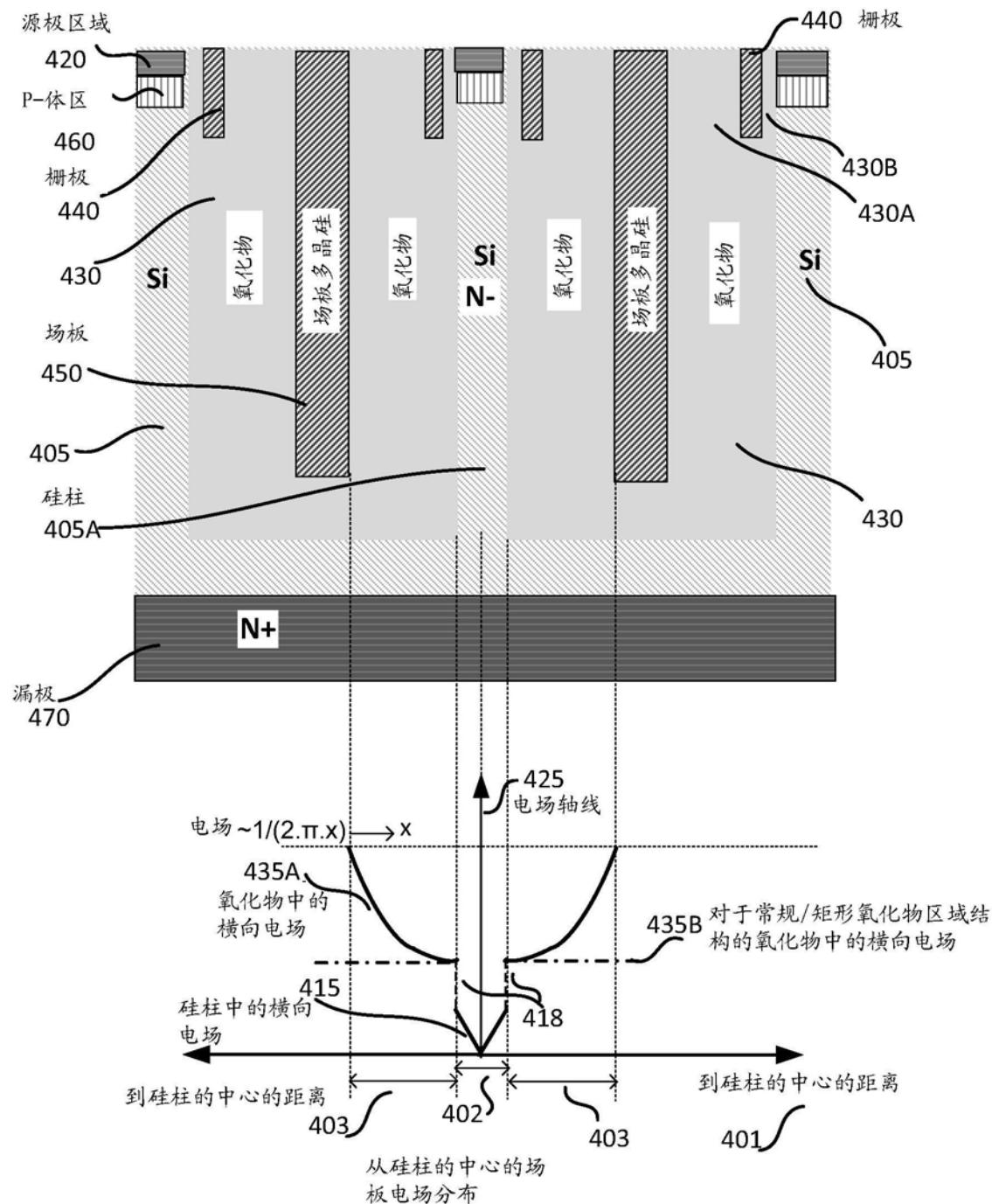

[0028] 图4是图3A的实施方案的截面侧视图,其中曲线图例示了器件的不同区域中的电场 (E场) 分布。

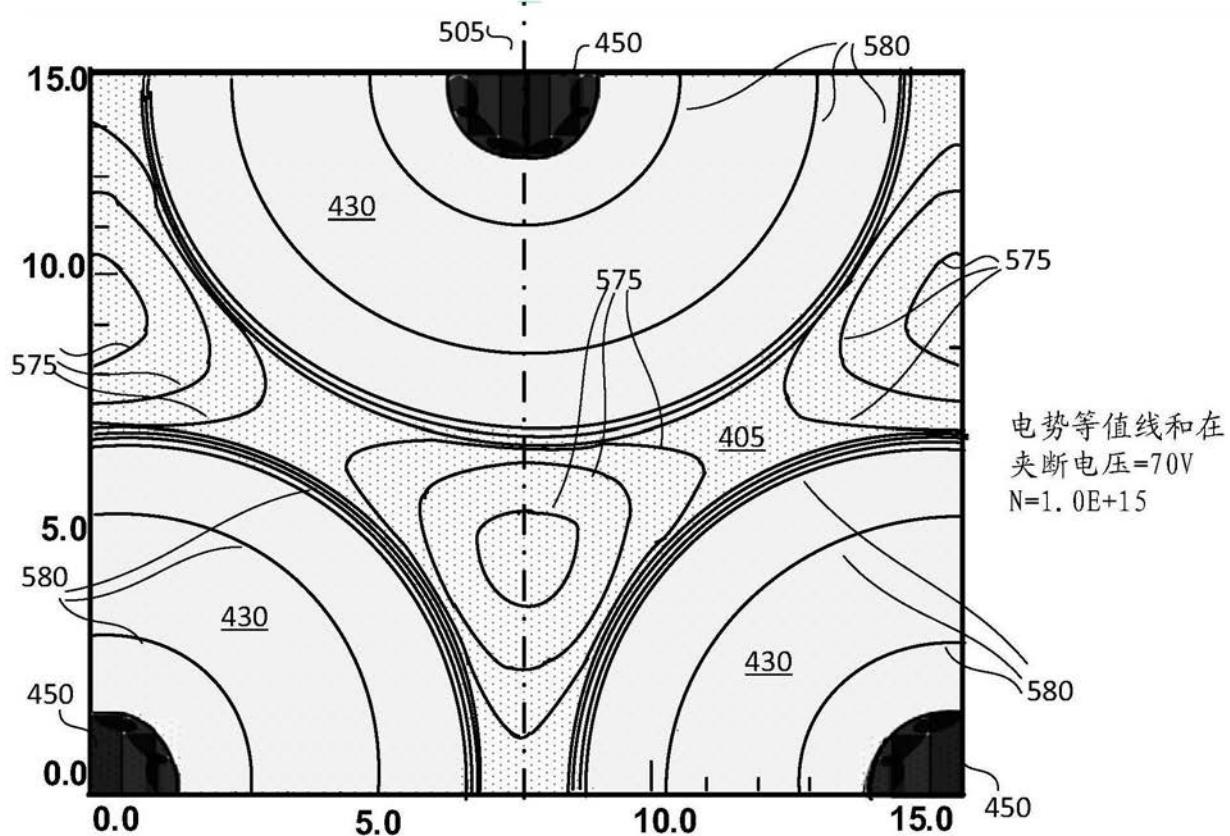

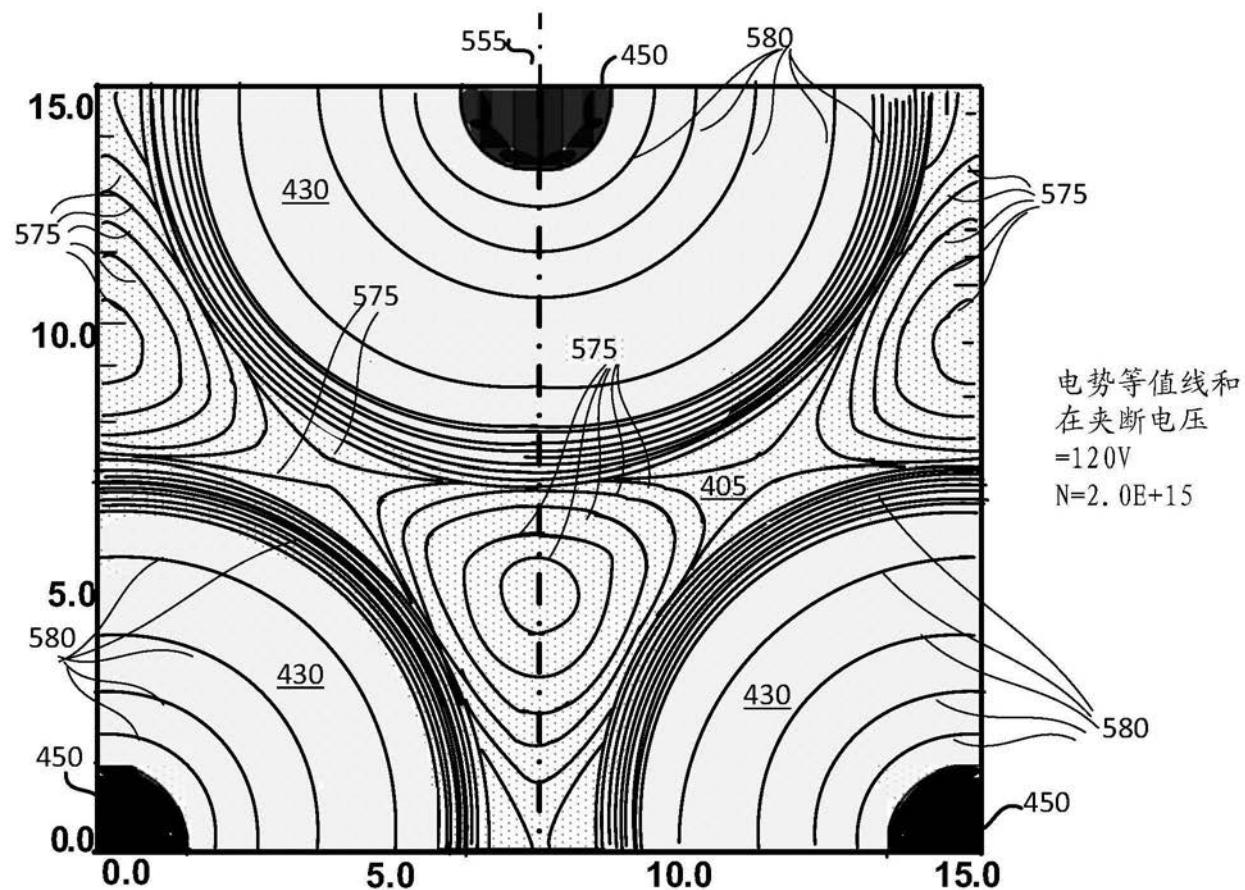

[0029] 图5A-图5B例示了一个仿真结果,该仿真结果示出对于一个示例纵向晶体管器件对于不同掺杂和电压条件,电势等值线与距离的关系。

[0030] 在附图的所有若干视图中,相应的参考字符指示相应的部件。本领域技术人员将理解,图中的元件是为了简化和清楚而例示的从而不必按比例绘制。例如,图中的某些元件的尺度相对于其它元件可能被夸大,以有助于更好地理解本发明的多种实施方案。另外,为了便于较少地遮挡本发明的这些多种实施方案的示图,通常不描绘出在商业上可行的实施方案中有用的或必需的通用但熟知的元件。

## 具体实施方式

[0031] 在下面的描述中阐述了许多具体的细节,以提供对本发明的透彻理解。然而,本领域的普通技术人员应明了,不需要采用具体细节来实践本发明。在其它实例中,为了避免模糊本发明,没有详细描述公知的系统、器件或方法。

[0032] 贯穿本说明书引用的“一个实施方案”、“一实施方案”、“一个实施例”或者“一实施例”意味着针对该实施方案或实施例描述的具体特征、结构或者特性包括在本发明的至少一个实施方案中。因此,在贯穿本说明书的各个位置出现的措辞“在一个实施方案中”、“在一实施方案中”、“一个实施例”或“一实施例”未必全部指的是相同的实施方案或实施例。此外,所述具体特征、结构或特性可以通过任何合适的组合和/或子组合被合并在一个或多个实施方案或实施例中。特定特征、结构或特性可被包括在集成电路、电子电路、组合逻辑电路或提供描述的功能的其它合适的部件中。另外,应理解,随此提供的附图用于向本领域普通技术人员进行解释的目的,并且所述附图未必按比例绘制。

[0033] 出于本公开内容的目的,“接地”或“接地电势”指的是参考电压或参考电势,相对于该参考电压或参考电势来限定或测量电路或集成电路(IC)的所有其它电压或电势。

[0034] 描述了具有圆柱形区域的纵向功率晶体管器件结构。该纵向功率晶体管器件结构具有低的特定导通状态电阻并且在断开状态时支持高电压。在其它实施方案中,相同的器件结构和布局可被用于实现各种不同的器件,包括P-N二极管、高电压肖特基二极管、结型场效应晶体管(JFET)、绝缘栅双极型晶体管(IGBT)等。

[0035] 该高电压纵向功率晶体管可利用场板,该场板有助于重新成形中央半导体柱或台面周围的电场从而增大击穿电压。在本申请中描述的纵向功率晶体管器件中的不同区域的圆柱形结构允许具有增加的电压额定值的紧凑尺寸和对硅体积的有效利用。

[0036] 图1是具有圆柱形区域的纵向晶体管器件100的示例截面立体视图。图1的纵向晶体管器件结构包括位于半导体层105(例如,硅)中的多个圆柱形电介质区域130(例如,氧化物),在一个实施方案中半导体层105包括n型外延层。位于每个区域130(例如,氧化物电介质区域)中央并且与半导体层105完全绝缘的是圆柱形导电场板构件150,在一个实施方案中,圆柱形导电场板构件150包括多晶硅。应注意,圆柱形电介质区域130被布置成由相互偏移的相邻行组成的布局,使得在沿着区域130的电介质材料和层105的半导体材料之间的侧壁界面的所有点处,任何两个相邻的圆柱形电介质区域130之间的横向距离是相等的,如通过虚线155A、155B和155C的相等长度所例示的。

[0037] 如图1中示出的,圆柱形电介质区域130在纵向方向上从半导体层105的顶部表面朝向衬底(未示出)向下延伸。圆柱形电介质区域130的相邻的圆柱形电介质区域沿着一个公共直径轴线(common diametrical axis)被半导体层105的窄区域横向隔开。隔开每对相邻的电介质区域130的该窄区域的横向宽度在沿着纵向向下延伸的氧化物-硅界面的所有点处是恒定的。在一个实施方案中,此窄区域包括由外延工艺形成的纵向功率场效应晶体管的延伸的漏极或漂移区域。漂移区域、电介质层130和场板构件150共同包括在横向方向上延伸的一个平行分层结构,该横向方向垂直于在导通状态时电流流动的方向。

[0038] 应注意,在图1中示出的器件结构100中,任意三个最近的横向相邻的电介质区域130包括三个一组的圆柱形电介质区域,即,任意三个最近的圆柱形电介质区域130的布局被布置成三角形图案。图1以从三个最近的场板构件150的中心连接的、形成等边三角形的

相等长度虚线155A、155B和155C示出了此三角形布局布置。

[0039] 在一个实施方案中,通过首先将深沟槽蚀刻到半导体层105中可形成每个圆柱形电介质区域130。然后用电介质材料(例如,二氧化硅)填充所述沟槽。通过类似的掩模、蚀刻和填充步骤可形成圆柱形场板构件150。在图1的实施例中,MOSFET器件源极电极可位于半导体层105的顶部表面上,并且漏极电极可位于半导体层105的底部表面上。

[0040] 图2是图1中示出的纵向晶体管器件结构的示例布局200的俯视图。在此视图中,一个阵列的圆柱形电介质区域230以偏移行的方式布置在半导体层(例如,硅)的顶部表面(源极)220范围内。圆柱形场板构件250位于每个圆柱形电介质区域230的中心。布局200还示出每个圆柱形电介质区域230还包括位于其中的沟槽中、在半导体材料和圆柱形导电场板构件250之间的横向延伸的环形栅极构件240。薄栅极氧化物将栅极构件240与半导体层的顶部表面220隔开。

[0041] 本领域技术人员应理解,在不同的实施方案中,栅极构件240可以是形成在顶部表面220的多个部分上的平面栅极构件,该平面栅极构件具有将每个栅极构件240与半导体层隔开的薄的电介质层(例如,二氧化硅)。

[0042] 如图2中示出的,在每三个相邻的圆柱形电介质区域230之间形成一个相对大的硅区域(虚线210所标注)。每个定位在内部的圆柱形电介质区域230被六个其它圆柱形电介质区域230和绕着每个圆柱形电介质区域230位于不同横向方向上的六个窄导电沟道所围绕。在某些实施方案中,由虚线210标示的硅区域可被蚀刻成沟槽并被填充有电介质材料(例如,氧化物、氮化物等)。这些附加的填充有电介质的沟槽可以是圆柱形形状,从顶部表面220纵向向下延伸到体半导体层材料(例如,硅)的部分深度内。

[0043] 图3A是图2中示出的纵向晶体管器件结构布局的一个实施方案的示例截面侧视图,该侧视图是沿单行圆柱形电介质区域330的切割线A-A'截取的。在此实施例中,每个栅极构件340均被示为沟槽栅极构件,该沟槽栅极构件在纵向方向上从电介质材料(氧化物)的顶部表面向下延伸到恰在横向相邻的p型体区(body region)360的底部下方的深度。每个体区360位于N+源极区域(顶部表面)320下方。体区360因此将源极区域320与硅柱(silicon pillar)305的延伸的漏极或漂移区域纵向隔开。在示出的实施方案中,示出了电介质区域330,该电介质区域包括将栅极构件340与场板构件350隔开的相对厚的内部电介质区域330A以及使得每个栅极构件340(例如,多晶硅)与包括源极区域320、P体区360和柱305的半导体材料充分绝缘的相对薄的层(例如,氧化物)330B。

[0044] 在图3A中,导电场板构件350位于圆柱形电介质区域330的中心的中央。环形栅极构件340位于半导体材料(区域320、360和305)和圆柱形场板构件350之间的电介质区域330中。如示出的,通过在每个电介质区域330下方横向延伸的硅材料连接硅柱305。N+掺杂的漏极区域370位于硅柱305的底部下方。在某些实施方案中,通过分级外延工艺形成硅柱中的掺杂浓度,使得漂移区域中的掺杂浓度随着从恰在体区360下方下降到靠近N+掺杂漏极区域370的纵向深度而增加。

[0045] 在图3A中示出的纵向功率晶体管的正常导通状态操作期间,控制信号被施加到栅极构件340。作为响应,沿着P体区360的侧部形成纵向导电沟道区域,使得电流从源极区域320向下流动经过沿着P体区360的侧部形成的导电沟道区域,经过硅柱305的N型漂移区域到达N+漏极区域370。漏极电极(未示出)可被形成在漏极区域370的底部上。

[0046] 在纵向晶体管技术状态中,高电压(例如,100V-1200V)通常被施加在相应的漏极区域370和源极区域320的两端。(源极区域320和场板构件350通常接地。)随着电压增加,窄漂移区域305的相对侧上的场板区域350的存在引起N型漂移区域耗尽自由载流子。

[0047] 图3B是沿切割线A-A'截取的图2中示出的纵向晶体管器件结构布局的另一个实施方案的示例截面侧视图。图3B的实施方案是与图3A中示出的实施方案大体上相同,除了图3B中每个圆柱形电介质区域330中向下延伸到下方漏极区域370中。

[0048] 在又另一个实施方案中,漏极区域370可位于P型衬底的顶部上。

[0049] 半导体领域的从业者应理解,相比于常规纵向晶体管结构,本文所描述的纵向晶体管器件结构改进了器件性能。原因是因为在器件击穿期间,击穿电压主要是由电介质(氧化物)层所支持的电压来确定的。本文所公开的纵向晶体管器件结构中的硅-氧化物-多晶硅场板的圆柱形状实现了沿着氧化物的更高的电场。这很大程度上是由于在全部横向方向上和沿着圆柱形电介质区域的电场的对称和均匀分布。因此,本文所描述的晶体管器件结构用较小尺度和较小体积的电介质(氧化物)材料实现了较高的击穿电压。

[0050] 图4示出图3A的实施方案的截面侧视图,其中曲线图(在器件结构下面)例示了该器件的多个区域中的电场(E场)分布。在图4中,通过线435A示出电介质区域430中的横向电场强度。线435A示出电场(E场)变化/减少相对于沿着从场板朝向硅柱405A的边界的径向方向距离场板的径向距离[ $E \sim 1/(2\pi x)$ ]的相反趋势。此相反趋势是由于场线朝向圆柱形电介质区域430的横向边界向外扩大。该变化通过图4中的曲线435A示出,对比了由直线435B示出的常规/矩形氧化物区域结构中的横向E场。

[0051] 线性线415示出了硅柱405A中的横向电场强度(在E场轴线4 25上)的变化。应注意,在柱405A和电介质区域430之间的界面处的E场的电场强度示出值的跳变418。参考数字402指示硅柱405A的窄区域的宽度,而参考数字403指示硅柱405A和场板构件(多晶硅)450之间的距离。在一个实施方案中,圆柱形电介质区域430被隔开约1.5微米的横向距离402,具有约5.5微米的横向氧化物厚度403。

[0052] 半导体领域的从业者还应理解,本文所公开的新型纵向器件结构用相同击穿电压支持更高的电场;或,换言之,相同的电场可用更薄的横向氧化物厚度403来实现。这意味着纵向晶体管器件结构可用更少的氧化物面积实现更好的器件性能。更少的氧化物面积转化成更多的硅面积,因此与现有技术的纵向晶体管器件布局相比减小了 $R_{dson}$ 。此外,由于实现相同的高击穿电压所需要的氧化物更薄,因此与常规纵向功率晶体管器件相比,明显减少和简化了制造本文所描述的纵向器件结构所需要的工艺。

[0053] 图5A-图5B例示了示出对于具有圆柱形结构且在半导体柱中具有分级掺杂的示例纵向晶体管器件的电势等值线与距离的关系的仿真结果,其中,漂移区域中的杂质的掺杂浓度随着从恰在体区下方朝向底部漏极区域(N+衬底)下降的纵向深度而逐渐变化(增加)。图5A和图5B的二维图各自展示了在充分耗尽具有多数载流子的截面的夹断电压下,在特定纵向深度和特定掺杂浓度下的特定横向截面中的电势等值线。在绘制的仿真结果中未示出电场线但可从示出的电势等值线计算出横向电场,并且可从夹断电压和每个截面的纵向位置计算出纵向电场。应注意,示出的仿真结果是针对如下一个布局,即其中圆柱形电介质区域被隔开约1.5微米的横向距离402,具有约5.5微米的横向氧化物厚度403(见图4)。在图5A的示例仿真结果中,示出硅柱/漂移区域405具有大约 $1 \times 10^{15}/\text{cm}^3$ 的掺杂浓度,70V的夹断电

压。图5B示出对于大约 $2 \times 10^{15}/\text{cm}^3$ 的掺杂浓度、120V的夹断电压的示例仿真结果。在一个实施方案中,漂移区域中的掺杂浓度作为从靠近体区向下到靠近N+漏极区域的纵向深度的函数而变化。在特定的实施方案中,掺杂浓度从靠近漂移区域顶部大约 $1 \times 10^{15}/\text{cm}^3$ 变化到靠近漂移区域底部大约 $1 \times 10^{17}/\text{cm}^3$ ,其中夹断电压从70V变化到810V。

[0054] 图5A和图5B的二维图中各自例示了对于如下纵向器件的电势等值线,该纵向器件在硅柱/漂移区域405的特定纵向深度处的特定横向截面中具有分级掺杂,并且在充分耗尽具有多数载流子的截面的夹断电压下具有特定掺杂浓度。在图5A中,场板构件450以三个一组的布置位于电介质区域430的中央。圆形图案线580示出每个圆柱形场板构件450周围的电势等值线和每个圆柱形电介质区域430内部的电势等值线。在硅区域附近看到电介质区域430中的较高密度的电势等值线580。电势等值线575在将每个电介质区域430隔开的硅柱/漂移区域405的内部。

[0055] 图5B示出在纵向深度具有分级掺杂的纵向器件的不同横向截面处的类似的仿真结果,其中,掺杂浓度是 $2 \times 10^{15}/\text{cm}^3$ ,夹断电压水平是120V。三个圆柱形场板构件450是对称三角形布置。圆形电势等值线580示出每个圆柱形场板构件450周围的电介质区域430中的电势等值线。与图5A的仿真结果比较,图5B中的电势等值线580示出电介质区域430内的更高的密度。电势等值线575在硅柱/漂移区域405的内部并由于三个相邻圆柱形场板和电介质区域的电场的对称效应而形成。电势等值线575示出了三个相邻圆柱形场板构件450和电介质区域430的关于图5A中的中央轴线505的对称图案和关于图5B中的中央轴线555的对称图案。

[0056] 例示的示例实施方案的上述描述,包括摘要中所描述的内容,不旨在穷举或限制到所公开的精确形式或结构。虽然本文描述的主题的特定实施方案和实施例是出于例示目的,但是在不脱离本发明的精神和范围的前提下,多种等同的改型是可能的。实际上,应理解,出于解释的目的提供特定示例厚度、材料类型、浓度、电压等并且在根据本发明的教导的其它实施方案和实施例中还可采用其它的值。

图1

图2

图3A

图3B

图4

图5A

图5B