(19)日本国特許庁(JP)

**(12)特許公報(B2)**

(11)特許番号

**特許第7638418号**

**(P7638418)**

(45)発行日 令和7年3月3日(2025.3.3)

(24)登録日 令和7年2月20日(2025.2.20)

(51)国際特許分類

|         |                 |     |         |       |         |

|---------|-----------------|-----|---------|-------|---------|

| H 1 0 D | 30/67 (2025.01) | F I | H 1 0 D | 30/67 | 1 0 4   |

| H 1 0 D | 86/40 (2025.01) |     | H 1 0 D | 86/40 | 1 0 1 B |

| H 1 0 B | 12/00 (2023.01) |     | H 1 0 D | 30/67 | 1 0 3 B |

|         |                 |     | H 1 0 D | 30/67 | 2 0 6 C |

|         |                 |     | H 1 0 B | 12/00 | 6 7 1 Z |

請求項の数 4 (全121頁) 最終頁に続く

|                   |                                    |          |                    |

|-------------------|------------------------------------|----------|--------------------|

| (21)出願番号          | 特願2024-62875(P2024-62875)          | (73)特許権者 | 000153878          |

| (22)出願日           | 令和6年4月9日(2024.4.9)                 |          | 株式会社半導体エネルギー研究所    |

| (62)分割の表示         | 特願2019-235990(P2019-235990)<br>の分割 |          | 神奈川県厚木市長谷398番地     |

| 原出願日              | 令和1年12月26日(2019.12.26)             | (72)発明者  | 山崎 舜平              |

| (65)公開番号          | 特開2024-91711(P2024-91711A)         |          | 神奈川県厚木市長谷398番地 株式会 |

| (43)公開日           | 令和6年7月5日(2024.7.5)                 | (72)発明者  | 社半導体エネルギー研究所内      |

| 審査請求日             | 令和6年5月8日(2024.5.8)                 |          | 山口 大裕              |

| (31)優先権主張番号       | 特願2018-248150(P2018-248150)        | (72)発明者  | 神奈川県厚木市長谷398番地 株式会 |

| (32)優先日           | 平成30年12月28日(2018.12.28)            |          | 社半導体エネルギー研究所内      |

| (33)優先権主張国・地域又は機関 | 日本国(JP)                            | (72)発明者  | 川口 忍               |

| (31)優先権主張番号       | 特願2019-11158(P2019-11158)          |          | 神奈川県厚木市長谷398番地 株式会 |

| (32)優先日           | 平成31年1月25日(2019.1.25)              | (72)発明者  | 社半導体エネルギー研究所内      |

| (33)優先権主張国・地域又は機関 |                                    |          | 最終頁に続く             |

(54)【発明の名称】 半導体装置

**(57)【特許請求の範囲】****【請求項1】**

基板上の第1の絶縁層と、

前記第1の絶縁層上の第2の絶縁層と、

前記第2の絶縁層上の第1の酸化物層と、

前記第1の酸化物層の上方に位置する第1の導電層と、

前記第1の酸化物層の上方に位置する第2の導電層と、

前記第1の酸化物層上に位置し、かつ前記第1の導電層の側面に接する領域を有する第2の酸化物層と、

前記第2の導電層の上面に接する第3の絶縁層と、

前記第1の絶縁層の上面に接する領域と、前記第2の絶縁層の側面と接する領域と、前記第3の絶縁層の側面と接する領域と、を有する第4の絶縁層を有する、半導体装置。

**【請求項2】**

基板上の第1の絶縁層と、

前記第1の絶縁層上の第2の絶縁層と、

前記第2の絶縁層上の第1の酸化物層と、

前記第1の酸化物層の上方に位置する第1の導電層と、

前記第1の酸化物層の上方に位置する第2の導電層と、

前記第1の酸化物層上に位置し、かつ前記第1の導電層の側面に接する領域を有する第2の酸化物層と、

前記第2の導電層の上面に接する第3の絶縁層と、

開口領域と、を有し、

前記開口領域は、

前記第2の酸化物層と、前記第2の導電層と、を有し、

前記第1の絶縁層の上面に接する領域と、前記第2の絶縁層の側面と接する領域と、前記第3の絶縁層の側面と接する領域と、を有する第4の絶縁層を有する、半導体装置。

**【請求項3】**

請求項1または2において、

前記第3の絶縁層と前記第4の絶縁層を覆う領域を有し、かつ前記第1の絶縁層の上面に接して設けられた第5の絶縁層を有する、半導体装置。

10

**【請求項4】**

請求項1乃至請求項3のいずれか一項において、

前記第1の酸化物層と前記第1の導電層の間に設けられた第6の絶縁層を有する、半導体装置。

**【発明の詳細な説明】**

**【技術分野】**

**【0001】**

本発明の一態様は、半導体装置、ならびに半導体装置の作製方法に関する。または、本発明の一態様は、半導体ウエハ、モジュール、および電子機器に関する。

**【0002】**

なお、本明細書等において半導体装置とは、半導体特性を利用することで機能し得る装置全般を指す。トランジスタなどの半導体素子をはじめ、半導体回路、演算装置、記憶装置は、半導体装置の一態様である。表示装置（液晶表示装置、発光表示装置など）、投影装置、照明装置、電気光学装置、蓄電装置、記憶装置、半導体回路、撮像装置、および電子機器などは、半導体装置を有すると言える場合がある。

20

**【0003】**

なお、本発明の一態様は、上記の技術分野に限定されない。本明細書等で開示する発明の一態様は、物、方法、または、製造方法に関するものである。または、本発明の一態様は、プロセス、マシン、マニュファクチャ、または、組成物（コンポジション・オブ・マター）に関するものである。

30

**【背景技術】**

**【0004】**

近年、半導体装置の開発が進められ、LSIやCPUやメモリが主に用いられている。CPUは、半導体ウエハから切り離された半導体集積回路（少なくともトランジスタ及びメモリ）を有し、接続端子である電極が形成された半導体素子の集合体である。

**【0005】**

LSIやCPUやメモリなどの半導体回路（ICチップ）は、回路基板、例えばプリント配線板に実装され、様々な電子機器の部品の一つとして用いられる。

**【0006】**

また、絶縁表面を有する基板上に形成された半導体薄膜を用いてトランジスタを構成する技術が注目されている。該トランジスタは集積回路（IC）や画像表示装置（単に表示装置とも表記する）のような電子デバイスに広く応用されている。トランジスタに適用可能な半導体薄膜としてシリコン系半導体材料が広く知られているが、その他の材料として酸化物半導体が注目されている。

40

**【0007】**

また、酸化物半導体を用いたトランジスタは、非導通状態において極めてリーク電流が小さいことが知られている。例えば、酸化物半導体を用いたトランジスタのリーク電流が低いという特性を応用した低消費電力のCPUなどが開示されている（特許文献1参照）。また、例えば、酸化物半導体を用いたトランジスタのリーク電流が低いという特性を応用して、長期にわたり記憶内容を保持することができる記憶装置などが、開示されてい

50

る（特許文献 2 参照。）。

【0008】

また、近年では電子機器の小型化、軽量化に伴い、集積回路のさらなる高密度化への要求が高まっている。また、集積回路を含む半導体装置の生産性の向上が求められている。

【先行技術文献】

【特許文献】

【0009】

【文献】特開 2012-257187 号公報

【文献】特開 2011-151383 号公報

【発明の概要】

【発明が解決しようとする課題】

【0010】

本発明の一態様は、良好な電気特性を有する半導体装置を提供することを課題の一つとする。または、本発明の一態様は、ノーマリーオフの電気特性を有する半導体装置を提供することを課題の一つとする。または、本発明の一態様は、信頼性が良好な半導体装置を提供することを課題の一つとする。または、本発明の一態様は、オン電流が大きい半導体装置を提供することを課題の一つとする。または、本発明の一態様は、高い周波数特性を有する半導体装置を提供することを課題の一つとする。または、本発明の一態様は、微細化または高集積化が可能な半導体装置を提供することを課題の一つとする。または、本発明の一態様は、生産性の高い半導体装置を提供することを課題の一つとする。

【0011】

本発明の一態様は、長期間においてデータの保持が可能な半導体装置を提供することを課題の一つとする。本発明の一態様は、情報の書き込み速度が速い半導体装置を提供することを課題の一つとする。本発明の一態様は、設計自由度が高い半導体装置を提供することを課題の一つとする。本発明の一態様は、消費電力を抑えることができる半導体装置を提供することを課題の一つとする。本発明の一態様は、新規な半導体装置を提供することを課題の一つとする。

【0012】

なお、これらの課題の記載は、他の課題の存在を妨げるものではない。なお、本発明の一態様は、これらの課題の全てを解決する必要はないものとする。なお、これら以外の課題は、明細書、図面、請求項などの記載から、自ずと明らかとなるものであり、明細書、図面、請求項などの記載から、これら以外の課題を抽出することが可能である。

【課題を解決するための手段】

【0013】

本発明の一態様は、酸化物半導体と、酸化物半導体と接する第1の絶縁体と、第1の絶縁体と接する第2の絶縁体とを有し、第1の絶縁体は過剰酸素を有し、第2の絶縁体は水素を捕獲、または固着する機能を有し、酸化物半導体中の水素は、過剰酸素と結合し、過剰酸素と結合した水素は、第1の絶縁体を経由し、第2の絶縁体に捕獲、または固着し、水素と結合した過剰酸素は、第1の絶縁体に過剰酸素として残存する半導体装置である。

【0014】

本発明の一態様は、酸化物半導体と、酸化物半導体と接する第1の絶縁体と、第1の絶縁体と接する第2の絶縁体と、第2の絶縁体と接する第3の絶縁体と、を有し、第1の絶縁体は過剰酸素を有し、第2の絶縁体は水素を捕獲、または固着する機能を有し、第3の絶縁体は水素に対するバリア性を有し、酸化物半導体中の水素は、過剰酸素と結合し、過剰酸素と結合した水素は、第1の絶縁体を経由し、第2の絶縁体に捕獲、または固着し、水素と結合した過剰酸素は、第1の絶縁体に過剰酸素として残存する半導体装置である。

【0015】

上記において、第3の絶縁体は、窒化シリコンを含む。

【0016】

上記において、第2の絶縁体は、酸化アルミニウムを含む。

10

20

30

40

50

**【 0 0 1 7 】**

上記において、酸化アルミニウムは、スパッタリング法により形成される。

**【 0 0 1 8 】**

上記において、酸化物半導体は、In - Ga - Zn酸化物である。

**【 0 0 1 9 】**

本発明の一態様は、上記に記載の半導体装置と、容量デバイスと、を有する、メモリデバイスである。

**【 発明の効果 】****【 0 0 2 0 】**

本発明の一態様により、良好な電気特性を有する半導体装置を提供することができる。

または、本発明の一態様により、ノーマリーオフの電気特性を有する半導体装置を提供する

ことができる。または、本発明の一態様により、信頼性が良好な半導体装置を提供する

ことができる。または、本発明の一態様により、オン電流が大きい半導体装置を提供する

ことができる。または、本発明の一態様により、高い周波数特性を有する半導体装置を提

供することができる。または、本発明の一態様により、微細化または高集積化が可能な半

導体装置を提供することができる。または、本発明の一態様により、生産性の高い半導体

装置を提供することができる。

10

**【 0 0 2 1 】**

または、長期間においてデータの保持が可能な半導体装置を提供することができる。また

は、データの書き込み速度が速い半導体装置を提供することができる。または、設計自

由度が高い半導体装置を提供することができる。または、消費電力を抑えることができる

半導体装置を提供することができる。または、新規な半導体装置を提供することができる

。

20

**【 0 0 2 2 】**

なお、これらの効果の記載は、他の効果の存在を妨げるものではない。なお、本発明の

一態様は、これらの効果の全てを有する必要はない。なお、これら以外の効果は、明細書

、図面、請求項などの記載から、自ずと明らかとなるものであり、明細書、図面、請求項

などの記載から、これら以外の効果を抽出することができる。

**【 図面の簡単な説明 】****【 0 0 2 3 】**

30

**【図1】**積層構造の断面図。

**【図2】**(A)乃至(B)絶縁体中の拡散モデルを説明する図。

**【図3】**(A)乃至(B)絶縁体中の拡散モデルを説明する図。

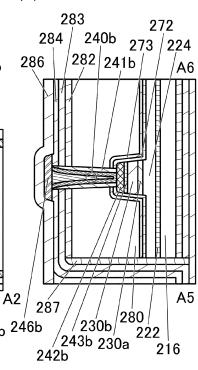

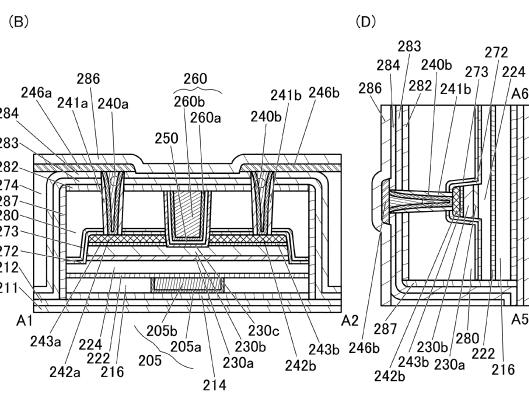

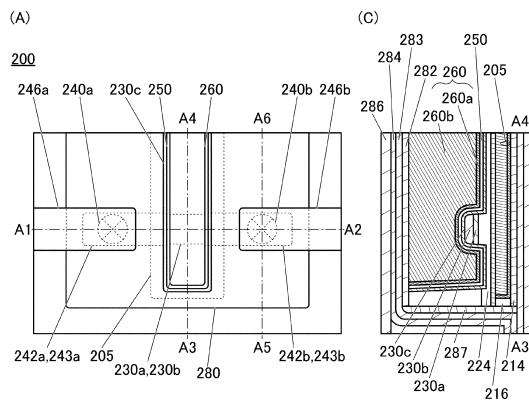

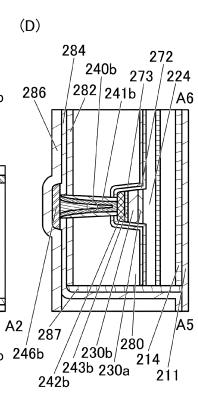

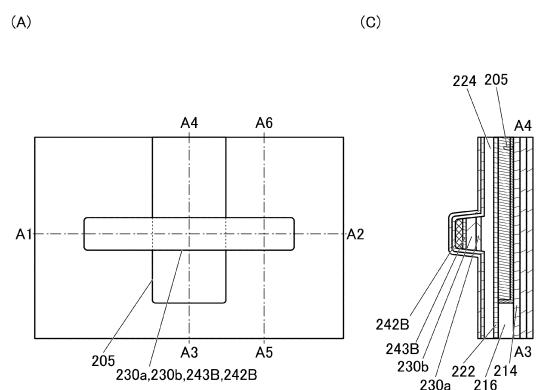

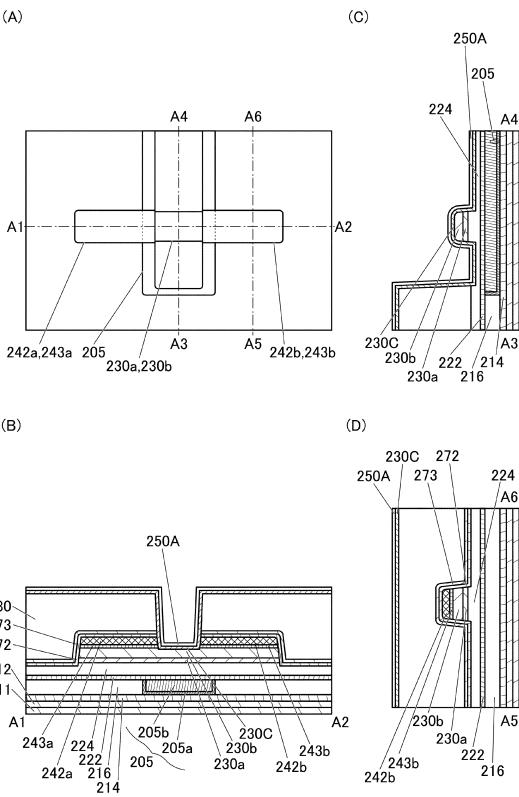

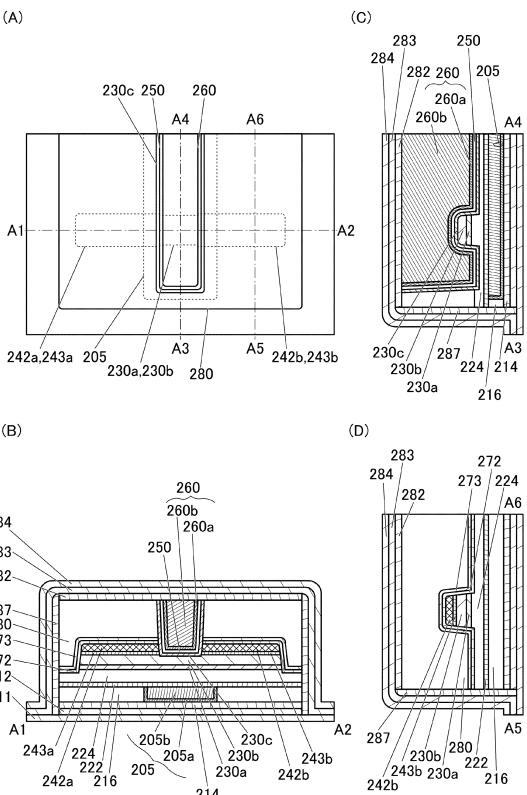

**【図4】**(A)半導体装置の上面図、(B)乃至(D)半導体装置の断面図。

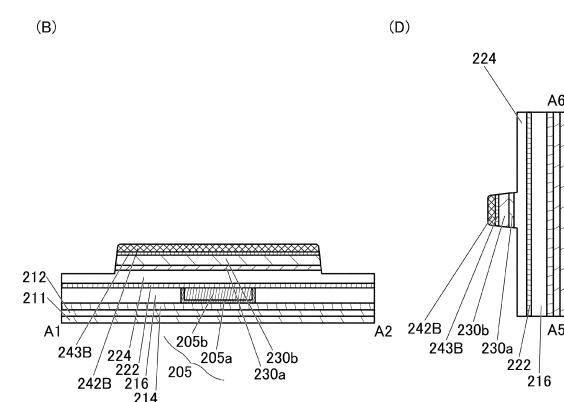

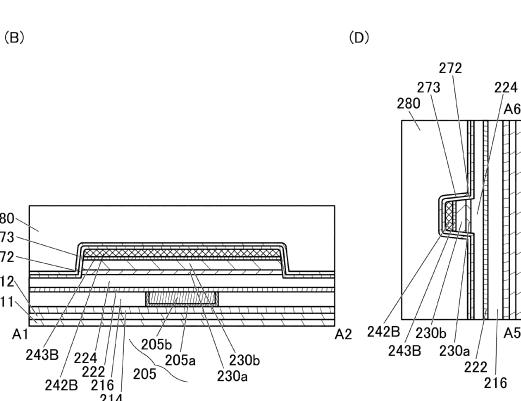

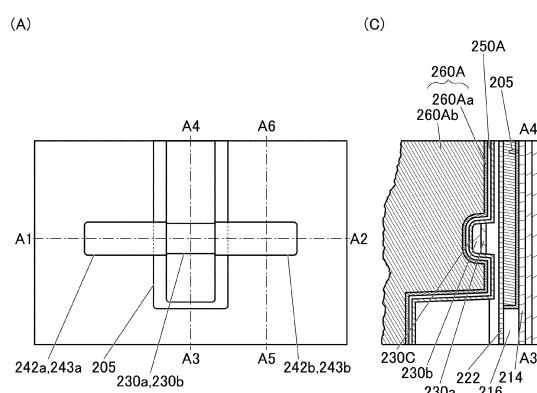

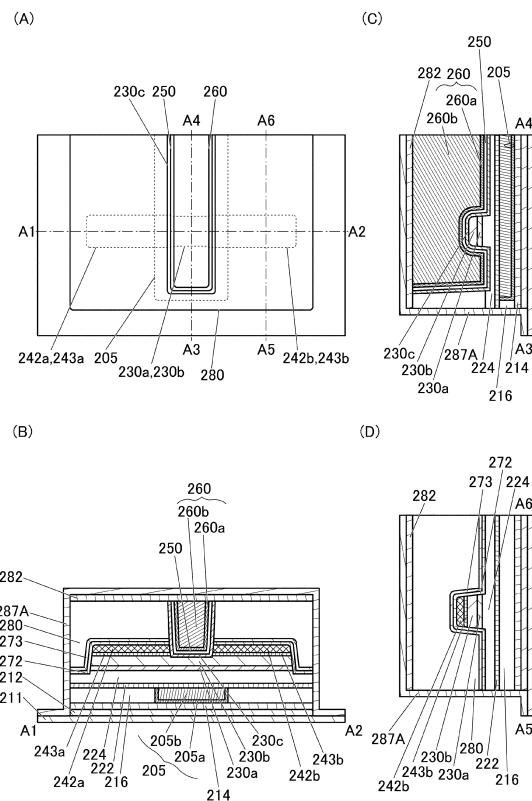

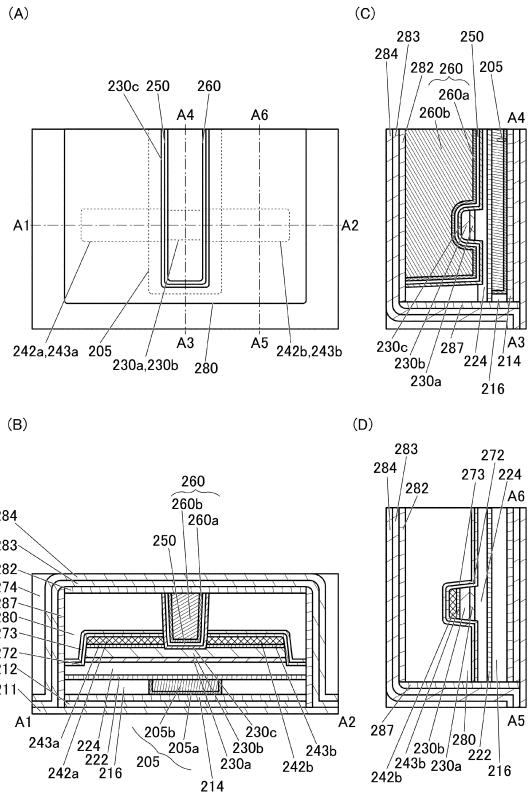

**【図5】**(A)半導体装置の上面図、(B)乃至(D)半導体装置の断面図。

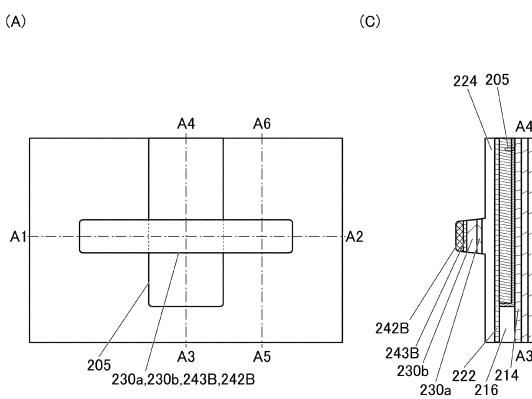

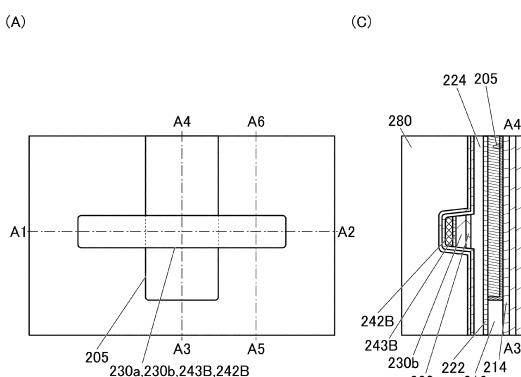

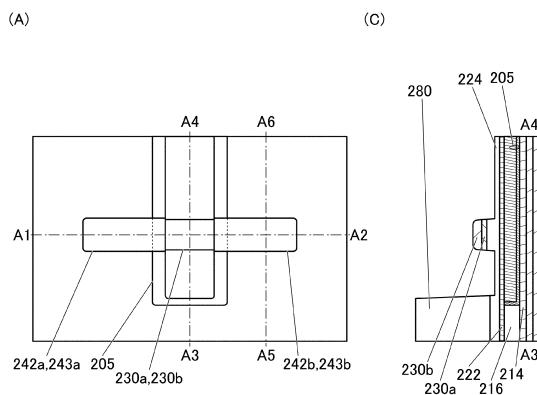

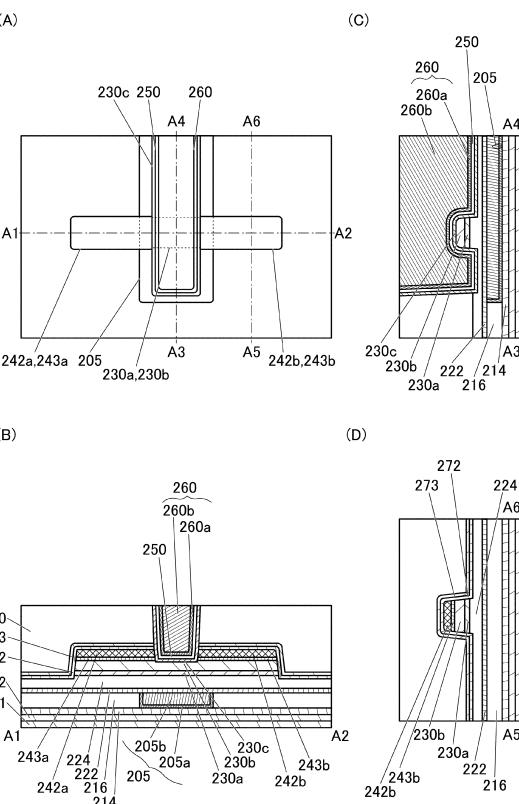

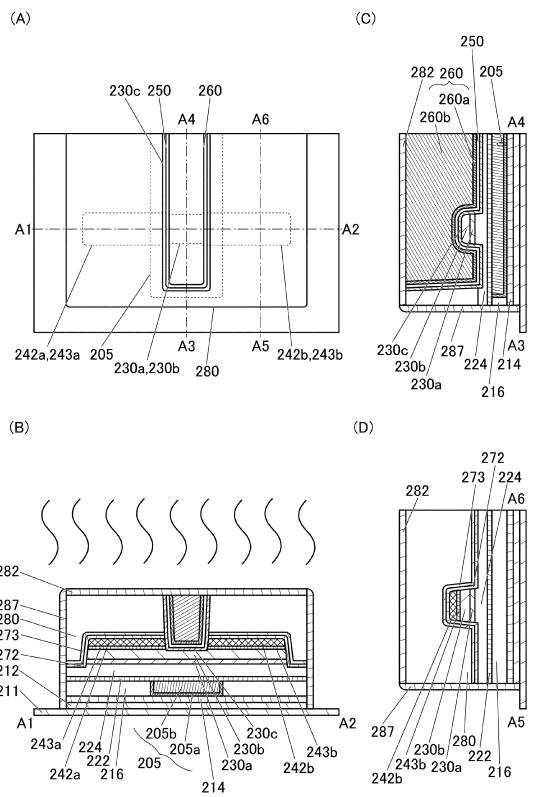

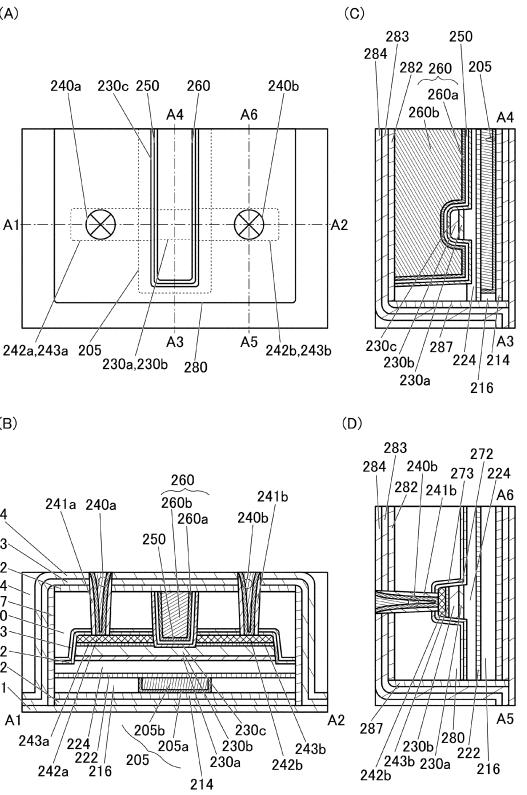

**【図6】**(A)半導体装置の上面図、(B)乃至(D)半導体装置の断面図。

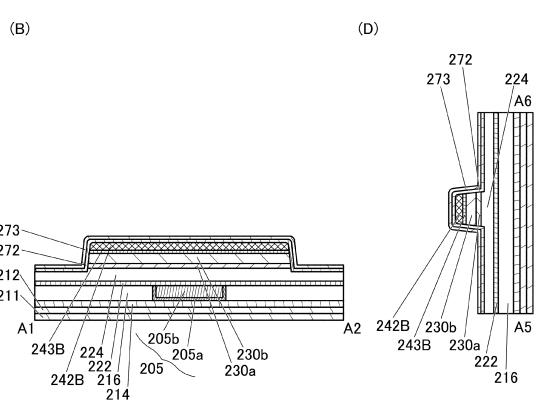

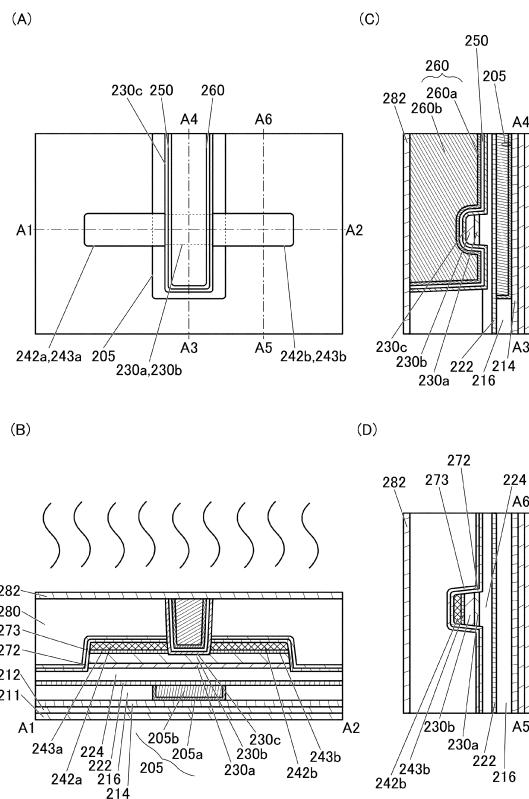

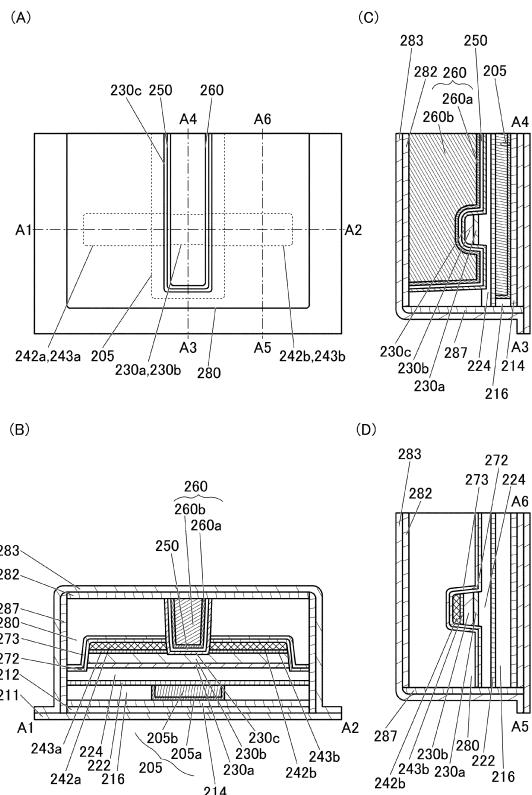

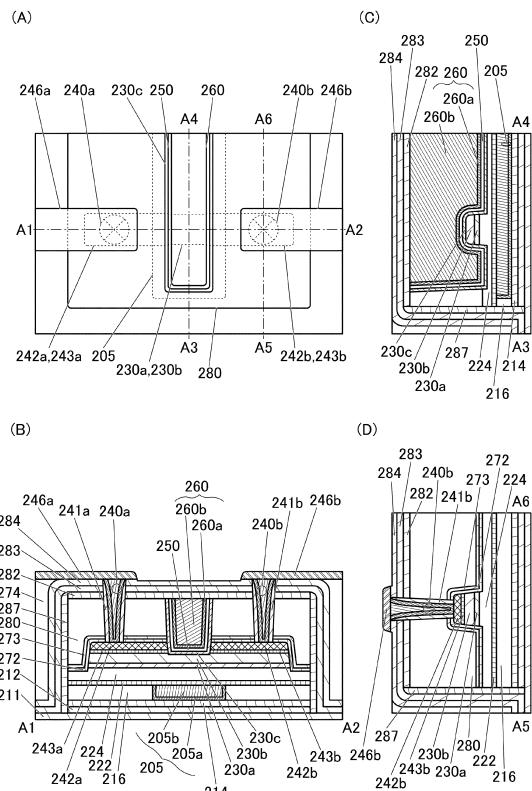

**【図7】**(A)半導体装置の作製方法を示す上面図、(B)乃至(D)半導体装置の作製

方法を示す断面図。

**【図8】**(A)半導体装置の作製方法を示す上面図、(B)乃至(D)半導体装置の作製

方法を示す断面図。

40

**【図9】**(A)半導体装置の作製方法を示す上面図、(B)乃至(D)半導体装置の作製

方法を示す断面図。

**【図10】**(A)半導体装置の作製方法を示す上面図、(B)乃至(D)半導体装置の作

製方法を示す断面図。

**【図11】**(A)半導体装置の作製方法を示す上面図、(B)乃至(D)半導体装置の作

製方法を示す断面図。

**【図12】**(A)半導体装置の作製方法を示す上面図、(B)乃至(D)半導体装置の作

製方法を示す断面図。

**【図13】**(A)半導体装置の作製方法を示す上面図、(B)乃至(D)半導体装置の作

製方法を示す断面図。

50

【図14】(A)半導体装置の作製方法を示す上面図、(B)乃至(D)半導体装置の作製方法を示す断面図。

【図15】(A)半導体装置の作製方法を示す上面図、(B)乃至(D)半導体装置の作製方法を示す断面図。

【図16】(A)半導体装置の作製方法を示す上面図、(B)乃至(D)半導体装置の作製方法を示す断面図。

【図17】(A)半導体装置の作製方法を示す上面図、(B)乃至(D)半導体装置の作製方法を示す断面図。

【図18】(A)半導体装置の作製方法を示す上面図、(B)乃至(D)半導体装置の作製方法を示す断面図。

10

【図19】(A)半導体装置の作製方法を示す上面図、(B)乃至(D)半導体装置の作製方法を示す断面図。

【図20】(A)半導体装置の作製方法を示す上面図、(B)乃至(D)半導体装置の作製方法を示す断面図。

【図21】(A)半導体装置の作製方法を示す上面図、(B)乃至(D)半導体装置の作製方法を示す断面図。

【図22】(A)半導体装置の作製方法を示す上面図、(B)乃至(D)半導体装置の作製方法を示す断面図。

【図23】(A)半導体装置の作製方法を示す上面図、(B)乃至(D)半導体装置の作製方法を示す断面図。

20

【図24】(A)乃至(B)半導体装置の断面図。

【図25】半導体装置の断面図。

【図26】(A)半導体装置の上面図、(B)半導体装置の断面図。

【図27】(A)乃至(B)半導体装置の断面図。

【図28】半導体装置の断面図。

【図29】半導体装置の断面図。

【図30】(A)乃至(B)半導体装置の断面図。

【図31】(A)IGZOの結晶構造の分類を説明する図、(B)石英ガラスのXRDスペクトルを説明する図、(C)結晶性IGZOのXRDスペクトルを説明する図。

30

【図32】記憶装置の構成を示す断面図。

【図33】記憶装置の構成を示す断面図。

【図34】記憶装置の構成を示す断面図。

【図35】記憶装置の構成を示す断面図。

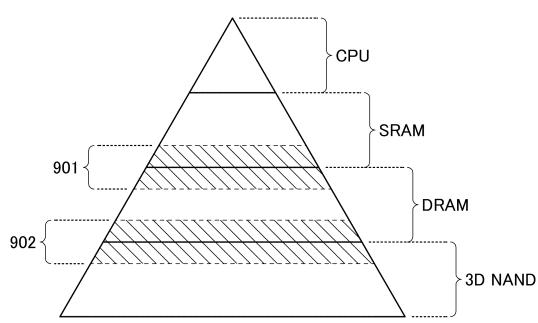

【図36】各種の記憶装置を階層ごとに示す図。

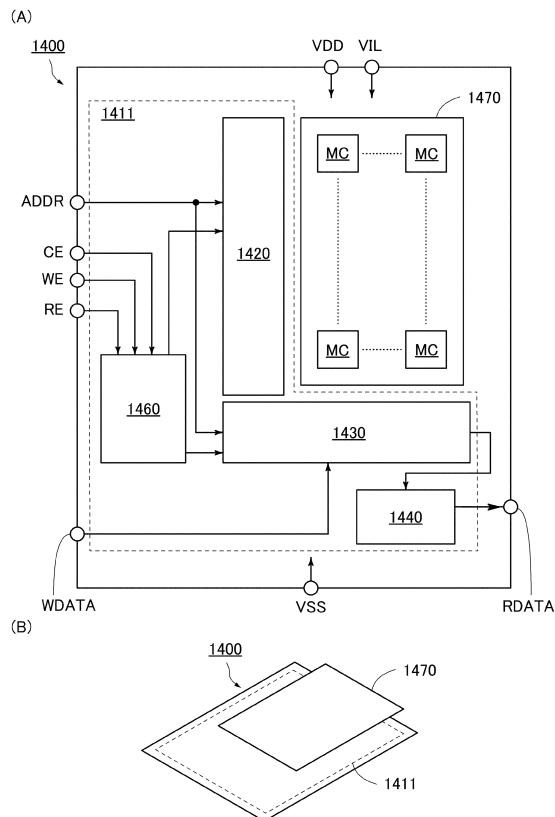

【図37】(A)乃至(B)記憶装置の構成例を示すブロック図および斜視図。

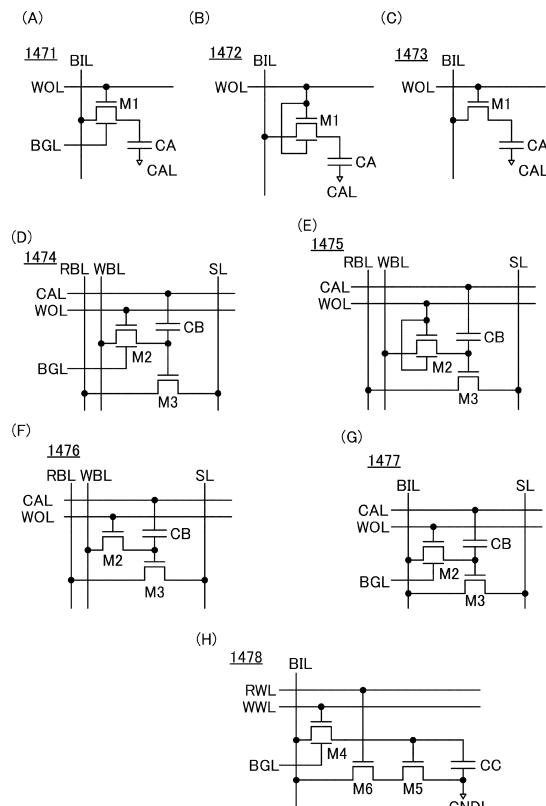

【図38】(A)乃至(H)記憶装置の構成例を示す回路図。

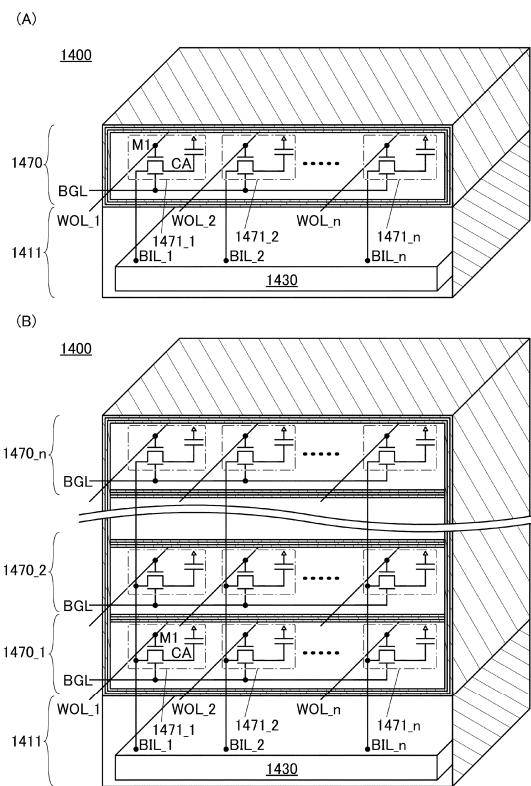

【図39】(A)乃至(B)記憶装置の構成例を示す回路図。

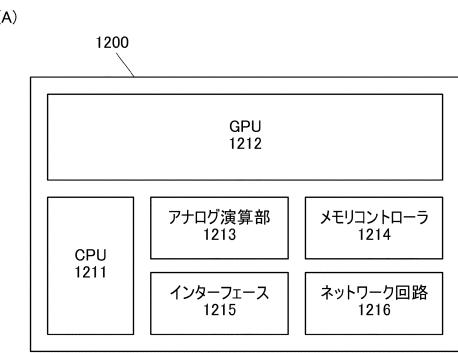

【図40】(A)乃至(B)半導体装置の模式図。

【図41】(A)乃至(E)記憶装置の模式図。

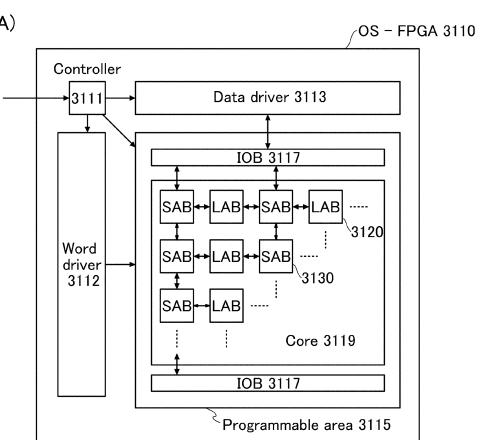

【図42】(A)乃至(C)半導体装置の構成例を示すブロック図。

40

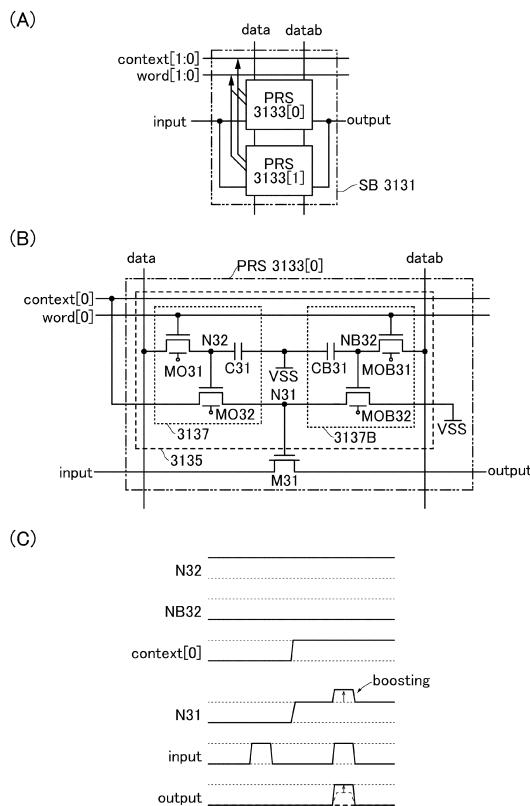

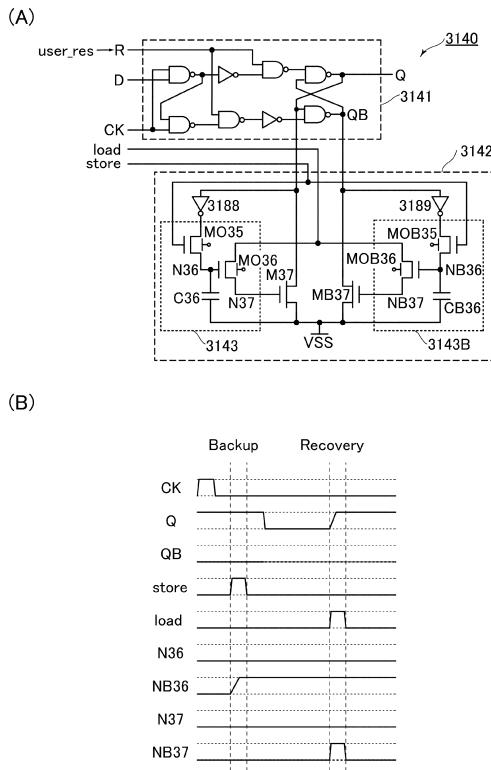

【図43】(A)半導体装置の構成例を示すブロック図、(B)半導体装置の構成例を示す回路図、(C)半導体装置の動作例を示すタイミングチャート。

【図44】半導体装置の構成例を示すブロック図。

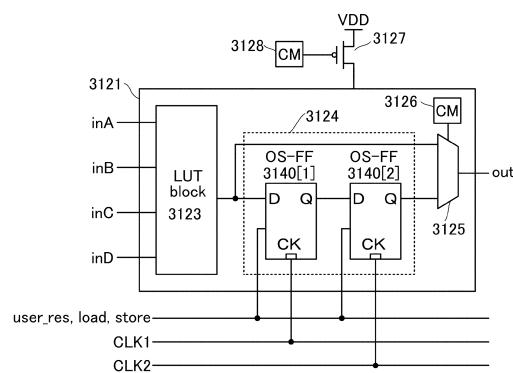

【図45】(A)半導体装置の構成例を示す回路図、(B)半導体装置の動作例を示すタイミングチャート。

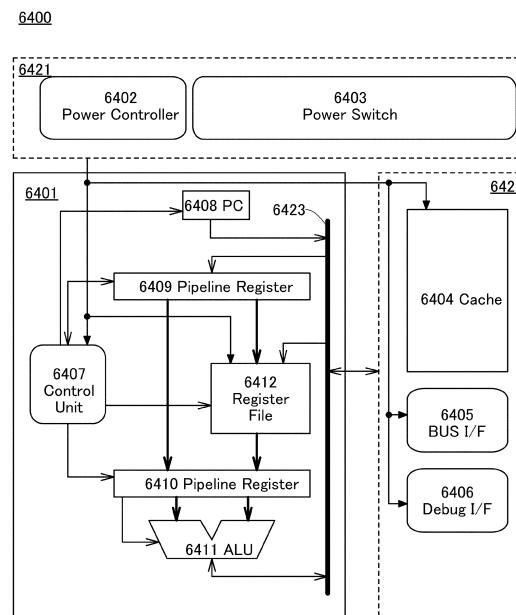

【図46】半導体装置を示すブロック図。

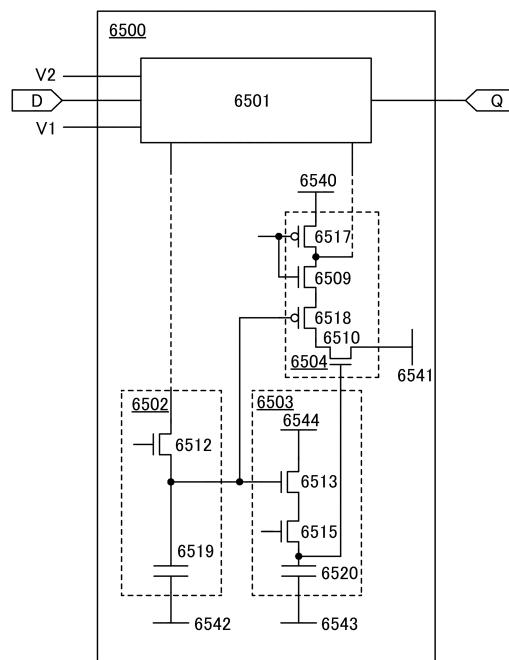

【図47】半導体装置を示す回路図。

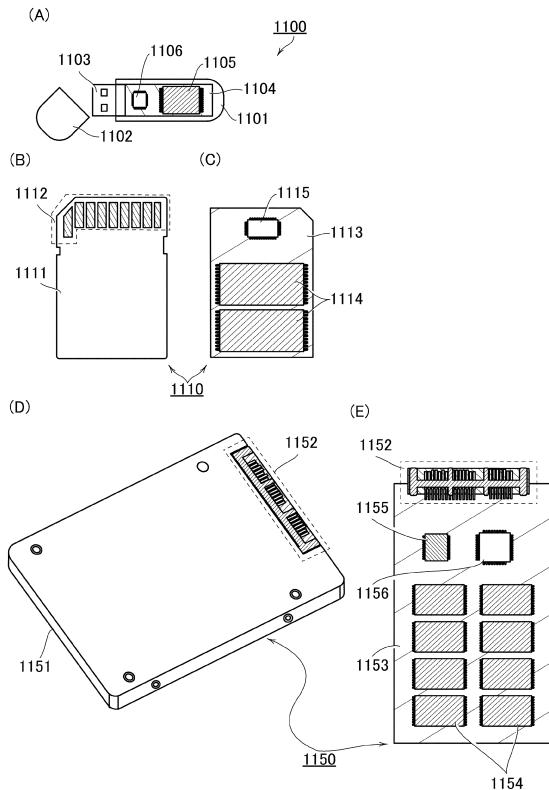

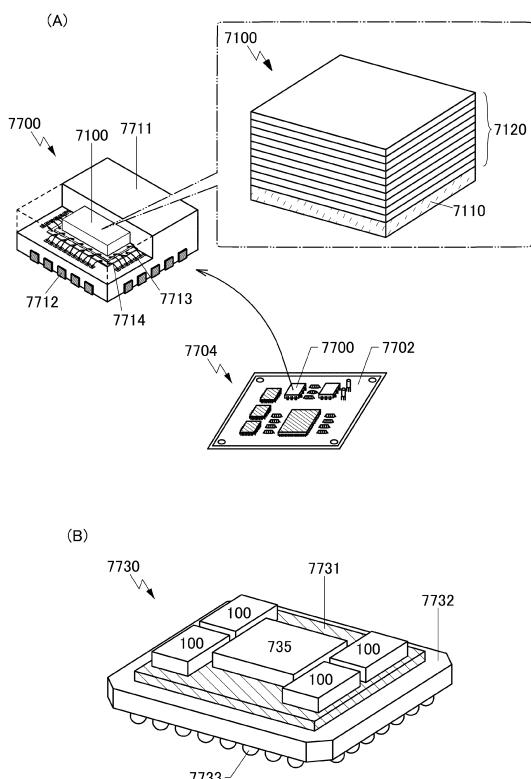

【図48】(A)乃至(B)電子部品の例を示す模式図。

【図49】(A)乃至(F)電子機器を示す図。

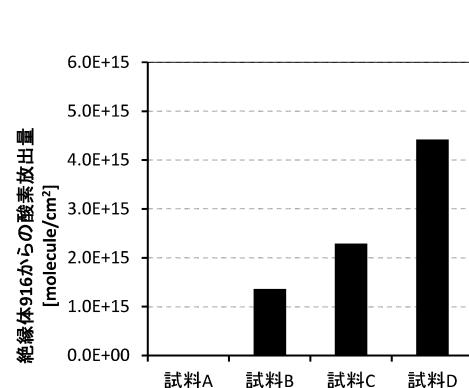

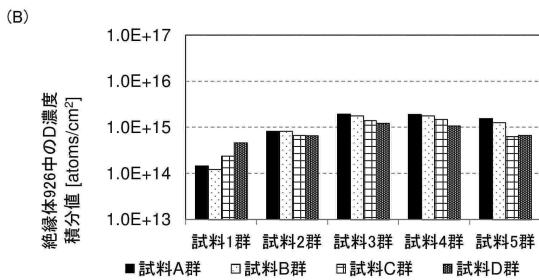

【図50】(A)試料の模式図、(B)TDS分析結果を示す図。

50

【図 5 1】試料の模式図。

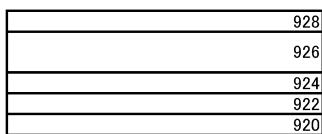

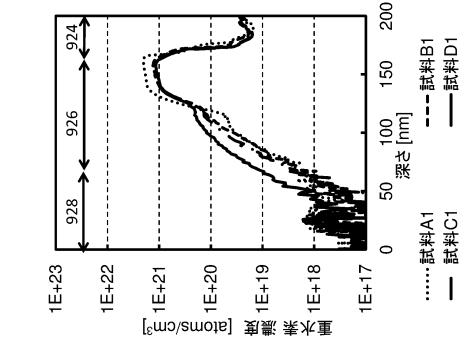

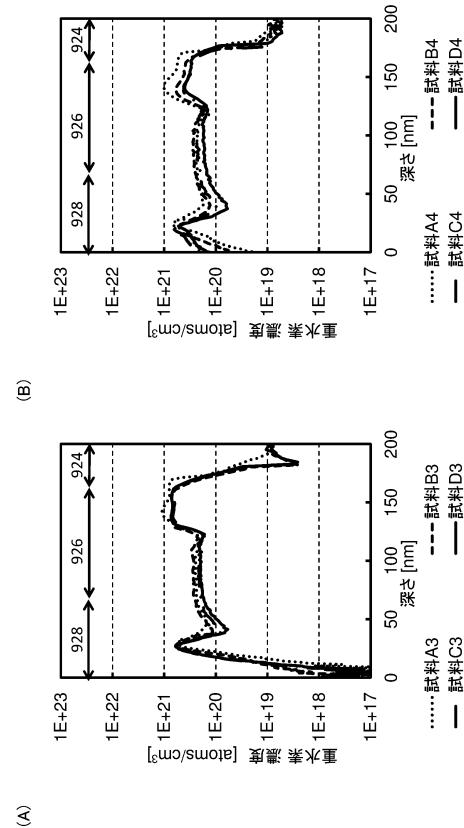

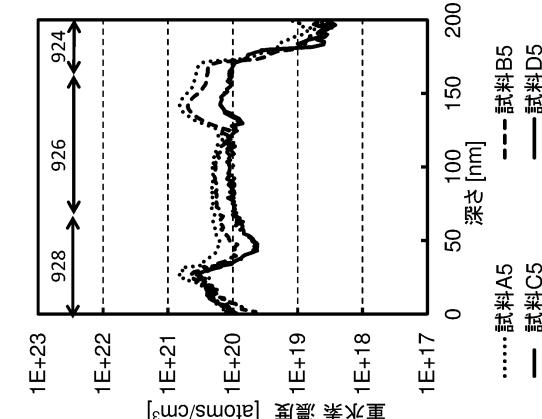

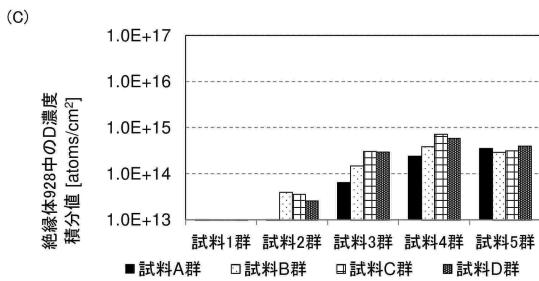

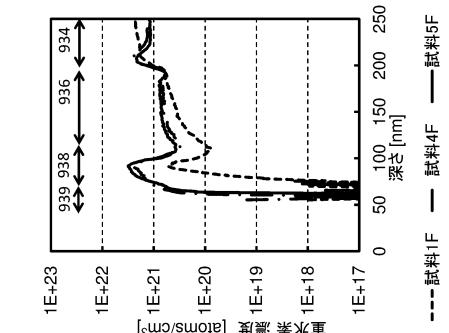

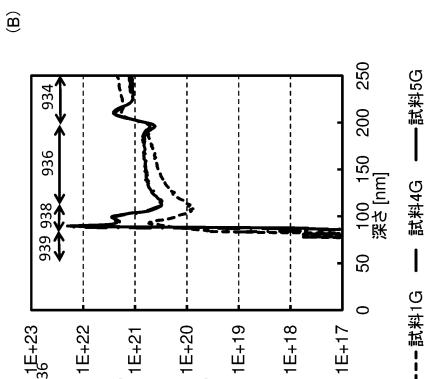

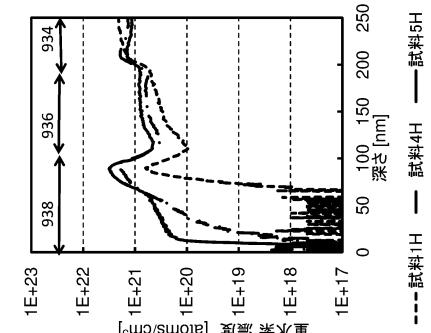

【図 5 2】( A ) 乃至 ( B ) S I M S 分析の結果を示す図。

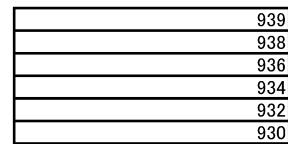

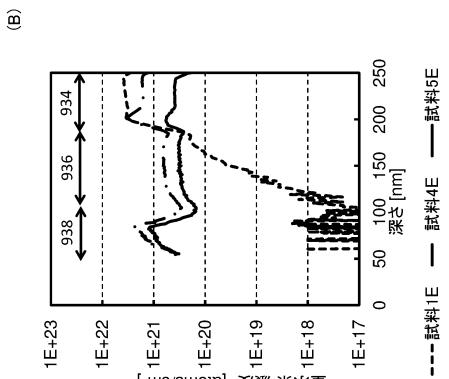

【図 5 3】( A ) 乃至 ( B ) S I M S 分析の結果を示す図。

【図 5 4】S I M S 分析の結果を示す図。

【図 5 5】( A ) 乃至 ( C ) 各構造が有する水素濃度の積分値を説明する図。

【図 5 6】試料の模式図。

【図 5 7】( A ) 乃至 ( B ) 実施例に係る試料の S I M S 分析の結果を示す図。

【図 5 8】( A ) 乃至 ( B ) 実施例に係る試料の S I M S 分析の結果を示す図。

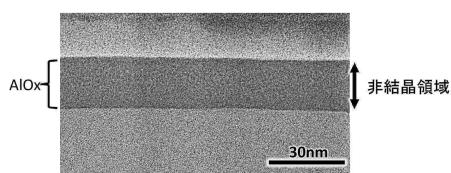

【図 5 9】( A ) 乃至 ( C ) 試料の断面を示す図。

【発明を実施するための形態】

10

【0 0 2 4】

以下、実施の形態について図面を参照しながら説明する。ただし、実施の形態は多くの異なる態様で実施することが可能であり、趣旨およびその範囲から逸脱することなくその形態および詳細を様々に変更し得ることは、当業者であれば容易に理解される。したがって、本発明は、以下の実施の形態の記載内容に限定して解釈されるものではない。

【0 0 2 5】

また、図面において、大きさ、層の厚さ、または領域は、明瞭化のために誇張されている場合がある。よって、必ずしもそのスケールに限定されない。なお、図面は、理想的な例を模式的に示したものであり、図面に示す形状または値などに限定されない。例えば、実際の製造工程において、エッティングなどの処理により層やレジストマスクなどが意図せずに目減りすることがあるが、理解を容易とするために図に反映しないことがある。また、図面において、同一部分または同様な機能を有する部分には同一の符号を異なる図面間で共通して用い、その繰り返しの説明は省略する場合がある。また、同様の機能を指す場合には、ハッチパターンを同じくし、特に符号を付さない場合がある。

20

【0 0 2 6】

また、特に上面図（「平面図」ともいう）や斜視図などにおいて、発明の理解を容易とするため、一部の構成要素の記載を省略する場合がある。また、一部の隠れ線などの記載を省略する場合がある。

【0 0 2 7】

また、本明細書等において、第 1、第 2 等として付される序数詞は便宜上用いるものであり、工程順または積層順を示すものではない。そのため、例えば、「第 1 の」を「第 2 の」または「第 3 の」などと適宜置き換えて説明することができる。また、本明細書等に記載されている序数詞と、本発明の一態様を特定するために用いられる序数詞は一致しない場合がある。

30

【0 0 2 8】

また、本明細書等において、「上に」、「下に」などの配置を示す語句は、構成同士の位置関係を、図面を参照して説明するために、便宜上用いている。また、構成同士の位置関係は、各構成を描写する方向に応じて適宜変化するものである。したがって、明細書で説明した語句に限定されず、状況に応じて適切に言い換えることができる。

【0 0 2 9】

40

例えば、本明細書等において、X と Y とが接続されている、と明示的に記載されている場合は、X と Y とが電気的に接続されている場合と、X と Y とが機能的に接続されている場合と、X と Y とが直接的に接続されている場合とが、本明細書等に開示されているものとする。したがって、所定の接続関係、例えば、図または文章に示された接続関係に限定されず、図または文章に示された接続関係以外のものも、図または文章に開示されているものとする。

【0 0 3 0】

ここで、X、Y は、対象物（例えば、装置、素子、回路、配線、電極、端子、導電膜、層、など）であるとする。

【0 0 3 1】

50

また、ソースやドレインの機能は、異なる極性のトランジスタを採用する場合や、回路動作において電流の方向が変化する場合などには入れ替わることがある。このため、本明細書等においては、ソースやドレインの用語は、入れ替えて用いることができる場合がある。

#### 【0032】

なお、本明細書等において、トランジスタの構造によっては、実際にチャネルの形成される領域（チャネル形成領域）におけるチャネル幅（以下、「実効的なチャネル幅」ともいう）と、トランジスタの上面図において示されるチャネル幅（以下、「見かけ上のチャネル幅」ともいう）と、が異なる場合がある。例えば、ゲートが半導体の側面を覆う場合、実効的なチャネル幅が、見かけ上のチャネル幅よりも大きくなり、その影響が無視できなくなる場合がある。例えば、微細かつゲートが半導体の側面を覆うトランジスタでは、半導体の側面に形成されるチャネル形成領域の割合が大きくなる場合がある。その場合は、見かけ上のチャネル幅よりも、実効的なチャネル幅の方が大きくなる。

10

#### 【0033】

このような場合、実効的なチャネル幅の、実測による見積もりが困難となる場合がある。例えば、設計値から実効的なチャネル幅を見積もるためにには、半導体の形状が既知という仮定が必要である。したがって、半導体の形状が正確にわからない場合には、実効的なチャネル幅を正確に測定することは困難である。

#### 【0034】

本明細書では、単にチャネル幅と記載した場合には、見かけ上のチャネル幅を指す場合がある。または、本明細書では、単にチャネル幅と記載した場合には、実効的なチャネル幅を指す場合がある。なお、チャネル長、チャネル幅、実効的なチャネル幅、見かけ上のチャネル幅などは、断面TEM像などを解析することなどによって、値を決定することができる。

20

#### 【0035】

なお、半導体の不純物とは、例えば、半導体を構成する主成分以外をいう。例えば、濃度が0.1原子%未満の元素は不純物と言える。不純物が含まれることにより、例えば、半導体のDOS（Density of States）が高くなることや、結晶性が低下することなどが起こる場合がある。半導体が酸化物半導体である場合、半導体の特性を変化させる不純物としては、例えば、第1族元素、第2族元素、第13族元素、第14族元素、第15族元素、および酸化物半導体の主成分以外の遷移金属などがあり、例えば、水素、リチウム、ナトリウム、シリコン、ホウ素、リン、炭素、窒素などがある。酸化物半導体の場合、水も不純物として機能する場合がある。また、酸化物半導体の場合、例えば不純物の混入によって酸素欠損を形成する場合がある。また、半導体がシリコンである場合、半導体の特性を変化させる不純物としては、例えば、酸素、水素を除く第1族元素、第2族元素、第13族元素、第15族元素などがある。

30

#### 【0036】

なお、本明細書等において、酸化窒化シリコンとは、その組成として、窒素よりも酸素の含有量が多いものである。また、窒化酸化シリコンとは、その組成として、酸素よりも窒素の含有量が多いものである。

40

#### 【0037】

また、本明細書等において、「絶縁体」という用語を、絶縁膜または絶縁層と言い換えることができる。また、「導電体」という用語を、導電膜または導電層と言い換えることができる。また、「半導体」という用語を、半導体膜または半導体層と言い換えることができる。

#### 【0038】

また、本明細書等において、「平行」とは、二つの直線が-10度以上10度以下の角度で配置されている状態をいう。したがって、-5度以上5度以下の場合も含まれる。また、「略平行」とは、二つの直線が-30度以上30度以下の角度で配置されている状態をいう。また、「垂直」とは、二つの直線が80度以上100度以下の角度で配置されて

50

いる状態をいう。したがって、85度以上95度以下の場合も含まれる。また、「略垂直」とは、二つの直線が60度以上120度以下の角度で配置されている状態をいう。

#### 【0039】

なお、本明細書において、バリア膜とは、水、水素などの不純物および酸素の透過を抑制する機能を有する膜のことであり、当該バリア膜に導電性を有する場合は、導電性バリア膜と呼ぶことがある。

#### 【0040】

本明細書等において、金属酸化物(metal oxide)とは、広い意味での金属の酸化物である。金属酸化物は、酸化物絶縁体、酸化物導電体(透明酸化物導電体を含む)、酸化物半導体(Oxide Semiconductorまたは単にOSともいう)などに分類される。例えば、トランジスタの半導体層に金属酸化物を用いた場合、当該金属酸化物を酸化物半導体と呼称する場合がある。つまり、OS FETあるいはOSトランジスタと記載する場合においては、酸化物または酸化物半導体を有するトランジスタと換言することができる。

10

#### 【0041】

また、本明細書等において、ノーマリーオフとは、ゲートに電位を印加しない、またはゲートに接地電位を与えたときに、トランジスタに流れるチャネル幅 $1\mu m$ あたりの電流が、室温において $1 \times 10^{-20} A$ 以下、85において $1 \times 10^{-18} A$ 以下、または125において $1 \times 10^{-16} A$ 以下であることをいう。

20

#### 【0042】

##### (実施の形態1)

以下では、本発明の一態様に係るトランジスタ200を有する半導体装置の一例、およびその作製方法について説明する。

#### 【0043】

##### <半導体装置の構成例1>

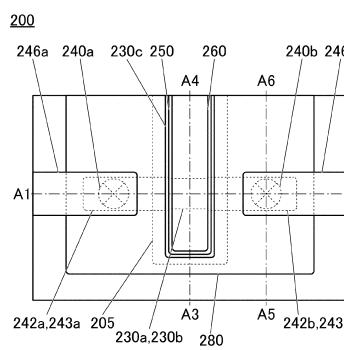

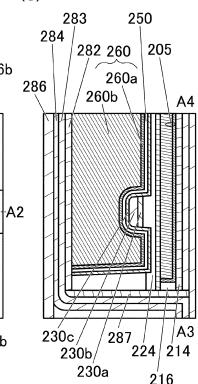

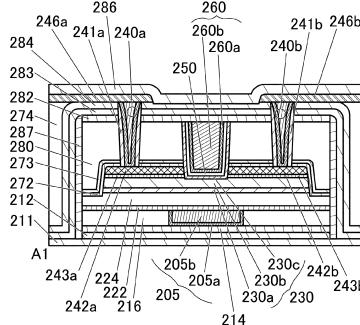

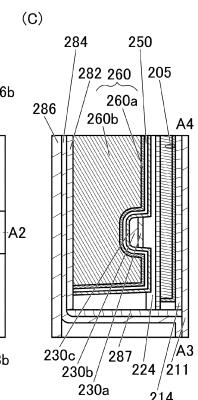

図4(A)、図4(B)、図4(C)、および図4(D)は、本発明の一態様に係るトランジスタ200、およびトランジスタ200周辺の上面図および断面図である。

#### 【0044】

図4(A)は、トランジスタ200を有する半導体装置の上面図である。また、図4(B)、および図4(C)は、当該半導体装置の断面図である。ここで、図4(B)は、図4(A)にA1-A2の一点鎖線で示す部位の断面図であり、トランジスタ200のチャネル長方向の断面図でもある。また、図4(C)は、図4(A)にA3-A4の一点鎖線で示す部位の断面図であり、トランジスタ200のチャネル幅方向の断面図でもある。また、図4(D)は、図4(A)にA5-A6の一点鎖線で示す部位の断面図である。なお、図4(A)の上面図では、図の明瞭化のために一部の要素を省いている。

30

#### 【0045】

ここで、トランジスタ200は、チャネルが形成される領域(以下、チャネル形成領域ともいう。)を含む半導体に、酸化物半導体として機能する金属酸化物(以下、酸化物半導体ともいう。)を用いることが好ましい。

#### 【0046】

酸化物半導体として、例えば、In-M-Zn酸化物(元素Mは、アルミニウム、ガリウム、イットリウム、銅、バナジウム、ベリリウム、ホウ素、チタン、鉄、ニッケル、ゲルマニウム、ジルコニウム、モリブデン、ランタン、セリウム、ネオジム、ハフニウム、タンタル、タングステン、またはマグネシウムなどから選ばれた一種、または複数種)等の金属酸化物を用いるとよい。また、酸化物半導体として、In-Ga酸化物、In-Zn酸化物を用いてもよい。

40

#### 【0047】

チャネル形成領域に酸化物半導体を用いたトランジスタ200は、非導通状態において極めてリーク電流が小さいため、低消費電力の半導体装置を提供できる。また、酸化物半導体は、スパッタリング法などを用いて成膜できるため、高集積型の半導体装置を構成す

50

るトランジスタ 200 に用いることができる。

**【0048】**

一方、酸化物半導体を用いたトランジスタは、酸化物半導体中の不純物及び酸素欠損によって、その電気特性が変動し、ノーマリーオン特性（ゲート電極に電圧を印加しなくてもチャネルが存在し、トランジスタに電流が流れる特性）となりやすい。

**【0049】**

そこで、不純物濃度、および欠陥準位密度が低減された酸化物半導体を用いるとよい。なお、本明細書等において、不純物濃度が低く、欠陥準位密度の低いことを高純度真性または実質的に高純度真性という。

**【0050】**

従って、酸化物半導体中の不純物濃度はできる限り低減されていることが好ましい。なお、酸化物半導体中の不純物としては、例えば、水素、窒素、アルカリ金属、アルカリ土類金属、鉄、ニッケル、シリコン等がある。

**【0051】**

特に、酸化物半導体に含まれる不純物としての水素は、酸化物半導体中に酸素欠損（ $V_O$  : oxygen vacancyともいう）を形成する場合がある。また、酸素欠損に水素が入った欠陥（以下、 $V_OH$ と呼ぶ場合がある。）は、キャリアとなる電子を生成する場合がある。さらに、水素の一部が金属原子と結合する酸素と反応し、キャリアとなる電子を生成する場合がある。

**【0052】**

従って、水素が多く含まれている酸化物半導体を用いたトランジスタは、ノーマリーオン特性となりやすい。また、酸化物半導体中の水素は、熱、電界などのストレスによって動きやすいため、酸化物半導体に多くの水素が含まれると、トランジスタの信頼性が悪化する恐れもある。

**【0053】**

従って、トランジスタに用いる酸化物半導体は、水素などの不純物、および酸素欠損が低減された高純度真性な酸化物半導体を用いることが好ましい。

**【0054】**

そこで、外部からの不純物混入を抑制するために、不純物の拡散を抑制する材料（以下、不純物に対するバリア性材料ともいう）を用いて、トランジスタ 200 を封止するとよい。

**【0055】**

なお、本明細書において、バリア性とは、対応する物質の拡散を抑制する機能（透過性が低いともいう）とする。または、対応する物質を、捕獲、および固着する（ゲッタリングともいう）機能とする。

**【0056】**

例えば、水素、および酸素に対する拡散を抑制する機能を有する材料として、酸化アルミニウム、酸化ハフニウム、酸化ガリウム、インジウムガリウム亜鉛酸化物、窒化シリコン、または窒化酸化シリコンなどがある。特に、窒化シリコンまたは窒化酸化シリコンは、水素に対するバリア性が高いため、封止する材質として用いることが好ましい。

**【0057】**

また、例えば、水素を捕獲、および固着する機能を有する材料として、酸化アルミニウム、酸化ハフニウム、酸化ガリウム、インジウムガリウム亜鉛酸化物、などの金属酸化物がある。

**【0058】**

ここで、トランジスタ 200 を封止する構造体は、単層、または 2 層以上の積層構造で設けることができる。特に、トランジスタ 200 を封止する構造体を積層構造、より好ましくは入れ子構造となるように、設けるとよい。

**【0059】**

具体的に、トランジスタ 200 を封止する構造体が 2 層構造を有する場合を用いて、説

10

20

30

40

50

明する。トランジスタ 200 を封止する構造体は、トランジスタ 200 と近接する第 1 の構造体、第 1 の構造体の外方に設けられる第 2 の構造体を有する。つまり、トランジスタ 200 と第 2 の構造体は、第 1 の構造体を介して設けられる。

#### 【0060】

上記構成において、第 1 の構造体には、水素を捕獲、および固着する機能を有する材料を用いるとよい。また、第 2 の構造体には、水素、および酸素に対する拡散を抑制する機能を有する材料を用いるとよい。

#### 【0061】

トランジスタ 200 に近接する側に、水素を捕獲、および固着する機能を有する材料を用いることで、トランジスタ 200 中、または第 1 の構造体とトランジスタ 200 との間に設けられた層間膜中の水素は、第 1 の構造体に、捕獲、および固着するため、トランジスタ 200 中の水素濃度を低減することができる。

10

#### 【0062】

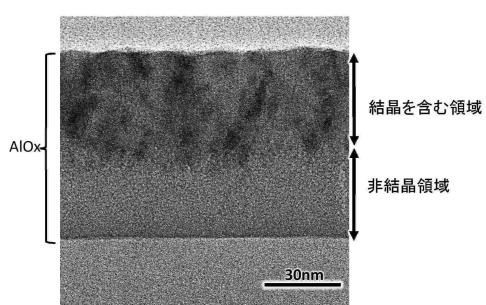

具体的には、酸化アルミニウムを用いることが好ましい。特に、結晶性が低い、または非晶質な酸化アルミニウムは、結晶性が高い酸化アルミニウムよりも、水素の捕獲、および固着する量が大きい場合がある。また、結晶性が低い、または非晶質な酸化アルミニウムは、加熱処理により、水素を拡散する性質を有する。つまり、水素濃度が高い領域と、水素濃度が低い領域との間に、結晶性が低い、または非晶質な酸化アルミニウムを配置し、加熱処理を行った場合、当該酸化アルミニウムを介して、水素濃度が低い領域中の水素は、水素濃度が高い領域へと、拡散する。

20

#### 【0063】

従って、第 1 の構造体として、結晶性が低い、または非晶質な酸化アルミニウムを用いた場合、第 1 の構造体により、トランジスタ 200 を封止した後、加熱処理を行うことが好ましい。当該加熱処理により、トランジスタ 200 中の水素は、層間膜、および当該酸化アルミニウムを介して、外方に拡散され、トランジスタ 200 、および当該酸化アルミニウム中の水素濃度を低減することができる。つまり、半導体装置中に存在する水素の絶対量を低減することができる。

#### 【0064】

一方、第 2 の構造体は、第 1 の構造体を介して、トランジスタ 200 を封止する。従って、第 2 の構造体の外方から拡散する水素は、第 2 の構造体により、第 2 の構造体の内部（トランジスタ 200 側）への拡散が、抑制される。つまり、第 1 の構造体は、第 2 の構造体の内側に設けられた構造に存在する水素を、効率よく捕獲し、固着することができる。

30

#### 【0065】

上記構造として、具体的には、第 1 の構造体には酸化アルミニウムなどの金属酸化物を用い、第 2 の構造体には窒化シリコンなどの窒化物を用いることができる。より、具体的には、トランジスタ 200 と、窒化シリコン膜との間に、酸化アルミニウム膜を配置するとよい。

#### 【0066】

さらに、構造体に用いる材料は、成膜条件を適宜設定することにより、膜中の水素濃度を低減することができる。

40

#### 【0067】

一般的に、CVD 法を用いて成膜した膜は、スパッタリング法を用いて成膜した膜よりも、被覆性が高い。一方で、CVD 法に用いる化合物ガスは、水素を含む場合が多く、CVD 法を用いて成膜した膜は、スパッタリング法を用いて成膜した膜よりも、水素の含有量が多い。

#### 【0068】

従って、例えば、トランジスタ 200 と近接する膜に、膜中の水素濃度が低減された膜（具体的にはスパッタリング法を用いて成膜した膜）を用いるとよい。一方で、不純物の拡散を抑制する膜として、被膜性が高い一方で膜中の水素濃度が比較的高い膜（具体的に

50

は CVD 法を用いて成膜した膜) を用いる場合、トランジスタ 200 と、水素濃度が比較的高い一方で被膜性が高い膜との間に、水素を捕獲、および固着する機能を有し、かつ水素濃度が低減された膜を配置するとよい。

#### 【0069】

つまり、トランジスタ 200 に近接して配置する膜は、膜中の水素濃度が比較的低い膜を用いるとよい。一方で、膜中の水素濃度が比較的高い膜は、トランジスタ 200 から遠隔して配置するとよい。

#### 【0070】

上記構造として、具体的には、トランジスタ 200 を、CVD 法を用いて成膜した窒化シリコン膜を用いて封止する場合、トランジスタ 200 と、CVD 法を用いて成膜した窒化シリコン膜との間に、スパッタリング法を用いて成膜した酸化アルミニウム膜を配置するとよい。さらに好ましくは、CVD 法を用いて成膜した窒化シリコン膜と、スパッタリング法を用いて成膜した酸化アルミニウム膜との間に、スパッタリング法を用いて成膜した窒化シリコン膜を配置するとよい。

10

#### 【0071】

なお、CVD 法を用いて成膜する場合、水素原子を含まない、または水素原子の含有量が少ないと、化合物ガスを用いて成膜することで、成膜した膜に含まれる水素濃度を低減してもよい。

#### 【0072】

以下では、トランジスタ 200 を封止する具体的な構成を、図 4 を用いて説明する。

20

#### 【0073】

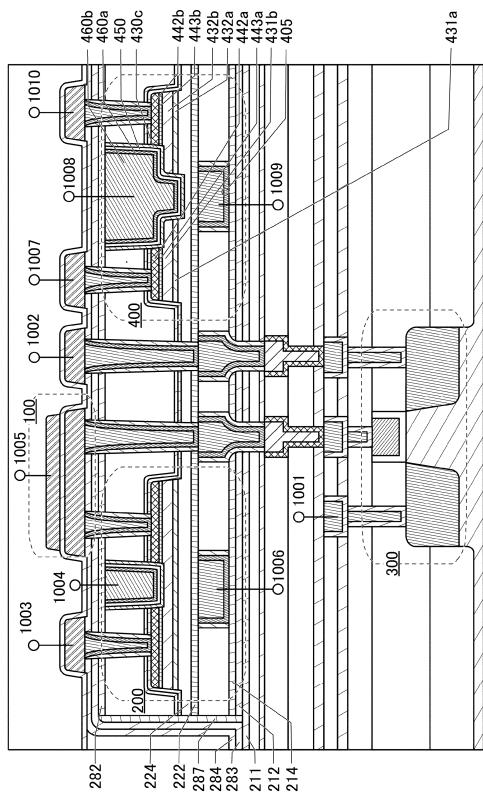

本発明の一態様の半導体装置は、基板(図示せず)上の絶縁体 211 と、絶縁体 211 上の絶縁体 212 と、絶縁体 212 上の絶縁体 214 と、絶縁体 214 上のトランジスタ 200 と、トランジスタ 200 上の絶縁体 280 と、絶縁体 280 上の絶縁体 282 と、絶縁体 280 の側面を覆う絶縁体 287 と、絶縁体 282、および絶縁体 287 を覆う絶縁体 283 と、絶縁体 283 上の絶縁体 284 と、絶縁体 284 に接して設けられた絶縁体 274 と、を有する。

#### 【0074】

なお、絶縁体 211、絶縁体 212、絶縁体 214、絶縁体 280、絶縁体 282、絶縁体 287、絶縁体 283、絶縁体 284、および絶縁体 274 は層間膜として機能する。

30

#### 【0075】

ここで、酸化物半導体の近傍に、過剰酸素領域を有する構造体を設けた場合、酸化物半導体に生じた酸素欠損に、該過剰酸素領域を有する構造体の過剰酸素を拡散することで、該酸素欠損を補償することができる。

#### 【0076】

なお、本明細書では、加熱により離脱する酸素を過剰酸素と呼ぶことがある。また、化学量論的組成を満たす酸素よりも多くの酸素を、過剰酸素と呼ぶ場合もある。また、化学量論的組成よりも酸素が過剰に存在する領域を、過剰酸素領域ともいう。

40

#### 【0077】

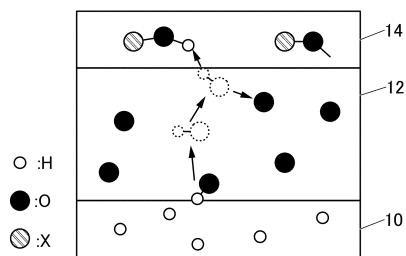

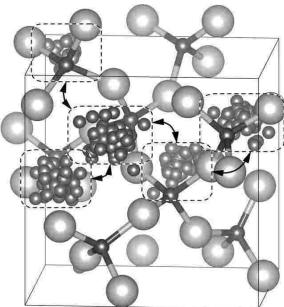

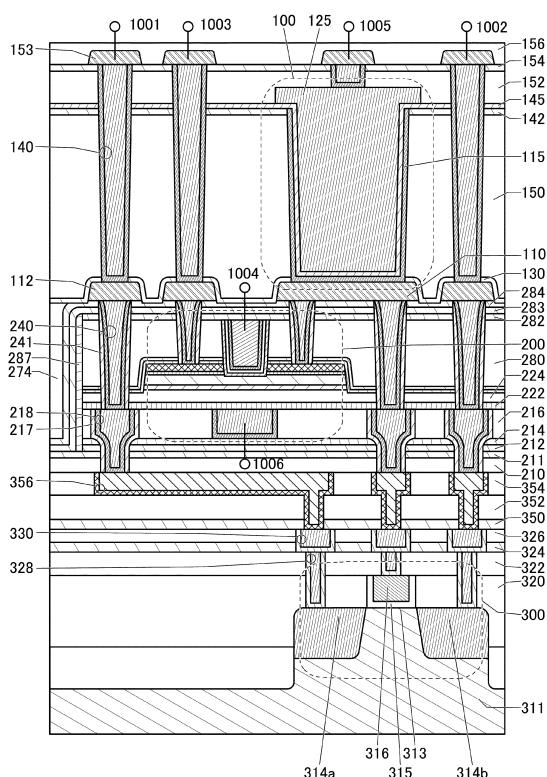

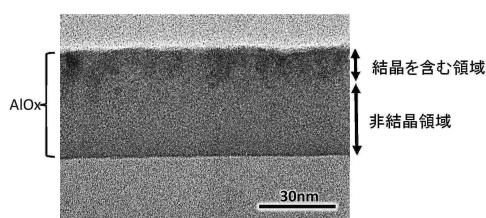

ここで、絶縁体中の過剰酸素は、当該絶縁体と接する酸化物半導体中の水素の拡散に対し、影響要因となる可能性がある。具体的には、図 1 を用いて説明する。図 1 に示す構造体は、水素を含む酸化物半導体 10、酸化物半導体 10 に接する過剰酸素を有する絶縁体 12、絶縁体 12 に接する金属酸化物 14 を有する。なお、金属酸化物 14 を構成する金属原子を、金属原子 X とする。

#### 【0078】

酸化物半導体 10 中に存在する水素は、酸化物半導体 10 に接する絶縁体 12 を介して、他の構造体へと拡散する。当該水素の拡散は、絶縁体 12 中の過剰酸素が酸化物半導体 10 中の水素と反応し OH 結合となり、絶縁体 12 中を拡散する。OH 結合を有した水素原子は、金属酸化物 14 に到達した際に、水素原子は金属酸化物 14 中の金属原子 X と結

50

合した酸素原子と反応し、金属酸化物 14 中に捕獲、または固着する。一方、OH 結合を有していた過剰酸素の酸素原子は、過剰酸素として絶縁体 12 中に残ると推測される。つまり、当該水素の拡散において、絶縁体 12 中の過剰酸素が、橋渡し的な役割を担う蓋然性が高い。

#### 【0079】

なお、図 4 では、上述の酸化物半導体 10 は酸化物 230c に相当し、絶縁体 12 は絶縁体 280 に相当する。従って、酸化物 230c と接する絶縁体 280 は、加熱により酸素を脱離することが好ましい。

#### 【0080】

過剰酸素領域を有する絶縁体として、具体的には、加熱により一部の酸素が脱離する酸化物を用いることが好ましい。加熱により一部の酸素が脱離する酸化物とは、TDS (Thermal Desorption Spectroscopy) 分析にて、酸素分子の脱離量が  $1.0 \times 10^{18}$  molecules/cm<sup>3</sup> 以上、好ましくは  $1.0 \times 10^{19}$  molecules/cm<sup>3</sup> 以上、さらに好ましくは  $2.0 \times 10^{19}$  molecules/cm<sup>3</sup> 以上、または  $3.0 \times 10^{20}$  molecules/cm<sup>3</sup> 以上である酸化物である。なお、上記 TDS 分析時における膜の表面温度としては 100 以上 700 以下、または 100 以上 400 以下の範囲が好ましい。

10

#### 【0081】

具体的には、過剰酸素を有する酸化シリコン、酸化窒化シリコン、窒化酸化シリコン、窒化シリコン、フッ素を添加した酸化シリコン、炭素を添加した酸化シリコン、炭素および窒素を添加した酸化シリコン、空孔を有する酸化シリコンを用いることができる。特に、酸化シリコン、および酸化窒化シリコンは熱に対し安定であるため好ましい。

20

#### 【0082】

従って、絶縁体 280 は、酸化シリコン、酸化窒化シリコン、窒化酸化シリコン、フッ素を添加した酸化シリコン、炭素を添加した酸化シリコン、炭素および窒素を添加した酸化シリコン、または空孔を有する酸化シリコンなどを有することが好ましい。

#### 【0083】

特に、絶縁体 280 として用いるには、酸化シリコンおよび酸化窒化シリコンは、熱的に安定であるため好ましい。また、酸化シリコン、酸化窒化シリコン、空孔を有する酸化シリコンなどの材料は、加熱により脱離する酸素を含む領域を容易に形成することができるため好ましい。また、絶縁体 280 は、上記の材料が積層された構造でもよく、例えば、スパッタリング法で成膜した酸化シリコンと、その上に積層された CVD 法で成膜された酸化窒化シリコンの積層構造とすればよい。また、さらに上に窒化シリコンを積層してもよい。

30

#### 【0084】

絶縁体 280 に過剰酸素領域を設けるには、絶縁体 280 に、酸素（少なくとも酸素ラジカル、酸素原子、酸素イオンのいずれかを含む）を導入し、酸素を過剰に含有する領域を形成する。

#### 【0085】

具体的に、酸素導入処理の一例として、絶縁体 280 上に、スパッタリング装置を用いて、金属酸化物を積層する方法がある。例えば、絶縁体 282 を成膜する手段として、スパッタリング装置を用いて、酸素ガス雰囲気下で成膜を行うことで、絶縁体 282 を成膜しながら、絶縁体 280 に酸素を導入することができる。

40

#### 【0086】

特に、絶縁体 280 として、酸化窒化シリコンを用い、絶縁体 282 として、酸化アルミニウムを用いることが好ましい。酸化窒化シリコン膜上に、スパッタリング法により酸化アルミニウム膜を成膜することで、被成膜物である酸化窒化シリコンに過剰酸素領域を形成することができる。

#### 【0087】

なお、絶縁体 280 中の水または水素などの不純物濃度が低減されていることが好まし

50

い。

#### 【 0 0 8 8 】

ここで、具体的に、酸化物 230 に接する絶縁体 280 に酸化シリコンを用いた場合における、絶縁体 280 中の過剰酸素、および水素の拡散挙動、ならびに水酸基の拡散挙動を、量子分子動力学計算を行い、調査した。

#### 【 0 0 8 9 】

##### < 計算モデルと計算方法 >

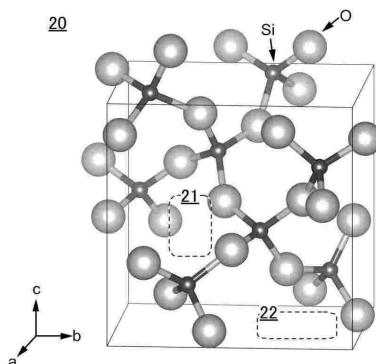

まず、基準となるアモルファス状態の  $\text{SiO}_2$  構造 (a- $\text{SiO}_2$  構造モデル) のモデルと、基準となるモデルに対して、1 個の OH 基を追加したモデル、および 1 個の H 原子と 1 個の O 原子とを追加したモデルを用いて計算を行った。

10

#### 【 0 0 9 0 】

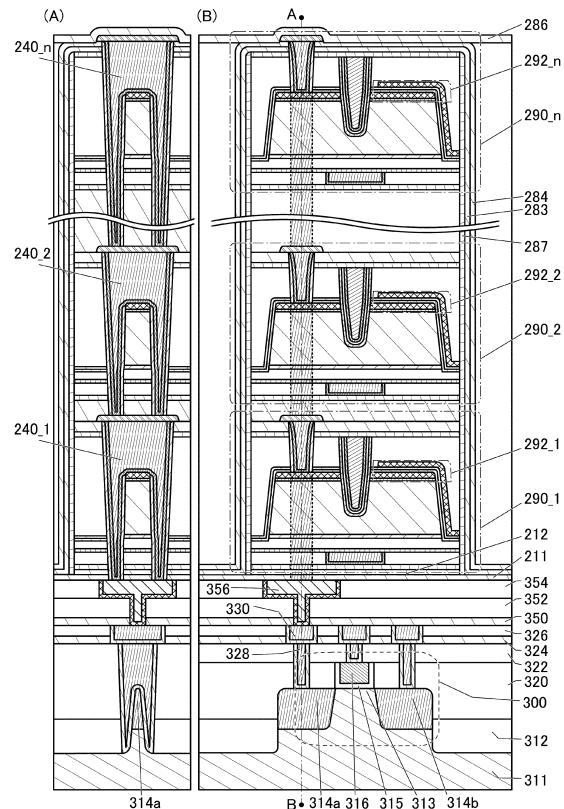

具体的には、基準となる結晶モデルとして、図 2 (A) に示す、複数の間隙領域を有する a- $\text{SiO}_2$  構造モデル 20 を用いた。なお、モデル 20 は、24 個の原子で構成した。

#### 【 0 0 9 1 】

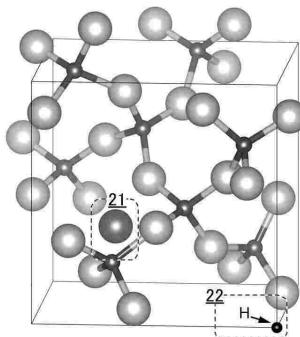

図 2 (B) に示すモデル 24 は、モデル 20 において、不純物に相当する H 原子、および過剰酸素に相当する O 原子が存在するとし、モデル 20 の間隙領域 21 に 1 個の O 原子を、および間隙領域 22 に 1 個の H 原子を配置した。また、図 3 (A) に示すモデル 26 は、モデル 20 において、不純物に相当する OH 基が存在するとし、モデル 20 の間隙領域 21 に 1 個の OH 基を配置した。

20

#### 【 0 0 9 2 】

具体的な計算内容を以下に示す。また、原子緩和計算には、第一原理電子状態計算パッケージ VASP (Vienna ab initio simulation package) を用いて行った。計算条件を下表に示す。

#### 【 0 0 9 3 】

##### 【表 1】

| 計算プログラム    | VASP    |

|------------|---------|

| 基底関数       | 平面波     |

| 汎関数        | GGA-PBE |

| 擬ポテンシャル    | PAW     |

| カットオフエネルギー | 500 eV  |

| 電子数        | 中性      |

| k点グリッド     | 1×1×1   |

30

#### 【 0 0 9 4 】

また、プロセス温度を鑑み、700 K (~400 ) の温度下で、150 ps 間の計算を行った。

40

#### 【 0 0 9 5 】

##### < 拡散挙動について >

図 2 (B) に示すモデル 24 において、計算開始直後に、過剰酸素に相当する O 原子は、不純物に相当する H 原子と結合して、水酸基 (OH 基) となり、アモルファス状態の  $\text{SiO}_2$  構造中を拡散し始めた。つまり、生成した OH 基は、アモルファス状態の  $\text{SiO}_2$  構造中を拡散し、複数の間隙領域を行き来する挙動が観察された。

#### 【 0 0 9 6 】

また、図 3 (A) に示すモデル 26 において、OH 基は、アモルファス状態の  $\text{SiO}_2$  構造中を拡散し、複数の間隙領域を行き来する挙動が観察された。

#### 【 0 0 9 7 】

50

ここで、図3(B)に、0から50ps間の拡散挙動を可視化した概略図を示す。なお、図3(B)において、OH基におけるO原子とH原子との中心座標の軌跡を示す。なお、アモルファス状態のSiO<sub>2</sub>構造は初期構造のまま、固定して表示した。図3(B)に示すように、OH基は、複数の間隙領域(図では、点線で囲む領域とする。)にわたって拡散していることが確認できた。

#### 【0098】

以上より、酸化物半導体10中に存在する水素は、酸化物半導体10に接する絶縁体12を介して、他の構造体へと拡散する。当該水素の拡散は、絶縁体12中の過剰酸素が酸化物半導体10中の水素と反応しOH結合となり、絶縁体12中を拡散することが確認できた。

10

#### 【0099】

また、絶縁体211、絶縁体212、絶縁体214、絶縁体282、絶縁体287、絶縁体283、および絶縁体284に、不純物に対するバリア性を有する材料を用いることで、トランジスタ200が有する酸化物半導体を高純度真性に保つことができる。

#### 【0100】

具体的には、絶縁体214、絶縁体287、および絶縁体282は、トランジスタ200、および絶縁体280を、封止する構造(以下、封止構造ともいう)とする。例えば、図4に示すように、トランジスタ200の下方に絶縁体214を設け、トランジスタ200の上方に絶縁体282を設ける。また、トランジスタ200の側面は、絶縁体287をサイドウォール状に設ける。さらに、サイドウォール状の絶縁体287の下端部は、絶縁体214の端部と接し、絶縁体287の上端部は、絶縁体282の端部と接する。

20

#### 【0101】

ここで、絶縁体287と絶縁体214とは、確実に接することが好ましい。従って、絶縁体214と絶縁体287とが確実に接する領域を設けるには、絶縁体214の下方に設けられた絶縁体212の側面に接するように、絶縁体287を設けることが好ましい。

#### 【0102】

従って、絶縁体214、絶縁体287、および絶縁体282により、トランジスタ200を包囲する構造を有する。

#### 【0103】

ここで、絶縁体214、絶縁体287、および絶縁体282には、同じ材料を用いる。また、好ましくは、絶縁体214、絶縁体287、および絶縁体282の成膜方法は、同じ条件を用いて成膜することが好ましい。膜質が等しい絶縁体214、絶縁体287、および絶縁体282が接することで、密閉性が高い封止構造とすることができる。

30

#### 【0104】

また、絶縁体214、絶縁体287、および絶縁体282には、水素を捕獲、および固着する機能を有する材料を用いることが好ましい。具体的には、酸化アルミニウム、酸化ハフニウム、酸化ガリウム、インジウムガリウム亜鉛酸化物などの金属酸化物を用いることができる。

#### 【0105】

封止構造を形成する絶縁体214、絶縁体287、および絶縁体282は、トランジスタ200、または絶縁体280に接して設けられる。従って、トランジスタ200中、または絶縁体280中に混入した水素を捕獲、および固着することで、トランジスタ200が有する酸化物半導体の水素濃度を低減することができる。

40

#### 【0106】

また、トランジスタ200を封止する構造である絶縁体214、絶縁体287、および絶縁体282は、絶縁体211、絶縁体212、絶縁体283により設けられた封止構造により包囲される。

#### 【0107】

例えば、図4に示すように、絶縁体214の下方には、絶縁体211、および絶縁体212を配置し、絶縁体287、および絶縁体282を覆って、絶縁体283を設ける。ま

50

た、絶縁体214、絶縁体287、および絶縁体282より設けられたトランジスタ200を封止する構造の外方で、絶縁体211と絶縁体283とが接することで、2重目の封止構造を形成する。

#### 【0108】

ここで、絶縁体211、絶縁体212と絶縁体283には、水素、および酸素に対する拡散を抑制する機能を有する材料を用いることが好ましい。特に、窒化シリコンまたは窒化酸化シリコンは、水素に対するバリア性が高いため、封止する材質として用いることが好ましい。

#### 【0109】

また、トランジスタ200の上方を被覆する絶縁体283の上方に、被膜性が高い絶縁体284を設けることが好ましい。なお、絶縁体284は、絶縁体211、絶縁体212および絶縁体283と同じ材料を用いることが好ましい。

10

#### 【0110】

例えば、絶縁体212、絶縁体283は、スパッタリング法を用いて成膜することで、膜中の水素濃度が比較的低い膜により封止構造を設けることができる。

#### 【0111】

一方、スパッタリング法を用いて成膜した膜は、比較的被膜性が低い。そこで、絶縁体211、および絶縁体284を、被膜性が高いCVD法などを用いて成膜することで、より密閉性を高めることができる。

20

#### 【0112】

従って、絶縁体212および絶縁体283は、絶縁体211と絶縁体284よりも水素濃度が低いことが好ましい。

#### 【0113】

なお、好ましくは、絶縁体211、絶縁体212、絶縁体214、絶縁体282、絶縁体287、絶縁体283、および絶縁体284は、酸素に対するバリア性を有する材料を用いてもよい。上記封止構造が、酸素に対するバリア性を有することで、絶縁体280が有する過剰酸素の外方拡散を抑制し、効率的にトランジスタ200へと供給することができる。

#### 【0114】

また、本発明の一態様の半導体装置は、トランジスタ200と電気的に接続し、プラグとして機能する導電体240（導電体240a、および導電体240b）とを有する。なお、プラグとして機能する導電体240の側面に接して絶縁体241（絶縁体241a、および絶縁体241b）が設けられる。また、絶縁体284上、および導電体240上には、導電体240と電気的に接続し、配線として機能する導電体246（導電体246a、および導電体246b）が設けられる。また、導電体246上、および絶縁体274上には、絶縁体286が設けられている。

30

#### 【0115】

ここで、絶縁体272、絶縁体273、絶縁体280、絶縁体282、絶縁体283、および絶縁体284に設けられた開口の内壁に接して、絶縁体241（絶縁体241a、または絶縁体241b）が設けられ、その側面に接して導電体240（導電体240a、または導電体240b）の第1の導電体が設けられ、さらに内側に導電体240の第2の導電体が設けられている。

40

#### 【0116】

なお、導電体240の上面の高さと、絶縁体284の上面の高さは同程度にできる。また、図では、導電体240の第1の導電体および導電体240の第2の導電体を積層する構成について示しているが、本発明はこれに限られるものではない。例えば、導電体240を単層、または3層以上の積層構造として設ける構成にしてもよい。

#### 【0117】

また、導電体240aおよび導電体240bは、タンゲステン、銅、またはアルミニウムを主成分とする導電性材料を用いることが好ましい。また、導電体240aおよび導電

50

体 2 4 0 b は積層構造としてもよい。なお、図 4 ( A ) で導電体 2 4 0 a および導電体 2 4 0 b は、上面視において円形状にしているが、これに限られるものではない。例えば、導電体 2 4 0 a および導電体 2 4 0 b が、上面視において、橢円などの略円形状、四角形などの多角形状、四角形等の多角形の角部を丸めた形状になっていてもよい。

#### 【 0 1 1 8 】

また、導電体 2 4 0 を積層構造とする場合、水または水素などの不純物、および酸素の透過を抑制する機能を有する導電性材料を用いることが好ましい。例えば、タンタル、窒化タンタル、チタン、窒化チタン、ルテニウム、または酸化ルテニウムなどを用いることが好ましい。また、水または水素などの不純物、および酸素の透過を抑制する機能を有する導電性材料は、単層または積層で用いてもよい。当該導電性材料を用いることで、絶縁体 2 8 0 などから拡散する水または水素などの不純物が、導電体 2 4 0 a および導電体 2 4 0 b を通じて酸化物 2 3 0 に混入するのをさらに低減することができる。また、絶縁体 2 8 0 に添加された酸素が導電体 2 4 0 a および導電体 2 4 0 b に吸収されるのを防ぐことができる。

10

#### 【 0 1 1 9 】

絶縁体 2 4 1 a および絶縁体 2 4 1 b としては、例えば、窒化シリコン、酸化アルミニウム、または窒化酸化シリコンなどの絶縁体を用いればよい。絶縁体 2 4 1 a および絶縁体 2 4 1 b は、絶縁体 2 7 4 、絶縁体 2 8 3 、絶縁体 2 8 2 、絶縁体 2 8 0 、絶縁体 2 7 3 、および絶縁体 2 7 2 に接して設けられるので、絶縁体 2 8 0 などから水または水素などの不純物が、導電体 2 4 0 a および導電体 2 4 0 b を通じて酸化物 2 3 0 に混入するのを抑制することができる。特に、窒化シリコンは水素に対するブロッキング性が高いので好適である。また、絶縁体 2 8 0 に含まれる酸素が導電体 2 4 0 a および導電体 2 4 0 b に吸収されるのを防ぐことができる。

20

#### 【 0 1 2 0 】

また、導電体 2 4 0 a の上面、および導電体 2 4 0 b の上面に接して配線として機能する導電体 2 4 6 ( 導電体 2 4 6 a 、および導電体 2 4 6 b ) を配置してもよい。導電体 2 4 6 は、タンゲステン、銅、またはアルミニウムを主成分とする導電性材料を用いることが好ましい。また、当該導電体 2 4 6 は、積層構造としてもよく、例えば、チタンまたは窒化チタンと上記導電性材料との積層としてもよい。なお、当該導電体 2 4 6 は、絶縁体に設けられた開口に埋め込むように形成してもよい。

30

#### 【 0 1 2 1 】

#### [トランジスタ 2 0 0 ]

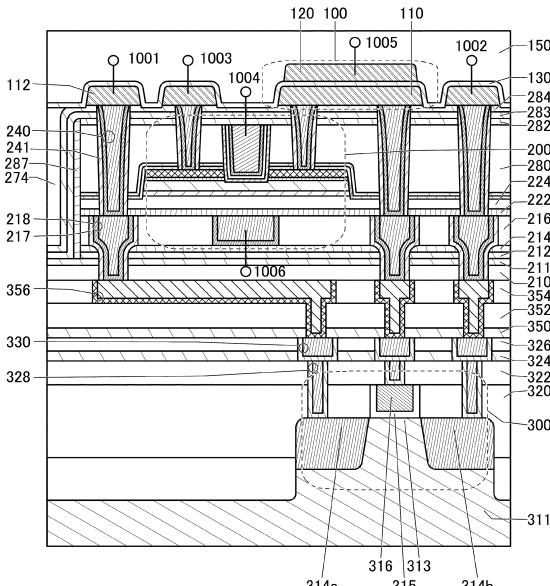

図 4 に示すように、トランジスタ 2 0 0 は、絶縁体 2 1 6 と、導電体 2 0 5 ( 導電体 2 0 5 a 、および導電体 2 0 5 b ) と、絶縁体 2 2 2 と、絶縁体 2 2 4 と、酸化物 2 3 0 ( 酸化物 2 3 0 a 、酸化物 2 3 0 b 、および酸化物 2 3 0 c ) と、導電体 2 4 2 ( 導電体 2 4 2 a 、および導電体 2 4 2 b ) と、酸化物 2 4 3 ( 酸化物 2 4 3 a 、および酸化物 2 4 3 b ) と、絶縁体 2 7 2 と、絶縁体 2 7 3 と、絶縁体 2 5 0 と、導電体 2 6 0 ( 導電体 2 6 0 a 、および導電体 2 6 0 b ) と、を有する。

#### 【 0 1 2 2 】

トランジスタ 2 0 0 において、導電体 2 6 0 は、トランジスタの第 1 のゲートとして機能し、導電体 2 0 5 は、トランジスタの第 2 のゲートとして機能する。また、導電体 2 4 2 a 、および導電体 2 4 2 b は、ソース電極またはドレイン電極として機能する。

40

#### 【 0 1 2 3 】

酸化物 2 3 0 は、チャネル形成領域を有する半導体として機能する。

#### 【 0 1 2 4 】

絶縁体 2 5 0 は、第 1 のゲート絶縁体として機能し、絶縁体 2 2 2 、および絶縁体 2 2 4 は、第 2 のゲート絶縁体として機能する。

#### 【 0 1 2 5 】

ここで、図 4 に示すトランジスタ 2 0 0 は、絶縁体 2 8 0 などの層間膜に設けた開口部内に、導電体 2 6 0 が、絶縁体 2 5 0 を介して、自己整合的に形成される。

50

**【 0 1 2 6 】**

つまり、導電体 260 は、絶縁体 250 を介して、絶縁体 280 を含む層間膜に設けた開口を埋めるように形成されるため、導電体 242a と導電体 242b の間の領域に、導電体 260 の位置合わせが不要となる。

**【 0 1 2 7 】**

また、絶縁体 280 を含む層間膜に設けた開口内に、酸化物 230c を設けることが好みしい。従って、絶縁体 250、および導電体 260 は、酸化物 230c を介して、酸化物 230b、および酸化物 230a の積層構造と重畳する領域を有する。当該構造とすることで、酸化物 230c と絶縁体 250 とを連続成膜により、形成することが可能となるため、酸化物 230 と絶縁体 250 との界面を清浄に保つことができる。従って、界面散乱によるキャリア伝導への影響が小さくなり、トランジスタ 200 は高いオン電流、および高い周波数特性を得ることができる。

10

**【 0 1 2 8 】**

また、図 4 に示すトランジスタ 200 は、導電体 260 の底面、および側面が絶縁体 250 に接する。また、絶縁体 250 の底面、および側面は、酸化物 230c と接する。

**【 0 1 2 9 】**

また、トランジスタ 200 は、図 4 (B)、図 4 (C)、および図 4 (D) に示すように、絶縁体 282 と、酸化物 230c とが、直接接する構造となっている。当該構造とすることで、絶縁体 280 に含まれる酸素の導電体 260 への拡散を抑制することができる。

20

**【 0 1 3 0 】**

従って、絶縁体 280 に含まれる酸素は、酸化物 230c を介して、酸化物 230a および酸化物 230b へ効率よく供給することができるので、酸化物 230a 中および酸化物 230b 中の酸素欠損を低減し、トランジスタ 200 の電気特性および信頼性を向上させることができる。

**【 0 1 3 1 】**

以下では、本発明の一態様に係るトランジスタ 200 を有する半導体装置の詳細な構成について説明する。

**【 0 1 3 2 】**

トランジスタ 200 は、チャネル形成領域を含む酸化物 230 (酸化物 230a、酸化物 230b、および酸化物 230c) に、酸化物半導体として機能する金属酸化物 (以下、酸化物半導体ともいう) を用いることが好みしい。

30

**【 0 1 3 3 】**

例えば、酸化物半導体として機能する金属酸化物は、エネルギーギャップが 2 eV 以上、好みしくは 2.5 eV 以上のものを用いることが好みしい。エネルギーギャップの大きい金属酸化物を用いることで、トランジスタ 200 の非導通状態におけるリーク電流 (オフ電流) を極めて小さくすることができる。このようなトランジスタを用いることで、低消費電力の半導体装置を提供できる。

**【 0 1 3 4 】**

具体的には、酸化物 230 として、In - M - Zn 酸化物 (元素 M は、アルミニウム、ガリウム、イットリウム、錫、銅、バナジウム、ベリリウム、ホウ素、チタン、鉄、ニッケル、ゲルマニウム、ジルコニア、モリブデン、ランタン、セリウム、ネオジム、ハフニウム、タンタル、タンクスティン、またはマグネシウムなどから選ばれた一種、または複数種) 等の金属酸化物を用いるとよい。特に、元素 M は、アルミニウム、ガリウム、イットリウム、または錫を用いるとよい。また、酸化物 230 として、In 酸化物、In - M 酸化物、In - Zn 酸化物、または M - Zn 酸化物を用いてもよい。

40

**【 0 1 3 5 】**

図 4 に示すように、酸化物 230 は、絶縁体 224 上の酸化物 230a と、酸化物 230a 上の酸化物 230b と、酸化物 230b 上に配置され、少なくとも一部が酸化物 230b の上面に接する酸化物 230c と、を有することが好みしい。ここで、酸化物 230

50

c の側面は、酸化物 243a、酸化物 243b、導電体 242a、導電体 242b、絶縁体 272、絶縁体 273、および絶縁体 280 に接して設けられていることが好ましい。

#### 【0136】

つまり、酸化物 230 は、酸化物 230a と、酸化物 230a 上の酸化物 230b と、酸化物 230b 上の酸化物 230c と、を有する。酸化物 230b 下に酸化物 230a を有することで、酸化物 230a よりも下方に形成された構造物から、酸化物 230b への不純物の拡散を抑制することができる。また、酸化物 230b 上に酸化物 230c を有することで、酸化物 230c よりも上方に形成された構造物から、酸化物 230b への不純物の拡散を抑制することができる。

#### 【0137】

なお、トランジスタ 200 では、チャネル形成領域と、その近傍において、酸化物 230a、酸化物 230b、および酸化物 230c の 3 層を積層する構成について示しているが、本発明はこれに限られるものではない。例えば、酸化物 230b の単層、酸化物 230b と酸化物 230a の 2 層構造、酸化物 230b と酸化物 230c の 2 層構造、または 4 層以上の積層構造を設ける構成にしてもよい。例えば、酸化物 230c を 2 層構造にして、4 層の積層構造を設ける構成にしてもよい。

10

#### 【0138】

また、酸化物 230 は、各金属原子の原子数比が異なる複数の酸化物層の積層構造を有することが好ましい。具体的には、酸化物 230a に用いる金属酸化物において、構成元素中の元素 M の原子数比が、酸化物 230b に用いる金属酸化物における、構成元素中の元素 M の原子数比より、大きいことが好ましい。また、酸化物 230a に用いる金属酸化物において、In に対する元素 M の原子数比が、酸化物 230b に用いる金属酸化物における、In に対する元素 M の原子数比より大きいことが好ましい。また、酸化物 230b に用いる金属酸化物において、元素 M に対する In の原子数比が、酸化物 230a に用いる金属酸化物における、元素 M に対する In の原子数比より大きいことが好ましい。また、酸化物 230c は、酸化物 230a または酸化物 230b に用いることができる金属酸化物を、用いることができる。

20

#### 【0139】

具体的には、酸化物 230a として、In : Ga : Zn = 1 : 3 : 4 [ 原子数比 ]、またはその近傍の組成、あるいは 1 : 1 : 0 . 5 [ 原子数比 ]、またはその近傍の組成の金属酸化物を用いればよい。また、酸化物 230b として、In : Ga : Zn = 4 : 2 : 3 [ 原子数比 ]、またはその近傍の組成、あるいは 1 : 1 : 1 [ 原子数比 ]、またはその近傍の組成の金属酸化物を用いればよい。また、酸化物 230c として、In : Ga : Zn = 1 : 3 : 4 [ 原子数比 ]、またはその近傍の組成、In : Ga : Zn = 4 : 2 : 3 [ 原子数比 ]、またはその近傍の組成、In : Ga : Zn = 5 : 1 : 3 [ 原子数比 ]、またはその近傍の組成、In : Ga : Zn = 10 : 1 : 3 [ 原子数比 ]、またはその近傍の組成、Ga : Zn = 2 : 1 [ 原子数比 ]、またはその近傍の組成、あるいは Ga : Zn = 2 : 5 [ 原子数比 ]、またはその近傍の組成の金属酸化物を用いればよい。また、酸化物 230c を積層構造とする場合の具体例としては、In : Ga : Zn = 4 : 2 : 3 [ 原子数比 ]、またはその近傍の組成と、In : Ga : Zn = 1 : 3 : 4 [ 原子数比 ]、またはその近傍の組成との積層構造、In : Ga : Zn = 4 : 2 : 3 [ 原子数比 ]、またはその近傍の組成、と In : Ga : Zn = 5 : 1 : 3 [ 原子数比 ]、またはその近傍の組成との積層構造、Ga : Zn = 2 : 1 [ 原子数比 ]、またはその近傍の組成と、In : Ga : Zn = 4 : 2 : 3 [ 原子数比 ]、またはその近傍の組成との積層構造、Ga : Zn = 2 : 5 [ 原子数比 ]、またはその近傍の組成との積層構造、酸化ガリウムと、In : Ga : Zn = 4 : 2 : 3 [ 原子数比 ]、またはその近傍の組成との積層構造などが挙げられる。なお、近傍の組成とは、所望の原子数比の ± 30 % の範囲を含む。

30

#### 【0140】

また、酸化物 230b は、結晶性を有していてもよい。例えば、後述する CAAAC-O

40

50

S(c-axis aligned crystalline oxide semiconductor)を用いることが好ましい。CAAC-OSなどの結晶性を有する酸化物は、不純物や欠陥(酸素欠損など)が少なく、結晶性の高い、緻密な構造を有している。よって、ソース電極またはドレイン電極による、酸化物230bからの酸素の引き抜きを抑制することができる。また、加熱処理を行っても、酸化物230bから酸素が、引き抜かれることを低減できるので、トランジスタ200は、製造工程における高い温度(所謂サーマルバジェット)に対して安定である。

#### 【0141】

導電体205は、酸化物230、および導電体260と、重なるように配置する。また、導電体205は、絶縁体216に埋め込まれて設けることが好ましい。

10

#### 【0142】

ここで、導電体260は、第1のゲート(トップゲートともいう)として機能する場合がある。また、導電体205は、第2のゲート(ボトムゲートともいう)として機能する場合がある。

#### 【0143】

導電体205がゲート電極として機能する場合、導電体205に印加する電位を、導電体260に印加する電位と、連動させず、独立して変化させることで、トランジスタ200のしきい値電圧(V<sub>th</sub>)を制御することができる。特に、導電体205に負の電位を印加することにより、トランジスタ200のV<sub>th</sub>をより大きくし、オフ電流を低減することが可能となる。したがって、導電体205に負の電位を印加したほうが、印加しない場合よりも、導電体260に印加する電位が0Vのときのドレイン電流を小さくすることができます。

20

#### 【0144】

なお、導電体205は、図4(A)に示すように、酸化物230の導電体242aおよび導電体242bと重ならない領域の大きさよりも、大きく設けるとよい。特に、図4(C)に示すように、導電体205は、酸化物230のチャネル幅方向と交わる端部よりも外側の領域においても、延伸していることが好ましい。つまり、酸化物230のチャネル幅方向における側面の外側において、導電体205と、導電体260とは、絶縁体を介して重畠していることが好ましい。または、導電体205を大きく設けることによって、導電体205形成以降の作製工程のプラズマを用いた処理において、局所的なチャージング(チャージアップと言う)の緩和ができる場合がある。ただし、本発明の一態様はこれに限定されない。導電体205は、少なくとも導電体242aと、導電体242bとの間に位置する酸化物230と重畠すればよい。

30

#### 【0145】

また、絶縁体224の底面を基準として、酸化物230aおよび酸化物230bと、導電体260とが、重ならない領域における導電体260の底面の高さは、酸化物230bの底面の高さより低い位置に配置されていることが好ましい。

#### 【0146】

図に示すように、ゲートとして機能する導電体260は、チャネル形成領域の酸化物230bの側面および上面を酸化物230cおよび絶縁体250を介して覆う構造とすることにより、導電体260から生じる電界を、酸化物230bに生じるチャネル形成領域全体に作用させやすくなる。従って、トランジスタ200のオン電流を増大させ、周波数特性を向上させることができる。本明細書において、第1のゲート、および第2のゲートの電界によって、チャネル形成領域を電気的に取り囲むトランジスタの構造を、surrounded channel(S-channel)構造とよぶ。

40

#### 【0147】

また、導電体205aは、水または水素などの不純物および酸素の透過を抑制する導電体が好ましい。例えば、チタン、窒化チタン、タンタル、または窒化タンタルを用いることができる。また、導電体205bは、タングステン、銅、またはアルミニウムを主成分とする導電性材料を用いることが好ましい。なお、導電体205を2層で図示したが、3

50

層以上の多層構造としてもよい。

**【0148】**

ここで、酸化物半導体と、酸化物半導体の下層に位置する絶縁体、または導電体と、酸化物半導体の上層に位置する絶縁体、または導電体とを、大気開放を行わずに、異なる膜種を連続成膜することで、不純物（特に、水素、水）の濃度が低減された、実質的に高純度真性である酸化物半導体膜を成膜することができるので好ましい。

**【0149】**

絶縁体222、絶縁体272、および絶縁体273の少なくとも一つは、水または水素などの不純物が、基板側から、または、上方からトランジスタ200に混入するのを抑制するバリア絶縁膜として機能することが好ましい。したがって、絶縁体222、絶縁体272、および絶縁体273の少なくとも一つは、水素原子、水素分子、水分子、窒素原子、窒素分子、酸化窒素分子（N<sub>2</sub>O、NO、NO<sub>2</sub>など）、銅原子などの不純物の拡散を抑制する機能を有する（上記不純物が透過しにくい）絶縁性材料を用いることが好ましい。または、酸素（例えば、酸素原子、酸素分子などの少なくとも一）の拡散を抑制する機能を有する（上記酸素が透過しにくい）絶縁性材料を用いることが好ましい。

10

**【0150】**

例えば、絶縁体273として、窒化シリコンまたは窒化酸化シリコンなどを用い、および絶縁体272として、酸化アルミニウムまたは酸化ハフニウムなどを用いることが好ましい。

**【0151】**

これにより、水または水素などの不純物が絶縁体222を介して、基板側からトランジスタ200側に拡散するのを抑制することができる。または、絶縁体224などに含まれる酸素が、絶縁体222を介して基板側に、拡散するのを抑制することができる。

20

**【0152】**

また、水または水素などの不純物が、絶縁体272および絶縁体273を介して配置されている絶縁体280などからトランジスタ200側に拡散するのを抑制することができる。このように、トランジスタ200を、水または水素などの不純物、および酸素の拡散を抑制する機能を有する絶縁体272、および絶縁体273で取り囲む構造とすることが好ましい。

**【0153】**

30

絶縁体222、および絶縁体224は、ゲート絶縁体としての機能を有する。

**【0154】**

ここで、酸化物230と接する絶縁体224は、加熱により酸素を脱離することが好ましい。本明細書では、加熱により離脱する酸素を過剰酸素と呼ぶことがある。例えば、絶縁体224は、酸化シリコンまたは酸化窒化シリコンなどを適宜用いればよい。酸素を含む絶縁体を酸化物230に接して設けることにより、酸化物230中の酸素欠損を低減し、トランジスタ200の信頼性を向上させることができる。

**【0155】**

絶縁体224として、具体的には、加熱により一部の酸素が脱離する酸化物材料を用いることが好ましい。加熱により酸素を脱離する酸化物とは、昇温脱離ガス分析（TDS（Thermal Desorption Spectroscopy）分析）にて、酸素分子の脱離量が $1.0 \times 10^{18}$  molecules/cm<sup>3</sup>以上、好ましくは $1.0 \times 10^{19}$  molecules/cm<sup>3</sup>以上、さらに好ましくは $2.0 \times 10^{19}$  molecules/cm<sup>3</sup>以上、または $3.0 \times 10^{20}$  molecules/cm<sup>3</sup>以上である酸化物である。なお、上記TDS分析時における膜の表面温度としては100℃以上700℃以下、または100℃以上400℃以下の範囲が好ましい。

40

**【0156】**

絶縁体222は、水または水素などの不純物が、基板側からトランジスタ200に混入するのを抑制するバリア絶縁膜として機能することが好ましい。例えば、絶縁体222は、絶縁体224より水素透過性が低いことが好ましい。絶縁体222、および絶縁体28

50

3によって、絶縁体224および酸化物230などを囲むことにより、外方から水または水素などの不純物がトランジスタ200に侵入することを抑制することができる。

#### 【0157】

さらに、絶縁体222は、酸素（例えば、酸素原子、酸素分子などの少なくとも一）の拡散を抑制する機能を有する（上記酸素が透過しにくい）ことが好ましい。例えば、絶縁体222は、絶縁体224より酸素透過性が低いことが好ましい。絶縁体222が、酸素や不純物の拡散を抑制する機能を有することで、酸化物230が有する酸素が、絶縁体222より下側へ拡散することを低減できるので、好ましい。また、導電体205が、絶縁体224や、酸化物230が有する酸素と反応することを抑制することができる。

#### 【0158】

絶縁体222は、絶縁性材料であるアルミニウムおよびハフニウムの一方または双方の酸化物を含む絶縁体を用いるとよい。アルミニウムおよびハフニウムの一方または双方の酸化物を含む絶縁体として、酸化アルミニウム、酸化ハフニウム、アルミニウムおよびハフニウムを含む酸化物（ハフニウムアルミネート）などを用いることが好ましい。このような材料を用いて絶縁体222を形成した場合、絶縁体222は、酸化物230からの酸素の放出や、トランジスタ200の周辺部から酸化物230への水素等の不純物の混入を抑制する層として機能する。

10

#### 【0159】

または、これらの絶縁体に、例えば、酸化アルミニウム、酸化ビスマス、酸化ゲルマニウム、酸化ニオブ、酸化シリコン、酸化チタン、酸化タンゲステン、酸化イットリウム、酸化ジルコニアを添加してもよい。またはこれらの絶縁体を窒化処理してもよい。上記の絶縁体に酸化シリコン、酸化窒化シリコンまたは窒化シリコンを積層して用いてよい。

20

#### 【0160】

また、絶縁体222は、例えば、酸化アルミニウム、酸化ハフニウム、酸化タンタル、酸化ジルコニア、チタン酸ジルコン酸鉛（PZT）、チタン酸ストロンチウム（SrTiO<sub>3</sub>）または（Ba, Sr）TiO<sub>3</sub>（BST）などのいわゆるhigh-k材料を含む絶縁体を単層または積層で用いてよい。トランジスタの微細化、および高集積化が進むと、ゲート絶縁体の薄膜化により、リーク電流などの問題が生じる場合がある。ゲート絶縁体として機能する絶縁体にhigh-k材料を用いることで、物理膜厚を保ちながら、トランジスタ動作時のゲート電位の低減が可能となる。

30

#### 【0161】

なお、絶縁体222、および絶縁体224が、2層以上の積層構造を有していてよい。その場合、同じ材料からなる積層構造に限定されず、異なる材料からなる積層構造でもよい。

#### 【0162】

また、酸化物230bと、ソース電極またはドレイン電極として機能する導電体242（導電体242aおよび導電体242b）と、の間に酸化物243（酸化物243aおよび酸化物243b）を配置してもよい。導電体242と、酸化物230とが接しない構成となるので、導電体242が、酸化物230の酸素を吸収することを抑制できる。つまり、導電体242の酸化を防止することで、導電体242の導電率の低下を抑制することができる。従って、酸化物243は、導電体242の酸化を抑制する機能を有することが好ましい。

40

#### 【0163】

従って、酸化物243は、酸素の透過を抑制する機能を有することが好ましい。ソース電極やドレイン電極として機能する導電体242と酸化物230bとの間に酸素の透過を抑制する機能を有する酸化物243を配置することで、導電体242と、酸化物230bとの間の電気抵抗が低減されるので好ましい。このような構成とすることで、トランジスタ200の電気特性およびトランジスタ200の信頼性を向上させることができる。

#### 【0164】

50

酸化物 243 として、元素Mを有する金属酸化物を用いてもよい。特に、元素Mは、アルミニウム、ガリウム、イットリウム、または錫を用いるとよい。酸化物 243 は、酸化物 230b よりも元素Mの濃度が高いことが好ましい。また、酸化物 243 として、酸化ガリウムを用いてもよい。また、酸化物 243 として、In - M - Zn 酸化物等の金属酸化物を用いてもよい。具体的には、酸化物 243 に用いる金属酸化物において、In に対する元素Mの原子数比が、酸化物 230b に用いる金属酸化物における、In に対する元素Mの原子数比より大きいことが好ましい。また、酸化物 243 の膜厚は、0.5 nm 以上 5 nm 以下が好ましく、より好ましくは、1 nm 以上 3 nm 以下である。また、酸化物 243 は、結晶性を有すると好ましい。酸化物 243 が結晶性を有する場合、酸化物 230 中の酸素の放出を好適に抑制することが出来る。例えば、酸化物 243 としては、六方晶などの結晶構造であれば、酸化物 230 中の酸素の放出を抑制できる場合がある。

#### 【0165】

なお、酸化物 243 は必ずしも設けなくてもよい。その場合、導電体 242（導電体 242a、および導電体 242b）と酸化物 230 とが接することで、酸化物 230 中の酸素が導電体 242 へ拡散し、導電体 242 が酸化する場合がある。導電体 242 が酸化することで、導電体 242 の導電率が低下する蓋然性が高い。なお、酸化物 230 中の酸素が導電体 242 へ拡散することを、導電体 242 が酸化物 230 中の酸素を吸収する、と言い換えることができる。

#### 【0166】

また、酸化物 230 中の酸素が導電体 242（導電体 242a、および導電体 242b）へ拡散することで、導電体 242a と酸化物 230b との間、および、導電体 242b と酸化物 230b との間に異層が形成される場合がある。当該異層は、導電体 242 よりも酸素を多く含むため、当該異層は絶縁性を有すると推定される。このとき、導電体 242 と、当該異層と、酸化物 230b との 3 層構造は、金属 - 絶縁体 - 半導体からなる 3 層構造とみなすことができ、MIS (Metal - Insulator - Semiconductor) 構造と呼ぶ、または MIS 構造を主としたダイオード接合構造と呼ぶ場合がある。

#### 【0167】

なお、上記異層は、導電体 242 と酸化物 230b との間に形成されることに限られず、例えば、異層が、導電体 242 と酸化物 230c との間に形成される場合や、導電体 242 と酸化物 230b との間、および導電体 242 と酸化物 230c との間に形成される場合がある。

#### 【0168】

酸化物 243 上には、ソース電極、およびドレイン電極として機能する導電体 242（導電体 242a、および導電体 242b）が設けられる。導電体 242 の膜厚は、例えば、1 nm 以上 50 nm 以下、好ましくは 2 nm 以上 25 nm 以下、とすればよい。

#### 【0169】

導電体 242 としては、アルミニウム、クロム、銅、銀、金、白金、タンタル、ニッケル、チタン、モリブデン、タングステン、ハフニウム、バナジウム、ニオブ、マンガン、マグネシウム、ジルコニア、ベリリウム、インジウム、ルテニウム、イリジウム、ストロンチウム、ランタンから選ばれた金属元素、または上述した金属元素を成分とする合金か、上述した金属元素を組み合わせた合金等を用いることが好ましい。例えば、窒化タンタル、窒化チタン、タングステン、チタンとアルミニウムを含む窒化物、タンタルとアルミニウムを含む窒化物、酸化ルテニウム、窒化ルテニウム、ストロンチウムとルテニウムを含む酸化物、ランタンとニッケルを含む酸化物などを用いることが好ましい。また、窒化タンタル、窒化チタン、チタンとアルミニウムを含む窒化物、タンタルとアルミニウムを含む窒化物、酸化ルテニウム、窒化ルテニウム、ストロンチウムとルテニウムを含む酸化物、ランタンとニッケルを含む酸化物は、酸化しにくい導電性材料、または、酸素を吸収しても導電性を維持する材料であるため、好ましい。

#### 【0170】

10

20

30

40

50

絶縁体 272 は、導電体 242 上面に接して設けられており、バリア層として機能することが好ましい。当該構成にすることで、導電体 242 による、絶縁体 280 が有する過剰酸素の吸収を抑制することができる。また、導電体 242 の酸化を抑制することで、トランジスタ 200 と配線とのコンタクト抵抗の増加を抑制することができる。よって、トランジスタ 200 に良好な電気特性および信頼性を与えることができる。

#### 【0171】

従って、絶縁体 272 は、酸素の拡散を抑制する機能を有することが好ましい。例えば、絶縁体 272 は、絶縁体 280 よりも酸素の拡散を抑制しやすいことが好ましい。絶縁体 272 としては、例えば、アルミニウムおよびハフニウムの一方または双方の酸化物を含む絶縁体を成膜するとよい。また、絶縁体 272 としては、例えば、窒化アルミニウムを含む絶縁体を用いればよい。

10

#### 【0172】

図4(B)、(D)に示すように、絶縁体 272 は、導電体 242b の上面の一部、および導電体 242b の側面と接する。また、絶縁体 272 は、導電体 242a の上面の一部、および導電体 242a の側面と接する。また、絶縁体 272 上に絶縁体 273 が配置されている。このようにすることで、例えば絶縁体 280 に添加された酸素が、導電体 242 に吸収されることを抑制することができる。

#### 【0173】

絶縁体 250 は、ゲート絶縁体として機能する。絶縁体 250 は、酸化物 230c の上面に接して配置することが好ましい。絶縁体 250 は、酸化シリコン、酸化窒化シリコン、窒化酸化シリコン、窒化シリコン、フッ素を添加した酸化シリコン、炭素を添加した酸化シリコン、炭素および窒素を添加した酸化シリコン、空孔を有する酸化シリコンを用いることができる。特に、酸化シリコン、および酸化窒化シリコンは熱に対し安定であるため好ましい。

20

#### 【0174】

絶縁体 224 と同様に、絶縁体 250 は、加熱により酸素が放出される絶縁体を用いて形成することが好ましい。加熱により酸素が放出される絶縁体を、絶縁体 250 として、酸化物 230c の上面に接して設けることにより、酸化物 230b のチャネル形成領域に効果的に酸素を供給することができる。また、絶縁体 224 と同様に、絶縁体 250 中の水または水素などの不純物濃度が低減されていることが好ましい。絶縁体 250 の膜厚は、1 nm 以上 20 nm 以下とするのが好ましい。

30

#### 【0175】

また、絶縁体 250 と導電体 260 との間に金属酸化物を設けてもよい。当該金属酸化物は、絶縁体 250 から導電体 260 への酸素拡散を抑制することが好ましい。酸素の拡散を抑制する金属酸化物を設けることで、絶縁体 250 から導電体 260 への酸素の拡散が抑制される。つまり、酸化物 230 へ供給する酸素量の減少を抑制することができる。また、絶縁体 250 の酸素による導電体 260 の酸化を抑制することができる。

30

#### 【0176】

また、当該金属酸化物は、ゲート絶縁体の一部としての機能を有する場合がある。したがって、絶縁体 250 に酸化シリコンや酸化窒化シリコンなどを用いる場合、当該金属酸化物は、比誘電率が高い hig h - k 材料である金属酸化物を用いることが好ましい。ゲート絶縁体を、絶縁体 250 と当該金属酸化物との積層構造とすることで、熱に対して安定、かつ比誘電率の高い積層構造とすることができます。したがって、ゲート絶縁体の物理膜厚を保持したまま、トランジスタ動作時に印加するゲート電位の低減化が可能となる。また、ゲート絶縁体として機能する絶縁体の等価酸化膜厚 (EOT) の薄膜化が可能となる。

40

#### 【0177】

具体的には、ハフニウム、アルミニウム、ガリウム、イットリウム、ジルコニウム、タンゲステン、チタン、タンタル、ニッケル、ゲルマニウム、または、マグネシウムなどから選ばれた一種、または二種以上が含まれた金属酸化物を用いることができる。特に、ア

50

ルミニウム、またはハフニウムの一方または双方の酸化物を含む絶縁体である、酸化アルミニウム、酸化ハフニウム、アルミニウムおよびハフニウムを含む酸化物（ハフニウムアルミネート）などを用いることが好ましい。

#### 【0178】

または、当該金属酸化物は、ゲートの一部としての機能を有する場合がある。この場合は、酸素を含む導電性材料をチャネル形成領域側に設けるとよい。酸素を含む導電性材料をチャネル形成領域側に設けることで、当該導電性材料から離脱した酸素がチャネル形成領域に供給されやすくなる。

#### 【0179】

特に、ゲートとして機能する導電体として、チャネルが形成される金属酸化物に含まれる金属元素および酸素を含む導電性材料を用いることが好ましい。また、前述した金属元素および窒素を含む導電性材料を用いてもよい。また、インジウム錫酸化物、酸化タンゲステンを含むインジウム酸化物、酸化タンゲステンを含むインジウム亜鉛酸化物、酸化チタンを含むインジウム酸化物、酸化チタンを含むインジウム錫酸化物、インジウム亜鉛酸化物、シリコンを添加したインジウム錫酸化物を用いてもよい。また、窒素を含むインジウムガリウム亜鉛酸化物を用いてもよい。このような材料を用いることで、チャネルが形成される金属酸化物に含まれる水素を捕獲することができる場合がある。または、外方の絶縁体などから混入する水素を捕獲することができる場合がある。

#### 【0180】

導電体260は、図4では2層構造として示しているが、単層構造でもよいし、3層以上の積層構造であってもよい。

#### 【0181】

導電体260aは、水素原子、水素分子、水分子、窒素原子、窒素分子、酸化窒素分子（N<sub>2</sub>O、NO、NO<sub>2</sub>など）、銅原子などの不純物の拡散を抑制する機能を有する導電性材料を用いることが好ましい。または、酸素（例えば、酸素原子、酸素分子などの少なくとも一）の拡散を抑制する機能を有する導電性材料を用いることが好ましい。

#### 【0182】

また、導電体260aが酸素の拡散を抑制する機能を持つことにより、絶縁体250に含まれる酸素により、導電体260bが酸化して導電率が低下することを抑制することができる。酸素の拡散を抑制する機能を有する導電性材料としては、例えば、タンタル、窒化タンタル、ルテニウム、または酸化ルテニウムなどを用いることが好ましい。

#### 【0183】

また、導電体260bは、タンゲステン、銅、またはアルミニウムを主成分とする導電性材料を用いることが好ましい。また、導電体260は、配線としても機能するため、導電性が高い導電体を用いることが好ましい。例えば、タンゲステン、銅、またはアルミニウムを主成分とする導電性材料を用いることができる。また、導電体260bは積層構造としてもよく、例えば、チタンまたは窒化チタンと上記導電性材料との積層構造としてもよい。

#### 【0184】

<<半導体装置の変形例1>>

以下では、図5を用いて、本発明の一態様に係るトランジスタ200を有する半導体装置の一例について説明する。

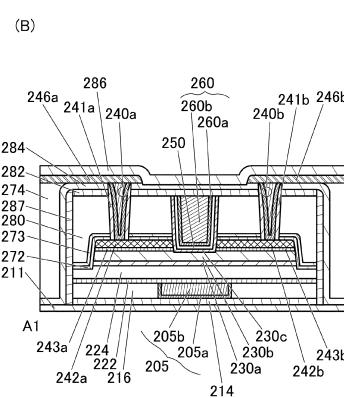

#### 【0185】

ここで、図5の（A）は上面図を示す。また、図5（B）は図5（A）に示すA1-A2の一点鎖線で示す部位に対応する断面図である。また、図5（C）は、図5（A）にA3-A4の一点鎖線で示す部位に対応する断面図である。また、図5（D）は、図5（A）にA5-A6の一点鎖線で示す部位に対応する断面図である。図5（A）の上面図では、図の明瞭化のために一部の要素を省いて図示している。

#### 【0186】

図5に示す半導体装置は、図4に示した半導体装置とは、絶縁体212と絶縁体283

10

20

30

40

50

とが接する構造であることが異なる。具体的には、絶縁体 212 が、絶縁体 273 の下方に延伸するように設けるとよい。また、絶縁体 212 において、トランジスタ 200 と重畠する領域の膜厚は、絶縁体 283 と接する領域の膜厚よりも、厚い場合がある。

#### 【0187】

<<半導体装置の変形例 2>>

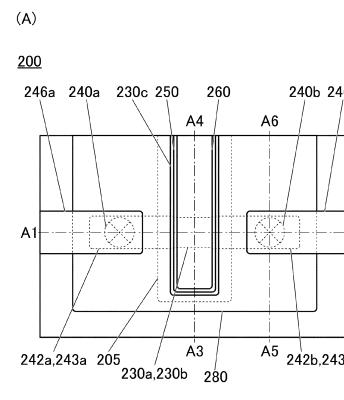

以下では、図 6 を用いて、本発明の一態様に係るトランジスタ 200 を有する半導体装置の一例について説明する。

#### 【0188】

ここで、図 6 の (A) は上面図を示す。また、図 6 (B) は図 6 (A) に示す A1 - A2 の一点鎖線で示す部位に対応する断面図である。また、図 6 (C) は、図 6 (A) に A3 - A4 の一点鎖線で示す部位に対応する断面図である。また、図 6 (D) は、図 6 (A) に A5 - A6 の一点鎖線で示す部位に対応する断面図である。図 6 (A) の上面図では、図の明瞭化のために一部の要素を省いて図示している。10

#### 【0189】

例えば、図 6 に示すように、絶縁体 211、および絶縁体 284 を、水素原子を含まない、または水素原子の含有量が少ない、化合物ガスを用いて CVD 法により成膜する場合、絶縁体 212、および絶縁体 284 は、必ずしも設けなくともよい。

#### 【0190】

例えば、水素原子を含まない、または水素原子の含有量が少ない、化合物ガスを用いて、絶縁体 211、絶縁体 212、絶縁体 283、および絶縁体 284 を、CVD 法により、成膜することができる。つまり、絶縁体 211、絶縁体 212、絶縁体 283、および絶縁体 284 に含まれる水素濃度を低減し、酸化物半導体のチャネル形成領域に混入する水素の低減を図ってもよい。20

#### 【0191】

例えば、窒化シリコン膜などシリコン原子を含む膜の成膜では、成膜ガスとして、シリコン原子を含む分子を有するガスが主に用いられる。形成する膜に含まれる水素を低減するには、当該シリコン原子を含む分子に含まれる水素原子が少ないことが好ましく、当該シリコン原子を含む分子が水素原子を含まないことがより好ましい。もちろん、シリコン原子を含む分子を有するガス以外の成膜ガスも、含有される水素原子が少ないことが好ましく、水素原子を含まないことがより好ましい。30

#### 【0192】

上記のようなシリコン原子を含む分子を  $S_i_x - R_y$  で表すと、例えば、官能基 R として、イソシアネート基 (-N=C=O)、シアネート基 (-O-C=N)、シアノ基 (-C≡N)、ジアゾ基 (=N<sub>2</sub>)、アジド基 (-N<sub>3</sub>)、ニトロソ基 (-NO)、およびニトロ基 (-NO<sub>2</sub>) の少なくとも一つを用いることができる。例えば、1 x 3、1 y 8、とすればよい。このようなシリコン原子を含む分子としては、例えば、テトライソシアネートシラン、テトラシアネートシラン、テラシアノシラン、ヘキサイソシアネートシラン、オクタイソシアネートシラン等を用いることができる。ここでは、シリコン原子に同じ種類の官能基が結合する分子を例示したが、本実施の形態はこれに限られるものではない。シリコン原子に異なる種類の官能基が結合する構成にしてもよい。40

#### 【0193】

また、例えば、官能基 R としてハロゲン (Cl、Br、I、または F) を用いる構成にしてもよい。例えば、1 x 2、1 y 6、とすればよい。このようなシリコン原子を含む分子としては、例えば、テトラクロロシラン (SiCl<sub>4</sub>)、ヘキサクロロジシラン (Si<sub>2</sub>Cl<sub>6</sub>) 等を用いることができる。塩素を官能基とする例を示したが、塩素以外の、臭素、ヨウ素、フッ素等のハロゲンを官能基として用いてもよい。また、シリコン原子に異なる種類のハロゲンが結合する構成にしてもよい。

#### 【0194】

絶縁体 211、絶縁体 212、絶縁体 283、および絶縁体 284 の成膜は、上記のようなシリコン原子を含む分子を有するガスを用いた、化学気相成長 (CVD : Chemi

10

20

30

40

50

cal Vapor Deposition) 法によって行えばよい。CVD法は、成膜速度が比較的早いので、膜厚が厚い絶縁体の成膜を行うにあたって好適である。

#### 【0195】

CVD法として、プラズマを利用するプラズマCVD(PECVD: Plasma Enhanced CVD)法、または熱を利用する熱CVD(TCVD: Thermal CVD)法、を用いることが好ましい。熱CVD法を用いる場合、大気圧下で成膜を行なう常圧CVD(APCVD: Atmospheric Pressure CVD)法を用いてもよいし、大気圧より低い減圧状態で成膜を行う減圧CVD(LPCVD: Low Pressure CVD)法を用いてもよい。

#### 【0196】

CVD法を用いて絶縁体211、絶縁体212、絶縁体283、および絶縁体284を成膜する場合、酸化剤を用いることが好ましい。酸化剤としては、O<sub>2</sub>、O<sub>3</sub>、NO、NO<sub>2</sub>、N<sub>2</sub>O、N<sub>2</sub>O<sub>3</sub>、N<sub>2</sub>O<sub>4</sub>、N<sub>2</sub>O<sub>5</sub>、CO、CO<sub>2</sub>、などの水素原子を含まないガスを用いることが好ましい。

#### 【0197】

また、絶縁体211、絶縁体212、絶縁体283、および絶縁体284の成膜は、ALD(Atomic Layer Deposition)法によって行ってもよい。ALD法では、反応のための第1の原料ガス(以下、プリカーサと呼ぶ。前駆体、金属プリカーサとも呼ぶことができる。)と第2の原料ガス(以下、リアクタントと呼ぶ。反応剤、非金属プリカーサとも呼ぶことができる。)を交互にチャンバーに導入し、これらの原料ガスの導入を繰り返すことで成膜を行う。

#### 【0198】

ALD法は、原料ガスを切り替えながら成膜することで、原子の性質である自己制御性を利用し、一層ずつ原子を堆積することができる。よって、ALD法は、極薄膜厚の成膜、アスペクト比の高い構造への成膜、ピンホールなどの欠陥の少ない成膜、および被覆性に優れた成膜などを行うことができる。このため、ALD法は、絶縁体211、絶縁体212、絶縁体283、および絶縁体284以外にも、トランジスタ200が有する絶縁体250、および絶縁体224の成膜を行うにあたって好適である。

#### 【0199】

ALD法としては、プリカーサ及びリアクタントの反応を熱エネルギーのみで行う熱ALD(Thermal ALD)法をもちいてもよいし、プラズマ励起されたリアクタントを用いるPEALD(Plasma Enhanced ALD)法を用いてもよい。

#### 【0200】

ALD法を用いる場合、プリカーサとして、上記シリコン原子を含む分子を有するガスを、リアクタントとして、上記酸化剤を用いればよい。これにより、絶縁体216、絶縁体274、絶縁体280、絶縁体224、および絶縁体250中に取り込まれる水素の量を大きく低減することができる。

#### 【0201】

なお、上記では、シリコン原子を含む分子が水素原子を含まない例について示したが、本実施の形態はこれに限られるものではない。上記のシリコン原子を含む分子において、シリコン原子に結合する官能基の一部が水素原子に置換される構成にしてもよい。ただし、上記のシリコン原子を含む分子に含まれる水素原子は、シラン(SiH<sub>4</sub>)より少ないことが好ましい。つまり、上記のシリコン原子を含む分子は、シリコン1原子あたり3原子以下の水素原子を有することが好ましい。また、上記のシリコン原子を含む分子を有するガスが、シリコン1原子あたり3原子以下の水素原子を有すると、より好ましい。

#### 【0202】

以上のように、水素原子が低減または除去されたガスを用いた成膜方法で、絶縁体211、絶縁体212、絶縁体283、および絶縁体284の少なくとも一つ以上を成膜することで、これらの絶縁体に含まれる水素の量を低減することができる。

#### 【0203】

10

20

30

40

50

従って、トランジスタ 200、および絶縁体 280 を、水素などの不純物を捕獲、または固着する材料を用いた第1の封止構造、および水素などの不純物の拡散を抑制する材料を用いた第2の封止構造により、2重に封止する構造とすることで、当該封止された領域内の水素濃度を低減し、さらに外部から混入する水素を、絶縁体 283 および絶縁体 212 によって低減できる。

#### 【0204】

##### << 金属酸化物 >>

酸化物 230 として、酸化物半導体として機能する金属酸化物を用いることが好ましい。以下では、本発明に係る酸化物 230 に適用可能な金属酸化物について説明する。

#### 【0205】

金属酸化物は、少なくともインジウムまたは亜鉛を含むことが好ましい。特に、インジウムおよび亜鉛を含むことが好ましい。また、それらに加えて、ガリウム、イットリウム、錫などが含まれていることが好ましい。また、ホウ素、チタン、鉄、ニッケル、ゲルマニウム、ジルコニウム、モリブデン、ランタン、セリウム、ネオジム、ハフニウム、タンタル、タングステン、マグネシウムなどから選ばれた一種、または複数種が含まれていてもよい。

#### 【0206】

ここでは、金属酸化物が、インジウム、元素M および亜鉛を有する  $In - M - Zn$  酸化物である場合を考える。なお、元素M は、アルミニウム、ガリウム、イットリウム、または錫とする。そのほかの元素M に適用可能な元素としては、ホウ素、チタン、鉄、ニッケル、ゲルマニウム、ジルコニウム、モリブデン、ランタン、セリウム、ネオジム、ハフニウム、タンタル、タングステン、マグネシウムなどがある。ただし、元素M として、前述の元素を複数組み合わせても構わない場合がある。

#### 【0207】

なお、本明細書等において、窒素を有する金属酸化物も金属酸化物 (metal oxide) と総称する場合がある。また、窒素を有する金属酸化物を、金属酸窒化物 (metal oxy nitride) と呼称してもよい。

#### 【0208】

##### [ 金属酸化物の構成 ]

本発明の一態様で開示されるトランジスタに用いることができる金属酸化物である CAC - OS (Cloud - Aligned Composite Oxide Semiconductor)、及び CAAC - OS (c-axis Aligned Crystal Oxide Semiconductor) の構成について説明する。

#### 【0209】

CAC - OS 又は CAAC - metal oxide とは、材料の一部では導電性の機能と、材料の一部では絶縁性の機能とを有し、材料の全体では半導体としての機能を有する。なお、CAC - OS 又は CAAC - metal oxide を、トランジスタの活性層に用いる場合、導電性の機能は、キャリアとなる電子（又はホール）を流す機能であり、絶縁性の機能は、キャリアとなる電子を流さない機能である。導電性の機能と、絶縁性の機能とを、それぞれ相補的に作用させることで、スイッチングさせる機能 (On / Off させる機能) を CAC - OS 又は CAAC - metal oxide に付与することができる。CAC - OS 又は CAAC - metal oxide において、それぞれの機能を分離させることで、双方の機能を最大限に高めることができる。

#### 【0210】

また、CAC - OS 又は CAAC - metal oxide は、導電性領域、及び絶縁性領域を有する。導電性領域は、上述の導電性の機能を有し、絶縁性領域は、上述の絶縁性の機能を有する。また、材料中において、導電性領域と、絶縁性領域とは、ナノ粒子レベルで分離している場合がある。また、導電性領域と、絶縁性領域とは、それぞれ材料中に偏在する場合がある。また、導電性領域は、周辺がぼけてクラウド状に連結して観察される場合がある。

10

20

30

40

50

**【0211】**

また、CAC-OS又はCAC-metal oxideにおいて、導電性領域と、絶縁性領域とは、それぞれ0.5nm以上10nm以下、好ましくは0.5nm以上3nm以下のサイズで材料中に分散している場合がある。

**【0212】**

また、CAC-OS又はCAC-metal oxideは、異なるバンドギャップを有する成分により構成される。例えば、CAC-OS又はCAC-metal oxideは、絶縁性領域に起因するワイドギャップを有する成分と、導電性領域に起因するナローギャップを有する成分と、により構成される。当該構成の場合、キャリアを流す際に、ナローギャップを有する成分において、主にキャリアが流れる。また、ナローギャップを有する成分が、ワイドギャップを有する成分に相補的に作用し、ナローギャップを有する成分に連動してワイドギャップを有する成分にもキャリアが流れる。このため、上記CAC-OS又はCAC-metal oxideをトランジスタのチャネル形成領域に用いる場合、トランジスタのオン状態において高い電流駆動力、つまり大きなオン電流、及び高い電界効果移動度を得ることができる。

10

**【0213】**

すなわち、CAC-OS又はCAC-metal oxideは、マトリックス複合材(matrix composite)、又は金属マトリックス複合材(metal matrix composite)と呼称することもできる。

**【0214】**

20

**[金属酸化物の構造]**

酸化物半導体は、単結晶酸化物半導体と、それ以外の非単結晶酸化物半導体と、に分けられる。非単結晶酸化物半導体としては、例えば、CAAC-OS(c-axis aligned crystalline oxide semiconductor)、多結晶酸化物半導体、nc-OS(nanocrystalline oxide semiconductor)、擬似非晶質酸化物半導体(a-like OS: amorphous-like oxide semiconductor)及び非晶質酸化物半導体などがある。

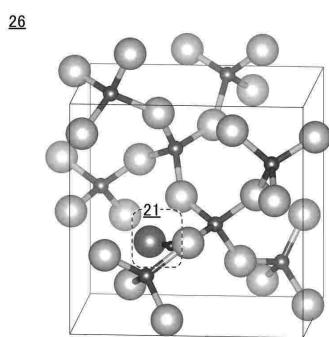

**【0215】**

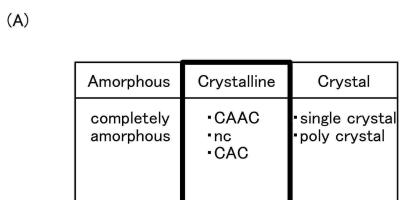

また、酸化物半導体は、結晶構造に着目した場合、上記とは異なる分類となる場合がある。ここで、酸化物半導体における、結晶構造の分類について、図31(A)を用いて説明を行う。図31(A)は、酸化物半導体、代表的にはIGZO(Inと、Gaと、Znと、を含む金属酸化物)の結晶構造の分類を説明する図である。

30

**【0216】**

図31(A)に示すように、IGZOは、大きく分けてAmorphousと、Crystallineと、Crystalと、に分類される。また、Amorphousの中には、completely amorphousが含まれる。また、Crystallineの中には、CAAC(c-axis aligned crystalline)、nc(nanocrystalline)、及びCAC(Cloud-Aligned Composite)が含まれる。また、Crystalの中には、single crystal、及びpoly crystalが含まれる。

40

**【0217】**

なお、図31(A)に示す太枠内の構造は、New crystalline phaseに属する構造である。当該構造は、Amorphousと、Crystalとの間の境界領域にある。すなわち、エネルギー的に不安定なAmorphousと、Crystallineとは全く異なる構造と言い換えることができる。

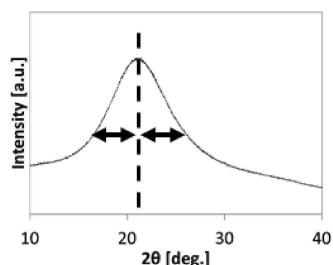

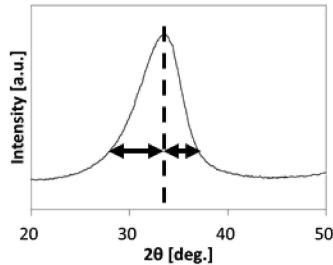

**【0218】**

なお、膜または基板の結晶構造は、X線回折(XRD:X-Ray Diffraction)像を用いて評価することができる。ここで、石英ガラス、及びCrystallineに分類される結晶構造を有するIGZO(結晶性IGZOともいう。)のXRDス

50

ペクトルを図31( B )、( C )に示す。また、図31( B )が石英ガラス、図31( C )が結晶性IGZOのXRDスペクトルである。なお、図31( C )に示す結晶性IGZOとしては、In : Ga : Zn = 4 : 2 : 3 [ 原子数比 ] の組成である。また、図31( C )に示す結晶性IGZOとしては、厚さ500nmである。

#### 【0219】

図31( B )の矢印に示すように、石英ガラスは、XRDスペクトルのピークがほぼ対称である。一方で、図31( C )の矢印に示すように、結晶性IGZOは、XRDスペクトルのピークが非対称である。XRDスペクトルのピークが非対称であることは、結晶の存在を明示している。別言すると、XRDスペクトルのピークで左右対称でないと、被測定物(ここでは結晶性IGZO)がAmorphousであるとは言えない。

10

#### 【0220】

CAAC-OSは、c軸配向性を有し、かつa-b面方向において複数のナノ結晶が連結し、歪みを有した結晶構造となっている。なお、歪みとは、複数のナノ結晶が連結する領域において、格子配列の揃った領域と、別の格子配列の揃った領域との間で格子配列の向きが変化している箇所を指す。

#### 【0221】

ナノ結晶は、六角形を基本とするが、正六角形状とは限らず、非正六角形状である場合がある。また、歪みにおいて、五角形、および七角形などの格子配列を有する場合がある。なお、CAAC-OSにおいて、歪み近傍においても、明確な結晶粒界(グレインバウンドリーもともいう。)を確認することは難しい。すなわち、格子配列の歪みによって、結晶粒界の形成が抑制されていることがわかる。これは、CAAC-OSが、a-b面方向において酸素原子の配列が稠密でないことや、金属元素が置換することで原子間の結合距離が変化することなどによって、歪みを許容することができるためである。

20

#### 【0222】

また、CAAC-OSは、インジウム、および酸素を有する層(以下、In層)と、元素M、亜鉛、および酸素を有する層(以下、(M, Zn)層)とが積層した、層状の結晶構造(層状構造ともいう)を有する傾向がある。なお、インジウムと元素Mは、互いに置換可能であり、(M, Zn)層の元素Mがインジウムと置換した場合、(In, M, Zn)層と表すこともできる。また、In層のインジウムが元素Mと置換した場合、(In, M)層と表すこともできる。

30

#### 【0223】

CAAC-OSは結晶性の高い金属酸化物である。一方、CAAC-OSは、明確な結晶粒界を確認することが難しいため、結晶粒界に起因する電子移動度の低下が起こりにくいといえる。また、金属酸化物の結晶性は不純物の混入や欠陥の生成などによって低下する場合があるため、CAAC-OSは不純物や欠陥(酸素欠損など)の少ない金属酸化物ともいえる。したがって、CAAC-OSを有する金属酸化物は、物理的性質が安定する。そのため、CAAC-OSを有する金属酸化物は熱に強く、信頼性が高い。

#### 【0224】

nc-OSは、微小な領域(例えば、1nm以上10nm以下の領域、特に1nm以上3nm以下の領域)において原子配列に周期性を有する。また、nc-OSは、異なるナノ結晶間で結晶方位に規則性が見られない。そのため、膜全体で配向性が見られない。したがって、nc-OSは、分析方法によっては、a-like OSや非晶質酸化物半導体と区別が付かない場合がある。

40

#### 【0225】

なお、インジウムと、ガリウムと、亜鉛と、を有する金属酸化物の一種である、In-Ga-Zn酸化物(以下、IGZO)は、上述のナノ結晶とすることで安定な構造をとる場合がある。特に、IGZOは、大気中では結晶成長がし難い傾向があるため、大きな結晶(ここでは、数mmの結晶、または数cmの結晶)よりも小さな結晶(例えば、上述のナノ結晶)とする方が、構造的に安定となる場合がある。

#### 【0226】

50

a - l i k e O S は、 n c - O S と非晶質酸化物半導体との間の構造を有する金属酸化物である。 a - l i k e O S は、 鬆または低密度領域を有する。 すなわち、 a - l i k e O S は、 n c - O S および C A A C - O S と比べて、 結晶性が低い。

#### 【 0 2 2 7 】

酸化物半導体（金属酸化物）は、 多様な構造をとり、 それぞれが異なる特性を有する。 本発明の一態様の酸化物半導体は、 非晶質酸化物半導体、 多結晶酸化物半導体、 a - l i k e O S 、 n c - O S 、 C A A C - O S のうち、 二種以上を有していてもよい。

#### 【 0 2 2 8 】

##### [ 不純物 ]

ここで、 金属酸化物中における各不純物の影響について説明する。

10

#### 【 0 2 2 9 】

酸化物半導体に不純物が混入すると、 欠陥準位または酸素欠損が形成される場合がある。 よって、 酸化物半導体のチャネル形成領域に不純物が混入することで、 酸化物半導体を用いたトランジスタの電気特性が変動しやすく、 信頼性が悪くなる場合がある。 また、 チャネル形成領域に酸素欠損が含まれていると、 トランジスタはノーマリーオン特性となりやすい。

#### 【 0 2 3 0 】

また、 上記欠陥準位には、 トラップ準位が含まれる場合がある。 金属酸化物のトラップ準位に捕獲された電荷は、 消失するまでに要する時間が長く、 あたかも固定電荷のように振る舞うことがある。 そのため、 トランジスタの電気特性が不安定となる場合がある。

20

#### 【 0 2 3 1 】

また、 酸化物半導体のチャネル形成領域に不純物が存在すると、 チャネル形成領域の結晶性が低くなる場合がある、 また、 チャネル形成領域に接して設けられる酸化物の結晶性が低くなる場合がある。 チャネル形成領域の結晶性が低いと、 トランジスタの安定性または信頼性が悪化する傾向がある。 また、 チャネル形成領域に接して設けられる酸化物の結晶性が低いと、 界面準位が形成され、 トランジスタの安定性または信頼性が悪化する場合がある。

#### 【 0 2 3 2 】

したがって、 トランジスタの安定性または信頼性を向上させるには、 酸化物半導体のチャネル形成領域およびその近傍の不純物濃度を低減することが有効である。 不純物としては、 水素、 窒素、 アルカリ金属、 アルカリ土類金属、 鉄、 ニッケル、 シリコン等がある。

30

#### 【 0 2 3 3 】

具体的には、 当該酸化物半導体のチャネル形成領域およびその近傍において、 S I M S により得られる上記不純物の濃度を、  $1 \times 10^{18}$  atoms / cm<sup>3</sup> 以下、 好ましくは  $2 \times 10^{16}$  atoms / cm<sup>3</sup> 以下にする。 または、 当該酸化物半導体のチャネル形成領域およびその近傍において、 E D X を用いた元素分析により得られる上記不純物の濃度を、 1 . 0 atomic % 以下にする。 なお、 当該酸化物半導体として元素 M を含む酸化物を用いる場合、 当該酸化物半導体のチャネル形成領域およびその近傍において、 元素 M に対する上記不純物の濃度比を、 0 . 10 未満、 好ましくは 0 . 05 未満にする。 ここで、 上記濃度比を算出する際に用いる元素 M の濃度は、 上記不純物の濃度を算出した領域と同じ領域の濃度でもよいし、 当該酸化物半導体中の濃度でもよい。

40

#### 【 0 2 3 4 】

また、 不純物濃度を低減した金属酸化物は、 欠陥準位密度が低いため、 トランジスタのトランジスタの電気特性が不安定となる場合がある。

#### 【 0 2 3 5 】

また、 金属酸化物中の酸素欠損に水素が入った場合、 酸素欠損と水素とが結合し V O H を形成する場合がある。 V O H はドナーとして機能し、 キャリアである電子が生成されることがある。 また、 水素の一部が金属原子と結合する酸素と結合して、 キャリアである電子を生成する場合がある。

50

**【 0 2 3 6 】**

従って、水素が多く含まれている酸化物半導体を用いたトランジスタは、ノーマリーオン特性となりやすい。また、酸化物半導体中の水素は、熱、電界などのストレスによって動きやすいため、酸化物半導体に多くの水素が含まれると、トランジスタの信頼性が悪化する恐れもある。

**【 0 2 3 7 】**

つまり、酸化物半導体中の $V_{OH}$ をできる限り低減し、高純度真性または実質的に高純度真性にすることが好ましい。このように、 $V_{OH}$ が十分低減された酸化物半導体を得るには、酸化物半導体中の水分、水素などの不純物を除去すること（脱水、脱水素化処理と記載する場合がある。）と、酸化物半導体に酸素を供給して酸素欠損を補填すること（加酸素化処理と記載する場合がある。）が重要である。 $V_{OH}$ および不純物が十分に低減された酸化物半導体をトランジスタのチャネル形成領域に用いることで、安定した電気特性を付与することができる。

10

**【 0 2 3 8 】**

また、トランジスタには、キャリア濃度の低い酸化物半導体を用いることが好ましい。酸化物半導体のキャリア濃度を低くする場合においては、酸化物半導体中の不純物濃度を低くし、欠陥準位密度を低くすればよい。本明細書等において、不純物濃度が低く、欠陥準位密度の低いことを高純度真性または実質的に高純度真性という。なお、酸化物半導体中の不純物としては、例えば、水素、窒素、アルカリ金属、アルカリ土類金属、鉄、ニッケル、シリコン等がある。

20

**【 0 2 3 9 】**

特に、酸化物半導体に含まれる水素は、金属原子と結合する酸素と反応して水になるため、酸化物半導体中に酸素欠損を形成する場合がある。酸化物半導体中のチャネル形成領域に酸素欠損が含まれていると、トランジスタはノーマリーオン特性となる場合がある。さらに、酸素欠損に水素が入った欠陥はドナーとして機能し、キャリアである電子が生成されることがある。また、水素の一部が金属原子と結合する酸素と結合して、キャリアである電子を生成する場合がある。従って、水素が多く含まれている酸化物半導体を用いたトランジスタは、ノーマリーオン特性となりやすい。

**【 0 2 4 0 】**

酸素欠損に水素が入った欠陥（ $V_{OH}$ ）は、酸化物半導体のドナーとして機能しうる。しかしながら、当該欠陥を定量的に評価することは困難である。そこで、酸化物半導体においては、ドナー濃度ではなく、キャリア濃度で評価される場合がある。よって、本明細書等では、酸化物半導体のパラメータとして、ドナー濃度ではなく、電界が印加されない状態を想定したキャリア濃度を用いる場合がある。つまり、本明細書等に記載の「キャリア濃度」は、「ドナー濃度」と言い換えることができる場合がある。

30

**【 0 2 4 1 】**

よって、酸化物半導体中の水素はできる限り低減されていることが好ましい。具体的には、酸化物半導体において、二次イオン質量分析法（S I M S : Secondary Ion Mass Spectrometry）により得られる水素濃度を、 $1 \times 10^{20}$  atoms / cm<sup>3</sup>未満、好ましくは $1 \times 10^{19}$  atoms / cm<sup>3</sup>未満、より好ましくは $5 \times 10^{18}$  atoms / cm<sup>3</sup>未満、さらに好ましくは $1 \times 10^{18}$  atoms / cm<sup>3</sup>未満とする。水素などの不純物が十分に低減された酸化物半導体をトランジスタのチャネル形成領域に用いることで、安定した電気特性を付与することができる。

40

**【 0 2 4 2 】**

また、チャネル形成領域の酸化物半導体のキャリア濃度は、 $1 \times 10^{18}$  cm<sup>-3</sup>以下であることが好ましく、 $1 \times 10^{17}$  cm<sup>-3</sup>未満であることがより好ましく、 $1 \times 10^{16}$  cm<sup>-3</sup>未満であることがさらに好ましく、 $1 \times 10^{13}$  cm<sup>-3</sup>未満であることがさらに好ましく、 $1 \times 10^{12}$  cm<sup>-3</sup>未満であることがさらに好ましい。なお、チャネル形成領域の酸化物半導体のキャリア濃度の下限値については、特に限定は無いが、例えば、 $1 \times 10^{-9}$  cm<sup>-3</sup>とすることができる。

50

**【 0 2 4 3 】**

本発明の一態様により、信頼性が良好な半導体装置を提供することができる。また、本発明の一態様により、良好な電気特性を有する半導体装置を提供することができる。また、本発明の一態様により、オン電流の大きい半導体装置を提供することができる。また、本発明の一態様により、微細化または高集積化が可能な半導体装置を提供することができる。また、本発明の一態様により、低消費電力の半導体装置を提供することができる。

**【 0 2 4 4 】**

<< その他の半導体材料 >>

酸化物 230 に用いることができる半導体材料は、上述の金属酸化物に限られない。酸化物 230 として、バンドギャップを有する半導体材料（ゼロギャップ半導体ではない半導体材料）を用いてもよい。例えば、シリコンなどの単体元素の半導体、ヒ化ガリウムなどの化合物半導体、半導体として機能する層状物質（原子層物質、2次元材料などともいう。）などを半導体材料に用いることが好ましい。特に、半導体として機能する層状物質を半導体材料に用いると好適である。

10

**【 0 2 4 5 】**

ここで、本明細書等において、層状物質とは、層状の結晶構造を有する材料群の総称である。層状の結晶構造は、共有結合やイオン結合によって形成される層が、ファンデルワールス力のような、共有結合やイオン結合よりも弱い結合を介して積層している構造である。層状物質は、単位層内における電気伝導性が高く、つまり、2次元電気伝導性が高い。半導体として機能し、かつ、2次元電気伝導性の高い材料をチャネル形成領域に用いることで、オン電流の大きいトランジスタを提供することができる。

20

**【 0 2 4 6 】**

層状物質として、グラフェン、シリセン、カルコゲン化物などがある。カルコゲン化物は、カルコゲンを含む化合物である。また、カルコゲンは、第 16 族に属する元素の総称であり、酸素、硫黄、セレン、テルル、ポロニウム、リバモリウムが含まれる。また、カルコゲン化物として、遷移金属カルコゲナイト、13 族カルコゲナイトなどが挙げられる。

**【 0 2 4 7 】**

酸化物 230 として、例えば、半導体として機能する遷移金属カルコゲナイトを用いることが好ましい。酸化物 230 として適用可能な遷移金属カルコゲナイトとして、具体的には、硫化モリブデン（代表的には  $MoS_2$ ）、セレン化モリブデン（代表的には  $MoSe_2$ ）、モリブデンテルル（代表的には  $MoTe_2$ ）、硫化タンゲステン（代表的には  $WS_2$ ）、セレン化タンゲステン（代表的には  $WSe_2$ ）、タンゲステンテルル（代表的には  $WT_{e2}$ ）、硫化ハフニウム（代表的には  $HfS_2$ ）、セレン化ハフニウム（代表的には  $HfSe_2$ ）、硫化ジルコニウム（代表的には  $ZrS_2$ ）、セレン化ジルコニウム（代表的には  $ZrSe_2$ ）などが挙げられる。

30

**【 0 2 4 8 】**

< 半導体装置の作製方法 >

次に、図 4 に示す、本発明に係るトランジスタ 200 を有する半導体装置について、作製方法を図 7 乃至図 23 を用いて説明する。また、図 7 乃至図 23 において、各図の（A）は上面図を示す。また、各図の（B）は、（A）に示す A1 - A2 の一点鎖線で示す部位に対応する断面図であり、トランジスタ 200 のチャネル長方向の断面図でもある。また、各図の（C）は、（A）に A3 - A4 の一点鎖線で示す部位に対応する断面図であり、トランジスタ 200 のチャネル幅方向の断面図でもある。また、各図の（D）は、（A）に A5 - A6 の一点鎖線で示す部位に対応する断面図である。なお、各図の（A）の上面図では、図の明瞭化のために一部の要素を省いている。

40

**【 0 2 4 9 】**

まず、基板（図示しない）を準備し、当該基板上に絶縁体 211 を成膜する。絶縁体 211 の成膜は、スパッタリング法、化学気相成長（CVD）法、分子線エピタキシー（MBE : Molecular Beam Epitaxy）法、パルスレーザ堆積（PLD

50

: P u l s e d L a s e r D e p o s i t i o n ) 法、または A L D 法などを用いて行うことができる。

#### 【 0 2 5 0 】

なお、 C V D 法は、プラズマを利用するプラズマ C V D ( P E C V D ) 法、熱を利用する熱 C V D 法、光を利用する光 C V D 法などに分類できる。さらに用いる原料ガスによって金属 C V D 法、有機金属 C V D 法に分けることができる。また、成膜時の圧力によって、大気圧下で成膜を行なう常圧 C V D 法、大気圧より低い減圧状態で成膜を行う減圧 C V D 法、に分けることができる。

#### 【 0 2 5 1 】

10

プラズマ C V D 法は、比較的低温で高品質の膜が得られる。また、熱 C V D 法は、プラズマを用いないため、被処理物へのプラズマダメージを小さくすることが可能な成膜方法である。例えば、半導体装置に含まれる配線、電極、素子（トランジスタ、容量素子など）などは、プラズマから電荷を受け取ることでチャージアップする場合がある。このとき、蓄積した電荷によって、半導体装置に含まれる配線、電極、素子などが破壊される場合がある。一方、プラズマを用いない熱 C V D 法の場合、こういったプラズマダメージが生じないため、半導体装置の歩留まりを高くすることができる。また、熱 C V D 法では、成膜中のプラズマダメージが生じないため、欠陥の少ない膜が得られる。

#### 【 0 2 5 2 】

また、 A L D 法としては、プリカーサ及びリアクタントの反応を熱エネルギーのみで行う熱 A L D ( T h e r m a l A L D ) 法、プラズマ励起されたリアクタントを用いる P 20

E A L D ( P l a s m a E n h a n c e d A L D ) 法などを用いることができる。

#### 【 0 2 5 3 】

A L D 法は、原子の性質である自己制御性を利用し、一層ずつ原子を堆積することができる、極薄の成膜が可能、アスペクト比の高い構造への成膜が可能、ピンホールなどの欠陥の少ない成膜が可能、被覆性に優れた成膜が可能、および低温での成膜が可能、などの効果がある。P E A L D 法では、プラズマを利用することで、より低温での成膜が可能となり好ましい場合がある。なお、 A L D 法で用いるプリカーサには炭素などの不純物を含むものがある。このため、 A L D 法により設けられた膜は、他の成膜法により設けられた膜と比較して、炭素などの不純物を多く含む場合がある。なお、不純物の定量は、 X 線光電子分光法 ( X P S : X - r a y P h o t o e l e c t r o n S p e c t r o s 30

c o p y ) を用いて行うことができる。

#### 【 0 2 5 4 】

C V D 法および A L D 法は、ターゲットなどから放出される粒子が堆積する成膜方法とは異なり、被処理物の表面における反応により膜が形成される成膜方法である。したがって、被処理物の形状の影響を受けにくく、良好な段差被覆性を有する成膜方法である。特に、 A L D 法は、優れた段差被覆性と、優れた厚さの均一性を有するため、アスペクト比の高い開口部の表面を被覆する場合などに好適である。ただし、 A L D 法は、比較的成膜速度が遅いため、成膜速度の速い C V D 法などの他の成膜方法と組み合わせて用いることが好ましい場合もある。

#### 【 0 2 5 5 】

40

C V D 法および A L D 法は、原料ガスの流量比によって、得られる膜の組成を制御することができる。例えば、 C V D 法および A L D 法では、原料ガスの流量比によって、任意の組成の膜を成膜することができる。また、例えば、 C V D 法および A L D 法では、成膜しながら原料ガスの流量比を変化させることによって、組成が連続的に変化した膜を成膜することができる。原料ガスの流量比を変化させながら成膜する場合、複数の成膜室を用いて成膜する場合と比べて、搬送や圧力調整に掛かる時間を要しない分、成膜に掛かる時間を短くすることができる。したがって、半導体装置の生産性を高めることができる場合がある。

#### 【 0 2 5 6 】

本実施の形態では、絶縁体 2 1 1 として、 C V D 法によって窒化シリコンを成膜する。

次に、絶縁体 211 上に絶縁体 212 を成膜する。絶縁体 212 の成膜は、スパッタリング法、CVD 法、MBE 法、PLD 法または ALD 法などを用いて行うことができる。本実施の形態では、絶縁体 212 として、スパッタリング法によって窒化シリコンを成膜する。

#### 【0257】

次に、絶縁体 212 上に絶縁体 214 となる膜を成膜する。絶縁体 214 となる膜の成膜は、スパッタリング法、CVD 法、MBE 法、PLD 法または ALD 法などを用いて行うことができる。本実施の形態では、絶縁体 214 となる膜として、酸化アルミニウムを用いる。

#### 【0258】

絶縁体 211、および絶縁体 212 として、窒化シリコンなどの銅が透過しにくい絶縁体を用い、さらに絶縁体 212 上に絶縁体 214 となる膜を配置することにより絶縁体 211 より下層（図示せず）の導電体に銅など拡散しやすい金属を用いても、当該金属が絶縁体 211、および絶縁体 212 を介して上の層に拡散するのを抑制することができる。また、窒化シリコンのように水または水素などの不純物が透過しにくい絶縁体を用いることにより絶縁体 211 より下層から水または水素などの不純物の拡散を抑制することができる。

#### 【0259】

絶縁体 212 の水素濃度は、絶縁体 211 の水素濃度より低く、絶縁体 214 となる膜の水素濃度は、絶縁体 212 の水素濃度より低いことが好ましい。絶縁体 212 をスパッタリング法によって窒化シリコンを成膜することで、CVD 法によって窒化シリコンを成膜する絶縁体 211 よりも水素濃度が低い窒化シリコンを形成することができる。また、絶縁体 214 となる膜を酸化アルミニウムとすることで、絶縁体 212 よりも水素濃度を低くすることができる。

#### 【0260】

この後の工程にて絶縁体 214 となる膜上に、トランジスタ 200 を形成するが、トランジスタ 200 に近接する膜は、水素濃度が比較的低いことが好ましく、水素濃度が比較的高い膜は、トランジスタ 200 から遠隔して配置することが好ましい。

#### 【0261】

次に、絶縁体 214 となる膜上に絶縁体 216 となる膜を成膜する。絶縁体 216 となる膜の成膜は、スパッタリング法、CVD 法、MBE 法、PLD 法または ALD 法などを用いて行うことができる。本実施の形態では、絶縁体 216 となる膜として、酸化シリコンまたは酸化窒化シリコンを用いる。また、絶縁体 216 となる膜は、上述の水素原子が低減または除去されたガスを用いた成膜方法で成膜することが好ましい。これにより、絶縁体 216 となる膜の水素濃度を低減することができる。

#### 【0262】

次に、絶縁体 216 となる膜に絶縁体 214 となる膜に達する開口を形成する。開口とは、例えば、溝やスリットなども含まれる。また、開口が形成された領域を指して開口部とする場合がある。開口の形成はウェットエッチングを用いてもよいが、ドライエッチングを用いるほうが微細加工には好ましい。また、絶縁体 214 となる膜は、絶縁体 216 となる膜をエッ칭して溝を形成する際のエッチングストップ膜として機能する絶縁体を選択することが好ましい。例えば、溝を形成する絶縁体 216 となる膜に酸化シリコン膜または酸化窒化シリコン膜を用いた場合は、絶縁体 214 となる膜は窒化シリコン膜、酸化アルミニウム膜、酸化ハフニウム膜を用いるとよい。

#### 【0263】

開口の形成後に、導電体 205a となる導電膜を成膜する。該導電膜は、酸素の透過を抑制する機能を有する導電体を含むことが望ましい。たとえば、窒化タンタル、窒化タンゲステン、窒化チタンなどを用いることができる。またはタンタル、タンゲステン、チタン、モリブデン、アルミニウム、銅、モリブデンタンゲステン合金との積層膜とすることができる。導電体 205a となる導電膜の成膜は、スパッタリング法、CVD 法、MBE

10

20

30

40

50

法、PLD法またはALD法などを用いて行うことができる。

#### 【0264】

本実施の形態では、導電体205aとなる導電膜を多層構造とする。まず、スパッタリング法によって窒化タンタルを成膜し、当該窒化タンタルの上に窒化チタンを積層する。このような金属窒化物を導電体205bの下層に用いることにより、後述する導電体205bとなる導電膜として銅などの拡散しやすい金属を用いても、当該金属が導電体205aから外に拡散するのを防ぐことができる。

#### 【0265】

次に、導電体205bとなる導電膜を成膜する。該導電膜の成膜は、メッキ法、スパッタリング法、CVD法、MBE法、PLD法またはALD法などを用いて行うことができる。本実施の形態では、導電体205bとなる導電膜として、銅などの低抵抗導電性材料を成膜する。

10

#### 【0266】

次に、CMP処理(Chemical Mechanical Polishing)を行うことで、導電体205aとなる導電膜、ならびに導電体205bとなる導電膜の一部を除去し、絶縁体216となる膜を露出する。その結果、開口部のみに、導電体205a及び導電体205bが残存する。これにより、上面が平坦な、導電体205を形成することができる。なお、当該CMP処理により、絶縁体216となる膜の一部が除去される場合がある(図7参照)。

20

#### 【0267】

なお、上記においては、導電体205を絶縁体216となる膜の開口に埋め込むように形成したが、本実施の形態はこれに限られるものではない。例えば、絶縁体214となる膜上に導電体205を形成し、導電体205上に絶縁体216となる膜を成膜し、絶縁体216となる膜にCMP処理を行うことで、絶縁体216となる膜の一部を除去し、導電体205の表面を露出させてよい。

#### 【0268】

次に、絶縁体216となる膜、および導電体205上に絶縁体222を成膜する。絶縁体222として、アルミニウムおよびハフニウムの一方または双方の酸化物を含む絶縁体を成膜するとよい。なお、アルミニウムおよびハフニウムの一方または双方の酸化物を含む絶縁体として、酸化アルミニウム、酸化ハフニウム、アルミニウムおよびハフニウムを含む酸化物(ハフニウムアルミネート)などを用いることが好ましい。アルミニウムおよびハフニウムの一方または双方の酸化物を含む絶縁体は、酸素、水素、および水に対するバリア性を有する。絶縁体222が、水素および水に対するバリア性を有することで、トランジスタ200の周辺に設けられた構造体に含まれる水素、および水が、絶縁体222を通じてトランジスタ200の内側へ拡散することが抑制され、酸化物230中の酸素欠損の生成を抑制することができる。

30

#### 【0269】

絶縁体222の成膜は、スパッタリング法、CVD法、MBE法、PLD法、またはALD法などを用いて行うことができる。

#### 【0270】

次に、絶縁体222上に絶縁体224を成膜する。絶縁体224の成膜は、スパッタリング法、CVD法、MBE法、PLD法、またはALD法などを用いて行うことができる。本実施の形態では、絶縁体224として、酸化シリコンまたは酸化窒化シリコンを用いる。また、絶縁体224は、上述の水素原子が低減または除去されたガスを用いた成膜方法で成膜することが好ましい。これにより、絶縁体224の水素濃度を低減することができる。絶縁体224は、後の工程で酸化物230aと接する絶縁体224となるので、このように水素濃度が低減されていることが好適である。

40

#### 【0271】

続いて、加熱処理を行うことが好ましい。加熱処理は、250以上650以下、好みしくは300以上500以下、さらに好みしくは320以上450以下で行え

50

ばよい。なお、加熱処理は、窒素または不活性ガス雰囲気、または酸化性ガスを10ppm以上、1%以上、もしくは10%以上含む雰囲気で行う。また、加熱処理は減圧状態で行ってもよい。または、加熱処理は、窒素または不活性ガス雰囲気で加熱処理した後に、脱離した酸素を補うために酸化性ガスを10ppm以上、1%以上、または10%以上含む雰囲気で加熱処理を行ってもよい。

#### 【0272】

本実施の形態では、窒素雰囲気にて400℃の温度で1時間の処理を行った後に、連続して酸素雰囲気にて400℃の温度で1時間の処理を行う。当該加熱処理によって、絶縁体224に含まれる水、水素などの不純物を除去することができる。

#### 【0273】

また、加熱処理は、絶縁体222の成膜後に行ってもよい。当該加熱処理は、上述した加熱処理条件を用いることができる。

#### 【0274】

ここで、絶縁体224に過剰酸素領域を形成するために、減圧状態で酸素を含むプラズマ処理を行ってもよい。酸素を含むプラズマ処理は、例えばマイクロ波を用いた高密度プラズマを発生させる電源を有する装置を用いることが好ましい。または、基板側にRFなどの高周波を印加する電源を有してもよい。高密度プラズマを用いることより、高密度の酸素ラジカルを生成することができ、基板側にRFを印加することで、高密度プラズマによって生成された酸素ラジカルを効率よく絶縁体224内に導くことができる。または、この装置を用いて不活性ガスを含むプラズマ処理を行った後に、脱離した酸素を補うために酸素を含むプラズマ処理を行ってもよい。なお、当該プラズマ処理の条件を選択することにより、絶縁体224に含まれる水、水素などの不純物を除去することができる。その場合、加熱処理は行わなくてもよい。

#### 【0275】

ここで、絶縁体224上に、例えば、スパッタリング法によって、酸化アルミニウムを成膜し、該酸化アルミニウムを絶縁体224に達するまで、CMPを行ってもよい。当該CMPを行うことで絶縁体224表面の平坦化および絶縁体224表面の平滑化を行うことができる。当該酸化アルミニウムを絶縁体224上に配置してCMPを行うことで、CMPの終点検出が容易となる。また、CMPによって、絶縁体224の一部が研磨され、絶縁体224の膜厚が薄くなることがあるが、絶縁体224の成膜時に膜厚を調整すればよい。絶縁体224表面の平坦化および平滑化を行うことで、後に成膜する酸化物の被覆率の悪化を防止し、半導体装置の歩留りの低下を防ぐことができる場合がある。また、絶縁体224上に、スパッタリング法によって、酸化アルミニウムを成膜することにより、絶縁体224に酸素を添加することができるので好ましい。

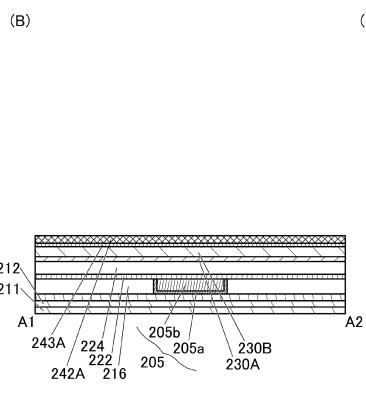

#### 【0276】

次に、絶縁体224上に、酸化膜230A、酸化膜230Bを順に成膜する(図7参照)。なお、上記酸化膜は、大気環境にさらさずに連続して成膜することが好ましい。大気開放せずに成膜することで、酸化膜230A、および酸化膜230B上に大気環境からの不純物または水分が付着することを防ぐことができ、酸化膜230Aと酸化膜230Bとの界面近傍を清浄に保つことができる。

#### 【0277】

酸化膜230Aおよび、酸化膜230Bの成膜はスパッタリング法、CVD法、MBE法、PLD法、またはALD法などを用いて行うことができる。

#### 【0278】

例えば、酸化膜230A、および酸化膜230Bをスパッタリング法によって成膜する場合は、スパッタリングガスとして酸素、または、酸素と希ガスの混合ガスを用いる。スパッタリングガスに含まれる酸素の割合を高めることで、成膜される酸化膜中の過剰酸素を増やすことができる。また、上記の酸化膜をスパッタリング法によって成膜する場合は、上記のIn-M-Zn酸化物ターゲットを用いることができる。

#### 【0279】

10

20

30

40

50

特に、酸化膜 230A の成膜時に、スパッタリングガスに含まれる酸素の一部が絶縁体 224 に供給される場合がある。したがって、酸化膜 230A のスパッタリングガスに含まれる酸素の割合は 70% 以上、好ましくは 80% 以上、より好ましくは 100% とすればよい。

#### 【0280】

また、酸化膜 230B をスパッタリング法で形成する場合、スパッタリングガスに含まれる酸素の割合を 1% 以上 30% 以下、好ましくは 5% 以上 20% 以下として成膜すると、酸素欠乏型の酸化物半導体が形成される。酸素欠乏型の酸化物半導体をチャネル形成領域に用いたトランジスタは、比較的高い電界効果移動度が得られる。また、基板を加熱しながら成膜を行うことによって、当該酸化膜の結晶性を向上させることができる。ただし、本発明の一態様はこれに限定されない。酸化膜 230B をスパッタリング法で形成する場合、スパッタリングガスに含まれる酸素の割合を、30% を超えて 100% 以下、好ましくは 70% 以上 100% 以下として成膜すると、酸素過剰型の酸化物半導体が形成される。酸素過剰型の酸化物半導体をチャネル形成領域に用いたトランジスタは、比較的高い信頼性が得られる。

#### 【0281】

本実施の形態では、酸化膜 230A として、スパッタリング法によって、 $In : Ga : Zn = 1 : 1 : 0.5$  [原子数比] ( $2 : 2 : 1$  [原子数比])、あるいは  $1 : 3 : 4$  [原子数比] のターゲットを用いて成膜する。また、酸化膜 230B として、スパッタリング法によって、 $In : Ga : Zn = 4 : 2 : 4.1$  [原子数比]、あるいは  $1 : 1 : 1$  [原子数比] のターゲットを用いて成膜する。なお、各酸化膜は、成膜条件、および原子数比を適宜選択することで、酸化物 230 に求める特性に合わせて形成するとよい。

#### 【0282】

次に、加熱処理を行ってもよい。加熱処理は、上述した加熱処理条件を用いることができる。加熱処理によって、酸化膜 230A、および酸化膜 230B 中の水、水素などの不純物を除去することができる。本実施の形態では、窒素雰囲気にて 400 の温度で 1 時間の処理を行った後に、連続して酸素雰囲気にて 400 の温度で 1 時間の処理を行う。

#### 【0283】

次に、酸化膜 230B 上に酸化膜 243A を成膜する（図 7 参照）。酸化膜 243A の成膜はスパッタリング法、CVD 法、MBE 法、PLD 法、または ALD 法などを用いて行うことができる。酸化膜 243A は、In に対する Ga の原子数比が、酸化膜 230B の In に対する Ga の原子数比より大きいことが好ましい。本実施の形態では、酸化膜 243A として、スパッタリング法によって、 $In : Ga : Zn = 1 : 3 : 4$  [原子数比] のターゲットを用いて成膜する。

#### 【0284】

次に、酸化膜 243A 上に導電膜 242A を成膜する（図 7 参照）。導電膜 242A の成膜はスパッタリング法、CVD 法、MBE 法、PLD 法、または ALD 法などを用いて行うことができる。

#### 【0285】

次に、リソグラフィー法を用いて、酸化膜 230A、酸化膜 230B、酸化膜 243A、および導電膜 242A を島状に加工して、酸化物 230a、酸化物 230b、酸化物層 243B、および導電体層 242B を形成する（図 8 参照）。ここで、酸化物 230a、酸化物 230b、酸化物層 243B、および導電体層 242B は、少なくとも一部が導電体 205 と重なるように形成する。また、当該加工はドライエッチング法やウェットエッチング法を用いることができる。ドライエッチング法による加工は微細加工に適している。なお、当該工程において、絶縁体 224 の酸化物 230a と重ならない領域の膜厚が薄くなることがある。

#### 【0286】

なお、リソグラフィー法では、まず、マスクを介してレジストを露光する。次に、露光

10

20

30

40

50

された領域を、現像液を用いて除去または残存させてレジストマスクを形成する。次に、当該レジストマスクを介してエッチング処理することで導電体、半導体または絶縁体などを所望の形状に加工することができる。例えば、KrFエキシマレーザ光、ArFエキシマレーザ光、EUV (Extreme Ultraviolet) 光などを用いて、レジストを露光することでレジストマスクを形成すればよい。また、基板と投影レンズとの間に液体（例えば水）を満たして露光する、液浸技術を用いてもよい。また、前述した光に代えて、電子ビームやイオンビームを用いてもよい。なお、電子ビームやイオンビームを用いる場合には、マスクは不要となる。なお、レジストマスクの除去には、アッティングなどのドライエッティング処理を行う、ウェットエッティング処理を行う、ドライエッティング処理後にウェットエッティング処理を行う、またはウェットエッティング処理後にドライエッティング処理を行うことができる。

10

#### 【0287】

また、レジストマスクの代わりに絶縁体や導電体からなるハードマスクを用いてもよい。ハードマスクを用いる場合、導電膜242A上にハードマスク材料となる絶縁膜や導電膜を形成し、その上にレジストマスクを形成し、ハードマスク材料をエッティングすることで所望の形状のハードマスクを形成することができる。導電膜242Aなどのエッティングは、レジストマスクを除去してから行っても良いし、レジストマスクを残したまま行っても良い。後者の場合、エッティング中にレジストマスクが消失することがある。導電膜242Aなどのエッティング後にハードマスクをエッティングにより除去しても良い。一方、ハードマスクの材料が後工程に影響が無い、あるいは後工程で利用できる場合、必ずしもハードマスクを除去する必要は無い。

20

#### 【0288】

ドライエッティング装置としては、平行平板型電極を有する容量結合型プラズマ（CCP : Capacitively Coupled Plasma）エッティング装置を用いることができる。平行平板型電極を有する容量結合型プラズマエッティング装置は、平行平板型電極の一方の電極に高周波電源を印加する構成でもよい。または平行平板型電極の一方の電極に複数の異なった高周波電源を印加する構成でもよい。または平行平板型電極それぞれに同じ周波数の高周波電源を印加する構成でもよい。または平行平板型電極それぞれに周波数の異なる高周波電源を印加する構成でもよい。または高密度プラズマ源を有するドライエッティング装置を用いることができる。高密度プラズマ源を有するドライエッティング装置は、例えば、誘導結合型プラズマ（ICP : Inductively Coupled Plasma）エッティング装置などを用いることができる。

30

#### 【0289】

また、酸化物230a、酸化物230b、酸化物層243B、および導電体層242Bの側面は、絶縁体222の上面に対し、概略垂直であることが好ましい。酸化物230a、酸化物230b、酸化物層243B、および導電体層242Bの側面が、絶縁体222の上面に対し、概略垂直であることで、複数のトランジスタ200を設ける際に、小面積化、高密度化が可能となる。ただし、これに限らず、酸化物230a、酸化物230b、酸化物層243B、および導電体層242Bの側面と絶縁体222の上面のなす角が低い角度になる構成にしてもよい。

40

#### 【0290】

次に、絶縁体224、酸化物230a、酸化物230b、酸化物層243B、および導電体層242B上に、絶縁体272を成膜する（図9参照）。絶縁体272の成膜は、スパッタリング法、CVD法、MBE法、PLD法またはALD法などを用いて行うことができる。本実施の形態では、絶縁体272として、スパッタリング法によって、酸化アルミニウムを成膜する。スパッタリング法によって、酸化アルミニウムを成膜することで、絶縁体224へ酸素を注入することができる。

#### 【0291】

次に、絶縁体272上に絶縁体273を成膜する。絶縁体273の成膜は、スパッタリング法、CVD法、MBE法、PLD法またはALD法などを用いて行うことができる。

50

実施の形態では、絶縁体 273 として、スパッタリング法によって、窒化シリコンを成膜する（図 9 参照）。

#### 【0292】

次に、絶縁体 280 となる絶縁膜を成膜する。絶縁体 280 となる絶縁膜の成膜は、スパッタリング法、CVD 法、MBE 法、PLD 法または ALD 法などを用いて行うことができる。例えば、絶縁体 280 として、スパッタリング法を用いて酸化シリコン膜を成膜し、その上に PEALD 法またはサーマル ALD 法を用いて酸化シリコン膜を成膜すればよい。また、絶縁体 280 となる絶縁膜は、上述の水素原子が低減または除去されたガスを用いた成膜方法で成膜することが好ましい。これにより、絶縁体 280 の水素濃度を低減することができる。

10

#### 【0293】

次に、絶縁体 280 となる絶縁膜に CMP 处理を行い、上面が平坦な絶縁体 280 を形成する（図 10 参照）。なお、絶縁体 224 と同様に、絶縁体 280 上に、例えば、スパッタリング法によって、酸化アルミニウムを成膜し、該酸化アルミニウムを絶縁体 280 に達するまで、CMP を行ってもよい。

#### 【0294】

次に、絶縁体 280 の一部、絶縁体 273 の一部、絶縁体 272 の一部、導電体層 242B の一部、および酸化物層 243B の一部を加工して、酸化物 230b に達する開口を形成する（図 11 参照）。該開口は、導電体 205 と重なるように形成することが好ましい。該開口の形成によって、導電体 242a、導電体 242b、酸化物 243a、および酸化物 243b を形成する。

20

#### 【0295】

絶縁体 280 の一部、絶縁体 273 の一部、絶縁体 272 の一部、酸化物層 243B の一部、および導電体層 242B の一部の加工は、ドライエッティング法、またはウェットエッティング法を用いることができる。ドライエッティング法による加工は微細加工に適している。また、当該加工は、それぞれ異なる条件で加工してもよい。例えば、絶縁体 280 の一部をドライエッティング法で加工し、絶縁体 273 の一部をウェットエッティング法で加工し、絶縁体 272 の一部をドライエッティング法で加工し、酸化物層 243B、および導電体層 242B の一部をドライエッティング法で加工してもよい。

30

#### 【0296】

これまでのドライエッティングなどの処理を行うことによって、エッティングガスなどに起因した不純物が酸化物 230a、および酸化物 230b などの表面または内部に付着または拡散することがある。不純物としては、例えば、フッ素または塩素などがある。

#### 【0297】

上記の不純物などを除去するために、洗浄を行う。洗浄方法としては、洗浄液など用いたウェット洗浄、プラズマを用いたプラズマ処理、または加熱処理による洗浄などがあり、上記洗浄を適宜組み合わせて行ってもよい。

#### 【0298】

ウェット洗浄としては、シュウ酸、リン酸、アンモニア水、またはフッ化水素酸などを炭酸水または純水で希釈した水溶液を用いて洗浄処理を行ってもよい。または、純水または炭酸水を用いた超音波洗浄を行ってもよい。

40

#### 【0299】

これまでドライエッティングなどの加工、または上述の洗浄処理によって、酸化物 230b の酸化物 243a、および酸化物 243b と重ならない領域の膜厚が、酸化物 230b の酸化物 243a、および酸化物 243b と重なる領域の膜厚より薄くなることがある（図 11 参照）。

#### 【0300】

上記エッティング後、または上記洗浄後に加熱処理を行ってもよい。加熱処理は、例えば、100 以上 450 以下、より好ましくは 350 以上 400 以下で行えばよい。なお、加熱処理は、窒素ガスもしくは不活性ガスの雰囲気、または酸化性ガスを 10pp

50

m以上、1%以上、もしくは10%以上含む雰囲気で行う。例えば、加熱処理は酸素雰囲気で行うことが好ましい。これにより、酸化物230aおよび酸化物230bに酸素を供給して、酸素欠損V<sub>O</sub>の低減を図ることができる。また、加熱処理は減圧状態で行ってもよい。または、酸素雰囲気で加熱処理した後に、大気に露出せずに連続して窒素雰囲気で加熱処理を行ってもよい。

#### 【0301】

次に、酸化膜230Cを成膜する(図12参照)。酸化膜230Cの成膜前に加熱処理を行っても良く、当該加熱処理は、減圧下で行い、大気に暴露することなく、連続して酸化膜230Cを成膜することが好ましい。また、当該加熱処理は、酸素を含む雰囲気で行うことが好ましい。このような処理を行うことによって、酸化物230bの表面などに吸着している水分および水素を除去し、さらに酸化物230aおよび酸化物230b中の水分濃度および水素濃度を低減させることができる。加熱処理の温度は、100以上400以下が好ましく、さらに好ましくは150以上350以下である。本実施の形態では、加熱処理の温度を200とし、減圧下で行う。

10

#### 【0302】

ここで、酸化膜230Cは、少なくとも酸化物230bの上面の一部、酸化物243の側面の一部、導電体242の側面の一部、絶縁体272の側面の一部、絶縁体273の側面の一部、および絶縁体280の側面の一部と接するように設けられることが好ましい。導電体242は、酸化物243、絶縁体272、絶縁体273、および酸化膜230Cに囲まれることで、以降の工程において導電体242の酸化による導電率の低下を抑制することができる。

20

#### 【0303】

酸化膜230Cの成膜はスパッタリング法、CVD法、MBE法、PLD法、またはALD法などを用いて行うことができる。酸化膜230Cとして、Inに対するGaの原子数比が、酸化膜230BのInに対するGaの原子数比より大きいことが好ましい。本実施の形態では、酸化膜230Cとして、スパッタリング法によって、In:Ga:Zn=1:3:4[原子数比]のターゲットを用いて成膜する。

#### 【0304】

尚、酸化膜230Cは、積層としてもよい。例えば、スパッタリング法によって、In:Ga:Zn=4:2:4.1[原子数比]のターゲットを用いて成膜して、連続してIn:Ga:Zn=1:3:4[原子数比]のターゲットを用いて成膜してもよい。

30

#### 【0305】

酸化膜230Cの成膜時に、スパッタリングガスに含まれる酸素の一部が酸化物230aおよび酸化物230bに供給される場合がある。または、酸化膜230Cの成膜時に、スパッタリングガスに含まれる酸素の一部が絶縁体280に供給される場合がある。したがって、酸化膜230Cのスパッタリングガスに含まれる酸素の割合は70%以上、好ましくは80%以上、より好ましくは100%とすればよい。

#### 【0306】

次に、加熱処理を行っても良い。また、当該加熱処理を減圧下で行い、大気に暴露することなく、連続して、絶縁膜250Aの成膜を行ってもよい。当該加熱処理を行うことによって、酸化膜230Cの表面などに吸着している水分および水素を除去し、さらに酸化物230a、酸化物230bおよび酸化膜230C中の水分濃度および水素濃度を低減させることができる。加熱処理の温度は、100以上400以下が好ましい。本実施の形態では、加熱処理の温度を200とする。

40

#### 【0307】

次に、酸化膜230C上に絶縁膜250Aを成膜する(図12参照)。絶縁膜250Aは、スパッタリング法、CVD法、MBE法、PLD法、またはALD法などを用いて成膜することができる。また、絶縁膜250Aは、上述の水素原子が低減または除去されたガスを用いた成膜方法で成膜することが好ましい。これにより、絶縁膜250Aの水素濃度を低減することができる。絶縁膜250Aは、後の工程で酸化物230cと接する絶縁

50

体 250 となるので、このように水素濃度が低減されていることが好適である。

#### 【0308】

次に、マイクロ波、またはRF等の高周波を照射してもよい。照射されたマイクロ波、またはRF等の高周波は絶縁体280、酸化物230b、および酸化物230a中に浸透して、これらの中の水素を除去する。特に、酸化物230aおよび酸化物230bにおいては、VOHの結合が切断される反応が起き、脱水素化されることになる。このとき発生した水素の一部は、酸化物230、および絶縁体280から除去される場合がある。また、水素の一部は、導電体242にゲッタリングされる場合がある。このように、マイクロ波、またはRF等の高周波を照射することで、絶縁体280、酸化物230b、および酸化物230a中の水素濃度を低減することができる。

10

#### 【0309】

また、マイクロ波、またはRF等の高周波によって酸素ガスをプラズマ化し、酸素ラジカルを形成してもよい。つまり、絶縁体280、酸化物230b、および酸化物230aに酸素を有する雰囲気でプラズマ処理を行ってもよい。このような処理を以下において、酸素プラズマ処理という場合がある。また、形成した酸素ラジカルによって、絶縁体280、酸化物230b、および酸化物230a中に酸素を供給することができる。また、絶縁体280、酸化物230b、および酸化物230aに酸素を有する雰囲気でプラズマ処理を行う場合、酸化物230にマイクロ波、またはRF等の高周波が照射されにくい構成にしてもよい。

20

#### 【0310】

なお、酸素プラズマ処理は、例えばマイクロ波を用いた高密度プラズマを発生させる電源を有する、マイクロ波処理装置を用いることが好ましい。また、マイクロ波処理装置は基板側にRFを印加する電源を有してもよい。高密度プラズマを用いることより、高密度の酸素ラジカルを生成することができる。また、基板側にRFを印加することで、高密度プラズマによって生成された酸素イオンを、効率よく絶縁体280および酸化物230中に導くことができる。また、上記酸素プラズマ処理は、減圧下で行うことが好ましく、圧力を60Pa以上、好ましくは133Pa以上、より好ましくは200Pa以上、さらには好ましくは400Pa以上とすればよい。また、酸素流量比(O<sub>2</sub>/O<sub>2</sub>+Ar)が50%以下、好ましくは10%以上30%以下で行うとよい。また、処理温度は、例えば400程度で行えばよい。また、酸素プラズマ処理を行った後に、外気に曝すことなく、連続して熱処理を行ってもよい。

30

#### 【0311】

次に、導電膜260A(導電膜260Aaおよび導電膜260Ab)を成膜する(図13参照)。導電膜260Aaおよび導電膜260Abの成膜は、スパッタリング法、CVD法、MBE法、PLD法またはALD法などを用いて行うことができる。例えば、CVD法を用いることが好ましい。本実施の形態では、ALD法を用いて、導電膜260Aaを成膜し、CVD法を用いて導電膜260Abを成膜する。

#### 【0312】

次に、CMP処理によって、酸化膜230C、絶縁膜250A、導電膜260Aaおよび導電膜260Abを絶縁体280が露出するまで研磨することによって、酸化物230c、絶縁体250および導電体260(導電体260aおよび導電体260b)を形成する(図14参照)。

40

#### 【0313】

次に、加熱処理を行ってもよい。本実施の形態では、窒素雰囲気にて400の温度で1時間の処理を行う。該加熱処理によって、絶縁体250および絶縁体280中の水分濃度および水素濃度を低減させることができる。なお、上記加熱処理後、大気に曝すことなく連続して、絶縁体282の成膜を行ってもよい。

#### 【0314】

次に、導電体260上、酸化物230c上、絶縁体250上、および絶縁体280上に、絶縁体282を形成する。絶縁体282の成膜は、スパッタリング法、CVD法、MB

50

E法、PLD法、またはALD法などを用いて行うことができる（図15参照）。

#### 【0315】

絶縁体282としては、例えば、スパッタリング法によって、酸化アルミニウムを成膜することが好ましい。スパッタリング法を用いて、酸素を含む雰囲気で絶縁体282の成膜を行うことで、成膜しながら、絶縁体280に酸素を添加することができる。このとき、基板加熱を行いながら、絶縁体282を成膜することが好ましい。また、導電体260の上面に接して、絶縁体282を形成することで、この後の加熱処理において、絶縁体280が有する酸素が導電体260へ吸収されることを抑制することができるので好ましい。

#### 【0316】

ここで、絶縁体282を成膜する前に、スパッタリング法により、酸素を含む雰囲気下で金属酸化物を成膜した後、当該金属酸化物を除去する工程を、1回以上繰り返してもよい。当該工程により、絶縁体280中に過剰酸素を投入することができる。また、当該工程を複数回繰り返すことにより、絶縁体280中に含まれる過剰酸素量を適宜調整することができる。

#### 【0317】

また、絶縁体282を成膜した後、加熱処理を行うことが好ましい（なお、図15（B）に示す曲線は、加熱処理を示す）。具体的には、酸素を含む雰囲気、窒素を含む雰囲気、または酸素と窒素の混合雰囲気にて、350以上、好ましくは400以上の温度で行う。加熱処理の時間は、1時間以上、好ましくは4時間以上、さらに好ましくは8時間以上とする。

#### 【0318】

当該加熱処理によって、酸化物230中の水素が、絶縁体280、および絶縁体282を介して、外方に拡散することができる。つまり、トランジスタ200中の水素は、絶縁体280、および絶縁体282を介して、外方に拡散され、トランジスタ200、および絶縁体282中の水素濃度を低減することができる。つまり、半導体装置中に存在する水素の絶対量を低減することができる。

#### 【0319】

次に、絶縁体282の一部、絶縁体280の一部、絶縁体273の一部、絶縁体272の一部、絶縁体224の一部、絶縁体222の一部、絶縁体216となる膜の一部、絶縁体214となる膜の一部、および絶縁体212の一部を加工して、絶縁体216、および絶縁体214を形成し、絶縁体211に達する開口を形成する（図16参照）。該開口は、トランジスタ200が囲まれるように形成される場合がある。または、該開口は、複数のトランジスタ200が囲まれるように形成される場合がある。よって、該開口において、絶縁体282の側面の一部、絶縁体280の側面の一部、絶縁体273の側面の一部、絶縁体272の側面の一部、絶縁体224の側面の一部、絶縁体222の側面の一部、絶縁体216の側面の一部、絶縁体214の側面の一部、および絶縁体212の側面の一部が露出する。

#### 【0320】

絶縁体282の一部、絶縁体280の一部、絶縁体273の一部、絶縁体272の一部、絶縁体224の一部、絶縁体222の一部、絶縁体216となる膜の一部、および絶縁体214となる膜の一部、絶縁体212の一部の加工は、ドライエッチング法、またはウェットエッチング法を用いることができる。ドライエッチング法による加工は微細加工に適している。また、当該加工は、それぞれ異なる条件で加工してもよい。

#### 【0321】

また、このとき、マイクロ波、またはRF等の高周波を絶縁体280などに照射してもよい。照射されたマイクロ波、またはRF等の高周波は絶縁体280、酸化物230b、および酸化物230aなどに浸透して、これらの中の水素を除去できることがある。例えば、酸化物230aおよび酸化物230bにおいては、VOHの結合が切断される反応が起き、脱水素化される。このとき発生した水素の一部は、酸化物230、および絶縁体2

10

20

30

40

50

80から除去される場合がある。また、水素の一部は、導電体242にゲッタリングされる場合がある。

#### 【0322】

次に、絶縁体282、絶縁体280、絶縁体273、絶縁体272、絶縁体224、絶縁体222、絶縁体216、絶縁体214および絶縁体212を覆って、絶縁体287Aを形成する(図17参照)。絶縁体287Aは、絶縁体282と同等の条件を用いて形成することが好ましい。例えば、絶縁体287Aの成膜は、スパッタリング法、CVD法、MBE法、PLD法、またはALD法などを用いて行うことができる。

#### 【0323】

具体的には、絶縁体287Aとしては、例えば、スパッタリング法によって、酸化アルミニウムを成膜することが好ましい。スパッタリング法を用いて、酸素を含む雰囲気で絶縁体287Aの成膜を行うことで、成膜しながら、絶縁体280に酸素を添加することができる。このとき、基板加熱を行いながら、絶縁体287Aを成膜することが好ましい。また、導電体260の上面に接して、絶縁体282が形成されているため、絶縁体287Aの成膜処理において、絶縁体280が有する酸素が導電体260へ吸収されることを抑制することができる。

#### 【0324】

続いて、絶縁体287Aに対し、異方性のエッチング処理を行い、絶縁体282、絶縁体280、絶縁体273、絶縁体272、絶縁体224、絶縁体222、絶縁体216、絶縁体214および絶縁体212の側面に、絶縁体287を形成する(図18参照)。

#### 【0325】

ここで、絶縁体282の側端部と絶縁体287の上端部とが接し、絶縁体214の側端部と絶縁体287の下端部とが接することで、トランジスタ200および絶縁体280を封止する構造を、形成することができる。

#### 【0326】

上記異方性のエッチング処理としては、ドライエッチング処理を行うことが好ましい。これにより、基板面に略平行な面に成膜された当該絶縁膜を除去して、絶縁体287を自己整合的に形成することができる。

#### 【0327】

また、絶縁体287を形成した後、加熱処理を行うことが好ましい(なお、図18(B)に示す曲線は、加熱処理を示す)。具体的には、酸素を含む雰囲気、窒素を含む雰囲気、または酸素と窒素の混合雰囲気にて、350以上、好ましくは400以上の温度で行う。加熱処理の時間は、1時間以上、好ましくは4時間以上、さらに好ましくは8時間以上とする。

#### 【0328】

当該加熱処理によって、酸化物230中の水素が、絶縁体280、絶縁体282、および絶縁体287を介して、外方に拡散することができる。つまり、トランジスタ200中の水素は、絶縁体280、絶縁体282、および絶縁体287を介して、外方に拡散され、トランジスタ200、絶縁体282、および絶縁体287中の水素濃度を低減することができる。つまり、半導体装置中に存在する水素の絶対量を低減することができる。

#### 【0329】

また、絶縁体282、絶縁体287、絶縁体211を覆って、絶縁体283を形成する(図19参照)。絶縁体283の成膜は、スパッタリング法、CVD法、MBE法、PLD法、またはALD法などを用いて行うことができる。また、絶縁体283は、多層としてもよい。例えば、スパッタリング法を用いて、窒化シリコンを成膜し、当該窒化シリコン上に、CVD法を用いて窒化シリコンを成膜してもよい。図19に示すように、絶縁体283は、上記開口の底面において、絶縁体211と接する。つまり、トランジスタ200は、上面及び側面が絶縁体283に、下面が絶縁体211に包み込まれることになる。このように、バリア性の高い絶縁体283および絶縁体211でトランジスタ200を包み込むことで、外部から水分、および水素が侵入するのを防止することができる。

10

20

30

40

50

**【 0 3 3 0 】**

次に、加熱処理を行ってもよい。本実施の形態では、窒素雰囲気にて400の温度で1時間の処理を行う。当該加熱処理によって、絶縁体282の成膜によって添加された酸素を絶縁体280へ拡散させ、さらに酸化物230cを介して、酸化物230a、および酸化物230bへ供給することができる。このように、酸化物230に加酸素化処理を行うことで、酸化物230(酸化物230b)中の酸素欠損を酸素により修復させる。

**【 0 3 3 1 】**

さらに、酸化物230中に残存した水素は、絶縁体280を介して、絶縁体282および絶縁体287に拡散し、絶縁体287に捕獲、または固着する。つまり、酸化物230中に残存していた水素が酸素欠損に再結合してVOHが形成されるのを抑制することができる。なお、当該加熱処理は、絶縁体283の成膜後に限らず、絶縁体282の成膜後に行ってもよい。

10

**【 0 3 3 2 】**