(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第6764473号

(P6764473)

(45) 発行日 令和2年9月30日(2020.9.30)

(24) 登録日 令和2年9月15日(2020.9.15)

(51) Int.Cl.

G 06 N 3/063 (2006.01)

G 11 C 13/00 (2006.01)

F 1

G 06 N 3/063

G 11 C 13/00 200

請求項の数 9 (全 26 頁)

(21) 出願番号 特願2018-514890 (P2018-514890)

(86) (22) 出願日 平成28年9月19日 (2016.9.19)

(65) 公表番号 特表2019-502970 (P2019-502970A)

(43) 公表日 平成31年1月31日 (2019.1.31)

(86) 國際出願番号 PCT/IB2016/055572

(87) 國際公開番号 WO2017/068443

(87) 國際公開日 平成29年4月27日 (2017.4.27)

審査請求日 平成31年2月25日 (2019.2.25)

(31) 優先権主張番号 14/887,564

(32) 優先日 平成27年10月20日 (2015.10.20)

(33) 優先権主張国・地域又は機関

米国(US)

(73) 特許権者 390009531

インターナショナル・ビジネス・マシーンズ・コーポレーション

INTERNATIONAL BUSINESS MACHINES CORPORATION

アメリカ合衆国 10504 ニューヨーク

州 アーモンク ニュー オーチャード

ロード

New Orchard Road, Armonk, New York 10504, United States of America

(74) 代理人 100108501

弁理士 上野 剛史

最終頁に続く

(54) 【発明の名称】 抵抗型処理ユニット

## (57) 【特許請求の範囲】

## 【請求項 1】

2 端子抵抗型処理ユニット(RPU)であって、

第1の端子と、

第2の端子と、

伝導状態を有する活性領域と

を含み、

前記活性領域は、前記第1の端子に印加された少なくとも1つの第1のコード化信号及び前記第2の端子に印加された少なくとも1つの第2のコード化信号に基づいて前記伝導状態の非線形変化をもたらすように構成され、

前記活性領域は、前記伝導状態の前記非線形変化に少なくとも部分的に基づいて訓練方法論のデータストレージ動作を局所的に行うようにさらに構成され、

前記活性領域は、前記伝導状態の前記非線形変化に少なくとも部分的に基づいて前記訓練方法論のデータ処理動作を局所的に行うようにさらに構成され、

前記少なくとも1つの第1のコード化信号及び前記少なくとも1つの第2のコード化信号のコード化は、パルスの確率的シーケンスを含む、

2 端子 RPU。

## 【請求項 2】

前記少なくとも1つの第1のコード化信号及び前記少なくとも1つの第2のコード化信号のコード化は、大きさ変調を含む、請求項1に記載の2端子RPU。

10

20

**【請求項 3】**

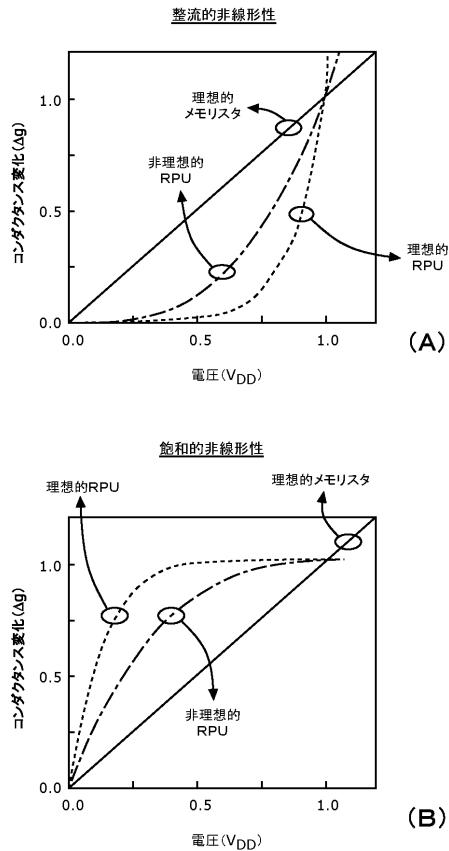

前記非線形変化は、整流的非線形変化又は飽和的非線形変化を含む、請求項1に記載の2端子RPU。

**【請求項 4】**

前記非線形変化は、指数関数的非線形変化を含む、請求項1に記載の2端子RPU。

**【請求項 5】**

訓練可能なクロスバーアレイであって

伝導性行ワイヤの組と、

前記伝導性行ワイヤの組との間の交差部に複数のクロスポイントを形成するように構成された伝導性列ワイヤの組と、

10

前記複数のクロスポイントの各々における2端子抵抗型処理ユニット(RPU)と、

を含み、

前記2端子RPUは、第1の端子と、第2の端子と、伝導状態を有する活性領域とを含み、

前記活性領域は、前記第1の端子に印加された少なくとも1つの第1のコード化信号及び前記第2の端子に印加された少なくとも1つの第2のコード化信号に基づいて前記伝導状態の非線形変化をもたらすように構成され、

前記活性領域は、前記伝導状態の前記非線形変化に少なくとも部分的に基づいて訓練方法論のデータストレージ動作を局所的に行うようにさらに構成され、

前記活性領域は、前記伝導状態の前記非線形変化に少なくとも部分的に基づいて前記訓練方法論のデータ処理動作を局所的に行うようにさらに構成され、

前記少なくとも1つの第1のコード化信号及び前記少なくとも1つの第2のコード化信号のコード化は、パルスの確率的シーケンスを含む、

アレイ。

**【請求項 6】**

2端子抵抗型処理ユニット(RPU)を形成する方法であって、

第1の端子を形成することと、

第2の端子を形成することと、

伝導状態を有する活性領域を形成することと、

前記活性領域を、前記第1の端子に印加された少なくとも1つの第1のコード化信号及び前記第2の端子に印加された少なくとも1つの第2のコード化信号に基づいて前記伝導状態の非線形変化をもたらすように構成することと、

30

前記活性領域を、前記伝導状態の前記非線形変化に少なくとも部分的に基づいて訓練方法論のデータストレージ動作を局所的に行うように構成することと、

前記活性領域を、前記伝導状態の前記非線形変化に少なくとも部分的に基づいて前記訓練方法論のデータ処理動作を局所的に行うように構成することと、

を含み、

前記少なくとも1つの第1のコード化信号及び前記少なくとも1つの第2のコード化信号のコード化は、パルスの確率的シーケンスを含む、

方法。

40

**【請求項 7】**

前記少なくとも1つの第1のコード化信号及び前記少なくとも1つの第2のコード化信号のコード化は、大きさ変調を含む、請求項6に記載の方法。

**【請求項 8】**

前記非線形変化は、整流的非線形変化又は飽和的非線形変化を含む、請求項6に記載の方法。

**【請求項 9】**

前記非線形変化は、指数関数的非線形変化を含む、請求項7に記載の方法。

**【発明の詳細な説明】****【技術分野】**

50

**【0001】**

本開示は、一般に、本明細書では抵抗型処理ユニット（RPU）と称する、訓練可能な抵抗型クロスポイントデバイスの新規構成に関する。より詳細には、本開示は、2端子RPU以外の付加的な処理要素を必要とせずに局所的データストレージ及び局所的データ処理を提供する2端子RPUのクロスバーアレイから形成される人工ニューラルネットワーク（ANN）に関し、これにより、ANNがオンライン・ニューラルネットワーク訓練、行列反転、行列分解などのようなアルゴリズムを学習し及び実装する能力が加速される。

**【背景技術】****【0002】**

「機械学習」は、データから学習する電子システムの主機能を説明するのに広範に使用されている。機械学習及び認知科学において、ANNは、動物の特に脳における生物学的ニューラルネットワークに触発された、統計的学習モデルのファミリーである。ANNを使用して、多数の入力に依存する一般に未知のシステム及び機能を推定し、又は近似することができる。

10

**【0003】**

ANNは、模擬「ニューロン」としての役割を果たして相互間で電子信号形態の「メッセージ」を交換する相互接続されたプロセッサ要素の、いわゆる「ニューロモーフィック」システムとしてしばしば具体化される。生物学的ニューロン間でメッセージを運ぶシナプス神経伝達物質接続のいわゆる「可塑性」と同様に、模擬ニューロン間で電子メッセージを運ぶ、ANNにおける接続には、所与の接続の強さ又は弱さに対応する数値重みが与えられる。重みを経験に基づいて調整し及びチューニングして、ANNを入力に対して適応的なもの及び学習可能なものにすることができる。例えば、手書き文字認識用のANNは、入力イメージの画素によって活性化され得る入力ニューロンの組によって定められる。ネットワークの設計者によって決定された関数によって重み付けされ変換された後、これら入力ニューロンの活性化は、しばしば「隠れ」ニューロンと称されるその他の下流ニューロンへと渡される。このプロセスは、出力ニューロンが活性化されるまで繰り返される。活性化された出力ニューロンは、どの文字を読み取ったのかを定める。

20

**【0004】**

クロスバーアレイは、クロスポイントアレイ又はクロスワイヤアレイとしても知られ、ANNアーキテクチャ、ニューロモーフィック・マイクロチップ及び超高密度不揮発性メモリを含む多様な電子回路及びデバイスを形成するために使用される、高密度低コストの回路アーキテクチャである。基本的なクロスバーアレイ構成は、伝導性行ワイヤの組と、この伝導性行ワイヤの組と交差するように形成された伝導性列ワイヤの組とを含む。2つのワイヤの組の間の交差部は、薄膜材料から形成することができる、いわゆるクロスポイントデバイスによって分離される。

30

**【0005】**

クロスポイントデバイスは、事実上、ANNのニューロン間の重み付き接続として機能する。高いエネルギー効率を有するシナプス可塑性をエミュレートするために、ナノスケールの2端子デバイス、例えば「理想的な」伝導状態のスイッチング特性を有するメモリストア（memristor）が、しばしばクロスポイントデバイスとして使用される。理想的なメモリストア材料の伝導状態（例えば抵抗）は、行ワイヤ及び列ワイヤの個々のワイヤ間に印加される電圧を制御することによって変更することができる。デジタルデータは、高伝導状態又は低伝導状態を達成する、交差部におけるメモリストア材料の伝導状態の変更によって格納することができる。メモリストア材料は、材料の伝導状態を選択的に設定することによって、2以上の相異なる伝導状態を維持するようにプログラムすることもできる。メモリストア材料の伝導状態は、該材料の両端に電圧を印加し、対象のクロスポイントデバイスを通る電流を測定することによって読み出すことができる。

40

**【0006】**

電力消費を制限するために、ANNチップアーキテクチャのクロスポイントデバイスは、オンライン学習技術を利用するように設計されることが多く、この場合、目的関数の近

50

似は、ひとたび初期訓練相が解決されると変化しない。オンライン学習は、クロスバー型ANNアーキテクチャのクロスポイントデバイスを、非常に少ない電力しか消費しないように単純化することを可能にする。

#### 【0007】

電力消費をより低くする可能性があるにもかかわらず、オンライン学習を実行することは、訓練データに対して入力・出力ペアを適合させるために典型的には訓練中にANNモデル内の著しい数の調整可能なパラメータ（例えば重み）を修正することを必要とするので、困難かつリソース集約的なものになることがある。従って、電力節約型のオンライン学習技術を優先するためにANNアーキテクチャのクロスポイントデバイスを単純化することは、典型的には、訓練速度及び訓練効率は最適化されないことを意味する。

10

#### 【先行技術文献】

#### 【非特許文献】

#### 【0008】

【非特許文献1】Anil K. Jain, Jianchang Mao及びK. M. M.ohiuddin、「Artificial Neural Networks: A Tutorial」、IEEE、1996年3月

【非特許文献2】C. Lehmann他、「A Generic Systolic Array Building Block For Neural Networks with On-Chip Learning」、IEEE Transactions On Neural Networks、1993年5月、第4巻、第3号

20

【非特許文献3】V. K. Chippa他、「STORM: A Stochastic Recognition and Mining Processor」、Proceedings of the 2014 International Symposium On Low power Electronics and Design

【非特許文献4】Chua, L.O.、「Resistance Switching Memories are Memristors」、Applied Physics A (2011年)、102(4): 765-783頁

【非特許文献5】D. Soudry他、「Memristor-Based Multilayer Neural Networks With Online Gradient Descent Training」、IEEE Transactions On Neural Networks and Learning Systems (2015年)

30

#### 【発明の概要】

#### 【発明が解決しようとする課題】

#### 【0009】

電力消費を許容可能な範囲内に保持するとともにANNアーキテクチャの訓練速度及び効率を加速する単純なクロスポイントデバイスを提供することは、全体としてのANN性能を改善し、より広範囲のANN用途を可能にするであろう。

#### 【課題を解決するための手段】

#### 【0010】

40

実施形態は、第1の端子、第2の端子及び活性領域を有する2端子抵抗型処理ユニット(RPU)に向けられる。活性領域は、RPUに適用される訓練方法論の重みを識別する伝導状態を有する。活性領域は、訓練方法論のデータストレージ動作を局所的に行うように構成され、かつ、活性領域は、訓練方法論のデータ処理動作を局所的に行うようにさらに構成される。

#### 【0011】

1つ又は複数の上記実施形態において、データストレージ動作は、データ処理動作の結果に少なくとも部分的に基づく伝導状態の変化を含む。

#### 【0012】

1つ又は複数の上記実施形態において、伝導状態の変化は、第1の端子に印加された少

50

なくとも 1 つの第 1 のコード化信号及び第 2 の端子に印加された少なくとも 1 つの第 2 のコード化信号に基づく非線形変化を含む。

【 0 0 1 3 】

1 つ又は複数の上記実施形態において、活性領域は、伝導状態の非線形変化に少なくとも部分的に基づいて訓練方法論のデータストレージ動作を局所的に行うようにさらに構成される。活性領域は、伝導状態の非線形変化に少なくとも部分的に基づいて訓練方法論の前記データ処理動作を局所的に行うようにさらに構成することができる。

【 0 0 1 4 】

1 つ又は複数の上記実施形態において、訓練方法論は、オンライン・ニューラルネットワーク訓練、行列反転又は行列分解とすることができる。

10

【 0 0 1 5 】

実施形態は、第 1 の端子、第 2 の端子及び活性領域を有する 2 端子 R P U にさらに向けられる。活性領域は、第 1 の端子に印加された少なくとも 1 つの第 1 のコード化信号及び第 2 の端子に印加された少なくとも 1 つの第 2 のコード化信号に基づいて活性領域の伝導状態の非線形変化をもたらす。活性領域は、伝導状態の非線形変化に少なくとも部分的に基づいて訓練方法論のデータストレージ動作を局所的に行うように構成される。活性領域は、伝導状態の非線形変化に少なくとも部分的に基づいて訓練方法論のデータ処理動作を局所的に行うようにさらに構成される。

【 0 0 1 6 】

1 つ又は複数の上記実施形態において、少なくとも 1 つの第 1 のコード化信号及び少なくとも 1 つの第 2 のコード化信号のコード化は、パルスの確率的シーケンス又は大きさ ( magnitude ) 変調を含む。

20

【 0 0 1 7 】

1 つ又は複数の上記実施形態において、非線形変化は、整流的非線形変化、飽和的非線形変化又は指數関数的非線形変化を含む。

【 0 0 1 8 】

実施形態は、伝導性行ワイヤの組と、伝導性行ワイヤの組との間の交差部に複数のクロスポイントを形成するように構成された伝導性列ワイヤの組と、を有する訓練可能なクロスバー配列にさらに向けられる。アレイは、複数のクロスポイントの各々における 2 端子抵抗型処理ユニット ( R P U ) を含む。R P U は、データストレージ動作を局所的に行うように、及びデータ処理動作を局所的に行うように構成され、局所的データストレージ動作及び局所的データ処理動作は両方とも、訓練可能なクロスバー配列に適用される訓練方法論の一部である。

30

【 0 0 1 9 】

1 つ又は複数の上記実施形態において、2 端子 R P U は、第 1 の端子と、第 2 の端子と、伝導状態を有する活性領域とを含み、伝導状態は、R P U に適用された訓練方法論の重みを識別する。

【 0 0 2 0 】

1 つ又は複数の上記実施形態において、データストレージ動作は、データ処理動作の結果に少なくとも部分的に基づく伝導状態の変化を含む。伝導状態の変化は、第 1 の端子に印加された少なくとも 1 つの第 1 のコード化信号及び第 2 の端子に印加された少なくとも 1 つの第 2 のコード化信号に基づく非線形変化を含む。

40

【 0 0 2 1 】

1 つ又は複数の上記実施形態において、活性領域は、伝導状態の非線形変化に少なくとも部分的に基づいて訓練方法論のデータストレージ動作を局所的に行う。活性領域は、さらに、伝導状態の非線形変化に少なくとも部分的に基づいて訓練方法論のデータ処理動作を局所的に行う。訓練方法論は、オンライン・ニューラルネットワーク訓練、行列反転及び行列分解を含む。

【 0 0 2 2 】

実施形態は、2 端子 R P U を形成する方法にさらに向けられる。方法は、第 1 の端子を

50

形成することと、第2の端子を形成することと、伝導状態を有する活性領域を形成することとを含む。方法は、活性領域を、第1の端子に印加された少なくとも1つの第1のコード化信号及び第2の端子に印加された少なくとも1つの第2のコード化信号に基づいて伝導状態の非線形変化をもたらすように構成することをさらに含む。方法は、活性領域を、伝導状態の非線形変化に少なくとも部分的に基づいて訓練方法論のデータストレージ動作を局所的に行うように構成することをさらに含む。方法は、活性領域を、伝導状態の非線形変化に少なくとも部分的に基づいて訓練方法論のデータ処理動作を局所的に行うように構成することをさらに含む。

【0023】

上記方法の1つ又は複数の実施形態において、少なくとも1つの第1のコード化信号及び少なくとも1つの第2のコード化信号のコード化は、パルスの確率的シーケンス又は大きさ変調を含む。10

【0024】

上記方法の1つ又は複数の実施形態において、非線形変化は、整流的非線形変化、飽和的非線形変化又は指数関数的非線形変化を含む。

【0025】

実施形態は、訓練可能なクロスバーアレイを形成する方法にさらに向けられる。方法は、伝導性行ワイヤの組を形成することと、伝導性行ワイヤの組との間の交差部に複数のクロスポイントを形成するように構成された伝導性列ワイヤの組を形成することと、を含む。方法は、複数のクロスポイントの各々において2端子RPUを形成することをさらに含む。方法は、RPUを、訓練可能なクロスバーアレイに適用された訓練方法論のデータストレージ動作を局所的に行うように構成することと、RPUを、訓練方法論のデータ処理動作を局所的に行うように構成することと、をさらに含む。20

【0026】

上記方法の1つ又は複数の実施形態において、2端子RPUを形成することは、第1の端子を形成することと、第2の端子を形成することと、伝導状態を有する活性領域を形成することとを含み、伝導状態は、RPUに適用された訓練方法論の重みを識別する。

【0027】

上記方法の1つ又は複数の実施形態において、データストレージ動作は、データ処理動作の結果に少なくとも部分的に基づく伝導状態の変化を含み、伝導状態の変化は、第1の端子に印加された少なくとも1つの第1のコード化信号及び第2の端子に印加された少なくとも1つの第2のコード化信号に基づく非線形変化を含む。30

【0028】

上記方法の1つ又は複数の実施形態において、方法は、活性領域を、伝導状態の非線形変化に少なくとも部分的に基づいて訓練方法論のデータストレージ動作を局所的に行うように構成することをさらに含む。方法は、活性領域を、伝導状態の非線形変化に少なくとも部分的に基づいて訓練方法論のデータ処理動作を局所的に行うように構成することをさらに含む。

【0029】

上記方法の1つ又は複数の実施形態において、訓練方法論は、オンライン・ニューラルネットワーク訓練、行列反転又は行列分解を含む。40

【0030】

さらなる特徴及び利点は、本明細書で説明する技術を通じて実現される。その他の実施形態および態様は、本明細書において詳細に説明される。より良く理解するために、説明及び図面を参照されたい。

【0031】

実施形態とみなされる主題は、特許請求の範囲及び本明細書の結論部において具体的に指摘され、明確に特許請求される。実施形態の上記及びその他の特徴及び利点は、添付の図面との関連で解釈される以下の詳細な説明から明らかである。

【図面の簡単な説明】50

**【0032】**

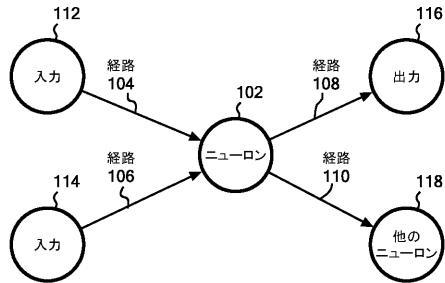

【図1】生物学的ニューロンの入力及び出力接続の略図を示す。

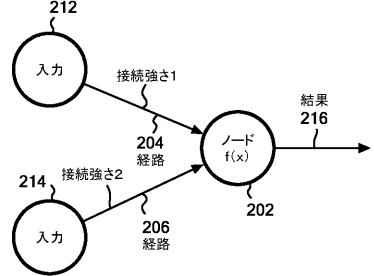

【図2】図1に示す生物学的ニューロンの公知の簡易モデルを示す。

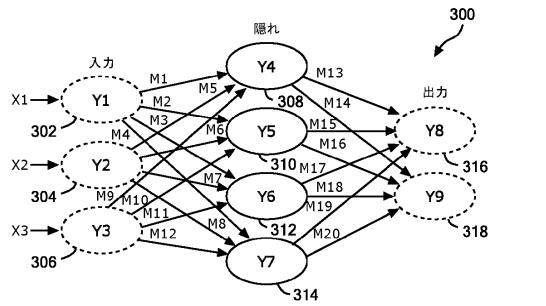

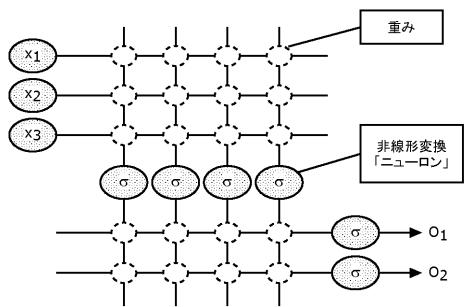

【図3】図2の生物学的ニューロンモデルを取り入れたANNの公知の簡易モデルを示す。

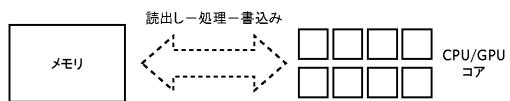

【図4】公知の重み更新方法論の略ブロック図を示す。

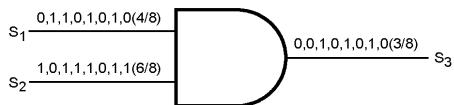

【図5】1つ又は複数の実施形態において使用可能な確率的計算方法論の略ブロック図を示す。

【図6】受動的2端子メモリスタの動作を支配する公知の式を示す。

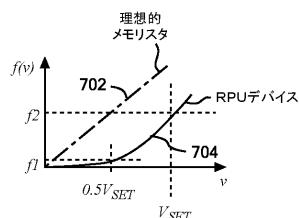

【図7】公知の2端子メモリスタの線形スイッチング特性と本開示の2端子RPUsの非線形特性との間の図式的比較を示す。 10

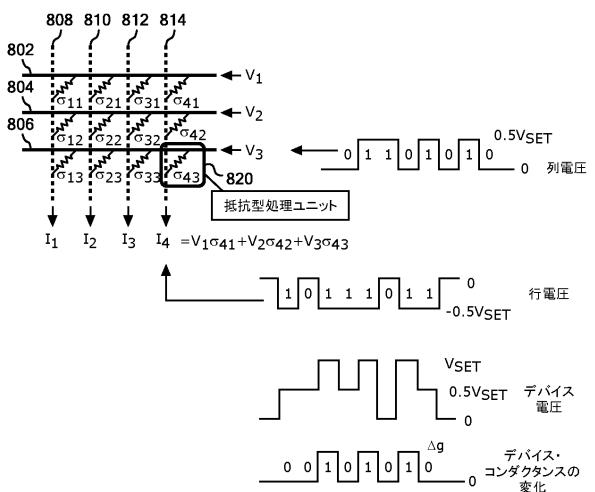

【図8】本開示による2端子非線形RPUsデバイスのクロスバーアレイを、RPUsの動作を例証する電圧シーケンスと共に示す。

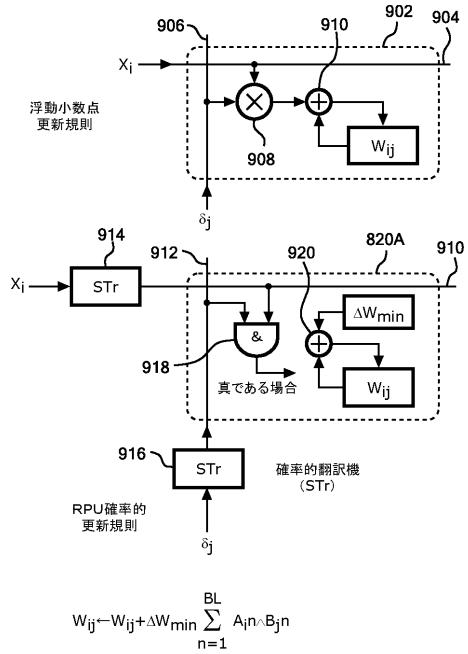

【図9】1つ又は複数の実施形態による確率的重み更新方法論の略ブロック図を示す。

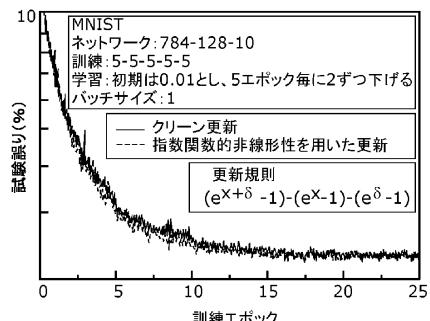

【図10】本開示の確率的重み更新方法論の異なるビット長(BL)に対して達成することができる異なる重み更新精度を使用してMINTデータセット上で訓練されたANNの分類精度を例証するグラフを示す。 20

【図11】(A)～(D)は、1つ又は複数の実施形態による2端子非線形RPUsを使用して確率的重み更新を実装するためのさらなる詳細を例証する略図及びグラフを示す。

【図12】(A)～(B)は、1つ又は複数の実施形態による正及び負の確率的重み更新サイクルを例証する電圧シーケンスを示す。 20

【図13】1つ又は複数の実施形態による2端子非線形RPUsを使用した確率的重み更新の実装についてのさらなる詳細を例証する略図及びグラフを示す。

【図14】(A)～(B)は、公知の2端子メモリスタの線形スイッチング特性と、本開示の2端子RPUsの非線形スイッチング特性との間の図式的比較を示す。

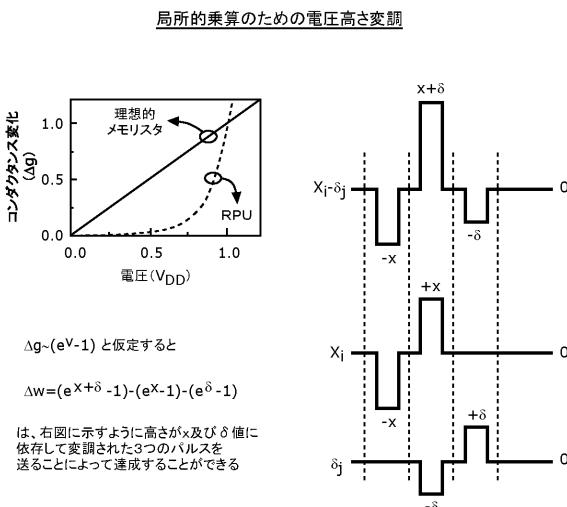

【図15】1つ又は複数の実施形態による指數関数的非線形性を有する2端子RPUsを使用した高さ変調重み更新方法論を例証するグラフ、図及び式を示す。

【図16】1つ又は複数の実施形態による2端子非線形RPUsを使用した高さ変調重み更新方法論をさらに例証するグラフ及び式を示す。

【図17】本開示の2端子非線形RPUsのクロスバーアレイを含むANNアーキテクチャの開発、訓練及び使用の態様を示す。 30

【図18】本開示の2端子非線形RPUsのクロスバーアレイを含むANNアーキテクチャの開発、訓練及び使用のさらなる態様を示す。

【図19】本開示の2端子非線形RPUsのクロスバーアレイを含むANNアーキテクチャの開発、訓練及び使用のさらなる態様を示す。

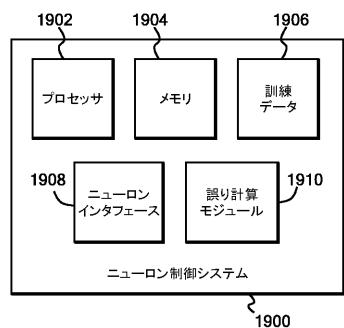

【図20】1つ又は複数の実施形態によるノード制御システムのブロック図を示す。

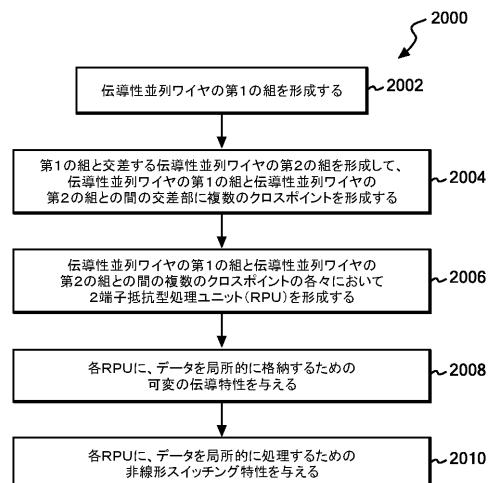

【図21】本開示の1つ又は複数の実施形態による方法論を例証するフロー図を示す。

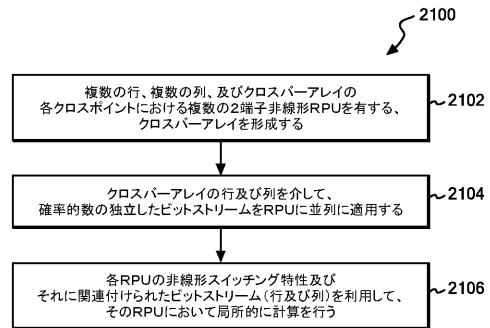

【図22】本開示の1つ又は複数の実施形態による別的方法論を例証するフロー図を示す。

【発明を実施するための形態】 40

**【0033】**

1つ又は複数の実施形態は、特に脳の構造及び機能をモデル化することに重点を置いた生物学的ニューラルネットワークの文脈で開示されるが、本明細書で記述する教示の実施は特定の環境のモデル化に限定されないことがあらかじめ理解される。むしろ本開示の実施形態は、環境に対する様々な入力をベクトルに変えることができる限り、例えば気象パターン、インターネットから収集される任意のデータなどを含む、あらゆるタイプの環境をモデル化することが可能である。

**【0034】**

本開示は、電子システムに向けられたものであるが、参照及び説明を容易にするために、本開示の電子システムの種々の態様を、例えばニューロン、可塑性及びシナプス等の神 50

経学的用語を使用して説明する。本明細書における電子システムのあらゆる議論又は例証について、神経学的用語又は神経学的略記法の使用は参照を容易にするためのものであり、記述した神経学的機能又は神経学的構成要素のニューロモーフィックなA N N等価物に及ぶことを意味することが理解されるであろう。

#### 【0035】

A N Nは、ニューロモーフィック又はシナプトロニック・システムとしても知られており、例えば、生物学的神経システム、画像認識、音声認識などのようなヒトの脳及び脳様の機能を含むその他の機能又はシステムを推定又は近似することができる、計算システムである。A N Nは、神経生理学、認知科学／心理学、物理学（統計力学）、制御理論、コンピュータ科学、人工知能、統計学／数学、パターン認識、計算機視覚、並列処理及びハードウェア（例えば、デジタル／アナログ／V L S I／光学）を含む多様な分野からの知識を取り入れている。10

#### 【0036】

0及び1を操作する伝統的なデジタルモデルを利用する代わりに、A N Nは、推定又は近似されるコアシステム機能の実質的な機能的等価物である処理要素間に接続を生成する。例えば、I B M（I B M社の登録商標）のS y N a p s eコンピュータチップは、哺乳類の脳に類似した形態、機能及びアーキテクチャを提供することを企図した電子的ニューロモーフィックマシンの中心的コンポーネントである。I B M（I B M社の登録商標）S y N a p s eコンピュータチップは、従来のコンピュータチップと同じ基本トランジスタコンポーネントを使用しているが、そのトランジスタは、ニューロン及びそのシナップス接続の挙動を模倣するように構成されている。I B M（I B M社の登録商標）S y N a p s eコンピュータチップは、生物学的ニューロン間のシナップス通信と類似した電気スパイクを用いて互いに通信する、百万個を超えるほどの模擬「ニューロン」のネットワークを使用して情報を処理する。I B M（I B M社の登録商標）S y N a p s eアーキテクチャは、メモリ（すなわち模擬「シナップス」）を読み出して単純な動作を行う、プロセッサ（すなわち模擬「ニューロン」）の構成を含む。典型的には異なるコア内に位置するこれらのプロセッサ間の通信は、オンチップ・ネットワークルータによって行われる。20

#### 【0037】

背景として、典型的なA N Nがどのように動作するかの一般的な説明を、ここで図1、図2及び図3を参照して提供する。本明細書で前述したように、典型的なA N Nは、約1000億もの相互接続されたニューロンと呼ばれる細胞を含むヒトの脳をモデル化する。図1は、上流の入力112、114、下流の出力116及び下流の「他の」ニューロン118に接続する経路104、106、108、110を有する、生物学的ニューロン102の略図を示す。各生物学的ニューロン102は、経路104、106、108、110を通して電気インパルスを送り及び受け取る。これらの電気インパルスの性質及びそれらが生物学的ニューロン102内でどのように処理されるかということが、主として脳全体の機能を担う。生物学的ニューロン間の経路接続は、強い場合もあり又は弱い場合もある。所与のニューロンが入力インパルスを受け取ると、そのニューロンは、ニューロンの機能に従って入力を処理し、その機能の結果を下流の出力及び／又は下流の「他の」ニューロンへ送る。30

#### 【0038】

生物学的ニューロン102は、図2において、図2に示す式で表される数学的関数 $f(x)$ を有するノード202としてモデル化される。ノード202は、入力212、214から電気信号を取得し、各入力212、214に対してそのそれぞれの接続経路204、206の強さを乗算し、入力の和を取り、その和を関数 $f(x)$ に代入して結果216を生成し、これは、最終出力、若しくは別のノードへの入力、又はその両方とすることができます。本開示において、アスタリスク(\*)は、乗算を表すために使用される。弱い入力信号には非常に小さい接続強さ数が乗算されるので、弱い入力信号が関数に与える影響は非常に低い。同様に、強い入力信号にはより高い接続強さ数が乗算されるので、強い入力信号が関数に与える影響はより大きくなる。関数 $f(x)$ は、設計上の選択であり、様々4050

な関数を使用することができる。 $f(x)$ についての典型的な設計上の選択は双曲線正接関数であり、これは、前の和をとり、-1と+1との間の数を出力する関数である。

#### 【0039】

図3は、重み付き有向グラフとして編成された単純化ANNモデル300を示し、ここで人工ニューロンはノード（例えば302、308、316）であり、重み付き有向エッジ（例えば、m1からm20まで）がノードを接続する。ANNモデル300は、ノード302、304、306が入力層ノードであり、ノード308、310、312、314が隠れ層ノードであり、ノード316、318が出力層ノードとなるように編成されている。各ノードは、隣接する層のあらゆるノードに接続経路によって接続され、この接続経路は図3において接続強さm1からm20までを有する有向矢印として描かれている。1つの入力層、1つの隠れ層及び1つの出力層のみが示されているが、実際には、複数の入力層、隠れ層及び出力層を設けることができる。

10

#### 【0040】

ヒトの脳の機能と同様に、ANN300の各入力層ノード302、304、306は、入力x1、x2、x3をソース（図示せず）から直接、接続強さの調整及びノード加算を伴わずに受け取る。従って、図3の下部に挙げた式で示されるように、 $y_1 = f(x_1)$ 、 $y_2 = f(x_2)$ 及び $y_3 = f(x_3)$ である。各隠れ層ノード308、310、312、314は、その入力を、すべての入力層ノード302、304、306から、該当する接続経路に関連付けられた接続強さに従って受け取る。それゆえ、隠れ層ノード308において、 $y_4 = f(m_1 * y_1 + m_5 * y_2 + m_9 * y_3)$ であり、ここで\*は乗算を表す。図3の下部に示した関数y5からy9までを定義する式によって示すように、隠れ層ノード310、312、314及び出力層ノード316、318について、同様の接続強さ乗算及びノード加算が行われる。

20

#### 【0041】

ANNモデル300は、データレコードを一度に1つずつ処理するものであり、初期の任意のレコード分類を既知の実際のレコード分類と比較することによって「学習」する。「バックプロパゲーション（誤差逆伝播法）」（すなわち「後方への誤差伝播」）として知られる訓練方法論を使用して、第1のレコードの初期分類に由来する誤りをネットワークへフィードバックし、これを使用して2回目にネットワークの重み付き接続を修正し、このフィードバックプロセスを多数回の反復にわたって続ける。ANNの訓練相においては、各レコードについての正しい分類は既知であり、したがって出力ノードに「正しい」値を割り当てることができる。例えば、正しいクラスに対応するノードに対してノード値「1」（又は0.9）、その他のノードに対してノード値「0」（又は0.1）とする。それゆえ、その出力ノードに対してネットワークが計算した値をこれらの「正しい」値と比較して、各ノードについて誤差項を計算することが可能である（すなわち「デルタ」則）。次にこれらの誤差項を使用して隠れ層における重みを調整して、次の反復において出力値が「正しい」値により近づくようとする。

30

#### 【0042】

多くのタイプのニューラルネットワークが存在するが、2つの最大カテゴリはフィードフォワード型（順伝播型）及びフィードバック型（逆伝播型）/リカレント型（回帰型）ネットワークである。ANNモデル300は、入力層、出力層及び隠れ層を有する非リカレント型のフィードフォワード型ネットワークである。信号は一方向のみに移動することができる。入力データは、計算を行う処理要素の層へ渡される。各処理要素は、その入力の重み付き和に基づいてその計算を行う。新たに計算された値が、次いで次層へ送られる新たな入力値になる。このプロセスは、すべての層を通過し終えて出力が決定されるまで続く。出力層内のニューロンの出力を定量するために、時には閾値伝達関数が使用される。

40

#### 【0043】

フィードバック型/リカレント型ネットワークはフィードバック経路を含むものであり、これは信号がループを使用して両方向に移動できることを意味する。ノード間のすべて

50

の可能な接続が許容される。このタイプのネットワーク内にはループが存在するので、特定の動作の下で、これは、平衡状態に達するまで連続的に変化する非線形動的システムとなり得る。フィードバック型ネットワークは、連合記憶及び最適化問題においてしばしば使用され、このときネットワークは、相互接続した因子の最良配置を探し求める。

#### 【0044】

フィードフォワード型及びリカレント型のANNアーキテクチャにおける機械学習の速度及び効率は、ANNクロスバーアレイのクロスポイントデバイスが、典型的な機械学習アルゴリズムのコア動作をどれほど効率的に行うかに依存する。機械学習の正確な定義を公式化することは難しいが、ANN文脈における学習プロセスは、クロスポイントデバイスの接続重みを、ネットワークが特定のタスクを効率的に行うことができるよう更新する問題として捉えることができる。クロスポイントデバイスは、典型的には、利用可能な訓練パターンから必要な接続重みを学習する。性能は、ネットワーク内の重みを反復的に更新することによって経時的に向上する。専門家によって指定された規則の組に従う代わりに、ANNは、根底にある（入力 - 出力関係の様な）規則を所与の代表例の集まりから「学習」する。従って、学習アルゴリズムは、一般に、学習規則を使用して該当する重みを更新する及び / 又は調整する手順として定義することができる。

#### 【0045】

3つの主要な学習アルゴリズムのパラダイムは、教師付き(supervised)、教師なし(unsupervised)及びハイブリッドである。教師付き学習、すなわち「教師(teacher)」を伴う学習において、ネットワークには、すべての入力パターンに対して正解(出力)が与えられる。重みは、ネットワークが既知の正解にできる限り近い解答を生成することを可能にするように決定される。強化学習は、教師付き学習の变形であり、ネットワークには、正解そのものではなく、ネットワーク出力の正しさに対する批評のみが与えられる。対照的に、教師なし学習、すなわち教師を伴わない学習は、訓練データセット内の各入力パターンに関連付けられた正解を必要としない。これは、データにおける根底にある構造、又はデータにおけるパターン間の相関を探求し、これらの相関からパターンをカテゴリに編成する。ハイブリッド学習は、教師付き学習と教師なし学習とを組み合わせたものである。重みの一部は、一般に教師付き学習を通じて決定され、その他は、教師なし学習を通じて得られる。ANN及び学習規則のさらなる詳細は、非特許文献1に記載されている。

#### 【0046】

本明細書において前述したように、電力消費を制限するために、ANNチップアーキテクチャのクロスポイントデバイスは、オンライン学習技術を利用するように設計されることが多く、この場合、目的関数の近似は、ひとたび初期訓練相が解決されると変化しない。オンライン学習は、クロスバー型ANNアーキテクチャのクロスポイントデバイスを、非常に少ない電力しか消費しないように単純化することを可能にする。

#### 【0047】

電力消費をより低くする可能性があるにもかかわらず、オンライン学習を実行することは、訓練データに対して入力 - 出力ペアを適合させるために典型的には訓練中にANNモデル内の著しい数の調整可能なパラメータ(例えば重み)を修正することを必要とするので、困難かつリソース集約的なものとなることがある。図4は、典型的な読み出し - 処理 - 書込みの重み更新動作の略図を示したものであり、CPU/GPUコア(すなわち模擬「ニューロン」)は、メモリ(すなわち模擬「シナプス」)を読み出し、重み更新処理動作を行い、次いで更新された重みを再びメモリに書き込む。従って、電力節約型のオンライン学習技術を優先するためにANNアーキテクチャのクロスポイントデバイスを単純化することは、典型的には、訓練速度及び訓練効率は最適化されないことを意味する。

#### 【0048】

電力消費を許容可能な範囲内に保持するとともにANNアーキテクチャの訓練速度及び効率を加速する単純なクロスポイントデバイスを提供することは、全体としてのANN性能を改善し、より広範囲のANN用途を可能にするであろう。

10

20

30

40

50

## 【0049】

ここで本開示の概要に目を向けると、1つ又は複数の実施形態は、本明細書において抵抗型処理ユニット（RPU）と称される2端子のプログラム可能な抵抗型クロスポートコンポーネントに向けられ、これは局所的データストレージ機能及び局所的データ処理機能を提供する。換言すれば、データ処理を行うとき、各RPUに格納された値は、並列的かつ局所的に更新され、そのことにより、該当データをプロセッサ及び別個のストレージ要素から出し入れして移動させる必要性が解消される。加えて、本開示の2端子RPUによって提供される局所的データストレージ及び局所的データ処理は、ANNが、バックプロパゲーション型オンライン・ニューラルネットワーク訓練、行列反転、行列分解などのアルゴリズムを学習し及び実装する能力を加速する。従って、本開示のRPUを有する機械学習ANNアーキテクチャを実装することは、学習の速度、効率及び電力消費を最適化するオンライン機械学習能力の実装を可能にする。本開示のRPU、及び結果として得られるANNアーキテクチャは、全体としてのANN性能を改善し、より広範囲の実用的なANN用途を可能にする。

10

## 【0050】

本開示のRPUは、2端子抵抗型クロスポートデバイスとして実装することができ、それらのスイッチング特性は、データを処理するために使用することができる非線形性を有する。それゆえ、本開示のRPUは、ANNにおいて計算を行うために使用することができる適切な非線形特性を有する、任意の2端子デバイスによって実装することができる。例えば、本開示のRPUデバイスは、抵抗変化型ランダムアクセスメモリ（RRAM）、相変化メモリ（PCM）、プログラム可能金属化セル（PMC）メモリ、非線形メモリスタ・システム、又はその他の非線形抵抗型スイッチング特性を有する任意の2端子デバイスで実装することができる。

20

## 【0051】

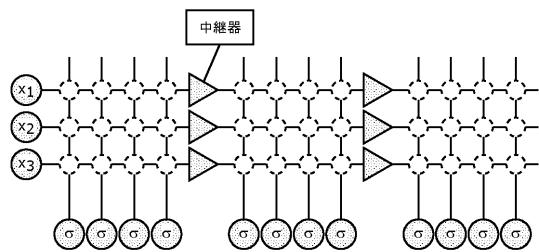

本開示のRPUのより詳細な説明に先立って、本開示に関連する、シストリックアレイ、確率的計算並びに線形及び非線形メモリスタ・デバイスの概要をここで提供する。シストリックアレイは、特定の大いに用いられているアルゴリズムの学習を加速することを企図した並列処理要素（PE）で構成される。シストリックアレイは、しばしば「積和（multiply and accumulate）」等の特定の演算用にハードウェイアードされており、積分、たたみこみ、相関、行列乗算又はデータ格納のタスクを大規模に並列に行う。非特許文献2において、シストリックアレイをオンライン学習ニューラルネットワーク用の構成ブロックとして使用することが提唱されており、ここでシストリックアレイ内の各PEは、単一の重み値を格納するための局所ストレージを有し、行列乗算及び重み更新のために必要な計算を行うことが可能である。非特許文献2に記載のPEの超大規模集積（VLSI）実装は、PE当たりおよそ1800個のトランジスタを要し、これは電力消費を増大させ、スケーラビリティを低減する。したがって、PE当たりに必要とされるトランジスタができるだけ少ないPEを提供することが望ましい。

30

## 【0052】

確率的計算は、ランダムビットのストリームによって連續的な値を表す技術の集まりであり、複雑な計算をストリーム上の単純なビット単位の演算で行うことができる。詳細には、確率的数（stochastic number）と呼ばれる2つのランダムかつ独立したビットストリーム $S_1$ 、 $S_2$ が存在するとして（すなわちベルヌーイ過程）、ここで第1のストリームにおける「1」の確率を $p$ 、第2のストリームにおける「1」の確率を $q$ とすると、2つのストリームの論理ANDを図5に示すように得ることができる。出力ストリームにおける「1」の確率は、 $p q$ である。十分な出力ビットを観測し、「1」の頻度を測定することによって、 $p q$ を任意の精度まで推定することができる。少ない論理ゲート/トランジスタで実装することができるこれらのいわゆる「積和」演算の設計の単純さゆえに、確率的計算は、しばしばニューラルネットワーク用のハードウェア設計において使用される。非特許文献3は、ニューラルネットワーク訓練アルゴリズムのためのハードウェアアクセラレータとして使用することができる2次元（2D）シストリッ

40

50

クアレイに対する確率的計算の適用を示す。

**【0053】**

しかしながら、非特許文献3においては、計算に必要な重みは、外部位置からシストリックアレイに供給され、重みに対する更新はアレイによって行われるわけではない。非特許文献3は、ニューラルネットワーク訓練中に大量に使用されるベクトル・行列乗算又は行列・行列乗算演算の加速のみを扱うものである。しかしながら、局所ストレージを伴わないシストリックアレイでは、重みは外部メモリ位置に格納されているので、重み更新を並列に行うこととはできない。全体としての学習アルゴリズムを加速するためには、非特許文献3には開示されていない重み更新の加速が必要である。

**【0054】**

「メモリスト」という用語は、デバイスの抵抗値がそのデバイスに以前に印加された電圧の履歴に依存する受動的2端子電気コンポーネントを記述するために使用される。メモリストの動作は、図6に示す式[1]及び式[2]によって支配され、式中、 $i$ はデバイスを通る電流、 $v$ はデバイスに印加された電圧、 $g$ はデバイスのコンダクタンス値（抵抗の逆数）、 $s$ はコンダクタンス値を制御するデバイスの内部状態変数、 $f$ は内部状態変数 $s$ の時間発展を示す関数である。非特許文献4において、メモリスト機能が、抵抗変化型ランダムアクセスメモリ（RRAM）、相変化メモリ（PCM）及び導電性ブリッジランダムアクセスメモリ（CBRAM）等の抵抗型メモリデバイスの動作に対して提案されている。メモリスト・デバイスは、その履歴を記憶する（すなわち、いわゆる「不揮発性」）ので、非特許文献4は、このようなデバイスを不揮発性メモリ技術の可能な代替として提案している。

**【0055】**

非特許文献5は、バックプロパゲーション型ニューラルネットワーク訓練ハードウェアに対するメモリストの使用を提案している。しかしながら、非特許文献5は、デバイスに印加された電圧に対して抵抗の変化が線形である、理想的なメモリスト動作を仮定している。非特許文献5の設計は、図6の式[2]における関数 $f(s, v)$ が関係 $f(s, v) = v$ で与えられる単順な関数であると仮定したものである。非特許文献5は、上述のような2Dシストリックアレイに類似したアーキテクチャを提案しており、各クロスポイントは、理想的メモリスト及び一対のトランジスタで実装されている。非特許文献5において、メモリストは、事実上、重み値を格納するのに使用され、一対のトランジスタは、重み更新のために必要な局所的乗算演算を計算するのに使用され、重み更新の結果がメモリストの伝導状態を修正する。非特許文献5は、事実上、メモリスト及び2つのトランジスタで構成された4端子デバイスを開示し、これはニューラルネットワーク・ハードウェアのバックプロパゲーション型訓練を実装するために4端子デバイスの2Dアレイを作製するのに使用される。

**【0056】**

ここで本開示のより詳細な説明に目を向けると、1つ又は複数の実施形態は、2端子RPUに向けられ、これは、トランジスタ並びにオフチップ・ストレージ及び/又は処理コンポーネント等の余分な回路要素を必要とすることなく、局所的データストレージ機能及び局所的データ処理機能を提供する。本開示のRPUは、RRAM、PCM、CBRAM、非線形メモリスト・システムなどを含むがこれらに限定されない、非線形スイッチング特性を有する任意のデバイスとして実装することができる。

**【0057】**

本開示のRPUデバイスをメモリスト・システムとして実装するとき、メモリストは、非線形スイッチング特性を有する非理想的なものであることが重要である。理想的メモリストにおいては、抵抗の変化は、理想的メモリスト・デバイスに印加された電圧に対して線形に比例する。従って、理想的メモリスト・デバイスは、なんらかの電圧を経験した途端に、その抵抗状態が変化する。しかしながら、非理想的な非線形メモリスト・システムとして実装された本開示のRPUの場合、明確な「セット」電圧 $V_{SET}$ （これはデバイスの特性である）が存在し、メモリストRPUデバイスは、その内部抵抗状態を変化させ

10

20

30

40

50

るためには電圧  $V > V_{SET}$  を経験することを必要とする。このようなデバイスの場合、電圧  $V = 0.5V_{SET}$  のハーフバイアス印加は、内部抵抗状態になんら変化を生じさせない。

#### 【0058】

理想的メモリスタと、本開示のRPUを実装するのに使用することができる非理想的な非線形メモリスタとの間の差異をさらに例証するために、図7は、理想的メモリスタと本開示によるRPUとの間での電圧スイッチング挙動比較を示すグラフである。縦軸は特定の電圧におけるデバイス状態変化を表し、横軸は印加された電圧を表す。理想的メモリスタ動作においては、抵抗の変化は、デバイスに印加された電圧に線形に比例する。それゆえ、メモリスタが電圧に遭遇した途端に、その抵抗状態が変化する。このことは曲線702によって示され、これは、低電圧であっても状態の変化が劇的であることを示す。

10

#### 【0059】

曲線704によって示されるような非線形RPUデバイスの場合、デバイスがその内部抵抗状態を変化させるために経験する必要がある明確なセット電圧  $V_{SET}$  が存在する。 $0.5V_{SET}$  のバイアス電圧は、内部抵抗状態を変化させない。本開示においては、このRPUデバイスの非線形特性を活用して、局所的に乗算を行う。 $f_1$  が小さいと仮定すると、デバイスは、 $0.5V_{SET}$  が印加されただけではその内部状態を変化させない。特に、図7は、正電圧と、RPUデバイスの抵抗状態に対する正の変化とを例証するが、負電圧と負の抵抗変化との間にも同様の関係が存在する。

20

#### 【0060】

図8は、本開示による、順方向行列乗算、逆方向行列乗算及び重み更新を行う2次元(2D)クロスバーアレイ800の図である。クロスバーアレイ800は、伝導性行ワイヤ802、804、806の組と、伝導性行ワイヤ802、804、806の組と交差する伝導性列ワイヤ808、810、812、814の組とから形成される。行ワイヤの組と列ワイヤの組との間の交差部は、RPUによって分離され、それらは図8において、各自がそれぞれ  $1\ 1\ \wedge\ 2\ 1\ \wedge\ 3\ 1\ \wedge\ 4\ 1\ \wedge\ 1\ 2\ \wedge\ 2\ 2\ \wedge\ 3\ 2\ \wedge\ 4\ 2\ \wedge\ 1\ 3$  、  $2\ 3\ \wedge\ 3\ 3$  及び  $4\ 3$  で表されるそれ自体の調整可能 / 更新可能な抵抗重みを有する抵抗要素として示される。図示を簡単にするために、図8においては1つのRPU820にのみ符号を付した。順方向行列乗算において、RPUの伝導状態(すなわち格納された重み)は、RPUの両端間に電圧を印加し、RPUを通る電流を測定することによって読み出すことができる。

30

#### 【0061】

入力電圧  $V_1$ 、 $V_2$ 、 $V_3$  がそれぞれ行ワイヤ802、804、806に印加される。各列ワイヤ808、810、812、814は、特定の列ワイヤに沿って各RPUによって生成された電流  $I_1$ 、 $I_2$ 、 $I_3$ 、 $I_4$  を合計する。例えば、図8に示すように、列ワイヤ814によって生成された電流  $I_4$  は、式  $I_4 = V_1 \cdot 4_1 + V_2 \cdot 4_2 + V_3 \cdot 4_3$  に従う。それゆえ、アレイ800は、RPUに格納された値に、電圧  $V_1$ 、 $V_2$ 、 $V_3$  で定められる行ワイヤ入力を乗ずることによって、順方向行列乗算を計算する。逆方向行列乗算は、全く同様である。逆方向行列乗算においては、電圧は列ワイヤ808、810、812、814に印加され、行ワイヤ802、804、806から読み出される。より詳細に後述する重み更新の場合、電圧は列ワイヤ及び行ワイヤに同時に印加され、該当するRPUデバイスに格納されたコンダクタンス値がすべて並列に更新される。従って、重み更新を行うために必要な積和演算は、RPUデバイス自体に加えて、アレイ800の該当する行又は列ワイヤを使用して、アレイ800の各RPU820において局所的に行われる。それゆえ、本開示によれば、アレイ800において読み出し - 更新 - 書込みサイクル(図4に示す)は必要とされない。

40

#### 【0062】

引き続き図8の図を用いて、1つ又は複数の実施形態により、ここで、正の重み更新方法論の動作を、RPU820及び伝導性行ワイヤ806と伝導性列ワイヤ814との交差部におけるその対応する重み  $4_3$  について提供する。RPU820の非線形特性を用い

50

て、後述のように確率的計算を使用して R P U 8 2 0 において局所的に乗算演算を行う。より詳細には、本開示の方法論は、R P U 8 2 0 の非線形スイッチング特性及び確率的ビットストリーム 8 3 0 、 8 3 2 を使用して、他の回路要素を必要とすることなく、乗算演算及び必要な重み更新を R P U 8 2 0 において局所的に行う。更新発生器回路（図示せず）がクロスバーアレイ 8 0 0 の周辺部に設けられ、2 D クロスバーアレイ 8 0 0 のすべての R P U に並列に印加される確率的ビットストリーム（例えば 8 3 0 、 8 3 2 ）形態の必要な電圧パルスを発生するための、周辺「翻訳機」として使用される。

#### 【 0 0 6 3 】

図 7 の図を一時的に参照すると、図 8 に示す R P U 8 2 0 に対する  $f_1$  は、非常に小さい（例えば  $f_1 = 0$  ）と仮定され、これは  $0.5 V_{S E T}$  が印加されただけでは R P U 8 2 0 がその内部状態を変化させないことを意味する。行電圧シーケンス又はビットストリーム 8 3 0 は、行ワイヤ 8 0 6 に印加され、ゼロ電圧又は  $+0.5 V_{S E T}$  電圧を有する、重み更新を表す電圧パルスのシーケンスとして示される。列電圧シーケンス又はビットストリーム 8 3 2 は、列ワイヤ 8 1 4 に印加され、ゼロ電圧又は  $-0.5 V_{S E T}$  電圧のいずれかを有する、同じく重み更新を表す電圧パルスのシーケンスとして示される。図 8 の例においては、4 / 8 が行電圧シーケンス 8 3 0 によってコード化され、6 / 8 が列電圧シーケンス 8 3 2 によってコード化されている。例示的な電圧シーケンス 8 3 0 、 8 3 2 は、重み更新の正の抵抗変化相を表す。正の重み更新が行われた後、それぞれの電圧の極性を反転させた別個のシーケンスの組を使用して、負の方向に、そのような訂正が必要な重みについて重みを更新することができる。

#### 【 0 0 6 4 】

電圧シーケンス 8 3 4 は、行電圧シーケンス 8 3 0 と列電圧シーケンス 8 3 2 との間の差分から得られる、R P U 8 2 0 に印加される電圧である。電圧シーケンス 8 3 4 は、0 V 、  $0.5 V_{S E T}$  及び  $V_{S E T}$  の 3 つの電圧段階を有する。しかしながら、R P U 8 2 0 の抵抗  $_{43}$  はデバイス電圧が  $V_{S E T}$  に達したときにのみ変化するので、列ワイヤ又は行ワイヤのどちらかを通じて送られる単一のパルスでは、R P U 8 2 0 の抵抗状態を変化させるのに十分ではない。列ワイヤが  $0.5 V_{S E T}$  の電圧を送り、行ワイヤが  $-0.5 V_{S E T}$  の電圧を送るとき、結果として生じる、該当の R P U に印加される  $V_{S E T}$  パルスが、デバイスの抵抗のインクリメンタルな変化を引き起こす。従って、R P U 8 2 0 に印加される電圧パルスは、（図 5 に示すような）ビット単位の確率的 A N D 演算を R P U 8 2 0 において局所的に行うために、R P U 8 2 0 の非線形スイッチング特性を利用することになる。それゆえ、結果として得られる、R P U の格納された重み（例えば  $_{43}$  ）の変化は、クロスバーアレイ 8 0 0 の周辺の更新発生器回路によって「翻訳」された 2 つの数の積（ $4 / 8 * 6 / 8 = 3 / 8$  ）に比例する。

#### 【 0 0 6 5 】

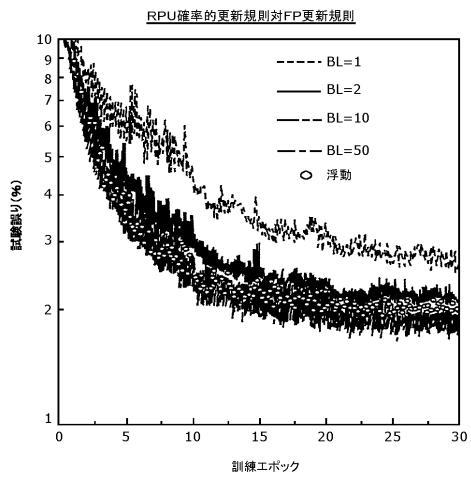

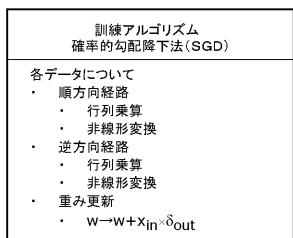

図 9 及び図 10 は、例示的な公知の浮動小数点（ F P ）重み更新規則の分類誤り率の性能と、本開示の確率的 R P U ( S R P U ) 更新規則との比較を示す。 F P 重み更新規則は、乗算演算と等価であるベクトル - ベクトル外積を計算することを必要とし、インクリメンタルな重み更新を図 9 に示すように各クロスポイントにおいて局所的に行わなければならない。 F P 重み更新規則は、  $w_{i,j} w_{i,j} + x_{i,j}$  として表すことができ、ここで  $w_{i,j}$  は、 i 番目の行及び j 番目の列に対する重み値を表し、  $x_{i,j}$  は、入力ニューロンにおける活性であり、  $x_{i,j}$  は、出力ニューロンによって計算された誤りであり、  $x_{i,j}$  は大域的学習率である。

#### 【 0 0 6 6 】

図 9 に示すように、 F P 重み更新規則は、クロスバーアレイ（図示せず）の行ワイヤ 9 0 4 と列ワイヤ 9 0 6 との間のクロスポイントに位置する F P クロスポイントデバイス 9 0 2 を使用する。 F P クロスポイントデバイス 9 0 2 は、 2 つより多い端子を有する処理コンポーネント（図示せず）を含み、処理コンポーネントは、それぞれ行ワイヤ 9 0 4 及び列ワイヤ 9 0 6 に印加される信号  $x_{i,j}$  及び  $x_{i,j}$  を介して、更新データを F P 数として受け取る。 F P クロスポイントデバイス 9 0 2 は、乗算演算 9 0 8 及び加算演算 9 1 0 を使

10

20

30

40

50

用して重み更新  $W_{i,j}$  を計算し、次いで重み更新  $W_{i,j}$  を格納する。FP重み更新規則は、精度をもたらすが、読み出し・書き込み・処理の更新動作（例えば図4に示す）、又は、2つより多くの端子を有する比較的複雑で電力を消費する局所処理コンポーネントのいずれかを必要とする。例えば、FPクロスポイントデバイス902の処理コンポーネントは、非特許文献5に記載されているように一対のトランジスタとタンデムで動作する2端子の理想的メモリスタとして実装することができる。メモリスタは、事実上、重み値を格納するために使用され、一対のトランジスタは、重み更新のために必要な局所的乗算演算を計算するのに使用され、重み更新の結果がメモリスタの伝導状態を修正する。

#### 【0067】

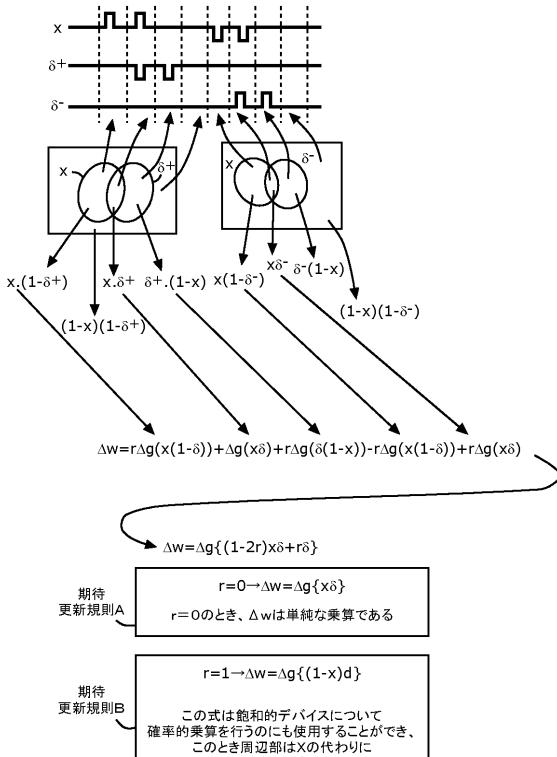

本開示のSRPU重み更新規則の実施形態は、図9の式3で示され、式中、BLは更新サイクル中に使用されるビットストリームの長さであり、 $w_{m_i,n}$ は単一の一一致事象に起因する重み値の有効変化であり、 $A_i^n$ 及び $B_j^n$ は、ベルヌーイ過程によって特徴づけられるランダム変数であり、それらの成功率はそれぞれ $x_i$ 及び $x_j$ によって特徴づけられ、上付き文字nはパルス指数を表す。図9に示すSRPU重み更新規則は、単一のアレイ内のすべてのRPUデバイスが並列に動作すること、及び、局所的乗算演算を単に一致事象の統計に対して応答することによって行うことを可能にする。しかしながら、更新の確率的(stochastic)性質ゆえに、結果は常に確率的(probabilistic)であり、乗算演算の分散対平均比は、BLの平方根の逆数に比例する。

#### 【0068】

図9に示すように、SRPU重み更新規則は、RPUクロスポイントデバイス820Aを使用し、これは図8に示しかつ上で詳述したRPU820と実質的に同じように動作する。RPU820Aは、クロスバーアレイ（図示せず）の行ワイヤ910と列ワイヤ912との間のクロスポイントに位置する。RPU820Aは、2つの端子を有する処理コンポーネント（図8で820において示す）を含み、処理コンポーネントは、入力データ $x_i$ 及び $x_j$ を受け取り、それぞれ行ワイヤ910及び列ワイヤ912に確率的電圧シーケンスを印加する、確率的翻訳機914、916によって生成された確率的信号を介して、更新データを確率的数として受け取る。RPU820Aは、 $w_{i,j}$ の新たな値を、確率的ビットストリーム、RPU820Aの非線形特性、AND演算918及び加算演算920を使用して計算する。より詳細には、RPU820Aは、一致事象毎に、重み変化 $w_{m_i,n}$ と等価なインクリメンタルなコンダクタンス変化を生じさせ、 $w_{m_i,n}$ を格納された重み値に加算して、更新された重み値 $w_{i,j}$ に到達する。

#### 【0069】

図10のグラフは、バックプロパゲーションアルゴリズムを使用した深層ニューラルネットワークの訓練問題を上述のSRPU重み更新規則として定義した確率的更新規則を用いて解析し、その結果を上述のFP重み更新規則を使用したベースラインと比較することによって、SRPU重み更新規則の分類誤り率とFP重み更新の分類誤り率との間の比較の結果を示す。MNISTデータセットに対して数字分類(digit classification)タスクを行う。深層ニューラルネットワークは、入力から出力まで各層がそれぞれ784、256、128及び10ニューロンを含む、完全に接続された層によって構成した。データの前処理は行わず、未処理の画素値を入力として与えた。シグモイド・ニューロンを隠れ層において使用し、ソフトマックス・ニューロンを出力において使用した。クロスエントロピー目的関数を使用した。ベースラインFP重み更新については、浮動小数点算術を使用して、バッチサイズ1(unity)、並びに、0~10、11~20及び21~30のエポックについてそれぞれ学習率0.01、0.005及び0.0025で訓練を行った。ベースラインは、図10に示すグラフ上の白丸で示すように、30エポックの終了時にテストデータに対して約2.0%の分類精度に達した。

#### 【0070】

学習率は、ニューラルネットワークの許容可能な収束特性を達成するためにある程度まで調整しなければならない重要なハイパーパラメータである。したがって、本開示のSRPU重み更新については、FP重み更新ベースラインに対して使用した値と平均して同一

10

20

30

40

50

となる学習率を使用する。図10に示すシミュレーションは、 $x_i$  及び  $j$  がスケーリングなしで確率的ストリームに直接翻訳されること、及び、 $P(A_i^n = \text{成功}) = x_i$  及び  $P(B_j^n = \text{成功}) = j$  であることを仮定した。したがって、重み値の平均変化は、 $E(w_{ij}) = BL \times w_{min} \times x_i - j$  と記述することができる。第1のシミュレーションの組において、FP重み更新ベースラインに対して使用した学習率と一致させるために、BLを固定し、 $w_{min} = / BL$ とした。異なるBLを使用して訓練を行い、SRPU重み更新に対するアルゴリズムの許容差を観測した。図10のグラフに示すように、SRPU重み更新規則はBLに対して非常にロバストであり、実際、BL=10について、SRPU重み更新規則の精度は、ベースラインのFP重み更新規則と区別できなくなる。それゆえ、図10で実証されるように、SRPU重み更新は、単にBL=10サイクルを使用することによって、FP重み更新と同様に行うことができ、アレイサイズに依存せずに並列に動作するRPUデバイスによって実装することができる。

10

#### 【0071】

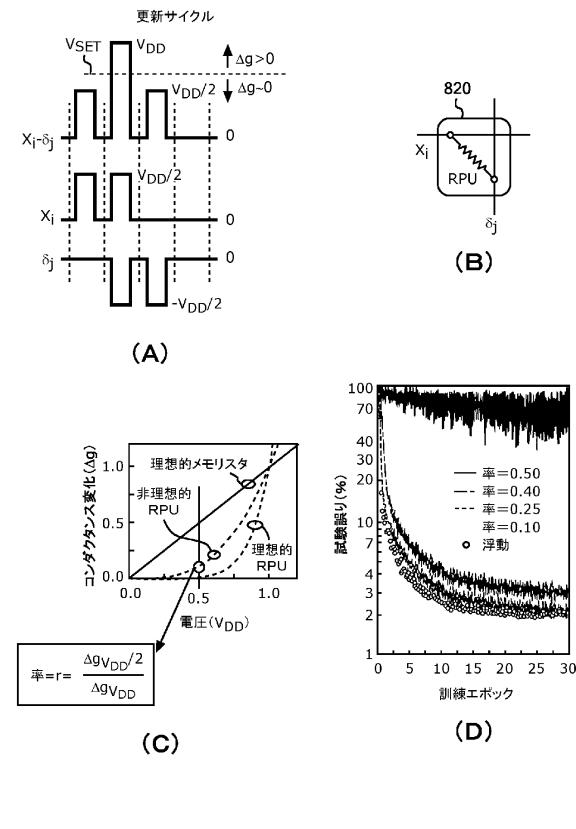

図11(A)～図11(D)は、1つ又は複数の実施形態による2端子非線形RPUを使用する本開示の確率的重み更新について、RPUの線形性( $r$ )をどのように計算するかを例証する略図及びグラフを示す。図11(A)は、前述の確率的電圧シーケンスを示し、図11(B)は、確率的電圧シーケンスを受け取って応答するRPU820を示す。図11(A)は、 $x_i$  及び  $j$  に印加された電圧シーケンスに応答したRPUの伝導値の変化である、 $g$  も示す。より詳細には、 $g$  は、 $V_{DD}$ に達した電圧パルスに対するRPU820の応答である。従って、デバイス線形率 $r$ は、図11(C)に示す式に従って決定することができる。図11(C)は、図7と同様のスイッチング図であり、これは $g$  対 $V_{DD}$ をプロットし、理想的メモリスタの応答を非理想的RPU及び理想的RPUと比較したものである。図11(D)は、異なる非線形率について、分類誤りを示す。図11(C)及び図11(D)は、関連したパラメータを変化させることによって異なる非線形性レベルでRPU820を設計し及び動作させることができる、及び、RPU820はたとえ非理想的であってもなお、許容可能な分類誤り率で動作することを実証する。

20

#### 【0072】

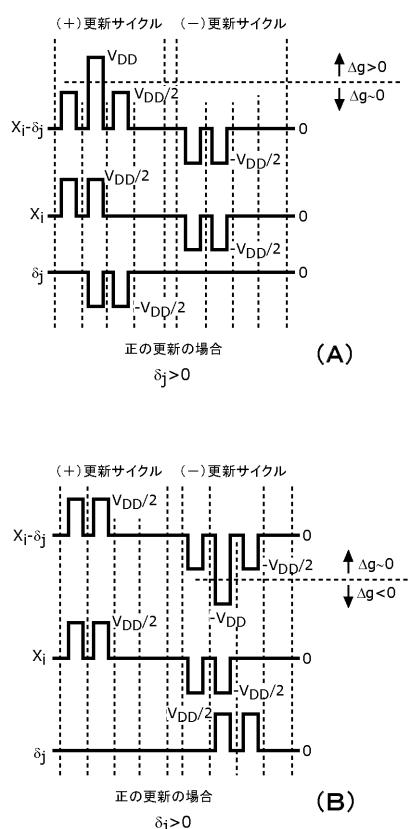

図11(A)は、正の更新サイクルパルスを示す。図12(A)及び図12(B)は、パルスの極性を変更することによって、正及び負の更新サイクルの両方を実装することができる事を示す。

30

#### 【0073】

図13は、1つ又は複数の実施形態による2端子非線形RPUを使用した確率的重み更新の実装についてのさらなる詳細を例証する略図及びグラフを示す。図13は、図12(A)及び図12(B)に示す正及び負のパルシング・スキームによって、平均で、どの程度の重み変化  $w$  が得られるかを示す。従って、 $x_i$  及び  $j$  をそれぞれのパルス符号に基づいて正の更新サイクル及び負の更新サイクルの両方に代入する。これは、RPU上に重なりがあるときにRPU上の電圧が  $g$  の符号に基づいて正方向又は負方向のいずれかで閾値を通ることが可能であることを保証する。パルスシーケンスの下に示す図は、パルスシーケンス内のパルス  $x$ 、 $+$  及び  $-$  がどのように相互作用するかの単なる図式的表現である。半パルス及び全パルスからの寄与に基づいて  $w$  についての式によって示されるように期待値を合計することによって、最終的な期待更新規則  $w$  の2つの形態を導出することができる。

40

#### 【0074】

図14(A)及び図14(B)は、本開示のRPUの整流的(rectifying)非線形性(図11(C)にも示す)及び本開示のRPUの飽和的(saturating)非線形性を横に並べて比較して示す。飽和的非線形性については、 $x$ をコード化してRPUへ入れる代わりに、飽和的非線形RPUが必要な乗算を行うために $1-x$ をコード化することが必要である。

#### 【0075】

図15及び図16は、指數関数的非線形性を有する2端子RPUと共に高さ変調パルシング・スキームを使用したときの期待重み更新規則  $w$ を例証するグラフ、図及び式を示す。この例においては、確率的コード化を電圧高さ変調によって置き換える。図16に示すように、テイラー展開を用いて、期待重み更新規則を単純化して  $w = x$  にすることができる。従って、図15及び図16に示す導出は、図15及び図16に示す高次項が問題にならないこと、及び、指數関数的高さ変調RPUは、図16の右下に示すグラフによつて示されるように前述の実施形態と同じく良い機能することを実証する。

#### 【0076】

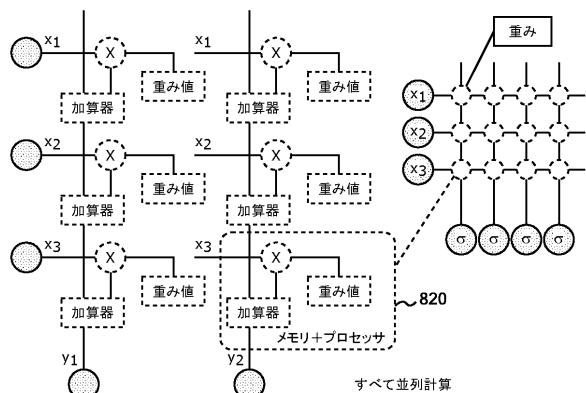

図17～図19は、本開示による2端子非線形RPUのクロスバーアレイを含むANNアーキテクチャの開発、訓練及び使用の態様を示す。図17は、ニューラルネットワークを設計するための開始点を示す。事実上、図17は、図3に示すニューラルネットワーク図の代替的表現である。図17に示すように、 $x_1$ 、 $x_2$ 及び $x_3$ である入力ニューロンは、シグマ( )で示される隠れニューロンに接続される。重みは、接続の強さを表し、入力ニューロンノードと隠れニューロンノードとの間、並びに、隠れニューロンノードと出力ニューロンノードとの間の接続に適用される。重みは、行列の形態である。データがネットワークを通じて順方向に移動するとき、ベクトル行列乗算が行われ、隠れニューロンノードは、入力を取得し、非線形変換を行い、次いで結果を次の重み行列へ送る。このプロセスは、データが出力ニューロンノードに到達するまで続く。出力ニューロンノードは、分類誤りを評価し、次いでこの分類誤りを順方向経路と同様の方式で逆方向に伝播し、その結果、ベクトル行列乗算が逆方向に行われる。各データセットについて、順方向経路及び逆方向経路が完了すると、重み更新が行われる。基本的に、各重みは、入力ニューロンノードによって定められるその重みに対する入力、及び、それが接続されたニューロンノードによって計算された誤りに比例して、更新される。

10

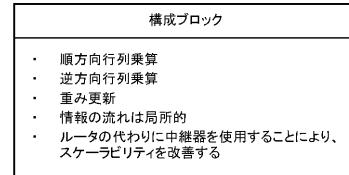

#### 【0077】

図18は、どのようにしてネットワークを中継器によって接続される構成ブロックに分割することができるかを示し、それゆえ、ニューラルネットワークを任意のサイズに拡張することができる。ネットワークは本開示のRPUを使用するので、情報の流れは局所的であり、そのことにより、構成ブロックを反復することが容易になり、また、スケーラビリティを制限するボトルネックとなり得るルータの必要性が排除される。

20

#### 【0078】

30

図19は、RPU820(図8に示す)から形成されるネットワーク構成ブロックを示す。RPU820には、図7、図11(C)、図14(A)、図14(B)又は図15に示す任意の非線形プロファイルを与えることができる。

#### 【0079】

ここで図20を参照して、ノード/ニューロン制御システム1900を示す。ニューロン制御システム1900は、ハードウェアプロセッサ1902及びメモリ1904を含む。ANN用の訓練データ1906は、メモリ1904内に格納され、ANNの重みを訓練するために使用される。ニューロンインタフェース1908は、ANN上のニューロンを制御し、ニューロンがフィードフォワードモード、バックプロパゲーションモード、又は重み更新モードのいずれであるかを決定する。ニューロンインタフェース1908は、さらに、入力ニューロンに入力を与え、出力ニューロンから出力を受け取る。誤り計算モジュール1910は、ニューロンからの出力を訓練データ1906と比較して、誤り信号を決定する。ニューロンインタフェース1908は、誤り信号をバックプロパゲーションモード中に出力ニューロンに印加し、次いで重み更新モードをトリガして、ANNの重みをそれに応じて訓練する。

40

#### 【0080】

図21は、1つ又は複数の実施形態による方法論2000を例証するフロー図を示す。方法論2000は、ブロック2002において、伝導性並列ワイヤの第1の組を形成することによって開始する。ブロック2004は、第1の組と交差する伝導性並列ワイヤの第2の組を形成して、伝導性並列ワイヤの第1の組と伝導性並列ワイヤの第2の組との間の

50

交差部に複数のクロスポイントを形成する。ブロック 2006 は、伝導性並列ワイヤの第 1 の組と伝導性並列ワイヤの第 2 の組との間の複数のクロスポイントの各々において 2 端子 RPU を形成する。ブロック 2008 は、各 RPU に、データを局所的に格納するための可変の伝導特性を与え、ブロック 2010 は、各 RPU に、データを局所的に処理するための非線形スイッチング特性を与える。

#### 【0081】

図 22 は、1つ又は複数の実施形態による方法論 2100 を例証する別のフロー図を示す。方法論 2100 は、ブロック 2102 において、複数の行、複数の列、及びクロスバーアレイの各クロスポイントにおける複数の 2 端子非線形 RPU を有する、クロスバーアレイを形成することによって開始する。ブロック 2104 は、クロスバーアレイの行及び列を介して、確率的数の独立したビットストリームを RPU に並列に適用する。ブロック 2106 は、各 RPU の非線形スイッチング特性及びそれに関連付けられたビットストリーム（行及び列）を利用して、その RPU において局所的に計算を行う。10

#### 【0082】

従って、本開示は、多くの技術的利益を提供する。単一の 2 端子デバイスは、コード化された入力ビットストリームとともに、そのデバイスの非線形スイッチング特性を使用して、重み更新を局所的に行い、これは、消費電力が低く、かつ、非線形 RPU のクロスバーアレイから形成された ANN における機械学習を加速する。本開示の RPU は、順方向経路の行列乗算、逆方向経路の行列乗算及び重み更新を行うために必要な処理及びストレージステップを局所的に行うことができる。この RPU は、オンライン・ニューラルネットワーク訓練、行列反転及び行列分解を含む様々な訓練方法論を加速することができる。20

#### 【0083】

1つ又は複数の実施形態の一部は、デバイス、システム、方法及び／又はコンピュータプログラム製品とすることができます。1つ又は複数の実施形態によるコンピュータプログラム製品は、1つ又は複数の実施形態の態様をプロセッサに実行させるためのプログラム命令を有する1つ又は複数のコンピュータ可読ストレージ媒体を含む。

#### 【0084】

コンピュータ可読ストレージ媒体は、命令実行デバイスによる使用のために命令を保持及び格納することができる有形デバイスとすることができます。コンピュータ可読ストレージ媒体は、例えば、電子ストレージデバイス、磁気ストレージデバイス、光ストレージデバイス、電磁気ストレージデバイス、半導体ストレージデバイス、又は上記のものの任意の適切な組合せとすることができますがこれらに限定されない。コンピュータ可読ストレージ媒体のより具体的な例の非網羅的なリストは、ポータブル・コンピュータ・ディスクケット、ハードディスク、ランダムアクセスメモリ (RAM)、読み出し専用メモリ (ROM)、消去可能プログラム可能読み出し専用メモリ (EPROM 又はフラッシュメモリ)、静的ランダムアクセスメモリ (SRAM)、ポータブル・コンパクトディスク読み出し専用メモリ (CD-ROM)、デジタル多目的ディスク (DVD)、メモリスティック、フロッピーディスク、記録された命令を有するパンチカード若しくは溝内に隆起した構造等の機械式コード化デバイス、及び上記のものの任意の適切な組合せを含む。コンピュータ可読ストレージ媒体は、本明細書で用いられる場合、無線波若しくは他の自由に伝搬する電磁波、導波路若しくは他の伝送媒体を通じて伝搬する電磁波（例えば光ファイバケーブルを通る光パルス）、又は電線を通じて伝送される電気信号のような一時的な信号自体と解釈されるべきではない。30

#### 【0085】

本明細書で説明されるコンピュータ可読プログラム命令は、コンピュータ可読ストレージ媒体からそれぞれのコンピューティング／処理デバイスにダウンロードすることもでき、又は、例えばインターネット、ローカル・エリア・ネットワーク、広域ネットワーク及び／若しくは無線ネットワークを経由して、外部コンピュータ若しくは外部ストレージデバイスにダウンロードすることもできる。ネットワークは、銅伝送ケーブル、光伝送ファイバ、無線伝送、ルータ、ファイアウォール、スイッチ、ゲートウェイ・コンピュータ及40

び／又はエッジサーバを含むことができる。各コンピューティング／処理デバイス内のネットワーク・アダプタ・カード又はネットワーク・インターフェースは、ネットワークからコンピュータ可読プログラム命令を受け取り、そのコンピュータ可読プログラム命令をそれぞれのコンピューティング／処理デバイス内のコンピュータ可読ストレージ媒体におけるストレージのために転送する。

#### 【0086】

本開示の動作を実行するためのコンピュータ可読プログラム命令は、アセンブラー命令、命令セット・アーキテクチャ（ISA）命令、機械語命令、機械依存命令、マイクロコード、ファームウェア命令、状態設定データ、又は、Smalltalk、若しくはC++などのオブジェクト指向プログラミング言語及び「C」プログラミング言語若しくは類似のプログラミング言語のような従来の手続き型プログラミング言語を含む1つ若しくは複数のプログラミング言語の任意の組合せで記述されたソースコード若しくはオブジェクトコードのいずれかとすることができます。コンピュータ可読プログラム命令は、完全にユーザのコンピュータ上で実行される場合もあり、一部がユーザのコンピュータ上で独立型ソフトウェア・パッケージとして実行される場合もあり、一部がユーザのコンピュータ上で実行され、一部が遠隔コンピュータ上で実行される場合もあり、又は完全に遠隔コンピュータ若しくはサーバ上で実行される場合もある。後者のシナリオにおいては、遠隔コンピュータは、ローカル・エリア・ネットワーク（LAN）若しくは広域ネットワーク（WAN）を含むいずれかのタイプのネットワークを通じてユーザのコンピュータに接続される場合もあり、又は外部コンピュータへの接続が行われる場合もある（例えば、インターネット・サービス・プロバイダを用いたインターネットを通じて）。幾つかの実施形態において、例えばプログラム可能論理回路、フィールドプログラム可能ゲートアレイ（FPGA）、又はプログラム可能論理アレイ（PLA）を含む電子回路は、本開示の態様を実施するために、コンピュータ可読プログラム命令の状態情報をを利用して電子回路を個別化することにより、コンピュータ可読プログラム命令を実行することができる。10

#### 【0087】

本開示の態様は、本明細書において、本開示の実施形態による方法、装置（システム）、及びコンピュータプログラム製品のフローチャート図及び／又はブロック図を参照して説明される。フローチャート図及び／又はブロック図の各ブロック、並びにフローチャート図及び／又はブロック図のブロックの組合せは、コンピュータ可読プログラム命令によつて実装することができることが理解されるであろう。30

#### 【0088】

これらのコンピュータ可読プログラム命令を、汎用コンピュータ、専用コンピュータ、又は他のプログラム可能データ処理装置のプロセッサに与えてマシンを製造し、それにより、コンピュータ又は他のプログラム可能データ処理装置のプロセッサによって実行される命令が、フローチャート及び／又はブロック図の1つ又は複数のブロック内で指定された機能／動作を実装するための手段を作り出すようにすることができる。これらのコンピュータプログラム命令を、コンピュータ、プログラム可能データ処理装置、及び／又は他のデバイスを特定の方式で機能させるように指示することができるコンピュータ可読ストレージ媒体内に格納し、それにより、その中に格納された命令を有するコンピュータ可読媒体が、フローチャート及び／又はブロック図の1つ又は複数のブロックにおいて指定された機能／動作の態様を実装する命令を含む製品を含むようにすることもできる。40

#### 【0089】

コンピュータ可読プログラム命令を、コンピュータ、他のプログラム可能データ処理装置又は他のデバイス上にロードして、一連の動作ステップをコンピュータ、他のプログラム可能データ処理装置又は他のデバイス上で行わせてコンピュータ実装のプロセスを生成し、それにより、コンピュータ、他のプログラム可能装置又は他のデバイス上で実行される命令が、フローチャート及び／又はブロック図の1つ又は複数のブロックにおいて指定された機能／動作を実装するようにすることもできる。

#### 【0090】

50

図面内のフローチャート及びブロック図は、本開示の種々の実施形態による、システム、方法、及びコンピュータプログラム製品の可能な実装の、アーキテクチャ、機能及び動作を示す。この点に関して、フローチャート又はブロック図内の各ブロックは、指定された論理機能を実装するための1つ又は複数の実行可能命令を含む、モジュール、セグメント、又は命令の一部を表すことができる。幾つかの代替的な実装において、ブロック内に記された機能は、図中に記された順序とは異なる順序で行われることがある。例えば、連続して示された2つのブロックは、関与する機能に応じて、実際には実質的に同時に実行されることもあり、又はこれらのブロックはときとして逆順で実行されることもある。ブロック図及び／又はフローチャート図の各ブロック、及びブロック図及び／又はフローチャート図中のブロックの組合せは、指定された機能又は動作を実行する専用ハードウェア・ベースのシステムによって実装することもでき、又は専用ハードウェアとコンピュータ命令との組合せを実行することもできるこ<sup>10</sup>とも留意されたい。

#### 【0091】

本明細書で用いられる用語は、特定の実施形態を説明のみを目的としたものであり、本開示を限定することを意図したものではない。本明細書で使用される単数形「a」、「a n」及び「t h e」は、前後関係から明らかに別の意味を示さない限り、複数形態も含むことを意図する。さらに、本明細書内で使用する場合に、「備える、含む」及び／又は「備えている、含んでいる」という用語は、そこに述べた特徴、整数、ステップ、動作、要素及び／又はコンポーネントの存在を明示しているが、1つ又は複数の他の特徴、整数、ステップ、動作、要素、コンポーネント及び／又はそれらの群の存在又は付加を排除するものではないことが理解されるであろう。<sup>20</sup>

#### 【0092】

以下の特許請求の範囲における全ての「手段又はステップと機能との組み合わせ（ミンズ又はステップ・プラス・ファンクション）」要素の対応する構造、材料、動作、及び均等物は、その機能を、明確に特許請求された他の請求要素との組み合わせで実行するためのあらゆる構造、材料、又は動作を含むことが意図されている。本開示は、例証及び説明を目的として提示されたものであるが、網羅的であること又は開示された形態に限定することを意図したものではない。本開示の範囲及び思想から逸脱しない多くの修正及び変形が当業者には明らかであろう。実施形態は、本開示の原理及び実際の用途を最も良く説明するように、また企図される特定の用途に適するような種々の修正を伴う種々の実施形態について本開示を当業者が理解するのを可能にするように、選択しかつ説明したものである。<sup>30</sup>

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

$$i=g(s,v)v$$

式[1]

$$\frac{\partial s(t)}{\partial t} = f(s,v)$$

式[2]

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

これは、高次項が問題にならないこと、及び、本開示の更新方法論が、右図に示すように完全な乗算の場合と同じくらい良く機能することを実証する

【図17】

【図18】

【図19】

【図20】

【図21】

## 【図22】

---

フロントページの続き

(74)代理人 100112690

弁理士 太佐 種一

(72)発明者 ゴクメン、タイフン

アメリカ合衆国 10598 ニューヨーク州 ヨークタウン・ハイツ キッチャワン・ロード

1101

(72)発明者 ウラソフ、ユーリ

アメリカ合衆国 10598 ニューヨーク州 ヨークタウン・ハイツ キッチャワン・ロード

1101

(72)発明者 キム、セヨン

アメリカ合衆国 10598 ニューヨーク州 ヨークタウン・ハイツ キッチャワン・ロード

1101

審査官 三坂 敏夫

(56)参考文献 特開平07-319507(JP,A)

特開平05-282272(JP,A)

特開平07-121498(JP,A)

米国特許出願公開第2015/0170025(US,A1)

特開平05-181993(JP,A)

特表2013-546064(JP,A)

ALIBART,Fabien et al., Pattern classification by memristive crossbar circuits using ex situ and in situ training , nature COMMUNICATIONS , Macmillan Publishers Limited. , 2013年 6月25日 , pages:1-7 , [令和2年5月11日検索] , インターネット<URL : <https://www.nature.com/articles/ncomms3072.pdf> >

(58)調査した分野(Int.Cl. , DB名)

G 06 N 3 / 00 - 3 / 12

10 / 00 - 20 / 20

G 11 C 13 / 00