공개특허 10-2020-0067928

(19) 대한민국특허청(KR)

(12) 공개특허공보(A)

(11) 공개번호 10-2020-0067928

(43) 공개일자 2020년06월12일

(51) 국제특허분류(Int. Cl.)

*H04N 5/374* (2011.01) *H01L 27/146* (2006.01)

*H04N 5/359* (2011.01) *H04N 5/363* (2011.01)

*H04N 5/378* (2011.01)

(52) CPC특허분류

*H04N 5/374* (2019.01)

*H01L 27/14612* (2013.01)

(21) 출원번호 10-2020-7015940(분할)

(22) 출원일자(국제) 2012년10월10일

심사청구일자 없음

(62) 원출원 특허 10-2019-7023492

원출원일자(국제) 2012년10월10일

심사청구일자 2019년08월23일

(85) 번역문제출일자 2020년06월03일

(86) 국제출원번호 PCT/JP2012/006497

(87) 국제공개번호 WO 2013/057903

국제공개일자 2013년04월25일

(30) 우선권주장

JP-P-2011-232282 2011년10월21일 일본(JP)

(71) 출원인

소니 주식회사

일본국 도쿄도 미나토구 코난 1-7-1

(72) 발명자

나가이 토시아키

일본국 도쿄도 미나토구 코난 1-7-1 소니 주식회사

사내

코세키 켄

일본국 카나가와Ken 요코하마시 호도가야구 고오도

쵸 134 소니 엘에스아이 디자인 가부시키가이샤

내

(뒷면에 계속)

(74) 대리인

최달용

전체 청구항 수 : 총 14 항

(54) 발명의 명칭 반도체 장치, 고체 활상 장치, 및 카메라 시스템

### (57) 요 약

[과제]

인접 비어를 전송되는 신호 사이의 간섭을 저감할 수 있고, 나아가서는 비어 수의 증대를 억제할 수 있고, 센서를 탑재한 칩의 면적, 실장 공정을 저감할 수 있고, 결과적으로 비용 절감을 도모할 수 있는 반도체 장치, 고체

(뒷면에 계속)

대 표 도 - 도10

100A

촬상 장치, 및 카메라 시스템을 제공한다.

[해결 수단]

제1칩(110)과, 제2칩(120)을 가지며, 제1칩(110)과 제2칩(120)은 접합된 적층 구조를 가지며, 제1칩과 제2칩 사이의 배선은, 비어(114)를 통하여 접속되고, 제1칩(110)은, 각 센서(111)에서 발생한 아날로그 신호를 시간이산화한 신호가, 대응하는 비어를 통하여 제2칩에 전송되고, 제2칩(120)은, 비어를 통한 제1칩부터 전송된 신호를 제1칩에서 샘플링한 타이밍과는 다른 타이밍에서 샘플링하는 기능과, 양자화하여 디지털 신호를 얻는 기능을 포함한다.

(52) CPC특허분류

*H01L 27/14634* (2013.01)

*H01L 27/14636* (2013.01)

*H04N 5/359* (2013.01)

*H04N 5/363* (2013.01)

*H04N 5/378* (2013.01)

(72) 발명자

**우에노 요스케**

일본국 도쿄도 미나토구 코난 1-7-1 소니 주식회사

내

**스즈키 아츠시**

일본국 도쿄도 미나토구 코난 1-7-1 소니 주식회사

내

## 명세서

### 청구범위

#### 청구항 1

제1의 기판과,

상기 제1의 기판에 접합된 제2의 기판을 가지며,

상기 제1의 기판은,

행과 열에 배열되고 그 하나가 입사광을 받아서 아날로그 신호를 출력하는 복수의 화소를 포함하는 화소 어레이와,

그 하나가 상기 아날로그 신호를 전달하도록 구성된 복수의 신호선과,

상기 화소 어레이의 제1의 측면에 따라 배치된 제1의 복수의 비아와 상기 제1의 측면에 수직한 상기 화소 어레이의 제2의 측면에 따라 배치된 제2의 복수의 비아를 구비하고,

상기 제2의 기판은,

복수의 비교기를 포함하는 칼럼 판독 회로와,

참조 신호를 출력하는 참조 신호 생성기와,

상기 제2의 복수의 비아 중 적어도 하나에 구동 디지털 신호를 출력하도록 구성된 행 선택 회로를 포함하고,

상기 복수의 비교기 중 하나의 비교기는 상기 아날로그 신호와 상기 참조 신호를 비교하여 디지털 신호를 출력하도록 구성되는 것을 특징으로 하는 수광 장치.

#### 청구항 2

제1항에 있어서,

상기 행 선택 회로는 상기 제2의 기판에 있는 것을 특징으로 하는 수광 장치.

#### 청구항 3

제1항에 있어서,

상기 칼럼 판독 회로는 카운터를 포함하는 것을 특징으로 하는 수광 장치.

#### 청구항 4

제1항에 있어서,

상기 제1의 측면에 수직한 상기 화소 어레이의 제3의 측면에 따라 배치된 제3의 복수의 비아를 또한 구비하고, 상기 제3의 복수의 비아의 적어도 하나는 구동 디지털 신호를 전달하는 것을 특징으로 하는 수광 장치.

#### 청구항 5

제1항에 있어서,

상기 제1의 복수의 비아 각각 및 상기 제2의 복수의 비아 각각은 집중하여 배치되고, 상기 제1의 복수의 비아와 상기 제2의 복수의 비아는 분리하여 배치되어 있는 것을 특징으로 하는 수광 장치.

#### 청구항 6

제1항에 있어서,

상기 제2의 복수의 비아는 패드와 상기 화소 어레이의 사이에 마련된 것을 특징으로 하는 수광 장치.

### 청구항 7

제1항에 있어서,

상기 제1의 복수의 비아는 패드와 상기 화소 어레이의 사이에 마련된 것을 특징으로 하는 수광 장치.

### 청구항 8

제1의 기판과,

상기 제1의 기판에 접합된 제2의 기판을 가지며,

상기 제1의 기판은, 행과 열에 배열되어 그 하나가 입사광을 받아서 아날로그 신호를 출력하는 복수의 화소를 포함하는 화소 어레이와,

그 하나가 상기 아날로그 신호를 전달하도록 구성된 복수의 신호선과,

상기 화소 어레이의 제1의 측면에 따라 배치되고, 상기 아날로그 신호를 상기 제2의 기판에 전달하는 제1의 복수의 비아와,

상기 제1의 측면에 수직한 상기 화소 어레이의 제2의 측면에 따라 배치되고, 상기 화소 어레이의 행을 선택하는 디지털 신호를 전달하는 제2의 복수의 비아를 구비하고,

상기 제2의 기판은,

상기 디지털 신호를 출력하도록 구성된 적어도 일부의 행 선택 회로를 포함하는 것을 특징으로 하는 수광 장치.

### 청구항 9

제8항에 있어서,

상기 제2의 기판은 복수의 비교기를 포함하는 칼럼 판독 회로를 갖는 것을 특징으로 하는 수광 장치.

### 청구항 10

제9항에 있어서,

상기 칼럼 판독 회로는 카운터를 포함하는 것을 특징으로 하는 수광 장치.

### 청구항 11

제9항에 있어서,

상기 복수의 비교기 중 하나의 비교기는 상기 아날로그 신호를 받는 것을 특징으로 하는 수광 장치.

### 청구항 12

제8항에 있어서,

상기 제1의 복수의 비아 각각 및 상기 제2의 복수의 비아 각각은 집중하여 배치되고, 상기 제1의 복수의 비아와 상기 제2의 복수의 비아는 분리하여 배치되어 있는 것을 특징으로 하는 수광 장치.

### 청구항 13

제8항에 있어서,

상기 제2의 복수의 비아는 패드와 상기 화소 어레이의 사이에 마련된 것을 특징으로 하는 수광 장치.

### 청구항 14

제8항에 있어서,

상기 제1의 복수의 비아는 패드와 상기 화소 어레이의 사이에 마련된 것을 특징으로 하는 수광 장치.

## 발명의 설명

## 기술 분야

- [0001] 본 기술은, 복수의 센서가 어레이형상으로 배치된 구조를 갖는 반도체 장치, 고체 활상 장치, 및 카메라 시스템에 관한 것이다.

- [0002] 배경 기술

CMOS 이미지 센서 등과 같이, 복수의 센서가 어레이형상으로 배치된 구조를 갖는 반도체 장치에서는, 신호 처리의 고도화와 소형화에의 요구가 높아져 오고 있다.

- [0003] 이것을 실현하기 위해, 예를 들면 특히 문헌 1에서는 칩을 적층 구조로 함으로써, 지금까지와 동등한 칩 사이즈로 보다 큰 신호 처리 회로를 집적하는 수법이 제안되어 있다.

- [0004] 이와 같은 반도체 장치는, 아날로그 신호를 발생하는 센서 어레이를 탑재한 칩(이하, 아날로그 칩으로 기재)과, 신호 처리용의 로직 회로를 탑재한 칩(이하, 디지털 칩으로 기재)과의 적층 구조를 갖는다.

- [0005] 그리고, 반도체 장치는, 아날로그 칩에 형성된 TC(S)V(Through Contact(Silicon) VIA)로 접속한 구조로, 이들의 칩을 상하로 적층함에 의해 소형화를 실현하고 있다.

- [0006] 이와 같은 수법으로 소형화를 실현하는 경우, 센서 어레이로부터 출력되는 데이터를 통과시키기 위한 신호 경로에 관련되는 회로 블록을 어떻게 상하의 칩에 배분하는지가 과제로 된다.

- [0007] 상기한 바와 같은 시스템에서, 센서 어레이로부터 신호를 취출하기 위한 배선은, 예를 들면 이미지 센서에서는, 종 또는 횡방향의 화소수와 같은 오더로 되기 때문에, 수천개 이상이 된다.

- [0008] 이 때문에, TCV를 이들의 경로에 삽입한 경우하는, 필연적으로 TCV를 밀집시켜서 배치할 필요가 있다. 따라서 어느 TCV에 인접한 TCV의 신호가 큰 진폭으로 천이한 경우, 주목하고 있는 TCV의 신호가 간섭을 받아, 오차가 생긴다.

- [0009] 이 간섭에 대해, 종래는 TCV를 통하여 전송하는 신호를 전압 방향으로 양자화된 신호(2치의 신호선 하나 내지 복수를 이용한다)로 제한함으로써, 대책을 행하고 왔다.

- [0010] 이하에 이들의 대책에 관해 상세를 기술한다.

- [0011] 이하에서는, 첫번째로 TCV를 통과하는 전송 신호를 시간이산(時間離散)하면서 양자화(量子化)된 신호, 즉 디지털 신호로 하는 대책에 관해 기술하고, 두번째로 TCV를 통과하는 전송 신호를 시간연속(時間連續)이지만 양자화된 신호로 하는 경우에 관해 기술한다.

- [0012] 우선, TCV 통하여 전송 신호를 시간이산하면서 양자화된 신호, 즉 디지털 신호로 하는 대책에 관해 기술한다.

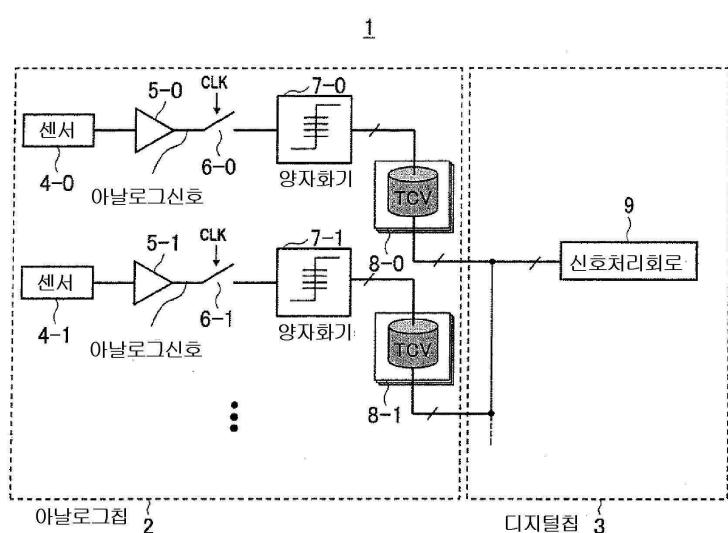

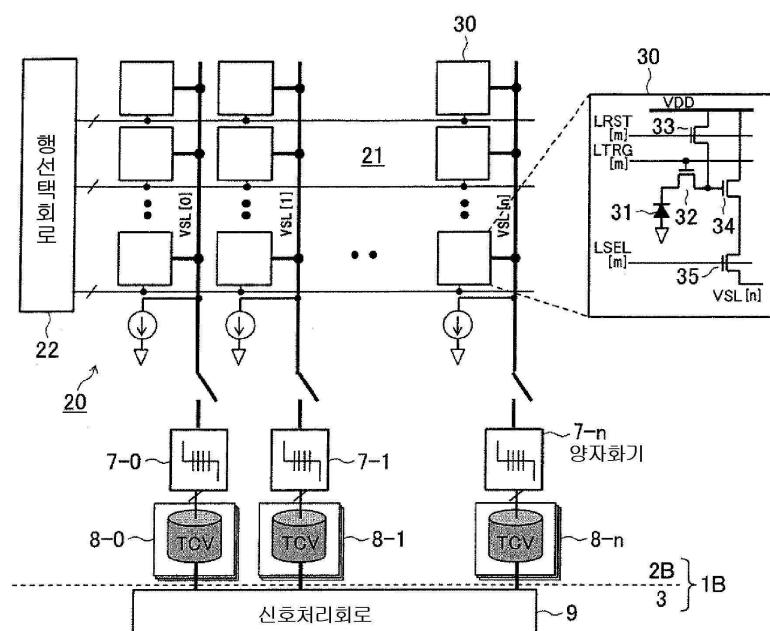

- [0013] 도 1은, 적층 칩을 사용한 반도체 장치에서, TCV를 통과하는 전송 신호를 시간이산하면서 양자화된 신호로 하는 제1의 구성례를 도시하는 도면이다.

- [0014] 반도체 장치(1)는, 아날로그 칩(2)과 디지털 칩(3)의 적층 구조를 갖는다.

- [0015] 이 반도체 장치(1)는, 적층 구조의 칩 중 아날로그 프로세스를 이용하여 제조된 아날로그 칩(2)상에 어레이형상으로 배치된 복수의 센서(4)(-0, -1, ...)를 갖는다.

- [0016] 이 센서(4) 각각의 출력에 앰프(5)(-0, -1, ...)를 통하여, 신호를 시간이산화하는 샘플링 스위치(6)(-0, -1, ...)가 접속되어 있다.

- [0017] 여기서 원래의 센서(4)로부터 나오는 신호의 전력이 충분히 큰 경우에 관해서는, 앰프를 경유하지 않고 직접 센서의 출력을 샘플링 스위치에 접속하여도 좋다.

- [0018] 샘플링 스위치(6)에서 시간이산화된 신호는, 양자화기(7)(-0, -1, ...)를 이용하여 전압 방향으로 양자화된다.

- [0019] 양자화기(7)는 복수의 비교기로 구성되고, 각각의 비교기는 어느 신호 레벨과 입력 신호의 레벨을 비교함에 의해 신호의 양자화를 행한다.

- [0020] 여기서 양자화기(7)는 한번에 양자화가 완결되는 것은 아니고, 복수의 스테이지로 구성되는 회로라도 좋다.

- [0021] 이와 같은 프로세스로 디지털화된 신호는 TCV(8)(-0, -1, ...)를 통하여 디지털 칩(3)에 전송되고, 디지털 신호

처리 회로(9)에서 처리된다.

[0022] 이 경우, TCV(8)를 통과하는 신호는 전원 레벨이나 그라운드(GND) 레벨로 2치화되어 있고, 전원 전압의 반분 정도의 크기까지 신호가 변화하여 버리지 않는 한은, 오차는 발생하지 않는다. 또한, TCV(8)의 기생용량에 의해 신호의 지연이 발생하였다고 하여도, 신호 처리 회로(9)의 세트 업 마진 내라면 문제는 발생하지 않는다.

[0023] 다음에, TCV를 통하여 전송하는 신호를 디지털 신호로 하는 경우의 다른 구성례에 관해 설명한다.

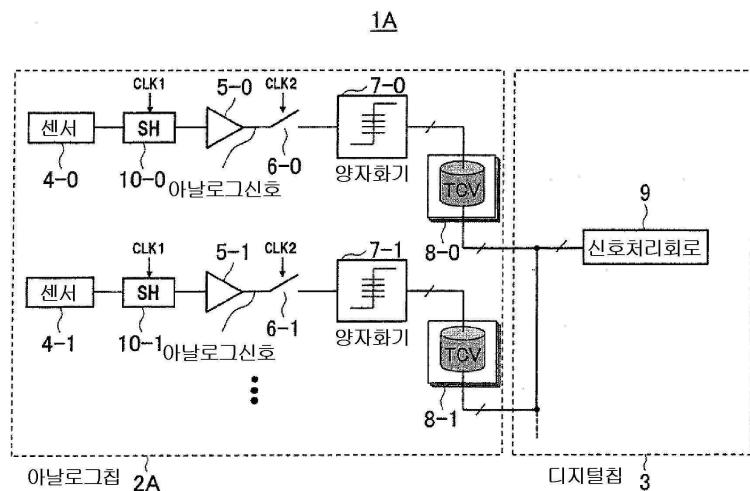

[0024] 도 2는, 적층 칩을 사용한 반도체 장치에서, TCV를 통과하는 전송 신호를 시간이산하면서 양자화된 신호로 하는 제2의 구성례를 도시하는 도면이다.

[0025] 이 경우의 반도체 장치(1A)에서는, 센서(4)의 출력 신호는 직접 샘플링 스위치(6)에서 시간이산화되는 것은 아니고, 센서(4)의 최근(直近)에 있는 SH(샘플 홀드) 회로(10)(-0, -1, ...)에서 시간이산화된다.

[0026] 이 샘플 홀드 회로(10)는 가장 간단하게는 스위치와 용량만으로 실현된다.

[0027] 다음에, TCV를 통하여 전송하는 신호를 디지털 신호로 하는 도 2의 구성례를 이미지 센서에 적용한 경우에 관해 설명한다.

[0028] 도 3은, 적층 칩을 사용한 반도체 장치에서, TCV를 통과하는 전송 신호를 시간이산하면서 양자화된 신호로 하는 제3의 구성례를 도시하는 도면으로서, 도 2의 구성례를 CMOS 이미지 센서에 적용한 한 예를 도시하는 도면이다.

[0029] 또한, 이해를 용이하게 하기 위해, 도 3에서는 도 1 및 도 2와 동일 구성 부분은 동일 부호로 써 나타내고 있다.

[0030] CMOS 이미지 센서는 화소마다 FD 앰프를 갖고 있고, 그 출력은, 화소 어레이의 중에 있는 1행을 선택하고, 그들을 동시에 열방향으로 판독하는 열병렬 출력형이 주류이다.

[0031] 이것은, 화소 내에 배치된 FD 앰프로는 충분한 구동 능력을 얻기가 어렵고, 따라서 데이터 레이트를 내릴 것이 필요하여, 병렬 처리가 유리하다고 되어 있기 때문이다.

[0032] 이와 같은 CMOS 이미지 센서(20)는, 센서 어레이로서의 화소 어레이부(21), 및 화소를 구동하기 위한 행 선택 회로(V스캐너)(22)를 포함하여 구성된다.

[0033] 화소 어레이부(21)는, 화소 회로(30)가 M행×N열의 매트릭스형상으로 배치되어 있다.

[0034] 행 선택 회로(22)는, 화소 어레이부(21) 중의 임의의 행에 배치된 화소의 동작을 제어한다. 행 선택 회로(22)는, 제어 선(LSEL, LRST, LTRG)을 통하여 화소를 제어한다.

[0035] 도 3에서는, 한 예로서 화소 회로(30)가 4개의 트랜지스터로 구성되어 있는 경우를 나타내고 있다.

[0036] 이 화소 회로(30)는, 예를 들면 포토 다이오드(PD)로 이루어지는 광전 변환 소자(이하, 단지 PD라고 할 때도 있다)(31)를 갖는다. 화소 회로(30)는, 이 1개의 광전 변환 소자(31)에 대해, 전송 트랜지스터(32), 리셋 트랜지스터(33), 증폭 트랜지스터(34), 및 선택 트랜지스터(35)의 4개의 트랜지스터를 능동 소자로서 갖는다.

[0037] CMOS 이미지 센서(20)에서는, 센서로서의 광전 변환 소자(포토 다이오드)(31)에 대해 플로팅 디퓨전(용량)(FD)과 전송 트랜지스터(전송 스위치)(32)로 도 2의 블록도에서의 샘플 홀드 회로의 기능이 실현되고 있다.

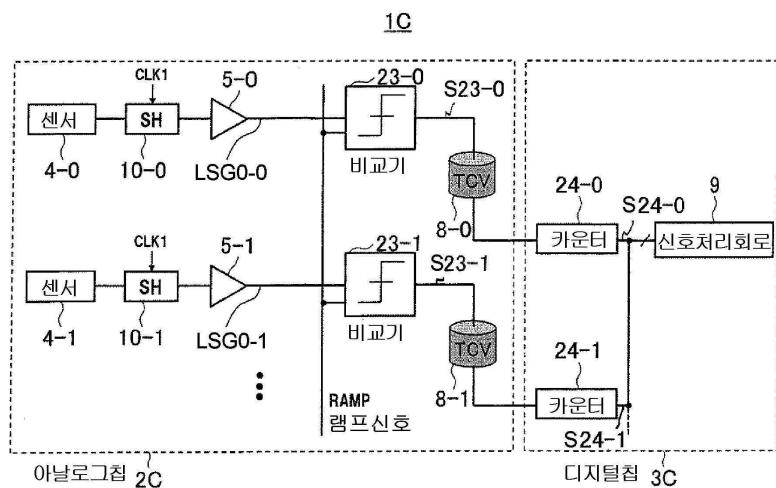

[0038] 도 4는, 적층 칩을 사용한 반도체 장치에서, TCV를 통과하는 전송 신호를 시간연속이지만 양자화된 신호로 하는 제1의 구성례를 도시하는 도면이다.

[0039] 도 4의 반도체 장치(1C)는, 도 2의 반도체 장치(1A)와 마찬가지로 SH 회로(10)에서 이산화된 신호와, 부도시의 램프 신호 발생기에서 생성한 램프파를 비교기(23)(-0, -1, ...)에서 비교함으로써, 센서(4)로부터 출력되는 아날로그 신호를 시간축의 신호로 변환한다.

[0040] TCV(8)를 통하여 이와 같이 하여 변환한 양자화된 센서 신호가 디지털 칩(2C)에 전송되고, 카운터(TDC)(24)에서 시간축의 정보를 양자화함에 의해, 디지털 신호를 얻는다.

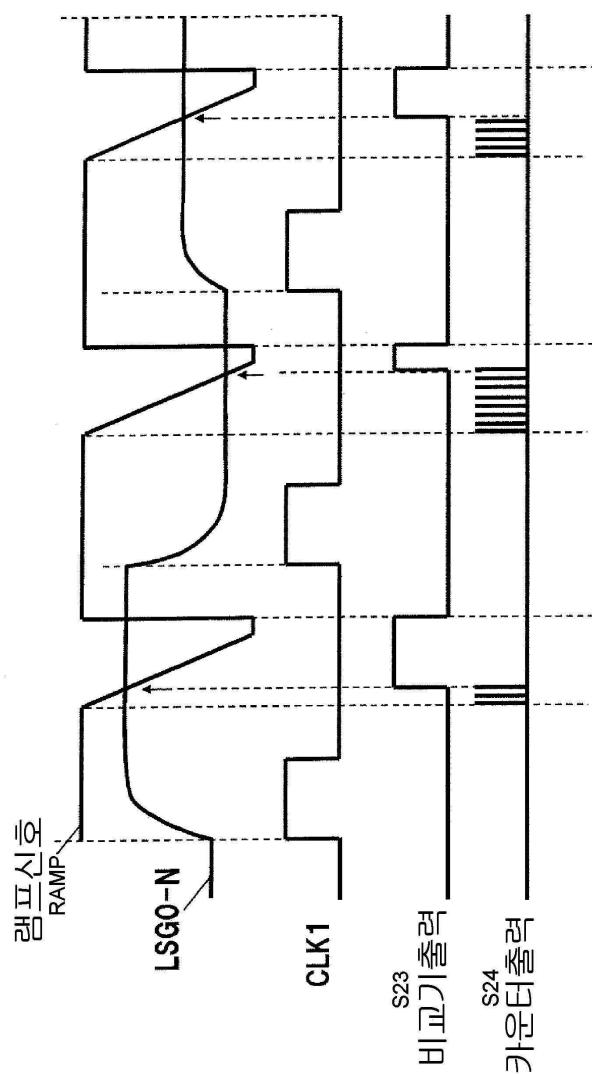

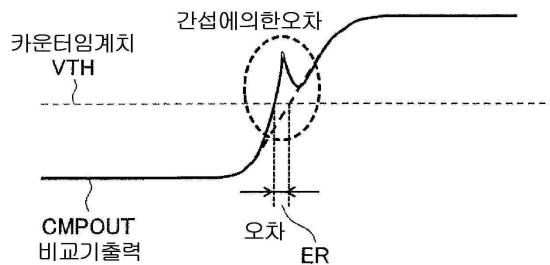

[0041] 이상의 동작을 시간축의 과정으로 도시하면, 도 5와 같이 된다.

[0042] 아날로그 신호와 램프파(RAMP)의 비교 결과가 비교기(23)로부터 신호(S23)로서 출력됨에 의해, 카운터(24)의 카운트 동작이 멈추고, 신호가 확정된다. 여기서, 램프파(RAMP)의 시작 타이밍과 카운터(24)의 카운트 동작의 시작 시간은 동기하고 있기 때문에, 이 동작에 의해, 전압 정보가 시간 정보로 변환된다.

[0043] 이와 같은 전송 방법을 이용한 경우, TCV를 경유하여 전송되는 신호는 디지털 신호를 전송한 경우와 마찬가지로

TCV(8)를 통과하는 신호는 전원 레벨/GND 레벨로 양자화되어 있다.

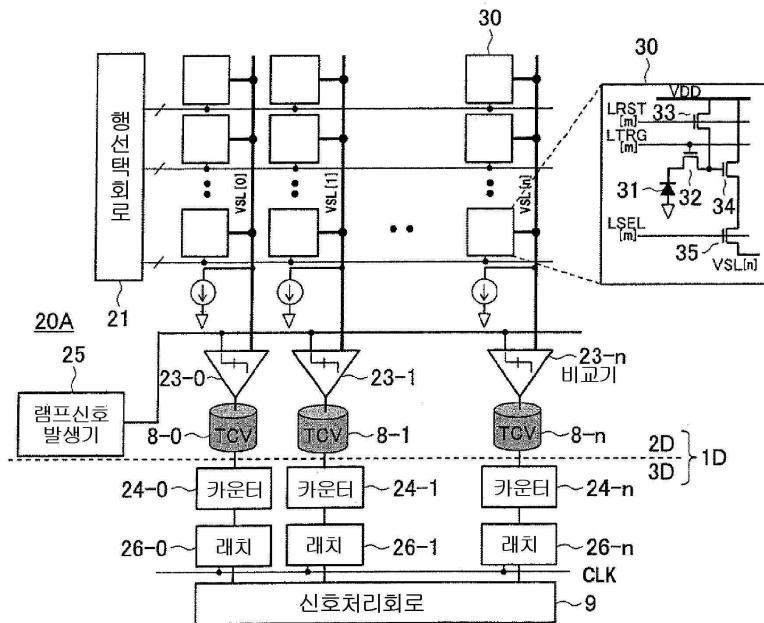

[0044] 도 6은, 적층 칩을 사용한 반도체 장치에서, 도 4의 구성을 CMOS 이미지 센서에 적용한 한 예를 도시하는 도면이다.

[0045] 또한, 도 6에서는, 이해를 용이하게 하기 위해, 도 3 및 도 4와 동일 구성 부분은 동일 부호로써 나타내고 있다.

[0046] 도 4의 경우와 동등하게, 램프 신호 발생기(25)에서 생성한 램프파를 비교기(23)(-0, -1, ...)에서 비교함으로써, 화소(30)로부터 출력되는 아날로그 신호를 시간축의 신호로 변환한다.

[0047] TCV(8)를 통하여 이와 같이 하여 변환한 양자화된 센서 신호가 디지털 칩(3D)에 전송되고, 카운터(TDC)(24)에서 시간축의 정보를 양자화하고, 이에 의해 얻어진 디지털 신호를 래치(메모리)(26)에 유지한다.

[0048] 래치(26)에 유지한 디지털 신호는 신호 처리 회로(9)에 의해 전송선을 수평 전송된다.

[0049] 또한, 각 칼럼에 배치된 비교기(23), 카운터(24), 및 래치(26)에 의해 싱글 슬로프형 AD 변환기(ADC)가 형성된다.

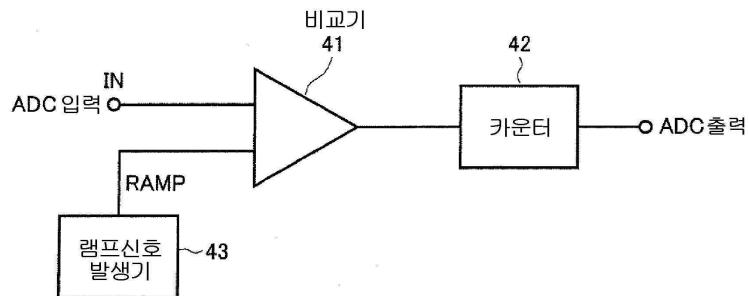

[0050] 도 7은, 일반적인 싱글 슬로프형 AD 변환기의 구성을 도시하는 도면이다.

[0051] 도 7의 싱글 슬로프형 AD 변환기(40)는, 비교기(41), 카운터(42), 및 램프 신호 발생기(43)를 포함하여 구성되어 있다.

[0052] 상술한 바와 같이, 싱글 슬로프형의 AD 변환기(40)에서는, 비교기(41)는 DAC 등의 램프 신호 발생기(43)로부터의 램프파(슬로프 신호)와 AD 변환기 입력 신호(IN)와 비교를 하여, 후단의 카운터(42)를 제어함에 의해 AD 변환을 행한다.

[0053] AD 변환기(40)의 중요한 성능 지표로서 노이즈 특성이 있고, 비교기(41)의 노이즈 특성이 종종 AD 변환기(40)의 노이즈 특성을 지배한다. 노이즈에는 광대역의 노이즈인 열(熱) 노이즈나, 저주파 노이즈인 플리커 노이즈, RTS(Random Telegraph Signal) 노이즈 등이 있는데, 이들이 각각 노이즈 특성을 열화시킨다.

[0054] 일반적으로, 이들의 노이즈의 저감 수법으로서 트랜지스터 사이즈를 증대시키는 것이나, 비교기의 초단(初段) 출력에 미러 용량을 삽입하는 방법(특히 문헌 2 참조)이 알려져 있다.

## 선행기술문현

### 특허문현

[0055] (특허문현 0001) 일본국 특개2011-159958호 공보

(특허문현 0002) 일본국 특개2010-93641호 공보

### 비특허문현

[0056] (비)특허문현 0001) "Impact of STA Effect on Flicker Noise in 0.13um RF nMOSFETs" IEEE TRANSACTIONS ON ELECTRON DEVICES, VOL. 54, NO. 12, DECEMBER 2007, pp. 3383-3392.

## 발명의 내용

### 해결하려는 과제

[0057] 그러나, 상기한 도 1 내지 도 3과 같이 TCV를 통과하는 신호를 디지털 신호로 하는 경우, 다음과 같은 문제가 있다.

[0058] 첫번째로 양자화기의 분해 성능을 올릴려고 하면, TCV의 갯수가 많아져 버리는 것이다.

[0059] 선술한 바와 같이, 이미지 센서에서 동시에 관찰되는 센서의 수(화소)는 수천개 정도가 되는 것이 일반적이다. 이 대책을 실시한 경우에는, 이 수천개에 분해능(bit수)분을 곱한 수의 TCV가 필요하기에 결과로서 쓸데없는 면

적/비용의 증대를 초래한다.

[0060] 두번째로 TCV를 통과하는 신호의 진폭이 커지는 것이다. 이에 의해 통상의 비아(VIA)에 비하여 큰 기생용량을 갖는 TCV를 대(大)신호 진폭으로 충전하는 것으로 되어, 전력의 증대와 전원 노이즈의 증가를 초래한다.

[0061] 세번째로 양자화기 자체가 큰 면적을 필요로 하는 것이다. 아날로그 칩은 센서를 실현하기 위해, 일반적으로 디지털 칩과 비하여 특수한 공정을 갖는 프로세스로 제조되어 있고, 면적당의 비용이 높다. 따라서 아날로그 칩의 면적이 커져 버리면 비용에의 영향이 크다.

[0062] 또한, 도 4 및 도 6과 같이 TCV를 통과하는 신호를 시간연속이면서 양자화된 신호로 하는 경우, 다음과 같은 문제가 일어난다.

[0063] 첫번째로 인접 TCV로부터의 신호의 간섭이다. TCV를 통과하는 신호가 전원 레벨/GND 레벨의 2치이기 때문에, 인접한 신호에 대해 간섭이 발생하기 쉽다.

[0064] 이 시스템에서는 비교기의 출력이 충분히 정정(靜定)하고, 전원 레벨/GND 레벨의 어느 하나에 가까워져 있는 경우에 관해서는, 인접 TCV로부터의 간섭에 강하지만, 비교기의 출력이 천이중에 관해서는 결코 간섭에 강하지 않다.

[0065] 이것은 비교기의 출력이 유한한 상승시간을 갖고 있고, 이 신호에 노이즈가 중첩하면, 어느 레벨을 넘는 시간에 오차가 발생하기 때문이다.

[0066] 도 8은, 이 인접 TCV로부터의 간섭에 의한 오차의 영향을 도시하는 도면이다.

[0067] 인접 TCV로부터의 간섭이 없으면, 비교기의 출력(CMPOUT)은 파선과 같이 되지만, 간섭이 있는 경우에는 실선과 같이 되고, 양자가 카운터의 임계치(VTH)를 넘는 시간에 오차(ER)가 발생하고 있다.

[0068] 이 시스템에서는 비교기의 신호가 상승하는 타이밍은 예를 들어 SH 회로를 구동하는 CLK1의 타이밍을 동일하다고 한 경우에도, 센서 출력의 레벨에 응하여 변하게 되기 때문에, 동일한 타이밍에서 관리하기가 어렵다.

[0069] 또한 상기에 기술한 이유로부터, 오차가 발생하는 것이 인접하는 비교기 출력이 거의 동시에 천이하는 경우이기 때문에, 원래 타이밍을 동기화하여도 원리적이게 간섭을 회피할 수가 없다.

[0070] TCV 사이에 실드를 행함으로써 이 문제는 완화 가능하지만, TCV 사이의 거리가 증대하게 되어 결과로서 면적이 크게 된다.

[0071] 두번째로, 비교기의 출력 신호가 커짐에 의한 전력과 전원 노이즈의 증가이다. 이 전력과 전원 노이즈의 증가는 디지털 신호를 전송한 경우와 동일한 이유에 의한다.

[0072] 세번째로, 이쪽도 디지털 신호를 전송한 경우와 마찬가지에서 비교기 자체의 면적으로 의한 비용 증가를 들 수 있다. 디지털 신호로 전송하는 경우에 비하여, 비교가 1회면 좋고, 회로가 간소하기 때문에, 그 만큼 비용의 증분은 고분해의 양자화기와 비하면 작은 것이지만, 비교기의 수는 TCV와 같이 수천개 있기 때문에 결코 무시할 수 있는 것이 아니다.

[0073] 이상과 같이, 적층 구조를 갖는 센서로부터 출력되는 신호를 처리한 반도체 장치에서, 종래 인접 TCV 사이의 신호의 간섭을 억제하는 방책으로서 전압 레벨에서의 양자화가 채용되어 왔다.

[0074] 그리고, 상기에서 기술한 어느 실장 방법을 취한 경우에서도, 공정수가 많은 아날로그 칩의 면적을 증대시켜서, 비용의 증분을 초래하는 것과, TCV를 통하여 전송하는 신호의 진폭이 커지기 때문에, 전력과 전원 노이즈의 증대를 수반하는 것이 문제이다.

[0075] 또한, 싱글 슬로프형 AD 변환기를 사용한 반도체 장치를 생각한 경우, 노이즈의 저감 수법으로서 트랜지스터 사이즈를 증대시키는 방법에서는 부작용으로서 기생용량도 증대하기 때문에, 회로 면적이 커지거나 동작 속도가 저하된다. 이 때문에, 하나 하나의 비교기의 면적이 증대하거나, 동작 속도가 제한된다는 문제가 발생한다. 더하여, 이들의 제약 때문에 노이즈의 저감 효과도 일정 이상의 효과는 얻기 힘들다.

[0076] 비교기의 초단 출력에 미려 용량을 삽입하는 방법에서도, 기본적으로는 노이즈의 대역 즉 동작 대역을 저감하는 수법인 이상, 동작 속도가 저하되기 때문에 일정 이상의 노이즈 저감 효과는 얻기 힘들다.

[0077] 또한 이 방법의 경우, 그 대역 제한에 의한 노이즈 저감이라는 원리상, 플리커 노이즈나 RTS 노이즈 등의 저주파 노이즈에 관해서는 효과가 작다는 과제도 있다.

[0078] 이들의 사정 때문에, 비교기에서의 더한층의 노이즈 저감, 특히 저주파 노이즈의 저감이 항상 요망되고 있다.

[0079] 본 기술은, 인접 비어를 전송되는 신호 사이의 간섭을 저감할 수 있고, 나아가서는 비어 수의 증대를 억제할 수 있고, 센서를 탑재한 칩의 면적, 실장 공정을 저감할 수 있고, 결과적으로 비용 절감을 도모할 수 있는 반도체 장치, 고체 활상 장치, 및 카메라 시스템을 제공하는 것에 있다.

### 과제의 해결 수단

[0080] 본 기술의 제1의 관점의 반도체 장치는, 어레이형상으로 배치된 복수의 센서를 갖는 제1칩과, 제2칩을 가지며, 상기 제1칩과 상기 제2칩은 접합된 적층 구조를 가지며, 상기 제1칩과 상기 제2칩 사이의 배선은, 비어를 통하여 접속되고, 상기 제1칩은, 각 센서에서 발생한 아날로그 신호를 시간이산화한 신호가, 대응하는 상기 비어를 통하여 제2칩에 전송되고, 상기 제2칩은, 상기 비어를 통한 상기 제1칩부터 전송된 신호를 상기 제1칩에서 샘플링한 타이밍과는 다른 타이밍에서 샘플링하는 기능과, 양자화하여 디지털 신호를 얻는 기능을 포함한다.

[0081] 본 기술의 제2의 관점의 고체 활상 장치는, 광전 변환을 행하는 복수의 화소가 행렬형상으로 배열된 화소 어레이부와, 상기 화소 어레이부로부터 복수의 화소 단위로 시간이산화한 화소 신호의 판독을 행하는 화소 신호 판독부를 가지며, 상기 화소 신호 판독부는, 화소의 열 배열에 대응하여 배치되고, 판독 신호 전위와 램프 신호를 비교 판정하고, 그 판정 신호를 출력하는 복수의 비교기와, 상기 비교기의 출력에 의해 동작이 제어되고, 대응하는 상기 비교기의 비교 시간을 카운트함에 의해 양자화하는 복수의 카운터와, 제1칩과, 제2칩을 가지며, 상기 제1칩과 상기 제2칩은 접합된 적층 구조를 가지며, 상기 제1칩은, 상기 화소 어레이부 및 시간이산화한 아날로그 화소 신호를 전송하는 신호선이 배치되고, 상기 제2칩은, 상기 화소 신호 판독부가 배치되고, 상기 제1칩과 상기 제2칩 사이의 배선은, 비어를 통하여 접속되어 있다.

[0082] 본 기술의 제3의 관점의 카메라 시스템은, 고체 활상 장치와, 상기 고체 활상 장치에 편사체상을 결상하는 광학계를 가지며, 상기 고체 활상 장치는, 광전 변환을 행하는 복수의 화소가 행렬형상으로 배열된 화소 어레이부와, 상기 화소 어레이부로부터 복수의 화소 단위로 시간이산화한 화소 신호의 판독을 행하는 화소 신호 판독부를 가지며, 상기 화소 신호 판독부는, 화소의 열 배열에 대응하여 배치되고, 판독 신호 전위와 램프 신호를 비교 판정하고, 그 판정 신호를 출력하는 복수의 비교기와, 상기 비교기의 출력에 의해 동작이 제어되고, 대응하는 상기 비교기의 비교 시간을 카운트함에 의해 양자화하는 복수의 카운터와, 제1칩과, 제2칩을 가지며, 상기 제1칩과 상기 제2칩은 접합된 적층 구조를 가지며, 상기 제1칩은, 상기 화소 어레이부 및 시간이산화한 아날로그 화소 신호를 전송하는 신호선이 배치되고, 상기 제2칩은, 상기 화소 신호 판독부가 배치되고, 상기 제1칩과 상기 제2칩 사이의 배선은, 상기 비어를 통하여 접속되어 있다.

### 발명의 효과

[0083] 본 기술에 의해, 전송하는 신호에 오차를 발생시키는 일 없이, 기존의 적층 구조와 비하여 TCV의 갯수를 저감하는 것이 가능해진다. 또한, 아날로그 칩상에 양자화기(비교기) 등의 회로가 불필요하게 된다. 이 때문에, 아날로그 칩의 면적을 센서만으로 정하여지는 면적까지 작게 할 수 있다.

[0084] 예를 들면, 이미지 센서에서 센서(화소)의 면적은, 시스템의 광학 사이즈로부터 결정되어 있기 때문에, 일반적으로 아날로그 칩을 최소화할 수 있는 거의 한계까지 작게 할 수 있는 것을 의미한다.

[0085] 아날로그 칩은 전술한 바와 같이, 로직 칩(디지털 칩)과 비교하여 공정수가 많기 때문에, 예를 들어 칩의 면적이 동일하였다고 하여도 비용이 높아진다.

[0086] 또한, 본 기술에 의해 아날로그 칩상에 배치한 회로를 센서에 관한 부분으로 한정할 수 있기 때문에, 배선이나 트랜지스터 제조에 관한 공정을 줄이는 것이 가능해진다. 일반적으로 비교기 등의 회로를 제작하기 위한 트랜지스터와, 센서를 구성하기 위한 트랜지스터는 공통이 아닌 것을 포함하는 공정에서 제조되고 있다. 따라서 비교기 등의 회로가 없어짐으로써, 이들의 공정을 절감할 수 있다.

[0087] 마찬가지로, 아날로그 칩상에 복잡한 배선을 배치할 필요가 없어지기 때문에, 배선의 총수를 절감할 수 있다.

[0088] 상기 2개의 이유로부터 본 기술에 의해, 센서로부터 출력되는 신호를 열화시키는 일 없이, 반도체 장치의 비용을 대폭적으로 저감하는 것이 가능해진다.

[0089] 또한, 상술한 바와 같이, 본 실시 형태에 관한 비교기(500C 내지 500H)는, 캐스코드 트랜지스터를 이용하여 노이즈를 저감하는 구성을 갖는다.

- [0090] 이들의 구성은, 슬로프 신호, 예를 들면 램프 신호와 비교를 행하는 경우에, 출력 노드와 입력 노드의 커플링에 의해, 실효적인 입력 신호 진폭이 감쇠하여 버리는 것을 회피함에 의해, 비교기의 입력 환산 노이즈의 저감을 실현할 수 있다.

- [0091] 이와 같이, 오토 제로 기능 부착의 비교기 및 그것을 이용한 싱글 슬로프 AD 변환기나 고체 활상 장치에서 잡음, 특히 플리커 노이즈나 RTS 노이즈와 같은 저주파 잡음을 저감하는 것이 가능해진다.

- [0092] 또한, 이와 같은 특징을 갖는 비교기는, 도 9의 적층 구조의 디지털 칩인 제2칩에 적용한 경우에 노이즈 저감의 효과는 크다.

- [0093] 단, 아날로그 칩인 제1칩측에 비교기를 탑재한 경우, 적층 구조가 아닌 회로 구성의 경우에도, 노이즈 저감의 효과는 크다.

- [0094] 그리고, 상술한 바와 같이, 오토 제로 기능 부착의 비교기를 이용한 싱글 슬로프 AD 변환기나 고체 활상 장치에서 잡음, 특히 플리커 노이즈나 RTS 노이즈와 같은 저주파 잡음을 저감하는 것이 가능해진다.

- [0095] 또한, 본 실시 형태에서는, 반도체 장치의 한 예로서 CMOS 이미지 센서의 구성에 관해 설명하였지만, 상기 구성은 예를 들면 이면 조사형 CMOS 이미지 센서에 적용할 수 있고, 상기 각 효과를 발현하는 것이 가능하다. 단, 표면 조사형이라도 충분히 상기 각 효과를 발현하는 것이 가능하다.

- [0096] 이와 같은 구성을 갖는 고체 활상 장치는, 디지털 카메라나 비디오 카메라의 활상 디바이스로서 적용할 수 있다.

### 도면의 간단한 설명

- [0097] 도 1은 적층 칩을 사용한 반도체 장치에서, TCV를 통과하는 전송 신호를 시간이산하면서 양자화된 신호로 하는 제1의 구성례를 도시하는 도면.

- 도 2는 적층 칩을 사용한 반도체 장치에서, TCV를 통과하는 전송 신호를 시간이산하면서 양자화된 신호로 하는 제2의 구성례를 도시하는 도면.

- 도 3은 적층 칩을 사용한 반도체 장치에서, TCV를 통과하는 전송 신호를 시간이산하면서 양자화된 신호로 하는 제3의 구성례를 도시하는 도면으로서, 도 2의 구성례를 CMOS 이미지 센서에 적용한 한 예를 도시하는 도면.

- 도 4는 적층 칩을 사용한 반도체 장치에서, TCV를 통과하는 전송 신호를 시간연속이지만 양자화된 신호로 하는 제1의 구성례를 도시하는 도면.

- 도 5는 도 4의 반도체 장치의 동작을 시간축의 과정으로 도시하는 도면.

- 도 6은 적층 칩을 사용한 반도체 장치에서, TCV를 통과하는 전송 신호를 시간이산하면서 양자화된 신호로 하는 제2의 구성례를 도시하는 도면으로서, CMOS 이미지 센서에 적용한 한 예를 도시하는 도면.

- 도 7은 일반적인 싱글 슬로프형 AD 변환기의 구성을 도시하는 도면.

- 도 8은 인접 TCV로부터의 간섭에 의한 오차의 영향을 도시하는 도면.

- 도 9는 본 기술의 실시 형태에 관한 반도체 장치의 적층 구조의 한 예를 도시하는 도면.

- 도 10은 본 실시 형태에 관한 반도체 장치에서의 회로 등의 제1의 배치 구성을 도시하는 도면.

- 도 11은 본 실시 형태에 관한 반도체 장치의 신호의 시간적 관계를 도시하는 도면이다.

- 도 12는 본 실시 형태에 관한 반도체 장치에서의 회로 등의 제2의 배치 구성을 도시하는 도면이다.

- 도 13은 본 실시 형태에 관한 반도체 장치에서의 회로 등의 제3의 배치 구성을 도시하는 도면.

- 도 14는 도 13의 반도체 장치의 동작을 시간축의 과정으로, 인접 칼럼으로부터의 간섭을 저감할 수 있는 것을 도시하는 도면.

- 도 15는 본 실시 형태에 관한 CMOS 이미지 센서(고체 활상장 장치)의 기본적인 구성을 도시하는 도면.

- 도 16은 본 실시 형태에 관한 4개의 트랜지스터로 구성되는 CMOS 이미지 센서의 화소의 한 예를 도시하는 도면.

- 도 17은 본 실시 형태에 관한 열병렬 ADC 탑재 CMOS 이미지 센서(고체 활상 장치)의 구성을 도시하는 블록도.

도 18은 본 실시 형태에 관한 열병렬 ADC 탑재 CMOS 이미지 센서에서의 회로 등의 제1의 배치 구성례를 도시하는 도면.

도 19는 이산 시간 아날로그 신호를 전송하는 TCV를 집중하여 배치하고, 디지털 신호를 전송하는 TCV와 분리하여 배치하는 예를 도시하는 도면.

도 20은 본 실시 형태에 관한 열병렬 ADC 탑재 CMOS 이미지 센서에서의 회로 등의 제2의 배치 구성례를 도시하는 도면.

도 21은 본 실시 형태에 관한 열병렬 ADC 탑재 CMOS 이미지 센서에서의 회로 등의 제3의 배치 구성례를 도시하는 도면.

도 22는 본 실시 형태에 관한 비교기의 제1의 구성례를 도시하는 회로도.

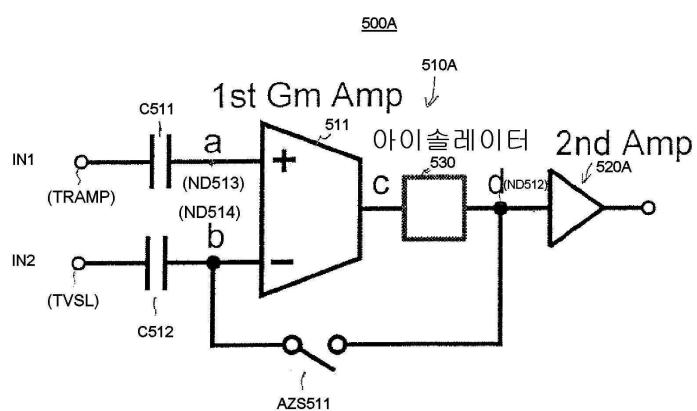

도 23은 본 실시 형태에 관한 저주파 노이즈를 저감 가능한, 아이솔레이터를 갖는 비교기의 기본 개념을 도시하는 도면.

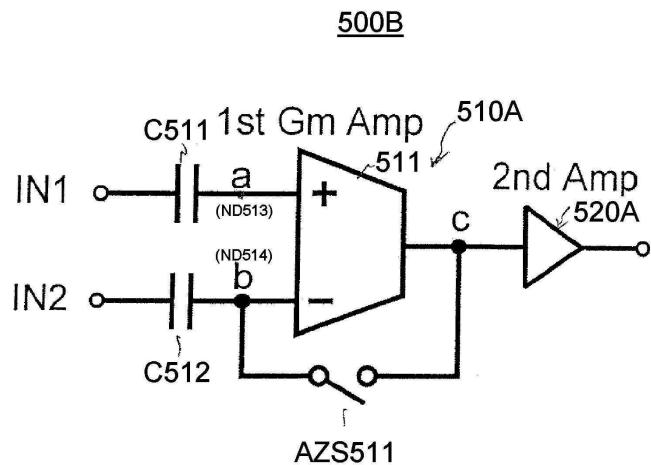

도 24는 도 23의 비교기의 비교레인 아이솔레이터를 갖지 않는 비교기의 기본 개념을 도시하는 도면.

도 25는 도 23의 본 실시 형태에 관한 비교기의  $G_m$  앰프의 입력측 노드와 출력측 노드 사이에 기생용량이 있는 예를 도시하는 도면.

도 26은 도 25의 구성례에서의 기생용량과 슬로프 신호 입력시에 각 노드의 파형을 도시하는 도면

도 27은 도 24의 비교례로서의  $G_m$  앰프의 입력측 노드와 출력측 노드 사이에 기생용량이 있는 예를 도시하는 도면.

도 28은 도 27의 구성례에서의 기생용량과 슬로프 신호 입력시에 각 노드의 파형을 도시하는 도면.

도 29는 비교기의 초단  $G_m$  앰프의 노이즈원에 관해 설명하기 위한 도면.

도 30은 전압 노이즈의 시간 노이즈의 변환례를 도시하는 도면.

도 31은 본 실시 형태에 관한 저주파 노이즈를 저감 가능한 비교기의 제1의 회로 구성례를 도시하는 도면.

도 32는 본 실시 형태에 관한 저주파 노이즈를 저감 가능한 비교기의 제2의 회로 구성례를 도시하는 도면.

도 33은 본 실시 형태에 관한 저주파 노이즈를 저감 가능한 비교기의 제3의 회로 구성례를 도시하는 도면.

도 34는 본 실시 형태에 관한 저주파 노이즈를 저감 가능한 비교기의 제4의 회로 구성례를 도시하는 도면.

도 35는 본 실시 형태에 관한 저주파 노이즈를 저감 가능한 비교기의 제5의 회로 구성례를 도시하는 도면.

도 36은 본 실시 형태에 관한 저주파 노이즈를 저감 가능한 비교기의 제6의 회로 구성례를 도시하는 도면.

도 37은 본 실시 형태에 관한 저주파 노이즈를 저감 가능한 비교기의 효과적인 실장례에 관해 설명하기 위한 도면.

도 38은 본 실시 형태에 관한 고체 활상 장치가 적용된 카메라 시스템의 구성의 한 예를 도시하는 도면.

### 발명을 실시하기 위한 구체적인 내용

[0098]

이하, 본 기술의 실시 형태를 도면에 관련지어서 설명한다.

[0099]

또한, 설명은 이하의 순서로 행한다.

[0100]

1. 반도체 장치의 개요

[0101]

1. 1 반도체 장치에서의 제1의 배치 구성례

[0102]

1. 2 반도체 장치에서의 제2의 배치 구성례

[0103]

1. 3 반도체 장치에서의 제3의 배치 구성례

[0104]

2. 고체 활상 장치의 개요

[0105]

2. 1 고체 활상 장치의 기본적인 구성례

- [0106] 2. 2 열병렬 ADC 탑재 고체 콜상 장치의 구성례

- [0107] 2. 3 고체 콜상 장치에서의 제1의 배치 구성례

- [0108] 2. 4 고체 콜상 장치에서의 제2의 배치 구성례

- [0109] 2. 5 고체 콜상 장치에서의 제3의 배치 구성례

- [0110] 3. 비교기의 구성례

- [0111] 3. 1 비교기의 기본적인 구성례

- [0112] 3. 2 저주파 노이즈를 저감 가능한 비교기의 기본적인 구성례

- [0113] 3. 3 저주파 노이즈를 저감 가능한 비교기의 구체적인 회로 구성례

- [0114] 4. 카메라 시스템의 구성례

- [0115] <1. 반도체 장치의 개요>

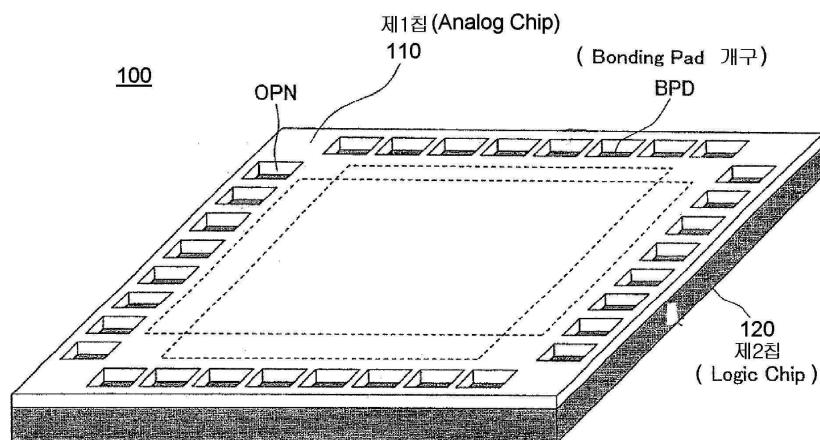

- [0116] 도 9는, 본 실시 형태에 관한 반도체 장치의 적층 구조의 한 예를 도시하는 도면이다.

- [0117] 본 실시 형태의 반도체 장치(100)는, 어레이형상으로 배치된, 광전 변환 소자 등을 포함하는 복수의 센서를 갖는다.

- [0118] 이하에서는, 이와 같은 구성을 갖는 반도체 장치의 구성례를 설명한 후, 반도체 장치의 한 예로서 고체 콜상 장치인 CMOS 이미지 센서의 구성례에 관해 설명한다. 그리고, 노이즈 저감 효과가 높고, 고체 콜상 장치에 적용 가능한 싱글 슬로프형 AD 변환기의 구체적인 구성례에 관해 설명한다.

- [0119] 반도체 장치(100)는, 도 9에 도시하는 바와 같이, 제1칩(상칩)(110)과 제2칩(하칩)(120)의 적층 구조를 갖는다.

- [0120] 적층된 제1칩(110)과 제2칩(120)은, 제1칩(110)에 형성된 비어(TCV)에 의해 전기적으로 접속된다.

- [0121] 이 반도체 장치(100)는, 웨이퍼 레벨로 접합한 후, 다이싱으로 절출(切出)한 적층 구조의 반도체 장치로서 형성된다.

- [0122] 상하 2칩의 적층 구조에서, 제1칩(110)은 어레이형상으로 복수의 센서가 배치된 아날로그 칩(센서 칩)으로 구성된다.

- [0123] 제2칩(120)은 제1칩(110)으로부터 TCV를 통하여 전송되는 아날로그 신호를 양자화하는 회로 및 신호 처리 회로를 포함하는 로직 칩(디지털 칩)으로 구성된다.

- [0124] 본딩 패드(BPD) 및 입출력 회로는 제2칩(120)에 형성되어 있고, 제1칩(110)에는, 제2칩(120)에 와이어 본드하기 위한 개구부(OPN)가 형성되어 있다.

- [0125] 그리고, 본 실시 형태에 관한 2칩의 적층 구조를 갖는 반도체 장치(100)는, 이하의 특징적인 구성을 갖는다.

- [0126] 제1칩(110)과 제2칩(120) 사이의 전기적 접속은, 예를 들면 비어(TCV)를 통하여 행하여진다.

- [0127] TCV(비어)의 배치 위치는 칩 단(端), 또는 패드(PAD)와 회로 영역의 사이로 한다.

- [0128] 예를 들면, 제어 신호 및 전력 공급용 TCV는 주로 칩 모서리부의 4개소에 집중하여, 제1칩(110)의 신호 배선 영역을 삭감할 수 있다.

- [0129] 제1칩(110)의 배선충수 삭감에 의해, 전원선 저항이 증가하고, IR-Drop가 증대하는 문제에 대해, TCV를 유효하게 배치함으로서, 제2칩(120)의 배선을 이용하여 제1칩(110)의 전원의 노이즈 대책이나 안정 공급 등을 위한 강화를 행하는 것이 가능하다.

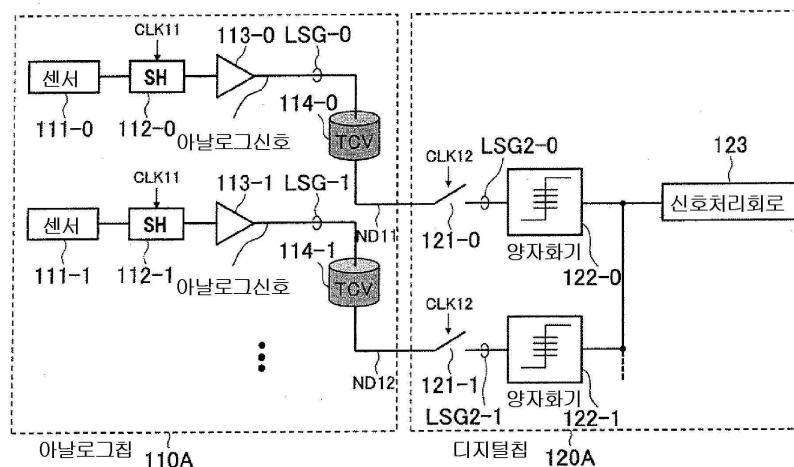

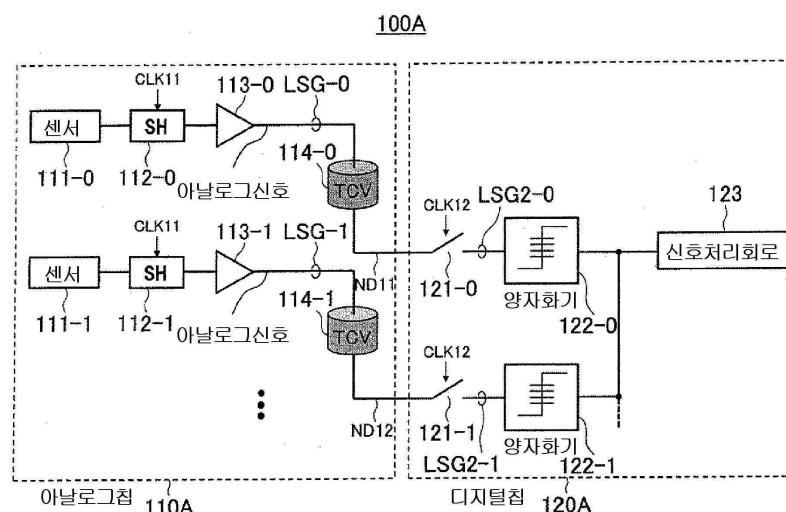

- [0130] <1. 1 반도체 장치에서의 제1의 배치 구성례>

- [0131] 도 10은, 본 실시 형태에 관한 반도체 장치에서의 회로 등의 제1의 배치 구성례를 도시하는 도면이다.

- [0132] 도 10의 반도체 장치(100A)는, 적층 구조를 갖는 제1칩(110A)과 제2칩(120A)의 회로 등의 배치를 용이하게 이해할 수 있도록, 제1칩(110A)과 제2칩(120A)이 2차원적으로 전개되어 도시되어 있다.

- [0133] 제1칩(110A)에는, 어레이형상으로 배치된 복수의 센서(111)(-0, -1, …), 각 센서(111)(-0, -1, …)의 출력 아

날로그 신호(센서 신호)를 전송하는 제1 신호선(LSG1)(-0, -1, ...)이 형성되어 있다.

[0134] 제1칩(110A)에서, 제1 신호선(LSG1)(-0, -1, ...)에는, 각 센서(111)(-0, -1, ...)의 센서 신호를 제1 클록(CLK11)으로 샘플링하는 샘플 훌드(SH) 회로(112)(-0, -1, ...)가 배치되어 있다.

[0135] 제1 신호선(LSG1)(-0, -1, ...)에는, 각각 샘플 훌드(SH) 회로(112)(-0, -1, ...)의 출력 센서 신호를 증폭하는 증폭기(앰프)(113)(-0, -1, ...)가 배치되어 있다.

[0136] 그리고, 제1칩(110A)에는, 제1 신호선(LSG1)(-0, -1, ...)을 제2칩(120A)측과 전기적으로 접속하고, 센서 신호를 전송하기 위한 TCV(114)(-0, -1, ...)가 형성되어 있다.

[0137] 또한, 도시하고 있지 않지만, 제1칩(110A)에는, 전원이나 제어 신호용의 TCV도 형성된다.

[0138] 제2칩(120A)에는, 제1칩(110A)에 형성된 각 TCV(114)에 접속된 제2 신호선(LSG2)(-0, -1, ...)이 형성되어 있다.

[0139] 각 제2 신호선(LSG2)(-0, -1, ...)에는, TCV(114)를 전송된 센서 신호를 제2 클록(CLK12)으로 샘플링하는 샘플링 스위치(121)(-0, -1, ...)가 배치되어 있다.

[0140] 각 제2 신호선(LSG2)(-0, -1, ...)에는, 샘플링 스위치(121)(-0, -1, ...)에서 샘플링된 신호를 양자화하는 양자화기(122)(-0, -1, ...)가 배치되어 있다.

[0141] 제2칩(120A)에는, 각 양자화기(122)(-0, -1, ...)에서 양자화된 신호를 디지털 연산 처리하는 신호 처리 회로(123)가 배치되어 있다.

[0142] 반도체 장치(100A)에서, 각 센서(111)로부터 출력되는 신호는, SH 회로(112)에서 샘플 훌드 되고, 앰프(113)를 통하여 TCV(114)에 전송된다.

[0143] 여기서, 센서(111)로부터 SH 회로(112)로부터 출력되는 신호의 전력이 충분히 큰 경우에 관해서는, 앰프는 없어도 좋다.

[0144] TCV(114)를 통하여 전송된 신호는 로직 칩(디지털 칩)인 제2칩(120A)상의 샘플링 스위치(121)에서 샘플링되고, 양자화기(122)를 이용하여 전압 방향으로 양자화된다. 이와 같이 하여 디지털화한 데이터는 신호 처리 회로(123)에서 연산 처리된다.

[0145] 도 2에 도시하는 기술에서는, TCV를 통하여 전송하는 신호를 전압 방향으로 양자화된 신호로 하고 있다.

[0146] 이에 대해, 본 기술에서는 TCV(114)를 전송하는 신호는 시간 방향으로 이산화되어 있고, 전압 방향으로 연속의 신호, 즉 이산 시간 아날로그 신호로 하고 있다.

[0147] 이 경우에 관해서도, 인접하는 TCV(114)로부터의 신호의 간섭이 발생한다.

[0148] 단, SH 회로(112)에서 샘플 훌드하는 타이밍을 제어하는 제1 클록(CLK11)과, 제2칩(120A)상에서 이산 시간 아날로그 신호를 샘플링하는 제2 클록(CLK12)의 타이밍을 적절하게 제어함에 의해, TCV 사이의 간섭을 회피할 수 있다.

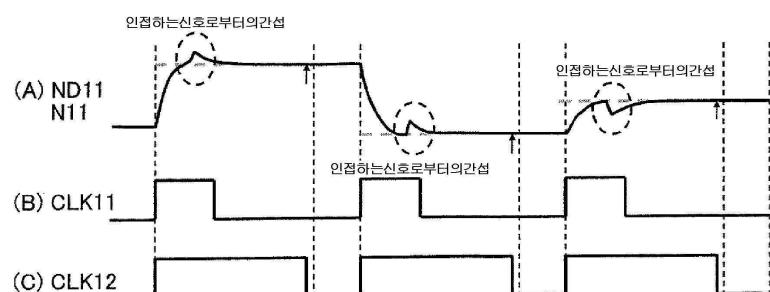

[0149] 도 11(A) 내지 (C)는, 본 실시 형태에 관한 반도체 장치의 신호의 시간적 관계를 도시하는 도면이다.

[0150] 도 11(A)는 TCV를 전송되는 신호가 공급되는 노드(ND11)의 신호 파형을, 도 11(B)는 제1 클록(CLK11)을, 도 11(C)는 제2 클록(CLK12)을, 각각 도시하고 있다.

[0151] 지금, TCV(114)를 통하여 전송되는 이산 시간 아날로그 신호의 노드(ND11)에 주목한다.

[0152] 제1 클록(CLK11)은 모든 센서(111)에 접속된 SH 회로(112)에서 공통의 타이밍을 사용하고 있기 때문에, 노드(ND11)와 인접한 노드(ND12)의 신호 전이의 시간은 이상적으로는 동기화되어 있다.

[0153] 단, 예를 들면 신호의 배선 지연 등으로 노드(ND11)와 노드(N12)에 센서로부터의 신호 출력 타이밍이 어긋난 경우에 관해서는, 도 11(A)에 도시하는 바와 같이 노드(ND11)의 신호에 간섭에 기인하는 해저드[hazard]가 발생한다.

[0154] 그러나, 1데이터 전송하는 구간에서 신호는 SH 회로(112)에서 이미 시간이산화되어 있기 때문에, 이 구간에서는 일정치이고, 충분히 시간을 경과하면 소망하는 값으로 정정(靜定)한다.

[0155] 이 충분히 값이 정정한 타이밍에서 제2 클록(CLK12)을 이용하여 샘플링을 행하도록 구동을 행함으로써,

TCV(114)의 간섭에 의해 발생한 오차를 무시할 수 있는 레벨까지 저감하는 것이 가능해진다.

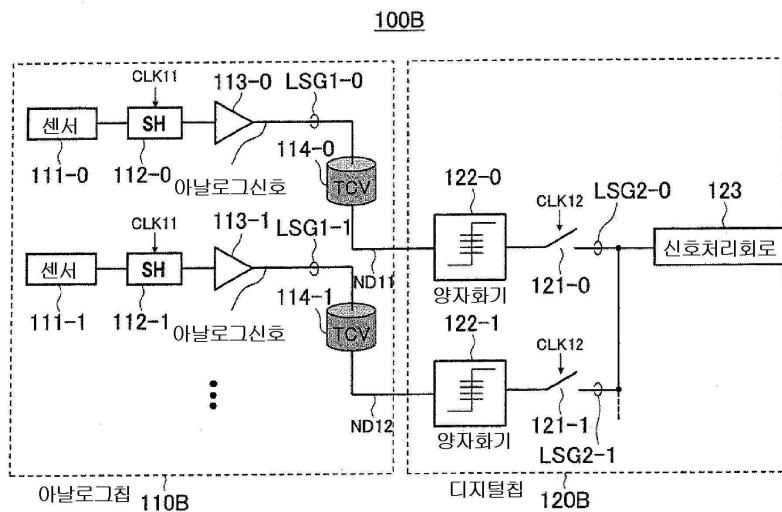

[0156] <1. 2 반도체 장치에서의 제2의 배치 구성례>

도 12는, 본 실시 형태에 관한 반도체 장치에서의 회로 등의 제2의 배치 구성례를 도시하는 도면이다.

도 12의 반도체 장치(100B)가 도 10의 반도체 장치(100A)와 다른 점은 이하와 같다.

즉, 제2칩(120B)에서, 각 제2 신호선(LSG2)(-0, -1, ...)에 배치되는 샘플링 스위치(121)(-0, -1, ...)와 양자화기(122)(-0, -1, ...)의 배치 위치(접속 위치)가 반대로 되어 있다.

본 기술에서의 제2 클록(CLK12)의 타이밍에서의 샘플링과 양자화는, 연속 시간으로의 양자화와 양자화기(122)에 접속된 샘플링 스위치(121)라는 바와 같이 순번을 교체하여도 상관없다.

[0161] 이 경우, 샘플링 스위치(121)의 동작은 플립플롭을 각 신호에 대해 마련함으로써 실현된다.

도 10과 같은 구성을 취한 경우, 샘플링 스위치(121)가 오프에 있는 때(끊어질 때)에 kT/C 노이즈가 발생하고, 이것이 문제가 될 우려가 있지만, 도 12의 구성이라면 kT/C 노이즈가 발생하지 않는다.

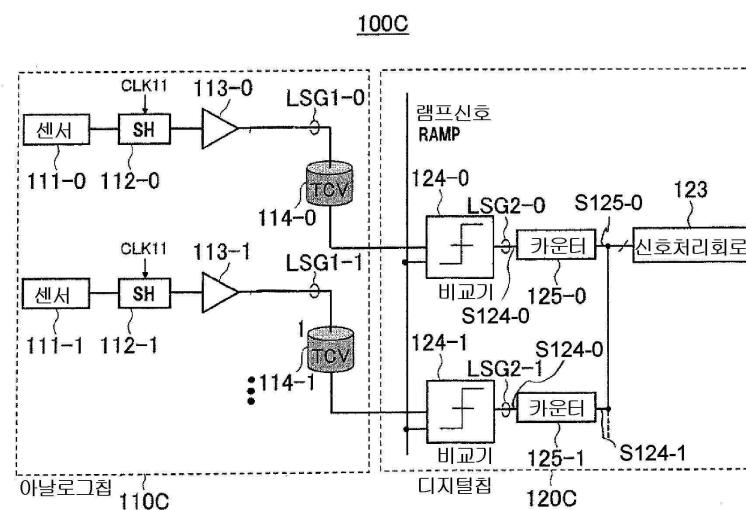

[0163] <1. 3 반도체 장치에서의 제3의 배치 구성례>

도 13은, 본 실시 형태에 관한 반도체 장치에서의 회로 등의 제3의 배치 구성례를 도시하는 도면이다.

도 13의 반도체 장치(100C)가 도 10 및 도 12의 반도체 장치(100A, 100B)와 다른 점은 이하와 같다.

즉, 제2칩(120C)에서는, 샘플링 스위치와 양자화기 대신에, 비교기(124)(-0, -1, ...) 및 카운터(125)(-0, -1, ...)가 마련되어 있다.

[0167] 이 제2칩(120C)에서는, 램프 신호(RAMP)와 TCV(114)를 전송된 센서 신호를 비교기(124)에 의해 비교함에 의해 전압축으로부터 시간축으로의 변환을 행하여, 시간 정보를 카운터(125)에서 양자화한다.

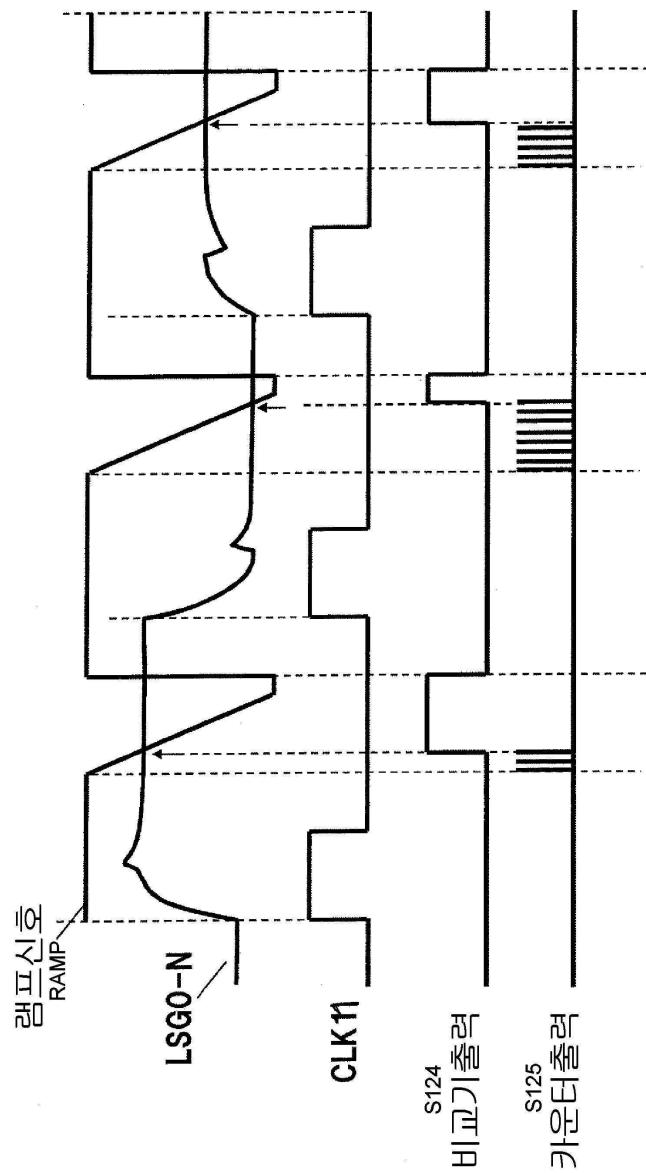

[0168] 이 경우에 도 11과 같은 원리로 인접 칼럼으로부터의 간섭을 저감할 수 있음을 도 14에 도시한다. 도 13의 구성에서, AD 변환 동작은 램프파(RAMP)와 신호를 비교하고, 이 시간을 카운터(124)에서 디지털값으로 변환함으로써 행하여지고 있다. 따라서 램프파 및 카운터(124)가 동작하고 있지 않는 시간에 관해서는, AD 변환기에서 신호의 받아들임은 행하여지지 않는다.

[0169] 여기서 도 14에 도시하는 바와 같이, 신호 출력(LSGO-N)이 충분히 정정하고 나서, 램프파의 천이 및 카운터의 동작을 시작함에 의해, 도 11과 마찬가지로 인접 TCV로부터의 간섭에 의한 오차를 저감하는 것이 가능해진다.

[0170] <2. 고체 활상 장치의 개요>

본 실시 형태에 관한 반도체 장치의 한 예로서 고체 활상 장치인 CMOS 이미지 센서의 구성례에 관해 설명한다.

[0172] <2. 1 고체 활상 장치의 기본적인 구성>

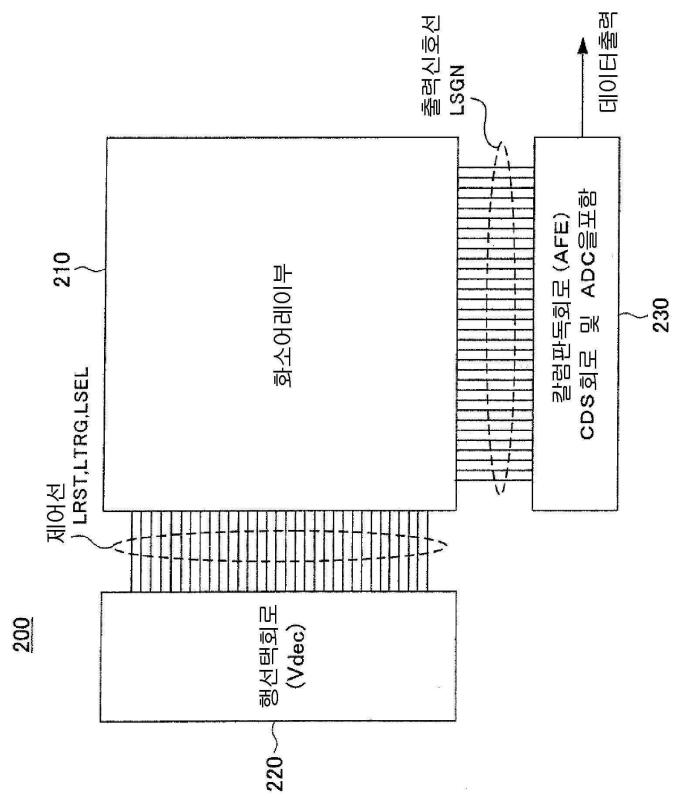

도 15는, 본 실시 형태에 관한 CMOS 이미지 센서(고체 활상장 장치)의 기본적인 구성례를 도시하는 도면이다.

[0174] 도 15의 CMOS 이미지 센서(200)는, 화소 어레이부(210), 행 선택 회로(Vdec)(220), 및 칼럼 판독 회로(AFE)(230)를 갖는다.

[0175] 그리고, 행 선택 회로(220) 및 칼럼 판독 회로(230)에 의해 화소 신호 판독부가 형성된다.

[0176] 이 반도체 장치로서의 CMOS 이미지 센서(200)는, 도 9의 적층 구조가 채용된다.

[0177] 본 실시 형태에서, 이 적층 구조에서는, 기본적으로, 제1칩(110)에는 화소 어레이부(210)가 배치되고, 제2칩(120)에 화소 신호 판독부를 형성하는 행 선택 회로(220) 및 칼럼 판독 회로(230)가 배치된다.

[0178] 그리고, 화소의 구동 신호나 화소(센서)의 아날로그 판독 신호, 전원 전압 등을 제1칩(110)이 형성된 TCV를 통하여, 제1칩(110)과 제2칩(120) 사이에서 송수(送受)된다.

[0179] 화소 어레이부(210)는, 복수의 화소 회로(210A)가 M행×N열의 2차원형상(매트릭스형상)으로 배열되어 있다.

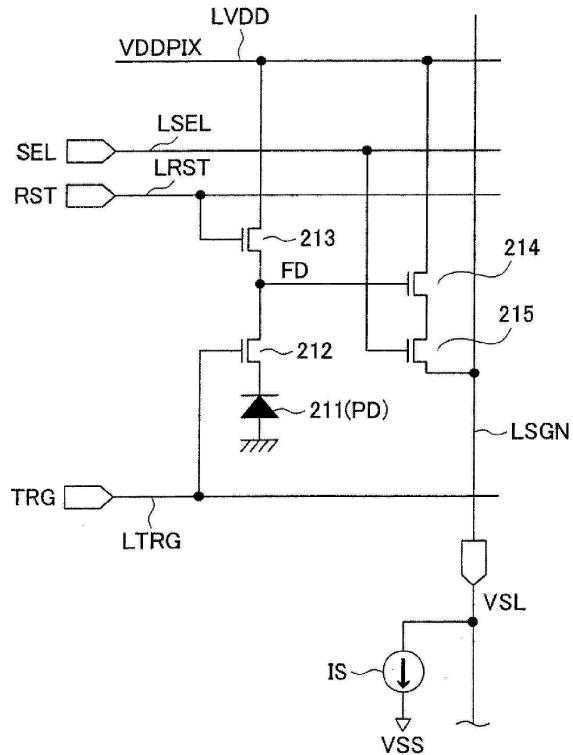

[0180] 도 16은, 본 실시 형태에 관한 4개의 트랜지스터로 구성되는 CMOS 이미지 센서의 화소의 한 예를 도시하는 도면이다.

[0181] 이 화소 회로(210A)는, 예를 들면 포토 다이오드(PD)로 이루어지는 광전 변환 소자(이하, 단지 PD라고 할 때도

있다)(211)를 갖는다.

[0182] 그리고, 화소 회로(210A)는, 이 1개의 광전 변환 소자(211)에 대해, 전송 트랜지스터(212), 리셋 트랜지스터(213), 증폭 트랜지스터(214), 및 선택 트랜지스터(215)의 4개의 트랜지스터를 능동 소자로서 갖는다.

[0183] 광전 변환 소자(211)는, 입사광을 그 광량에 응한 양의 전하(여기서는 전자)로 광전 변환한다.

[0184] 전송 소자로서의 전송 트랜지스터(212)는, 광전 변환 소자(211)와 입력 노드로서의 플로팅 디퓨전(FD)과의 사이에 접속되고, 전송 제어선(LTRG)을 통하여 그 게이트(전송 게이트)에 제어 신호인 전송 신호(TRG)가 주어진다.

[0185] 이에 의해, 전송 트랜지스터(212)는, 광전 변환 소자(211)에서 광전 변환된 전자를 플로팅 디퓨전(FD)에 전송한다.

[0186] 리셋 트랜지스터(213)는, 전원 전압(VDD)이 공급되는 전원 라인(LVDD)과 플로팅 디퓨전(FD)과의 사이에 접속되고, 리셋 제어선(LRST)을 통하여 그 게이트에 제어 신호인 리셋 신호(RST)가 주어진다.

[0187] 이에 의해, 리셋 소자로서의 리셋 트랜지스터(213)는, 플로팅 디퓨전(FD)의 전위를 전원 라인(LVDD)의 전위로 리셋한다.

[0188] 플로팅 디퓨전(FD)에는, 증폭 소자로서의 증폭 트랜지스터(214)의 게이트가 접속되어 있다. 즉, 플로팅 디퓨전(FD)은 증폭 소자로서의 증폭 트랜지스터(214)의 입력 노드로서 기능한다.

[0189] 증폭 트랜지스터(214)와 선택 트랜지스터(215)는 전원 전압(VDD)이 공급되는 전원 라인(LVDD)과 신호선(LSGN)과의 사이에 직렬로 접속되어 있다.

[0190] 이와 같이, 증폭 트랜지스터(214)는, 선택 트랜지스터(215)를 통하여 신호선(LSGN)에 접속되고, 화소부 외의 정전류원(IS)과 소스 팔로워를 구성하고 있다.

[0191] 그리고, 선택 제어선(LSEL)을 통하여 어드레스 신호에 응한 제어 신호인 선택 신호 SEL이 선택 트랜지스터(215)의 게이트에 주어져, 선택 트랜지스터(215)가 온 한다.

[0192] 선택 트랜지스터(215)가 온 하면, 증폭 트랜지스터(214)는 플로팅 디퓨전(FD)의 전위를 증폭하여 그 전위에 응한 전압을 신호선(LSGN)에 출력한다. 신호선(LSGN)을 통하여, 각 화소로부터 출력되는 전압은, 칼럼 판독 회로(230)에 출력된다.

[0193] 이들의 동작은, 예를 들면 전송 트랜지스터(212), 리셋 트랜지스터(213), 및 선택 트랜지스터(215)의 각 게이트가 행 단위로 접속되어 있기 때문에, 1행분의 각 화소에 관해 동시에 행하여진다.

[0194] 화소 어레이부(210)에 배선되어 있는 리셋 제어선(LRST), 전송 제어선(LTRG), 및 선택 제어선(LSEL)이 1조(組)로서 화소 배열의 각 은행 단위로 배선되어 있다.

[0195] LRST, LTRG, LSEL의 각 제어선은 각각 M개씩 마련되어 있다.

[0196] 이들의 리셋 제어선(LRST), 전송 제어선(LTRG), 및 선택 제어선(LSEL)은, 행 선택 회로(220)에 의해 구동된다.

[0197] 이와 같은 구성을 갖는 화소 어레이부(210)는, 상술한 바와 같이, 신호 배선 및 제어 배선을 포함하여 제1침(110)에 형성된다.

[0198] 그리고, 본 실시 형태에서는, 제1침(110)에 배치된 증폭 트랜지스터(214)와 소스 팔로워를 형성하는 정전류원(IS)은 제2침(120)측에 배치된다.

[0199] 행 선택 회로(220)는, 화소 어레이부(210) 중의 임의의 행에 배치된 화소의 동작을 제어한다. 행 선택 회로(220)는, 제어선(LSEL, LRST, LTRG)을 통하여 화소를 제어한다.

[0200] 행 선택 회로(220)는, 예를 들면 셔터 모드 전환 신호에 응하여 노광 방식을 행마다 노광을 행하는 롤링 셔터 방식 또는 전 화소에 노광을 행하는 글로벌 셔터 방식으로 전환하여, 화상 구동 제어를 행한다.

[0201] 칼럼 판독 회로(230)는, 행 선택 회로(220)에 의해 판독 제어된 화소행의 데이터를 신호 출력선(LSGN)을 통하여 수취하고, 후단의 신호 처리 회로에 전송한다.

[0202] 칼럼 판독 회로(230)는, CDS 회로나 ADC(Analog digital converter : 아날로그 디지털 컨버터)를 포함한다.

[0203] <2. 2 열병렬 ADC 탑재 고체 콜상 장치의 구성례>

- [0204] 또한, 본 실시 형태에 관한 CMOS 이미지 센서는, 특히 한정되지 않지만, 예를 들면 열병렬형의 아날로그-디지털 변환 장치(이하, ADC라고 약칭한다)를 탑재한 CMOS 이미지 센서로서 구성하는 것도 가능하다.

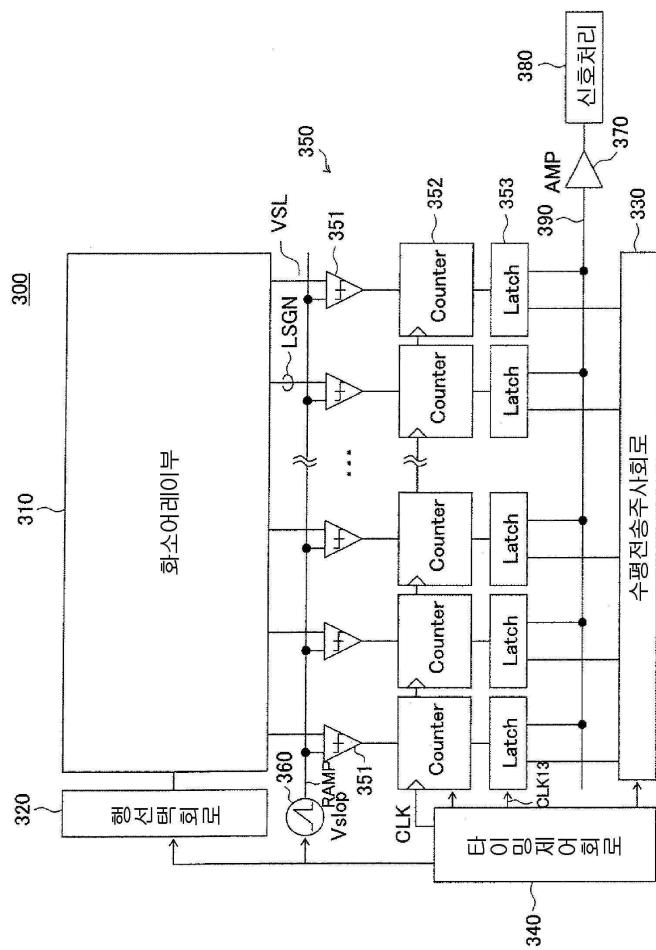

- [0205] 도 17은, 본 실시 형태에 관한 열병렬 ADC 탑재 CMOS 이미지 센서(고체 활상 장치)의 구성례를 도시하는 블록도이다.

- [0206] 이 고체 활상 소자(300)는, 도 17에 도시하는 바와 같이, 활상부로서의 화소 어레이부(310), 화소 구동부로서의 행 선택 회로(320), 수평 전송 주사 회로(330), 타이밍 제어 회로(340)를 갖는다.

- [0207] 또한, 고체 활상 소자(300)는, ADC군(350), 램프 신호 발생기로서의 디지털-아날로그 변환 장치(이하, DAC(Digital Analog converter)라고 약칭한다)(360), 앰프 회로(S/A)370, 신호 처리 회로(380), 및 수평 전송 선(390)을 갖는다.

- [0208] 화소 어레이부(310)는, 광전 변환 소자(포토 다이오드)와 화소 내 앰프를 포함하는, 예를 들면 도 16에 도시하는 바와 같은 화소가 매트릭스형상(행렬형상)으로 배치되어 구성된다.

- [0209] 또한, 고체 활상 소자(300)에서는, 화소 어레이부(310)의 신호를 순차적으로 판독하기 위한 제어 회로로서 다음의 회로가 배치되어 있다.

- [0210] 즉, 고체 활상 소자(300)에서는, 제어 회로로서 내부 클록을 생성하는 타이밍 제어 회로(340), 행 어드레스나 행 주사를 제어하는 행 선택 회로(320), 그리고 열어드레스(address)나 열 주사를 제어하는 수평 전송 주사 회로(330)가 배치된다.

- [0211] ADC군(350)은, 비교기(351), 카운터(352), 및 래치(353)를 갖는 스크립트형 ADC가 복수열 배열되어 있다.

- [0212] 비교기(351)는, DAC(360)에 의해 생성되는 참조 전압을 계단형상으로 변화시킨 램프파형(RAMP)인 참조 전압(Vslop)과, 행선(行線)마다 화소로부터 수직 신호선(LSGN)을 경유하여 얻어지는 아날로그 신호를 비교한다.

- [0213] 카운터(352)는, 비교기(351)의 비교 시간을 카운트한다.

- [0214] ADC군(350)은, n비트 디지털 신호 변환 기능을 가지며, 수직 신호선(열선)마다 배치되고, 열병렬 ADC 블록이 구성된다.

- [0215] 각 래치(353)의 출력은, 예를 들면 2n비트 폭의 수평 전송선(390)에 접속되어 있다.

- [0216] 그리고, 수평 전송선(390)에 대응하는 2n개의 앰프 회로(370), 및 신호 처리 회로(380)가 배치된다.

- [0217] ADC군(350)에서는, 수직 신호선(LSGN)에 판독된 아날로그 신호(전위(VSL))는 열마다 배치된 비교기(351)에서 참조 전압(Vslop)(어느 경사를 갖는 선형으로 변화하는 스크립트 파형)과 비교된다.

- [0218] 이 때, 비교기(351)와 마찬가지로 열마다 배치된 카운터(352)가 동작하고 있고, 램프파형(RAMP)의 어느 전위(Vslop)와 카운터값이 1대1 대응을 취하면서 변화함으로써 수직 신호선의 전위(아날로그 신호)(VSL)를 디지털 신호로 변환한다.

- [0219] 참조 전압(Vslop)의 변화는 전압의 변화를 시간의 변화로 변환하는 것이고, 그 시간을 있는 주기(클록)로 헤아림으로써 디지털값으로 변환하는 것이다.

- [0220] 그리고 아날로그 전기 신호(VSL)와 참조 전압(Vslop)이 교차한 때, 비교기(351)의 출력이 반전하고, 카운터(352)의 입력 클록을 정지하고, AD 변환이 완료된다.

- [0221] 이상의 AD 변환 기간 종료 후, 수평 전송 주사 회로(330)에 의해, 래치(353)에서 유지된 데이터가, 수평 전송선(390), 앰프 회로(370)를 경유하여 신호 처리 회로(380)에 입력되고, 2차원 화상이 생성된다.

- [0222] 이와 같이 하여, 열병렬 출력 처리가 행하여진다.

- [0223] 또한, 여기서 채용되는 비교기(351)의 구체적인 구성에 관해서는 후에 상세히 기술한다.

- [0224] 이 반도체 장치로서의 CMOS 이미지 센서(300)에서도, 도 9의 적층 구조가 채용된다.

- [0225] 본 실시 형태에서, 이 적층 구조에서는, 기본적으로, 제1침(110)에는 화소 어레이부(310)가 배치된다.

- [0226] 제2침(120)에, 행 선택 회로(320), 수평 전송 주사 회로(330), 타이밍 제어 회로(340), ADC군(350), DAC(램프 신호 발생기)(360), 앰프 회로(S/A)(370), 신호 처리 회로(380), 및 수평 전송선(390)이 배치된다.

- [0227] 그리고, 화소의 구동 신호나 화소(센서)의 아날로그 판독 신호, 전원 전압 등은 제1칩(110)이 형성된 TCV를 통하여, 제1칩(110)과 제2칩(120) 사이에서 송수된다.

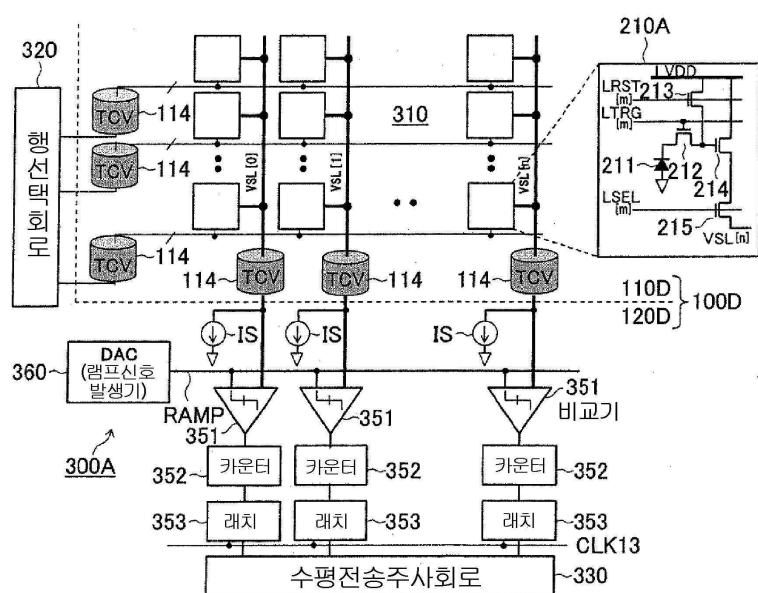

- [0228] <2. 3 고체 활상 장치에서의 제1의 배치 구성례>

- [0229] 여기서, 도 17의 열병렬 ADC 탑재 CMOS 이미지 센서의 각 구성 요소를 적층 구조의 제1칩 및 제2칩에 배치한 구성례에 관해 설명한다.

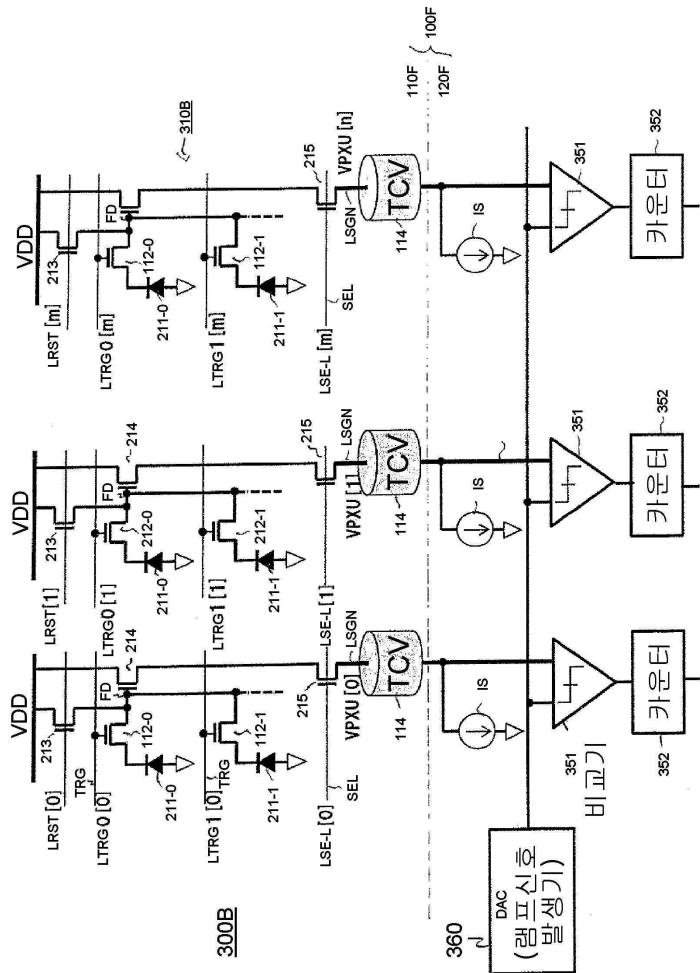

- [0230] 도 18은, 본 실시 형태에 관한 열병렬 ADC 탑재 CMOS 이미지 센서에서의 회로 등의 제1의 배치 구성례를 도시하는 도면이다.

- [0231] 도 18에서도, 적층 구조를 갖는 제1칩(110D)과 제2칩(120D)의 회로 등의 배치를 용이하게 이해할 수 있도록, 제1칩(110D)과 제2칩(120D)이 2차원적으로 전개되어 도시되어 있다.

- [0232] 또한, 도 18에서는, 타이밍 제어 회로(340)나 앰프 회로(370), 신호 처리 회로(380)는 생략되어 있다. 이들의 회로도 제2칩(110D)에 배치된다.

- [0233] 전술한 바와 같이, 이 적층 구조에서는, 기본적으로, 제1칩(110D)에는 화소 어레이부(310)가 배치된다.

- [0234] 제2칩(120D)에, 행 선택 회로(320), 수평 전송 주사 회로(330), 타이밍 제어 회로(340), ADC군(350)의 비교기(351), 카운터(352), 래치(353), 및 DAC(앰프 신호 발생기)(360)가 배치된다.

- [0235] 그리고, 화소의 구동 신호나 화소(센서)의 아날로그 판독 신호, 전원 전압 등은 제1칩(110D)이 형성된 TCV를 통하여, 제1칩(110D)과 제2칩(120D) 사이에서 송수된다.

- [0236] 또한, 본 실시 형태에서는, 제1칩(110D)에 배치되는 화소의 증폭 트랜지스터 등과 소스 팔로워를 형성하는 전류원(IS)은, 제2칩(120D)에 배치된다.

- [0237] 이 도 18의 배치 구성례는 도 13의 배치 구성례와 마찬가지로 행하여지고 있다.

- [0238] 도 18의 CMOS 이미지 센서(300A)에서는, 행 선택 회로(320)로부터 출력되는 전송 트랜지스터(전송 스위치)를 온 오프 제어하는 전송 제어 신호(TRG)가 도 13에서의 제1 클록(CLK11)과 동등한 기능으로 된다.

- [0239] 이에 대해 램프파의 생성 타이밍을 VSL[m]가 충분히 정정한 시간을 주도록 제어함으로써, 도 14에 도시한 바와 같이 인접 TCV로부터의 간섭에 의한 오차를 억제하고 신호를 전송하는 것이 가능해진다.

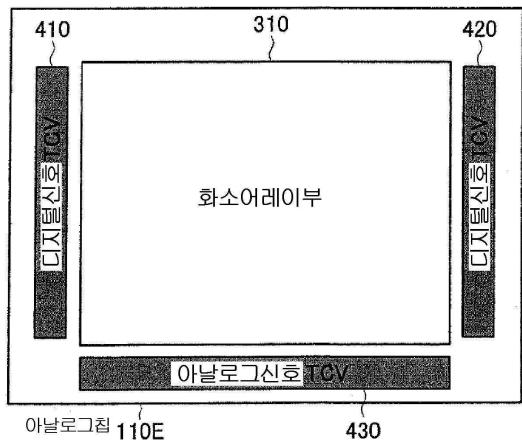

- [0240] 도 19는, 이산 시간 아날로그 신호를 전송하는 TCV를 집중하여 배치하고, 디지털 신호를 전송하는 TCV와 분리하여 배치하는 예를 도시하는 도면이다.

- [0241] 이상과 같은 구성을 취함으로써, 인접 TCV로부터의 간섭이 억제된다.

- [0242] 그러나, 예를 들면 도 18의 시스템에서, 행 선택 회로(320)의 출력은, 스위치를 온, 오프 시키기 위한 통상의 디지털 신호이고, 이들의 신호로부터 신호선(LSGN)[n]에의 간섭을 저감하는 것은 용이하지가 않다.

- [0243] 따라서 본 기술에서는, 도 19에 도시하는 바와 같이, 이산 시간 아날로그 신호를 전송하는 TCV를 집중하여 배치하고, 이것을 디지털 신호를 전송하는 TCV와 분리하여 배치하는 것이 유효해진다.

- [0244] 도 19의 예에서는, 제1칩(110E)에서, 화소 어레이부(310)의 도 19 중에서의 좌우 양측부에 디지털 신호용 TCV의 배치 영역(410, 420)이 형성되어 있다.

- [0245] 그리고, 화소 어레이부(310)의 도 19 중의 하측의 측부에 아날로그 신호용 TCV의 배치 영역(430)이 형성되어 있다.

- [0246] <2. 4 고체 활상 장치에서의 제2의 배치 구성례>

- [0247] 도 20은, 본 실시 형태에 관한 열병렬 ADC 탑재 CMOS 이미지 센서에서의 회로 등의 제2의 배치 구성례를 도시하는 도면이다.

- [0248] 도 20의 CMOS 이미지 센서(300B)는, 화소 어레이부(310B)가 하나의 플로팅 디퓨전(FD)을 복수의 화소에서 공유하고 있는 경우의 예이다.

- [0249] 도 20의 예에서는, 2개의 화소로, 플로팅 디퓨전(FD), 리셋 트랜지스터(213), 증폭 트랜지스터(214), 선택 트랜지스터(215)가 공유되어 있다.

- [0250] 각 화소는, 광전 변환 소자(포토 다이오드)(211) 및 전송 트랜지스터(212)를 포함하여 구성되어 있다.

- [0251] 이 경우도, 기본적으로, 제1칩(110F)에는 화소 어레이부(310B)가 배치되고, 그 밖의 구성은, 도 18과 마찬가지이다.

- [0252] <2. 5 고체 활상 장치에서의 제3의 배치 구성례>

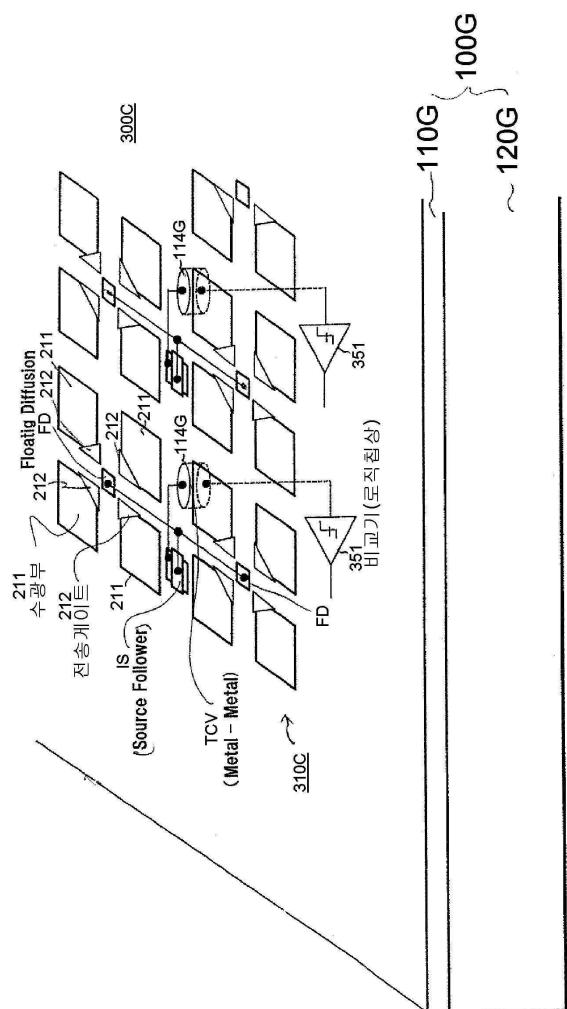

- [0253] 도 21은, 본 실시 형태에 관한 열병렬 ADC 탑재 CMOS 이미지 센서에서의 회로 등의 제3의 배치 구성례를 도시하는 도면이다.

- [0254] 도 21의 CMOS 이미지 센서(300C)는, 도 20과 마찬가지로, 화소 어레이부(310C)가 하나의 플로팅 디퓨전(FD)을 복수의 화소에서 공유하고 있는 경우의 예이다.

- [0255] 이 경우도, 기본적으로, 제1칩(110G)에는 화소 어레이부(310C)가 배치되어 있다.

- [0256] 이 예에서는, 공유 영역의 부근에 TCV(114G)가 형성되어 있다.

- [0257] TCV(114G)는 제1칩(110G)과 제2칩(120G)에 형성된 금속(예를 들면 Cu)의 접속 전극 사이를 금속으로 접속하여 형성되고, 신호선(LSGN)에 출력되는 화소 신호를, TCV(114G)를 통하여 제2칩(120G)측의 비교기(351)에 공급한다.

- [0258] <3. 비교기의 구성례>

- [0259] 다음에, ADC군에 적용되고, 칼럼 ADC를 형성하는 비교기(351)의 구체적인 구성례에 관해 설명한다.

- [0260] 상술한 바와 같은, 본 기술을 실시하는 경우에 우려되는 점으로서, 디지털 칩인 제2칩상에 양자화기, 비교기를 실현하기 때문에 이들의 회로의 노이즈가 아날로그 칩에 실현한 경우와 비교하여 커져 버리는 것을 들 수 있다.

- [0261] 이하에, 도 17 내지 도 21의 CMOS 이미지 센서에 관해, 이 노이즈에 대해 유효하게 되는 비교기의 구성례를 나타낸다.

- [0262] <3. 1 비교기의 기본적인 구성례>

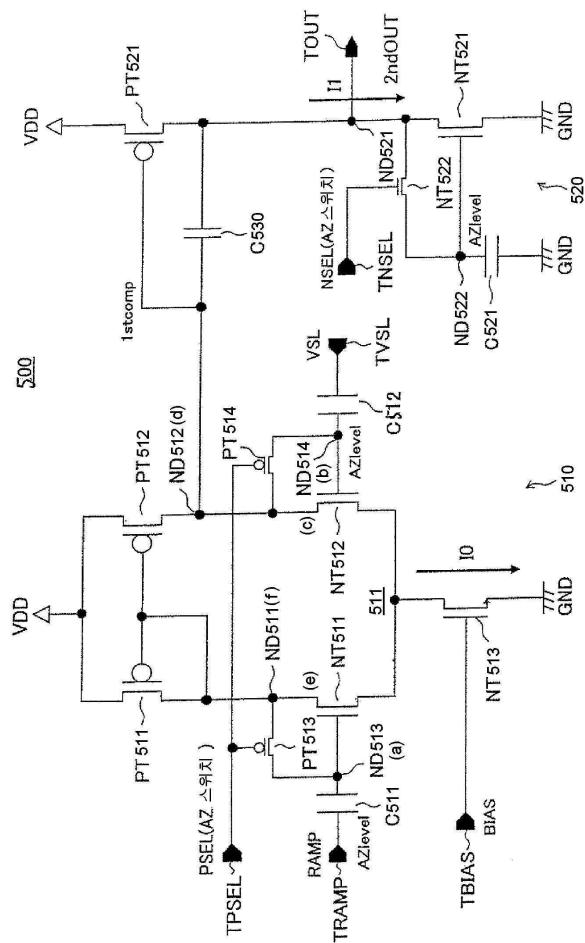

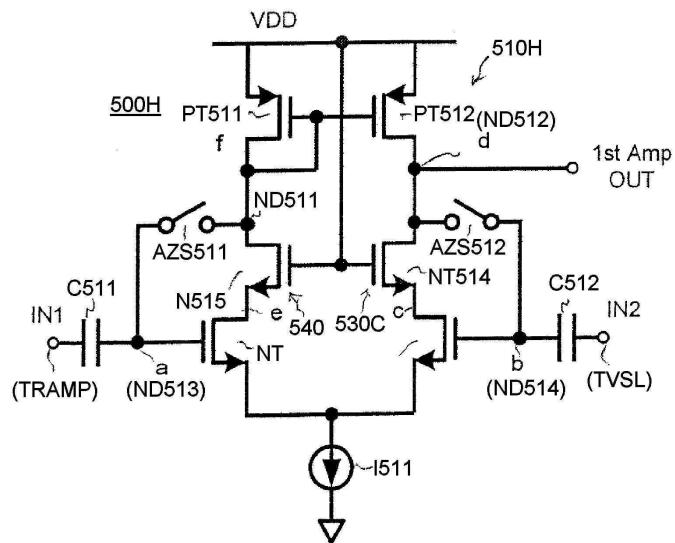

- [0263] 도 22는, 본 실시 형태에 관한 비교기의 제1의 구성례를 도시하는 회로도이다.

- [0264] 이하의 비교기는 부호 500을 붙이고 설명한다.

- [0265] 도 22는, 미러 용량을 이용하여 대역(帶域)을 크게 제한하여 노이즈를 저감하는 비교기의 구성례를 도시하고 있다. 비교기를 이와 같이 구성함으로써 비교기가 출력하는 노이즈 전력이 작아지기 때문에, 디지털 칩인 제2칩상에서 비교기를 실현하는 것의 디메리트를 보완하는 것이 가능해진다.

- [0266] 칼럼마다 배치되는 비교기(500)는, 도 22에 도시하는 바와 같이, 종속 접속된 제1 앰프(510), 제2 앰프(520), 및 미러 효과를 발현하기 위한 용량인 커패시터(C530)를 갖고 있다.

- [0267] 그리고, 2단째의 제2 앰프(520)의 소스 접지형 증폭기의 입출력 사이에 용량이 접속되어 있다. 이 용량은, 미러 효과를 발현하고, 소스 접지 입력에 게인배(倍)의 용량이 접속된 것과 등가(等價)가 된다.

- [0268] 이에 의해, 각 비교기(500)의 대역은 작은 용량으로 크게 좁혀진다.

- [0269] 각 비교기(500)는, 행동작(行動作) 시작시에 칼럼마다 동작점을 정하기 위해 초기화(오토 제로 : AZ)하여 샘플링하는 기능을 갖는다.

- [0270] 또한, 본 실시 형태에서, 제1 도전형은 p채널 또는 n채널이고, 제2 도전형은 n채널 또는 p채널이다.

- [0271] 제1 앰프(510)는, 절연 게이트형 전계효과 트랜지스터인 p채널 MOS(PMOS) 트랜지스터(PT511 내지 PT514), 및 n 채널 MOS(NMOS) 트랜지스터(NT511 내지 NT513)를 갖고 있다.

- [0272] 제1 앰프(510)는, AZ 레벨의 샘플링 용량(입력 용량)으로서의 제1 및 제2의 커패시터(C511, C512)를 갖는다.

- [0273] PMOS 트랜지스터(PT511)의 소스 및 PMOS 트랜지스터(PT512)의 소스가 전원 전위원(VDD)에 접속되어 있다.

- [0274] PMOS 트랜지스터(PT511)의 드레인은 NMOS 트랜지스터(NT511)의 드레인에 접속되고, 그 접속점에 의해 노드(ND511)가 형성되어 있다. 또한, PMOS 트랜지스터(PT511)의 드레인과 게이트가 접속되고, 그 접속점이 PMOS 트랜지스터(512)의 게이트에 접속되어 있다.

- [0275] PMOS 트랜지스터(PT512)의 드레인이 NMOS 트랜지스터(NT512)의 드레인에 접속되고, 그 접속점에 의해 제1 앰프(510)의 출력 노드(ND512)가 형성되어 있다.

- [0276] NMOS 트랜지스터(NT511)와 NMOS 트랜지스터(NT512)의 소스끼리가 접속되고, 그 접속점이 NMOS 트랜지스터(NT513)의 드레인에 접속되어 있다. NMOS 트랜지스터(NT513)의 소스는 기준 전위원(예를 들면 접지 전위)(GND)에 접속되어 있다.

- [0277] NMOS 트랜지스터(NT511)의 게이트가 커페시터(C511)의 제1 전극에 접속되고, 그 접속점에 의해 노드(ND513)가 형성되어 있다. 그리고, 커페시터(C511)의 제2 전극이 램프 신호(RAMP)의 입력단자(TRAMP)에 접속되어 있다.

- [0278] NMOS 트랜지스터(NT512)의 게이트가 커페시터(C512)의 제1 전극에 접속되고, 그 접속점에 의해 노드(ND514)가 형성되어 있다. 그리고, 커페시터(C512)의 제2 전극이 아날로그 신호(VSL)의 입력단자(TVSL)에 접속되어 있다.

- [0279] 또한, NMOS 트랜지스터(NT513)의 게이트가 바이어스 신호(BIAS)의 입력단자(TBIAS)에 접속되어 있다.

- [0280] PMOS 트랜지스터(PT513)의 소스가 노드(ND511)에 접속되고, 드레인이 노드(ND513)에 접속되어 있다. PMOS 트랜지스터(PT514)의 소스가 노드(ND512)에 접속되고, 드레인이 노드(ND514)에 접속되어 있다.

- [0281] 그리고, PMOS 트랜지스터(PT513 및 PT514)의 게이트가 로우 레벨에서 액티브의 제1의 AZ 신호(PSEL)의 입력단자(TPSEL)에 공통으로 접속되어 있다.

- [0282] 이와 같은 구성을 갖는 제1 앰프(510)에서 PMOS 트랜지스터(PT511, PT512)에 의해 커런트 미러 회로가 구성된다.

- [0283] 그리고, NMOS 트랜지스터(NT511, NT512)에 의해 NMOS 트랜지스터(NT513)를 전류원으로 하는 차동 비교부(트랜스 컨덕턴스 앰프(Gm 앰프))(511)가 구성된다.

- [0284] 또한, PMOS 트랜지스터(PT513, PT514)가 AZ(오토 제로 : 초기화) 스위치로서 기능하고, 커페시터(C511, C512)가 AZ 레벨의 샘플링 용량으로서 기능한다.

- [0285] 그리고, 제1 앰프(510)의 출력 신호(1st comp)는 출력 노드(ND512)로부터 제2 앰프(520)에 출력된다.

- [0286] 제2 앰프(520)는, PMOS 트랜지스터(PT521), NMOS 트랜지스터(NT521, NT522), 및 AZ 레벨의 샘플링 용량으로서의 제3의 커페시터(C521)를 갖는다.

- [0287] PMOS 트랜지스터(PT521)의 소스가 전원 전위원(VDD)에 접속되고, 게이트가 제1 앰프(510)의 출력 노드(ND512)에 접속되어 있다.

- [0288] PMOS 트랜지스터(PT521)의 드레인이 NMOS 트랜지스터(NT521)의 드레인에 접속되고, 그 접속점에 의해 출력 노드(ND521)가 형성되어 있다.

- [0289] NMOS 트랜지스터(NT521)의 소스가 접지 전위(GND)에 접속되고, 게이트가 커페시터(C521)의 제1 전극에 접속되고, 그 접속점에 의해 노드(ND522)가 형성되어 있다. 커페시터(C521)의 제2 전극은 접지 전위(GND)에 접속되어 있다.

- [0290] NMOS 트랜지스터(NT522)의 드레인이 노드(ND521)에 접속되고, 소스가 노드(ND522)에 접속되어 있다.

- [0291] 그리고, NMOS 트랜지스터(NT522)의 게이트가 하이 레벨에서 액티브의 제2의 AZ 신호(NSEL)의 입력단자(TNSEL)에 접속되어 있다.

- [0292] 이 제2의 AZ 신호(NSEL)는, 제1 앰프(510)에 공급되는 제1의 AZ 신호(PSEL)와 상보적인 레벨을 취한다.

- [0293] 이와 같은 구성을 갖는 제2 앰프(520)에서, PMOS 트랜지스터(PT521)에 의해 입력 및 증폭 회로가 구성되어 있다.

- [0294] 또한, NMOS 트랜지스터(PT522)가 AZ 스위치로서 기능하고, 커페시터(C521)가 AZ 레벨의 샘플링 용량으로서 기능한다.

- [0295] 그리고, 제2 앰프(520)의 출력 노드(ND521)는, 비교기(500)의 출력 단자(TOUT)에 접속되어 있다.

- [0296] 커페시터(C530)는, 제1 전극이 소스 접지형 증폭기로서 PMOS 트랜지스터(PT521)의 게이트(입력)에 접속되고, 제2 전극이 PMOS 트랜지스터(PT521)의 드레인(출력)에 접속되어 있다.

- [0297] 이 커패시터(C530)는, 미러 효과를 발현하고, 소스 접지 입력에 게인배의 용량이 접속된 것과 등가가 된다.

- [0298] 제1 앰프(510)의 출력에 보이는 용량은, PMOS 트랜지스터(PT521)의 게인을  $A_{V2}$ 로 하여, 커패시터(C530)의 용량을 C라고 하면,  $\{C*(1+A_{V2})\}$ 와 같이 게인배되기 때문에 커패시터(C530)의 용량치를 작게 하여도 좋다.

- [0299] 이에 의해, 비교기(500)의 대역은 작은 용량으로 크게 좁혀진다.

- [0300] 이 비교기(500)의 초단의 제1 앰프(510)의 출력에 미러 용량을 삽입하는 구성에서는, 기본적으로는 노이즈의 대역 즉 동작 대역을 저감하는 수법인 이상, 동작 속도가 저하되기 때문에 일정 이상의 노이즈 저감 효과는 작다.

- [0301] 또한 이 구성의 경우, 그 대역 제한에 의한 노이즈 저감이라는 원리상, 플리커 노이즈나 RTS 노이즈 등의 저주파 노이즈에 관해서는 효과가 작다.

- [0302] 이하에, 비교기(500)에서의 더한층의 노이즈 저감, 특히 저주파 노이즈의 저감을 도모할 수 있는 구성에 관해 설명한다.

- [0303] 이하에 설명하는 비교기는, 제1 앰프의 구성에 특징이 있다.

- [0304] 또한, 이하의 설명에서는, 이해를 용이하게 하기 위해, 기본적으로 도 22와 대강 동일 구성 부분은 동일 부호로 써 나타낸다.

- [0305] <3. 2 저주파 노이즈를 저감 가능한 비교기의 기본적인 구성례>

- [0306] [구성의 기본 개념]

- [0307] 도 23은, 본 실시 형태에 관한 저주파 노이즈를 저감 가능한, 아이솔레이터를 갖는 비교기의 기본 개념을 도시하는 도면이다.

- [0308] 도 24는, 도 23의 비교기의 비교레인 아이솔레이터를 갖지 않는 비교기의 기본 개념을 도시하는 도면이다.

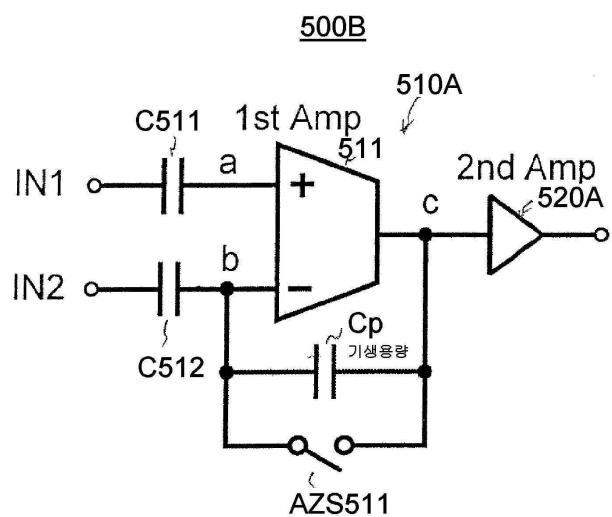

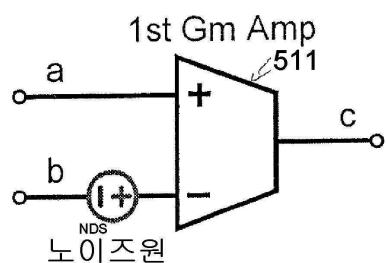

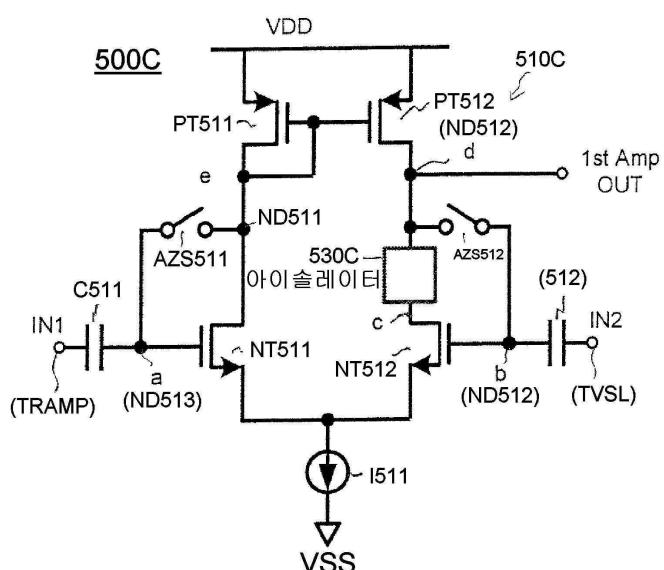

- [0309] 본 실시 형태에 관한 비교기(500A)는, 오토 제로 레벨의 샘플링 용량(C511, C512), 오토 제로 스위치(AZS511), 초단의 트랜스 컨덕턴스(Gm) 앰프(511)를 포함하는 제1 앰프(510A), 및 그것에 계속된 제2 앰프(520A)를 갖는다.

- [0310] 그리고, 본 실시 형태에 관한 비교기(500A)는, 비교례로서 도 24의 비교기(500B)와 달리, 제1 앰프(510A)의 적어도 출력 노드측에 배치되고, 전압 변동을 억제하기 위한 아이솔레이터(530)를 포함하여 구성된다.

- [0311] 또한, 도 23 및 도 24에서, 제1 앰프(510A)의 후단에는 2단째의 제2 앰프만을 나타내고 있지만, 몇단 있어도 좋다.

- [0312] 또한, 제1 앰프(510A)의 일방의 입력측 노드(ND513)를 노드(a)로 하여, 타방의 입력측 노드(ND514)를 노드(b)로 하고, 제1 앰프(510A)의 Gm 앰프(511)의 출력부를 노드(c)로 하고, 제1 앰프(510A)의 출력 노드(ND512)를 노드(d)로 하여 설명한다.

- [0313] 제1 앰프(510A)의 차동 비교부(Gm 앰프)(511)의 출력부의 노드(c)는, 도 22의 비교기(500)에서의 제1 앰프(510)의 NMOS 트랜지스터(NT512)의 드레인 단자측에 상당한다.

- [0314] 아이솔레이터(530)는 초단 Gm 앰프(511)의 출력 노드(c)의 전압을 대진폭(大振幅) 전압 노드(d)로부터 분리하고, 가능한 한 일정하게 유지한다.

- [0315] 오토 제로 스위치(AZS511)는 아이솔레이터(530)의 출력측의 노드(d)와 고임피던스 노드(b) 사이에 접속된다.

- [0316] [슬로프 신호 입력시의 과형]

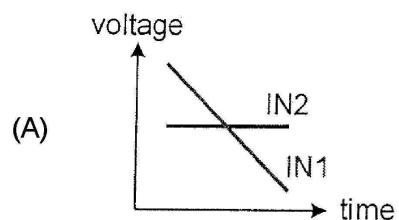

- [0317] 여기서, 비교기의 일방의 입력(IN2)에 고정된 입력 신호를, 타방의 입력(IN1)에 슬로프 신호를 입력한 경우를 고찰한다. 여기서, 슬로프 신호란 RAMP 과형과 같이 신호 레벨이 어느 경사로써 감소 또는 증가하는 신호를 말한다.

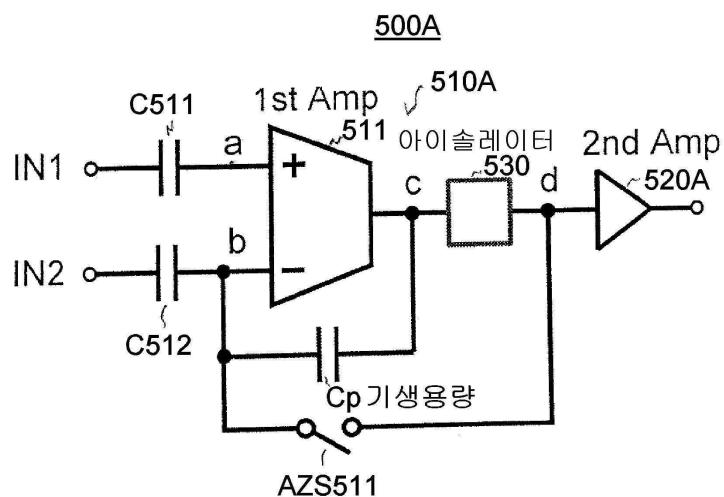

- [0318] 도 25는, 도 23의 본 실시 형태에 관한 비교기의 Gm 앰프의 입력측 노드와 출력측 노드 사이에 기생용량이 있는 예를 도시하는 도면이다.

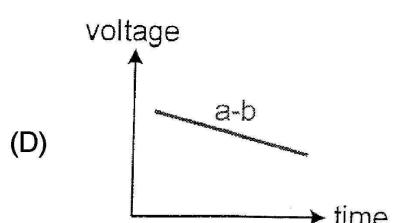

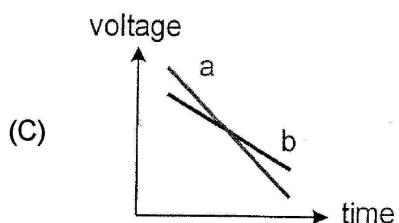

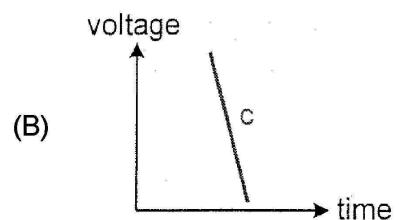

- [0319] 도 26(A) 내지 (D)는, 도 25의 구성례에서의 기생용량과 슬로프 신호 입력시에 각 노드의 과형을 도시하는 도면이다

- [0320] 도 27은, 도 24의 비교례로서의 Gm 앰프의 입력측 노드와 출력측 노드 사이에 기생용량이 있는 예를 도시하는 도면이다.

- [0321] 도 28(A) 내지 (D)는, 도 27의 구성례에서의 기생용량과 슬로프 신호 입력시에 각 노드의 파형을 도시하는 도면이다.

- [0322] 본 실시 형태에 관한 비교기(500A)의 일방의 입력(IN2)에 고정된 입력 신호를, 타방의 입력(IN1)에 슬로프 신호를 입력한 경우, 노드(d)는 도 26(B)에 도시하는 바와 같이, 입력 슬로프 신호와 비교하여 매우 큰 구배의 슬로프 파형이 된다.

- [0323] 그러나, 아이솔레이터(530)에 의해 초단 Gm 앰프(511)의 출력 노드(c)의 전압은 일정하게 유지된다.

- [0324] 따라서 노드(b)- 노드(c) 사이에 기생용량(Cp)이 존재하였다고 하여도, 노드(b)는, 도 26(C)에 도시하는 바와 같이, 외란을 받는 일 없이 일정 전압으로 유지된다.

- [0325] 따라서, 비교기(500A)의 초단 Gm 앰프(511)의 차동 입력 신호(a-b)에는, 도 26(D)에 도시하는 바와 같이, 입력 경사(IN1)가 그대로 전파된다.

- [0326] 한편, 비교례의 비교기(500B)의 구성에서는, 도 28(B)에 도시하는 바와 같이, 노드(c)가 매우 큰 구배의 슬로프 파형이 된다.

- [0327] 이 때문에, 노드(b)- 노드(c) 사이의 기생용량(Cp)을 통하여 그 경사가 노드(b)에 주입된다(도 7).

- [0328] 이 결과로서, 비교기(500B)의 초단 Gm 앰프의 차동 입력 신호(a-b)의 경사는, 도 28(D)에 도시하는 바와 같이, 입력 경사(IN1)와 비교하여 구배가 대폭적으로 저감하는 것으로 된다.

- [0329] [노이즈 저감]

- [0330] 다음에, 노이즈 저감에 관해 고찰한다.

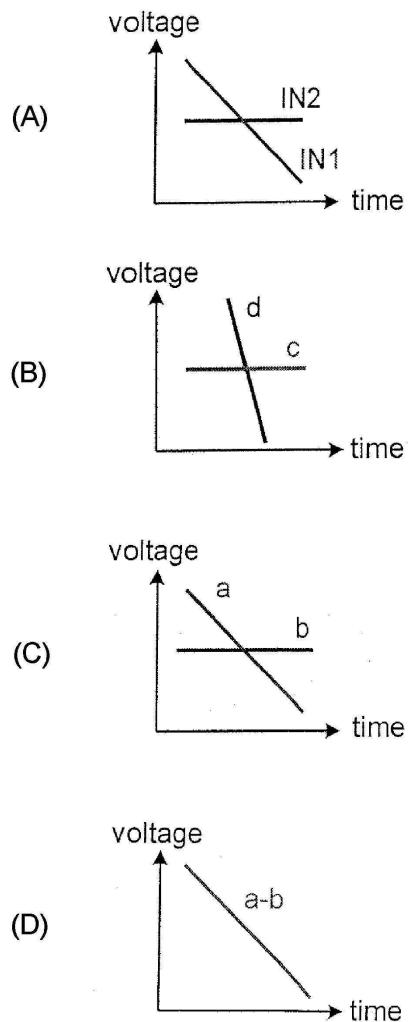

- [0331] 도 29는, 비교기의 초단 Gm 앰프의 노이즈원에 관해 설명하기 위한 도면이다.

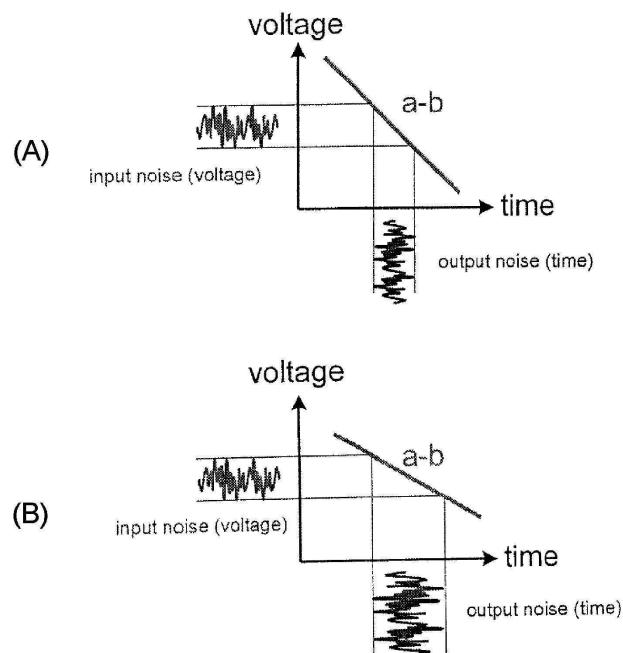

- [0332] 도 30(A) 및 (B)는, 전압 노이즈의 시간 노이즈의 변환례를 도시하는 도면이다.

- [0333] 비교기(500A, 500B)의 초단 Gm 앰프(511)에는 입력 환산된 일정한 노이즈원이 존재하고, 도 29에 도시하는 바와 같이, 이 노이즈원은 입력 환산된 노이즈원(NOS)으로서 기술할 수 있다.

- [0334] 비교기(500A, 500B)의 일방의 입력(IN2)에 고정된 입력 신호를, 타방의 입력(IN1)에 슬로프 신호(파형)를 입력한 경우, 상기한 전압 노이즈는, 도 30(A), (B)에 도시하는 바와 같이 변환된다.

- [0335] 즉, 초단 Gm 앰프(511)의 차동 입력 신호(a-b)의 경사 구배를 변환 개인으로 하여 시간축의 노이즈(이른바 지타)로 변환된다.

- [0336] 따라서 차동 입력 신호(a-b)의 경사 구배가 감쇠하면, 비교기(500A, 500B)의 출력 노이즈는 증대한다.

- [0337] 이미 기술한 바와 같이, 본 구성의 비교기(500A)에서는, 도 30(A)에 도시하는 바와 같이, 이 경사 구배의 감쇠를 저감한다. 이 결과로서 비교기(500A)의 출력 노이즈가 저감된다.

- [0338] 또한, 차동 입력 신호(a-b)의 경사 구배가 커지면, 비교기(500A)의 초단 Gm 앰프(511)의 동작이 빨라진다.

- [0339] 즉, 비교기(500A)의 대역도 오르기 때문에, 열 노이즈와 같이 고주파에 까지 미치는 노이즈에 관해서는 차동 입력 신호(a-b)의 경사 구배의 증대에 의한 기여는 정비례보다도 작아진다.

- [0340] 그 한편, 플리커 노이즈나 RTS일 것인 저주파의 노이즈에 관해서는 차동 입력 신호(a-b)의 경사 구배의 증대에 의한 기여는 정비례에 가까워진다. 즉, 그와 같은 저주파 노이즈의 저감에 관해 본 기술은 특히 유효하다.

- [0341] <3. 3 저주파 노이즈를 저감 가능한 비교기의 구체적인 회로 구성례>

- [0342] [제1의 회로 구성례]

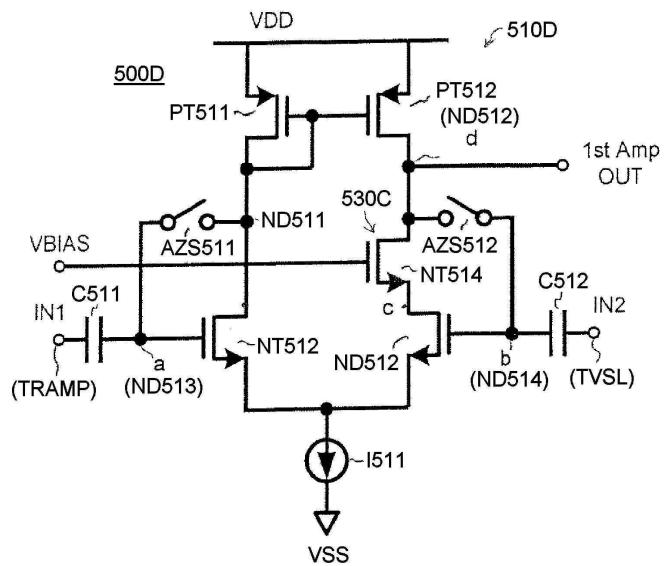

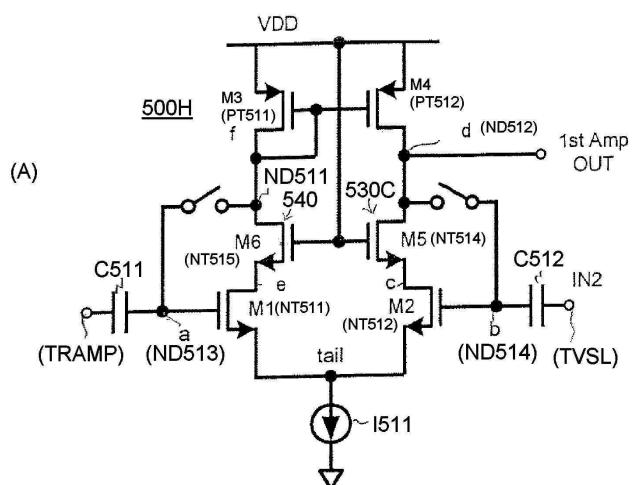

- [0343] 도 31은, 본 실시 형태에 관한 저주파 노이즈를 저감 가능한 비교기의 제1의 회로 구성례를 도시하는 도면이다.

- [0344] 도 31의 비교기(500C)는, 도 22의 비교기(500)의 제1 앰프(510)에서, 출력 노드(ND512)와 NMOS 차동쌍(Gm 앰프)을 형성하는 NMOS 트랜지스터(NT512)의 드레인 단자(출력 단자)측과의 사이에 아이솔레이터(530C)가 배치

되어 있다.

[0345] 또한, 도 31에서는, 도 22의 오토 제로 스위치로서 PMOS 트랜지스터(PT513, PT514)를 오토 제로 스위치(AZS511, AZS512)로서 나타내고, NMOS 트랜지스터(NT513)를 전류원(I511)으로서 나타내고 있다.

[0346] 도 25에서 도시한 기생용량(C<sub>p</sub>)은, 이 도 31의 비교기(500C)의 경우에는, 주로 NMOS 차동쌍의 NMOS 트랜지스터(NT512)의 게이트·드레인 사이 용량(C<sub>gd</sub>) 및 각각의 금속 배선 사이에 생기는 기생용량에 의해 형성된다.

[제2의 회로 구성례]

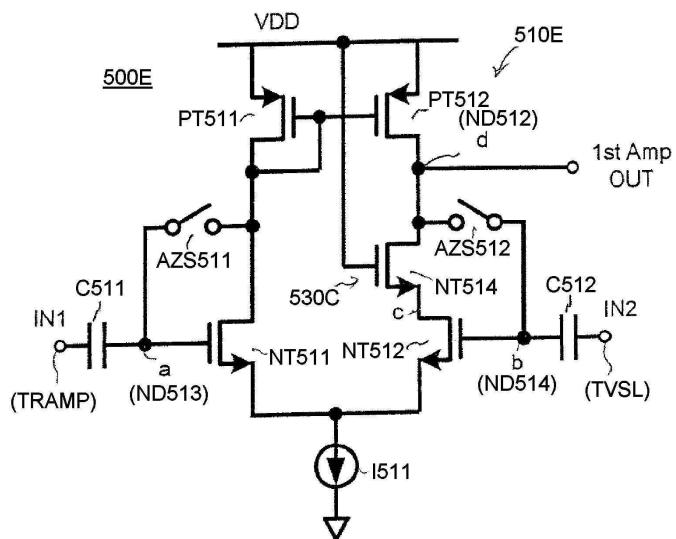

[0348] 도 32는, 본 실시 형태에 관한 저주파 노이즈를 저감 가능한 비교기의 제2의 회로 구성례를 도시하는 도면이다.

[0349] 도 32의 비교기(500D)는, 도 31의 비교기(500C)의 아이솔레이터(530C)가 NMOS 트랜지스터(NT514)에 의해 형성되어 있다.

[0350] NMOS 트랜지스터(NT514)의 드레인이 제1 앰프(510D)의 출력 노드(ND512)(d)에 접속되고, 소스가 G<sub>m</sub> 앰프를 형성하는 NMOS 트랜지스터(NT512)의 드레인(노드(c))에 접속되어 있다.

[0351] 그리고, 도 32의 비교기(500D)에서는, 아이솔레이터(530C)를 형성하는 NMOS 트랜지스터(NT514)의 게이트가 바이어스 전압(VBIAS)의 공급 라인에 접속되어 있다.

[0352] 이에 의해, NMOS 트랜지스터(NT514)를 통하여 일정 전류가 흐름에 의해, NMOS 트랜지스터(NT512)의 게이트(입력 노드(b))와 드레인(출력 노드(c)) 사이에 기생용량이 있었다고 하여도 전압 변동이 억제되고, 저주파 노이즈가 저감된다.

[0353] 또한, 아이솔레이션에 이용하는 트랜지스터는 차동쌍의 트랜지스터와 동일 종류의 것으로 한되지 않는다.

[제3의 회로 구성례]

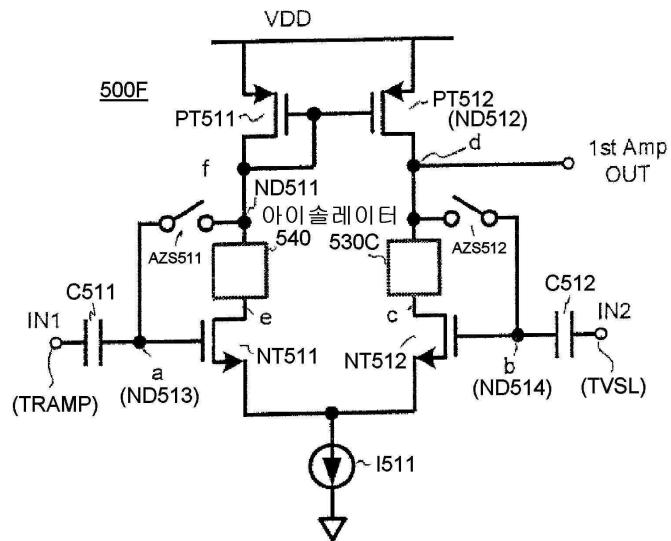

[0355] 도 33은, 본 실시 형태에 관한 저주파 노이즈를 저감 가능한 비교기의 제3의 회로 구성례를 도시하는 도면이다.

[0356] 도 33의 비교기(500E)가 도 32의 비교기(500D)와 다른 점은, 아이솔레이터(530C)의 NMOS 트랜지스터(NT514)의 게이트가 바이어스 전압(VBIAS)의 공급 라인 대신에 전원 전압원(VDD)에 접속되어 있는 것에 있다.

[0357] 도 32의 비교기(500D)에서는, NMOS 트랜지스터(NT514)를 동작시키기 위해, 별개의 바이어스 전압(VBIAS)을 필요로 한다.

[0358] 예를 들면, CMOS 이미지 센서 등의 용도에 대해, 칼럼 병렬 싱글 슬로프 AD 변환기로서 이용하는 경우, 이 바이어스 전압(VBIAS)의 필요성은 이하의 (1) 내지 (3) 등에 나타내는 점이 우려된다.

[0359] (1) 칼럼 사이의 간섭, (2) VBIAS 배선 영역의 증대, (3) VBIAS 생성 회로의 필요성, 등이다.

[0360] 이에 대해, NMOS 트랜지스터(NT514)의 게이트를 전원 전압원(VDD)에 접속하는 도 33의 비교기(500E)에서는 이와 같은 우려가 없어서, 칼럼 병렬 싱글 슬로프 AD 변환기의 실현에 특히 적합하다.

[제4의 회로 구성례]

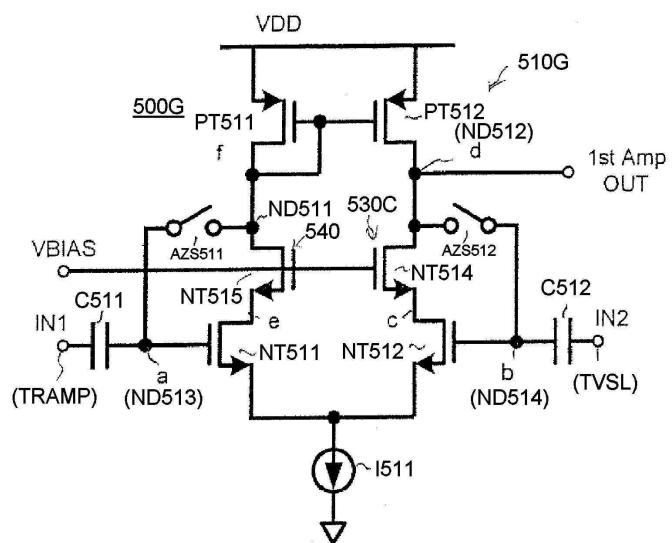

[0362] 도 34는, 본 실시 형태에 관한 저주파 노이즈를 저감 가능한 비교기의 제4의 회로 구성례를 도시하는 도면이다.

[0363] 도 34의 비교기(500F)가 도 31의 비교기(500C)와 다른 점은, 다음과 같다.

[0364] 비교기(500F)는, 부하측 노드(ND511)(노드(f))와 NMOS 차동쌍(G<sub>m</sub> 앰프)을 형성하는 NMOS 트랜지스터(NT511)의 드레인 단자(노드(e))측과의 사이에 제2의 아이솔레이터(540)가 또한 배치되어 있다.

[0365] 노드(e)는 PMOS 부하가 다이오드 접속이 되어 있고 임피던스가 작다, 즉 노드(e)는 대부분 일정 전압으로 유지되기 때문에 아이솔레이션의 기여는 작다.

[0366] 고로 노드(e)에 관해서는 아이솔레이션을 실시하여도 하지 않아도 좋다.

[0367] 단, 도 34의 비교기(500F)에서는, 회로의 대칭성이 높기 때문에, 오토 제로 기능을 갖는 비교기(500F)에서는 보다 정밀도가 높은 비교 동작을 실현하는 것이 가능해진다.

[제5의 회로 구성례]

[0369] 도 35는, 본 실시 형태에 관한 저주파 노이즈를 저감 가능한 비교기의 제5의 회로 구성례를 도시하는 도면이다.

- [0370] 도 35의 비교기(500G)는, 도 34의 비교기(500F)의 아이솔레이터(540)가 NMOS 트랜지스터(NT515)에 의해 형성되어 있다.

- [0371] NMOS 트랜지스터(NT515)의 드레인이 제1 앰프(510G)의 부하측 노드(ND511)(노드(f))에 접속되고, 소스가 Gm 앰프를 형성하는 NMOS 트랜지스터(NT511)의 드레인(노드(e))에 접속되어 있다.

- [0372] 그리고, 도 35의 비교기(500G)에서는, 아이솔레이터(530C)를 형성하는 NMOS 트랜지스터(NT514)의 게이트 및 아이솔레이터(540)를 형성하는 NMOS 트랜지스터(NT515)의 게이트가 바이어스 전압(VBIAS)의 공급 라인에 접속되어 있다.

- [0373] 이에 의해, NMOS 트랜지스터(NT514)를 통하여 일정 전류가 흐름에 의해, NMOS 트랜지스터(NT512)의 게이트(입력 노드(b))와 드레인(출력 노드(c))사이에 기생용량이 있었다고 하여도 전압 변동이 억제되고, 저주파 노이즈가 저감된다.

- [0374] 마찬가지로, NMOS 트랜지스터(NT515)를 통하여 일정 전류가 흐름에 의해, NMOS 트랜지스터(NT511)의 게이트(입력 노드(a))와 드레인(출력 노드(e))사이에 기생용량이 있었다고 하여도 전압 변동이 억제되고, 저주파 노이즈가 저감된다.

- [0375] 이 경우도, 아이솔레이션에 이용한 트랜지스터는 차동쌍의 트랜지스터와 동일 종류의 것으로 한되지 않는다.

- [0376] [제6의 회로 구성례]

- [0377] 도 36은, 본 실시 형태에 관한 저주파 노이즈를 저감 가능한 비교기의 제6의 회로 구성례를 도시하는 도면이다.

- [0378] 도 36의 비교기(500H)가 도 35의 비교기(500G)와 다른 점은, 다음과 같다.

- [0379] 비교기(500H)에서는, 아이솔레이터(530C)의 NMOS 트랜지스터(NT514)의 게이트 및 아이솔레이터(540)를 형성하는 NMOS 트랜지스터(NT515)의 게이트가 바이어스 전압(VBIAS)의 공급 라인 대신에 전원 전압원(VDD)에 접속되어 있다.

- [0380] 도 35의 비교기(500G)에서는, NMOS 트랜지스터(NT514, NT515)를 동작시키기 위해, 별개의 바이어스 전압(VBIA S)을 필요로 한다.

- [0381] 예를 들면, 제3의 회로 구성 예의 경우와 마찬가지로, CMOS 이미지 센서 등의 용도에 대해, 칼럼 병렬 싱글 슬로프 AD 변환기로서 이용한 경우, 이 바이어스 전압(VBIAS)의 필요성은 이하의 (1) 내지 (3) 등에 나타내는 점이 우려된다.

- [0382] (1) 칼럼 사이의 간섭, (2) VBIAS 배선 영역의 증대, (3) VBIAS 생성 회로의 필요성, 등이 있다.

- [0383] 이에 대해, NMOS 트랜지스터(NT514, NT515)의 게이트를 전원 전압원(VDD)에 접속한 도 36의 비교기(500H)에서는 이와 같은 우려가 없어서, 칼럼 병렬 싱글 슬로프 AD 변환기의 실현에 특히 적합하다.

- [0384] [효과적인 실장례]

- [0385] 여기서, 본 실시 형태에 관한 저주파 노이즈를 저감 가능한 비교기의 효과적인 실장례에 관해 설명한다.

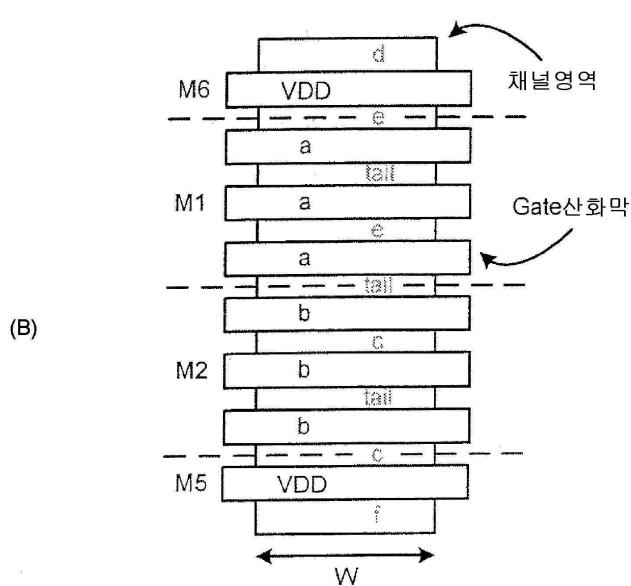

- [0386] 도 37(A) 및 (B)는, 본 실시 형태에 관한 저주파 노이즈를 저감 가능한 비교기의 효과적인 실장례에 관해 설명하기 위한 도면이다.

- [0387] 이 실장례는, 도 37(A)에 도시하는 바와 같이, 대칭성이 높은 도 36의 비교기(500H)에 관한 예이다.

- [0388] 도 37에서, NMOS 차동쌍 트랜지스터(NT511, NT512)를 M1, M2로 나타내고, 아이솔레이션용 트랜지스터(NT514, NT515)를 M5, M6로 나타내고 있다.

- [0389] 차동쌍 트랜지스터(M1, M2)의 채널 폭(W)과 아이솔레이션용 트랜지스터(M5, M6)의 채널 폭(W)을 일치시킨다. 또한, 차동쌍 트랜지스터(M1, M2)의 핑거(finger)수를 각각 홀수로 함으로써, 아이솔레이션용 트랜지스터(M5, M6)와 차동쌍 트랜지스터(M1, M6)는 채널 영역을 공통화할 수 있다.

- [0390] 이 결과, 차동쌍 트랜지스터(M1, M2)는 양단의 채널 영역이 자연스럽게 확장된다.

- [0391] 이와 같은 실장 방법에 의해 플리커 노이즈나 RTS 노이즈 등의 저주파 노이즈가 개선되는 것이 알려져 있다(비 특허 문헌 1).

- [0392] 따라서 이와 같이 본 기술을 실장함에 의해, 저주파 노이즈는 상기한 2개의 메커니즘(회로 동작과 프로세스 특성)에 의해 개선할 수 있다.

- [0393] [비]특허 문헌 1]

- [0394] "Impact of STA Effect on Flicker Noise in 0.13um RF nMOSFETs" IEEE TRANSACTIONS ON ELECTRON DEVICES, VOL. 54, NO. 12, DECEMBER 2007, pp. 3383-3392.

- [0395] 이상 설명한 바와 같이, 본 실시 형태에 의하면, 이하의 효과를 얻을 수 있다.

- [0396] 본 기술에 의해, 전송하는 신호에 오차를 발생시키는 일 없이, 기존의 적층 구조와 비하여 TCV의 갯수를 저감하는 것이 가능해진다. 또한, 아날로그 칩상에 양자화기(비교기) 등의 회로가 불필요하게 된다. 이 때문에, 아날로그 칩의 면적을 센서만으로 정하여지는 면적까지 작게 할 수 있다.

- [0397] 예를 들면, 이미지 센서에서 센서(화소)의 면적은, 시스템의 광학 사이즈로부터 결정되어 있기 때문에, 일반적으로 아날로그 칩을 최소화할 수 있는 거의 한계까지 작게 할 수 있는 것을 의미한다.

- [0398] 아날로그 칩은 전술한 바와 같이, 로직 칩(디지털 칩)과 비교하여 공정수가 많기 때문에, 예를 들어 칩의 면적이 동일하였다고 하여도 비용이 높아진다.

- [0399] 또한, 본 기술에 의해 아날로그 칩상에 배치한 회로를 센서에 관한 부분으로 한정할 수 있기 때문에, 배선이나 트랜지스터 제조에 관한 공정을 줄이는 것이 가능해진다. 일반적으로 비교기 등의 회로를 제작하기 위한 트랜지스터와, 센서를 구성하기 위한 트랜지스터는 공통이 아닌 것을 포함하는 공정에서 제조되고 있다. 따라서 비교기 등의 회로가 없어짐으로써, 이들의 공정을省略할 수 있다.

- [0400] 마찬가지로, 아날로그 칩상에 복잡한 배선을 배치할 필요가 없어지기 때문에, 배선의 총수를 삭감할 수 있다.

- [0401] 상기 2개의 이유로부터 본 기술에 의해, 센서로부터 출력되는 신호를 열화시키는 일 없이, 반도체 장치의 비용을 대폭적으로 저감하는 것이 가능해진다.

- [0402] 또한, 상술한 바와 같이, 본 실시 형태에 관한 비교기(500C 내지 500H)는, 캐스코드 트랜지스터를 이용하여 노이즈를 저감하는 구성을 갖는다.

- [0403] 이들의 구성을, 슬로프 신호, 예를 들면 램프 신호와 비교를 행하는 경우에, 출력 노드와 입력 노드의 커플링에 의해, 실효적인 입력 신호 진폭이 감쇠하여 버리는 것을 회피함에 의해, 비교기의 입력 환산 노이즈의 저감을 실현할 수 있다.

- [0404] 이와 같이, 오토 제로 기능 부착의 비교기 및 그것을 이용한 싱글 슬로프 AD 변환기나 고체 활상 장치에서 잡음, 특히 플리커 노이즈나 RTS 노이즈와 같은 저주파 잡음을 저감하는 것이 가능해진다.

- [0405] 또한, 이와 같은 특징을 갖는 비교기는, 도 9의 적층 구조의 디지털 칩인 제2칩에 적용한 경우에 노이즈 저감의 효과는 크다.

- [0406] 단, 아날로그 칩인 제1칩측에 비교기를 탑재한 경우, 적층 구조가 아닌 회로 구성의 경우에도, 노이즈 저감의 효과는 크다.

- [0407] 그리고, 상술한 바와 같이, 오토 제로 기능 부착의 비교기를 이용한 싱글 슬로프 AD 변환기나 고체 활상 장치에서 잡음, 특히 플리커 노이즈나 RTS 노이즈와 같은 저주파 잡음을 저감하는 것이 가능해진다.

- [0408] 또한, 본 실시 형태에서는, 반도체 장치의 한 예로서 CMOS 이미지 센서의 구성을 관해 설명하였지만, 상기 구성을 예를 들면 이면 조사형 CMOS 이미지 센서에 적용할 수 있고, 상기 각 효과를 발현하는 것이 가능하다. 단, 표면 조사형이라도 충분히 상기 각 효과를 발현하는 것이 가능하다.

- [0409] 이와 같은 구성을 갖는 고체 활상 장치는, 디지털 카메라나 비디오 카메라의 활상 디바이스로서 적용할 수 있다.

- [0410] <4. 카메라 시스템의 구성례>

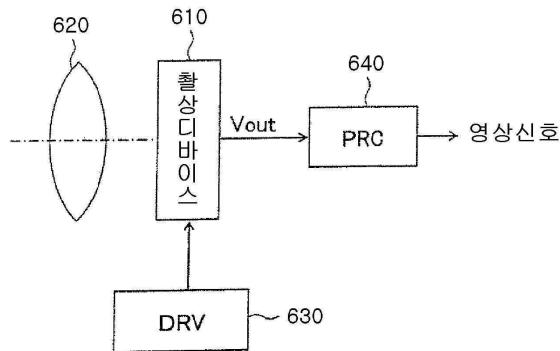

- [0411] 도 38은, 본 실시 형태에 관한 고체 활상 장치가 적용된 카메라 시스템의 구성의 한 예를 도시하는 도면이다.

- [0412] 본 카메라 시스템(600)은, 도 38에 도시하는 바와 같이, 본 실시 형태에 관한 CMOS 이미지 센서(고체 활상 장치)(200, 300, 300A 내지 300C)가 적용 가능한 활상 디바이스(610)를 갖는다.

- [0413] 또한, 카메라 시스템(600)은, 이 활상 디바이스(610)의 화소 영역에 입사광을 유도하는(파사체상을 결상하는) 광학계, 예를 들면 입사광(상광)을 활상면상에 결상시키는 렌즈(6200)을 갖는다.

- [0414] 카메라 시스템(600)은, 활상 디바이스(610)를 구동하는 구동 회로(DRV)(630)와, 활상 디바이스(610)의 출력 신호를 처리하는 신호 처리 회로(PRC)(640)를 갖는다.

- [0415] 구동 회로(630)는, 활상 디바이스(610) 내의 회로를 구동하는 스타트 펄스나 클록 펄스를 포함하는 각종의 타이밍 신호를 생성하는 타이밍 제너레이터(도시 생략)를 가지며, 소정의 타이밍 신호로 활상 디바이스(610)를 구동한다.

- [0416] 또한, 신호 처리 회로(640)는, 활상 디바이스(610)의 출력 신호에 대해 소정의 신호 처리를 시행한다.

- [0417] 신호 처리 회로(640)에서 처리된 화상 신호는, 예를 들면 메모리 등의 기록 매체에 기록된다. 기록 매체에 기록된 화상 정보는, 프린터 등에 의해 하드 카피 된다. 또한, 신호 처리 회로(640)에서 처리된 화상 신호를 액정 디스플레이 등으로 이루어지는 모니터에 동화로서 투영된다.

- [0418] 상술한 바와 같이, 디지털 카메라 등의 활상 장치에서, 활상 디바이스(610)로서, 선술한 고체 활상 장치(200, 300, 300A 내지 300C)를 탑재함으로써, 고정밀한 카메라가 실현할 수 있다.

- [0419] 또한, 본 기술은 이하와 같은 구성을 취할 수 있다.

- [0420] (1) 어레이형상으로 배치된 복수의 센서를 갖는 제1칩과,

- [0421] 제2칩을 가지며,

- [0422] 상기 제1칩과 상기 제2칩은 접합된 적층 구조를 가지며,

- [0423] 상기 제1칩과 상기 제2칩 사이의 배선은,

- [0424] 비어를 통하여 접속되고,

- [0425] 상기 제1칩은,

- [0426] 각 센서에서 발생한 아날로그 신호를 시간이산화한 신호가, 대응하는 상기 비어를 통하여 제2칩에 전송되고,

- [0427] 상기 제2칩은,

- [0428] 상기 비어를 통한 상기 제1칩부터 전송된 신호를 상기 제1칩에서 샘플링한 타이밍과는 다른 타이밍에서 샘플링하는 기능과,

- [0429] 양자화하여 디지털 신호를 얻는 기능을 포함하는

- [0430] 반도체 장치.

- [0431] (2) 상기 제2칩은,

- [0432] 상기 비어를 통한 상기 제1칩부터의 신호를 상기 제1칩에서 샘플링한 타이밍과는 다른 타이밍에서 샘플링하고, 당해 샘플링한 신호를 양자화하여 디지털 신호를 얻는

- [0433] 상기 (1)에 기재된 반도체 장치.

- [0434] (3) 상기 제2칩은,

- [0435] 시간연속의 양자화기를 포함하고,

- [0436] 상기 비어를 통한 상기 제1칩부터의 신호를 상기 양자화기에서 양자화한 신호를, 상기 제1칩에서 샘플링한 타이밍과는 다른 타이밍에서 샘플링하는

- [0437] 상기 (1)에 기재된 반도체 장치.

- [0438] (4) 상기 제2칩은,

- [0439] 상기 비어를 통한 상기 제1칩부터의 신호와 램프 신호를 비교 판정하고, 그 판정 신호를 출력하는 비교기와,

- [0440] 상기 비교기의 출력에 의해 동작이 제어되고, 상기 비교기의 비교 시간을 카운트함에 의해 양자화를 행하는 카운터를 포함하는

- [0441] 상기 (1)에 기재된 반도체 장치.

- [0442] (5) 상기 제1칩과 상기 제2칩 사이에서, 아날로그 신호를 전송하는 비어와 디지털 신호를 전송하는 비어가 각각 집중하여 배치되고, 또한 아날로그 신호를 전송하는 비어와 디지털 신호를 전송하는 비어가 분리하여 배치되어 있는

- [0443] 상기 (1)부터 (4)의 어느 하나에 기재된 반도체 장치.

- [0444] (6) 광전 변환을 행하는 복수의 화소가 행렬형상으로 배열된 화소 어레이부와,

- [0445] 상기 화소 어레이부로부터 복수의 화소 단위로 시간이산화한 화소 신호의 판독을 행하는 화소 신호 판독부를 가지며,

- [0446] 상기 화소 신호 판독부는,

- [0447] 화소의 열 배열에 대응하여 배치되고, 판독 신호 전위와 램프 신호를 비교 판정하고, 그 판정 신호를 출력하는 복수의 비교기와,

- [0448] 상기 비교기의 출력에 의해 동작이 제어되고, 대응하는 상기 비교기의 비교 시간을 카운트함에 의해 양자화하는 복수의 카운터와,

- [0449] 제1칩과,

- [0450] 제2칩을 가지며,

- [0451] 상기 제1칩과 상기 제2칩은 접합된 적층 구조를 가지며,

- [0452] 상기 제1칩은,

- [0453] 상기 화소 어레이부 및 시간이산화한 아날로그 화소 신호를 전송하는 신호선이 배치되고,

- [0454] 상기 제2칩은,

- [0455] 상기 화소 신호 판독부가 배치되고,

- [0456] 상기 제1칩과 상기 제2칩 사이의 배선은,

- [0457] 비어를 통하여 접속되어 있는

- [0458] 고체 콜상 장치.

- [0459] (7) 상기 제1칩과 상기 제2칩 사이에서, 아날로그 신호를 전송하는 비어와 디지털 신호를 전송하는 비어가 각각 집중하여 배치되고, 또한 아날로그 신호를 전송하는 비어와 디지털 신호를 전송하는 비어가 분리하여 배치되어 있는

- [0460] 상기 (6)에 기재된 고체 콜상 장치.

- [0461] (8) 고체 콜상 장치와,

- [0462] 상기 고체 콜상 장치에 피사체상을 결상하는 광학계를 가지며,

- [0463] 상기 고체 콜상 장치는,

- [0464] 광전 변환을 행하는 복수의 화소가 행렬형상으로 배열된 화소 어레이부와,

- [0465] 상기 화소 어레이부로부터 복수의 화소 단위로 시간이산화한 화소 신호의 판독을 행하는 화소 신호 판독부를 가지며,

- [0466] 상기 화소 신호 판독부는,

- [0467] 화소의 열 배열에 대응하여 배치되고, 판독 신호 전위와 램프 신호를 비교 판정하고, 그 판정 신호를 출력하는 복수의 비교기와,

- [0468] 상기 비교기의 출력에 의해 동작이 제어되고, 대응하는 상기 비교기의 비교 시간을 카운트함에 의해 양자화하는 복수의 카운터와,

- [0469] 제1칩과,

- [0470] 제2칩을 가지며,

- [0471] 상기 제1칩과 상기 제2칩은 접합된 적층 구조를 가지며,

- [0472] 상기 제1칩은,

- [0473] 상기 화소 어레이부 및 시간이산화한 아날로그 화소 신호를 전송하는 신호선이 배치되고,

- [0474] 상기 제2칩은,

- [0475] 상기 화소 신호 판독부가 배치되고,

- [0476] 상기 제1칩과 상기 제2칩 사이의 배선은,

- [0477] 상기 비어를 통하여 접속되어 있는

- [0478] 카메라 시스템.

- [0479] (9) 상기 제1칩과 상기 제2칩 사이에서, 아날로그 신호를 전송하는 비어와 디지털 신호를 전송하는 비어가 각각 집중하여 배치되고, 또한 아날로그 신호를 전송하는 비어와 디지털 신호를 전송하는 비어가 분리하여 배치되어 있는

- [0480] 상기 (8)에 기재된 카메라 시스템.

### **부호의 설명**

- [0481] 100, 100A 내지 100G : 반도체 장치

- 110, 110A 내지 110G : 제1칩(아날로그 칩)

- 111(-0, -1, ...) : 센서

- 112(-0, -1, ...) : 샘플 홀드(SH) 회로

- 113(-0, -1, ...) : 앰프

- 114(-0, -1, ...) : TCV(비어)

- 115(-0, -1, ...) : 샘플링 스위치

- 120, 120A 내지 120G : 제2칩(로직 칩, 디지털 칩)

- 121(-0, -1, ...) : 샘플링 스위치

- 122(-0, -1, ...) : 양자화기

- 123 : 신호 처리 회로

- 124(-0, -1, ...) : 비교기

- 125(-0, -1, ...) : 카운터

- 200 : 고체 콜상 장치

- 210 : 화소 어레이부

- 220 : 행 선택 회로

- 230 : 칼럼 판독 회로

- 300, 300A 내지 300C : 고체 콜상 장치

- 310 : 화소 어레이부

- 320 : 행 선택 회로

- 330 : 수평 전송 주사 회로

- 340 : 타이밍 제어 회로

350 : ADC군

360 : DAC(램프 신호 발생기)

370 : 앰프 회로(S/A)

380 : 신호 처리 회로

390 : 수평 전송선

410, 420 : 디지털 신호 TCV 배치 영역

430 : 아날로그 신호 TCV 배치 영역

500, 500A 내지 500H : 비교기

510, 510A 내지 510C : 제1 앰프

511 : Gm 앰프

520 : 제2 앰프

530, 530C : 아이솔레이터(제1의 아이솔레이터)

540 : 아이솔레이터(제2의 아이솔레이터)

600 : 카메라 시스템

610 : 촬상 디바이스

620 : 렌즈

630 : 구동 회로

640 : 신호 처리 회로

## 도면

### 도면1

## 도면2

## 도면3

## 도면4

도면5

## 도면6

21

## 도면7

40

## 도면8

도면9

도면10

도면11

도면12

도면13

도면14

도면15

## 도면16

110A

도면17

도면18

## 도면19

도면20

도면21

도면22

도면23

도면24

도면25

## 도면26

## 도면27

## 도면28

## 도면29

## 도면30

## 도면31

도면32

도면33

도면34

도면35

## 도면36

도면37

도면38

600