(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第4583694号

(P4583694)

(45) 発行日 平成22年11月17日(2010.11.17)

(24) 登録日 平成22年9月10日(2010.9.10)

(51) Int.Cl.

HO3M 1/44 (2006.01)

F 1

HO3M 1/44

請求項の数 12 (全 20 頁)

(21) 出願番号 特願2001-560540 (P2001-560540)

(86) (22) 出願日 平成12年8月25日 (2000.8.25)

(65) 公表番号 特表2003-523679 (P2003-523679A)

(43) 公表日 平成15年8月5日 (2003.8.5)

(86) 國際出願番号 PCT/US2000/023456

(87) 國際公開番号 WO2001/061860

(87) 國際公開日 平成13年8月23日 (2001.8.23)

審査請求日 平成19年7月25日 (2007.7.25)

(31) 優先権主張番号 09/506,037

(32) 優先日 平成12年2月17日 (2000.2.17)

(33) 優先権主張国 米国(US)

(73) 特許権者 591016172

アドバンスト・マイクロ・ディバイシズ・

インコーポレイテッド

ADVANCED MICRO DEVI

CES INCORPORATED

アメリカ合衆国、94088-3453

カリフォルニア州、サンディベイル、ビイ・

オウ・ボックス・3453、ワン・エイ・

エム・ディ・プレイス、メイル・ストップ

・68 (番地なし)

(74) 代理人 100064746

弁理士 深見 久郎

(74) 代理人 100085132

弁理士 森田 俊雄

最終頁に続く

(54) 【発明の名称】パイプラインアナログ-デジタル(A/D)変換器のためのデジタル論理訂正回路

## (57) 【特許請求の範囲】

## 【請求項1】

パイプラインアナログ-デジタル(A/D)変換器のためのデジタル論理訂正(DLC)回路であって、A/D変換器は複数のステージを有し、各ステージは少なくとも1対のデジタル出力ビットを生成し、そこからアナログ入力信号のデジタル表現を得ることができ、DLC回路は、

加算器を含み、加算器は複数の入力および出力を有し、前記DLC回路はさらに、複数のデジタル遅延セットを含み、各デジタル遅延セットは少なくとも1つのデジタル遅延を含み、デジタル遅延セットの入力は対応するデジタル出力ビットを受取り、遅延セットの出力は、遅延されたデジタル出力ビットをそれぞれの加算器入力に提供し、前記DLC回路はさらに、

クロックジェネレータを含み、クロックジェネレータは、DLC回路にクロック信号を提供してデータ有効周期の間に加算器入力で各デジタル遅延セットの出力の到着を同期させ、

1次クロック信号は、1つおきのステージのためのデジタル遅延セットに与えられ、2次クロック信号は残りのデジタル遅延セットに与えられ、1次クロック信号と2次クロック信号とのタイミングは、それぞれのデジタル遅延セットを介して各ステージのデジタル出力ビットを遅延してデジタル出力ビットをデータ有効周期の間に加算器入力に到着させ、加算器が加算器出力でアナログ入力信号のデジタル表現を生成するのに有効である、デジタル論理訂正(DLC)回路。

10

20

**【請求項 2】**

1 次クロック信号と 2 次クロック信号とは、2 相の重なり合わないクロックを形成する、請求項 1 に記載の D L C 回路。

**【請求項 3】**

各遅延セットに与えられるクロック信号は、遅延セットによって遅延されているデジタル出力ビットをラッチするために用いられる 2 相の重なり合わないクロックの逆位相である、請求項 2 に記載の D L C 回路。

**【請求項 4】**

1 次クロック信号のパルスおよび 2 次クロック信号のパルスは、ほぼ同じ長さを有する

、請求項 2 に記載の D L C 回路。

10

**【請求項 5】**

各遅延は遅延に与えられるクロック信号の立上がり端縁上でサンプリングする、請求項 1 に記載の D L C 回路。

**【請求項 6】**

加算器は 1 次クロック信号と同期させられる、請求項 5 に記載の D L C 回路。

**【請求項 7】**

加算器は 1 次クロック信号と同期させられる、請求項 1 に記載の D L C 回路。

**【請求項 8】**

A / D 変換器はサンプルホールドステージを有し、サンプルホールドステージは、アナログ入力信号をサンプリングし、かつホールドし、サンプリングされかつホールドされた信号を出力し、A / D 変換器は第 1 のステージを有し、第 1 のステージは、サンプリングされかつホールドされた信号に基づいて第 1 のデジタル出力を生成し、かつラッチし、アナログ入力信号とデジタル出力のアナログ表現との比較に基づいて残差信号を生成し、A / D 変換器は第 2 のステージを有し、第 2 のステージは、第 1 のステージが生成する残差信号に基づいて第 2 のデジタル出力を生成し、かつラッチする、請求項 1 に記載の D L C 回路。

20

**【請求項 9】**

サンプルホールドステージはアナログ入力信号の ± 2.5 % の許容限界を有する、請求項 8 に記載の D L C 回路。

**【請求項 10】**

30

D L C 回路およびパイプライン A / D 変換器は、データネットワークデバイスのためのフロントエンド回路の一部であり、アナログ入力信号は電話線上で受取られて入ってくるデータ信号である、請求項 8 に記載の D L C 回路。

**【請求項 11】**

アナログ入力信号のデジタル表現でのビットの数は奇数であり、デジタル出力ビットを生成する M の数のステージが存在し、各ステージは B の数のデジタル出力ビットを生成し、遅延の合計数は  $B(1 + M/2)(M/2)$  に等しい、請求項 1 に記載の D L C 回路。

**【請求項 12】**

アナログ入力信号のデジタル表現でのビットの数は偶数であり、デジタル出力ビットを生成する M の数のステージが存在し、各ステージは B の数のデジタル出力ビットを生成し、遅延の合計数は、

40

**【数 1】**

$$B \left( \left( 1 + \frac{M-1}{2} \right) \left( \frac{M-1}{2} \right) + \frac{M+1}{2} \right)$$

に等しい、請求項 1 に記載の D L C 回路。

**【発明の詳細な説明】****【0001】**

50

**【技術分野】**

この発明は一般に、パイプラインアナログ - デジタル (A / D) 変換器に関し、より具体的には、シフトレジスタの数が減じられたパイプライン A / D 変換器デジタル論理訂正回路に関する。

**【0002】****【背景】**

アナログ電圧信号をデジタル表現へと正確に変換するアナログ - デジタル (A / D) 変換器に対する需要が絶えず存在している。より少ない電力を使用し、かつ集積回路上でより小さな面積を占める、より高速の A / D 変換器も必要とされている。

**【0003】**

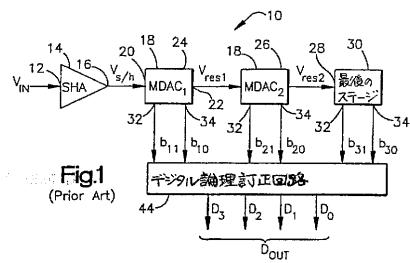

図 1 は、従来のパイプラインアナログ - デジタル (A / D) 変換器 10 を示す。A / D 変換器 10 は、アナログ電気入力信号 ( $V_{IN}$ ) をアナログ信号のデジタル表現 ( $D_{OUT}$ ) へと変換する。示される例は 4 ビット A / D 変換器であるが、変換器ステージの追加または除去とともに、より多くのビットまたはより少ないビットの解像度が実現され得ることが理解されるだろう。したがって、A / D 変換器の解像度は、N ビット A / D 変換器と呼ばれることもあり、N はデジタル出力ビット数を示す。A / D 変換器 10 は、最初のステージ上で提供されるアナログ信号入力 12 を有する。最初のステージは、サンプルホールド増幅器 (SHA) 14 である。SHA 14 は、アナログ入力信号をサンプリングし、パイプライン A / D 変換器 10 の次のステージのために SHA 出力 16 で、サンプリングされた電圧、または  $V_{s/h}$  をホールドする。SHA 14 に続くステージは、複式デジタル - アナログ変換器 (MDAC) 18 である。MDAC 18 ステージがパイプラインに加えられて出力ビット数が増大される。

10

**【0004】**

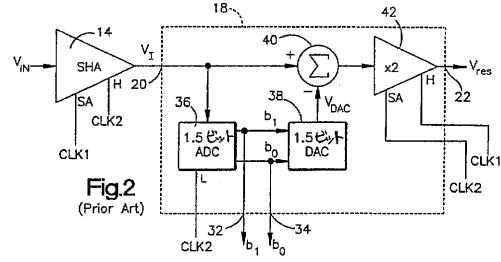

さらに図 2 を参照して、MDAC 18 の各々は、アナログ入力 20 とアナログ出力 22 を有する。各 MDAC 18 は、アナログ入力 20 に与えられる MDAC 入力信号  $V_1$  のアナログからデジタルへの変換を行なう。各 MDAC 18 はまた、増幅された残差信号  $V_{res}$  を計算し、これがアナログ出力 22 で次のステージのために出力される。MDAC 18 ステージの数は、A / D 変換器 10 の所望の解像度によって、または N の値によって、決定される。MDAC 18 ステージの数は N - 2 に等しい。例では、解像度は 4 ビットである。したがって、2 つの MDAC 18 ステージが存在し、それらは MDAC<sub>1</sub> ( 参照番号 24 ) および MDAC<sub>2</sub> ( 参照番号 26 ) と呼ばれる。SHA 出力 16 が MDAC<sub>1</sub> のアナログ入力 20 に接続される。MDAC<sub>1</sub> のアナログ出力 22 が MDAC<sub>2</sub> のアナログ入力 20 に接続される。したがって、 $V_{s/h}$  を受取る MDAC<sub>1</sub> を除いては、各 MDAC の  $V_1$  20 は、先立つ MDAC 18 の  $V_{res}$  であり、それはここで  $V_{resm}$  とも呼ばれ、m は出力信号を生成する MDAC 18 を表す。例では MDAC<sub>2</sub> である最後の MDAC 18 のアナログ出力 22 が最後のステージ 30 の入力 28 に接続される。以下でより詳細に考察される最後のステージ 30 は、アナログ出力を有さない。

20

**【0005】**

MDAC 18 の各々と最後のステージとは、解像度の 1 ビットと、誤差を訂正するための 1 ビットとを提供するための 2 つのデジタル出力 32 および 34 を有する。ビットは一般に  $b_1$  および  $b_0$  と呼ばれるか、または、特定の MDAC 18 では  $b_{m1}$  および  $b_{m0}$  と呼ばれ、m は、出力信号を生成する MDAC 18 または最後のステージ 30 を表す。MDAC<sub>1</sub> はいくらかの度合いの誤差を備えた  $b_{10}$  および  $b_{11}$  を生成し、MDAC<sub>2</sub> はいくらかの度合いの誤差を備えた  $b_{20}$  および  $b_{21}$  を生成し、以下同様であることが注目される。さらに図 4 を参照して、例示的な 4 ビット A / D 変換器 10 の最後のステージ 30 は、 $b_{31}$  および  $b_{30}$  を生成し、 $b_{30}$  は最下位ビット (LSB) であり、 $b_{31}$  は、 $b_{31}$  と  $b_{20}$  とを加えることによって、MDAC<sub>2</sub> が生成する誤差を訂正するために用いられる。例示されるように、 $b_{21}$  が  $b_{10}$  に加えられて、MDAC<sub>1</sub> が生成する誤差が訂正される。したがって、一般に、 $b_{m1}$  を用いて MDAC<sub>m-1</sub> が生成する誤差が訂正される。

30

**【0006】**

40

50

図1および図2を引き続き参照して、各M D A C 1 8は、 $V_1$ から $b_1$ および $b_0$ を生成するための1.5ビットアナログ - デジタル変換器(ADC)36を有する。表1は、M D A C 1 8の $V_1$ についての $b_1$ および $b_0$ の値についての定義表である。 $\pm V_r$ はADC36のフルスケールレンジであることが注目される。

【0007】

【表1】

表1

| 入力電圧範囲 ( $V_1$ )        | $b_1$ | $b_0$ |

|-------------------------|-------|-------|

| $V_1 < -V_r/4$          | 0     | 0     |

| $-V_r/4 < V_1 < +V_r/4$ | 0     | 1     |

| $V_1 > +V_r/4$          | 1     | 0     |

10

【0008】

ADC36によって $b_1$ および $b_0$ が一旦生成されると、それらはデジタル出力32および34で出力され、また1.5ビットデジタル - アナログ変換器(DAC)38へと入力される。DAC38は $b_1$ および $b_0$ をアナログ信号または $V_{DAC}$ へと変換し、それは $V_{res}$ の計算で用いられる。表2は、M D A C 1 8の $b_1$ および $b_0$ についての $V_{DAC}$ の値についての定義表である。

20

【0009】

【表2】

表2

| $b_1$ | $b_0$ | $V_{DAC}$ |

|-------|-------|-----------|

| 0     | 0     | $-V_r/2$  |

| 0     | 1     | 0         |

| 1     | 0     | $+V_r/2$  |

30

【0010】

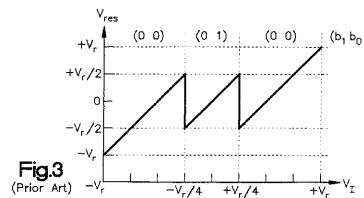

M D A C 1 8は、加算器40でもって $V_1$ から $V_{DAC}$ を減じ、さらには合計値(summed value)を2の利得を有する増幅器42で増幅することによって、 $V_{res}$ を生成する。さらに図3を参照して、M D A C 1 8の特性が示される。図3は、 $V_1 - V_{res}$ をグラフで示し、 $V_1$ の値の範囲上の $b_1$ および $b_0$ の値を示す。

【0011】

最後のステージ30は、最後のステージの入力電圧 $V_1$ を2ビットのデジタル値へと変換するための2ビットアナログ - デジタル変換器(ADC)である。したがって、M D A C 1 8と同様に、最後のステージは、 $b_1$ および $b_0$ をそれぞれ提供する2つのデジタル出力32および34を有する。最後のステージ30の第2のデジタル出力34で提供される $b_0$ は、A / D変換器10のデジタル出力の最下位ビットを示す。代替的には、最後のステージ30は、出力22を他のいかなるステージにも接続せずにM D A C 1 8で実現され得る。表3は、2ビットの最後のステージ30の $V_1$ についての $b_1$ および $b_0$ の値についての定義表である。

40

【0012】

【表3】

表3

| 入力電圧範囲 (V <sub>i</sub> )                                   | b <sub>1</sub> | b <sub>0</sub> |

|------------------------------------------------------------|----------------|----------------|

| V <sub>i</sub> < -V <sub>r</sub> /3/4                      | 0              | 0              |

| -V <sub>r</sub> /3/4 < V <sub>i</sub> < -V <sub>r</sub> /4 | 0              | 1              |

| -V <sub>r</sub> /4 < V <sub>i</sub> < +V <sub>r</sub> /4   | 1              | 0              |

| V <sub>i</sub> > +V <sub>r</sub> /4                        | 1              | 1              |

10

## 【0013】

M D A C 1 8 および最後のステージ 3 0 のデジタル出力はデジタル論理訂正回路 4 4 に入力される。デジタル論理訂正回路 4 4 は、A / D 変換器 1 0 のデジタル出力 D<sub>OUT</sub> を生成する。デジタル出力は、一連のビット、または D<sub>N-1</sub> から D<sub>0</sub> である。例では、N は 4 ビットである。したがって、デジタル出力は D<sub>3</sub>、D<sub>2</sub>、D<sub>1</sub>、および D<sub>0</sub> であり、D<sub>3</sub> は最上位ビット (M S B) であり、D<sub>0</sub> は最下位ビット (L S B) である。デジタル論理訂正回路 4 4 は、M D A C 1 8 の 1 . 5 ビット A D C 3 6 および最後のステージ 3 0 の 2 ビット A D C 内の不正確なしきい値によって生じた誤差を訂正する。個々のしきい値が理想値から V<sub>r</sub> / 4 以下で逸脱する限りは、各ステージのシフトされたデジタル出力を加えることによって、誤差は訂正され得る。

20

## 【0014】

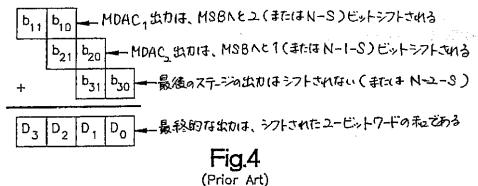

図 4 は、デジタル誤差訂正回路 4 4 のシフティング動作を示す。S は、S H A 1 4 および最後のステージ 3 0 を除いた A / D 変換器 1 0 のステージの数であることが注目される。言い換えると、S はパイプライン A / D 変換器 1 0 内の M D A C 1 8 の数である。

## 【0015】

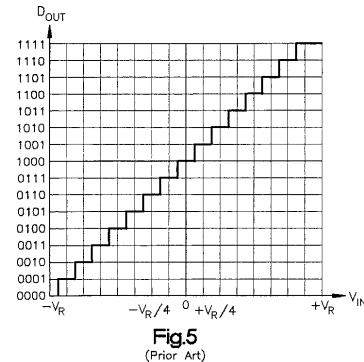

図 5 は、M D A C 1 8 の 1 . 5 ビット A D C 3 6 および最後のステージ 3 0 の 2 ビット A D C のためのしきい値が V<sub>r</sub> / 4 以下で逸脱するという条件下での、図 1 で示された 4 ビット A / D 変換器 1 0 の特性を示すグラフである。± V<sub>R</sub> は A / D 変換器 1 0 のフルスケールレンジであることが注目される。0 ボルトのアナログ入力電圧がデジタルの中心 1 0 0 0 として定められることも注目される。しかし、最後のステージ 3 0 の 2 ビット A D C のしきい値が表 3 で示されるしきい値ではなく、+ V<sub>r</sub> \* 3 / 4、+ V<sub>r</sub> / 4 および - V<sub>r</sub> / 4 ならば、図 5 で示される A / D 変換曲線は 1 つの L S B だけ右に移動し、結果として 0 ボルトのアナログ入力電圧がデジタルの中心 0 1 1 1 として定められる。

30

## 【0016】

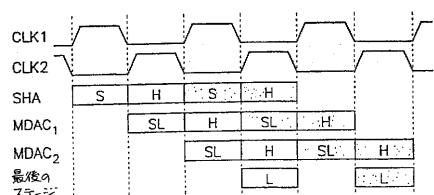

図 2 および図 1 3 を参照して、A / D 変換器 1 0 のタイミングが考察される。A / D 変換器 1 0 は、バイアスおよび基準ジェネレータ (図示せず) と、クロックジェネレータ (図示せず) とを有する。バイアスおよび基準ジェネレータは、A / D 変換器 1 0 の種々のステージによる使用のための適切な電圧基準およびバイアス電流を生成する。クロックジェネレータは、2 相の重なり合わない (nonoverlapping) クロック信号を生成し、そのそれぞれのクロックパルス信号は C L K 1 および C L K 2 と呼ばれる。2 つのクロックパルス信号 C L K 1 および C L K 2 の波形は図 1 3 の上部で示される。C L K 1 は事実上、約 5 0 % のデューティサイクルを有する。C L K 2 も事実上約 5 0 % のデューティサイクルを有するが、C L K 1 に対し 1 8 0 ° 遅れる。

40

## 【0017】

図 2 で示されるように、C L K 1 は、S H A 1 4 のサンプルクロック入力 S A と、M D A C<sub>1</sub> の増幅器 4 2 のホールドクロック入力 H とに与えられる。C L K 2 は、S H A 1 4 のホールドクロック入力 H と、M D A C<sub>1</sub> の A D C 3 6 のラッチクロック入力 L と、M D A C<sub>1</sub> の増幅器 4 2 のサンプルクロック入力 S A とに与えられる。図 1 3 で示されるように、同じクロック信号が M D A C<sub>2</sub> のために用いられるが、クロック信号は互い違いになっている (alternated)。より具体的には、C L K 1 は、M D A C<sub>2</sub> の A D C 3 6 のラッチク

50

ロック入力 L と、MDAC<sub>2</sub>の増幅器 42 のサンプルクロック入力 SA とに与えられ、CLK2 は、MDAC<sub>2</sub>の増幅器 42 のホールドクロック入力 H に与えられる。より高い解像度の A/D 変換器 10 のためにさらなる MDAC18 ステージが存在するならば、第 3 の MDAC18 および後続の MDAC18 が、サンプル/ラッチ動作およびホールド動作のために CLK1 と CLK2 とを交互に用い、MDAC18 のサンプル/ラッチが前の MDAC18 のホールドと一致する。CLK2 は、最後のステージ 30 のラッチクロック入力に与えられる。最後のステージ 30 は残差出力を生成しないため、最後のステージ 30 はサンプルおよび / またはホールド動作を行なわないことが注目される。

## 【0018】

S HA ステージ 14 と、MDAC<sub>1</sub> と、MDAC<sub>2</sub> と、最後のステージ 30 とのサンプル、ホールド、およびラッチ動作が図 13 の下部で示される。タイミング図の中の異なる陰影は、サンプルがすべてのステージを通るときの一連の 2 つのアナログ入力サンプル上のパイプライン変換プロセスを示す。S HA 14 は、CLK1 の間にアナログ入力信号 V<sub>IN</sub> をサンプリングし、CLK2 の間にホールド動作を行なう。MDAC<sub>1</sub> は、CLK2 の間に V<sub>s/h</sub> をサンプリングする。MDAC<sub>1</sub> の ADC36 は、CLK2 のパルスの間に動作し、好ましくは CLK2 の立下がり端縁上でデジタル出力をラッチし、V<sub>s/h</sub> に N ビット確度のアナログ等価(analog equivalent of N bit accuracy)に整定する(settle)ための時間を与える。したがって、S HA 14 の許容限界(tolerance)は、1 つの LSB のアナログ等価である。MDAC<sub>1</sub> は、CLK1 の間に残差出力 V<sub>res1</sub> を生成し、ホールドする。MDAC<sub>2</sub> は、CLK1 の間に V<sub>res1</sub> をサンプリングし、そのデジタル出力を CLK1 の終わりに、または CLK1 の立下がり端縁上でラッチし、V<sub>res</sub> に N - 1 ビット確度のアナログ等価に整定するための時間を与える。MDAC<sub>2</sub> は CLK2 の間に V<sub>res2</sub> を生成し、ホールドする。最後のステージ 30 は、そのデジタル出力を CLK2 の終わりに、または CLK2 の立下がり端縁上でラッチし、V<sub>res2</sub> に N - 2 ビット確度のアナログ等価に整定するための時間を与える。

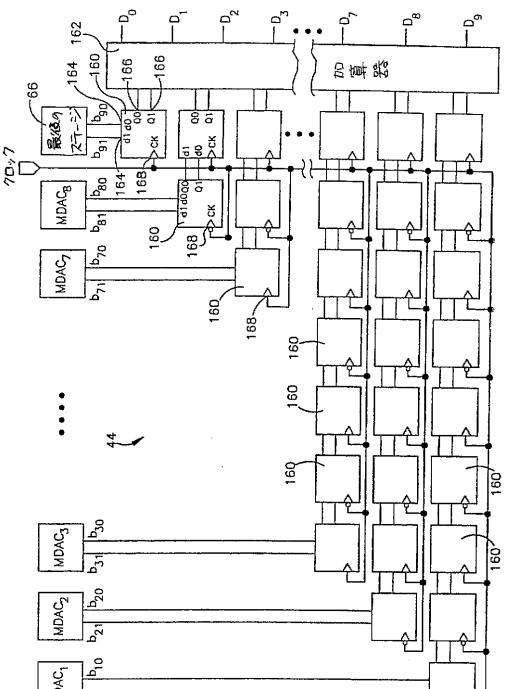

## 【0019】

図 14 を参照して、従来のデジタル論理訂正(DLC)回路 44 が示される。N - ビットパイプライン A/D 変換器 10 のこれまでの DLC 回路 44 は、各 MDAC ステージ 18 および最後のステージ 66 のデジタル出力を遅延するための一連の遅延またはシフトレジスタを有し、図 4 で示されるようにそれらのそれぞれのデジタル出力が組合せられ得る。遅延の各々にはデジタル入力 164 とデジタル出力 166 とが設けられる。簡素化および明確化のために、図 14 の例示される DLC 回路 44 は、一つの連なり(one series)の遅延 160 を通して送られる各デジタル出力生成ステージの(上で考察された b<sub>m1</sub> および b<sub>m0</sub> 表記法でラベル付けされる)多数のデジタル出力を示すことが注目される。しかし、実際の実現例では、各ステージのデジタル出力ビットの各々のために、別個の連なりの遅延 160 が必要とされる。A/D 変換器 10 ステージ当たりのデジタル出力数は、ステージ当たり B ビットとここで呼ばれる。A/D 変換器 10 の各ステージが B デジタル出力ビットを有する、N ビットパイプライン A/D 変換器 10 の従来の DLC 回路 44 が必要とする遅延 160 の合計数は、以下の式によって計算され得る。

## 【0020】

## 【数 2】

$$\text{遅延の数} = B(1 + 2 + \dots + N) = B(N + 1) \left\{ \frac{N}{2} \right\}$$

## 【0021】

各遅延には、クロック入力 168 とリセット入力(図示せず)とが設けられる。同じクロック信号が DLC 回路 44 内の各遅延 160 のクロック入力 168 に与えられる。しかし、図 14 で示されるように、ある特定のいずれかの A/D 変換器 10 ステージの 1 つおきの遅延 160 が、反転されたクロック入力 168 を有する。したがって、各 A/D 変換器 10 ステージのデジタルデータ出力は、各クロック周期について 2 回遅延される。10 ビ

10

20

30

40

50

ット A / D 変換器 10 が図 14 で示される。したがって、MDAC<sub>1</sub> のデジタル出力は、合計で 9 回または 4.5 クロックサイクル遅延される。各ステージのデジタル出力が遅延された後、それらは、上で説明され、図 4 で示されるように、加算器 162 によって組合せられる。加算器 162 は、アナログ入力信号のデジタル表現または D<sub>OUT</sub> を出力する。例の 10 ビット A / D 変換器 10 は、合計で 90 の遅延 160 を必要とする。

#### 【0022】

従来のパイプライン A / D 変換器に関してさらなる情報が望まれるならば、以下が注目される。スティーブン H. ルイーズ他 (Stephen H. Lewis et al.)、「パイプライン 5-Mサンプル / s 9 ビットアナログ - デジタル変換器」(“A Pipelined 5-Msample/s 9-bit Analog-to-Digital Converter”), IEE E J. Solid-State Circuits), vol. Sc-22, no. 6, 第 954 - 961 頁, 1987 年 12 月; スティーブン H. ルイーズ他、「10-b 20-Mサンプル / s アナログ - デジタル変換器」(“A 10-b 20-Msample/s Analog-to-Digital Converter”), IEE E J. Solid-State Circuits, vol. 27, no. 3, 第 351 - 358 頁, 1992 年 3 月; トマス B. チョー他 (Thomas B. Cho et al.), 「10b, 20 Mサンプル / s, 35 mW パイプライン A / D 変換器」(“A 10b, 20Msample/s, 35mW Pipeline A/D Converter”), IEE E J. Solid-State Circuits, vol. 30, no. 3, 第 166 - 172 頁, 1995 年 3 月; クリッシュナスワミイ ナガラー他 (Krishnaswamy Nagaraj et al.), 「減じられた数の増幅器を備えた、250 mW, 8-b, 52-Mサンプル / s 並列パイプライン A / D 変換器」(“A 250mW, 8-b, 52-Msample/s Parallel-Pipelined A/D Converter with Reduced Number of Amplifiers”), IEE E J. Solid-State Circuits, vol. 32, no. 3, 第 312 - 320 頁, 1997 年 3 月; ユーミンリン他 (Yuh-Min Lin et al.), 「3-μm CMOS における 13-b 2.5-MHZ 自己較正パイプライン A / D 変換器」(“A 13-b 2.5-MHZ Self-Calibrated Pipelined A/D Converter in 3-μm CMOS”), IEE E J. Solid-State Circuits, vol. 26, no. 4, 第 628 - 636 頁, 1991 年 4 月、が注目される。

#### 【0023】

##### 【発明の概要】

この発明は、パイプラインアナログ - デジタル (A / D) 変換器のためのデジタル論理訂正 (DLC) 回路を提供する。A / D 変換器は複数のステージを有し、各ステージは少なくとも 1 対のデジタル出力ビットを生成し、そこからアナログ入力信号のデジタル表現が得られ得る。DLC 回路は加算器を有し、加算器は複数の入力および出力を有する。DLC 回路は複数のデジタル遅延セットを有し、各デジタル遅延セットは少なくとも 1 つのデジタル遅延を含み、デジタル遅延セットの入力は対応するデジタル出力ビットを受取り、遅延セットの出力は遅延されたデジタル出力ビットをそれぞれの加算器入力に提供する。DLC 回路はクロックジェネレータを有し、クロックジェネレータは DLC 回路にクロック信号を提供してデータ有効周期の間に加算器入力における各デジタル遅延セットの出力の到着を同期させる。1 次クロック信号が、1 つおきのステージのためのデジタル遅延セットに与えられる。2 次クロック信号が残りのデジタル遅延セットに与えられる。1 次クロック信号と 2 次クロック信号とのタイミングは、それぞれのデジタル遅延セットを介して各ステージのデジタル出力ビットを遅延してデジタル出力ビットをデータ有効周期の間に加算器入力に到着させ、さらには加算器が加算器出力でアナログ入力信号のデジタル表現を生成するのに有効である。

#### 【0024】

この発明のこれらの特徴およびさらなる特徴は、以下の説明および図を参照することによって明らかとなるだろう。

#### 【0025】

##### 【発明の開示】

以下の詳細な説明では、同一の構成要素には同じ参照番号が与えられ、これは、それらが

10

20

30

40

50

この発明の異なる実施例で示されているか否かにかかわらず行なわれる。この発明を明確に、かつ簡潔に例示するために、図は必ずしも一定の縮尺に応じているわけではなく、ある特定の特徴は多少概略的な形で示されることもある。

#### 【 0 0 2 6 】

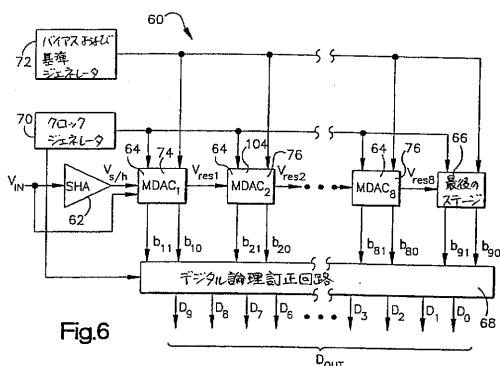

図6を参照して、この発明に従ったアナログ - デジタル( A / D )変換器60が示される。A / D変換器60は、アナログ電気入力信号( $V_{IN}$ )をアナログ信号のデジタル表現( $D_{OUT}$ )へと変換する。示される例は10ビットA / D変換器であるが、変換器ステージの追加または除去とともに、より多くのビットまたはより少ないビットの解像度が容易に実現されることが理解されるだろう。したがって、A / D変換器の解像度はNビットA / D変換器と呼ばれることもあり、Nはデジタル出力ビット数を示す。示される例のA / D変換器60は、40MHzのサンプリング速度を有する。25 - 250MHz等の他のサンプリング速度も用いられ得る。

10

#### 【 0 0 2 7 】

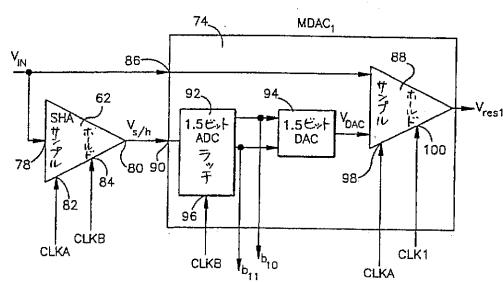

図1で示されるA / D変換器10と同様に、A / D変換器60は、サンプルホールド増幅器(SHA)62と、MDAC<sub>1</sub>からMDAC<sub>8</sub>、または総称してMDAC<sub>m</sub>とラベル付けされる複式デジタル - アナログ変換器(MDAC)64とも呼ばれる一連のアナログ信号変換器ステージと、最後のステージ66と、デジタル論理訂正回路68とを有する。加えて、A / D変換器60にはクロックジェネレータ70と、バイアスおよび基準電圧ジェネレータ72とが設けられる。バイアスおよび基準ジェネレータ72は、A / D変換器60の種々のステージの各々のために適切なバイアス電流および電圧基準を生成する。クロックジェネレータ70は4つのクロックパルス信号を生成し、それらはここで第1のクロックパルス信号またはCLKA、第2のクロックパルス信号またはCLKB、第3のクロックパルス信号またはCLK1、および第4のクロックパルス信号またはCLK2と呼ばれる。クロックジェネレータ70は、これらのクロックパルス信号の早期立下がりバージョンも生成し、それらはここでCLKA、CLKB、CLK1、およびCLK2と呼ばれる。すべてのクロック線のロードおよび駆動能力は、クロック信号の重なり合わない特性を維持する助けとなるように、好ましくは同じである。A / D変換器60のタイミングは以下により詳細に考察される。MDAC<sub>1</sub>(参考番号74)は、MDAC<sub>2</sub>からMDAC<sub>m</sub>(参考番号76)とは異なった構成を有する。MDAC<sub>2</sub>からMDAC<sub>m</sub>の各々は同じ構成を有する。

20

#### 【 0 0 2 8 】

図7を参照して、A / D変換器60の一般的な動作が示される。A / D変換器60の動作の具体的な詳細は、以下により詳細に考察される。しかし、例示され、かつ説明されるMDACのデジタル出力は例示的なものであり、1.5ビットよりも高い、またはそれよりも低い解像度を有するMDACが同様の結果でもって用いられ得ることが注目される。MDAC<sub>1</sub>は $V_{s/h}$ を用いて $b_{11}$ および $b_{10}$ を生成する。しかし、MDAC<sub>1</sub>は、残差計算で直接 $V_{s/h}$ を用いない。むしろ、MDAC<sub>1</sub>は、 $V_{IN}$ を残差計算動作で直接用いる。 $V_{s/h}$ は残差計算に直接加わらないため、 $V_{s/h}$ はNビット確度のアナログ電圧等価を必要としない。これは、SHA62の許容限界が1つの LSB よりも大きくなり得ることを意味する。言い換えると、 $V_{s/h}$ は緩和された(relaxed)確度要件を有する。以下により完全に説明されるように、 $V_{s/h}$ と、MDAC<sub>1</sub>のADCのしきい値オフセットとの中に含まれるいかなる誤差も $V_r / 4$ 内に保たれるならば、デジタル訂正論理回路68は有効な $D_{OUT}$ を回復できる。MDAC<sub>1</sub>の残差出力はN - 1ビットのアナログ等価内で正確であるべきことが注目される。しかし、SHA62のNビット確度を達成するための困難さが取り除かれ、それによってA / D変換器60の速度が上げられ、電力消費が減じられ、さらには集積回路サイズ要件も減じられる助けがなされ、同時にA / D変換器60の全体的な確度も維持される。

30

#### 【 0 0 2 9 】

図7を続けて参照して、SHA62とMDAC<sub>1</sub>とがより詳細に考察される。SHA62は好ましくは単位(unity)利得を有する。 $V_{IN}$ がSHA62のアナログ信号入力78に入

40

50

力される。S H A 6 2 は、アナログ入力信号 ( $V_{IN}$ ) をサンプリングし、サンプリングされた電圧または  $V_{s/h}$  を S H A 出力 8 0 で M D A C<sub>1</sub> のためにホールドする。各 M D A C 6 4 のための  $V_{IN}$ 、 $V_{s/h}$ 、および残差電圧 ( $V_{res}$ ) は自己を基準にし(つまり、微分)、したがって、各々は 1 対の導体にわたって運ばれることが注目される。代替的には、 $V_{IN}$ 、 $V_{s/h}$ 、および  $V_{res}$  は、シングルエンドで(single-ended)あってもよく、接地を基準にした単一の導体上で運ばれ得る。

#### 【 0 0 3 0 】

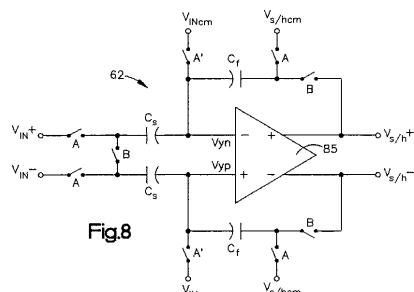

S H A 6 2 は、クロックジェネレータ 7 0 からの C L K A 信号を受取るためのサンプルクロック入力 8 2 と、クロックジェネレータ 7 0 からの C L K B 信号を受取るためのホールドクロック入力 8 4 とを有する。S H A 6 2 は、図 8 で示されるような完全差動(fully differential)演算増幅器 8 5 を用いてスイッチドキャパシタ回路で実現され得る。スイッチ A および B は、クロック信号 C L K A および C L K B によってそれぞれ制御される C M O S トランスマッショングートで実現される。共に考慮すると、C L K A および C L K B は、2 相の重なり合わないクロックを形成し、その詳細は以下でより完全に考察される。スイッチ A は、C L K A の早期立下がりバージョンまたは C L K A によって制御される。完全差動演算増幅器 8 5 は、入力オフセット電圧 ( $V_{os}$ )、各入力ノードのための入力寄生キャパシタンス ( $C_p$ )、および D C 差動利得 ( $A_o$ ) を有する。記号 c m、+、および - が、図 8 および以下の式のある特定の電圧の接尾部 (suffixes) に加えられることが注目される。当業者は、c m はコモンモードを表し、+ および - 記号は、 $V_{IN}$ 、 $V_{s/h}$ 、および  $V_{res}$  のための導体ペア(pairs)の個々の導体上の電位を区別することを理解するだろう。S H A 6 2 の確度要件がここで説明されるように緩和されていないならば、 $C_s$  および  $C_f$  とラベル付けされる S H A 6 2 内のキャパシタは、全デバイスノイズ効果(つまり、K T / C ノイズとオペアンプノイズ)が量子化ノイズよりもずっと小さくなるのに十分なほど大きい必要があることが注目される。その場合、0.35 μm ダブルポリ技術における 20 μm × 20 μm ポリ - ポリ(poly-poly)キャパシタで実現される 0.45 p f キャパシタが、10 ビット A / D 変換器のためのキャパシタ  $C_s$  および  $C_f$  のために用いられる。しかし、この発明は、 $C_s$  および  $C_f$  のためにより小さなキャパシタを用いることもできる。位相 B では、演算増幅器の安定した入力値 ( $V_{yn}$ ) が以下の式によって満たされる。

#### 【 0 0 3 1 】

##### 【 数 3 】

$$V_{yn} = V_{INcm^+} \left( \frac{V_{s/h^+} + V_{s/h^-}}{2} - V_{s/hcm} \right) \left( \frac{C_f}{(C_f + C_p)} \right) - \frac{V_{os}}{2} + \frac{V_{s/h^+} - V_{s/h^-}}{2A_o}$$

#### 【 0 0 3 2 】

位相 B では、演算増幅器の安定した出力値が以下の式によって表わされる。

#### 【 0 0 3 3 】

##### 【 数 4 】

$$V_{s/h^+} - V_{s/h^-} = \frac{\left( \frac{(C_s + C_f)}{C_f} \right) (V_{IN^+} - V_{IN^-}) - \left( 1 + \frac{C_s}{C_f} + \frac{C_p}{C_f} \right) (V_{os})}{1 + \left( \frac{1}{A_o} \right) \left( 1 + \frac{C_s}{C_f} + \frac{C_p}{C_f} \right)}$$

#### 【 0 0 3 4 】

図 7 を参照して、M D A C<sub>1</sub> は、アナログ入力信号 ( $V_{IN}$ ) を直接受取るためのアナログ信号入力 8 6 を有する。アナログ信号入力 8 6 は、残差増幅器 8 8 の入力に接続され、M

10

20

30

40

50

D A C<sub>1</sub>の残差信号またはV<sub>res1</sub>を計算するために用いられる。M D A C<sub>1</sub>にはまた、V<sub>s/h</sub>を受取るためにS H A出力80に接続されるサンプルホールド電圧入力90が設けられる。M D A C<sub>1</sub>は、図2で示されるM D A C 18のために用いられるA D C 36と同様のフラッシュ型1.5ビットアナログ-デジタル変換器(A D C)92を有する。A D C 92は、サンプルホールド電圧入力90に接続される入力を有し、上の表1で示される定義に従ってV<sub>s/h</sub>を2つのビットb<sub>1</sub>およびb<sub>0</sub>へと変換する。A D C 92によってb<sub>1</sub>およびb<sub>0</sub>が一旦生成されると、それらは、M D A C<sub>1</sub>からデジタル論理訂正回路68へと出力され、また1.5ビットデジタル-アナログ変換器(D A C)94へと入力される。A D C 92は、クロックジェネレータ70が生成するC L K B信号を受取るためのラッチクロック入力96を有する。D A C 94は、図2で示されるM D A C 18のために用いられるD A C 38と同様のものである。D A C 94は、上の表2で示される定義に従ってb<sub>1</sub>およびb<sub>0</sub>をV<sub>DAC</sub>へと変換する。D A C 94はV<sub>DAC</sub>を出力し、これは、V<sub>res1</sub>の計算で用いられる残差増幅器88の第2の入力によって受取られる。残差増幅器には、C L K A信号を受取るためのサンプルクロック入力98と、C L K 1信号を受取るためのホールドクロック入力100とが設けられる。

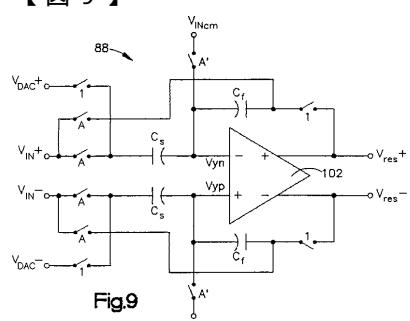

## 【0035】

さらに図9を参照して、残差増幅器88は、完全差動演算増幅器102を用いる差動スイッチドキャパシタ倍電圧器である。演算増幅器102は好ましくは、高い利得(たとえば、80dB)および速い整定を提供するために利得増強力スケードロードを備えるテレスコープ状オペアンプである。M D A C<sub>1</sub>のV<sub>res1</sub>の確度は、1/2<sup>N-1</sup>であって最下位ビットの半分よりも少ない微分(differential)非線形(D N L)(つまり、D N L < 1/2 L S B)を達成することが望まれる。C<sub>s</sub>およびC<sub>f</sub>とラベル付けされる残差増幅器88内のキャパシタは好ましくは、全デバイスノイズ効果(つまり、K T / C ノイズとオペアンプノイズ)が量子化ノイズよりもずっと小さくなるのに十分なほど大きいことが注目される。好ましくは、キャパシタC<sub>s</sub>およびC<sub>f</sub>のために0.45pFキャパシタが用いられる。0.45pFキャパシタは、20μm × 20μmポリ-ポリキャパシタで実現され得る。スイッチAおよび1は、クロック信号C L K AおよびC L K 1によってそれぞれ制御されるC M O Sトランスマッショングートで実現される。スイッチA<sub>1</sub>は、C L K Aの早期立ち下がりバージョンまたはC L K A<sub>1</sub>によって制御される。増幅器102は、入力オフセット電圧(V<sub>os</sub>)、各入力ノードのための入力寄生キャパシタンス(C<sub>p</sub>)、およびD C差動利得(A<sub>o</sub>)を有する。10ビットA/D変換器60のための例の差動利得A<sub>o</sub>は、少なくとも4000である。図9および以下の式のある特定の電圧の接尾部に記号c m、+、および-が加えられることが注目される。当業者は、c mはコモンモードを表し、+および-記号は、V<sub>IN</sub>、V<sub>s/h</sub>、およびV<sub>res</sub>のための導体ペアの個々の導体上の電位を区別することを理解するだろう。位相1では、増幅器102の安定した入力値(V<sub>yn</sub>)が以下の式によって満たされる。

## 【0036】

## 【数5】

$$V_{yn} = V_{INcm} + X \left( \frac{C_f}{(C_s + C_f + C_p)} \right) - \frac{V_{os}}{2} + \frac{V_{res+} - V_{res-}}{2A_o}$$

式中、

$$X = \left( \frac{C_f(V_{res+} + V_{res-})}{2} + \frac{C_s(V_{DAC+} + V_{DAC-})}{2} - \frac{(C_f + C_s)(V_{IN+} + V_{IN-})}{2} \right)$$

## 【0037】

位相1では、増幅器102の安定出力値が以下の式で表わされる。

## 【0038】

## 【数6】

10

20

30

40

50

$$V_{res+} - V_{res-} = \frac{\left( \frac{(C_s + C_p)}{C_f} \right) (V_{IN+} - V_{IN-}) - \left( 1 + \frac{C_s}{C_f} + \frac{C_p}{C_f} \right) (V_{os}) + \left( \frac{C_s}{C_f} \right) (V_{DAC+} - V_{DAC-})}{1 + \left( \frac{1}{A_o} \right) \left( 1 + \frac{C_s}{C_f} + \frac{C_p}{C_f} \right)}$$

## 【0039】

図7を参照して、MDAC<sub>1</sub>は、b<sub>11</sub>およびb<sub>10</sub>を生成するためだけにV<sub>s/h</sub>を用い、直接V<sub>res1</sub>の計算ではそれを用いない。むしろ、MDAC<sub>1</sub>は、残差電圧V<sub>res1</sub>の計算ではアナログ入力信号V<sub>IN</sub>を直接用いる。SHA62は、Nビット精度のアナログ電圧等価または1つの LSB の許容限界をもはや必要としない。なぜならば、残差生成プロセスから SHA62ステージは除去されるためである。V<sub>s/h</sub>のための精度要件は、Nビット解像度のアナログ電圧等価を達成するための困難さからデジタル論理訂正回路を用いて訂正可能な許容限界にまで緩和される。したがって、SHA62ステージの精度または許容限界は、V<sub>r</sub>/4よりも少ない誤差であるとして表わされ得るが、V<sub>r</sub>はMDAC<sub>1</sub>のADC92のフルスケールレンジである。MDAC<sub>1</sub>のADC92のフルスケールレンジは、V<sub>IN</sub>のフルスケールレンジに対応していることが注目される。したがって、SHA62の許容限界は、V<sub>IN</sub>の±25%であるか、代替的にはN-1ビットのアナログ電圧等価の電圧出力精度として表わされる。当業者によって理解されるように、SHA62に必要とされる精度を減じることによって、ある特定の利点が提供される。それはSHA62内の速い整定時間に対する必要性を大きく減じ、SHA62の設計の実現がより容易になる。また、SHA62は、電力消費およびチップ面積が減じられた回路で実現され得る。

10

20

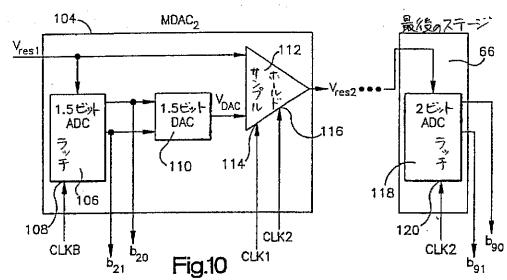

## 【0040】

図10を参照して、第2のMDACまたはMDAC<sub>2</sub>(参照番号104)と、最後のステージ66とが示される。MDAC<sub>2</sub>は、図1で示されるA/D変換器10の中で見られるMDAC18(図2)と作動的に同じである。加えて、第1のMDACまたはMDAC<sub>1</sub>の後のすべてのMDAC76は、タイミングを確立するためにMDAC76に与えられる入力クロック波形を除いては、同一である。種々のステージに与えられるクロック信号は、以下でより詳細に考察される。したがって、MDAC<sub>1</sub>の後の、パイプライン内のMDAC76についての考察は、MDAC<sub>2</sub>の以下の考察に限られる。MDAC<sub>2</sub>は、2つのコンパレータとラッチクロック入力108とを有するフラッシュ型1.5ビットADC106を提供する。ADC106は、前のMDAC64の残差電圧V<sub>res</sub>を上述のような2つの出力ビットb<sub>m1</sub>およびb<sub>m0</sub>へと変換する。出力ビットb<sub>m1</sub>およびb<sub>m0</sub>は、デジタル出力D<sub>OUT</sub>の計算のためにデジタル誤差訂正回路へと入力される。出力ビットb<sub>m1</sub>およびb<sub>m0</sub>は、MDAC<sub>2</sub>が提供する1.5ビットDAC110にも入力され、上述のようなV<sub>DAC</sub>が生成される。MDAC<sub>2</sub>は、MDAC<sub>1</sub>のための残差増幅器88と実質的に同じ残差増幅器112を提供する。残差増幅器112は、上述のように前のステージの残差電圧およびV<sub>DAC</sub>を用いてA/D変換器60の次のステージのために残差電圧V<sub>resm</sub>を計算する。残差増幅器112は、サンプルクロック入力114とホールドクロック入力116とを有する。

30

40

## 【0041】

続けて図10を参照して、最後のステージ66は、A/D変換器10のための最後のステージ30(図1)と作動的に同じである。最後のステージ66は、3つのコンパレータとラッチクロック入力120とを有するフラッシュ型2ビットADC118を提供する。ADC118は、前のMDAC64の残差電圧V<sub>res</sub>を上述のような2つの出力ビットb<sub>m1</sub>およびb<sub>m0</sub>へと変換する。出力ビットb<sub>m1</sub>およびb<sub>m0</sub>は、デジタル出力D<sub>OUT</sub>の計算のためにデジタル誤差訂正回路に入力される。

## 【0042】

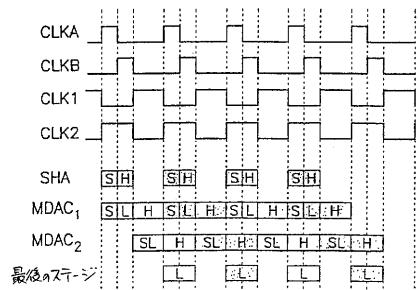

図11を参照して、この発明に従って構成された例の4ビットA/D変換器のタイミング

50

が説明される。図6で示される10ビットA/D変換器と同様に、例の4ビットA/D変換器は、SHAステージ62、第1のMDAC<sub>1</sub>、第2のMDAC<sub>2</sub>、および最後のステージ66を有するが、さらなる6つの中間のMDACステージ76、またはMDAC<sub>3</sub>からMDAC<sub>8</sub>を有さない。より高い解像度のA/D変換器ではなく、4ビットA/D変換器のタイミングが簡素化および明確化のために説明される。同じタイミングがより高いNビット変換器のために用いられるが、第3のMDAC76および後続のMDAC76のサンプルおよびホールドのためのクロック位相はステージごとに互い違いになる。より具体的には、第3のMDAC76および後続のMDAC76は、サンプル/ラッチ動作およびホールド動作のためにCLK1およびCLK2を代わるがわる用い、図11および図13のMDAC<sub>1</sub>およびMDAC<sub>2</sub>で例示されるように、MDAC64のサンプル/ラッチが前のMDAC76のホールドと一致する。

#### 【0043】

4つのクロックパルス、CLKA、CLKB、CLK1、およびCLK2のための波形が図11の上部で示される。共に考慮すると、CLKAおよびCLKBは、2相の重なり合わないクロックを形成する。CLKAは事実上、約25%のデューティサイクルを有する。CLKBも事実上、約25%のデューティサイクルを有するが、CLKAに対して90°遅れる。共に考慮すると、CLK1およびCLK2は、2相の重なり合わないクロックを形成する。CLK1は事実上、約50%のデューティサイクルを有するが、CLKAに対して180°遅れる。CLK2も事実上、約50%のデューティサイクルを有するが、CLK1に対して180°遅れる。明確化および簡素化のために、4つのクロックパルス信号は方形の波として図11で示されることが注目される。しかし、クロックパルスは好ましくは、図13で示されるクロック信号で例示されるような傾斜した立上がり端縁および立下がり端縁を有する。

#### 【0044】

SHAステージ62と、第1のMDAC<sub>1</sub>と、第2のMDAC<sub>2</sub>と、最後のステージ46とのサンプル、ホールド、およびラッチ動作が図11の下部で例示される。タイミング図の中の異なる陰影は、サンプルがすべてのステージを通るときの一連の4つのアナログ入力サンプル上のパイプライン変換プロセスを示す。

#### 【0045】

SHA62は、CLKAの間にアナログ入力信号V<sub>IN</sub>をサンプリングし、CLKBの間にホールド動作を行なう。したがって、SHA62は、受け入れ可能な許容限界内のV<sub>s/h</sub>をCLKBのパルスの終わりまでに生成する。言い換えると、V<sub>s/h</sub>はデューティサイクルの半分内でN-1ビット確度のアナログ等価に整定した。

#### 【0046】

V<sub>s/h</sub>を用いて、MDAC<sub>1</sub>のADC92はCLKBのパルスの間に動作し、そのデジタル出力b<sub>11</sub>およびb<sub>10</sub>を生成する。好ましくは、ADC92はCLKBの立下がり端縁上でデジタル出力をラッチし、V<sub>s/h</sub>に最大限の整定時間を与える。MDAC<sub>1</sub>のラッチ動作はデューティサイクルの半分内で達成されることが理解されるだろう。

#### 【0047】

SHA62が行なうサンプリングと同時に、MDAC<sub>1</sub>もCLKAの間に入力信号V<sub>IN</sub>をサンプリングする。これが行なわれることによりすべてのステージが適切な時にV<sub>IN</sub>の同じサンプルを変換することができ、各ステージのそれぞれの出力ビットb<sub>1</sub>およびb<sub>0</sub>が、ともに組合せられるのに適当な時間にデジタル論理訂正回路72にカスケード接続されて同じ入力サンプルのためにデジタル出力信号D<sub>OUT</sub>が生成される。

#### 【0048】

MDAC<sub>1</sub>は、CLK1の間に残差出力V<sub>res1</sub>を生成し、ホールドする。MDAC<sub>2</sub>は、CLK1の間にV<sub>res1</sub>をサンプリングし、そのデジタル出力をCLK1の終りに、好ましくはCLK1の立下がり端縁上でラッチし、V<sub>res1</sub>にN-1ビット確度に整定するための時間を与える。MDAC<sub>2</sub>は、CLK2の間にV<sub>res2</sub>を生成し、ホールドする。最後のステージ66は、そのデジタル出力をCLK2の終りで、またはCLK2の立下がり端縁上で

10

20

30

40

50

ラッチし、 $V_{res_2}$ にN - 2ビット確度に整定するための時間を与える。最後のステージ6

6はサンプルおよび／またはホールド動作を行わない。なぜならば、最後のステージ6

6は残差出力を生成しないからである。従来のA / D変換器10と比較して、 $V_{IN}$ から $D_{OUT}$

へのサンプルの全変換はA / D変換器60では半デューティサイクル分進んでいること

が理解されるべきである。したがって、A / D変換器60は、サンプリングされた $V_{IN}$ の

各々のための $D_{OUT}$ をA / D変換器10よりも速く引出す。たとえば、この発明に従った

4ビットA / D変換器60は、従来の4ビットA / D変換器10より25%速い。なぜな

らば、この発明に従った4ビットA / D変換器60が $V_{IN}$ サンプルを1.5クロックサイ

クルで変換するのに対し、4ビットの従来のA / D変換器は $V_{IN}$ サンプルを2クロックサ

イクルで変換するからである。

10

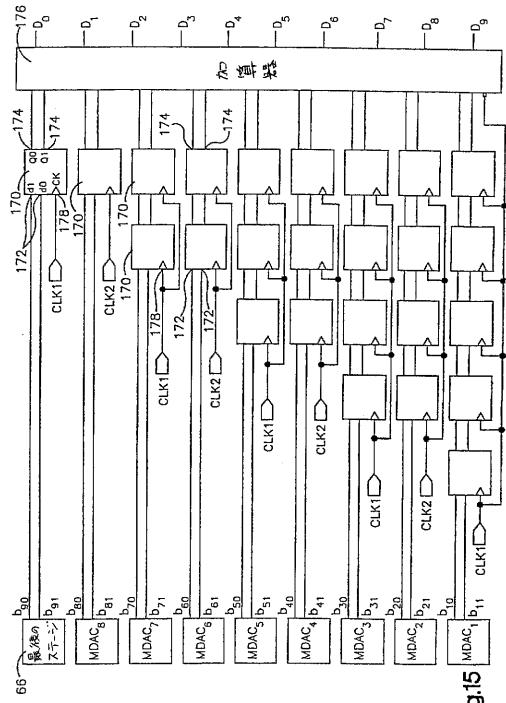

## 【0049】

図15を参照して、この発明に従ったデジタル論理訂正(DLC)回路68が示される。

DLC回路68は、従来のA / D変換器10(図1)とともに、またはA / D変換器60

(図6)とともに用いられ得る。DLC回路68は、A / D変換器60の各ステージのデ

ジタル出力を遅延またはシフトさせる。加えて、DLC回路68は、上で説明され図4で

例示されるように、加算器176を用いて、シフトされたデジタル出力を組合せる。加算

器176は、一連の入力と一連の出力を有する。DLC回路68には、A / D変換器60

の各デジタル出力生成ステージ(つまり、MDAC<sub>1</sub>からMDAC<sub>m</sub>および最後のステ

ージ66)のための遅延170のセットまたはチェーンが設けられる。各セット内の遅延1

70は、直列に(in series)接続され、当該技術分野で周知であるようなフリップフロッ

プで実現され得る。一連の遅延170の各々は、デジタル出力生成ステージのそれぞれの

デジタル出力に接続されるデジタル入力172と、加算器のそれぞれの入力に接続される

出力174とを有する。簡素化および明確化のために、図15の例示されるDLC回路6

8は、一つの連なりの遅延170を通して送られる各デジタル出力生成ステージの(上で

考察された $b_{m1}$ および $b_{m0}$ 表記法でラベル付けされる)多数のデジタル出力を示すことが

注目される。しかし、最も実際的な実現例では、各ステージの各デジタル出力ビットのた

めに別個の連なりの遅延170が必要とされる(つまり、各遅延170は1つの入力17

2と1つの出力174とを有する)。代替的には、1よりも多くのビットを遅延する遅延

170が用いられ得る。

20

## 【0050】

30

各遅延170にはクロック入力178も設けられる。MDAC<sub>1</sub>から始めると、MDAC<sub>1</sub>

の出力ビットを加算器176に伝達する遅延170のクロック入力178がCLK1を受

取る。MDAC<sub>2</sub>のデジタル出力ビットを伝達する遅延170が、遅延170のクロック

入力178でCLK2を受取る。このパターンが図15で示されるように繰返され、ここ

では、CLK1およびCLK2は一連の遅延170の各々の間で代わるがわかるになる。よ

り具体的には、ある特定のいずれかの遅延170のクロック入力178に接続されるクロ

ックパルス信号は、遅延170が伝達するデジタル出力をラッチするのに用いられる2相

の重なり合わないクロック位相の逆位相である。たとえば、図11で示されるように、M

DAC<sub>2</sub>はその出力をCLK1の立下がり端縁上でラッチし、したがって、MDAC<sub>2</sub>のデ

ジタル出力を加算器178へと運ぶ一連の遅延170にはCLK2が与えられる。A / D

変換器60のタイミングでは、MDAC<sub>1</sub>はそのデジタル出力をCLK2の立下がり端縁

と一致するCLKBの立下がり端縁でラッチする。したがって、MDAC<sub>1</sub>から加算器1

76へとデジタル出力を運ぶ遅延170は、CLK1でクロックされる。遅延170は好

ましくは、それらのそれぞれのクロック入力信号の立上がり端縁でトリガーする。各遅延

170にはリセット入力(図示せず)も設けられる。当該技術分野で公知であるように、

各遅延170のリセット入力はリセットクロックに接続される。より具体的には、各遅延

は、各データ変換プロセスの始めでリセットされる。以下でより詳細に説明されるよう

に、加算器176はCLK1と同期がとられる。

40

## 【0051】

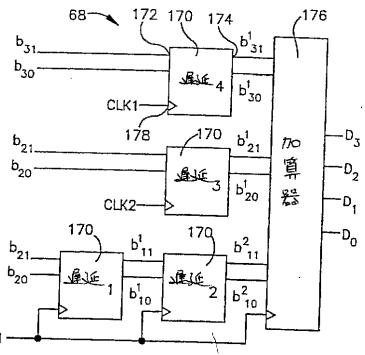

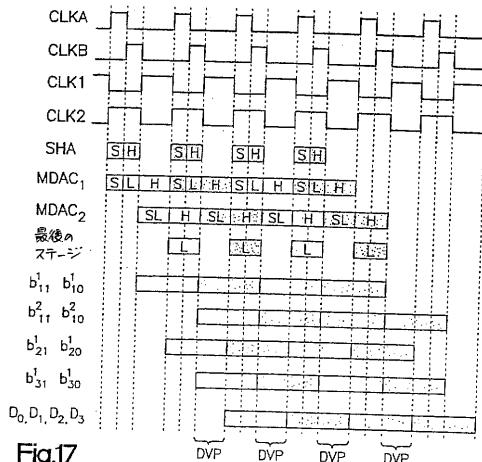

図16および図17を参照して、DLC回路68のタイミングがより詳細に考察される。

50

明確にするために、図16は4ビットA/D変換器のためのDLC回路68を示し、図17は関連のタイミング図を示す。MDAC<sub>1</sub>は、そのデジタル出力b<sub>11</sub>およびb<sub>10</sub>を(CLK2と一致する)CLKBの立下がり端縁でラッチする。b<sub>11</sub>およびb<sub>10</sub>を受取る第1の遅延ユニット170または遅延<sub>1</sub>は、CLK1の立上がり端縁でb<sub>11</sub>とb<sub>10</sub>とをサンプリングし、b<sub>11</sub>とb<sub>10</sub>との遅延されたバージョンまたはb<sup>1</sup><sub>11</sub>およびb<sup>1</sup><sub>10</sub>を出力し、上付き数字はビットが何回遅延されたかを示す。b<sub>11</sub>とb<sub>10</sub>とを受取る第2の遅延ユニット170または遅延<sub>2</sub>は、CLK1の次の立上がり端縁でb<sup>1</sup><sub>11</sub>とb<sup>1</sup><sub>10</sub>とをサンプリングし、b<sup>2</sup><sub>11</sub>とb<sup>2</sup><sub>10</sub>とを出力する。MDAC<sub>2</sub>は、そのデジタル出力b<sub>21</sub>とb<sub>20</sub>とをCLK1の立下がり端縁でラッチする。b<sub>21</sub>とb<sub>20</sub>とを受取る第1の遅延ユニット170または遅延<sub>3</sub>は、CLK2の立上がり端縁でb<sub>21</sub>とb<sub>20</sub>とをサンプリングし、b<sub>21</sub>とb<sub>20</sub>との遅延されたバージョンまたはb<sup>1</sup><sub>21</sub>とb<sup>1</sup><sub>20</sub>とを出力する。最後のステージ66は、そのデジタル出力b<sub>31</sub>とb<sub>30</sub>とをCLK2の立下がり端縁でラッチする。b<sub>31</sub>とb<sub>30</sub>とを受取る第1の遅延ユニット170または遅延<sub>4</sub>は、CLK1の立上がり端縁でb<sub>31</sub>とb<sub>30</sub>とをサンプリングし、b<sub>31</sub>とb<sub>30</sub>との遅延されたバージョンまたはb<sup>1</sup><sub>31</sub>とb<sup>1</sup><sub>30</sub>とを出力する。

## 【0052】

結果として得られる加算器への入力は、b<sup>2</sup><sub>11</sub>およびb<sup>2</sup><sub>10</sub>、b<sup>1</sup><sub>21</sub>およびb<sup>1</sup><sub>20</sub>、b<sup>1</sup><sub>31</sub>およびb<sup>1</sup><sub>30</sub>である。図17で示されるように、b<sup>1</sup><sub>21</sub>およびb<sup>1</sup><sub>20</sub>は、残りのビットよりも半クロックサイクル早く到着する。すべてのビットが所与のサンプルについて有効であるときの時間または時間範囲、またはデータ有効周期(DVP)は、すべての加算器入力がアナログ入力の同じサンプルを示す瞬間(moment(s))である。DVPは、CLK1の立上がり端縁でのビットb<sup>2</sup><sub>11</sub>、b<sup>2</sup><sub>10</sub>、b<sup>1</sup><sub>31</sub>およびb<sup>1</sup><sub>30</sub>の到着と、CLK2の立上がり端縁でのb<sup>1</sup><sub>21</sub>およびb<sup>1</sup><sub>20</sub>ビットの次のサンプルの到着との間にある。加算器176の出力、またはD<sub>0</sub>、D<sub>1</sub>、D<sub>2</sub>、およびD<sub>3</sub>は、DVP内にあるCLK1の立下がり端縁を用いて同期がとられる。当業者は、DVPの間に加算器176を同期させるために用いられるクロック信号およびビットをサンプリングするために遅延170によって用いられるクロック信号を変更して等しい結果を達成することができることを理解するだろう。たとえば、CLK1およびCLK2は互いに取替えられてもよく、および/または立上がり端縁および立下がり端縁は互いに取替えられてもよい。

## 【0053】

図15を参照して、例示されるDLC回路68は、各ステージが2つのデジタル出力を有する10ビットA/D変換器のためのものである。この10ビットA/D変換器のためのDLC回路68は、50の遅延70を必要とする。DLC回路68は、アナログ入力を示す、あらゆる数のデジタル出力ビットまたはNを有するA/D変換器にも適合され得ることが注目される。DLC回路68は、図6で示されるA/D変換器60にも、図1で示される従来のA/D変換器10にも、または他のあらゆるパイプラインA/D変換器にも用いられ得る。DLC回路68を用いるA/D変換器が奇数の出力ビットNを有し、各ステージがBの数のデジタル出力ビットを有し、デジタル出力を生成するMの数のステージが存在するならば(この発明のA/D変換器60は、出力ビット数Nよりも1つ少ないデジタル出力生成ステージMを有する)、遅延170の数は、以下の式を用いて計算され得る。

## 【0054】

## 【数7】

$$\text{遅延の数} = B \cdot 2 \left( 1 + 2 + \dots + \frac{M}{2} \right) = B \left( 1 + \frac{M}{2} \right) \left( \frac{M}{2} \right)$$

## 【0055】

デジタル出力ビット数Nが偶数ならば、遅延170の数は以下の式を用いて計算され得る。

10

20

30

40

50

【0056】

【数8】

$$\text{遅延の数} = B \left( 2 \left( 1 + 2 + \dots + \frac{M-1}{2} \right) + \frac{M+1}{2} \right) = B \left( \left( 1 + \frac{M-1}{2} \right) \left( \frac{M-1}{2} \right) + \frac{M+1}{2} \right)$$

【0057】

A / D 変換器 60 と従来の A / D 変換器 10 との各デジタル出力生成ステージは、 C L K 1 および C L K 2 ともここで呼ばれる 2 相の重なり合わないクロックの各クロックサイクルの間にデジタルデータビットを生成する。いずれか 1 つのステージのデジタル出力は本来、後続のデジタル出力生成ステージに半クロックサイクル先立つ。たとえば、 C L K 1 および C L K 2 が周期 T を有するならば、 M D A C<sub>1</sub> のデジタル出力は、 T / 2 または半クロックサイクルでラッチされ、その後 M D A C<sub>2</sub> のデジタル出力がラッチされる。各デジタル出力生成ステージのデジタル出力をラッチするのに用いられるような逆クロックを用いることによってそのデジタル出力を遅延することにより、図 14 の従来の D L C 回路 44 で示されるように、パイプライン内の 1 つ 1 つすべてのステージのために半クロックサイクル分だけ 1 つ 1 つのすべてのデータビットをシフトする必要がなくなる。したがって、デジタル出力生成ステージ当りより少ない遅延 170 が必要とされる。遅延の数を減じることによって、 D L C 回路 68 が必要とするハードウェアの量が減じられ、これによって D L C 回路 68 が必要とする電力が減じられ、遅延の数を減じることによってさらに、 D L C 回路 68 が生成するノイズも減じられる。加えて、遅延 170 が p / n トランスマッショングートおよび静止インバータで実現され、かつ加算器が当該技術分野で周知であるような従来の加算器で実現されるならば、 D L C 回路 68 のシリコン面積は 340 μm × 170 μm であり、電力消費は、 3.3V の電力供給で 40Mサンプル / 秒において 3mW よりも少ない。各デジタル出力生成ステージからの出力は、適切な数の全クロックサイクルまたは半クロックサイクル遅延され、すべてのデジタル出力生成ステージのすべてのデジタル出力がデータ有効周期の間に加算器に到着し、正しい D<sub>OUT</sub> が引出され得る。

【0058】

この発明の A / D 変換器 60 は、種々の応用で用いられるのに非常に適している。たとえば、 A / D 変換器 60 は、メモリ回路の一部として用いられ得る。加えて、 A / D 60 変換器は、個別部品とともに、または集積回路の一部として実現され得る。 A / D 変換器 60 が集積回路の一部として実現されるならば、 A / D 変換器 60 は、 0.35 μm CMOS 等の媒体内で公知の集積回路製造技術を用いて製造され得る。

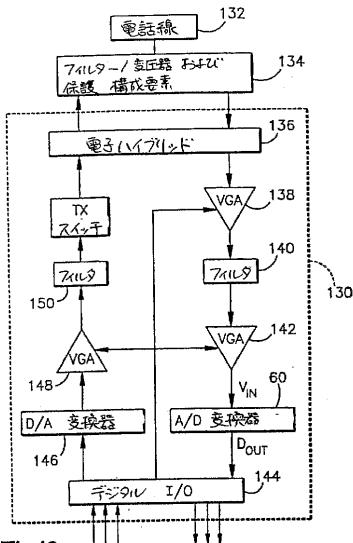

【0059】

別の例の応用として、 A / D 変換器 60 は、従来の R J 11 電話線 132 上で動作する 10Mbps またはより広い帯域幅の屋内ネットワークデータネットワーク等のネットワークデバイスの物理層またはアナログフロントエンド回路 130 ( 図 12 ) の一部として用いられ得る。図 12 を参照して、アナログフロントエンド回路 130 は、フィルタ、変圧器、およびサージ保護等の、データ信号を調整するための構成要素を有する回路 134 を介して電話線 132 からデータ信号を受取る。受取られた信号は、電子ハイブリッド回路 136 によって処理されて衝突検出等の機能が行なわれる。次に、受取られた信号は、第 1 の可変利得増幅器 ( VGA ) 138 、フィルタ 140 、および第 2 の VGA 142 を通つて伝わり受取られた信号がさらに調整される。調整された受取られた信号は、 V<sub>IN</sub> として A / D 変換器 60 に入力される。上でより詳細に説明されたように、 A / D 変換器 60 は、アナログ入力信号 V<sub>IN</sub> をデジタル出力 D<sub>OUT</sub> へと変換する。この応用では、 V<sub>IN</sub> は好ましくは 25 から 50Mサンプル / s でサンプリングされ、 D<sub>OUT</sub> は好ましくは 10 から 12 ビットを有する。次に、 D<sub>OUT</sub> は A / D 変換器 60 からデジタル入力 / 出力 ( I / O ) 回路 144 へと送られる。デジタル I / O 回路 144 は、アナログフロントエンド回路

10

20

30

40

50

130と、開放形システム間相互接続(open systems interconnection)(O S I)プロトコルスタックのデータリンク層を実現するための回路等の後続のネットワークデバイス回路との間のインターフェイスとして働く。

**【0060】**

アナログフロントエンド回路130が後続のネットワークデバイス回路から受取るデジタルデータ出力信号は、デジタルI/O回路144によって受取られる。デジタルデータ出力信号は、デジタル-アナログ(D/A)変換器146によって伝達アナログ信号へと変換される。伝達アナログ信号は、第3のVGA148によって調整される。第3のVGA148は、調節可能な利得伝達減衰器として働いてアナログフロントエンド回路130の伝達電力を設定するときの柔軟性を可能にする。減衰された伝達信号はさらにフィルタ150によって調整される。フィルタリングされ、かつ減衰された伝達信号は任意で伝達スイッチを通り、電子ハイブリッド回路136および回路134を介して電話線132へと送られる。

**【0061】**

この発明の具体的な実施例が詳細に説明されてきたが、この発明は、それに対応するよう範囲において限定されておらず、添付の請求項の範囲に入るすべての変化、変形、および均等物を含むことが理解されるべきである。

**【図面の簡単な説明】**

**【図1】** 従来の4ビットパイプラインアナログ - デジタル(A/D)変換器のブロック図である。

10

20

**【図2】** 従来のA/D変換器のステージを示す従来の複式デジタル - アナログ変換器(MDAC)のブロック図である。

**【図3】** 図2で示されるMDACの特性を示すグラフである。

**【図4】** 従来のA/D変換器のデジタル誤差訂正回路部分のシフティング動作を示す図である。

**【図5】** 図1で示されるA/D変換器の特性を示すグラフである。

**【図6】** この発明の1つの局面に従った10ビットパイプラインA/D変換器のブロック図である。

**【図7】** 図6で示されるA/D変換器に従ったサンプルホールド増幅器(SHA)ステージおよび第1の複式デジタル - アナログ変換器(MDAC)のブロック図である。

30

**【図8】** 図6で示されるA/D変換器に従ったSHAの回路図である。

**【図9】** 図6で示されるA/D変換器に従った第1のMDACの残差増幅器部分の回路図である。

**【図10】** 図6で示されるA/D変換器に従った第2のMDACおよび最後のステージのブロック図である。

**【図11】** 図6で示されるA/D変換器とともに用いられるための4ビットパイプラインA/D変換器のタイミング図である。

**【図12】** 図6で示されるA/D変換器を有するアナログフロントエンド回路のブロック図である。

**【図13】** 図1で示されるA/D変換器の従来のタイミング図である。

40

**【図14】** 従来のデジタル論理訂正(DLC)回路のブロック図である。

**【図15】** 10ビットパイプラインA/D変換器のためのこの発明に従ったデジタル論理訂正(DLC)回路のブロック図である。

**【図16】** 4ビットパイプラインA/D変換器のためのこの発明に従ったDLC回路のブロック図である。

**【図17】** 図16で示されるDLC回路を有する4ビットパイプラインA/D変換器のタイミング図である。

【図1】

【図4】

【図2】

【図3】

【図5】

【図6】

【図8】

【図7】

【図9】

【図10】

【図11】

Fig.11

【図12】

Fig.12

【図13】

Fig.13

(Prior Art)

【図14】

Fig.14

(Prior Art)

【図15】

【図16】

【図17】

---

フロントページの続き

(74)代理人 100083703

弁理士 仲村 義平

(74)代理人 100096781

弁理士 堀井 豊

(74)代理人 100098316

弁理士 野田 久登

(74)代理人 100109162

弁理士 酒井 將行

(72)発明者 チアン, メーイ - リン

アメリカ合衆国、95129 カリフォルニア州、サン・ノゼ、レインボードライブ、6497

審査官 柳下 勝幸

(56)参考文献 特表平5-502560(JP,A)

特開平5-14199(JP,A)

特開平11-88172(JP,A)

(58)調査した分野(Int.Cl., DB名)

H03M1/00-1/88