(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第5407976号

(P5407976)

(45) 発行日 平成26年2月5日(2014.2.5)

(24) 登録日 平成25年11月15日(2013.11.15)

(51) Int.Cl.

HO4J 3/00 (2006.01)

F 1

HO4J 3/00

H

請求項の数 18 (全 25 頁)

(21) 出願番号 特願2010-69760 (P2010-69760)

(22) 出願日 平成22年3月25日 (2010.3.25)

(65) 公開番号 特開2011-205329 (P2011-205329A)

(43) 公開日 平成23年10月13日 (2011.10.13)

審査請求日 平成24年8月29日 (2012.8.29)

(73) 特許権者 000006013

三菱電機株式会社

東京都千代田区丸の内二丁目7番3号

(74) 代理人 100113077

弁理士 高橋 省吾

(74) 代理人 100112210

弁理士 稲葉 忠彦

(74) 代理人 100108431

弁理士 村上 加奈子

(74) 代理人 100128060

弁理士 中鶴 一隆

(72) 発明者 鈴木 巨生

東京都千代田区丸の内二丁目7番3号 三菱電機株式会社内

最終頁に続く

(54) 【発明の名称】 通信装置、子局装置、通信システム及び通信方法

## (57) 【特許請求の範囲】

## 【請求項 1】

所定速度のクロックに同期して送信データを処理するデータ処理部と、

前記送信データのトラヒック有無を監視して制御信号を生成する制御部と、

前記クロックを整数倍に低速化する低速クロック生成部と、

前記制御信号に基づいて、前記送信データ又は前記低速クロックを異なる出力強度で送信

する送信部と、を備え、

前記送信部は、前記送信データを第1の出力強度で送信し、前記低速クロックを前記第1

の出力強度よりも小さな第2の出力強度で送信することを特徴とする通信装置。

## 【請求項 2】

所定速度のクロックに同期して送信データを処理する送信データ処理部と、

前記送信データのトラヒック有無を監視して第1の制御信号を生成する第1の制御部と、

前記クロックを整数倍に低速化する低速クロック生成部と、

前記第1の制御信号に基づいて、前記送信データ又は前記低速クロックを異なる出力強度

で送信する送信部と、

データを受信する受信部と、

前記受信データを前記所定速度のクロックに同期して処理する受信データ処理部と、

前記受信データから将来のデータ受信時間情報を抽出して第2の制御信号を生成する第2

の制御部と、を備え、

前記受信データ処理部は、前記第2の制御信号に基づいて受信データ処理機能を休止し、

10

20

前記送信部は、前記送信データを第1の出力強度で送信し、前記低速クロックを前記第1の出力強度よりも小さな第2の出力強度で送信することを特徴とする通信装置。

【請求項3】

前記制御部は、将来のデータ送信する時間情報を前記送信データとして生成することを特徴とする請求項1または請求項2に記載の通信装置。

【請求項4】

親局装置に同期して通信を行う子局装置において、

前記親局装置からデータを受信する受信部と、

前記受信データから前記親局装置が将来データ送信する時間情報を抽出して制御信号を生成する制御部と、

前記制御信号に基づいて、前記受信データから前記親局装置と同期したクロックを再生するクロック再生部と、

を備え、

前記受信部は、前記制御信号に基づいて、強度の異なる前記受信データを同一のレベル強度に増幅することを特徴とする子局装置。

【請求項5】

前記クロック再生部は、前記制御信号に基づいて分周率が切り替わる可変分周器を備えたことを特徴とする請求項4に記載の子局装置。

【請求項6】

親局装置に同期して通信する子局装置において、

前記親局装置からデータを受信する受信部と、

前記受信データから前記親局装置が将来データ送信する時間情報を抽出して第1の子局制御信号を生成する第1の制御部と、

前記第1の子局制御信号に基づいて、前記受信データから前記親局装置と同期したクロックを再生するクロック再生部と、

前記親局装置に送信するデータを生成する送信データ生成部と、

前記送信データを前記親局装置に送信する送信部と、

前記再生クロックに同期して前記送信データの有無情報を監視し、第2の子局制御信号を生成する第2の制御部と、

前記送信データ生成部と前記送信部の間に設けられ、前記送信データの波形整形およびタイミング再生を行うCDRと、

前記再生クロックを分周する分周器と、を備え、

前記送信データ生成部と前記CDRの間は、前記第2の子局制御信号に基づいて前記分周クロックで動作し、

前記受信部は、前記第1の子局制御信号に基づいて、強度の異なる前記受信データを同一のレベル強度に増幅することを特徴とする子局装置。

【請求項7】

前記クロック再生部は、前記第1の子局制御信号に基づいて分周率が切り替わる可変分周器を備えたことを特徴とする請求項6に記載の子局装置。

【請求項8】

前記第2の制御部は、前記送信データに将来の前記送信データのトラヒック有無情報を格納することを特徴とする請求項6または請求項7に記載の子局装置。

【請求項9】

親局装置と子局装置が同期して通信する通信システムにおいて、

前記親局装置は、

所定速度のクロックに同期して前記子局装置へ送信するデータを処理するデータ処理部と、

前記データの有無を監視して親局制御信号を生成すると共に、将来のデータ送信する時間情報を前記データとして生成する親局制御部と、

前記クロックを整数倍に低速化する低速クロック生成部と、

10

20

30

40

50

前記親局制御信号に基づいて、前記データ又は前記低速クロックを異なる出力強度で送信する送信部と、を備え、

前記送信部は、前記データを第1の出力強度で送信し、前記低速クロックを前記第1の出力強度よりも小さな第2の出力強度で送信し、

前記子局装置は、

前記親局装置から前記データ及び前記低速クロックを受信する受信部と、

前記受信データから前記親局装置が将来データ送信する時間情報を抽出して子局制御信号を生成する子局制御部と、

前記子局制御信号に基づいて、前記データ及び前記低速クロックから前記所定速度のクロックを再生するクロック再生部と、

を備え、

前記受信部は、前記子局制御信号に基づいて、強度の異なる前記受信データを同一のレベル強度に增幅することを特徴とする通信システム。

【請求項10】

前記クロック再生部は、前記子局制御信号に基づいて分周率が切り替わる可変分周器を備えたことを特徴とする請求項9に記載の通信システム。

【請求項11】

親局装置と子局装置が同期して通信する通信システムにおいて、

前記親局装置は、

所定速度のクロックに同期して前記子局装置へ送信するデータを処理するデータ処理部と、

前記データのトラヒック有無を監視してすると共に、将来のデータ送信する時間情報を前記データとして生成する親局制御部と、

前記クロックを整数倍に低速化する低速クロック生成部と、

前記親局制御信号に基づいて、前記データ又は前記低速クロックを異なる出力強度で送信する親局送信部と、を備え、

前記親局送信部は、前記データを第1の出力強度で送信し、前記低速クロックを前記第1の出力強度よりも小さな第2の出力強度で送信し、

前記子局装置は、

前記親局装置からデータ及び前記低速クロックを受信する受信部と、

前記受信データから将来のデータ受信情報を抽出して第1の子局制御信号を生成する第1の子局制御部と、

前記第1の子局制御信号に基づいて、前記受信データから前記所定速度のクロックを再生するクロック再生部と、

前記親局装置に送信するデータを生成する送信データ生成部と、

前記送信データを前記親局装置に送信する子局送信部と、

前記再生クロックに同期して前記送信データの有無情報を監視し、第2の子局制御信号を生成する第2の子局制御部と、

前記送信データ生成部と前記子局送信部の間に設けられ、前記送信データの波形整形およびタイミング再生を行うCDRと、

前記再生クロックを分周する分周器と、を備え、

前記送信データ生成部と前記CDRの間は、前記第2の子局制御信号に基づいて前記分周クロックで動作し、

前記受信部は、前記第1の子局制御信号に基づいて、強度の異なる前記受信データを同一のレベル強度に增幅することを特徴とする通信システム。

【請求項12】

前記クロック再生部は、前記第1の子局制御信号に基づいて分周率が切り替わる可変分周器を備えたことを特徴とする請求項11に記載の通信システム。

【請求項13】

親局装置と子局装置が同期して通信する通信システムにおいて、

10

20

30

40

50

前記親局装置は、

所定速度のクロックに同期して前記子局装置へ送信する下りデータを処理する下りデータ処理部と、

前記下りデータのトラヒック有無を監視して第1の親局制御信号を生成する第1の親局制御部と、

前記クロックを整数倍に低速化する低速クロック生成部と、

前記第1の親局制御信号に基づいて、前記下りデータ又は前記低速クロックを異なる出力強度で送信する親局送信部と、

上りデータを受信する親局受信部と、

前記上りデータを前記所定速度のクロックに同期して処理する上りデータ処理部と、

10

前記上りデータから将来の上りデータ受信時間情報を抽出して第2の親局制御信号を生成する第2の親局制御部と、を備え、

前記親局送信部は、前記下りデータを第1の出力強度で送信し、前記低速クロックを前記第1の出力強度よりも小さな第2の出力強度で送信し、

前記子局装置は、

前記親局装置から下りデータ及び前記低速クロックを受信する子局受信部と、

前記下りデータから前記親局装置が将来下りデータを送信する時間情報を抽出して第1の子局制御信号を生成する第1の子局制御部と、

前記第1の子局制御信号に基づいて、前記下りデータから前記所定速度のクロックを再生するクロック再生部と、

20

前記親局装置に送信する上りデータを生成する上りデータ生成部と、

前記上りデータを前記親局装置に送信する子局送信部と、

前記再生クロックに同期して前記上りデータの有無情報を監視し、第2の子局制御信号を生成すると共に、前記上りデータに将来の前記上りデータのトラヒック有無情報を格納する第2の子局制御部と、

前記上りデータ生成部と前記子局送信部の間に設けられ、前記送信上りデータの波形整形およびタイミング再生を行うCDRと、

前記再生クロックを分周する分周器と、を備え、

前記子局受信部は、前記第1の子局制御信号に基づいて、強度の異なる前記受信データを同一のレベル強度に増幅し、

30

前記親局装置は、前記第2の親局制御信号に基づいて前記上りデータ処理部を休止し、

前記子局装置は、前記第2の子局制御信号に基づいて前記上りデータ生成部と前記CDRの間を前記分周クロックで動作させることを特徴とする通信システム。

#### 【請求項14】

前記クロック再生部は、前記第1の子局制御信号に基づいて分周率が切り替わる可変分周器を備えたことを特徴とする請求項13に記載の通信システム。

#### 【請求項15】

親局装置と子局装置が所定速度のクロックに同期して通信する通信システムにおいて、前記親局装置が送信するデータのトラヒック有無を監視して将来データを送信する時間情報を前記子局装置へ通知する工程と、

40

前記親局装置が前記時間情報に基づいて前記データ又は前記所定速度を整数倍に低速化した低速クロックのいずれか一方を異なる出力強度で前記子局装置に送信する工程と、

前記子局装置が前記時間情報に基づいて前記データ及び前記低速クロックから前記所定速度のクロックを再生する工程と、を有し、

前記親局装置は、前記データを第1の出力強度で送信し、前記低速クロックを前記第1の出力強度よりも小さな第2の出力強度で送信することを特徴とする通信方法。

#### 【請求項16】

前記子局装置は、前記時間情報に基づいて自装置のデータ受信機能を休止することを特徴とする請求項15に記載の通信方法。

#### 【請求項17】

50

前記子局装置は、送信するデータの波形整形およびタイミング再生を行うC D Rを備え、前記親局装置へ送信するデータのトラヒック有無を監視し、送信するデータが無い期間は前記所定速度よりも低速で前記C D Rへデータを入力することを特徴とする請求項15または請求項16に記載の通信方法。

【請求項18】

前記子局装置は、前記親局装置へ送信するデータのトラヒック有無を監視し、将来データを送信する時間情報を前記親局装置へ通知する工程を有し、

前記親局装置は、前記時間情報に基づいて自装置のデータ受信機能を休止することを特徴とする請求項17に記載の通信方法。

【発明の詳細な説明】

10

【技術分野】

【0001】

本発明は、常時信号を送信することで子局の通信装置と同期して動作している親局の通信装置、子局の通信装置、及びこの通信装置を用いた通信システム、並びに通信方法の省電力化に関するものである。

【背景技術】

【0002】

光通信の一形態であるP O N (P a s s i v e O p t i c a l N e t w o r k )システムにおいては、通信プロトコルを用いて有効データの有無を監視し、有効データが存在する区間のみ、間欠的に信号を送信する方法が提案されている（例えば、特許文献1参照）。

20

【先行技術文献】

【特許文献】

【0003】

【非特許文献1】R . K u b o et al . , " P r o p o s a l a n d P e r f o r m a n c e A n a l y s i s o f a P o w e r - S a v i n g M e c h a n i s m f o r 10 G i g a b i t C l a s s P a s s i v e O p t i c a l n e t w o r k S y s t e m s , " N O C 2 0 0 9 .

【発明の概要】

【発明が解決しようとする課題】

30

【0004】

しかしながら、P O Nシステムのように親局と子局が同期して動作する通信システムにおいては、通信プロトコルに対応して有効データが存在する区間のみ間欠的に光信号を生成してデータを送信すると、無信号状態から有効データを送信する際に同期の確立に数ミリ秒程度の時間を要し、同期確立までの間にデータを損失する恐れがある。

【0005】

本発明はこのような問題を解決するためになされたもので、データを損失すること無く、消費電力を低減できる通信装置、子局装置及び通信システム、並びに通信方法を得ることを目的とする。

【課題を解決するための手段】

40

【0006】

本発明に係る通信装置は所定速度のクロックに同期して送信データを処理するデータ処理部と、送信データのトラヒック有無を監視して制御信号を生成する制御部と、クロックを整数倍に低速化する低速クロック生成部と、制御信号に基づいて送信データ又は前記低速クロックを異なる出力強度で送信する送信部とを備え、送信部は、送信データを第1の出力強度で送信し、低速クロックを第1の出力強度よりも小さな第2の出力強度で送信するものである。

【0007】

また、本発明に係る通信システムは、親局装置と子局装置が同期して通信する通信システムであって、親局装置は、所定速度のクロックに同期して子局装置へ送信するデータを処

50

理するデータ処理部と、データの有無を監視して親局制御信号を生成すると共に、将来のデータ送信する時間情報をデータとして生成する親局制御部と、クロックを整数倍に低速化する低速クロック生成部と、親局制御信号に基づいて、データ又は低速クロックを異なる出力強度で送信する送信部とを備え、送信部は、データを第1の出力強度で送信し、低速クロックを第1の出力強度よりも小さな第2の出力強度で送信し、子局装置は、親局装置からデータ及び低速クロックを受信する受信部と、受信データから親局装置が将来データ送信する時間情報を抽出して子局制御信号を生成する子局制御部と、子局制御信号に基づいて、データ及び低速クロックから所定速度のクロックを再生するクロック再生部とを備え、受信部は、子局制御信号に基づいて、強度の異なる受信データを同一のレベル強度に増幅するものである。

10

#### 【0008】

本発明にかかる通信方法は、親局装置と子局装置が所定速度のクロックに同期して通信する通信システムにおいて、親局装置が送信するデータのトラヒック有無を監視して将来データを送信する時間情報を子局装置へ通知する工程と、親局装置が時間情報に基づいて前記データ又は前記所定速度を整数倍に低速化した低速クロックのいずれか一方を異なる出力強度で子局装置に送信する工程と、子局装置が時間情報に基づいてデータ及び低速クロックから所定速度のクロックを再生する工程とを有し、親局装置は、データを第1の出力強度で送信し、低速クロックを第1の出力強度よりも小さな第2の出力強度で送信するものである。

20

#### 【発明の効果】

#### 【0009】

本発明によれば、通信装置は所定速度のクロックに同期して送信データを処理するデータ処理部と、送信データのトラヒック有無を監視して制御信号を生成する制御部と、クロックを整数倍に低速化する低速クロック生成部と、制御信号に基づいて送信データ又は前記低速クロックを異なる出力強度で送信する送信部とを備えたことにより、データを損失することなく、消費電力を低減できる通信装置を得ることができる。

#### 【0010】

また、本発明によれば、親局装置と子局装置が同期して通信する通信システムにおいて、親局装置は、所定速度のクロックに同期して子局装置へ送信するデータを処理するデータ処理部と、データの有無を監視して親局制御信号を生成すると共に、将来のデータ送信する時間情報をデータとして生成する親局制御部と、クロックを整数倍に低速化する低速クロック生成部と、親局制御信号に基づいて、データ又は低速クロックを異なる出力強度で送信する送信部とを備え、子局装置は、親局装置からデータ及び低速クロックを受信する受信部と、受信データから親局装置が将来データ送信する時間情報を抽出して子局制御信号を生成する子局制御部と、子局制御信号に基づいて、データ及び低速クロックから所定速度のクロックを再生するクロック再生部とを備えたことにより、データを損失することなく、消費電力を低減できる通信システムを得ることができる。

30

#### 【0011】

また、本発明によれば、親局装置と子局装置が所定速度のクロックに同期して通信する通信システムにおいて、親局装置が送信するデータのトラヒック有無を監視して将来データを送信する時間情報を子局装置へ通知する工程と、親局装置が時間情報に基づいて前記データ又は前記所定速度を整数倍に低速化した低速クロックのいずれか一方を異なる出力強度で子局装置に送信する工程と、子局装置が時間情報に基づいてデータ及び低速クロックから所定速度のクロックを再生する工程とを備えたことにより、データを損失することなく、消費電力を低減できる通信方法を得ることができる。

40

#### 【図面の簡単な説明】

#### 【0012】

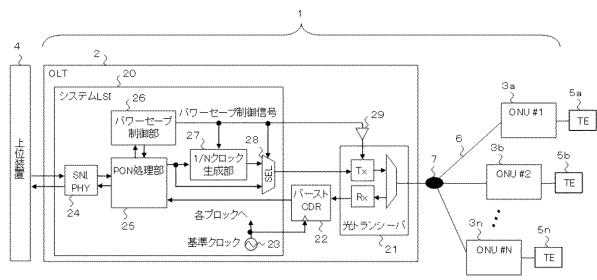

【図1】本発明の実施の形態1に係るPONシステムの構成を示す図である。

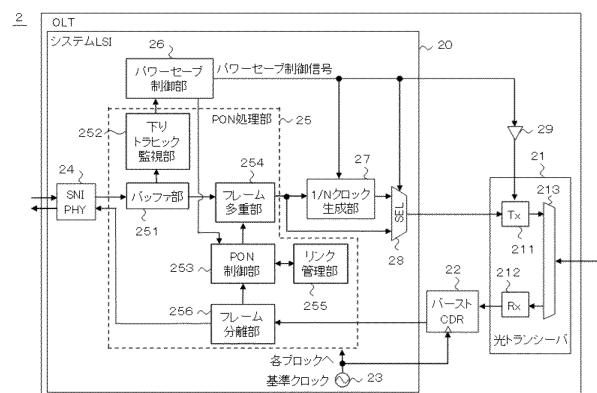

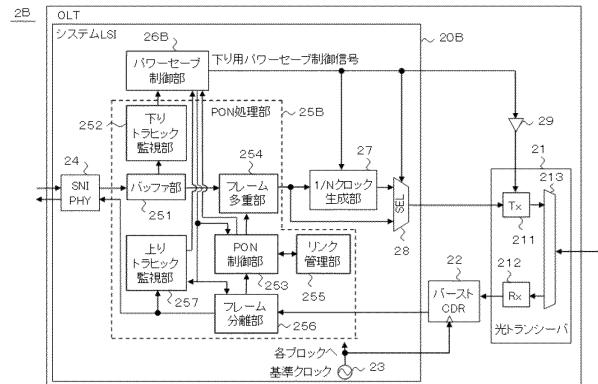

【図2】本発明の実施の形態1に係るOLTの構成を示す図である。

50

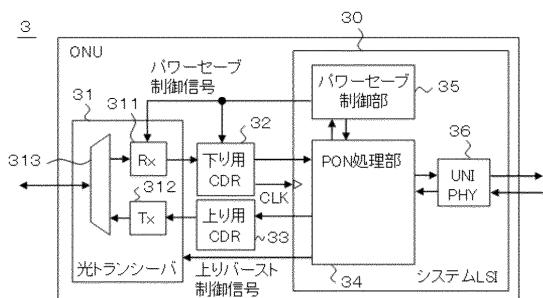

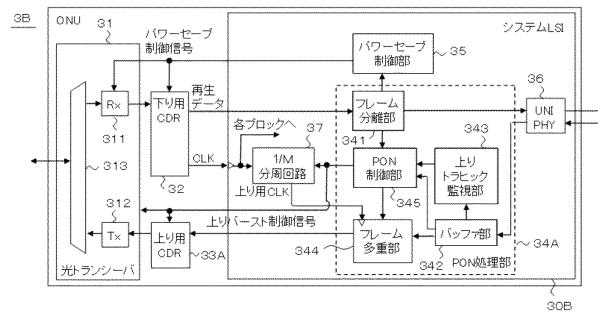

【図3】本発明の実施の形態1に係るONUの構成を示す図である。

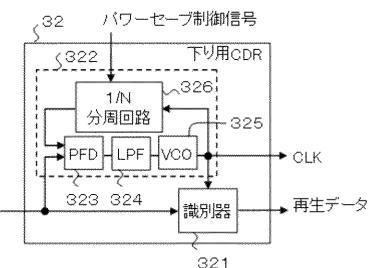

【図4】実施の形態1における下り用CDRの構成を示す図である。

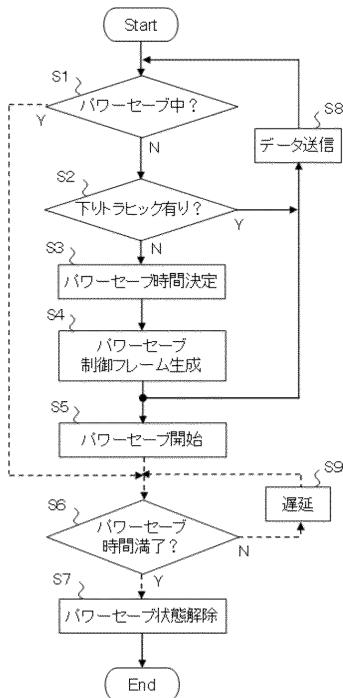

【図5】実施の形態1におけるOLTの動作を示すフローチャートである。

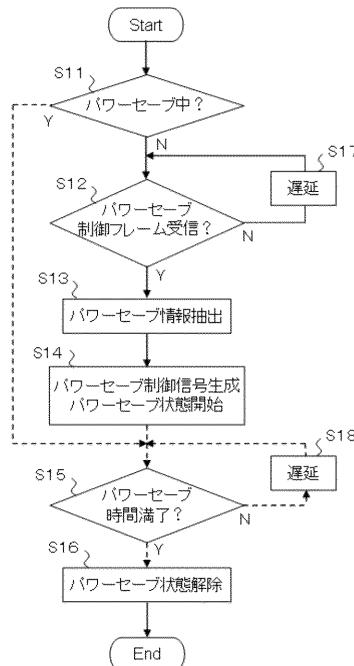

【図6】実施の形態1におけるONUの動作を示すフローチャートである。

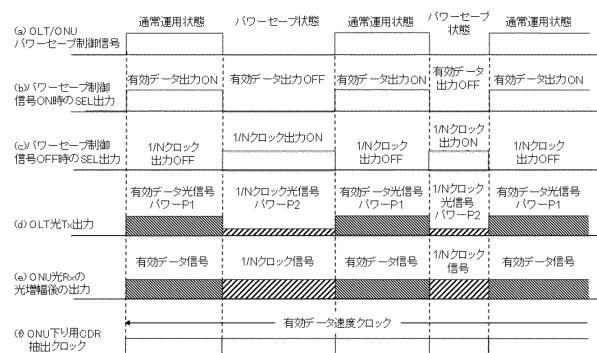

【図7】実施の形態1に係るPONシステムの信号出力タイミングを示す図である。

【図8】実施の形態1に係るPONシステムの制御シーケンスを示す図である。

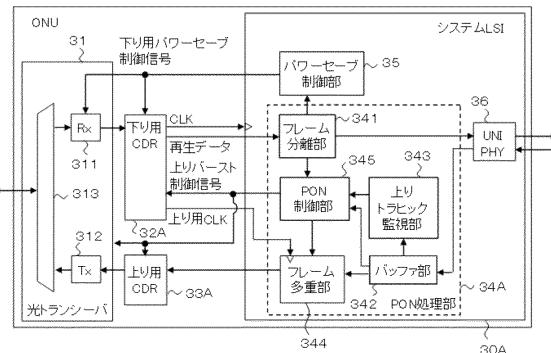

【図9】本発明の実施の形態2に係るONUの構成を示す図である。

【図10】実施の形態2における下り用CDRの構成を示す図である。

【図11】実施の形態2における上り用CDRの構成を示す図である。

【図12】実施の形態2におけるONUの動作を示すフローチャートである。 10

【図13】本発明の実施の形態3に係るOLTの構成を示す図である。

【図14】本発明の実施の形態3に係るONUの構成を示す図である。

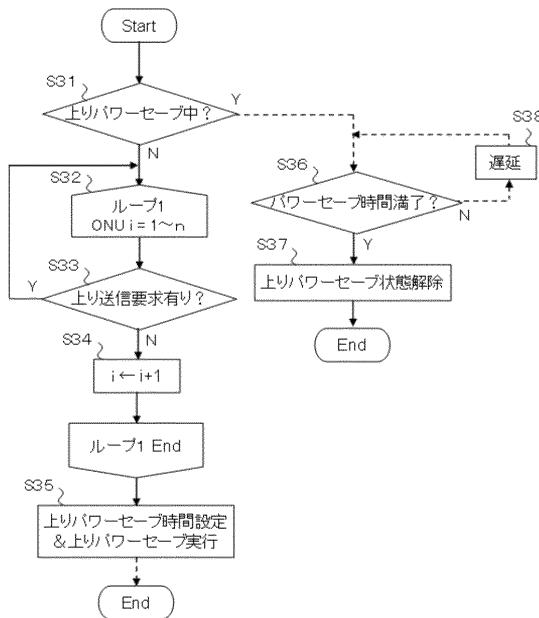

【図15】実施の形態3におけるOLTの動作を示すフローチャートである。

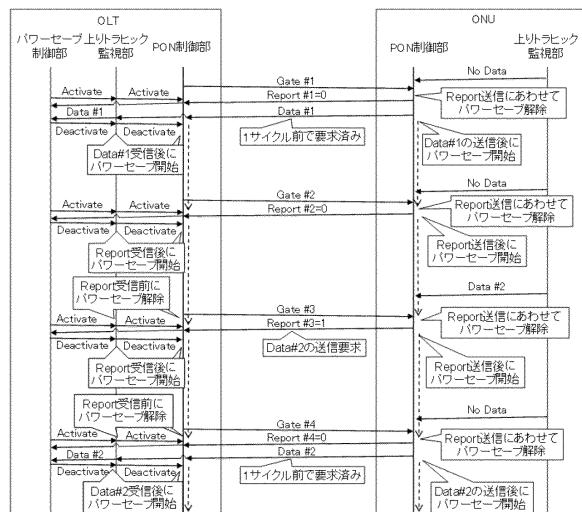

【図16】実施の形態3に係るPONシステムの制御シーケンスを示す図である。

【発明を実施するための形態】

【0013】

実施の形態1.

本発明を実施する実施の形態1におけるPONシステムを図1ないし図8を用いて説明する。図1において、PONシステム1は上位装置4と加入者端末であるTE(Terminal Equipment)5の間に設けられ、上位装置4のネットワーク側に接続された通信装置であるOLT(Optical Line Terminal)2すなわち親局装置と、TE5 a~5nに接続したONU(Optical Network Unit)3a~3nすなわち子局装置と、OLT2およびONU3a~3nを接続する光ファイバ6と、光ファイバ6の途中に配置され、OLT2から送信された光信号を各ONU3a~3n向けに分岐する光カプラ7とで構成されている。TE5としては、例えばHGW(Home Gate Way)、VoIP(Voice over Internet Protocol-Terminal Adapter)、PCなどがある。

ここではONU3がn台(nは整数)接続された場合を示しているが、1台以上であれば何台でも良く、各ONU3に接続するTE5も1台のみならず複数台であっても良い。また、PONシステム1では一般に、OLT2からONU3向きを下り方向、ONU3からOLT2向きを上り方向と呼ぶ。 30

【0014】

OLT2は、CMOS半導体等で形成された電気信号を処理するシステムLSI20と、システムLSI20で処理する電気信号と光ファイバ6上を伝送する光信号とをE/O変換またはO/E変換する光トランシーバ21と、光トランシーバ21を駆動する駆動回路29とを備えている。また、光トランシーバ21とシステムLSI20の間にはバーストCDR(Clock and Data Recovery)22が設けられ、ONU3からバースト的に送信される信号を入力としてデータとクロックを再生すると共に、システムLSI20上の各素子を駆動する基準クロック23へ載せ替えを行っている。

【0015】

システムLSI20は、基準クロック23と、上位装置4と信号の送受信を行うSNI(Service Node Interface)PHY24と、GE-PON(ギガビットEthernet(登録商標)-PON)システムのPON処理と同等のフレーム処理機能を有するPON処理部25すなわち送信データ処理部、下りトラヒック量に基づいて通常運用状態とパワーセーブ状態とを切り替えるパワーセーブ制御信号すなわち親局制御信号を生成すると共に、パワーセーブする時間情報を有効データとして生成し、PON処理部25に転送するパワーセーブ制御部26と、基準クロック23をN分周(Nは整数)して低速クロックを生成する1/Nクロック生成部27すなわち低速クロック生成部と、パワーセーブ制御信号に基づいてPON処理部25から出力されるフレームを1/Nクロックに切替えるセレクタ28と、を備えている。 40 50

## 【0016】

PON処理部25は、図2に示すように、SNI-PHY24からのデータを一時的に蓄積するバッファ部251と、上位装置4からPONシステム1へ送信する下りデータのトラヒック量を監視する下りトラヒック監視部252と、制御フレームを生成してONU3との間で送受信することによりPONシステム1区間を制御するPON制御部253と、バッファ部251およびPON制御部253から出力された有効データをフレームとして多重するフレーム多重部254と、PON制御部253と連動してONU3との間のリンク状態を管理するリンク管理部255と、ONU3から受信したフレームをユーザデータフレームと制御フレームに分離するフレーム分離部256を備えている。

なお、データ処理を行う各ブロックはソフトウェアで構成しても良い。

10

## 【0017】

光トランシーバ21は駆動回路29の出力に基づいて、システムLSI20から入力された電気信号を出力P1の高速光信号または出力P2の低速光信号にE/O変換してPONシステム1に送信する光送信器211と、PONシステム1から受信した光信号を電気信号にO/E変換してシステムLSI20へ出力する光受信器212と、送信光信号及び受信光信号を合分波する光合分波器213とで構成されている。

なお、低速光信号の出力P2は高速光信号の出力P1よりも小さく、例えば高速光信号の伝送速度が10GHz程度であれば駆動電流20mA程度の出力強度を要するのに対し、伝送速度が100MHz程度まで低速化すると駆動電流3mA程度の出力強度に抑えることができる。

20

## 【0018】

ONU3は、図3に示すように、光ファイバ6上を伝送する光信号を電気信号にO/E変換すると共に、ONU3内で用いた電気信号を光ファイバ6上を伝送する光信号にE/O変換する光トランシーバ31すなわち受信部と、CMOS半導体等で形成され、電気信号を処理するシステムLSI30と、光トランシーバ31とシステムLSI30との間に設けられ、PONシステム1から受信した信号に基づいてデータおよびクロックを再生する下り用CDR32すなわちクロック再生部と、システムLSI30から受取った信号を整形すると共にタイミング調整を行う上り用CDR33とを備えている。

## 【0019】

システムLSI30は、制御フレームを生成してOLT2との間で送受信することによりPONシステム1区間の制御、すなわちPON制御を行うPON処理部34と、PON処理部34と連携してOLT2がパワーセーブする時間情報を抽出し、パワーセーブ制御信号すなわち子局制御信号を生成するパワーセーブ制御部35と、TE5と信号の送受信を行うUNI(User Network Interface)PHY36とを備え、下り用CDR32で抽出された再生クロックに同期して動作する。

30

## 【0020】

光トランシーバ31は、パワーセーブ制御信号に基づいてPONシステム1から受信した高速光信号および低速光信号を同程度の光強度に増幅し、O/E変換して下り用CDR32へ出力する光受信器311と、上り用CDR33から入力された電気信号を所定強度の光信号にE/O変換してPONシステム1に送信する光送信器312と、送信光信号及び受信光信号を合分波する光合分波器313とで構成されている。

40

## 【0021】

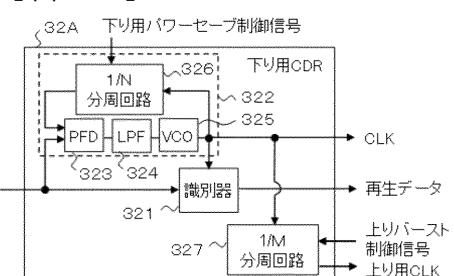

下り用CDR32は、図4に示すように、光受信器311からの入力信号とフィードバック信号の位相差を検出する位相比較器323と、位相比較器323の出力を平均化し、電圧として出力するループフィルタ324と、ループフィルタ324の電圧を所定の発振周波数で発振するようフィードバック制御するVCO(Voltage Controlled Oscillator)325すなわち電圧制御発振器と、で構成されたPLL(Phase-locked Loop)回路322と、再生したクロックに同期して受信したデータを再生する識別器321を備えている。また、VCO325から位相比較器323へのフィードバック回路の途中にはパワーセーブ制御信号に基づいて分周率が変化す

50

る 1 / N 分周回路 326 すなわち可変分周器が設けられている。

【0022】

なお、PONシステム1はGE-PONシステムと同様に、リンクを維持するため定期的にOLT2のPON制御部253とONU3のPON処理部34の間で制御フレームをやり取りして、リンクが維持されている場合にのみデータ通信を行う。

【0023】

次に動作について説明する。

まず、下り方向の通信について説明する。OLT2は、上位装置4からSNI-PHY24を介して入力されたデータはバッファ部251及び下りトラヒック監視部252に送られ、バッファ部251に一次蓄積されたデータはその後フレーム多重部254に送られる。下りトラヒック監視部252は下り方向のトラヒック量を監視し、その情報をパワーセーブ制御部26に伝達する。パワーセーブ制御部26は下りトラヒック監視部252から受取ったトラヒック情報、PON制御部253がPON制御を行う制御フレームのトラヒック情報、およびパワーセーブ制御部26自身が生成するパワーセーブの時間情報を格納したパワーセーブ制御フレームのトラヒック情報を合わせて有効データとし、この有効データの有無を判定して有効データが無い場合にパワーセーブ制御信号をLow出力する。

10

【0024】

PON制御部253はパワーセーブ制御信号に基づいて、ONU3とのリンク維持やPON制御するための制御フレームを生成すると共に、パワーセーブ制御部26から受取ったパワーセーブ制御フレームをフレーム多重部254へ出力する。フレーム多重部254はバッファ部251からのデータフレームとPON制御部253からのフレームを時分割多重して出力する。

20

なお、ここではリンク維持やPON制御の詳細説明は省略するが、例えばGE-PONシステムと同様にプロトコルの一種であるMPCP(Multi-Point Control Protocol)を利用すれば、DiscoveryプロセスやGate/Reportプロセスで実現できる。

【0025】

フレーム多重部254の出力は2つに分岐された後、一方は1/Nクロック生成部27に入力され、他方は直接セレクタ28に送られる。1/Nクロック生成部27は入力信号を元に基準クロック23をN倍に低速化した低速クロックデータを生成し、パワーセーブ制御信号がLow、すなわち有効データが無くIDLEデータで補間された状態を示しているとき、フレーム多重部254からの信号を低速クロックデータに置換したデータをセレクタ28へ出力する。セレクタ28はパワーセーブ制御信号に基づいて、有効データがある状態ではフレーム多重部254から入力される有効データを、有効データが無い状態では1/Nクロックデータを選択して光送信器211へ出力する。

30

なお、1/Nクロック生成部27では常時低速クロックを出力し、セレクタ28にてパワーセーブ制御信号に対応した有効データと低速クロックデータの出力切り替えを行っても良い。

【0026】

パワーセーブ制御信号は光トランシーバ21の駆動回路29にも伝えられ、駆動回路29はこれを元に光送信器211の光出力強度を切替える制御信号を生成する。光送信器211はシステムLSI20から電気信号が入力されると光信号にE/O変換し、この光信号を駆動回路29からの制御信号に応じて出力強度P1またはP2に調整してPONシステム1に向けて送信する。

40

【0027】

ここで、図5は上記OLT2のシステムLSI20について、下り通信用の各機能をソフトウェアで構成した場合の動作を説明するフローチャートである。

システムLSI20はパワーセーブ中であるか否かを判定し(S1)、パワーセーブ中で無い、すなわち通常運用状態であると判定すれば上位装置4から下りデータのトラヒックが有るか無いかを確認する(S2)。下りトラヒックが無い場合はパワーセーブ状態の開

50

始時間及び継続時間を決定し(S3)、これらの時間情報を格納したパワーセーブ制御フレームを生成し(S4)、ONU3へ送信する(S8)。その後、パワーセーブ制御信号の出力タイミングに合わせてOLT2全体をパワーセーブ状態に遷移させ、PONシステム1に向けて低速の1/Nクロックデータを低出力で送信する(S5)。パワーセーブ状態にあるOLT2は定期的にパワーセーブ制御の継続時間が満了したか否かを確認し(S6)、継続時間満了であると判定するとS7にてパワーセーブ状態を解除し、S1の工程に戻る。なお、パワーセーブ状態の解除とは、通常運用状態で高速かつ高出力の光信号を送信することを意味する。

#### 【0028】

S1においてパワーセーブ中であると判定した場合、パワーセーブ状態にあるOLT2はS6にてパワーセーブ制御の継続時間が満了したか否かを確認する。また、S2において下りトラヒックが有ると判断した場合、高速かつ高出力の光信号としてONU3へデータを送信する(S8)。S8では下りトラヒックの他に、PON制御に必要な制御フレームや上記のパワーセーブ制御フレームも有効データとして高速かつ高出力の光信号に変換して送信する。S6においてパワーセーブ制御の継続時間が満了していない場合は、予め定めた期間だけ待って(S9)再びS6の工程に戻る。

10

なお、図内の実線は通常運用状態を、破線はパワーセーブ状態であることを示している。

#### 【0029】

このように、OLT2は有効データの有無に応じて、有効データ送信用の高速かつ高出力の光信号と、この光信号にタイミング同期した低速クロックデータ送信用の低速かつ低出力の光信号とを切替えることにより、消費電力を低減できる。

20

なお、ここでいう高速/低速および高出力/低出力とは2種類の光信号を比較した場合の速度および出力強度であり、具体的な基準によるものでは無い。

#### 【0030】

一方、ONU3は、PONシステム1から光信号が入力されると、光トランシーバ31の光受信器311で受信する。光受信器311は光信号をパワーセーブ制御信号に基づいて所定レベルに増幅した後に電気信号にO/E変換し、下り用CDR32に出力する。

#### 【0031】

下り用CDR32は電気信号を2分岐して一方を識別器321に、他方をPLL回路322の位相比較器323に送る。位相比較器323は光受信器311からの信号とVCO325からのフィードバック信号を入力としてループフィルタ324に位相差を出力し、ループフィルタ324は入力された2つの信号の位相差を平均化して電圧に変換した値をVCO325に出力する。VCO325は所定の発振周波数で発振するため、PLL回路322はフィードバック制御を行って適切な電圧が得られるように調整する。

30

#### 【0032】

フィードバック回路の途中に設けられた1/N分周回路326はパワーセーブ制御信号に基づいて適切な分周率に切り替えられ、VCO325からの信号をN分周して位相比較器323に出力する。PLL回路322の出力は再生クロックとして識別器331に送られ、入力データのたたき直しに用いられる。識別器321にてたたき直されたデータは再生データとして、再生クロックと共にシステムLSI30に送られる。

40

#### 【0033】

システムLSI30に送られたデータは、PON処理部34にて上位装置4からのデータを格納したデータフレーム、PON制御に用いられる制御フレーム、パワーセーブ用のパワーセーブ制御フレームに分離され、データフレームはUNI-PHY36を介してTE5に転送される。一方、制御フレームはGE-PONシステムと同様にPON処理部34内でPON制御に用いられ、パワーセーブ制御フレームはパワーセーブ制御部35に転送される。

#### 【0034】

パワーセーブ制御部35はOLT2がパワーセーブする時間情報をパワーセーブ制御フレームから抽出し、自装置であるONU3用のパワーセーブ制御信号を生成する。例えは光

50

受信器 311 に高速光信号の受信状態を示す H i g h レベルのパワーセーブ制御信号が入力されると、光受信器 311 は受信信号の増幅前の光強度は駆動電流 20 mA 程度であるとし、低速光信号の受信状態を示す L o w レベルのパワーセーブ制御信号が入力されると、増幅前の光強度が駆動電流 3 mA 程度であるとして、受信した光信号を同レベルの強度まで増幅した後に電気信号に O / E 変換する。

#### 【 0035 】

ここで、高速光信号の周波数が 10 GHz、低速光信号の周波数が 1 GHz の場合を例として 1 / N 分周回路 336 の切替え動作について説明する。

下り用 CDR32 に高速光信号の受信状態を示すパワーセーブ制御信号が入力されると、1 / N 分周回路 336 の分周率は N = 1 に設定され、低速光信号の受信状態を示すパワーセーブ制御信号が入力されると、1 / N 分周回路 336 の分周率は N = 10 に変更される。

10

#### 【 0036 】

このように、パワーセーブ制御信号に基づいて分周率可変の 1 / N 分周回路 336 を用いることにより、ONU3 はOLT2 から速度及び強度の異なる光信号を受信しても常に高速データの処理速度と等しいクロックを抽出できる。

また、ONU3 はパワーセーブ制御信号に応じて、自身の PON 処理部 34 の下り方向の機能をスリープさせて省電力化を図ることもできる。

#### 【 0037 】

ここで、図 6 は上記 ONU3 のシステム LSI30 について、各機能をソフトウェアで構成した場合の動作を説明するフローチャートである。

20

システム LSI30 はパワーセーブ中であるか否かを判定し (S11)、パワーセーブ中で無いと判定すればパワーセーブ制御フレームを受信しているか否かを確認する (S12)。パワーセーブ制御フレームを受信している場合はパワーセーブ状態の開始時間及び継続時間の情報を抽出し (S13)、これらの時間情報に合わせて自装置向けのパワーセーブ制御信号を出力すると共に、ONU3 全体をパワーセーブ状態に遷移させる (S14)。S12 にてパワーセーブ制御フレームを受信していないと判断した場合は予め定めた期間だけ待って (S17)、再度 S12 の工程を繰り返す。

#### 【 0038 】

S11 にてパワーセーブ中であると判定した場合、パワーセーブ状態にある ONU3 は定期的にパワーセーブ制御の継続時間が満了したか否かを確認し (S15)、継続時間満了であると判定するとパワーセーブ状態を解除し (S16)、高速かつ高出力の光信号を受信できる状態 (S11) に戻る。また、S15 においてパワーセーブ制御の継続時間が満了していないと判定した場合も予め定めた期間だけ待って (S18)、再び S15 の工程に戻る。

30

なお、図内の実線は通常運用状態を、破線はパワーセーブ状態であることを示している。

#### 【 0039 】

ところで、図 7 は OLT2 及び ONU3 のパワーセーブ制御信号とこれに関連する信号の出力タイミングを示す図である。ただし、この図は動作を模式的に示すものであって内部回路遅延等によるタイミング誤差は含んでおらず、また、GE-PON システムと同様に OLT2 と ONU3 は時刻同期していることを前提としている。ここでいう時刻同期とは、すなわち、OLT2 が自身の内部クロックで時刻 T0 のときに ONU3 へフレームを送信すると、ONU3 はこのフレームを受信する時刻が自身の内部クロックの時刻 T0 となるよう調整することを意味する。

40

#### 【 0040 】

図 7 (a) は OLT2 及び ONU3 がそれぞれ自装置に対してパワーセーブ制御信号を出すタイミングを示しており、OLT2 のセレクタ 28 は、パワーセーブ制御信号の出力が H i g h で通常運用状態を示しているときは図 7 (b) に示すように有効データを出力し、パワーセーブ制御信号の出力が L o w でパワーセーブ状態を示しているときは図 7 (c) に示すように 1 / N クロックデータを出力する。

50

## 【0041】

OLT2の光送信器211は、図7(d)に示すように、有効データの出力時は高速伝送に耐えられるよう比較的強度の大きな出力P1で光信号を送信し、1/Nクロックデータの出力時は出力P1よりも強度の小さな出力P2で光信号を送信する。これに対し、ONU3の光受信器311は、図7(e)に示すように、有効データの高速光信号および1/Nクロックデータの低速光信号が同じ光強度となるよう増幅し、E/O変換して電気信号として出力する。また、上述のとおり、ONU3の下り用CDR32はパワーセーブ制御信号に応じて1/N分周回路336の分周率を適切な値に切替えるため、図7(f)に示すように、パワーセーブ状態であるか否かに関わらず常に有効データの処理速度と等しいクロックを抽出できる。

10

## 【0042】

このように、OLT2がパワーセーブする時間に対応してONU3のパワーセーブ制御信号を生成することにより、OLT2が速度及び強度の異なる光信号を送信してもONU3は常に有効データの処理速度と等しいクロックを再生できるため、有効データを損なうこと無く受信できる。

## 【0043】

次に、上り方向の通信について説明する。

ONU3は、TE5からユーザデータフレームを受信すると、UNI-PHY37を介してPON処理部34に取り込み、PON制御用の制御フレームと時間多重して上り用CDR33に出力する。

20

なお、10GHz程度の高速信号を伝送する場合、ONU3は送信信号の波形整形及びタイミング調整のために上り用CDR33を用いる必要がある。上り方向のデータは各ONU3からバースト的に出力されるが、上り用CDR33の同期確立には数秒程度を要するため、有効データの不在時にはPON処理部34にてIDLEデータを補間し、システムLSI30と上り用CDR33の間は有効データの有無に関わらず連続的にデータ伝送する。

## 【0044】

上り用CDR33はPON処理部34から入力された信号を、タイミング調整すると共に波形整形して光トランシーバ31の光送信器312に送る。PON処理部34はまた、ユーザデータフレーム及び制御フレームで構成される有効データのバースト送出期間と、バースト補間期間とを信号レベルHigh/Lowで識別する上りバースト制御信号を生成し、光トランシーバ31に出力する。光送信器312は受け取った電気信号を予め定めた出力強度の光信号にE/O変換し、上りバースト制御信号がHighレベルで有効データ送出期間を示しているとき、PONシステム1に向けてこの光信号を送信する。上りバースト制御信号がLowレベルで上りバーストデータが不在の時は、光トランシーバ31からは何も送信しない。

30

## 【0045】

一方、OLT2はPONシステム1を伝送してきた光信号を、光合分波器213を介して光受信器212にて受信し、所定レベルの信号に増幅した後に電気信号にO/E変換してバーストCDR22に出力する。バーストCDR22は入力信号からデータとクロックを再生すると共に、再生したデータを基準クロック23にクロック載せ替えし、システムLSI20に出力する。

40

## 【0046】

システムLSI20に入力された再生データは、フレーム分離部256にてユーザデータフレームと制御フレームとに分離される。分離されたユーザデータフレームはSNI-PHY24を介して上位装置4に転送され、制御フレームはPON制御部253に送られる。PON制御部253は、GE-PONシステムと同様に、制御フレームを用いてPON制御を行うと共にリンク管理部255と連携してONU3とのリンク維持を図る。

## 【0047】

ここまで各装置の動作である。続けてPONシステム1のシステム動作について説明す

50

る。

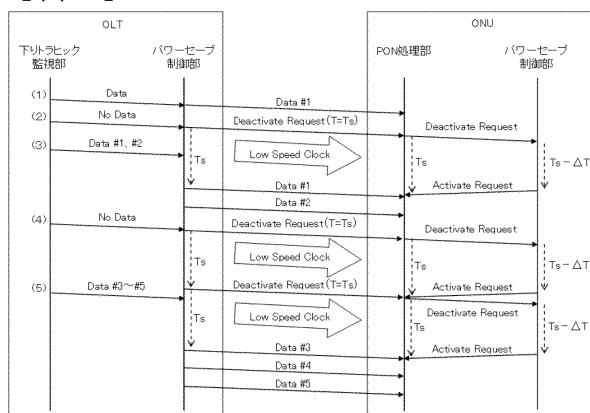

図8は下り方向のパワーセーブ制御シーケンスを示す図である。例えば(1)のように上位装置4からのデータが有る場合、OLT2の下りトラヒック監視部252はパワーセーブ制御部26にその情報を伝え、パワーセーブ制御部26はPON処理部25にデータを出力させる。ONU3はこのデータを受信すると、PON処理部34にて有効データとして処理する。

#### 【0048】

ところで(2)のように上位装置4からOLT2へのデータが無い場合、下りトラヒック監視部252は下りトラヒックが無いという情報をパワーセーブ制御部26に伝える。パワーセーブ制御部26はPON処理部35が生成する制御フレーム等のトラヒック情報を加味して予め定めた継続時間Tsだけパワーセーブすることを決め、パワーセーブ制御の開始時間および継続時間の情報を格納したパワーセーブ制御フレームを生成してONU3へ送信する。その後、パワーセーブ制御部26は決定した開始時間から所定の継続時間が満了するまでの間、自装置内をパワーセーブ状態にするパワーセーブ制御信号を出力し、光トランシーバ21はこのパワーセーブ制御信号に対応して1/N低速クロックデータをONU3に連続的に送信する。

#### 【0049】

ONU3はパワーセーブ制御フレームを受信すると、パワーセーブ制御部35にてフレーム内に格納されたパワーセーブ制御の開始時間および継続時間Tsの情報を抽出し、OLT2のパワーセーブ状態に対応できるよう自装置向けのパワーセーブ制御信号を生成する。このパワーセーブ制御信号はOLT2がパワーセーブ状態を解除してデータ送信してきた場合に、データを損なうこと無く受信できるタイミングでONU3の各構成要素に対して出力される。図8ではパワーセーブ制御部35からPON処理部34にパワーセーブ状態解除を指示するActivate Requestを出力しているが、同時にパワーセーブ制御信号を用いて光受信器311及び下り用CDR32にもパワーセーブ状態の解除を指示することは言うまでもない。

#### 【0050】

さて、(3)のようにパワーセーブ中に上位装置4からデータが送られてきた場合、下りトラヒック監視部252はその情報をパワーセーブ制御部26に伝える。OLT2のパワーセーブ状態は継続時間Ts満了まで継続され、このデータはバッファ部251に一時蓄積される。パワーセーブ制御部26は継続時間Tsが満了すると、下りトラヒック監視部252よりデータ有りの情報を受けたか否かを確認し、データがある場合にはバッファ部251に一次蓄積したデータをONU3へ送信する。

#### 【0051】

バッファ部251に蓄積されたデータをすべて送出すると、OLT2は再び下りトラヒック監視部252より(4)のようなデータ無しの情報を受取る、あるいは予め定めた所定時間に何も情報を受取らなければ、上記(2)と同様にパワーセーブ状態に遷移する。(5)のように、パワーセーブ継続時間Tsの満了時までに下りトラヒック監視部252からデータ有りの情報が伝達されていなければ、パワーセーブ制御部26は下りトラヒックが無いと判断してOLT2のパワーセーブ状態を継続するようパワーセーブ制御フレームをONU3宛に送信する。(5)のデータは上記(3)と同様に、次のパワーセーブ継続時間Tsが満了するまでバッファ部251にて一次蓄積され、その後ONU3へ送信される。以降、OLT2及びONU3は同様の動作を繰り返す。

#### 【0052】

この実施の形態によれば、OLT2は有効データのトラヒック有無に応じてパワーセーブ制御信号を生成し、通常運用状態では高速かつ出力強度の大きな光信号を送信すると共に、パワーセーブ状態では低速かつ通常運用状態よりも出力強度の小さな光信号を送信することにより、消費電力を低減できる。

#### 【0053】

また、OLT2はパワーセーブ状態の開始時間及び継続時間の情報を格納したパワーセー

10

20

30

40

50

ブ制御フレームを生成してONU3へ送信し、ONU3はこのパワーセーブ制御フレームを受信すると上記の時間情報を抽出して自装置向けのパワーセーブ制御信号を生成してパワーセーブ制御を行うことにより、ONU3はOLT2が速度及び強度の異なる光信号を送信しても常に有効データの処理速度と等しいクロックを抽出することができ、有効データを損なうこと無く受信できる。さらに、ONU3はパワーセーブ制御信号に応じて自身のPON処理部34における下り方向の機能をスリープさせて省電力化を図ることもできる。

また、このようなOLT2及びONU3で構成されるPONシステム1も、有効データを損失すること無く消費電力を低減できる。

#### 【0054】

10

##### 実施の形態2.

上記実施の形態1ではOLTのパワーセーブについて示したが、実施の形態2ではあわせてONUのパワーセーブも行う。本実施の形態に係るPONシステムを図9ないし図12を用いて説明する。なお、実施の形態1と同じ構成については同一符号を付して説明を省略する。

#### 【0055】

PONシステム1及びOLT2の構成は実施の形態1と同じである。また、ONU3Aも図9に示すように、システムLSI30Aと下り用CDR32A以外は実施の形態1と同じ構成を有し、CMOS半導体等で形成されるシステムLSI30Aは、PON処理機能を有するPON処理部34Aと、パワーセーブ制御部35すなわち第1の子局制御部と、UNI-PHY37とを備えている。

20

#### 【0056】

PON処理部34Aは、下り方向のフレームをPON制御用の制御フレーム、パワーセーブ制御フレーム、データフレームに分離するフレーム分離部341と、TE5から受信した上り方向のユーザデータを一時的に蓄積するバッファ部342と、上り方向のユーザデータのトラヒック有無を監視する上りトラヒック監視部343と、OLT2との間でPON制御を行うPON制御部345すなわち第2の子局制御部と、バッファ部342に一次蓄積されたユーザデータのデータフレーム及びPON制御部345からの制御フレームを時分割多重するフレーム多重部344とで構成されている。

#### 【0057】

30

また、下り用CDR32Aすなわちクロック再生部は、図10に示すように、実施の形態1に記載のPLL回路322および識別器321に加え、PON制御部345からの上りバースト制御信号すなわち第2の子局制御信号に基づいて再生クロックを分周率M(Mは整数)で低速化する1/M分周回路327すなわち可変分周器を備えている。

システムLSI30A上の各ブロックは下り用CDR32Aで抽出した再生クロックに同期して動作するが、フレーム多重部344は1/M分周回路327から出力される上り用クロックに同期して動く。

#### 【0058】

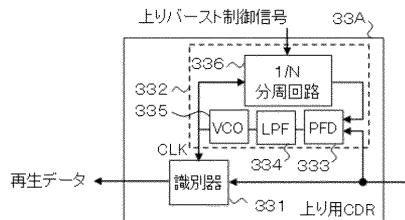

上り用CDR33Aは、図11に示すように、フレーム多重部344からの入力信号とフィードバック信号の位相差を検出する位相比較器333と、位相比較器333の出力を平均化し、電圧として出力するループフィルタ334と、ループフィルタ334の電圧を所定の発振周波数で発振するようフィードバック制御するVCO335とで構成されたPLL回路332と、再生したクロックに同期して受信したデータを再生する識別器331を備えている。また、VCO335から位相比較器333へのフィードバック回路の途中には上りバースト制御信号に基づいて分周率が変化する1/N分周回路336が設けられている。

40

#### 【0059】

次に動作について説明する。

まず、下り方向の通信について説明する。OLT2は実施の形態1と同じため、説明を省略する。

50

一方、ONU3AはPONシステム1から光信号が入力されると、光トランシーバ31の光受信器311で受信する。光受信器311は光信号をパワーセーブ制御信号に基づいて所定レベルに増幅した後に電気信号にO/E変換し、下り用CDR32Aに出力する。

#### 【0060】

下り用CDR32Aでは電気信号を2分岐して一方を識別器321、他方をPLL回路322の位相比較器323に送る。位相比較器323は光受信器311からの信号とVCO325からのフィードバック信号を入力としてループフィルタ324に位相差を出力し、ループフィルタ324は入力された2つの信号の位相差を平均化して電圧に変換した値をVCO325に出力する。VCO325は所定の発振周波数で発振するため、PLL回路322はフィードバック制御を行って適切な電圧が得られるように調整する。

10

#### 【0061】

フィードバック回路の途中に設けられた1/N分周回路326は下り用パワーセーブ制御信号に基づいて適切な分周率に切り替えられ、VCO325からの信号をN分周して位相比較器323に出力する。PLL回路322の出力は再生クロックとして識別器321に送られ、入力データのたたき直しに用いられる。識別器321にてたたき直されたデータは再生データとして、再生クロックと共にシステムLSI30Aに送られる。

#### 【0062】

また、1/M分周回路327はPON制御部345からの上りバースト制御信号の立下りエッジを検出すると再生クロックを分周率Mで低速化し、上りバースト制御信号の立上りエッジを検出すると再生クロックそのものを上り用クロックとしてシステムLSI30Aのフレーム多重部344に出力する。

20

#### 【0063】

システムLSI30Aに送られた再生データは、フレーム分離部341にて上位装置4からのデータを格納したデータフレーム、PON制御に用いられる制御フレーム、下りパワーセーブ用のパワーセーブ制御フレームに分離され、データフレームはUNI-PHY37を介してTE5に転送される。一方、制御フレームはGE-PONシステムと同様にPON制御部345に送られ、パワーセーブ制御フレームはパワーセーブ制御部35に転送される。

#### 【0064】

パワーセーブ制御部35はOLT2が下り方向のパワーセーブを実行する時間情報を受信したパワーセーブ制御フレームから抽出し、自装置であるONU3A用のパワーセーブ制御信号を生成する。例えば光受信器311に高速光信号の受信状態を示すHighレベルのパワーセーブ制御信号が入力されると、光受信器311は受信信号の増幅前の光強度は駆動電流20mA程度であるとし、低速光信号の受信状態を示すLowレベルのパワーセーブ制御信号が入力されると、増幅前の光強度が駆動電流3mA程度であるとして、受信した光信号を同レベルの強度まで増幅した後に電気信号にO/E変換する。

30

#### 【0065】

ここで、高速光信号の周波数が10GHz、低速光信号の周波数が1GHzの場合を例として1/N分周回路336の切替え動作について説明する。

下り用CDR32Aに高速光信号の受信状態を示すパワーセーブ制御信号が入力されると、1/N分周回路336の分周率はN=1に設定され、低速光信号の受信状態を示すパワーセーブ制御信号が入力されると、1/N分周回路336の分周率はN=10に変更される。

40

#### 【0066】

このように、パワーセーブ制御信号に基づいて分周率可変の1/N分周回路336を用いることにより、ONU3AはOLT2から速度及び強度の異なる光信号を受信しても常に高速データの処理速度と等しいクロックを抽出できる。

また、ONU3AはOLT2が下り方向のパワーセーブを実行する時間に対応して下り用パワーセーブ制御信号を生成することにより、OLT2が速度及び強度の異なる光信号を送信しても常に有効データの処理速度と等しいクロックを再生でき、有効データを損なう

50

こと無く受信できる。

また、ONU3Aはパワーセーブ制御信号に応じて、自身のPON処理部34Aの下り方向の機能をスリープさせて省電力化を図ることもできる。

また、実施の形態1と同様に、システムLSI30Aの下り方向通信に関する各機能をソフトウェアで構成することもできる。

#### 【0067】

次に、上り方向の通信について説明する。

ONU3Aは、TE5からユーザデータフレームを受信すると、UNI-PHY37を介してPON処理部34A内のバッファ部342を取り込む。バッファ部342はユーザデータを一時的に蓄積すると共に上りトラヒック監視部343に転送し、上りトラヒック監視部343は上りトラヒック量の情報をパワーセーブ制御部35に伝達する。

10

#### 【0068】

PON制御部345はOLT2とのリンク維持やPON制御するための制御フレームを生成するのに加え、この制御フレームのトラヒック情報と上りトラヒック監視部343から受取ったユーザデータのトラヒック情報から上り有効データの有無を判定する。上り有効データが有ると判定した場合は、OLT2から受信した制御フレームの情報に基づいてフレーム多重部344にデータ送信指示と共に、下り用CDR32Aと光トランシーバ31へ上りバースト送信タイミングにあわせて上りバースト制御信号をHighレベルで出力する。一方、上りバーストデータが無いと判定した場合はフレーム多重部344へは何も指示せず、下り用CDR32Aと光トランシーバ31へ上りバースト制御信号をLowレベルで出力する。

20

#### 【0069】

バッファ部342で一時蓄積されたユーザデータフレーム及びPON制御部345で生成された制御フレームは共にフレーム多重部344に伝達され、PON制御部345の指示に基づいて、時分割多重で上り用CDR33Aに送られる。なお、フレーム多重部344はユーザデータフレーム及び制御フレームの不在時にはIDLEデータを補間して連続信号を出力する。

#### 【0070】

ところで、フレーム多重部344と上り用CDR33A間の高速信号伝送には非常に大きな電力消費を伴う。PON制御部345は有効データを送出時には上りバースト制御信号をHighレベルで出力するため、下り用CDR32Aは上りバースト制御信号の立上りエッジを検出して再生クロックを上り用クロックとして出力し、フレーム多重部344はこの再生クロックに同期して動作する。

30

#### 【0071】

一方、上りバーストデータ不在時にはPON制御部345は上りバースト制御信号をLowレベルで出力するため、下り用CDR32Aは上りバースト制御信号の立下りエッジを検出して再生クロックを分周率Mで低速化したクロックを上り用クロックとして出力し、フレーム多重部344は低速クロックに同期して動作する。

このようにして、上りバーストデータ不在時にフレーム多重部344と上り用CDR33A間を低速クロックで動作に切替えることにより、消費電力が大幅に低減できる。

40

#### 【0072】

ところで、上り用CDR33Aに設けられた1/N分周回路336の分周率は上りパワーセーブ制御信号に基づいて適切な値に切り替えられる。例えば、周波数が10GHzの高速光信号が入力される場合、上りバースト制御信号も入力されて分周率はN=1となり、周波数が1GHzの低速光信号で上りバースト制御信号が入力されない場合、分周率はN=10に切り替えられる。このように、上り用CDR33AのVCO335は入力データの速度によらず安定的に発振するため、上り用CDR33Aに入力されたデータはタイミング調整及び波形整形され、光トランシーバ31の光送信器312に送られる。

#### 【0073】

光送信器312は受け取った電気信号を予め定めた出力強度の光信号にE/O変換し、P

50

ON制御部345からの上りバースト制御信号がHighレベルで上りバーストデータの送出期間を示しているときはPONシステム1に向けてこの光信号を送信し、上りバースト制御信号がLowレベルのときは上りバーストデータが不在なので光トランシーバ31からは何も送信しない。

【0074】

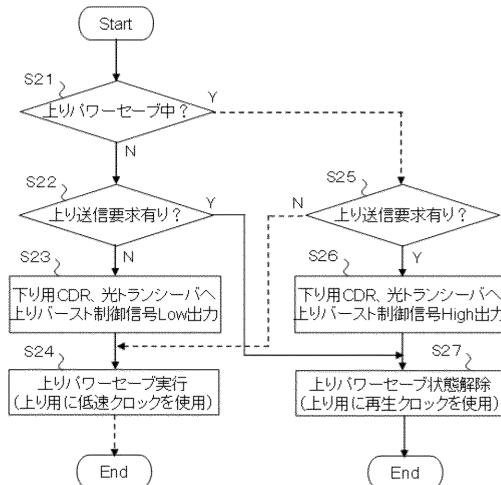

ここで、図12は上記ONU3AのシステムLSI30Aについて、上り方向のパワーセーブに関する各機能をソフトウェアで構成した場合の動作を説明するフローチャートである。

まず、上り方向のパワーセーブ中であるか否かを判定し(S21)、パワーセーブ中で無い、すなわち通常運用状態であると判定すればTE5から上りデータのトラヒック送信要求が有るか無いかを確認する(S22)。上り送信要求が無い場合は下り用CDR32A及び光トランシーバ31へ上りバースト制御信号をLow出力し(S23)、上り方向のパワーセーブを実行するために下り用CDR32Aに上り用低速クロックを生成させ、システムLSI30Aと上り用CDR33A間を低速で信号伝送させ(S24)、フローを終了する。

10

【0075】

S21においてパワーセーブ中であると判定した場合も、TE5から上りデータのトラヒック送信要求が有るか無いかを確認し(S25)、上り送信要求が有る場合は下り用CDR32A及び光トランシーバ31へ上りバースト制御信号をHigh出力し(S26)、上り方向のパワーセーブ状態を解除してシステムLSI30Aと上り用CDR33A間を下り用CDR32Aが抽出する再生クロックに同期して高速で信号伝送させ(S27)、フローを終了する。

20

【0076】

また、S22において上りトラヒック送信要求が有ると判定した場合はS26に状態遷移し、S25において上りトラヒック送信要求が無いと判定した場合はS23へ状態遷移する。

なお、図内の実線は通常運用状態を、破線はパワーセーブ状態であることを示している。

【0077】

ところで、OLT2はPONシステム1を伝送してきた光信号を、光合分波器213を介して光受信器212にて受信し、所定レベルの信号に増幅した後に電気信号にO/E変換してバーストCDR22に出力する。バーストCDR22は入力信号からデータとクロックを再生すると共に、再生したデータを基準クロック23にクロック載せ替えし、システムLSI20に出力する。

30

【0078】

システムLSI20に入力された再生データは、フレーム分離部256にてユーザデータフレームと制御フレームとに分離される。分離されたユーザデータフレームはSNI-PHY24を介して上位装置4に転送され、制御フレームはPON制御部253に送られる。PON制御部253は、GE-PONシステムと同様に制御フレームを用いてPON制御を行うと共にリンク管理部255と連携してONU3Aとのリンク維持を図る。

なお、本実施の形態はONU3A内部の動作が実施の形態1と異なるのみで、PONシステム1のシステム動作は同じであるため説明を省略する。

40

【0079】

この実施の形態によれば、実施の形態1の効果に加えて、ONU3AのPON制御部345がユーザデータフレームと制御フレームで構成される上りバーストデータの送信タイミングにあわせて上りバースト制御信号を生成し、下り用CDR32Aは上りバースト制御信号に基づいて上りバーストデータの不在時に低速クロックを生成し、システムLSI30Aと上り用CDR33A間を低速で信号伝送させることにより、ONU3Aの消費電力を大幅に低減できる。

また、このようなOLT2及びONU3Aで構成されるPONシステムも、有効データを損失すること無く実施の形態1に記載のPONシステム1よりもさらに消費電力を低減で

50

きる。

【0080】

実施の形態3.

上記実施の形態2では、上りバーストデータが無い場合にONU3Aの下り用CDR32Aにて低速クロックを生成し、システムLSIと上り用CDR間の消費電力を低減している。本実施の形態では、下り用CDR32Aの代わりにシステムLSI上で上り用の低速クロックを生成する。また、OLTに接続するいずれのONUからも上りバーストデータを受信しない場合に上り方向の機能を休止させてOLTの更なるパワーセーブを図る。本実施の形態に係るPONシステム1を図13ないし図16を用いて説明する。なお、実施の形態1または実施の形態2と同じ構成については同一符号を付して説明を省略する。

10

【0081】

PONシステム1の構成は実施の形態1と同じである。

OLT2Bは、図13に示すように、システムLSI20B以外は実施の形態1と同じ構成を有し、CMOS半導体等で形成されるシステムLSI20Bは、基準クロック23と、SNI-PHY24と、PON処理機能を有するPON処理部25Bすなわち下りデータ処理部兼上りデータ処理部と、実施の形態1に記載のパワーセーブ制御部26の機能に加えて上り方向のバーストデータ不在時に上りパワーセーブ制御信号すなわち第2の親局制御信号を生成するパワーセーブ制御部26Bと、1/Nクロック生成部27すなわち低速クロック生成部と、下り用パワーセーブ制御信号に基づいてPON処理部25Bから出力されるフレームと1/Nクロックを切替えるセレクタ28を備えている。

20

【0082】

PON処理部25Bは、SNI-PHY24からのデータを一時的に蓄積するバッファ部251と、上位装置4からPONシステム1へ送出する下りデータのトラヒック量を監視する下りトラヒック監視部252と、制御フレームを生成してONU3Bとの間で送受信することによりPONシステム1区間を制御するPON制御部253と、バッファ部251およびPON制御部253から出力された有効データをフレームとして多重するフレーム多重部254と、PON制御部253と連動してONU3Bとの間のリンク状態を管理するリンク管理部255と、ONU3Bから受信したフレームをユーザデータフレームと制御フレームに分離するフレーム分離部256に加えて、上りのユーザデータフレームのトラヒック量を監視する上りトラヒック監視部257とで構成されている。

30

【0083】

一方、ONU3Bは、図14に示すように、システムLSI30B以外は実施の形態1と同じ構成を有し、CMOS半導体等で形成されるシステムLSI30Bは、PON処理機能を有するPON処理部34Aと、パワーセーブ制御部35と、UNI-PHY37に加え、下り用CDR32で抽出された再生クロックをPON制御部345からの上りバースト制御信号に基づいて分周率Mで低速化する1/M分周回路37とを備えている。

なお、OLT2B及びONU3Bのデータ処理を行う各ブロックはソフトウェアで構成しても良い。

【0084】

次に動作について説明する。

40

下り方向の通信は実施の形態1と同じであるため省略し、上り方向の通信について説明する。

ONU3Bは、TE5からユーザデータフレームを受信すると、UNI-PHY37を介してPON処理部34A内のバッファ部342に取り込む。バッファ部342はユーザデータを一時的に蓄積すると共に上りトラヒック監視部343に転送し、上りトラヒック監視部343は上りトラヒック量の情報をパワーセーブ制御部35に伝達する。

【0085】

PON制御部345はOLT2Bとのリンク維持やPON制御するための制御フレームを生成するのに加え、この制御フレームのトラヒック情報と上りトラヒック監視部343から受取ったユーザデータのトラヒック情報から上り有効データの有無を判定する。上り有

50

効データが有ると判定した場合は、OLT2Bから受信した制御フレームの情報に基づいてフレーム多重部344にデータ送信指示をすると共に、1/M分周回路37と光トランシーバ31へ上りバースト送信タイミングにあわせて上りバースト制御信号をHighレベルで出力する。一方、上りバーストデータが無いと判定した場合はフレーム多重部344へは何も指示せず、1/M分周回路37と光トランシーバ31へ上りバースト制御信号をLowレベルで出力する。

#### 【0086】

バッファ部342で一時蓄積されたユーザデータフレーム及びPON制御部345で生成された制御フレームは共にフレーム多重部344に伝達され、PON制御部345の指示に基づいて、時分割多重で上り用CDR33Aに送られる。なお、フレーム多重部344はユーザデータフレーム及び制御フレームの不在時にはIDLEデータを補間して連続信号を出力する。

10

#### 【0087】

1/M分周回路37は、上りバーストデータの送信時にHighレベルに切替えられる上りバースト制御信号の立上りエッジを検出し、フレーム多重部344を駆動する上り用クロックとして抽出した再生クロックを出力する。

#### 【0088】

一方、上りバーストデータ不在時には上りバースト制御信号がLowレベルに切替えられるため、1/M分周回路37は上りバースト制御信号の立下りエッジを検出して、再生クロックを分周率Mで低速化したクロックをフレーム多重部344を駆動する上り用クロックとして出力する。

20

このように、上りバーストデータ不在時にフレーム多重部344と上り用CDR33A間を低速クロックで動作に切替えることにより、実施の形態2と同様に消費電力を大幅に低減できる。

#### 【0089】

上り用CDR33Aは入力された信号を、タイミング調整すると共に波形整形して光トランシーバ31の光送信器312に送る。光送信器312は受け取った電気信号を予め定めた出力強度の光信号にE/O変換し、PON制御部345からの上りバースト制御信号がHighレベルで上りバーストデータの送出期間を示しているときはPONシステム1に向けてこの光信号を送信し、上りバースト制御信号がLowレベルのときは上りバーストデータが不在なので光トランシーバ31からは何も送信しない。

30

なお、システムLSI30Bの各機能をソフトウェアで構成した場合の動作は実施の形態2とほぼ同じで、上りバースト制御信号の出力先が下り用CDR32Aの代わりに1/M分周回路37になる点のみ異なる。

#### 【0090】

ところで、OLT2BはPONシステム1を伝送してきた光信号を、光合分波器213を介して光受信器212にて受信し、所定レベルの信号に増幅した後に電気信号にO/E変換してバーストCDR22に出力する。バーストCDR22は入力信号からデータとクロックを再生すると共に、再生したデータを基準クロック23にクロック載せ替えし、システムLSI20Bに出力する。

40

#### 【0091】

システムLSI20Bに入力された再生データは、フレーム分離部256にてユーザデータフレームと制御フレームとに分離され、ユーザデータフレームはSNI-PHY24を介して上位装置4に転送される。上りトラヒック監視部257はフレーム分離部256からSNI-PHY24に送られるユーザデータフレームを監視して上りトラヒック情報を抽出し、パワーセーブ制御部26Bに伝達する。

#### 【0092】

一方、分離された制御フレームはPON制御部253に送られ、PON制御部253はこの制御フレームを用いてPON制御を行うと共にリンク管理部255と連携してONU3Bとのリンク維持を図る。PON制御部253は、OLT2Bがリンク維持している各O

50

ONU3Bに上りデータの送信タイミングを割り当てるため、OLT2Bが各ONU3Bから上りデータを受信する時間を把握している。

【0093】

パワーセーブ制御部26Bは上りトラヒック監視部257からの上りトラヒック情報に加え、PON制御部253からリンク維持している各ONU3Bの上りデータを受信する時間情報を受取り、いずれのONU3Bからも上りバーストデータを受信しない期間を示す上り用パワーセーブ制御信号を生成する。この上り用パワーセーブ制御信号はPON制御部253、フレーム分離部256、上りトラヒック監視部257に伝達され、上り用パワーセーブ制御信号により指定された期間、各ブロックの上り通信機能を休止させる。

【0094】

ここで、図15は上記OLT2BのシステムLSI20Bについて、上り方向のパワーセーブに関する各機能をソフトウェアで構成した場合の動作を説明するフローチャートである。

まず、上り方向のパワーセーブ中であるか否かを判定し(S31)、パワーセーブ中で無い、すなわち通常運用状態であると判定すれば、リンクしている各ONU3BについてID番号iを特定し(S32)、上りトラヒック送信要求が有るか無いかを確認する(S33)。上り送信要求が無い場合はS34にてID番号iに1加算し、S32に戻る。リンクしている全ONU3BについてS32～S34を実行すると、上り方向のパワーセーブ時間を設定して上り通信に必要な各機能のパワーセーブを実行し(S35)、フローを終了する。

【0095】

S31においてパワーセーブ中であると判定した場合はパワーセーブ時間が満了したか否かを確認し(S36)、時間満了していれば上りパワーセーブ状態を解除し(S37)、フローを終了する。S36にてパワーセーブ時間が満了していないと判断した場合は、予め定めた期間だけ待って(S38)再びS36の工程に戻る。

なお、図内の実線は通常運用状態を、破線はパワーセーブ状態であることを示している。

【0096】

このように、OLT2Bはリンクしている全ONU3Bの上りデータ送信タイミングを把握できるので、いずれのONU3Bからも上りバーストデータを受信しない期間に合わせて上り通信用の機能を休止させることにより、OLT2Bの消費電力低減が見込める。

【0097】

ここまで各装置の動作である。続けてPONシステム1のシステム動作について説明する。

図16は上り方向のパワーセーブを行う場合の制御シーケンスを示す図である。ここでは、説明を簡潔にするためにONU3Bが1台の例を示している。

【0098】

OLT2BとONU3B間はMPCPプロトコルで制御されており、OLT2BはONU3Bに対して上り方向の送信要求があるか否かをGateメッセージで問合せる。ONU3BはGateメッセージを受信すると、上り方向のデータがあるか否かを確認してReportメッセージを返す。このとき、上り方向の送信要求が有る場合は、必要とする帯域情報をReportメッセージに格納する。

OLT2BはReportメッセージを受信すると、そのONU3Bに割当てる帯域を決定し、次のGateメッセージにONU3Bに許容する送信帯域及び送信タイミングの情報を格納して送信する。以降、OLT2BとONU3B間では同様の動作を繰り返す。

【0099】

最初のGateメッセージ#1の到達時点において、ONU3BのPON制御部345は上りトラヒック監視部343から上り送信要求無しの情報を受取っているため、Reportメッセージ送信にあわせてパワーセーブ状態を解除し、上り送信要求値がゼロのReportメッセージ#1を送信する。その後、1つ前のグラントサイクルで送信要求していたData#1を送信し、再びパワーセーブを開始する。

10

20

30

40

50

OLT2Bのパワーセーブ制御部26Bは、ONU3BからReportメッセージ#1を受信する前にパワーセーブ状態を解除し、Data#1受信後に再びパワーセーブを開始する。

【0100】

ONU3BはGateメッセージ#2受信時も上りトラヒック監視部343から上り送信要求無しの情報を受取っているため、Reportメッセージ#2送信にあわせてパワーセーブ状態を解除し、上り送信要求値ゼロの情報を格納したReportメッセージ#2を送信すると、再びパワーセーブ状態に戻る。

OLT2Bのパワーセーブ制御部26Bは、ONU3BからReportメッセージ#2を受信する前にパワーセーブ状態を解除し、Reportメッセージ#2を受信するとパワーセーブ状態に戻る。

10

【0101】

ONU3Bは、OLT2BからGateメッセージ#3を受信する前に上りトラヒック監視部343にてData#2の上り送信要求を検出していることから、PON制御部345はReportメッセージ#3送信にあわせてパワーセーブ状態を解除し、Reportメッセージ#3にData#2の上り送信要求を格納してOLT2Bへ送信する。Reportメッセージ#3の送信後は再びパワーセーブ状態に戻る。

OLT2Bのパワーセーブ制御部26Bは、先ほどと同様に、ONU3BからReportメッセージ#3を受信する前にパワーセーブ状態を解除し、Reportメッセージ#3を受信するとパワーセーブ状態に戻る。

20

【0102】

ONU3BはGateメッセージ#4受信時も上りトラヒック監視部343から上り送信要求無しの情報を受取っているため、Reportメッセージ#4送信にあわせてパワーセーブ状態を解除し、上り送信要求値ゼロの情報を格納したReportメッセージ#4を送信する。続けて、ONU3BはGateメッセージ#4から抽出した情報に基づいてData#2を送信し、その後はパワーセーブ状態に戻る。

OLT2Bのパワーセーブ制御部26Bは、ONU3BからReportメッセージ#4を受信する前にパワーセーブ状態を解除し、Reportメッセージ#4及び自身がONU3Bに割当てたData#2の受信期間を待って再びパワーセーブ状態に戻る。

以降、同様の動作を繰り返す。

30

【0103】

この実施の形態によれば、実施の形態2の効果に加えて、ONU3Bが上りデータを送信する時間情報を上りフレームに格納して送信し、OLT2Bは上りトラヒック情報及び接続する各ONU3Bの上りデータを受信する時間情報に基づいて、いずれのONU3Bからも上りバーストデータを受信しない期間を示す上り用パワーセーブ制御信号を生成し、PON制御部253、フレーム分離部256、上りトラヒック監視部257等の上り通信機能を休止させることにより、OLT2Bの消費電力をさらに低減できる。

また、このようなOLT2B及びONU3Bで構成されるPONシステムは、有効データを損失すること無く消費電力を低減できる。

なお、本実施の形態に記載のONU3Bは実施の形態2に記載のONU3Aと低速クロックを生成する箇所が異なるのみであり、OLT2BにONU3Aを接続しても同様の効果が得られる。

40

【符号の説明】

【0104】

1 PONシステム

2、2B OLT

3、3A、3B、3a～3n ONU

21 光トランシーバ

23 基準クロック

25 PON処理部

50

|             |               |    |

|-------------|---------------|----|

| 2 5 2       | 下りトラヒック監視部    |    |

| 2 5 3       | P O N 制御部     |    |

| 2 5 6       | フレーム分離部       |    |

| 2 5 7       | 上りトラヒック監視部    |    |

| 2 6 、 2 6 B | パワーセーブ制御部     |    |

| 2 7         | 1 / N クロック生成部 |    |

| 2 8         | セレクタ          |    |

| 2 9         | 駆動回路          |    |

| 3 1         | 光トランシーバ       | 10 |

| 3 2 、 3 2 A | 下り用 C D R     |    |

| 3 2 2       | P L L 回路      |    |

| 3 2 6       | 1 / N 分周回路    |    |

| 3 2 7       | 1 / M 分周回路    |    |

| 3 3 、 3 3 A | 上り用 C D R     |    |

| 3 3 6       | 1 / N 分周回路    |    |

| 3 4 、 3 4 A | P O N 処理部     |    |

| 3 4 3       | 上りトラヒック監視部    |    |

| 3 4 5       | P O N 制御部     |    |

| 3 5         | パワーセーブ制御部     |    |

| 3 7         | 1 / M 分周回路    | 20 |

【図 1】

【図 2】

【図 3】

【図 4】

【図5】

【図6】

【図7】

【図9】

【図8】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

---

フロントページの続き

(72)発明者 木挽 謙一

東京都千代田区丸の内二丁目7番3号 三菱電機株式会社内

審査官 阿部 弘

(56)参考文献 特開平07-288507 (JP, A)

特開2008-219103 (JP, A)

特開2002-344420 (JP, A)

特開2011-188356 (JP, A)

特開平06-311068 (JP, A)

(58)調査した分野(Int.Cl., DB名)

H04J 3

H04B 10

H04L 7

H04L 12

H04L 29