(19)日本国特許庁(JP)

**(12)特許公報(B2)**

(11)特許番号

**特許第7558650号**

**(P7558650)**

(45)発行日 令和6年10月1日(2024.10.1)

(24)登録日 令和6年9月20日(2024.9.20)

(51)国際特許分類

|         |                 |         |       |         |

|---------|-----------------|---------|-------|---------|

| B 4 1 J | 2/447 (2006.01) | B 4 1 J | 2/447 | 1 0 1 B |

| B 4 1 J | 2/45 (2006.01)  | B 4 1 J | 2/447 | 1 0 1 D |

| G 0 3 G | 15/04 (2006.01) | B 4 1 J | 2/45  |         |

| G 0 3 G | 21/14 (2006.01) | G 0 3 G | 15/04 | 1 1 3   |

| G 0 3 G | 15/00 (2006.01) | G 0 3 G | 21/14 |         |

請求項の数 6 (全29頁) 最終頁に続く

(21)出願番号 特願2019-152968(P2019-152968)

(22)出願日 令和1年8月23日(2019.8.23)

(65)公開番号 特開2021-30564(P2021-30564A)

(43)公開日 令和3年3月1日(2021.3.1)

審査請求日 令和4年8月8日(2022.8.8)

前置審査

(73)特許権者 000001007

キヤノン株式会社

東京都大田区下丸子3丁目30番2号

(74)代理人 100123559

弁理士 梶 俊和

100177437

弁理士 中村 英子

吉田 英史

(72)発明者 東京都大田区下丸子3丁目30番2号

キヤノン株式会社内

小山 勇人

東京都大田区下丸子3丁目30番2号

キヤノン株式会社内

大関 朋子

審査官

最終頁に続く

(54)【発明の名称】 画像形成装置

**(57)【特許請求の範囲】****【請求項1】**

第1の解像度で潜像を形成する第1のモードと、前記第1の解像度よりも低い第2の解像度で潜像を形成する第2のモードと、で動作する画像形成装置であって、回転する感光体と、

前記感光体の回転軸方向に沿って、かつ、前記回転軸方向において前記第1の解像度に対応する間隔で配列された複数の発光部を有する発光チップと、前記複数の発光部の駆動を制御する画像データを生成し、生成した前記画像データをクロック信号に同期して出力する生成部と、

前記複数の発光部のそれぞれに対応して設けられる複数の駆動部であって、前記クロック信号に同期して前記画像データが入力され、入力された前記画像データに応じて前記複数の発光部のそれぞれの点灯と消灯とを駆動する複数の駆動部と、

を備え、

前記複数の発光部は、前記感光体の回転方向における、前記画像形成装置の出力解像度だけ前記感光体の表面が移動する周期で発されるライン同期信号に対応した間隔で発光し、前記画像形成装置が前記第1のモードで動作する場合、前記複数の駆動部のそれぞれに異なる画像データが入力され、

前記画像形成装置が前記第2のモードで動作する場合、前記複数の発光部に含まれる第1の発光部に対応する第1の駆動部と、前記複数の発光部に含まれ、前記回転軸方向における一方において前記第1の発光部に隣接する第2の発光部に対応する第2の駆動部と、に

同一の画像データが入力され、

前記画像形成装置は、前記画像形成装置が前記第1のモードで動作する場合、前記第1の駆動部と前記第2の駆動部とに異なる画像データを出力し、前記画像形成装置が前記第2のモードで動作する場合、前記第1の駆動部と前記第2の駆動部とに同一の画像データを出力するセレクタを備える、

ことを特徴とする画像形成装置。

**【請求項2】**

前記第1の解像度は前記第2の解像度の2倍の解像度である、

ことを特徴とする請求項1に記載の画像形成装置。

**【請求項3】**

前記複数の発光部は有機ELである、

ことを特徴とする請求項1に記載の画像形成装置。

**【請求項4】**

前記発光チップは、シリコン基板と、層状に形成され光が透過可能な第1の電極層と、前記シリコン基板の表面に垂直な垂直方向において前記第1の電極層と前記シリコン基板との間に層状に形成された第2の電極層であって、前記回転軸方向に沿って並べられた複数の電極を有する第2の電極層と、前記垂直方向において前記第1の電極層と前記第2の電極層との間に層状に形成された発光層と、を有し、

前記発光層が発した光は前記第1の電極層を透過して出射される、

ことを特徴とする請求項1に記載の画像形成装置。

**【請求項5】**

前記駆動部は、前記シリコン基板に設けられ、画像データに基づいて前記複数の発光部の点灯と消灯とを制御する駆動回路を有し、

前記複数の電極と前記駆動回路とは、前記回転軸方向においてオーバーラップし、前記感光体の回転方向においてオーバーラップする、

ことを特徴とする請求項4に記載の画像形成装置。

**【請求項6】**

前記第1の電極層は前記複数の電極の全てに対して共通に形成されている、

ことを特徴とする請求項4に記載の画像形成装置。

**【発明の詳細な説明】**

30

**【技術分野】**

**【0001】**

本発明は、画像形成装置に関する。

**【背景技術】**

**【0002】**

電子写真方式の画像形成装置であるプリンタでは、露光ヘッドを使用して感光ドラムを露光し、潜像形成を行う方式が一般的に知られている。ここで、露光ヘッドには、例えばLED(Light Emitting Diode)や有機EL(Organic Electro Luminescence)などが用いられる。露光ヘッドは、感光ドラムの長手方向に配列された発光素子列と、発光素子列からの光を感光ドラム上に結像させるロッドレンズアレイと、から構成される。LEDや有機ELは、発光面からの光の照射方向がロッドレンズアレイと同一方向となる面発光形状を有する構成が知られている。ここで、発光素子列の長さは、感光ドラム上における画像領域幅に応じて決まり、プリンタの解像度に応じて発光素子間の間隔が決まる。例えば、1200 dpiのプリンタの場合、画素の間隔は21.16 μmであり、そのため、発光素子間の間隔も21.16 μmに対応する間隔となる。このような露光ヘッドを使用したプリンタでは、レーザビームを回転多面鏡によって偏向されたレーザビームによって感光ドラムを走査するレーザ走査方式のプリンタと比べて、使用する部品数が少ないため、装置の小型化、低コスト化が容易である。

**【0003】**

40

50

例えば特許文献 1 では、主走査方向に並ぶ各発光素子を 1 画素ごとに千鳥状に配置している。画像の解像度が低い場合は、主走査方向における偶数又は奇数番目の発光素子のみ点灯させ、画像の解像度が高い場合は、偶数、奇数合わせてすべての発光素子を点灯させる。これにより、画像の解像度に対応した発光を行うことが提案されている。

**【先行技術文献】**

**【特許文献】**

**【0004】**

**【文献】**特開 2008-246703 号公報

**【発明の概要】**

**【発明が解決しようとする課題】**

**【0005】**

しかしながら、従来例のように、画像の解像度に応じて発光素子数を変更する場合、解像度が低いときには発光素子数を減らし、発光する発光素子間を解像度に合わせた間隔にする必要がある。このとき、感光体上に各発光素子が発光することで形成されるスポットのサイズが画像の解像度の画素間隔より小さい場合、隣接する発光素子同士が作るスポットが離れてしまう。このため、主走査方向におけるドットが離間した画像形成となり、例えば画像輪郭にジャギーが発生するなどの画質の低下が発生するという課題がある。

**【0006】**

上記課題に鑑み、本発明は、電極が配列された間隔に対応する第 1 の解像度の半分の第 2 の解像度で形成される画像の画質が低下してしまうことを抑制することを目的とする。

**【課題を解決するための手段】**

**【0007】**

上述した課題を解決するために、本発明は、以下の構成を備える。

**【0008】**

(1) 第 1 の解像度で潜像を形成する第 1 のモードと、前記第 1 の解像度よりも低い第 2 の解像度で潜像を形成する第 2 のモードと、で動作する画像形成装置であって、回転する感光体と、前記感光体の回転軸方向に沿って、かつ、前記回転軸方向において前記第 1 の解像度に対応する間隔で配列された複数の発光部を有する発光チップと、前記複数の発光部の駆動を制御する画像データを生成し、生成した前記画像データをクロック信号に同期して出力する生成部と、前記複数の発光部のそれぞれに対応して設けられる複数の駆動部であって、前記クロック信号に同期して前記画像データが入力され、入力された前記画像データに応じて前記複数の発光部のそれぞれの点灯と消灯とを駆動する複数の駆動部と、を備え、前記複数の発光部は、前記感光体の回転方向における、前記画像形成装置の出力解像度だけ前記感光体の表面が移動する周期で発されるライン同期信号に対応した間隔で発光し、前記画像形成装置が前記第 1 のモードで動作する場合、前記複数の駆動部のそれぞれに異なる画像データが入力され、前記画像形成装置が前記第 2 のモードで動作する場合、前記複数の発光部に含まれる第 1 の発光部に対応する第 1 の駆動部と、前記複数の発光部に含まれ、前記回転軸方向における一方において前記第 1 の発光部に隣接する第 2 の発光部に対応する第 2 の駆動部と、に同一の画像データが入力され、前記画像形成装置は、前記画像形成装置が前記第 1 のモードで動作する場合、前記第 1 の駆動部と前記第 2 の駆動部とに異なる画像データを出力し、前記画像形成装置が前記第 2 のモードで動作する場合、前記第 1 の駆動部と前記第 2 の駆動部とに同一の画像データを出力するセレクタを備える、ことを特徴とする画像形成装置。

**【発明の効果】**

**【0010】**

本発明によれば、電極が配列された間隔に対応する第 1 の解像度の半分の第 2 の解像度で形成される画像の画質が低下してしまうことを抑制することができる。

**【図面の簡単な説明】**

**【0011】**

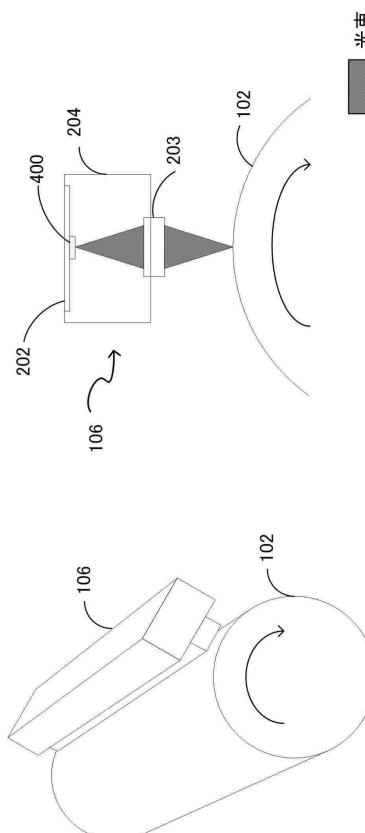

**【図 1】**実施例 1、2 の画像形成装置の構成を示す概略断面図

- 【図 2】実施例 1、2 の露光ヘッドの構成を示す図

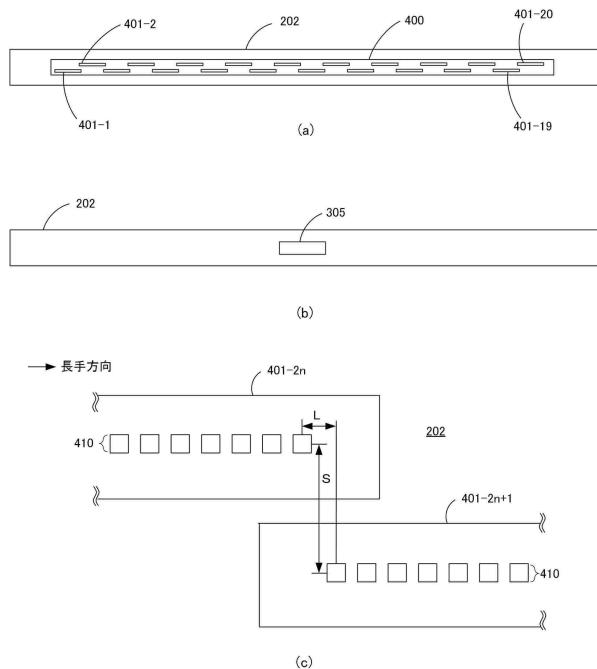

【図 3】実施例 1 のプリント基板の構成を示す図

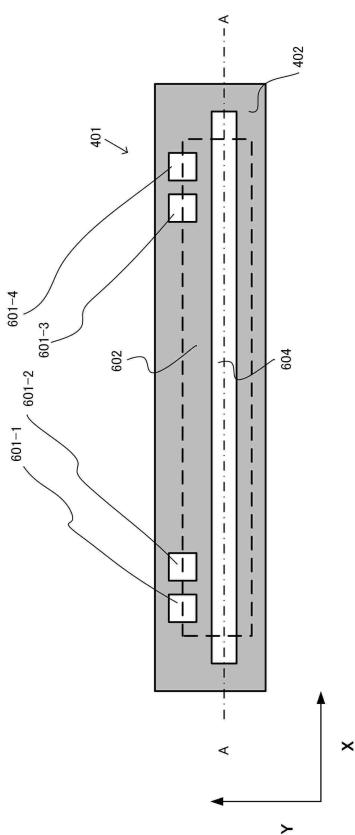

【図 4】実施例 1、2 のシリコン基板の構成を示す図

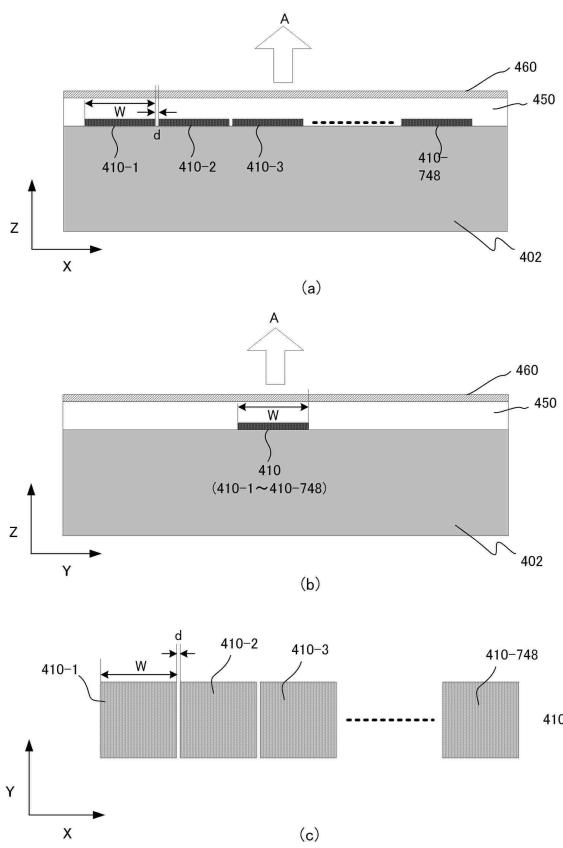

【図 5】実施例 1 の発光領域の断面図、発光装置の構成図

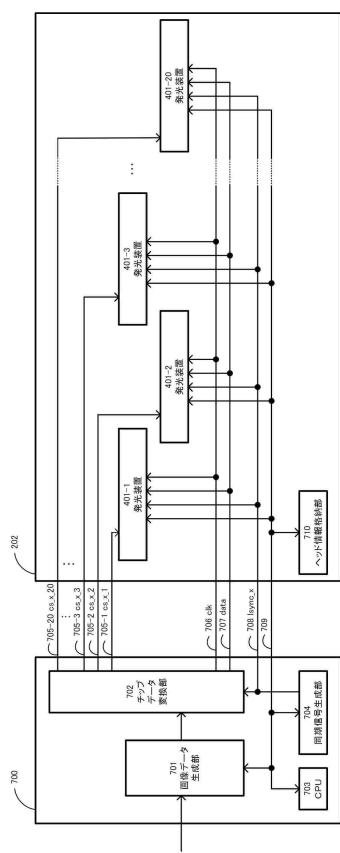

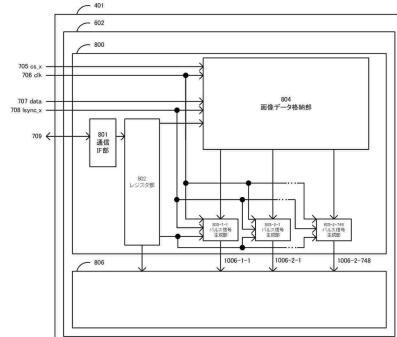

【図 6】実施例 1、2 の画像コントローラ部及びプリント基板のブロック図

【図 7】実施例 1 のデータ転送を説明するタイミングチャート

【図 8】実施例 1 の発光装置内の回路図

【図 9】実施例 1 の各信号の波形及び画像データのシフトを示す図

【図 10】実施例 1 のパルス信号生成部の説明図、各信号の波形を示す図

【図 11】実施例 1、2 のアナログ部のブロック図、駆動部の回路図

【図 12】実施例 1 の感光ドラム上の潜像を説明する図

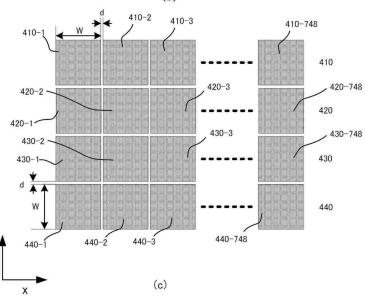

【図 13】実施例 2 のプリント基板の構成を示す図、シリコン基板の構成図

【図 14】実施例 2 の発光装置内の回路図

【図 15】実施例 2 の各信号の波形及び画像データのシフトを示す図

【図 16】実施例 2 の感光ドラム上の潜像を説明する図

## 【発明を実施するための形態】

## 【0012】

以下に、図面を参照して本発明の実施の形態について詳細に説明する。

## 【実施例 1】

## 【0013】

## [ 画像形成装置の構成 ]

図 1 は、実施例 1 における電子写真方式の画像形成装置の構成を示す概略断面図である。図 1 に示す画像形成装置は、スキャナ機能とプリンタ機能を備える複合機（マルチファンクションプリンタ：MFP）である。画像形成装置は、スキャナ部 100、作像部 103、定着部 104、給紙 / 搬送部 105、及びこれらを制御するプリンタ制御部（不図示）から構成される。スキャナ部 100 は、原稿台に置かれた原稿に照明を当てて原稿画像を光学的に読み取り、読み取った画像を電気信号に変換して画像データを作成する。

## 【0014】

作像部 103 は、無端の搬送ベルト 111 の回転方向（反時計回り方向）に沿って、シャン（C）、マゼンタ（M）、イエロー（Y）、ブラック（K）の順に並べられた、4 連の画像形成ステーションを備える。4 つの画像形成ステーションは同じ構成を有し、各画像形成ステーションは、矢印方向（時計回り方向）に回転する感光体である感光ドラム 102、露光ヘッド 106、帯電器 107、現像器 108 を備えている。なお、感光ドラム 102、露光ヘッド 106、帯電器 107、現像器 108 の添え字 a、b、c、d は、それぞれ画像形成ステーションのブラック（K）、イエロー（Y）、マゼンタ（M）、シャン（C）に対応する構成であることを示す。なお、以下では、特定の感光ドラム等を指す場合を除き、符号の添え字を省略することとする。

## 【0015】

作像部 103 では、感光ドラム 102 を回転駆動し、帯電器 107 によって感光ドラム 102 を帯電させる。露光手段である露光ヘッド 106 は、発光装置を画像データに応じて発光させ、発光装置によって生成される光を、ロッドレンズアレイによって感光ドラム 102 上（感光体上）に集光し、静電潜像を形成する。現像手段である現像器 108 は、感光ドラム 102 に形成された静電潜像をトナーで現像する。そして、現像されたトナー像は、記録紙を搬送する搬送ベルト 111 上の記録紙に転写される。このような一連の電子写真プロセスが各画像形成ステーションで実行される。なお、画像形成時には、シャン（C）の画像形成ステーションでの画像形成が開始されて所定時間が経過した後に、順次、マゼンタ（M）、イエロー（Y）、ブラック（K）の各画像形成ステーションで、画像形成動作が実行される。これにより、フルカラーの画像が形成される。

## 【0016】

図 1 に示す画像形成装置は、記録紙を給紙するユニットとして、給紙 / 搬送部 105 が

10

20

30

40

50

有する本体内給紙ユニット 109a、109b、大容量の給紙ユニットである外部給紙ユニット 109c、及び手差し給紙ユニット 109d を備えている。画像形成時には、このうち、予め指示された給紙ユニットから記録紙が給紙され、給紙された記録紙はレジストレーションローラ 110まで搬送される。レジストレーションローラ 110は、上述した作像部 103において形成されたトナー像が記録紙に転写されるタイミングで、搬送ベルト 111に記録紙を搬送する。搬送ベルト 111により搬送される記録紙には、各画像形成ステーションの感光ドラム 102上に形成されたトナー像が順次転写される。未定着のトナー像が転写された記録紙は、定着部 104へと搬送される。定着部 104は、ハロゲンヒータ等の熱源を内蔵し、記録紙上のトナー像を、2つのローラにより加熱・加圧することによって記録紙に定着させる。定着部 104によりトナー像が定着された記録紙は、排出ローラ 112により画像形成装置の外部に排出される。

10

#### 【0017】

ブラック (K) の画像形成ステーションの記録紙搬送方向の下流側には、搬送ベルト 111に対向する位置に、検知手段である光学センサ 113が配置されている。光学センサ 113は、各画像形成ステーション間のトナー像の色ずれ量を導出するため、搬送ベルト 111上に形成されたテスト画像の位置検出を行う。光学センサ 113により導出された色ずれ量は、後述する画像コントローラ部 700(図6参照)等に通知され、記録紙上に色ずれのないフルカラートナー像が転写されるように、各色の画像位置が補正される。また、プリンタ制御部(不図示)は、複合機(MFP)全体を制御するMFP制御部(不図示)からの指示に応じて、上述したスキヤナ部 100、作像部 103、定着部 104、給紙／搬送部 105等を制御しながら、画像形成動作を実行する。

20

#### 【0018】

ここでは、電子写真方式の画像形成装置の例として、搬送ベルト 111上の記録紙に各画像形成ステーションの感光ドラム 102に形成されたトナー像を直接転写する方式の画像形成装置について説明した。本発明は、このような感光ドラム 102上のトナー像を直接、記録紙に転写する方式のプリンタに限定されるものではない。例えば、感光ドラム 102上のトナー像を中間転写ベルトに転写する1次転写部と、中間転写ベルト上のトナー像を記録紙に転写する2次転写部を備える画像形成装置についても、本発明は適用することができる。

30

#### 【0019】

##### [露光ヘッドの構成]

次に、感光ドラム 102に露光を行う露光ヘッド 106について、図2を参照して説明する。図2(a)は、露光ヘッド 106と感光ドラム 102との位置関係を示す斜視図であり、図2(b)は、露光ヘッド 106の内部構成と、露光ヘッド 106からの光束がロッドレンズアレイ 203により感光ドラム 102に集光される様子を説明する図である。図2(a)に示すように、露光ヘッド 106は、矢印方向に回転する感光ドラム 102の上部の、感光ドラム 102に対向する位置に、取付け部材(不図示)によって画像形成装置に取り付けられている(図1)。

#### 【0020】

図2(b)に示すように、露光ヘッド 106は、プリント基板 202と、プリント基板 202に実装された発光装置群 400と、ロッドレンズアレイ 203と、ハウジング 204から構成されている。ハウジング 204には、ロッドレンズアレイ 203とプリント基板 202が取り付けられる。図2に示すようにロッドレンズアレイ 203は、発光装置群 400と感光ドラム 102の間に配置されている。ロッドレンズアレイ 203は、プリント基板 202の長手方向に沿って設けられ、発光装置群 400がそれぞれ出射する光束を感光ドラム 102上に集光させる。工場では、露光ヘッド 106単体で組立て調整作業が行われ、ピント調整、光量調整が行われる。ここで、感光ドラム 102とロッドレンズアレイ 203との間の距離、及びロッドレンズアレイ 203と発光装置群 400との間の距離が、所定の間隔となるように組立て調整が行われる。これにより、発光装置群 400からの光が感光ドラム 102上に結像される。そのため、工場でのピント調整時においては

40

50

、ロッドレンズアレイ 203 と発光装置群 400 との距離が所定の値となるように、ロッドレンズアレイ 203 の取付け位置の調整が行われる。また、工場での光量調整時においては、後述する発光装置 401 の下部電極を駆動し、ロッドレンズアレイ 203 を介して感光ドラム 102 上に集光させた光が所定光量になるように、発光装置 401 に印加する後述の電圧の調整が行われる。

#### 【0021】

##### [ 発光装置群の構成 ]

図 3 は、プリント基板 202 及びプリント基板 202 に実装された発光装置群 400 を説明する図である。図 3 (a) は、プリント基板 202 の発光装置群 400 が実装された面の構成を示す模式図であり、図 3 (b) は、プリント基板 202 の発光装置群 400 が実装された面 ( 第 1 面 ) とは反対側の面 ( 第 2 面 ) の構成を示す模式図である。

10

#### 【0022】

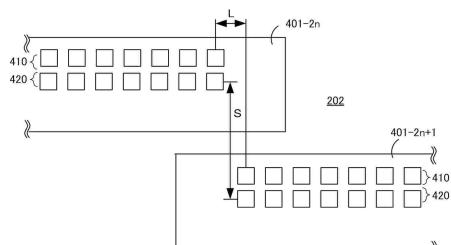

図 3 (a) に示すように、第 2 の基板であるプリント基板 202 に実装された発光装置群 400 は、20 個の独立したチップである発光装置 401 - 1 ~ 401 - 20 が、プリント基板 202 の長手方向に沿って、千鳥状に 2 列に配置された構成を有している。すなわち、プリント基板 202 上 ( 第 2 の基板上 ) には、奇数番目の発光装置 401 - 1 · · · ( 401 - 2n + 1 : n = 0 ) と偶数番目の発光装置 401 - 2 · · · ( 401 - 2n : n = 1 ) とが感光ドラム 102 の回転方向において異なる位置に配列されている。発光装置 401 - 1 ~ 401 - 20 を総称して発光装置 401 ということもある。なお、図 3 (a) において、上下方向は第 1 の方向である感光ドラム 102 の回転方向を示し、水平方向は、第 1 の方向と直交する第 2 の方向である長手方向を示す。長手方向は、感光ドラム 102 の回転方向と交差する交差方向でもある。各々の発光装置 401 の内部には、計 748 個の後述する下部電極を有する。本実施例では、下部電極は 21.16 μm ( 2.54 cm / 1200 ドット ) に 1 つ配置されている。その結果、1 つの発光装置 401 内における 748 個の下部電極の端から端までの配列距離は、約 15.8 mm ( 21.16 μm × 748 ) である。発光装置群 400 は、20 個の発光装置 401 から構成されている。発光装置群 400 における露光可能な下部電極の数は 14,960 個 (= 748 個の電極 × 20 チップ) となり、発光装置群 400 によって約 316 mm ( 約 15.8 mm × 20 チップ ) の長手方向の画像幅に対応した露光が可能となる。

20

#### 【0023】

また、図 3 (b) に示すように、発光装置群 400 が実装された面とは反対側のプリント基板 202 の面には、コネクタ 305 が実装されている。コネクタ 305 は、後述する画像コントローラ部 700 ( 図 6 参照 ) から発光装置群 400 を制御する制御信号及び電源ラインを接続するためのコネクタであり、コネクタ 305 を介して各発光装置 401 - 1 ~ 401 - 20 が駆動される。

30

#### 【0024】

図 3 (c) は、長手方向に 2 列に配置された発光装置 401 のチップ間の境界部の様子を示す図であり、水平方向は、図 3 (a) の発光装置群 400 の長手方向であり、発光装置 401 が複数配置されている。図 3 (c) に、発光装置 401 のチップ間の境界部 ( 長手方向においてチップ同士の端部が重なっている部分 ( 重なり部 ) ) を示す。発光装置 401 - 2n と発光装置 401 - 2n + 1 間の境界部においても、異なる発光装置 401 間における端部の下部電極 410 の長手方向のピッチ ( 2 つの下部電極の中心点と中心点の間隔 ( L ) ) は、1200 dpi の解像度のピッチである略 21.16 μm となっている。

40

#### 【0025】

また、短手方向の上下 2 列に並んだ発光装置 401 は、次のように配置されている。すなわち、上下の発光装置 401 の後述する下部電極の間隔 ( 図中、矢印 S で示す ) が約 105 μm ( 1200 dpi で 5 画素分 ) となるように配置されている。また、露光ヘッド 106 の長手方向の発光点の間隔 ( 図中、矢印 L で示す ) は、約 21.16 μm ( 1200 dpi で 1 画素分 ) となっている。なお、本発明においては、発光装置 401 間の間隔 S 、 L は、前述した値に限定する必要はないものとする。

50

## 【0026】

### [発光装置の構成]

図4は発光装置401の内部構成を示す概略図である。ここで、図4に示すように、発光装置401の長手方向をX方向、短手方向をY方向とする。ここで、Y方向は感光ドラム102の回転方向、言い換えれば回転する感光ドラム102の感光面(感光体表面)の移動方向である。X方向は、Y方向すなわち感光ドラム102の回転方向に略直交する方向である。また、感光ドラム102の回転軸線方向に略平行な方向もある。なお、略直交は角度90°に対して±1°程度の傾きを許容し、略平行は互いのなす角度が0°を基準に±1°程度の傾きを許容する。すなわち、発光装置401の長手方向は感光ドラム102の回転軸線方向に対して±1°程度傾いていても構わない。また、発光装置401の短手方向も感光ドラム102の回転方向に対して±1°程度傾いていても構わない。発光装置401は第1の基板であるシリコン基板402の上にワイヤボンディング用パッド(以下、WBパッドという)601-1、601-2、601-3、601-4が形成されている。なお、シリコン基板402には駆動部である回路部602(破線)が内蔵されている。回路部602としてはアナログ駆動回路、デジタル制御回路、又はその両方を含んだ構成を用いることができる。回路部602の電源供給や発光装置401外からの信号等の入出力はWBパッド601を介して行われる。

10

## 【0027】

本実施例の発光装置401は、感光ドラム102の回転軸線方向に沿って延びるライン状の発光領域604を含む。発光領域604は、後述する陽極と陰極と発光層450(図5参照)とを含み、陽極と陰極に電位差が生じることによって発光する領域である。

20

## 【0028】

シリコン基板402としては、シリコン(Si)基板を好適に用いることができる。これは、次のようなメリットがあるからである。すなわち、シリコン基板については、集積回路形成用のプロセス技術も発達しており、既に様々な集積回路の基板として用いられているため、高速かつ高機能な回路を高密度に形成できるというメリットがある。また、シリコン基板については、大口径のウェハが出回っており、安価に入手することができるというメリットがある。

## 【0029】

実施例1では、回路部602に発光領域604を駆動する駆動部及び発光領域604を発光させるための信号(以下、発光信号という)を生成するためのデータ転送、発光信号生成部を設け、回路部602をシリコン基板402上に形成する。これにより、高速対応が可能な回路を形成する。

30

## 【0030】

### [発光領域の構成]

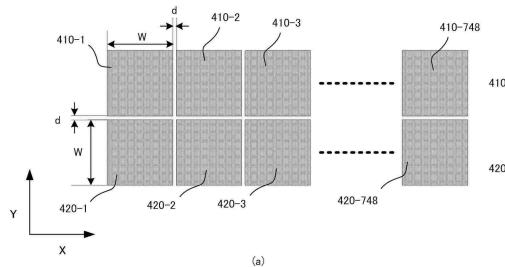

図5を用いて発光装置401をさらに詳しく説明する。図5におけるX方向は、露光ヘッド106の長手方向を示している。Z方向は、後述する層構造の各層が重なる方向(積層方向)である。図5(a)は、図4中のA-A断面の概略図の要部拡大図である。図5(a)は、Y方向から見た後述する下部電極410-1~410-748の概略図である。図5(a)、図5(c)に示すように、発光装置401は、シリコン基板402、下部電極410-1~410-748、発光層450、上部電極460を備える。シリコン基板402は製造プロセスにおいて後述する下部電極410-1~410-748それぞれに対応する駆動部を含む駆動回路が形成された駆動基板である。

40

## 【0031】

図5(a)、図5(c)に示すように、下部電極410-1~410-748(陰極)は、シリコン基板402上に層状(第1の電極層)に形成された複数の電極である。各下部電極410-1~410-748は、シリコン基板402を製造する製造プロセスとともにSi集積回路加工技術を用いてシリコン基板402に内蔵されている複数の駆動部上に形成される。下部電極410-1~410-748は、後述する発光層450の発光波長に対して反射率の高い金属が好ましい。そのため、下部電極410-1~410-74

50

8には、銀(Ag)、アルミニウム(Al)、またはこれらの合金、銀・マグネシウム合金など含有することが好ましい。

#### 【0032】

図5に示すように、下部電極410-1~410-748は、X方向における各画素に対応して設けられた電極である。すなわち、下部電極410-1~410-748はそれぞれ1画素を形成するために設けられた電極である。下部電極410-1~410-748を第1の電極列とする。第1の電極列をなす下部電極410-1~410-748は感光ドラム102の回転軸線方向に沿って並んでいる。ここで、これら下部電極410-1~410-748は感光ドラム102の回転軸線方向に対して±1°程度傾いて並んでも構わない。厳密に感光ドラム102の回転軸線方向に対して平行に並んでいる必要はない。

10

#### 【0033】

本実施例におけるX方向における下部電極410-1~410-748の幅Wは1画素の幅に対応する幅である。間隔dはX方向における下部電極間距離(配列間隔)である。下部電極410-1~410-748はシリコン基板402上に間隔dを開けて形成されているため、シリコン基板402に形成された複数の駆動部はそれぞれ個別に下部電極410-1~410-748の電圧を制御することができる。間隔dには発光層450の有機材料が充填されており、下部電極は有機材料によって仕切られている。

#### 【0034】

本実施例における発光装置401において、下部電極410-1~410-748の幅Wは称呼寸法として20.90μm、間隔dは称呼寸法として0.26μmに設定されている。つまり、本実施例の発光装置401は、X方向において21.16μm毎に1つの下部電極410を備える。21.16μmは1200dpiにおける1画素の大きさであるので、各下部電極410のX方向における下部電極410の幅は本実施例の画像形成装置の出力解像度に対応する1画素相当の大きさを有することになる。なお、本実施例の発光装置401におけるプロセス・ルールは0.2μm程度と高精度であり、dの幅を0.26μmの分解能で形成することは可能である。

20

#### 【0035】

また、図5(b)に示すように、感光ドラム102の回転方向であるY方向における下部電極410-1~410-748の幅もWである。つまり、本実施例の下部電極410-1~410-748は20.90μm四方の形状をなしており、下部電極410の面積は436.81μm<sup>2</sup>の大きさとなる。これは、1画素の面積447.7456μm<sup>2</sup>に対して約97.6%を占める。有機発光材料はLEDに比較して光量が少ない。それに対して、上記のように下部電極410を正方形として隣接する下部電極間の距離を小さくしてシリコン基板402上に形成することで、感光ドラム102の電位を変化させ得る程度の光量を得るために発光面積を確保することが可能となる。なお、1画素の占有面積に対して90%以上の下部電極面積を確保することが望ましい。したがって、1200dpiの出力解像度の画像形成装置に対しては下部電極410の一辺の幅を約20.07μm以上で形成することが望ましく、2400dpiの出力解像度の画像形成装置に対しては下部電極410の一辺の幅を約10.04μm以上で形成することが望ましい。

30

#### 【0036】

一方で、下部電極410の占有面積の上限値は、ロッドレンズアレイ203や後述する上部電極460の透過率に基づいて設定されるべきであるが、本実施例では、1画素の占有面積に対して110%を上限として設定する。1画素の占有面積に対して110%よりも大きく設計すると、感度の高い感光ドラム102を露光する際に形成される画素のサイズが解像度を大きく超えてしまう可能性があるため、下部電極410の占有面積の上限値を110%に設定する。したがって、1200dpiの出力解像度の画像形成装置に対しては下部電極410の一辺の幅を約22.19μm以下で形成することが望ましく、2400dpiの出力解像度の画像形成装置に対しては下部電極410の一辺の幅を約11.10μm以下で形成することが望ましい。すなわち、1画素の占有面積に対する下部電極4

40

50

10 の占有面積の範囲は 90 % 以上 110 % 以下であることが好ましい。

#### 【0037】

なお、下部電極 410 の形状は正方形に限られず、画像形成装置の出力解像度に対応する露光領域サイズの光を射出し、その光によって出力画像の画質が画像形成装置の設計仕様を満たすレベルであれば四角形以上の多角形、円形、橢円形などの形状でも良い。

#### 【0038】

次に、発光層 450 について説明する。発光層 450 は下部電極 410 - 1 ~ 410 - 748 が形成されたシリコン基板 402 に積層されて形成される。すなわち、下部電極 410 - 1 ~ 410 - 748 が形成された部分において発光層 450 は下部電極 410 - 1 ~ 410 - 748 上に積層される。下部電極 410 - 1 ~ 410 - 748 が形成されていない部分においてシリコン基板 402 上に積層される。本実施例では、発光装置 401 において発光層 450 は、下部電極 410 - 1 ~ 410 - 748 すべてに跨るように形成されているが、実施の形態はこれに限られるものではない。例えば、下部電極 410 - 1 ~ 410 - 748 と同様に発光層 450 を各下部電極上に分離して積層するように形成しても良いし、下部電極 410 - 1 ~ 410 - 748 を複数のグループに分割して、分割したグループ毎にそのグループに属する下部電極上に一つの発光層を積層させても良い。

10

#### 【0039】

発光層 450 は、例えば有機材料を用いることができる。有機 EL 膜である発光層 450 は、電子輸送層、正孔輸送層、電子注入層、正孔注入層、電子プロック層、正孔プロック層などの機能層を含む積層構造体である。発光層 450 には、有機材料以外でも無機材料を用いても良い。

20

#### 【0040】

発光層 450 には上部電極 460 (陽極) が積層 (第 2 の電極層) とされている。上部電極 460 は、発光層 450 の発光波長の光を透過させることができ (透過可能) な電極である。そのため、本実施例の上部電極 460 は酸化インジウムスズ (ITO) を含有する材料を透明電極として採用している。酸化インジウムスズの電極は、可視光領域の光に関して 80 % 以上の透過率を有するため、有機 EL の電極としては好適である。

#### 【0041】

上部電極 460 は、少なくとも発光層 450 を挟んで下部電極 410 - 1 ~ 410 - 748 の反対側に形成されている。すなわち、Z 方向において、上部電極 460 と下部電極 410 - 1 ~ 410 - 748 の間に発光層 450 が配置されており、Z 方向において下部電極 410 - 1 ~ 410 - 748 を上部電極 460 に投影したときに下部電極 410 - 1 ~ 410 - 748 が形成された領域は上部電極 460 が形成された領域に収まる。なお、透明電極は発光層 450 全体に積層されていなくても良いが、発光層 450 で生じた光を効率良く発光装置 401 の外部に出射するためには、1 画素の占有面積に対して上部電極 460 の占有面積が 100 % 以上であることが好ましく、より好ましくは 120 % 以上であることが好ましい。上部電極 460 の占有面積の上限値はシリコン基板 402、発光層 450 の面積によって任意に設計される。上部電極 460 において光を透過させる部分以外は配線を設けても良い。

30

#### 【0042】

本実施例の上部電極 460 は、各下部電極 410 - 1 ~ 410 - 748 に対して共通に設けられた陽極であるが、各下部電極 410 - 1 ~ 410 - 748 それぞれに対して個別に設けても良いし、複数の下部電極毎に一つの上部電極を設けても良い。

40

#### 【0043】

駆動回路は、上部電極 460 と、下部電極 410 - 1 ~ 410 - 748 のうちの任意の下部電極と、に電位差を生じさせるために画像データに基づいて各下部電極 410 - 1 ~ 410 - 748 の電位を制御する。

#### 【0044】

本実施例における発光装置 401 は所謂トップエミッション型の出射方式のデバイスである。陽極である上部電極 460 と陰極である下部電極 410 それぞれに電圧を印加して

50

両者に電位差が生じると、陰極から電子が発光層 450 に流れ込み、陽極から正孔が発光層 450 に流れ込む。そして、発光層 450 において電子と正孔が再結合することによって発光層 450 が発光する。発光層 450 が発光することによって上部電極 460 に向かう光は上部電極 460 を透過して発光装置 401 から図 5 に示す矢印 A 方向に出射される。また、発光層 450 から下部電極 410 に向かう光は下部電極 410 よりてそれぞれ上部電極 460 に向けて反射され、その反射光も上部電極 460 を透過して発光装置 401 から出射される。発光層 450 から直接上部電極 460 に向かって出射される光と、下部電極 410 それぞれによって反射されて上部電極 460 から出射される光と、の上部電極 460 からの出射タイミングに時間差は生じるが、発光装置 401 の層の厚さは極小さいため、ほぼ同時の出射と見做すことができる。

10

#### 【 0045 】

上部電極 460 として酸化インジウムスズなどの透明電極を用いることによって電極の光の透過割合を示す開口率を実質的に上部電極 460 の透過率と同等とすることができます。すなわち、実質的に上部電極 460 以外に光を減衰させる、あるいは光を遮蔽する部分がないため、発光層 450 の発光が極力減衰する、あるいは遮蔽されることなく出射光となる。

#### 【 0046 】

また、前述した様に下部電極 410 - 1 ~ 410 - 748 を高精度な Si 集積回路加工技術を用いて形成することで下部電極 410 - 1 ~ 410 - 748 を高密度に配置することができる。そのため、発光領域 604 の面積（ここでは下部電極 410 - 1 ~ 410 - 748 の面積と、互いに隣接する下部電極間の領域の面積の合計）のほとんどを下部電極 410 - 1 ~ 410 - 748 に割り当てることができる。すなわち、単位面積当たりの発光領域の利用効率が高い露光ヘッドとなる。

20

#### 【 0047 】

なお、発光層 450 として有機 EL 層や無機 EL 層などの水分に弱い発光材料を用いる際は発光領域 604 への水分侵入を阻止するために封止しておくことが望ましい。封止方法としては、例えば、シリコンの酸化物、シリコンの窒化物、アルミの酸化物などの薄膜の単体あるいは積層した封止膜を形成する。封止膜の形成方法としては段差などの構造の被覆性能に優れた方法が好ましく、例えば、原子層堆積法（ALD 法）などを用いることができる。なお、封止膜の材料、構成、形成方法などは一例であり、上述した例には限定されず、適宜好適なものを選択すればよい。

30

#### 【 0048 】

##### 〔 制御プロック 〕

図 6 に、画像コントローラ部 700、プリント基板 202 のプロック図を示す。以下、チップセレクト信号を c\_s\_x、ライン同期信号を l\_s\_y\_n\_c\_x、クロック信号を c\_k、画像データ信号を d\_a\_t\_a とする。なお、チップセレクト信号 c\_s\_x は、各発光装置 401 に対応して出力される。具体的には、発光装置 401 - 1 に対してはチップセレクト信号 c\_s\_x\_1 が出力され、発光装置 401 - 2 に対してはチップセレクト信号 c\_s\_x\_2 が出力される。発光装置 401 - 20 に対してはチップセレクト信号 c\_s\_s\_20 が出力される。実施例 1 では、説明を簡易化するために単色の処理について説明するが、同様の処理を 4 色について並列に処理するものとする。

40

#### 【 0049 】

##### （ 画像コントローラ部 ）

画像コントローラ部 700 には、スキャナ部 100 が生成した画像データが入力され、プリント基板 202 を制御するための制御信号を送信する。なお、画像コントローラ部 700 に入力される画像データは、前述したようにスキャナ部 100 で生成したデータでもよいし、パーソナルコンピューターよりネットワーク機器（不図示）を介して転送されたデータでもよい。制御信号は、画像データの有効範囲を表すチップセレクト信号 c\_s\_x、クロック信号 c\_k、画像データ信号 d\_a\_t\_a、画像データの 1 ライン毎の区切りを表すライン同期信号 l\_s\_y\_n\_c\_x、C P U 703 との通信信号である。各々の信号は、チ

50

ップセレクト信号線 705、クロック信号線 706、画像データ信号線 707、ライン同期信号線 708、通信信号線 709を介してプリント基板 202内の発光装置 401に送信される。なお、チップセレクト信号線 705は、具体的にはチップセレクト信号線 705 - 1 ~ 705 - 20である。画像コントローラ部 700では、画像データに対する処理と、印刷タイミングに対する処理が行われる。画像データ生成部 701は、スキヤナ部 100又は画像形成装置外部から受信した画像データに対して、CPU 703により指示された解像度でディザリング処理を行いプリント出力のための画像データを生成する。実施例1では、例えば第2の解像度である600 dpiの解像度でディザリング処理を行う第2のモードである低解像度モードと、1200 dpiの解像度でディザリング処理を行う第1のモードである高解像度モードがあるものとする。

10

#### 【0050】

同期信号生成部 704は、第2の信号であるライン同期信号 l s y n c \_ xを生成し、ライン同期信号線 708を介して出力する。CPU 703は、予め定められた感光ドラム 102の回転速度及び解像度に対して、1ライン周期として、同期信号生成部 704に信号周期の時間間隔を指示する。ここで、1ライン周期とは、感光ドラム 102表面が回転方向に解像度に対応した画素サイズ分移動する周期である。感光ドラム 102表面の回転方向において、CPU 703は、低解像度モードの場合は600 dpiに相当する画素サイズ(約42.32 μm)分移動する周期を1ライン周期として、同期信号生成部 704に信号周期の時間間隔を指示する。例えば、記録紙の搬送方向に200 mm / sの速度で印刷が行われる場合、CPU 703は1ライン周期を211.6 μs(小数点2桁以下省略)として時間間隔を同期信号生成部 704に指示する。また、CPU 703は、高解像度モードの場合は1200 dpiに相当する画素サイズ(約21.16 μm)分移動する周期を1ライン周期として、同期信号生成部 704に信号周期の時間間隔を指示する。例えば、記録紙の搬送方向に200 mm / sの速度で印刷が行われる場合、CPU 703は1ライン周期を105.8 μs(小数点2桁以下省略)として時間間隔を指示する。搬送方向の速度については、感光ドラム 102の速度を制御する制御部(不図示)に設定される印刷速度(画像形成速度)の設定値(固定値)を用いてCPU 703が算出するものとする。なお、印刷速度は例えば記録紙の種類に応じて設定される。

20

#### 【0051】

チップデータ変換部 702は、同期信号生成部 704で生成したライン同期信号 l s y n c \_ xに同期して1ライン分の画像データを発光装置 401毎に分割する。チップデータ変換部 702は、発光装置 401毎に分割した画像データをクロック信号 c 1 k とチップセレクト信号 c s \_ xとともにプリント基板 202へ送信する。クロック信号 c 1 kは、制御の基準となる信号である。

30

#### 【0052】

##### (プリント基板)

次にプリント基板 202の構成について説明する。ヘッド情報格納部 710は各発光装置 401の発光量や実装位置情報といったヘッド情報を格納する記憶装置であり、通信信号を伝送する通信信号線 709を介してCPU 703と接続されている。クロック信号線 706、画像データ信号線 707、ライン同期信号線 708、通信信号線 709は発光装置 401の全てに接続されている。チップセレクト信号線 705は発光装置 401毎にチップセレクト信号線 705 - 1 ~ 705 - 20があり、各発光装置 401 - 1 ~ 401 - 20に接続されている。各発光装置 401は、チップセレクト信号 c s \_ x、クロック信号 c 1 k、ライン同期信号 l s y n c \_ x、画像データ信号 data、通信信号で設定された設定値に基づいて下部電極 410を駆動する。

40

#### 【0053】

##### (画像コントローラ部からプリント基板へのデータ転送)

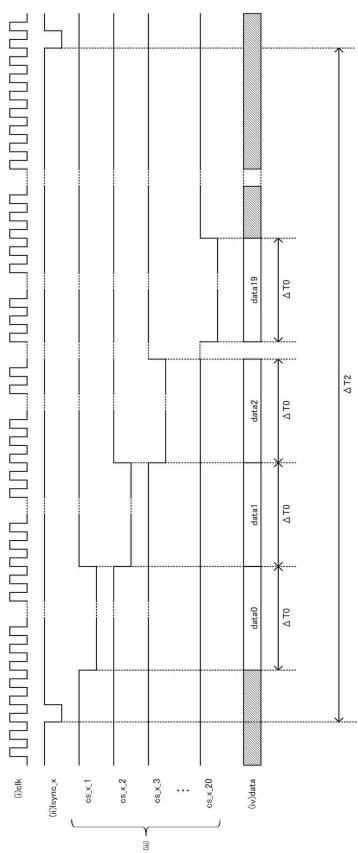

ここで、画像コントローラ部 700からプリント基板 202に搭載されている発光装置 401へのデータ転送について説明する。図7は画像コントローラ部 700とプリント基板 202の発光装置 401との間で接続されている各信号を示す図である。図7で(i)

50

はクロック信号  $c_{lk}$  の波形を示し、(i<sub>i</sub>) はライン同期信号  $l_{sync\_x}$  の波形を示す。(i<sub>ii</sub>) はチップセレクト信号  $c_s\_x\_1 \sim c_s\_x\_20$  の波形を示し、(i<sub>v</sub>) は画像データ信号  $data$  ( $data_0 \sim data_{19}$ ) を示す。画像データ信号  $data$  について斜線で示す部分は、画像データとしては無効なデータを示す。なお、チップセレクト信号  $c_s\_x\_1$  等はチップセレクト信号線  $705 \sim 1$  等を介して発光装置  $401 \sim 1$  等に入力されるチップセレクト信号を示す。また、n番目の発光装置  $401 \sim n$  内の下部電極  $410$  を駆動するための画像データを  $data(n-1)$  と表す。例えば 1 番目の発光装置  $401 \sim 1$  内の下部基板を駆動するための画像データは  $data_0$  である。よって、 $data_0$  から  $data_{19}$  で 1 ライン分の画像データとなる。また、画像データ信号  $data$  はクロック信号  $c_{lk}$  の 1 周期で画像の 1 画素分の画像データが転送される。1 ライン分の画像データ量は解像度モードによって異なる。例えば、高解像度モードでは 1 ラインは  $14960$  画素分の画像データとなり、低解像度モードでは 1 ラインはその半分である  $7480$  画素分の画像データとなる。

#### 【0054】

図 7 中の  $T_0$  は、発光装置  $401 \sim 1$  等に画像データ信号  $data$  を送信するために要する時間を示している。すなわち、時間  $T_0$  は、高解像度モードの場合はクロック信号  $c_{lk}$  の 1 周期の  $748 (\text{ }= 14960 / 20)$  倍の時間となる。一方、低解像度モードの場合はクロック信号  $c_{lk}$  の 1 周期の  $374 (\text{ }= 7480 / 20)$  倍の時間となる。各発光装置  $401 \sim 1 \sim 401 \sim 20$  に入力されるチップセレクト信号  $c_s\_x\_1 \sim c_s\_x\_20$  は、順次有効となる（アサートする）。これにより、画像データ  $data_0 \sim data_{19}$  と発光装置  $401 \sim 1 \sim 401 \sim 19$  との対応（同期）が取れるようになっている。ライン同期信号  $l_{sync\_x}$  の 1 周期である時間  $T_2$  は、前述したとおり、高解像度モードでは  $105.8 \mu\text{s}$ 、低解像度モードでは  $211.6 \mu\text{s}$  となっている。クロック信号  $c_{lk}$  の 1 周期は整数倍すると時間  $T_2$  と同一になる周期に設定されているが、ライン同期信号  $l_{sync\_x}$  の 1 周期内で画像データ  $data_0 \sim data_{19}$  がすべて発光装置  $401$  に転送できる周期であればよい。

#### 【0055】

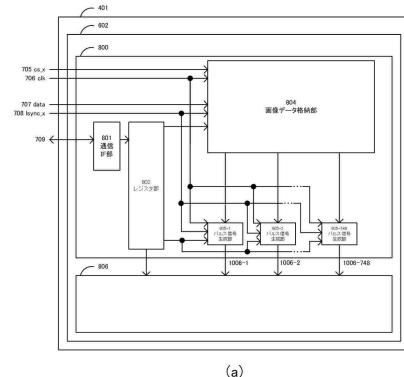

##### [発光装置内の回路構成]

図 8 (a) に発光装置  $401$  内の回路ブロック図を示す。発光装置  $401$  内の回路部  $602$  はデジタル部  $800$  とアナログ部  $806$  を有する。デジタル部  $800$  は、クロック信号  $c_{lk}$  に同期して、通信信号によって予め設定された設定値や各種信号に基づいて下部電極  $410 \sim n$  を駆動するためのパルス信号を生成し、パルス信号線  $1006$  を介してアナログ部  $806$  へ送信する機能を有する。ここで、各種信号とは、チップセレクト信号  $c_s\_x$ 、画像データ信号  $data$ 、ライン同期信号  $l_{sync\_x}$  をいう。

#### 【0056】

##### [デジタル部]

通信 IF 部  $801$  は、CPU  $703$  からの通信信号に基づいて、レジスタ部  $802$  に対する設定値のライト及びリードを制御する。レジスタ部  $802$  は、動作に必要な設定値（予め設定された設定値）を格納する。この設定値には、画像データ格納部  $804$  で使用される露光タイミング情報、パルス信号生成部  $805$  で生成されるパルス信号の幅及び位相情報（遅延情報）、アナログ部  $806$  で設定される駆動電圧の設定情報等がある。なお、駆動電圧は下部電極と上部電極間の抵抗値から導出でき、かつこの抵抗値のレンジは予め判っているため、駆動電圧の設定情報に代えて駆動電流に関する情報が格納されていても良い。画像データ格納部  $804$  は、入力されてきたチップセレクト信号  $c_s\_x$  が有効な間の画像データを保持し、ライン同期信号  $l_{sync\_x}$  に同期して画像データをパルス信号生成部  $805$  に出力する。詳細は後述する。

#### 【0057】

パルス信号生成部  $805$  は、画像データ格納部  $804$  から入力された画像データに応じて、レジスタ部  $802$  で設定されたパルス信号の幅情報及び位相情報（遅延情報）に基づきパルス信号を生成し、アナログ部  $806$  に出力する。詳細は後述する。アナログ部  $806$

6はデジタル部800で生成されたパルス信号に基づいて、下部電極410を駆動するために必要な信号を生成する。詳細は後述する。

### 【0058】

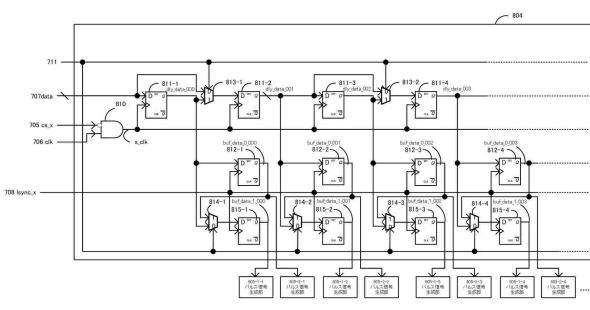

#### (画像データ格納部)

次に画像データ格納部804の動作について説明する。実施例1の画像データ格納部804は、発光装置401に内蔵されている。画像データ格納部804は、後述するように、画像データを解像度に応じた画像データに変換する変換部として機能する。図8(b)は画像データ格納部804の回路構成図である。チップセレクト信号cs\_x及びライン同期信号lSync\_xは負論理信号である例を説明するが、正論理であってもよい。さらに、解像度モード信号線711を介してレジスタ部802と接続される解像度モード信号は、例えば「0」で低解像度モード(600dpi)に対応し、「1」で高解像度モード(1200dpi)に対応する。解像度モード信号は、画像データ生成部701の動作に合わせて設定されるレジスタ信号である。クロックゲート回路810はチップセレクト信号cs\_xの反転信号とクロック信号clkとの論理積を出力とする。クロックゲート回路810は、チップセレクト信号cs\_xが有効なときのみフリップフロップ回路811にクロック信号sclickを出力する。

10

### 【0059】

フリップフロップ回路811は、画像データ格納部804へ入力されてきた画像データ信号dataを大元の入力とする。フリップフロップ回路811は発光装置401の長手方向に設けられた下部電極410の数と同じ数(実施例1では748)が直列に接続されている。フリップフロップ回路811は全体がシフト回路として機能する。具体的には、フリップフロップ回路811は、フリップフロップ回路811-1、811-2、...、811-748からなる。ここで、フリップフロップ回路811-2、811-4のような偶数番目のフリップフロップ回路811のデータ入力端子Dの前段には、セレクタ813-1、813-2...が接続されている。セレクタ813-1等を総称してセレクタ813という。セレクタ813には、セレクト信号として解像度モード信号線711が接続され、解像度モード信号が入力されている。

20

### 【0060】

セレクタ813は、解像度モード信号が「1」のときには、セレクタ813の前段に接続されているフリップフロップ回路811の出力を、セレクタ813の後段に接続されているフリップフロップ回路811に出力する。セレクタ813は、解像度モード信号が「0」のときには、セレクタ813の前段に接続されているフリップフロップ回路811の入力を、セレクタ813の後段に接続されているフリップフロップ回路811に出力する。具体的にセレクタ813-2について説明する。セレクタ813-2は、解像度モード信号が「1」のとき、セレクタ813-2の前段のフリップフロップ回路811-3の出力(dly\_data\_002)を、セレクタ813-2の後段のフリップフロップ回路811-4に出力する。セレクタ813は、解像度モード信号が「0」のとき、セレクタ813-2の前段のフリップフロップ回路811-3の入力(dly\_data\_001)を、セレクタ813-2の後段のフリップフロップ回路811-4に出力する。

30

### 【0061】

フリップフロップ回路811は、クロックゲート回路810から送られてきたクロック信号sclickに応じて動作する。フリップフロップ回路811の出力は、画像データdly\_data\_000~dly\_data\_747として、隣接して接続された次のフリップフロップ回路811又はセレクタ813及びフリップフロップ回路812に出力される。フリップフロップ回路811及びフリップフロップ回路812は下部電極410の長手方向において下部電極410の数(実施例1では748個)分設けられている。

40

### 【0062】

フリップフロップ回路812は、フリップフロップ回路811の出力を入力とし、ライン同期信号lSync\_xに応じて動作する。フリップフロップ回路812は、フリップフロップ回路812-1、812-2、...、812-748からなる。フリップフロ

50

ップ回路 812 の出力は、画像データ  $b u f\_d a t a\_0\_0 0 0 \sim b u f\_d a t a\_0\_7 4 7$  として、パルス信号生成部 805 - 1 ~ 805 - 748 に出力される。なお、ライン同期信号  $l s y n c\_x$  の 1 周期は、高解像度モードでは  $1 0 5 . 8 \mu s$  ( 小数点 2 衔以下省略 ) となる。

#### 【 0 0 6 3 】

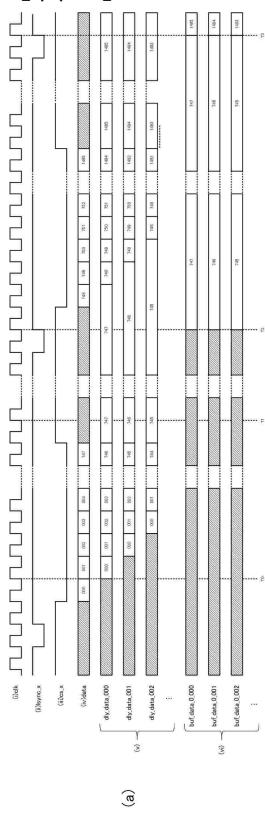

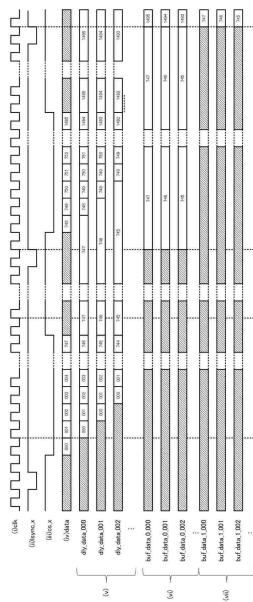

( 高解像度モードの場合 )

図 9 ( a ) は、高解像度モード、すなわち解像度モード信号が「 1 」の場合の画像データ格納部 804 の発光装置 401 の長手方向の動作を表すタイミングチャートである。図 9 ( a ) は、( i ) にクロック信号  $c l k$  の波形を示し、( ii ) にライン同期信号  $l s y n c\_x$  の波形を示し、( iii ) にチップセレクト信号  $c s\_x$  の波形を示し、( iv ) に画像データ信号  $d a t a$  を  $0 0 0 \sim 7 4 7$  で示す。ここで、「 747 」は、例えば下部電極 410 - 1 に対応する画像データを示し、「 000 」は下部電極 410 - 748 に対応する画像データを示す。画像データ信号  $d a t a$  について斜線で示す部分は、画像データとしては無効なデータを示す。( v ) はフリップフロップ回路 811 の出力である画像データ  $d l y\_d a t a\_0 0 0$  等を示し、( vi ) はフリップフロップ回路 812 の出力である画像データ  $b u f\_d a t a\_0\_0 0 0$  等を示す。

#### 【 0 0 6 4 】

チップセレクト信号  $c s\_x$  が  $0$  ( $c s\_x = 0$  ( ローレベル )) である時刻  $T_0$  から時刻  $T_1$  までの間、直列に接続されたフリップフロップ回路 811 を介して画像データは次のようにシフトしていく。時刻  $T_0$  は  $c s\_x = 0$  をクロック信号  $c l k$  の立ち上がりで捉えた時刻である。すなわち、 $d a t a\_d l y\_d a t a\_0 0 0 \sim d l y\_d a t a\_0 0 1 \dots d l y\_d a t a\_7 4 7$  といった具合に順にシフトしていく。高解像度モードの場合は、フリップフロップ回路 811 がシフトレジスタとして動作し、入力された画像データがフリップフロップ回路 811 - 1, 811 - 2 ... と順次転送される。チップセレクト信号  $c s\_x$  がローレベルとなっている期間 ( $c s\_x = 0$ ) には、クロック信号  $c l k$  が、発光装置 401 の長手方向の下部電極 410 の数と同じ数、すなわち 748 だけ入力されるものとする。こうすることで、1 ライン分の画像データが  $d l y\_d a t a\_0 0 0 \sim d l y\_d a t a\_7 4 7$  に保持されることとなる。

#### 【 0 0 6 5 】

時刻  $T_1$  以降はチップセレクト信号  $c s\_x$  が  $1$  ( $c s\_x = 1$  ( ハイレベル )) であるためにシフト動作は行われずに時刻  $T_1$  の画像データが保持される。例えば、1 つ目のフリップフロップ回路 811 で時刻  $T_1$  以降に保持される画像データ  $d l y\_d a t a\_0 0 0$  は 747 である。時刻  $T_2$  でライン同期信号  $l s y n c\_x$  が  $0$  ( $l s y n c\_x = 0$  ( ローレベル )) となると、1 ライン分の画像データが一齊に  $b u f\_d a t a\_0\_0 0 0 \sim b u f\_d a t a\_0\_7 4 7$  として、パルス信号生成部 805 に出力される。時刻  $T_2$  は  $l s y n c\_x = 0$  をクロック信号  $c l k$  の立ち上がりで捉えた時刻である。すなわち、フリップフロップ回路 811 で保持されていた画像データ  $d l y\_d a t a\_0 0 0$  等がフリップフロップ回路 812 を介して画像データ  $b u f\_d a t a\_0\_0 0$  等としてパルス信号生成部 805 に出力され、各下部電極 410 を駆動する。時刻  $T_2$  以降も同様の動作を繰り返し、順次、ライン同期信号  $l s y n c\_x$  毎にパルス信号生成部 805 - 1, 805 - 2 ... へ出力される画像データは更新される。なお、ライン同期信号  $l s y n c\_x$  の周期は高解像度モードの場合、 $1 0 5 . 8 \mu s$  であり、この周期で画像データが更新される。

#### 【 0 0 6 6 】

( 低解像度モードの場合 )

図 9 ( b ) は、低解像度モード、すなわち解像度モード信号が「 0 」の場合の画像データ格納部 804 の発光装置 401 の長手方向の動作を表すタイミングチャートである。図 9 ( b ) の ( i ) ~ ( vi ) は図 9 ( a ) の ( i ) ~ ( vi ) と同様のグラフである。

#### 【 0 0 6 7 】

チップセレクト信号  $c s\_x$  が  $0$  ( $c s\_x = 0$  ( ローレベル )) をクロック信号  $c l$

10

20

30

40

50

$k$  の立ち上がりで捉えた時刻  $T_0$  から時刻  $T_1$  の間、画像データ信号  $data$  は 0 0 0 から順次フリップフロップ回路 811 に入力される。しかし、低解像度モードの場合は、偶数番目のフリップフロップ回路 811 - 2、811 - 4、…の前段にセレクタ 813 - 1、…が挿入されている。このセレクタ 813 により、画像データ  $dly_data_{2n}$ 、 $dly_data_{2n+1}$  ( $n > 0$ ) を 1 組として同一の画像データが転送されるようになっている。具体的には、 $dly_data_{000}$  と  $dly_data_{001}$  には同一の画像データ、 $dly_data_{002}$  と  $dly_data_{003}$  には同一のデータ…が入力される。このように、画像データ信号  $data$  が隣り合う 2 つのフリップフロップ回路 811 に入力され、各画素の 2 倍のデータ量に増やされて転送される。

## 【0068】

時刻  $T_2$  でライン同期信号が 0 ( $lSync_x = 0$  (ローレベル)) をクロック信号  $c1k$  の立ち上がりで捉えると、次のように画像データが転送される。すなわち、 $dly_data_{000}$   $buf_data_{0_000}$ 、 $dly_data_{001}$   $buf_data_{0_001}$ 、…のように転送される。これにより、画像データ  $buf_data_{0_000}$ 、 $buf_data_{0_001}$ …がパルス信号生成部 805 - 1、805 - 2 …へと出力され、各下部電極 410 を駆動する。時刻  $T_2$  以降も同様の動作を繰り返し、順次、ライン同期信号  $lSync_x$  毎にパルス信号生成部 805 - 1、805 - 2 …へ出力される画像データは更新される。なお、ライン同期信号  $lSync_x$  の周期は低解像度モードの場合、 $211.6 \mu s$  であり、この周期で画像データが更新される。

## 【0069】

このように画像データが転送されることで、下部電極 410 において下部電極 410 の数が、主走査方向に高解像度モードに対応する画素数と同等の数存在する場合であっても、低解像度モードにも対応することができる。すなわち、低解像度モードでは、下部電極 410 の連続する 2 つの下部電極が同一の画像データに基づいて駆動するように画像データの転送を行う。これにより、プリント基板 202 内において主走査方向における解像度の変換が行われる。また、副走査方向は高解像度モードの場合はライン同期信号  $lSync_x$  の周期でラインの形成が行われることになり、 $1200 dpi$  の間隔でラインが形成される。一方、低解像度モードの場合は副走査方向においては $600 dpi$  の間隔でラインが形成される。

## 【0070】

実施例 1 ではこのように画像データを転送することで、下部電極 410 が主走査方向に高解像度モードと同等の素子数が存在するが、低解像度モードでは下部電極 410 の連続する 2 つの下部電極が同一データで駆動するようにデータ転送を行う。これにより主走査方向の解像度変換を行っている。

## 【0071】

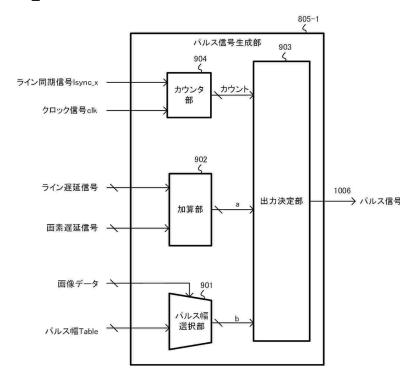

## (パルス信号生成部)

パルス信号生成部 805 について説明する。下部電極 410 の数が  $n$  個の場合、パルス信号生成部 805 も下部電極 410 の数と同数の  $n$  個、存在する。実施例 1 では、下部電極 410 - 1 ~ 410 - 748 に対してパルス信号生成部 805 - 1 ~ 805 - 748 が存在する。なお、下部電極 410 每に有するパルス信号生成部 805 の構造はそれぞれ同じである。そのためここではパルス信号生成部 805 - 1 を例に挙げて説明する。

## 【0072】

図 10 (a) にパルス信号生成部 805 - 1 のブロック図を示す。パルス信号生成部 805 - 1 は、パルス幅選択部 901、加算部 902、出力決定部 903 及びカウンタ部 904 を有する。パルス幅選択部 901 は、レジスタ部 802 によって設定されるパルス信号のパルス幅  $T_{ab1e}$  に従って画像データ格納部 804 から入力される画像データをパルス幅  $b$  に変換する。表 1 に画像データからパルス幅  $b$  に変換する際の変換表であるパルス幅  $T_{ab1e}$  の一例を示す。

## 【0073】

10

20

30

40

50

【表 1】

| 画像データ[3:0] | パルス幅b |

|------------|-------|

| 0          | 0     |

| 1          | 4     |

| 2          | 8     |

| 3          | 12    |

| 4          | 16    |

| 5          | 20    |

| 6          | 24    |

| 7          | 28    |

| 8          | 32    |

| 9          | 36    |

| 10         | 40    |

| 11         | 44    |

| 12         | 48    |

| 13         | 52    |

| 14         | 56    |

| 15         | 60    |

10

表 1 は、1 列目に画像データを示し、2 列目に画像データに対応するパルス信号のパルス幅 b を示す。例えば画像データは 4 ビット ([ 3 : 0 ]) ( 0 ~ 15 ) とする。

20

#### 【0074】

例えば画像データの入力が 2 である場合、パルス幅選択部 901 は、レジスタ部 802 によって設定された表 1 のパルス幅 T ab1e に基づいてパルス幅 b を 8 として出力決定部 903 に出力する。ただし表 1 に示したパルス幅 T ab1e は一例であり、画像データ及びパルス幅のビット幅は表 1 の例と異なっていてもよいし、パルス幅 b の値に関しても任意に設定可能である。レジスタ部 802 に格納されるパルス幅 T ab1e は、下部電極 410 ごとに個別に設定しても良いし、共通としても良い。

#### 【0075】

下部電極 410 に対応する発光層 450 はプロセスばらつきなどにより、パルス信号を同じパルス幅とした場合でも光量が異なる場合がある。下部電極 410 - 1 ~ 410 - 7 48 に対応する発光層 450 毎の光量のばらつきによって、感光ドラム 102 上に形成される静電潜像にムラが生じ、印刷画像上のムラとなる。この静電潜像のムラを無くすために、測定した光量に応じて下部電極 410 - 1 ~ 410 - 748 ごとにパルス幅 T ab1e の設定を行うことで、入力された画像データに対して正しい静電潜像となるように出力するパルス信号のパルス幅を変化させる。以上の制御により、下部電極 410 - 1 ~ 410 - 748 ごとにパルス幅 T ab1e を設定することで、下部電極 410 - 1 ~ 410 - 748 に対応する発光層 450 每の光量ばらつきによって生じる印刷画像のムラを補正することが可能である。なお、下部電極 410 - 1 ~ 410 - 748 に対応する発光層 450 の光量測定は工場で測定する又は露光ヘッド 106 に対向する位置に光量測定装置（不図示）を設置して行う。

30

#### 【0076】

加算部 902 は、全てのパルス信号生成部 805 で共通となるライン遅延信号及びパルス信号生成部 805 每に異なる画素遅延信号を加算する。これにより、加算部 902 はパルス信号の遅延時間 a を決定する。カウンタ部 904 は、クロック信号 c1k をカウントし、ライン同期信号 l x y n c\_x の周期（以下、ライン同期信号周期という）c ごとにカウントをリセットする。ライン同期信号周期は、後述する図 10 (b) にタイミング C - 1、C - 2 として表示している。カウントは出力決定部 903 に入力される。実施例 1 ではクロック信号 c1k のカウント方法をアップカウントとしているが、ダウンカウントとしてもよい。カウンタ部 904 は各下部電極 410 に対応するパルス信号生成部 805 ごとに持つてもよいし、共通としてもよい。

40

50

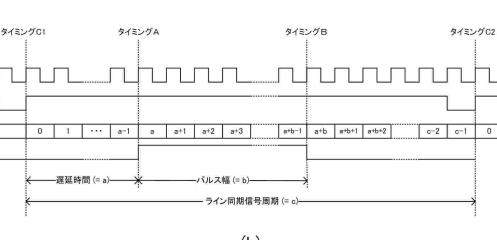

**【 0 0 7 7 】**

出力決定部 903 の動作について図 10 ( b ) を用いて説明する。図 10 ( b )において、( i ) はクロック信号 c1k の波形を示し、( i i ) はライン同期信号 l s y n c\_x の波形を示す。( i i i ) はカウンタ部 904 の出力であるカウントの値を示し、( i v ) はパルス信号生成部 805 によって生成されたパルス信号の波形を示す。

**【 0 0 7 8 】**

出力決定部 903 は、カウンタ部 904 から入力されるカウント、加算部 902 から出力される遅延時間 a 及びパルス幅選択部 901 から出力されるパルス幅 b に応じたパルス信号を生成する。出力決定部 903 は、クロック信号 c1k の立ち上がり時にライン同期信号 l s y n c\_x がローレベルであるタイミング (タイミング C - 1、C - 2) からカウントが a になるタイミング (タイミング A) で、出力であるパルス信号をハイレベルとする。出力決定部 903 は、その後、クロック信号 c1k の立ち上がり時にカウントがパルス幅 b の時間だけ経過したカウント a + b となるタイミング (タイミング B) で出力であるパルス信号をローレベルにする。これにより、出力決定部 903 はパルス信号を生成する。パルス幅 T a b l e 、ライン遅延信号及び画素遅延信号はレジスタ部 802 より送信されており、レジスタ部 802 の情報を書き換えることによりそれぞれクロック周期単位で値を変更することが可能である。10

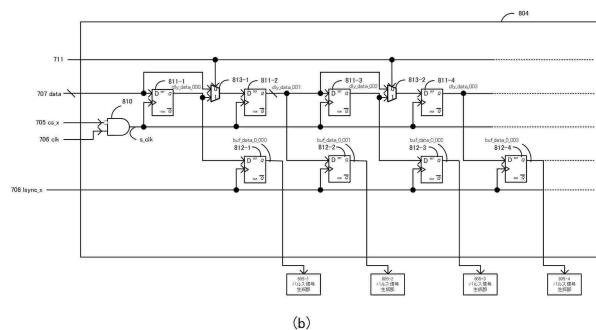

**【 0 0 7 9 】****[ アナログ部 ]**

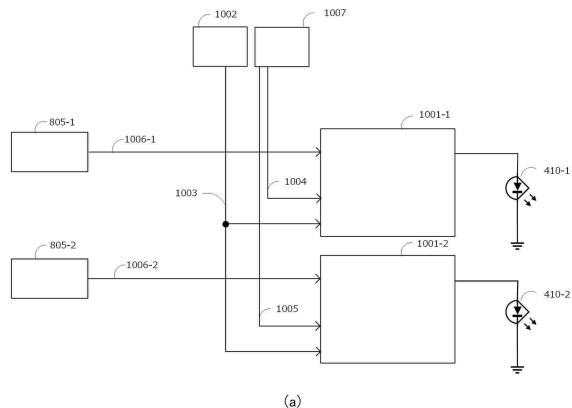

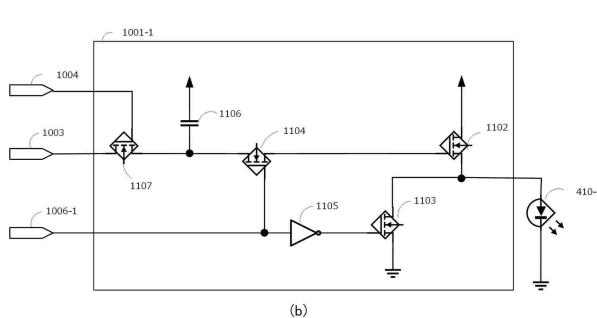

図 11 ( a ) に、アナログ部 806 のブロック図を示す。実施例 1 では説明を簡略化するため、下部電極 410-1 ~ 410-748 における 2 つの下部電極 410-1、410-2 を駆動する駆動部 1001-1、1001-2 を図示して説明する。しかし、同様の駆動部 1001-3 ~ 1001-748 が下部電極 410-3 ~ 410-748 に対応して形成されているものとする。また、上述したように、下部電極 410-1、410-2 を駆動することにより実際に発光するのは、下部電極 410-1、410-2 のそれに対応する領域の発光層 450 である。20

**【 0 0 8 0 】**

パルス信号生成部 805-1、805-2 は、下部電極 410-1、410-2 の発光 (ON) タイミングを制御するパルス信号を生成する。パルス信号生成部 805-1、805-2 は、パルス信号線 1006-1、1006-2 を介して駆動部 1001-1、1001-2 にパルス信号を入力する。30

**【 0 0 8 1 】**

デジタルアナログ変換器 (以下、DAC とする) 1002 は、レジスタ部 802 に設定されたデータに基づき信号線 1003 を介して、駆動電流を決定するアナログ電圧を駆動部 1001-1、1001-2 に供給する。駆動部選択部 1007 は、レジスタ部 802 に設定されたデータに基づき、駆動部 1001-1、1001-2 を選択する駆動部セレクト信号を、信号線 1004、1005 を介して、駆動部 1001-1、1001-2 に供給する。駆動部セレクト信号は、選択された駆動部 1001 に接続されている信号のみがハイレベルとなるように生成される。例えば、駆動部 1001-1 が選択される場合、信号線 1004 にのみハイレベルの駆動部セレクト信号が供給され、信号線 1005 など他の駆動部 1001-2 等に接続されている信号線 1005 等にはローレベルの駆動部セレクト信号が供給される。実施例 1 では駆動部セレクト信号は正論理としているが、負論理であってもよい。40

**【 0 0 8 2 】**

駆動部 1001-1、1001-2 は、各々駆動部選択部 1007 によって選択されたタイミング (駆動部セレクト信号がハイレベルになるタイミング) で、信号線 1003 を介して入力されるアナログ電圧が設定される。CPU703 はレジスタ部 802 を介して駆動部 1001-1、1001-2 を順次選択し、選択した駆動部 1001-1、1001-2 に対応した電圧を設定する。これにより、CPU703 は 1 つの DAC1002 で全ての駆動部 1001 のアナログ電圧を設定する。前述した動作により駆動部 1001-50

1、1001-2には、駆動電流を決定するアナログ電圧とパルス信号とが入力され、以降に説明する駆動回路によって各下部電極410-1、410-2が独立して駆動電流と発光時間が制御される。

#### 【0083】

##### (駆動部)

図11(b)に、下部電極410-1を駆動する駆動部1001-1の回路について示す。なお、他の下部電極410-2～410-748に対する駆動部1001-2～1001-748についても、同様の回路で駆動するものとする。MOS型電界効果トランジスタ(以下、MOSFETとする)1102は、ゲート電圧値に応じて下部電極410-1に駆動電流を供給し、ゲート電圧がローレベルのときには、駆動電流がオフ(消灯)するように電流を制御する。

10

#### 【0084】

MOSFET1104のゲート端子には、パルス信号線1006-1が接続されており、パルス信号がハイレベルのときにコンデンサ1106に充電された電圧を、MOSFET1102に受け渡す。MOSFET1107は、駆動部選択部1007から送信された駆動部セレクト信号(信号線1004より伝送)がゲート端子に接続されている。MOSFET1107は、受信した駆動部セレクト信号がハイレベルのときにオンし、DAC1002から出力されたアナログ電圧(信号線1003より伝送)を、コンデンサ1106に充電する。実施例1においては、画像形成前のタイミングで、DAC1002はコンデンサ1106にアナログ電圧を設定し、画像形成期間中はMOSFET1107をオフ状態にすることで、電圧レベルを保持し続けるものとする。

20

#### 【0085】

このような動作により、MOSFET1102は、設定されたアナログ電圧とパルス信号とに応じて駆動電流を下部電極410に供給する。下部電極410-1の入力容量が大きく、オフ時の応答速度が遅い場合は、MOSFET1103によりオフの速度を速めることが可能である。MOSFET1103はゲート端子にインバータ1105によりパルス信号を論理反転させた信号が入力されている。パルス信号がローレベルのときに、MOSFET1103のゲート端子はハイレベルになり、下部電極410-1の入力容量に充電された電荷を強制的に放電する。

#### 【0086】

30

##### [感光ドラム上の潜像]

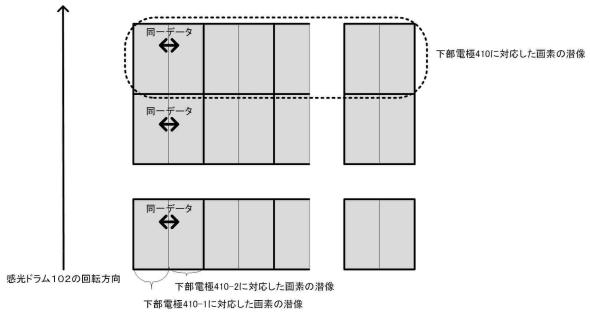

図12は実施例1における動作を用いて形成された感光ドラム102上の潜像を示す模式図であり、感光ドラム102の回転方向も示す。図中破線で示す部分は下部電極410、発光層450、上部電極460(以下、下部電極410等という)で形成された画素に対応する潜像を示す。また、回転方向に直交する方向の1マスは、下部電極410-1、410-2、...等でそれぞれ形成された画素に対応する潜像を示す。図12(a)は高解像度モード時に感光ドラム102上に形成される潜像の模式図である。高解像度モード時は感光ドラム102の回転方向と直交する方向にも平行な方向にも1200dpiの潜像が形成される。

#### 【0087】

40

図12(b)は低解像度モード時に感光ドラム102上に形成される潜像の模式図である。低解像度モード時は感光ドラム102の回転方向と直交する方向にも平行な方向にも1200dpiの潜像が形成される。しかし、回転方向に直交する方向においては、2画素毎、言い換えれば隣り合う2つの下部電極410を用いて同一の画像データに基づく画像が形成される(「同一データ」として示す)。このため、解像度としては600dpi相当の潜像となる。また、感光ドラム102の回転方向と平行方向にも、ライン同期信号1sync\_xが600dpiに相当する周期で出力されるため、600dpiの画素が形成される。

#### 【0088】

以上のように、発光装置401の内部に解像度を変換する回路を有することで同一の露

50

光ヘッドを用いて高解像度の画像も低解像度の画像も扱うことが可能となる。また、入力された解像度に依らず発光装置 401 の下部電極等（言い換えれば発光点）と同様の解像度に変換するため、解像度による発光点の距離差も発生せず、安定した画像を形成することができる。なお、実施例 1 では同一の画像コントローラ部 700 が低解像度、高解像度の両画像を出力できる構成である。しかし、本構成の露光ヘッドであれば、低解像度のみしか出力できない画像コントローラ部や、高解像度のみしか出力できない画像コントローラ部であっても、同一の露光ヘッドを接続することが可能である。

#### 【0089】

以上、実施例 1 によれば、高解像度の画像も低解像度の画像も画質を低下させることなく同一の露光ヘッドを用いることができる。

10

#### 【実施例 2】

#### 【0090】

有機 E L を用いた発光装置は、レーザーダイオードなどと比べて一般的に発光輝度が比較的低い傾向がある。特に実施例 1 の高解像度モードのようにライン同期信号 1 s y n c — × の 1 周期が短くなると 1 画素（又は 1 ライン）の露光時間が短くなり、感光ドラム 102 上での潜像形成が困難になる場合がある。そこで、実施例 2 では下部電極 410 を 2 列に配置した例を説明する。なお、画像形成装置全体の構成、露光ヘッドの構成、基板の構成、は実施例 1 と同様であり、実施例 1 との差について説明する。

#### 【0091】

##### 〔発光領域における複数の下部電極の配列（多重発光）〕

20

図 13 に示すように、実施例 2 の発光装置 401 は、下部電極 410 - 1 ~ 410 - 7 48 に加えて、下部電極 420 - 1 ~ 420 - 748 を備える。下部電極 420 - 1 ~ 420 - 748 は、下部電極 410 - 1 ~ 410 - 748 と同様に、シリコン基板 402 上に層状（第 1 の電極層）に形成された複数の電極である。下部電極 420 - 1 ~ 420 - 748 を第 2 の電極列とする。第 2 の電極列をなす下部電極 420 - 1 ~ 420 - 748 は感光ドラム 102 の回転軸線方向に沿って並んでいる。ここで、これら下部電極 420 - 1 ~ 420 - 748 は感光ドラム 102 の回転軸線方向に対して ± 1° 程度傾いて並んでいても構わない。厳密に感光ドラム 102 の回転軸線方向に対して平行に並んでいる必要はない。

#### 【0092】

30

すなわち、発光装置 401 は、2 次元配列された下部電極を備える。下部電極 420 - 1 ~ 420 - 748 のサイズ、形状、X 方向における配列は下部電極 410 - 1 ~ 410 - 748 と同様であるので説明を省略する。

#### 【0093】

下部電極 420 - 1 ~ 420 - 748（第 2 の電極列）は Y 方向において下部電極 410 - 1 ~ 410 - 748（第 1 の電極列）に対して間隔 d を開けて配置されている。Y 方向において下部電極 420 - 1 は下部電極 410 - 1 に隣接して配置され、同様に下部電極 420 - 2 ~ 下部電極 420 - 748 は、それぞれ下部電極 410 - 2 ~ 下部電極 410 - 748 に隣接して配置される。ここで、Y 方向は感光ドラム 102 の回転方向に略平行な方向である。すなわち、第 1 の電極列と第 2 の電極列とが並ぶ方向は、感光ドラム 102 の回転方向に対して ± 1° 程度傾いていても構わない。なお、実施例 2 のように、必ずしも X 方向における下部電極間距離と Y 方向における下部電極間距離とを等しく設計する必要はないが、所定面積内に効率よく下部電極を配列するために双方向における下部電極間距離を等しく設計することが望ましい。また、実施例 2 では説明を簡易にするために 2 列の電極列を備える発光装置を例示するが、図 13 (c) に示すように、電極列は 3 列以上の任意の数の列であっても良い。例えば、上記と同様に、下部電極 420 - 1 ~ 420 - 748 それぞれに対して下部電極 430 - 1 ~ 430 - 748 を隣接して配置し、さらに、下部電極 430 - 1 ~ 430 - 748 に対して下部電極 440 - 1 ~ 440 - 748 を隣接して配置しても良い。以下では、説明を簡易にするために、下部電極 410 - 1 ~ 410 - 748、および下部電極 420 - 1 ~ 420 - 748 を有する発光装置 401

40

50

を例に説明を進める。

【0094】

下部電極410-1および下部電極420-1を同時に駆動したときに、感光ドラム102上における両電極の駆動により露光される中心位置間の距離は感光ドラム102の回転方向において $W + d$ ずれる。本実施例の画像形成装置は、感光ドラム102の回転方向において隣接する複数の下部電極（例えば、下部電極410-1と下部電極420-1）を駆動することによって画像形成装置の出力解像度におけるある1画素に相当する領域を露光する。そのため、感光ドラム102の回転速度に応じて下部電極410-1への電圧印加のタイミングと下部電極420-1への電圧印加のタイミングとに時間差を設けることによって1画素に相当する領域を複数回露光することができる（多重露光）。 10

【0095】

下部電極410、420は、図中X方向に所定の間隔、例えば解像度が1200dpiである場合には21.16μmのピッチで列状に配列される。また、下部電極410、420はY方向に21.16μmのピッチの間隔で配列されている。実施例2の場合、幅Wは20.9μm、隣接間隔dは0.26μmピッチに配置している。なお、下部電極410、420の断面は実施例1と同様である。

【0096】

図13(b)は、長手方向に2列に配置された発光装置401のチップ間の境界部の様子を示す図であり、水平方向は、図3(a)の発光装置群400の長手方向であり、発光装置401が複数配置されている。図13(b)に、発光装置401のチップ間の境界部（長手方向においてチップ同士の端部が重なっている部分（重なり部））を示す。発光装置401は、複数の下部電極410を有している。発光装置401-2nと発光装置401-2n+1間の境界部においても、下部電極410の長手方向のピッチ（2つの下部電極の中心点と中心点の間隔(L)）は、1200dpiの解像度のピッチである略21.16μmとなっている。 20

【0097】

また、短手方向の上下2列に並んだ発光装置401は、次のように配置されている。すなわち、上下の発光装置401の下部電極の間隔（図中、矢印Sで示す）が約105μm（1200dpiで5画素分）となるように配置されている。また、露光ヘッド106の長手方向の下部電極410の間隔（図中、矢印Lで示す）は、約21.16μm（1200dpiで1画素分）となっている。なお、実施例2においても、発光装置401間の間隔S、Lは、前述した値に限定する必要はないものとする。 30

【0098】

図14(a)に発光装置401内の回路ブロック図を示す。回路の構成は実施例1と同じである。しかし、下部電極410が2列に増えているため、パルス信号生成部805の数も2倍となる。具体的には、下部電極410に対応するパルス信号生成部は805-1-1、805-1-2、…805-1-748となる。また、下部電極420に対応するパルス信号生成部は805-2-1、805-2-2、…805-2-748となる。また、パルス信号生成部805-1-1、805-2-1等は、パルス信号線1006-1-1、1006-2-1等を介してアナログ部806に接続される。 40

【0099】

（画像データ格納部）

次に画像データ格納部804の動作について説明する。チップセレクト信号c\_s\_x及びライン同期信号l\_s\_y\_n\_c\_xは負論理信号である例を説明するが、正論理であってもよい。解像度モード信号線711を介してレジスタ部802と接続される解像度モード信号は、「0」で低解像度モード（600dpi）に対応し、「1」で高解像度モード（1200dpi）に対応する。解像度モード信号は、画像データ生成部701の動作に合わせて設定されるレジスタ信号である。図8(b)は画像データ格納部804の回路構成図である。クロックゲート回路810はチップセレクト信号c\_s\_xの反転信号とクロック信号c\_l\_kとの論理積を出力とする。クロックゲート回路810は、チップセレクト信号 50

`c s _ x` が有効なときのみフリップフロップ回路 811 にクロック信号 `s _ c l k` を出力する。

#### 【0100】

フリップフロップ回路 811 は、画像データ格納部 804 へ入力されてきた画像データ信号 `d a t a` を大元の入力とする。フリップフロップ回路 811 は発光装置 401 の長手方向に設けられた下部電極 410 数と同じ数（実施例 2 では 748）が直列に接続されている。偶数番目のフリップフロップ回路 811 - 2、811 - 4 … のデータ入力端子 D の前段には、セレクタ 813 - 1、813 - 2 … が接続されている。セレクタ 813 - 1、813 - 2、… には解像度モード信号線 711 が接続されセレクト信号が入力される。

10

#### 【0101】

フリップフロップ回路 811 は、クロックゲート回路 810 から送られてきたクロック信号 `s _ c l k` に応じて動作する。フリップフロップ回路 811 の出力は、画像データ `d l y _ d a t a _ 0 0 0 ~ d l y _ d a t a _ 7 4 7` として、隣接して接続された次のフリップフロップ回路 811 又はセレクタ 813 並びにフリップフロップ回路 812 及びセレクタ 814 に出力される。フリップフロップ回路 811 及びフリップフロップ回路 812 は下部電極 410 の長手方向において下部電極 410 の数（実施例 2 では 748 個）分設けられている。フリップフロップ回路 811 は全体がシフト回路として機能する。

#### 【0102】

フリップフロップ回路 812 は、フリップフロップ回路 811 の出力を入力とし、ライン同期信号 `l s y n c _ x` に応じて動作する。フリップフロップ回路 812 の出力は、画像データ `b u f _ d a t a _ 0 _ 0 0 0 ~ b u f _ d a t a _ 0 _ 7 4 7` として、パルス信号生成部 805（805 - 2 - 1、805 - 2 - 2、805 - 2 - 3 …）とセレクタ 814 に出力される。フリップフロップ回路 812 は各々がメモリ回路として機能し、1つの下部電極 420 に対して設けられたフリップフロップ回路 812 はメモリ回路群（又は第 2 のメモリ回路群）として機能する。パルス信号生成部 805 - 2 - 1、805 - 2 - 2、805 - 2 - 3 … は第 1 のパルス信号を生成する第 1 のパルス信号生成部群として機能する。

20

#### 【0103】

セレクタ 814 の出力はフリップフロップ回路 815 に接続される。セレクタ 814 には、セレクタ 813 と同様に解像度モード信号線 711 が接続され、セレクト信号が入力されている。セレクタ 814 は、解像度モード信号が「1」のときには、フリップフロップ回路 812 の出力をフリップフロップ回路 815 に出力する。セレクタ 814 は、解像度モード信号が「0」のときには、フリップフロップ回路 811 の出力をフリップフロップ回路 815 に出力する。具体的にセレクタ 814 - 2 について説明する。セレクタ 814 - 2 は、解像度モード信号が「1」のときには、フリップフロップ回路 812 - 2 の出力（`b u f _ d a t a _ 0 _ 0 0 1`）をフリップフロップ回路 815 - 2 に出力する。セレクタ 814 - 2 は、解像度モード信号が「0」のときには、フリップフロップ回路 811 - 2 の出力（`d l y _ d a t a _ 0 0 1`）をフリップフロップ回路 815 - 2 に出力する。

30

#### 【0104】

セレクタ 814 の出力はフリップフロップ回路 815 に入力される。フリップフロップ回路 815 の出力は、画像データ `b u f _ d a t a _ 1 _ 0 0 0 ~ b u f _ d a t a _ 1 _ 7 4 7` として、パルス信号生成部 805（805 - 1 - 1、805 - 1 - 2、805 - 1 - 3 …）に出力される。フリップフロップ回路 815 は各々がメモリ回路として機能し、1つの下部電極 410 に対して設けられたフリップフロップ回路 815 はメモリ回路群（又は第 1 のメモリ回路群）として機能する。パルス信号生成部 805 - 1 - 1、805 - 1 - 2、805 - 1 - 3 … は第 2 のパルス信号を生成する第 2 のパルス信号生成部群として機能する。

40

#### 【0105】

50

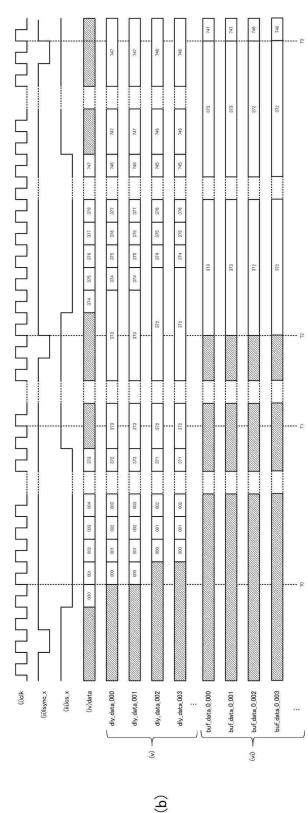

(高解像度モードの場合)

図15(a)は高解像度モード、すなわち解像度モード信号が「1」の場合の画像データ格納部804のタイミングチャートである。図15(a)の(i)~(v)は図9(a)の(i)~(v)と同様のグラフである。図15(a)の(vi)はフリップフロップ回路812の出力である画像データbuf\_data\_0\_000等を示し、(vii)はフリップフロップ回路815の出力である画像データbuf\_data\_1\_000等を示す。

【0106】

チップセレクト信号cs\_xが0(cs\_x=0(ローレベル))である時刻T0から時刻T1までの間、直列に接続されたフリップフロップ回路811を介して画像データは次のようにシフトしていく。時刻T1はcs\_x=0をクロック信号clkの立ち上がりで捉えた時刻である。すなわち、data\_dly\_data\_000 data\_001 ... dly\_data\_747といった具合に順にシフトしていく。チップセレクト信号cs\_xがローレベルとなっている期間(cs\_x=0)には、クロック信号clkが、発光装置401の長手方向の下部電極の数と同じ数、すなわち748だけ入力されるものとする。こうすることで、1ライン分の画像データがdly\_data\_00 ~ dly\_data\_747に保持されることとなる。

【0107】

時刻T1以降はチップセレクト信号cs\_xが1(cs\_x=1(ハイレベル))であるためにシフト動作は行われずに時刻T1の画像データが保持される。例えば、1つ目のフリップフロップ回路811で時刻T1以降に保持される画像データdly\_data\_000は747である。時刻T2でライン同期信号lSync\_xが0(lSync\_x=0(ローレベル))となると、1ライン分の画像データが一齊にbuf\_data\_0\_000 ~ buf\_data\_0\_747として、パルス信号生成部805に出力される。時刻T2はlSync\_x=0をクロック信号clkの立ち上がりで捉えた時刻である。すなわち、フリップフロップ回路811で保持されていた画像データdly\_data\_000等がフリップフロップ回路812を介して画像データbuf\_data\_0\_00等としてパルス信号生成部805-2-1、805-2-2等に出力される。

【0108】

また、次のライン同期信号lSync\_xがアサートされるまでに、次の1ライン分の画像データ748 ~ 1495が画像データ信号線707を介して転送される。時刻T3でbuf\_data\_0\_000 buf\_data\_1\_000、buf\_data\_0\_001 buf\_data\_1\_001、...といった具合に1ライン分のデータが一齊に転送される。すなわち、フリップフロップ回路812で保持されていた画像データbuf\_data\_0\_000等がフリップフロップ回路815を介して画像データbuf\_data\_1\_000等としてパルス信号生成部805-1-1、805-1-2等に出力される。このように2ライン分の画像データがパルス信号生成部805に出力される。

【0109】

(低解像度モードの場合)

図15(b)は低解像度モード、すなわち解像度モード信号が「0」の場合の画像データ格納部804のタイミングチャートである。図15(b)の(i)~(vii)は図15(a)の(i)~(vii)と同様のグラフである。チップセレクト信号が0(cs\_x=0(ローレベル))をクロック信号clkの立ち上がりで捉えた時刻T0から時刻T1の間、直列に接続されたフリップフロップ回路811を介して画像データは次のようにシフトしていく。ここで、画像データ信号dataから順次入力されるが、偶数番目のフリップフロップ回路811の前段にはセレクタ813が挿入されている。低解像度モードの場合、セレクタ813により、画像データ信号dataは、dly\_data\_2n、dly\_data\_2n+1(n>0)を1組として同一のデータが転送されるようになっている。具体的には、dly\_data\_000とdly\_data\_001には同一の画像データ、dly\_data\_002とdly\_data\_003には同一の画像データが転送される。

10

20

30

40

50

ータ…が入力される。このように画像データ信号 `data` が各画素の 2 倍のデータ量に増やされて転送される。

#### 【0110】

時刻  $T_2$  でライン同期信号 `sync_x` が 0 ( $sync_x = 0$  (ローレベル)) をクロック信号 `clk` の立ち上がりで捉える。低解像度モードの場合、次のようにフリップフロップ回路  $815$  の前段にあるセレクタ  $814$  によって、`buf_data_0_n`、`buf_data_1_n` が同一の画像データとなるように画像データが選択される。具体的には、`dy_data_000 buf_data_0_000` 及び `buf_data_1_000` となるまた、`dy_data_001 buf_data_0_01` 及び `buf_data_1_001` となる。そのため、1 ライン分の画像データが 2 ライン分の画像データとしてコピーされるように一齊に転送され、2 ライン分のデータとしてパルス信号生成部  $805$  に出力される。10

#### 【0111】

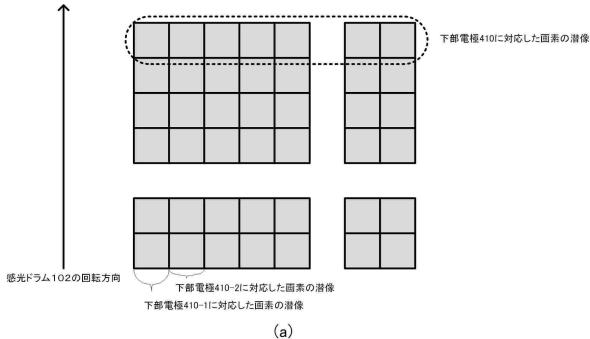

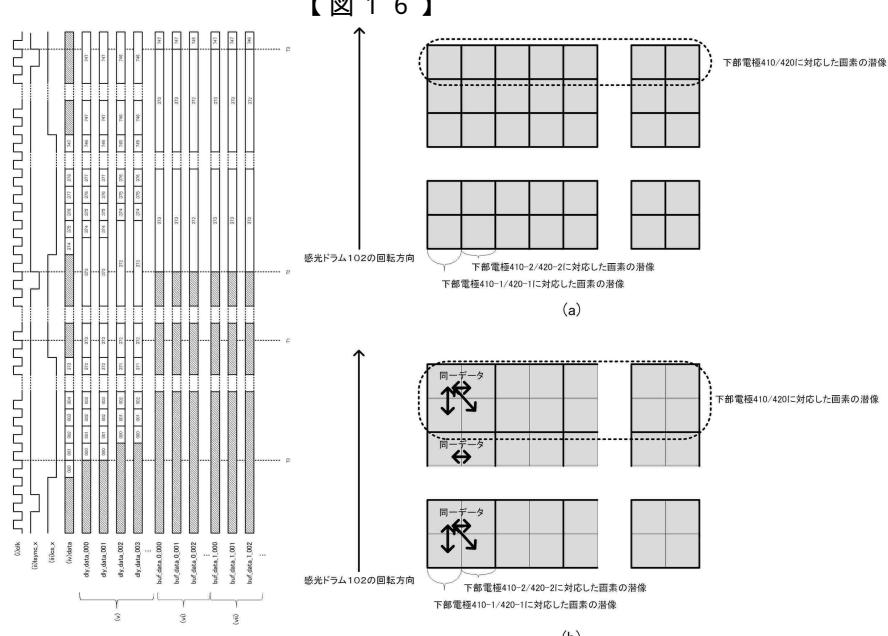

##### [感光ドラム上の潜像]

図 16 は実施例 2 における動作を用いて形成された感光ドラム  $102$  上の潜像を示す模式図であり、感光ドラム  $102$  の回転方向も示す。図中破線で示す部分は下部電極  $410$  及び下部電極  $420$  で形成された画素に対応する潜像を示す。また、回転方向に直交する方向の 1 マスは、下部電極  $410 - 1$  及び下部電極  $420 - 1$ 、下部電極  $410 - 2$  及び下部電極  $420 - 2$  … でそれぞれ形成された画素に対応する潜像を示す。図 16 (a) は高解像度モード時に感光ドラム  $102$  上に形成される潜像の模式図である。高解像度モード時は感光ドラム  $102$  の回転方向と直交する方向には、下部電極  $410$ 、 $420$  の解像度と同様の  $1200 \text{ dpi}$  の潜像が形成される。感光ドラム  $102$  の回転方向に平行な方向にも、 $1200 \text{ dpi}$  の潜像が形成される。また、各画素は下部電極  $410$ 、 $420$  がそれぞれ同じ画像データを感光ドラム  $102$  上の同一画素に時間差で露光するため、2 回の露光で各画素の潜像が形成される。20

#### 【0112】

図 16 (b) は低解像度モード時に感光ドラム  $102$  上に形成される潜像の模式図である。低解像度モード時は感光ドラム  $102$  の回転方向と直交する方向にも平行な方向にも  $1200 \text{ dpi}$  の潜像が形成される。しかし、感光ドラム  $102$  の回転方向に直交する方向においては、2 画素毎、言い換えれば隣り合う 2 つの下部電極を用いて同一の画像データに基づく画像が形成されるため、解像度としては  $600 \text{ dpi}$  相当の潜像となる。また、感光ドラム  $102$  の回転方向と平行方向にも、同一の画像データに基づく画像が形成されるため、 $1200 \text{ dpi}$  で画像を形成しているが、実質的な解像度としては  $600 \text{ dpi}$  と等価の潜像が形成される。30

#### 【0113】

以上のように、実施例 2 では、下部電極を複数列（実施例 2 の場合 2 列）有する下部電極が 2 次元配列された発光装置  $401$  を有する露光ヘッドである。この場合でも、発光装置  $401$  内部に解像度を変換する回路を持つことで、高解像度モードのように 1 画素に対する発光時間が短い場合でも多重に露光することが可能である。また、低解像度モードの場合でも解像度変換を行うことで入力された解像度に依らず発光装置  $401$  の発光点と同様の解像度に変換するため、解像度による発光点の距離差も発生しない。このように、本発明は、下部電極が少なくとも 1 列配置されたシリコン基板  $402$  に適用することができる。40

#### 【0114】

以上、実施例 2 によれば、高解像度の画像も低解像度の画像も画質を低下させることなく同一の露光ヘッドを用いることができる。

#### 【符号の説明】

#### 【0115】

202 プリント基板

401 発光装置

|       |          |

|-------|----------|

| 4 0 2 | シリコン基板   |

| 4 1 0 | 下部電極     |

| 4 5 0 | 発光層      |

| 4 6 0 | 上部電極     |

| 6 0 2 | 回路部      |

| 6 0 4 | 発光領域     |

| 8 0 4 | 画像データ格納部 |

〔义面〕

【 四 1 】

【 図 2 】

10

20

30

40

50

【図3】

【図4】

10

20

30

40

【図5】

【図6】

50

【図 7】

【図 8】

10

(a)

20

(b)

【図 9】

【図 10】

30

(a)

40

(b)

50

【図 1 1】

【図 1 2】

10

20

30

40

【図 1 3】

【図 1 4】

50

【図 15】

(a)

【図 16】

10

20

30

40

50

---

**フロントページの続き****(51)国際特許分類**F I

G 0 3 G    15/00    3 0 3**(56)参考文献**

特開2007-098772(JP,A)

特開2016-110743(JP,A)

特開2005-169703(JP,A)

特開2014-088021(JP,A)

特開2003-182138(JP,A)

特開2008-246703(JP,A)

米国特許第05828400(US,A)**(58)調査した分野** (Int.Cl., DB名)B 4 1 J    2 / 4 4 7

B 4 1 J    2 / 4 5

G 0 3 G    1 5 / 0 4

G 0 3 G    2 1 / 0 4

H 0 5 B    3 3 / 1 4

H 0 5 B    4 4 / 0 0