(19)日本国特許庁(JP)

**(12)特許公報(B2)**

(11)特許番号

**特許第7703045号**

**(P7703045)**

(45)発行日 令和7年7月4日(2025.7.4)

(24)登録日 令和7年6月26日(2025.6.26)

## (51)国際特許分類

|        |                |        |              |

|--------|----------------|--------|--------------|

| H 03 F | 3/08 (2006.01) | H 03 F | 3/08         |

| A 61 B | 6/03 (2006.01) | A 61 B | 6/03 5 7 3   |

| A 61 B | 6/42 (2024.01) | A 61 B | 6/42 5 3 0 R |

| G 01 T | 1/24 (2006.01) | G 01 T | 1/24         |

| G 01 T | 1/17 (2006.01) | G 01 T | 1/17 A       |

請求項の数 11 (全21頁)

|                   |                             |

|-------------------|-----------------------------|

| (21)出願番号          | 特願2023-564057(P2023-564057) |

| (86)(22)出願日       | 令和4年4月28日(2022.4.28)        |

| (65)公表番号          | 特表2024-518290(P2024-518290) |

|                   | A)                          |

| (43)公表日           | 令和6年5月1日(2024.5.1)          |

| (86)国際出願番号        | PCT/EP2022/061327           |

| (87)国際公開番号        | WO2022/233699               |

| (87)国際公開日         | 令和4年11月10日(2022.11.10)      |

| 審査請求日             | 令和5年12月15日(2023.12.15)      |

| (31)優先権主張番号       | 102021111362.8              |

| (32)優先日           | 令和3年5月3日(2021.5.3)          |

| (33)優先権主張国・地域又は機関 |                             |

|                   | ドイツ(DE)                     |

|          |                                                                                                                                                                                               |

|----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| (73)特許権者 | 521548733<br>アーエムエス インターナショナル アー<br>ガー<br>A M S I N T E R N A T I O N A L A G<br>スイス国 ヨーナ アイヒヴィースシュト<br>ラーセ 18 ベー<br>E i c h w i e s s t r a s s e 1 8<br>b , J o n a , S w i t z e r l a n d |

| (74)代理人  | 110002952<br>弁理士法人鷺田国際特許事務所                                                                                                                                                                   |

| (72)発明者  | アンドレウ ハラランボス<br>スイス国 タン エリカシュトラーセ 7<br>ア-                                                                                                                                                     |

| (72)発明者  | マイケル フリドリン<br>スイス国 ウ シュトッフェルシュトラ<br>最終頁に続く                                                                                                                                                    |

(54)【発明の名称】 電磁放射センサ応用例のためのフロントエンド電子回路

## (57)【特許請求の範囲】

## 【請求項 1】

電磁放射センサ応用例のためのフロントエンド電子回路であって、

電磁放射センサに結合されて前記センサから入力信号 (I in) を受け取るように構成された入力端子 (I 1 0 ) と、

出力信号 (V out\_shaper) を供給する出力端子 (O 1 0 ) と、

増幅回路 (1 1 0 0 ) とアクティブ動的フィードバック回路 (1 2 0 0 ) とを含む信号整形回路 (1 0 0 0 ) であって、前記アクティブ動的フィードバック回路 (1 2 0 0 ) は、前記信号整形回路 (1 0 0 0 ) のフィードバック経路 (1 0 0 1 ) 内に配置されている、前記信号整形回路 (1 0 0 0 ) と、を含み、

前記増幅回路 (1 1 0 0 ) は、前記入力端子 (I 1 0 ) に結合された入力ノード (I 1 0 0 a ) と、前記出力信号 (V out\_shaper) を供給する出力ノード (O 1 1 0 0 ) とを有し、前記出力ノード (O 1 1 0 0 ) は前記出力端子 (O 1 0 ) に結合され、

前記アクティブ動的フィードバック回路 (1 2 0 0 ) は、前記アクティブ動的フィードバック回路の第1の電流経路 (1 2 0 1 ) 内に配置された第1のソース - ドレイン経路を有する第1の入力トランジスタ (1 0 0 ) と、前記アクティブ動的フィードバック回路の第2の電流経路 (1 2 0 2 ) 内に配置された第2のソース - ドレイン経路を有する第2の入力トランジスタ (2 0 0 ) と、を含み、

前記第1の入力トランジスタ (1 0 0 ) は、前記出力信号 (V out\_shaper) を受け取るための制御ノードを有し、

10

20

前記第2の入力トランジスタ(200)は、基準信号( $V_{ref}$ )を受け取るための制御ノードを有し、

前記アクティブ動的フィードバック回路(1200)は、前記第1及び第2の電流経路(1201、1202)の間に配置されたバッファ回路(300)を含み、

前記第1の電流経路(1201)は、基準電位( $VSS$ )を供給する端子と前記バッファ回路(300)との間に接続され、

前記第2の電流経路(1202)は、前記基準電位( $VSS$ )を供給する前記端子と前記アクティブ動的フィードバック回路(1200)の第1のノード(1210)との間に接続され、

前記バッファ回路(300)は、前記第1のノード(1210)に接続されている入力側(I300a、I300b)と、前記第1の入力トランジスタ(100)に接続されている出力側(O300)とを有し、

前記第1の入力トランジスタ(100)のソースは、前記バッファ回路(300)の前記出力側(O300)に接続され、

前記第2の入力トランジスタ(200)のソースは、前記第1のノード(1210)に接続され、

前記アクティブ動的フィードバック回路(1200)は、第3の電流経路(1203)を含み、

前記アクティブ動的フィードバック回路(1200)は、供給電位( $VDD$ )を供給する端子と前記第1のノード(1210)との間の前記第3の電流経路(1203)内に配置された電流源(400)を含み、

前記第3の電流経路(1203)は、前記第1及び前記第2の電流経路(1201、1202)のそれに直列に接続されており、

前記アクティブ動的フィードバック回路(1200)は、前記アクティブ動的フィードバック回路(1200)の前記第1の電流経路(1201)と第6の電流経路(1206)との間に配置されて、前記アクティブ動的フィードバック回路(1200)の前記第1の電流経路(1201)からの電流を、前記第6の電流経路(1206)内に結合するカレントミラー(600)を含み、

前記アクティブ動的フィードバック回路(1200)の前記第6の電流経路(1206)は、前記信号整形回路(1000)の前記增幅回路(1100)の前記入力ノード(I1100a)と前記基準電位( $VSS$ )を供給する前記端子との間に接続される、前記フロントエンド電子回路。

### 【請求項2】

前記バッファ回路(300)は、第1及び第2の入力ノード(I300a、I300b)と出力ノード(O300)とを含み、

前記バッファ回路(300)の前記第1の入力ノード(I300a)は、前記第1のノード(1210)に接続され、

前記バッファ回路(300)の前記第2の入力ノード(I300b)は、前記バッファ回路(300)の前記出力ノード(O300)に結合され、

前記バッファ回路(300)の前記出力ノード(O300)は、前記第1の入力トランジスタ(100)に接続される、請求項1に記載のフロントエンド電子回路。

### 【請求項3】

前記バッファ回路(300)は、トランジスタ(310)と電流源(320)とを含み、

前記トランジスタ(310)は、前記基準電位( $VSS$ )を供給する前記端子と第2のノード(1220)との間の前記アクティブ動的フィードバック回路(1200)の第4の電流経路(1204)内に配置され、

前記第1の電流経路(1201)及び前記第4の電流経路(1204)は、前記基準電位( $VSS$ )を供給する前記端子と、前記アクティブ動的フィードバック回路(1200)の前記第2のノード(1220)との間に並列に接続され、

前記電流源(320)は、供給電位( $VDD$ )を供給する端子と前記第2のノード(1

10

20

30

40

50

220)との間の前記アクティブ動的フィードバック回路(1200)の第5の電流経路(1205)内に配置される、請求項1または2に記載のフロントエンド電子回路。

**【請求項4】**

前記バッファ回路(300)は増幅器(330)を含み、前記増幅器(330)は、前記アクティブ動的フィードバック回路(1200)の前記第1のノード(1210)に接続された第1の入力ノード(I330a)と、前記アクティブ動的フィードバック回路(1200)の前記第2のノード(1220)に接続された第2の入力ノード(I330b)と、前記バッファ回路(300)の前記トランジスタ(310)の制御ノードに接続された出力ノード(O330)と、を有する、請求項3に記載のフロントエンド電子回路。

**【請求項5】**

前記第2の入力トランジスタ(200)の前記制御ノードに結合されて前記基準信号(Vref)を供給する基準信号生成回路(500)を含む、請求項1に記載のフロントエンド電子回路。

**【請求項6】**

前記カレントミラー(600)は、前記第1の電流経路(1201)内に配置された第1のミラートランジスタ(610)と、前記第6の電流経路(1206)内に配置された第2のミラートランジスタ(620)とを含み、

前記カレントミラー(600)は、前記第1のミラートランジスタ(610)のゲートノードと前記第2のミラートランジスタ(620)のゲートノードとの間に配置された少なくとも1つの抵抗器(630)を含む、請求項1に記載のフロントエンド電子回路。

**【請求項7】**

前記第1の入力トランジスタ(100)は弱反転領域において動作する、請求項1に記載のフロントエンド電子回路。

**【請求項8】**

前記信号整形回路(1000)は、前記増幅回路(1100)の前記入力ノード(I100a)と前記増幅回路(1100)の前記出力ノード(O1100)との間に配置されたフィードバックコンデンサ(1300)を含み、

前記信号整形回路(1000)は、供給電位(VDD)を供給する端子と前記入力端子(I10)との間に配置された第3の電流源(1500)を含む、請求項1に記載のフロントエンド電子回路。

**【請求項9】**

前記増幅回路(1100)は、单一入力、单一出力構成、または差動入力、单一出力構成で具体化される、請求項1に記載のフロントエンド電子回路。

**【請求項10】**

光子計数回路であって、

請求項1に記載のフロントエンド電子回路(10)と、

光子感知領域(21)を有する光子検出器(20)であって、前記光子検出器(20)は、光子が前記光子感知領域(21)に当たると電流パルスを生成するように構成されている、前記光子検出器(20)と、

前記フロントエンド電子回路(10)の前記出力端子(O10)に接続されたエネルギー弁別器(30)と、を含み、

前記光子検出器(20)は、前記フロントエンド電子回路(10)の前記入力端子(I10)に接続され、

前記フロントエンド電子回路(10)は、前記電流パルスが前記フロントエンド電子回路(10)の前記入力端子(I10)に印加されると、前記フロントエンド電子回路(10)の前記出力端子(O10)において電圧パルスを生成するように構成され、

前記エネルギー弁別器(30)は、前記電圧パルスのレベルに応じてデジタル信号を生成するように構成されている、前記光子計数回路。

**【請求項11】**

医療診断用デバイスであって、

10

20

30

40

50

請求項 1\_0 に記載の光子計数回路 (2) を含み、前記デバイス (1) は、X 線装置またはコンピュータ断層撮影スキャナとして構成されている、前記医療診断用デバイス。

【発明の詳細な説明】

【技術分野】

【0 0 0 1】

本開示は、電磁放射センサ応用例のためのフロントエンド電子回路に関し、特に、マルチエネルギースペクトル CT (コンピュータ断層撮影) などの X 線画像化応用例または光子計数応用例に関する。本開示はさらに、フロントエンド電子回路を使用する光子計数センサ回路、及び医療診断用デバイスに関する。

10

【背景技術】

【0 0 0 2】

典型的な CT 装置及び X 線画像化製品では、間接変換型センサを使用している。間接変換型センサは、X 線を可視光線に変換するシンチレーターを含んでいる。可視光線は、光検出器またはフォトダイオードによって取り込まれ、X 線がシンチレーターの材料に当たることに応答して電気信号を生成する。

20

【0 0 0 3】

間接検出原理を用いる従来のコンピュータ断層撮影とは対照的に、直接変換型センサでは、入射光子が CdTe / CZT などの直接変換材料に当たると電気信号を生成することができる。直接変換材料とともに連続時間非同期フロントエンド電子機器によって、CT 装置は光子計数システムの利点を活用することができる。光子計数医用画像化は、より優れた解像度及び / またはより低いドーズ、ならびにスペクトル情報など、典型的なアプローチに比べて多くの利点がある。

【0 0 0 4】

光子計数画像化システムは、入力信号 (入力電流パルス) の高速かつ非同期の連続時間処理を必要とする。詳細には、光子計数アプローチは、電流入力を受け取り、出力において、弁別器によるさらなる処理を容易にするために整形された電圧を供給するフロントエンド回路が必要である。

30

【0 0 0 5】

フロントエンドトポロジは通常、単一段アプローチ及び二段アプローチである。入力容量が小さくて固定されている場合、単一段アーキテクチャを使用できる。これには、増幅回路とそれに続いて弁別器及びカウンタを含む信号整形回路が組み込まれている。

【0 0 0 6】

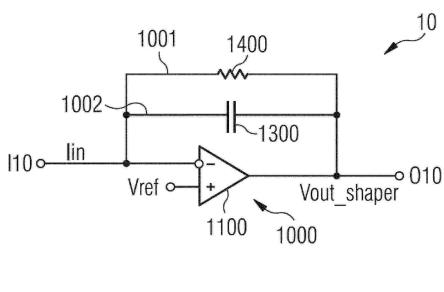

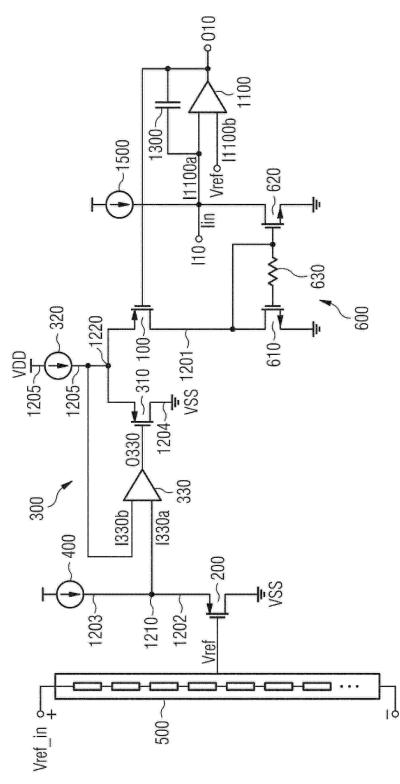

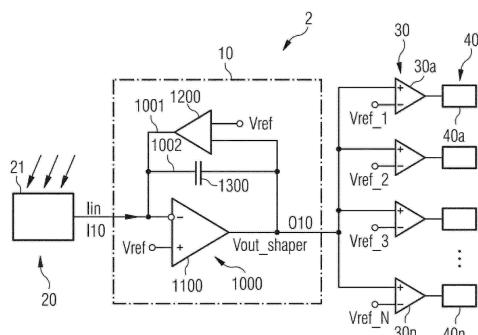

図 1 に、単一段アプローチによるフロントエンド電子回路 1\_0 を示す。フロントエンド電子回路 1\_0 は、信号整形回路 1\_0\_0\_0 を含む。信号整形回路 1\_0\_0\_0 は、電磁放射センサ、たとえば光子検出器から入力信号  $I_{in}$  を受け取るための入力端子  $I_{1_0}$  を有する。信号整形回路 1\_0\_0\_0 は、増幅回路 1\_1\_0\_0 を含む。増幅回路 1\_1\_0\_0 は、センサからの入力信号  $I_{in}$  と基準信号  $V_{ref}$  とを受け取る入力側と、フロントエンド回路の出力端子  $O_{1_0}$  において出力信号  $V_{out\_shaper}$  を供給する出力側とを有する。コンデンサ 1\_3\_0\_0 が、増幅回路 1\_1\_0\_0 の入力側と出力側との間のフィードバック経路 1\_0\_0\_2 内に配置されている。抵抗器として構成し得るフィードバック要素 1\_4\_0\_0 が、コンデンサ 1\_3\_0\_0 と並列にフィードバック経路 1\_0\_0\_1 内に配置されている。

40

【0 0 0 7】

入射光子が光子検出器の直接変換材料に当たると、過渡電流信号が生成される。この電流は入射光子のエネルギーに比例する。電流は、入力信号 / 入力電流パルス  $I_{in}$  として入力端子  $I_{1_0}$  に印加され、その後、信号整形回路 1\_0\_0\_0 によって処理されて、出力端子  $O_{1_0}$  に整形された電圧が供給される。整形された電圧は、入力電流に比例し、したがってすべての单一入射光子のエネルギーに比例する。整形器の出力電圧は、いくつかの弁別器及びカウンタによってさらに処理できる。カウント数は入射光子の数に比例する。複数の弁別器及びカウンタを有すると、各入射光子のエネルギーレベルの情報がさらに得ら

50

れる。

#### 【 0 0 0 8 】

入力容量が大きくて可変である場合、フロントエンド電子回路の二段アーキテクチャアプローチを使用できる。單一段信号整形回路の代わりに、二段フロントエンドアプローチの信号整形回路は、整形増幅器に結合された電荷感応型増幅器と、それに続いて弁別器及びカウンタを含む。フロントエンド電子回路の二段トポロジでは、信号整形段がフロントエンド電子回路の入力における入力容量から切り離されるが、電荷感応型増幅器はバッファとして機能するため、二段フロントエンド回路には、より高いノイズとパワー・ペナルティが伴う。

#### 【 0 0 0 9 】

信号整形回路の出力のベースラインは、電荷感応型増幅器及び整形増幅器の両方の正入力端子に接続された基準電圧によって規定される。これらの増幅器は通常、差動入力及びシングルエンド出力の演算相互コンダクタンス増幅器（O T A）である。

#### 【 0 0 1 0 】

光子計数フロントエンドの最も重要な性能パラメータは、低電力、低雑音、高い計数率、整形出力のパルス幅に関連する小さな F W H M（半値幅）、小さなシリコン面積、高直線性及び低い弾道欠損である。

#### 【 0 0 1 1 】

パルス幅、したがって F W H M 性能も減らして、計数率を高めるためには、前述のトポロジでは大電力を消費する必要がある。これは、このようなシステムでは望ましくない熱及び熱安定性の影響など、他の問題を引き起こす。

10

#### 【 0 0 1 2 】

光子計数フロントエンドの最も重要な構成要素は、信号整形回路とともに、そのフィードバック要素である。このブロックの構成は、フロントエンドの性能、したがってシステム全体の性能を決定するために重大である。信号整形回路自体は、必要なバンド幅を達成するために高い相互コンダクタンス  $g_m$  を示す必要がある。しかし、高い計数率を可能にする十分に高いバンド幅を達成するために、整形回路は著しい量の電力を消費する必要がある。

#### 【 0 0 1 3 】

ここで、フィードバック抵抗及びフィードバック容量であるフィードバック要素が発揮される。高い計数率を得るために F W H M を減らし、パイルアップを最小限に抑えるためには、フィードバック容量を十分に小さくする必要がある。しかし、十分な位相マージンを維持し、安定性の問題を回避するために、最小限の容量が要求される。

20

#### 【 0 0 1 4 】

他方のフィードバック要素は抵抗であり、これは、標準抵抗器（たとえば、ポリシリコン抵抗器）または線形領域で動作する M O S ドレインによって実装できる。後者が好み。なぜならば、面積を節約し、抵抗器値を非常に大きくできるだけでなく、入射放射がセンサのターゲット材料に当たるとき、パルス活動中に整形器出力がベースラインから離れるときに、飽和挙動が得られるからである。

#### 【 0 0 1 5 】

他のフィードバック実施態様では、アクティブトランスコンダクタを使用している。しかし、大きな入力エネルギーが存在し、入力パルスの大きな振幅につながる場合、またはパイルアップ事象が存在する場合は、既存のアクティブフィードバックトポロジは電流枯渇となり、したがって入力信号をさらに処理することができなくなる。

30

#### 【 0 0 1 6 】

電磁放射センサ応用例のためのフロントエンド電子回路に対するアプローチであって、整形器出力のパルス幅、したがって F W H M を減らし、さらに、信号整形回路において過剰な量の電力を消費することなく、パイルアップからの回復を改善するアプローチを提供することが求められている。

#### 【 発明の概要 】

40

50

**【 0 0 1 7 】**

電磁放射センサ応用例のためのフロントエンド電子回路であって、フロントエンド電子回路の信号整形器出力のパルス幅、したがって F W H M を強化し、さらに、パイルアップ中の計数率を改善するフロントエンド電子回路が、請求項 1 に記載されている。

**【 0 0 1 8 】**

フロントエンド電子回路は、電磁放射センサに結合されてセンサから入力信号を受け取るように構成された入力端子と、出力信号を供給する出力端子とを含む。フロントエンド電子回路は信号整形回路を含む。信号整形回路は、増幅器と、増幅回路のフィードバック経路内に配置されたアクティブ動的フィードバック回路とを含む。増幅回路は、フロントエンド電子回路の入力端子に結合された入力ノードと、出力信号を供給する出力ノードとを有する。増幅回路の出力ノードは、フロントエンド電子回路の出力端子に結合されている。

10

**【 0 0 1 9 】**

アクティブ動的フィードバック回路は、アクティブ動的フィードバック回路の第 1 の電流経路内に配置された第 1 の入力トランジスタを含む。アクティブ動的フィードバック回路はさらに、アクティブ動的フィードバック回路の第 2 の電流経路内に配置された第 2 の入力トランジスタを含む。第 1 の入力トランジスタは、出力信号を受け取るための制御ノードを有する。第 2 の入力トランジスタは、基準信号を受け取るための制御ノードを有する。アクティブ動的フィードバック回路は、第 1 及び第 2 の電流経路を切り離すように配置されたバッファ回路を含む。

20

**【 0 0 2 0 】**

提案されたアクティブ動的フィードバック回路により、パルス形状と F W H M を強化することで、信号整形回路の入力ダイナミックレンジならびにパイルアップ事象中の電流枯渇制限を改善することができる。これを達成するために、提案されたアクティブ動的フィードバック回路は、フロントエンド電子回路のフィードバック経路において非線形フィードバック抵抗 ( $1 / g_m$ ) を実現することによって、非線形性を意図的に導入する。その結果、信号整形器増幅回路において過剰な量の電力を消費することなく、計数率が著しく向上する。トポロジは、P V T 及び不一致に対して非常に頑強である。さらに、P V T とは独立して、整形器出力を基準信号の電圧レベルに調整することができる。

30

**【 0 0 2 1 】**

フロントエンド電子回路の実施形態によれば、第 1 の電流経路及び第 2 の電流経路はそれぞれ、基準電位を供給する端子とアクティブ動的フィードバック回路の共通ノードとの間に接続される。バッファ回路は、共通ノードと第 1 の入力トランジスタとの間に配置されて、第 1 及び第 2 の電流経路を切り離す。

**【 0 0 2 2 】**

バッファ回路は、第 1 の入力トランジスタ及び第 2 の入力トランジスタのそれぞれのバイアス電流をそれぞれ切り離すことができるため、第 2 の入力トランジスタを渴求させて出力のクリッピングを引き起こすことなく、整形器出力において大きな信号またはベースラインからの大きなずれを処理することができる。

40

**【 0 0 2 3 】**

フロントエンド電子回路の実施形態によれば、アクティブ動的フィードバック回路は第 3 の電流経路を含む。アクティブ動的フィードバック回路はさらに、供給電位を供給する端子と共通ノードとの間の第 3 の電流経路内に配置された電流源を含む。第 3 の電流経路は、第 1 及び第 2 の電流経路のそれぞれに直列に接続されている。

**【 0 0 2 4 】**

フロントエンド電子回路の実施形態によれば、バッファ回路は、第 1 及び第 2 の入力ノードと出力ノードとを含む。バッファ回路の第 1 の入力ノードは、共通ノードに接続されている。バッファ回路の第 2 の入力ノードは、バッファ回路の出力ノードに結合されている。可能な実施形態によれば、バッファ回路の第 2 の入力ノードは、バッファ回路の出力ノードに直接接続されているか、または、他の可能な実施形態によれば、バッファ回路の

50

第2の入力ノードは、フィードバックネットワークを介してバッファ回路の出力ノードに結合されている。バッファ回路の出力ノードは、第1の入力トランジスタに接続されている。

#### 【0025】

フロントエンド電子回路の実施形態によれば、バッファ回路は、トランジスタと電流源とを含む。トランジスタは、アクティブ動的フィードバック回路の第4の電流経路内に配置されている。第1の電流経路及び第4の電流経路は、基準電位を供給する端子とアクティブ動的フィードバック回路の第2の共通ノードとの間に並列に接続されている。電流源は、供給電位を供給する端子と第2の共通ノードとの間のアクティブ動的フィードバック回路の第5の電流経路内に配置されている。第2の共通ノードに結合された電流源によって、PVTに対して安定した電流定義が保証される。10

#### 【0026】

フロントエンド電子回路の実施形態によれば、バッファ回路は増幅器を含み、増幅器は、アクティブ動的フィードバック回路の共通ノードに接続された第1の入力ノードを有する。バッファ回路の増幅器はさらに、アクティブ動的フィードバック回路の第2の共通ノードに接続された第2の入力ノードを含む。バッファ回路の増幅器は、バッファ回路のトランジスタの制御ノードに接続された出力ノードを有する。

#### 【0027】

バッファ回路の増幅器によって、第1の入力トランジスタ及びバッファ回路のトランジスタのそれぞれのバイアス電流をそれぞれ切り離すことができるため、第2の入力トランジスタを渴求させて出力のクリッピングを引き起こすことなく、また整形器出力の飽和を引き起こすことなく、整形器出力において大きな信号またはベースラインからの大きなずれを処理することができる。バッファ回路によって第1の電流経路と第4の電流経路とを切り離すことによって、アクティブ動的フィードバック回路の第2の共通ノードにおいて低インピーダンスノードを形成することができる。20

#### 【0028】

第1及び第4の電流経路におけるそれぞれのバイアス電流を切り離すことによって、第1の電流経路における小さな電流が可能になり、信号整形回路のフィードバック経路における低い相互コンダクタンス、したがって高い抵抗が得られる。他方では、第1及び第4の電流経路におけるそれぞれのバイアス電流を切り離すことによって、第4の電流経路における大電流が可能になり、枯渇して出力のクリッピングを引き起こすことなく、信号整形回路の増幅回路の出力ノードにおいて生成される大きな信号によって要求される過電流を供給することができる。30

#### 【0029】

バッファ回路の増幅器は、バッファ回路の電流源のドレインにおけるアクティブ動的フィードバック回路の第2の共通ノードを、高インピーダンスから低インピーダンスに変換できるようにするインピーダンス変換を提供する。

#### 【0030】

フロントエンド電子回路の実施形態によれば、第1の入力トランジスタは弱反転において動作する。前述したように、アクティブ動的フィードバック回路は、非線形フィードバック抵抗を実現することによって非線形性を導入する。非線形性は、たとえば、従来、信号整形回路のフィードバック経路内に設けられことが多いMOS抵抗器とは対照的に、とりわけ、第1の入力トランジスタを弱反転においてバイアスすることによって達成される。40

#### 【0031】

信号整形回路のフィードバック経路におけるMOS抵抗器は、バイアス発生器のPVT変動によって広がるそのゲートバイアスによる抵抗変化を減らすために、強反転においてバイアスする必要がある。さらに、非線形性は、第2の共通ノードの電位が、第4の電流経路におけるバッファ回路のトランジスタによって大電流により固定され、したがって、第2の共通ノードは低インピーダンスノードのようになるという事実によって達成される50

。第1の電流経路における電流と第4の電流経路における電流とを切り離すことは、バッファ回路の増幅器によって達成される。

#### 【0032】

アクティブ動的フィードバック回路によって非線形性を信号整形段のフィードバック経路内に意図的に導入することによって、信号整形回路の増幅回路の出力ノードにおいて供給される出力信号の大きな信号振幅全体を、そうでなければ生じるバッファ回路の第2の共通ノードにおける電圧降下によって劣化することなく、第1の入力トランジスタのオーバードライブに適用できることが可能になる。

#### 【0033】

フロントエンド電子回路の実施形態によれば、第1及び第2の入力トランジスタは互いに整合している。さらに、アクティブ動的フィードバック回路の第1の電流源とバッファ回路の第2の電流源とを、互いに整合させることができる。

10

#### 【0034】

フロントエンド電子回路の実施形態によれば、アクティブ動的フィードバック回路は、アクティブ動的フィードバック回路の第1の電流経路と第6の電流経路との間に配置されて、アクティブ動的フィードバック回路の第1の電流経路からの電流を、第6の電流経路内に結合するカレントミラーを含む。アクティブ動的フィードバック回路の第6の電流経路は、信号整形回路の増幅回路の入力ノードに接続されている。

#### 【0035】

カレントミラーをアクティブ動的フィードバック回路の第1の電流経路と第6の電流経路との間に配置することによって、速度及び低オフセットを得るために十分に高い電流で第1の入力トランジスタをバイアスしながら、小さな実効相互コンダクタンス、すなわち高い等価抵抗を実現することができる。

20

#### 【0036】

実施形態によれば、フロントエンド電子回路は、第2の入力トランジスタの制御ノードに結合されて基準信号を供給する基準信号生成回路を含む。

#### 【0037】

アクティブ動的フィードバック回路に加えて、信号整形回路は、増幅回路の入力ノードと信号整形回路の増幅回路の出力ノードとの間に配置されたフィードバックコンデンサを含む。さらに、信号整形回路は、供給電位を供給する端子とフロントエンド電子回路の入力端子との間に配置された第3の電流源を含む。第1の電流源は第3の電流源と整合している。増幅回路は、单一入力、单一出力構成、または差動入力、单一出力構成で具体化することができる。

30

#### 【0038】

光子計数回路におけるフロントエンド電子回路の可能な応用例の実施形態は、請求項14に記載されている。

#### 【0039】

光子計数回路は、前述の実施形態のうちの1つによるフロントエンド電子回路を含む。光子計数回路はさらに、光子感知領域を有する光子検出器を含む。光子検出器は、光子が光子感知領域に当たると電流パルスを生成するように構成されている。光子計数回路はさらに、フロントエンド電子回路の出力端子に接続されたエネルギー弁別器を含む。

40

#### 【0040】

光子検出器は、フロントエンド電子回路の入力端子に接続されている。フロントエンド電子回路は、電流パルスがフロントエンド電子回路の入力ノードに印加されると、フロントエンド電子回路の出力ノードにおいて電圧パルスを生成するように構成されている。エネルギー弁別器は、電圧パルスのレベルに応じてデジタル信号を生成するように構成されている。

#### 【0041】

光子計数の原理を使用する医療診断用デバイスが、請求項15に記載されている。

#### 【0042】

50

デバイスは、前述で記載したように、光子計数回路を含む。デバイスは、X線装置またはコンピュータ断層撮影スキャナとして構成してもよい。

#### 【0043】

フロントエンド電子回路のさらなる特徴及び利点について、以下の詳細な説明で述べる。当然のことながら、前述の概要及び以下の詳細な説明は両方とも、単に典型的であり、特許請求の範囲の性質及び特性を理解するために概観または枠組みを提供することが意図されている。

#### 【0044】

添付図面は、さらなる理解を提供するために含まれており、本明細書に組み込まれて、その一部を構成する。したがって、本開示は、以下の詳細な説明を、添付の図と併せて取り入れることによって、より十分に理解される。

10

#### 【図面の簡単な説明】

#### 【0045】

【図1】抵抗フィードバックを備えた差動信号整形回路を含む電磁放射センサ応用例のためのフロントエンド電子回路の従来の実施形態を示す図である。

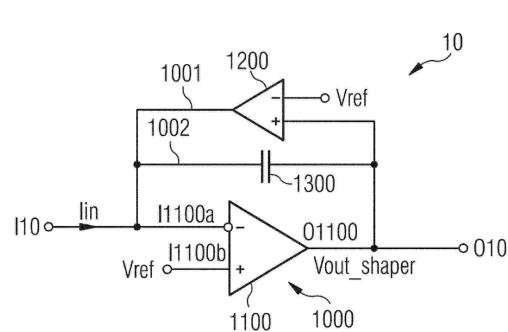

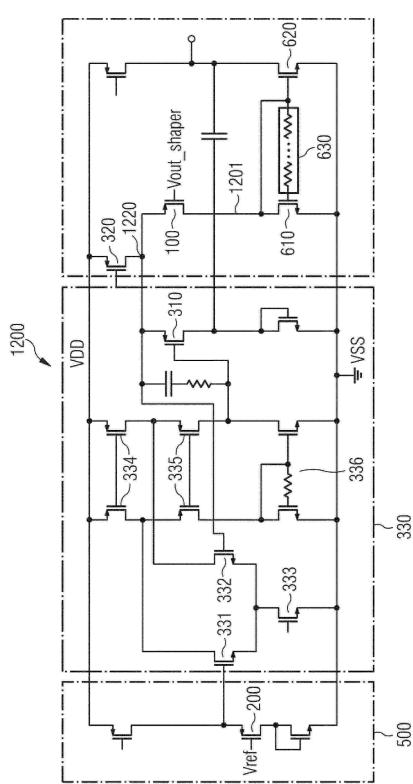

【図2A】アクティブ動的フィードバック回路を備えた差動入力信号整形回路を含む電磁放射センサ応用例のためのフロントエンド電子回路の実施形態を示す図である。

【図2B】アクティブ動的フィードバック回路を備えた单一入力信号整形回路を含む電磁放射センサ応用例のためのフロントエンド電子回路の実施形態を示す図である。

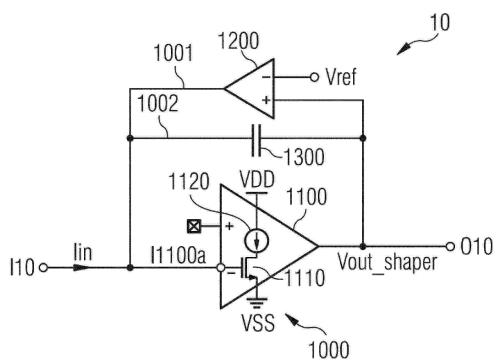

【図3A】パルス形状を強化することによって入力ダイナミックレンジならびにパイルアップ事象中の電流枯渇制限を改善するためのアクティブ動的フィードバック回路を含む電磁放射センサ応用例のためのフロントエンド電子回路の実施形態を示す図である。

20

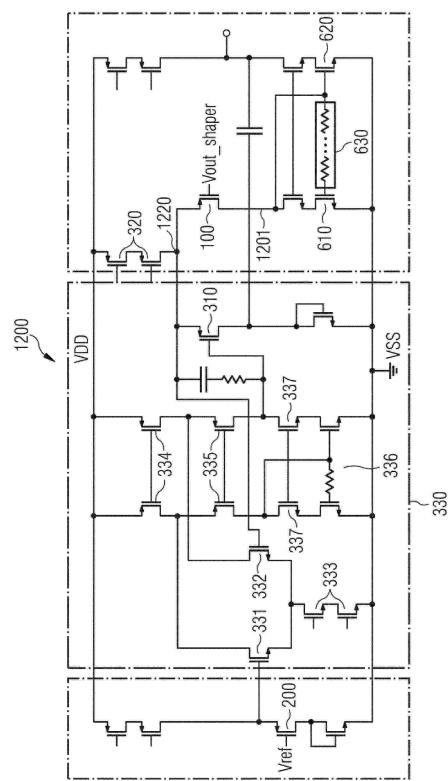

【図3B】非線形フィードバック抵抗を実現することによって非線形性を導入するためのアクティブ動的フィードバック回路を含む電磁放射センサ応用例のためのフロントエンド電子回路の第2の実施形態を示す図である。

【図4A】折り返し補助増幅器を備えた電磁放射センサ応用例のためのフロントエンド電子回路のアクティブ動的フィードバック回路の第1の実施形態を示す図である。

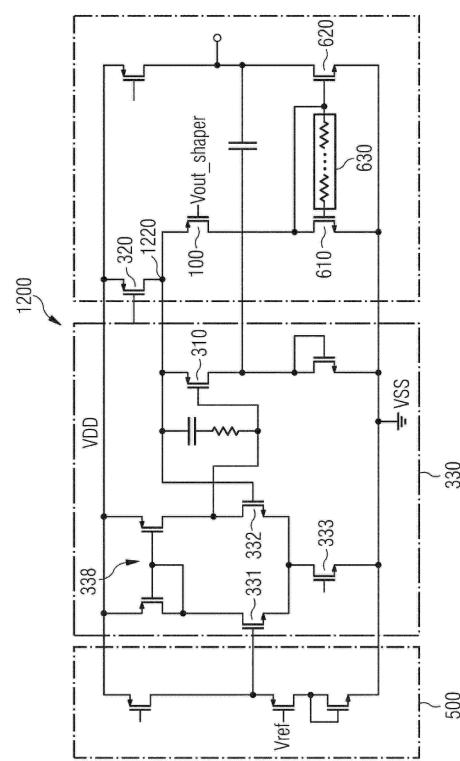

【図4B】單一段補助増幅器を備えた電磁放射センサに対するフロントエンド電子回路のアクティブ動的フィードバック回路の第2の実施形態を示す図である。

【図4C】折り返しカスコード補助増幅器を備えた電磁放射センサに対するフロントエンド電子回路のアクティブ動的フィードバック回路の実施形態を示す図である。

30

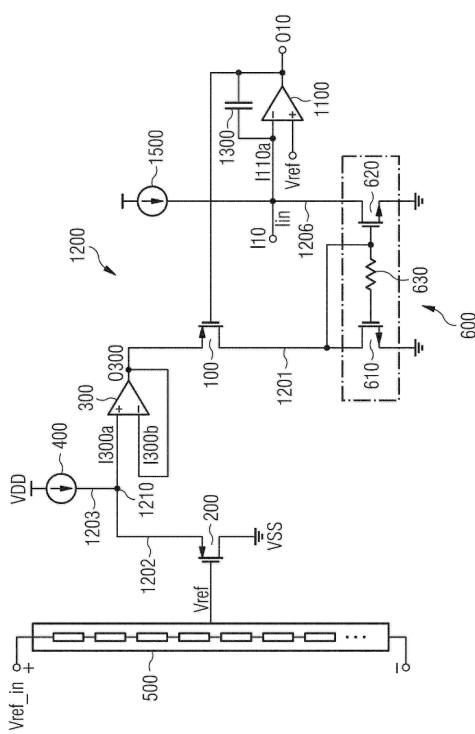

【図5A】フロントエンド電子回路の單一段アプローチを備えた光子計数回路の第1の実施形態のアーキテクチャ図を示す図である。

【図5B】フロントエンド電子回路の二段アプローチを備えた光子計数回路のアーキテクチャ図を示す図である。

【図6】光子計数回路を含む医療診断用デバイスを示す図である。

#### 【発明を実施するための形態】

#### 【0046】

図2A及び2Bはそれぞれ、電磁放射センサ応用例のためのフロントエンド電子回路10の実施形態を示す。フロントエンド電子回路10は、光子計数回路における光子計数整形器として使用してもよい。フロントエンド電子回路10は、電磁放射(たとえば、X線照射)に敏感なセンサに結合され、センサからの入力信号 $I_{in}$ を受け取るように構成された入力端子 $I_{10}$ を含む。センサは、光子検出器として構成してもよい。フロントエンド電子回路はさらに、出力信号 $V_{out\_shaper}$ を供給する出力端子 $O_{10}$ を含む。

40

#### 【0047】

フロントエンド電子回路は、信号整形回路1000を含む。信号整形回路1000は、増幅回路1100とアクティブ動的フィードバック回路1200とを含む。アクティブ動的フィードバック回路1200は、フロントエンド電子回路1000のフィードバック経路1001内に配置されている。増幅回路1100は、フロントエンド電子回路の入力端子 $I_{10}$ に結合された入力ノード $I_{1100a}$ と、出力信号 $V_{out\_shaper}$ を供

50

給する出力ノード O 1 1 0 0 とを有する。増幅回路 1 1 0 0 の出力ノード O 1 1 0 0 は、フロントエンド電子回路 1 0 の出力端子 O 1 0 に結合されている。フィードバックコンデンサ 1 3 0 0 が、増幅回路 1 1 0 0 の入力ノード I 1 1 0 0 a と増幅回路 1 1 0 0 の出力ノード O 1 1 0 0 との間に配置されている。

#### 【 0 0 4 8 】

図 2 A に、差動入力整形器アプローチを示す。増幅回路 1 1 0 0 は、差動入力、单一出力構成で具体化されている。差動入力増幅回路 1 1 0 0 は、入力信号 I i n を受け取る入力ノード I 1 1 0 0 a と、基準信号 V r e f を受け取る第 2 の入力ノード I 1 1 0 0 b とを有している。

#### 【 0 0 4 9 】

図 2 B に、フロントエンド電子回路 1 0 の单一入力アプローチを示す。増幅回路 1 1 0 0 は、单一入力、单一出力構成で具体化されている。図 2 A に示す差動入力整形器アプローチと比較すると、図 2 B の増幅回路 1 1 0 0 は、入力信号 I i n を受け取る单一入力ノード I 1 1 0 0 a のみを含む。増幅回路 1 1 0 0 は、单一入力ノード I 1 1 0 0 a に結合された制御ノードを有する入力トランジスタ 1 1 1 0 を含む。増幅回路 1 1 0 0 はさらに、入力トランジスタ 1 1 1 0 と直列に配置された電流源 1 1 2 0 を含む。

#### 【 0 0 5 0 】

図 1 に示したような抵抗フィードバックを含むフロントエンド電子回路とは対照的に、図 2 A 及び 2 B に示すフロントエンド電子回路 1 0 は、信号整形回路 1 0 0 0 のフィードバック経路 1 0 0 1 内にアクティブ動的フィードバック回路 1 2 0 0 を含んでいる。アクティブ動的フィードバック回路 1 2 0 0 は、図 1 のフロントエンド回路における信号整形回路のフィードバック抵抗器と置き換わっている。

#### 【 0 0 5 1 】

提案されたアクティブ動的フィードバック回路 1 2 0 0 は、非線形フィードバック抵抗 ( $1 / g m$ ) を実現することによって非線形性を導入する。このアプローチによって、整形器出力のパルス幅、したがって半値幅 (FWHM) が著しく減り、したがってパイルアップ中の計数率が向上する。また、フロントエンド電子回路 1 0 によって、パイルアップからの回復が改善される。したがって、信号整形回路において過剰な量の電力を消費することなく、入力ダイナミックレンジならびに計数率が増加する。

#### 【 0 0 5 2 】

また、提案されたアクティブ動的フィードバック回路は、信号整形回路の高速経路内に制御ループを必要としないため、最高速度と位相マージンが得られる。さらに、提案されたアクティブ動的フィードバック回路によって、図 2 B に示したように、演算相互コンダクタンス増幅器として構成してもよい单一入力増幅回路 1 1 0 0 を利用することができ、電力消費ならびにフロントエンドのノイズがさらに減るであろう。図 1 のフロントエンド回路アプローチの抵抗素子 1 4 0 0 と置き換わるフィードバック経路 1 0 0 1 における提案されたアクティブ動的フィードバック増幅器を使用しないでは、信号整形回路の单一入力増幅回路は実現できない。

#### 【 0 0 5 3 】

アクティブ動的フィードバック回路 1 2 0 0 は、その相互コンダクタンス  $g m$  を介して抵抗として機能するだけでなく、出力ノード O 1 1 0 0 / 出力端子 O 1 0 におけるベースラインを基準電圧 V r e f に調節する。さらに、提案されたアクティブ動的フィードバック回路によって、信号整形回路の電力消費及び FWHM の点で性能も著しく向上する。

#### 【 0 0 5 4 】

前述の要件を有する信号整形回路 1 0 0 0 のフィードバック経路 1 0 0 1 内にアクティブ動的フィードバック回路を実装することは、困難である。課題の背後にある理由は、このような回路が満たさなければならない以下の要件である。

#### 【 0 0 5 5 】

第 1 に、アクティブ動的フィードバック回路 1 2 0 0 は抵抗に似ていなければならない。アクティブ動的フィードバック回路 1 2 0 0 が、同じテールノードを共有する一対の入

10

20

30

40

50

カトランジスタを含む演算相互コンダクタンス増幅器として実現されると仮定すると、これは、増幅器の入力トランジスタのうちの1つが有する抵抗 $1 / g_m$ を使用して達成され得る。しかし、アクティブ動的フィードバック回路1200は非常に高い抵抗値を提供しなければならないため、入力トランジスタの相互コンダクタンス $g_m$ は非常に小さくなければならず、これは、小さなバイアス電流と大きなオーバードライブ電圧との組み合わせによって達成できる。大きなオーバードライブ電圧は通常、供給電圧と共にテールノードに結合された電流源の飽和とによって制限されるが、小さなバイアス電流は、アクティブ動的フィードバック回路が動作できる速度ならびにダイナミックレンジに影響を及ぼす。大きなダイナミックレンジ、すなわち、大きなパルスまたはパイルアップ事象を処理すると、同じコモンモードテール電流を共有するトランジスタの入力対の他方のトランジスタの渇望が生じる。

10

#### 【0056】

第2に、アクティブ動的フィードバック回路1200はFWHMを改善しなければならない。アクティブ動的フィードバック回路は、振幅が大きなパルスに対するパルス幅またはパイルアップ事象中のパルス幅を低減することによってFWHMを改善することができる。これは非線形スキームで行われ、フィードバック要素として抵抗を使用することと比べて、FWHMが著しく改善される。しかし、この役割を果たすために、アクティブ動的フィードバック回路は、整形器出力パルスを非常に高速に処理しなければならず、効果的に反応して出力パルスを再整形できるハイダイナミックレンジを有する必要がある。したがって、入力デバイスにおける比較的大きな電流を意味する高い相互コンダクタンス $g_m$ が必要になる。これは、十分に大きなフィードバック抵抗を得るために小さな電流が必要であるという第1の前述の要件と矛盾する。

20

#### 【0057】

第3に、アクティブ動的フィードバック回路1200は、低いオフセットを達成しなければならない。アクティブ動的フィードバック回路はさらに、基準電圧を追跡し、フィードバックを介して信号整形回路の出力ベースラインを調整する役割を果たす。したがって、ミスマッチに起因するオフセットは、信号整形回路の出力ノードにおいてベースラインに対するずれを誘発する。あるレベルのずれは、比較器入力においてDACによって補正できるため、許容できる。しかし、過剰なずれは、相互コンダクタンス増幅器/比較器を入力コモンモード範囲から外してしまうため、許容できない。

30

#### 【0058】

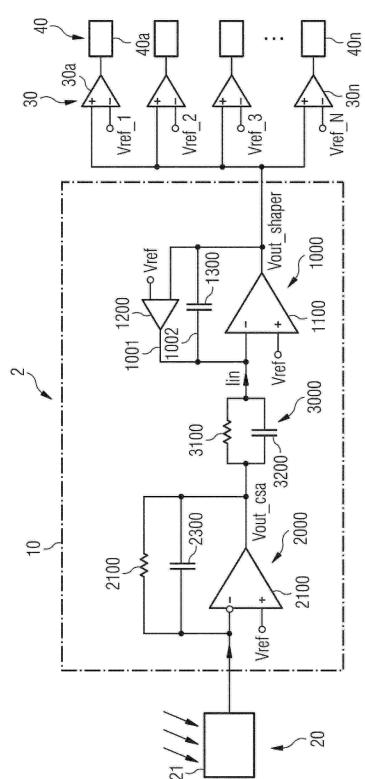

図3Aに、電磁センサ応用例のための(たとえば、光子計数フロントエンドのための)フロントエンド電子回路10の実施形態を示す。この実施形態に含まれる信号整形回路1000は、増幅回路1100、アクティブ動的フィードバック回路1200、及びフィードバックコンデンサ1300を備えている。信号整形回路1000は、供給電位VDDを供給する端子とフロントエンド電子回路10の入力端子I10との間に配置された電流源1500を含む。フロントエンド電子回路10によって、信号整形回路の差動入力増幅回路の性能を向上させることができる。さらに、フロントエンド電子回路10の提案された実施形態によって、信号整形回路に対する单一入力増幅回路の実現が可能になる。

40

#### 【0059】

図3Aのフロントエンド電子回路10を参照して、アクティブ動的フィードバック回路1200は、アクティブ動的フィードバック回路の第1の電流経路1201内に配置された第1の入力トランジスタ100を含む。アクティブ動的フィードバック回路1200は、アクティブ動的フィードバック回路1200の第2の電流経路1202内に配置された第2の入力トランジスタ200を含む。第1の入力トランジスタ100は、増幅回路1100の出力ノードO1100において生成された出力信号Vout\_shaperを受け取るための制御ノードを有する。第2の入力トランジスタ200は、基準信号/電圧Vrefを受け取るための制御ノードを有する。アクティブ動的フィードバック回路1200はさらに、第1の電流経路1201と第2の電流経路1202とを切り離すように配置されたバッファ回路300を含む。

50

**【0060】**

したがって、バッファ回路300によって、第1及び第2の電流経路1201、1202におけるバイアス電流を切り離すことができ、これにより、第2の入力トランジスタ200を渴求せることなく、かつ出力のクリッピングを引き起こすことなく、信号整形回路1000の増幅回路1100の出力ノードO1100における大きな信号またはベースラインからの大きなずれを処理することがさらに可能になる。

**【0061】**

第1の電流経路1201及び第2の電流経路1202はそれぞれ、基準電位VSSを供給する端子とアクティブ動的フィードバック回路1200の共通ノード1210との間に接続されている。

10

**【0062】**

アクティブ動的フィードバック回路1200は第3の電流経路1203を含む。アクティブ動的フィードバック回路1200はさらに、供給電位VDDを供給する端子と共にノード1210との間の第3の電流経路1203内に配置された電流源400を含む。第3の電流経路1203は、第1及び第2の電流経路1201及び1202のそれぞれに直列に接続されている。

**【0063】**

バッファ回路300は、第1の電流経路1201を第2の電流経路1202から切り離すために、共通ノード1210と第1の入力トランジスタ100との間に配置されている。バッファ回路300は、第1の入力ノードI300a、第2の入力ノードI300b、及び出力ノードO300を含む。バッファ回路300の第1の入力ノードI300aは、共通ノード1210に接続されている。バッファ回路300の第2の入力ノードI300bは、出力ノードO300に結合されている。これは、バッファ回路300の第2の入力ノードI300bは、出力ノードO300に直接接続することができるか、またはフィードバックネットワークを介して出力ノードO300に結合できることを意味する。

20

**【0064】**

アクティブ動的フィードバック回路1200によって、非線形性が導入される。これは、とりわけ、従来の信号整形回路のフィードバック経路内に配置できる従来のMOS抵抗器とは対照的に、第1の入力トランジスタ100は弱反転において動作できるという事実によって達成される。従来のMOS抵抗器は、バイアス発生器のPVT変動によって広がるそのVgat eバイアスによる抵抗変化を減らすために、強反転においてバイアスする必要がある。

30

**【0065】**

アクティブ動的フィードバック回路1200は、第2の入力トランジスタ200の制御ノードに結合されて基準信号/電圧Vrefを供給する基準信号生成回路500を含んでいてもよい。アクティブ動的フィードバック回路のオフセットは、基準信号生成回路500によって補正することができる。基準信号生成回路は、アクティブ動的フィードバック回路増幅器のオフセットを補正するために、抵抗性DAC(デジタルアナログコンバータ-)として構成してもよい。

**【0066】**

40

図3Bに、バッファ回路300の有利な実施形態を備えた図3Aのフロントエンド電子回路10を示す。

**【0067】**

バッファ回路300は、アクティブ動的フィードバック回路1200の第4の電流経路1204内に配置されたトランジスタ310を含む。第1の電流経路1201及び第4の電流経路1204は、基準電位VSSを供給する端子とアクティブ動的フィードバック回路1200の第2の共通ノード1220との間に、並列に接続されている。バッファ回路300はさらに電流源320を含む。電流源320は、供給電位VDDを供給する端子と第2の共通ノード1220との間のアクティブ動的フィードバック回路1200の第5の電流経路1205内に配置されている。

50

**【0068】**

フロントエンド電子回路10の有利な実施形態によれば、第1及び第2の入力トランジスタ100、200は互いに整合している。また、電流源400は電流源1500と整合している。さらに、電流源400及び電流源320は互いに整合している。

**【0069】**

バッファ回路300はさらに(補助)増幅器330を含む。増幅器330は、アクティブ動的フィードバック回路1200の共通ノード1210に接続された第1の入力ノードI330aを有する。増幅器330は、アクティブ動的フィードバック回路1200の第2の共通ノード1220に接続された第2の入力ノードI330bと、トランジスタ310の制御ノードに接続された出力ノードO330とを有する。

10

**【0070】**

第1の電流経路1201におけるバイアス電流と第4の電流経路1204におけるバイアス電流とを切り離すことによって、第2の共通ノード1220において低インピーダンスを形成することができる。(補助)増幅器330はインピーダンス変換を提供する。詳細には、電流源320のドレインにおける共通テールノード1220を、高インピーダンスから低インピーダンスに変換することができる。

**【0071】**

非線形性は、共通テールノード1220の電位を(補助)増幅器330によって大電流により固定でき、共通テールノード1220が低インピーダンスノードのようになるという事実によって達成される。第1の電流経路1201における入力電流を第4の電流経路1204における補助電流と切り離すことは、(補助)増幅器330を介して達成される。したがって、整形器出力は、その大きな信号振幅全体を、そうでなければ生じるテール共通ノード1220における電圧降下によって劣化することなく、第1の入力トランジスタのオーバードライブ行使することができる。

20

**【0072】**

最終的に、(補助)増幅器がないと、アクティブ動的フィードバック回路の増幅器1100の負入力ノードI1100bは、特に高エネルギー及び/またはパイルアップ事象において、枯渇し、したがって出力をクリップする。正及び負の入力バイアス電流を切り離すことによって、正入力における小さな電流、すなわち第1の電流経路1201における小さな電流が可能になり、フィードバック経路1001における低い相互コンダクタンス、したがって高い抵抗が得られ、また負入力、すなわち第4の電流経路1204における大電流が可能になり、枯渇して出力のクリッピングを引き起こすことなく、整形器出力の大きな信号によって要求される過電流を供給することができる。

30

**【0073】**

信号整形回路1000のフィードバック経路1001内にアクティブ動的フィードバック回路1200を含むフロントエンド電子回路の主な技術的利点は、以下のようにまとめることができる。

**【0074】**

信号整形回路1000のフィードバック経路1001内にアクティブ動的フィードバック回路1200を設けることによって、差動入力整形器の性能を向上させることができ、また図3Bに示したように、单一入力整形器の実現が可能になる。提案されたアクティブ動的フィードバック回路は、パルス幅を改善する、すなわち縮小することによってより低いFWHMを達成し、したがってより高い計数率において動作する。これは、ポリシリコン抵抗器の場合の線形関係、またはバルク及びソースが整形器出力に接続されたMOS抵抗器(NMOS)の場合の二次関係とは対照的に、入力電圧と出力電流との間に高度に非線形フィードバック抵抗( $1/gm$ )を意図的に導入することによって達成される。

40

**【0075】**

入力トランジスタの差動対の非線形性は、第1の入力トランジスタ100がゲートソース電圧としてフル整形器出力電圧を受けるように、アクティブフィードバックループを使用してそのテールノード1220を強制的に定電圧にすることによって高められる。した

50

がって、(MOS)第1の入力トランジスタ100ドレイン電流対ゲートソース電圧の完全な非線形関係が利用される。

#### 【0076】

弱反転においてバイアスすると、フィードバック経路における抵抗の指數関数的な特性を実現することができ、FWHMが向上する。これにより、光子計数システムの速度及びパイルアップ中の計数率の性能が向上する。弱反転においてバイアスすることが可能であるのは、アクティブフィードバックループ用の適切な基準電圧生成、すなわち基準電圧 $V_{ref}$ に入力トランジスタ200のゲートソース電圧をえたものによって、第1の入力トランジスタ100のオーバードライブを整形器のベースラインから切り離すことができるからである。

10

#### 【0077】

同時に、標準的な差動トランジスタ対の場合と同様に、テール電流源320によって、 $PVT$ に対して安定した電流定義が保証される。アクティブフィードバックループは、第2の共通ノード1220におけるテール電位を規定するため、第4の電流経路1204における電流を第1の電流経路1201における電流から切り離す。これにより、標準的な差動対の場合のような整合制限なしに、第1の入力トランジスタ100とバッファ回路300のトランジスタ310との高度に非対称なバイアスが可能になる。

#### 【0078】

一方で、第1の入力トランジスタ100は、高いフィードバック抵抗要件に従って、より低い電流によりバイアスすることができるが、バッファ回路300のトランジスタ310は、第2の共通ノード1220における低いテールノードインピーダンスを実現し、アクティブフィードバックループがそれほど効果的ではない高周波の場合でもテール電位クランピングを達成するために、大電流によりバイアスすることができる。

20

#### 【0079】

アクティブフィードバックループと低いテールノードインピーダンスとにより、整形器出力とは関係なく第2の共通ノード1220におけるテールノード電位が一定に保たれるため、典型的な差動対アプローチの場合と同様に、大きな整形器ピークに対する電流枯渇の可能性はない。第1の入力トランジスタ100が、大きな整形器ピークに応答して過剰電流を引き出すと、その電流は、アクティブフィードバックループまたはバッファ回路300の非対称に高バイアスされたトランジスタ310のいずれかによって供給される。その結果、アクティブフィードバックループとバッファ回路300のトランジスタ310とが、第1の電流経路1201内に過電流を供給できるため、大きな整形器ピークに対する電流枯渇はない。

30

#### 【0080】

結果として、パイルアップ保護には制限がない。また、高速経路におけるアクティブ動的フィードバック回路の相互コンダクタンスを制御する相互コンダクタンスコントローラを設ける必要がなく、アクティブ動的フィードバック回路1200を高速で動作させることができる。

#### 【0081】

アクティブ動的フィードバック回路1200はさらに、アクティブ動的フィードバック回路1200の第1の電流経路1201と第6の電流経路1206との間に配置されたカレントミラー600を含む。カレントミラー600は、第1の電流経路1201内に配置されたトランジスタ610と、第6の電流経路内に配置されたトランジスタ620とを含む。カレントミラー600によって、アクティブ動的フィードバック回路1200の第1の電流経路1201からの電流を第6の電流経路1206内に結合することができる。アクティブ動的フィードバック回路1200の第6の電流経路1206は、信号整形回路100の增幅回路1100の入力ノードI1100aに接続されている。トランジスタ610及び620のそれぞれのゲートノードは、ミラーポール補償を提供するために、少なくとも1つの抵抗器630を介して接続してもよい。

40

#### 【0082】

50

カレントミラー 600 によって、第 1 の電流経路 1201 における電流のダウンスケーリングが可能になる。結果として、電流経路 1201 内の電流をダウンスケーリングすることによって、速度及び低オフセットのために十分に高い電流により第 1 の入力トランジスタ 100 をバイアスしながら、小さな実効相互コンダクタンスを実現することができる。

#### 【0083】

図 4 A、4 B、及び 4 C に、図 3 A 及び 3 B に示したアクティブ動的フィードバック回路 1200 に対する可能な実施態様を示す。図 4 A ~ 4 C では、図 3 A 及び 3 B と同じ要素には同じ引用符号により印を付けている。

#### 【0084】

図 4 A には、バッファ回路 300 の折り返し補助増幅器 330 を備えたアクティブ動的フィードバック回路 1200 に対する実施態様を示す。補助増幅器は、バイアス電流源 333 に結合された差動トランジスタ対 331、332 を含む。折り返し補助増幅器 330 はさらに、バイアストランジスタ 334、カスコードトランジスタ 335、及びカレントミラー 336 を含む。

10

#### 【0085】

図 4 B には、バッファ回路 300 の折り返しカスコード補助増幅器 330 を備えたアクティブ動的フィードバック回路 1200 に対する実施態様を示す。折り返しカスコード補助増幅器 330 は、差動トランジスタ対 331、332、バイアス電流トランジスタ 333、バイアストランジスタ 334、第 1 のカスコード段 335 のトランジスタ、第 2 のカスコード段 337、及びカレントミラー 336 を含む。

20

#### 【0086】

図 4 C には、バッファ回路 300 の單一段補助増幅器 330 を備えたアクティブ動的フィードバック回路 1200 の可能な実施態様を示す。補助増幅器 330 は、差動トランジスタ対 331、332、バイアストランジスタ 333、及びカレントミラー 338 を含む。

#### 【0087】

フィードバック経路 1001 内にアクティブ動的フィードバック回路 1200 を備えた信号整形回路 1000 を含むフロントエンド電子回路 10 の提案されたデザインは、図 5 A に示したような單一段アーキテクチャまたは図 5 B に示したような二段アーキテクチャアプローチを有する光子計数回路内に設けることができる。図 5 A 及び 5 B に、差動入力構成でのアクティブ動的フィードバック回路 1200 を示す。單一入力構成でのアクティブ動的フィードバック回路 1200 の実施態様も可能である。

30

#### 【0088】

図 5 A の光子計数回路 2 の單一段アーキテクチャを参照して、光子感知領域 21 を有する光子検出器 20 がフロントエンド電子回路 10 の入力端子 I10 に接続されている。光子検出器 20 は、光子が光子感知領域 21 に当たると電流パルスを生成するように構成されている。

#### 【0089】

フロントエンド電子回路 10 は、光子検出器 20 によって生成された電流パルスがフロントエンド電子回路 10 の入力端子 I10 に印加されると、出力ノード O10 において出力信号  $V_{out\_shape}$  の電圧パルスを生成するように構成されている。その後、整形器の出力電圧  $V_{out\_shape}$  は、エネルギー弁別器 30 のいくつかの弁別器回路 30a、...、30n によってさらに処理される。エネルギー弁別器 30 は、出力端子 O10 における電圧パルスのレベルに応じてデジタル信号を生成するように構成されている。その後、弁別器の出力は、カウンタ 40 のカウンタ回路 40a、...、40n 内に供給される。カウント数は入射光子の数に比例する。複数の弁別器回路 30a、...、30n 及びカウンタ回路 40a、...、40n を有すると、各入射光子のエネルギーレベルに関する情報が得られる。カウンタ出力は、図 5 A には示していない DSP (デジタル信号プロセッサ) によって処理してもよい。

40

#### 【0090】

入力容量が小さくて固定されている場合、図 5 A に示す光子計数回路 2 の單一段アーキ

50

テクチャを使用することができる。入力容量が大きくて可変である場合、図 5 B に示すような光子計数回路 2 の二段アーキテクチャアプローチを使用することができる。

#### 【 0 0 9 1 】

図 5 B の光子計数回路 2 の二段アーキテクチャアプローチを参照して、信号整形回路 1 0 0 0 は、電荷感応増幅回路 2 0 0 0 を介して入力端子 I 1 0 に結合されている。電荷感応増幅回路 2 0 0 0 は、入力端子 I 1 0 における入力容量から信号整形回路 1 0 0 0 を切り離すバッファとして機能する。電荷感応増幅回路 2 0 0 0 は、演算相互コンダクタンス増幅器 2 1 0 0 、フィードバック抵抗器 2 2 0 0 、及びフィードバックコンデンサ 2 3 0 0 を含む。電荷感応増幅回路 2 0 0 0 及び信号整形回路 1 0 0 0 は、抵抗器 3 1 0 0 及びコンデンサ 3 2 0 0 の並列接続を含む結合ネットワーク 3 0 0 0 によって結合されている。10

#### 【 0 0 9 2 】

光子計数応用例のフロントエンド電子回路の信号整形回路においてアクティブ動的フィードバック回路 1 2 0 0 を使用する場合、速度及び計数率の点でバジェットを提供する小さな FWHM が達成されて、フィードバックコンデンサ 1 3 0 0 の容量を増加させ得る。コンデンサ 1 3 0 0 の容量を増加させることにより、低い弾道欠損を達成することができる。

#### 【 0 0 9 3 】

光子計数応用例においてフロントエンド電子回路 1 0 を使用することに加えて、図 3 A 、 3 B または 4 A ~ 4 C に示したようなアクティブ動的フィードバック回路 1 2 0 0 を含むフロントエンド電子回路 1 0 の提案された構成を、種々の X 線画像化応用例、たとえば、コンピュータ断層撮影、セキュリティ、食品または手荷物検査、材料及び電子機器の欠陥検査などに使用してもよい。20

#### 【 0 0 9 4 】

図 6 に、図 3 A 、 3 B 、または 4 A ~ 4 C に示すアプローチのうちの 1 つによるフロントエンド電子回路 1 0 を備えた光子計数回路 2 を、医療診断用のデバイス 1 内に設ける応用の例を示す。医療診断用のデバイス 1 は、たとえば、 X 線装置またはコンピュータ断層撮影スキャナとして構成してもよい。

#### 【 0 0 9 5 】

本明細書で開示したフロントエンド電子回路の実施形態を、読者にフロントエンド回路のデザインの新規な態様を知ってもらうことを目的として説明してきた。好ましい実施形態について図示して説明してきたが、開示した考え方の多くの修正、変更、均等物、及び置換が、特許請求の範囲から不必要に逸脱することなく当業者によってなされ得る。30

#### 【 0 0 9 6 】

詳細には、フロントエンド電子回路のデザインは、開示した実施形態に限定されず、説明した実施形態に含まれる特徴について可能な限り多くの代替案の例を示す。しかし、開示した考え方の任意の変更、均等物、及び置換が、本明細書に添付される特許請求の範囲内に含まれることが意図されている。

#### 【 0 0 9 7 】

別個の従属請求項に記載された特徴は、有利に組み合わせてもよい。また、特許請求の範囲において使用される引用符号は、特許請求の範囲を限定するものと解釈されることに限定されない。40

#### 【 0 0 9 8 】

さらに、本明細書で使用する場合、項目「含む ( c o m p r i s i n g ) 」は他の要素を除外するものではない。さらに、本明細書で使用する場合、冠詞「 a 」は、 1 つ以上の構成要素または要素を含むことが意図されており、 1 つだけを意味するものと解釈されることに限定されない。

#### 【 0 0 9 9 】

本特許出願は、ドイツ特許出願、出願第 1 0 2 0 2 1 1 1 3 6 2 . 8 号の優先権を主張する。この文献の開示内容は参照により本明細書に組み込まれている。

#### 【 符号の説明 】

10

20

30

40

50

## 【0100】

- 1 医療診断用デバイス

2 光子計数回路

10 フロントエンド電子回路

20 光子検出器

30 エネルギー弁別器

40 カウンタ

100 第1の入力トランジスタ

200 第2の入力トランジスタ

300 バッファ回路

310 トランジスタ

320 電流源

330 増幅器

400 電流源

500 基準信号生成回路

600 カレントミラー

1000 信号整形回路

1100 増幅回路

1200 アクティブ動的フィードバック回路

1300 コンデンサ

2000 電荷感應増幅回路

2100 演算相互コンダクタンス増幅器

2200 フィードバック抵抗器

2300 コンデンサ

3000 結合ネットワーク

3100 コンデンサ

3200 抵抗器

## 【図面】

【図1】

【図2A】

30

40

50

10

20

【図 2 B】

【図 3 A】

10

20

【図 3 B】

【図 4 A】

30

40

50

【図 4 B】

【図 4 C】

10

20

30

40

【図 5 A】

【図 5 B】

50

【図 6】

10

20

30

40

50

---

フロントページの続き

-セ 2

審査官 石田 昌敏

- (56)参考文献      特表2020-516878 (JP, A)

特開2020-010333 (JP, A)

米国特許出願公開第2011/0210235 (US, A1)

特開2015-012617 (JP, A)

特表2016-540208 (JP, A)

米国特許出願公開第2010/0329425 (US, A1)

米国特許出願公開第2010/0172467 (US, A1)

(58)調査した分野 (Int.Cl., DB名)

H 03 F     1 / 00 - 3 / 72

A 61 B     6 / 03

A 61 B     6 / 42

G 01 T     1 / 24

G 01 T     1 / 17