(19) 日本国特許庁(JP)

## (12) 公開特許公報(A)

(11) 特許出願公開番号

特開2004-120759

(P2004-120759A)

(43) 公開日 平成16年4月15日(2004.4.15)

(51) Int.CI.<sup>7</sup>H03J 3/28

H04B 1/18

H04N 5/44

F 1

H03J 3/28

H04B 1/18

H04N 5/44

テーマコード(参考)

5C025

5K058

5K062

審査請求 未請求 請求項の数 19 O L (全 21 頁)

|              |                              |          |                                                                         |

|--------------|------------------------------|----------|-------------------------------------------------------------------------|

| (21) 出願番号    | 特願2003-332604 (P2003-332604) | (71) 出願人 | 501263810<br>トムソン ライセンシング ソシエテ ア<br>ノニム<br>Thomson Licensing S.A.       |

| (22) 出願日     | 平成15年9月25日 (2003.9.25)       |          | フランス国、エフ-92100 プロ<br>ニュ ビヤンクール、ケ アルフォンス<br>ル ガロ、46番地                    |

| (31) 優先権主張番号 | 10/256,878                   | (74) 代理人 | 100087321<br>弁理士 渡辺 勝徳                                                  |

| (32) 優先日     | 平成14年9月27日 (2002.9.27)       | (74) 代理人 | 100115864<br>弁理士 木越 力                                                   |

| (33) 優先権主張国  | 米国(US)                       | (72) 発明者 | マイケル アンソニー プーゲル<br>アメリカ合衆国 インディアナ州 ノープ<br>ルズビル クリーク・ロード 20925<br>最終頁に続く |

(54) 【発明の名称】テレビジョン信号チューナ用の電子的整合システム

## (57) 【要約】

【課題】 テレビジョン信号チューナ用の電子的整合システムを提供すること。

【解決手段】 第1および第2のコントローラを利用して、信号処理装置のそれぞれの第1および第2の信号処理回路に向けたそれぞれの第1および第2の制御信号を生成する。第1および第2の信号処理回路は、それぞれの第1および第2の制御信号に応答するそれぞれの第1および第2の可同調要素を有する。第1の制御信号の偏移範囲は、第2の制御信号の偏移範囲よりも高い。

【選択図】

図6

**【特許請求の範囲】****【請求項 1】**

無線周波数（RF）信号源と、

信号出力点と、

前記無線周波数（RF）信号源と前記信号出力点との間に結合され、第1および第2の信号処理回路をそれぞれ備える信号処理装置とを含む同調装置であって、

前記第1および第2の信号処理回路が、それぞれの第1および第2の可同調要素を備え、同調装置は更に

前記第1の可同調要素に結合された、第1の制御信号を生成するための第1のコントローラと、

前記第2の可同調要素に結合された、第2の制御信号を生成するための第2のコントローラとを含み、

前記第1の制御信号の偏移範囲が前記第2の制御信号の偏移範囲よりも高い同調装置。

**【請求項 2】**

前記第2の信号処理回路が、第1の周波数帯域信号処理回路および第2の周波数帯域処理回路を含む、請求項1に記載の同調装置。

**【請求項 3】**

前記第1の信号処理回路が発振器回路を含み、前記第2の信号処理回路が無線周波数（RF）同調回路を備える、請求項1に記載の同調装置。

**【請求項 4】**

前記第1のコントローラが位相ロック・ループを含み、前記第2のコントローラがデジタル・アナログ変換器を含む、請求項1に記載の同調装置。

**【請求項 5】**

前記第1の可同調要素が、前記第1の制御信号に応答する第1および第2の局部発振器回路を含み、前記第2の可同調要素が、前記第2の制御信号に応答する第1および第2の可同調フィルタ要素を含む、請求項1に記載の同調装置。

**【請求項 6】**

前記第1の可同調フィルタ要素が、選択された周波数を前記第2の制御信号の前記偏移範囲に応答して通過させる第1の単同調の可同調フィルタおよび第1の複同調の可同調フィルタを含み、前記第2の可同調フィルタ要素が、選択された周波数を前記第2の制御信号の前記偏移範囲に応答して通過させる第2の単同調の可同調フィルタおよび第2の複同調の可同調フィルタを含む、請求項5に記載の同調装置。

**【請求項 7】**

前記第1および第2の単同調の可同調フィルタがそれぞれ、前記第2の制御信号の前記偏移範囲に応答するバラクタを含み、前記第1および第2の複同調の可同調フィルタがそれぞれ、前記第2の制御信号の前記偏移範囲にそれぞれ別々に応答する2つのバラクタを含む、請求項6に記載の同調装置。

**【請求項 8】**

無線周波数（RF）信号受信手段と、

信号出力手段と、

前記無線周波数（RF）信号受信手段と前記信号出力手段との間に結合された無線周波数（RF）信号処理手段とを含む同調装置であって、前記無線周波数（RF）信号処理手段が、無線周波数（RF）信号を処理するための第1の無線周波数（RF）信号処理手段および無線周波数（RF）信号を処理するための第2の無線周波数（RF）信号処理手段をそれぞれ備え、

前記第1の無線周波数（RF）信号処理手段が第1の無線周波数（RF）信号同調手段を備え、

前記第2の無線周波数（RF）信号処理手段が第2の無線周波数（RF）信号同調手段を備え、同調装置は更に、

前記第1の同調手段に結合された、第1の制御信号を生成するための第1の制御手段と

10

20

30

40

50

、前記第2の同調手段に結合された、第2の制御信号を生成するための第2の制御手段とを含み、

前記第2の制御手段の偏移範囲が前記第1の制御手段の偏移範囲よりも高い同調装置。

【請求項9】

前記無線周波数（RF）信号を処理するための第1の無線周波数（RF）信号処理手段が、第1の周波数帯域信号を処理する手段および第2の周波数帯域信号を処理する手段を含む、請求項8に記載の同調装置。

【請求項10】

前記第2の無線周波数（RF）信号処理手段がミクシング手段を含む、請求項8に記載の同調装置。 10

【請求項11】

前記第2の制御手段が位相ロック・ループ手段を含み、前記第1の制御手段がデジタル・アナログ変換器を含む、請求項8に記載の同調装置。

【請求項12】

前記第2の同調手段が、前記第2の制御信号に応答して局部発振器信号を生成する第1および第2の手段を含み、前記第1の同調手段が、無線周波数（RF）信号を可同調濾波する第1および第2の手段を含む、請求項8に記載の同調装置。

【請求項13】

前記無線周波数（RF）信号を可同調濾波する前記第1の手段が、選択された周波数を前記第1の制御信号の前記偏移範囲に応答して通過させる第1の単同調の可同調フィルタ手段および第1の複同調の可同調フィルタ手段を含み、前記無線周波数（RF）信号を可同調濾波する前記第2の手段が、選択された周波数を前記第1の制御信号の前記偏移範囲に応答して通過させる第2の単同調の可同調フィルタ手段および第2の複同調の可同調フィルタ手段を含む、請求項12に記載の同調装置。 20

【請求項14】

前記第1および第2の単同調の可同調フィルタ手段がそれぞれ、前記第1の制御信号の前記偏移範囲に応答するバラクタを含み、前記第1および第2の複同調の可同調フィルタ手段がそれぞれ、前記第1の制御信号の前記偏移範囲にそれぞれ別々に応答する2つのバラクタを含む、請求項13に記載の同調装置。 30

【請求項15】

テレビジョン信号受信機における同調方法であって、

複数の無線周波数（RF）信号を受信するステップと、

第1の偏移範囲を有する第1の制御信号を第1のコントローラにより生成するステップと、

前記複数の無線周波数（RF）信号に前記第1の制御信号に従って同調して、前記無線周波数（RF）信号のうちの選択された1つを得るステップと、

前記第1の偏移範囲よりも高い第2の偏移範囲を有する第2の制御信号を第2のコントローラにより生成するステップと、

前記第2の制御信号に従って局部発振器信号を生成するステップと、 40

前記局部発振器信号を前記無線周波数（RF）信号のうちの前記選択された1つとミクシングして、IF信号を生成するステップとを含む方法。

【請求項16】

第1の偏移範囲を有する第1の制御信号を第1のコントローラにより生成する前記ステップが、デジタル・アナログ変換器を含む第1のコントローラにより、第1の偏移範囲を有する第1の制御信号を生成するステップを含む、請求項15に記載の方法。

【請求項17】

第2の偏移範囲を有する第2の制御信号を第2のコントローラにより生成する前記ステップが、位相ロック・ループを含む第2のコントローラにより、第2の偏移範囲を有する第2の制御信号を生成するステップを含む、請求項15に記載の方法。 50

**【請求項 18】**

前記複数の無線周波数（R F）信号に前記第1の制御信号に従って同調するステップが、単同調の可同調フィルタと複同調の可同調フィルタの第1と第2の対のうちの一方を介して、前記第1の制御信号に従って前記無線周波数（R F）信号のうちの1つを選択するステップを含む、請求項15に記載の方法。

**【請求項 19】**

単同調の可同調フィルタと複同調の可同調フィルタの第1と第2の対のうちの一方を介して、前記第1の制御信号に従って前記無線周波数（R F）信号のうちの1つを選択するステップが、バラクタ・ダイオードを介した単同調の可同調フィルタとデュアル・バラクタ・ダイオードを介した複同調の可同調フィルタの第1と第2の対のうちの一方を介して、前記第1の制御信号に従って前記無線周波数（R F）信号のうちの1つを選択するステップを含む、請求項18に記載の方法。 10

**【発明の詳細な説明】****【技術分野】****【0001】**

本発明は、テレビジョン信号チューナーに関し、より詳細には、テレビジョン信号チューナ用の電子的整合（electronic alignment）システムに関する。

**【背景技術】****【0002】**

すべてではないにしても大半のテレビジョン信号受信機は、特定のテレビジョン信号（チャンネル）を選択するためのチューナを備えている。選択されたチャンネルに基づいて電圧信号を利用する、テレビジョン信号チューナ用の電子的整合システムが開発されてきた。本質的に、同調させようとする選択されたチャンネルが、チャンネル選択信号を同調電圧コントローラに供給する。 20

**【0003】**

電子的整合は、これまで常に、テレビジョン信号チューナの無線周波数同調回路（R F tuning circuitry）とテレビジョン信号チューナの局部発振器回路（local oscillator circuitry）とが同じ電圧コントローラ／電圧源上で稼動する必要があった。

**【0004】**

しかし、電子的整合システムは、無線周波数同調回路と局部発振器回路の両方を稼動させるために、高電圧バラクタ・ダイオード（varactor diode）を利用して、電圧コントローラにより発生される高電圧を受け取って利用する。 30

**【発明の開示】****【発明が解決しようとする課題】****【0005】**

従って、少なくとも回路の一部では低電圧バラクタ・ダイオードを利用する、テレビジョン信号受信機用の電子的整合システムを有することが望ましい。

**【0006】**

更に、独立して制御される無線周波数同調回路と局部発振器回路とを有する電子的整合システムを有することが望ましい。 40

**【課題を解決するための手段】****【0007】**

本発明によれば、同調装置が提供される。この同調装置は、無線周波数（R F）信号受信手段と、信号出力手段と、無線周波数（R F）信号受信手段と信号出力手段との間に結合された無線周波数（R F）信号処理手段とを含み、無線周波数（R F）信号処理手段は、第1の無線周波数（R F）信号処理手段および第2の無線周波数（R F）信号処理手段をそれぞれ含んでいる。第1および第2の無線周波数（R F）信号処理手段は、それぞれの第1および第2の無線周波数（R F）信号同調手段を含んでいる。この同調装置は更に、第1の同調手段に結合された、第1の制御信号を生成するための第1の制御手段と、第 50

2の同調手段に結合された、第2の制御信号を生成するための第2の制御手段とを含んでいる。第1の制御手段の偏移範囲は、第2の制御手段の偏移範囲よりも高い。

#### 【0008】

各図において、対応する参照符号は対応する部分を示す。

#### 【発明を実施するための最良の形態】

#### 【0009】

一形態として、特にテレビジョン信号チューナ用である同調装置が、第1および第2のコントローラを利用して、信号処理装置のそれぞれの第1および第2の信号処理回路に向けたそれぞれの第1および第2の制御信号を生成する。第1および第2の信号処理回路は、それぞれの第1および第2の制御信号に応答するそれぞれの第1および第2の可同調要素を有する。第1の制御信号の偏移範囲 (deviation range) は、第2の制御信号の偏移範囲 (deviation range) よりも高い。一形態として、第1および第2の信号処理回路は、異なる周波数帯域 (frequency band) に応答する。第1および第2のコントローラは、第1および第2の電圧コントローラとすることができる、一形態として、第1および第2の電圧コントローラは、同調コントローラおよびデジタル・アナログ変換器とすることができます。第1および第2の信号処理回路は、無線周波数同調回路、および無線周波数同調回路のための局部発振器回路とすることができます。無線周波数回路は、第1の可同調要素の一部として、低電圧デジタル・アナログ変換器から提供される第1の電圧範囲 (voltage range) (偏移範囲) にわたって動作する低電圧バラクタを利用することができる。局部発振器回路は、第2の可同調要素の一部として、第1の電圧範囲よりも高く、位相ロック・ループから提供される第2の電圧範囲 (voltage range) (偏移範囲) にわたって動作する、より高い電圧のバラクタを利用することができる。

#### 【0010】

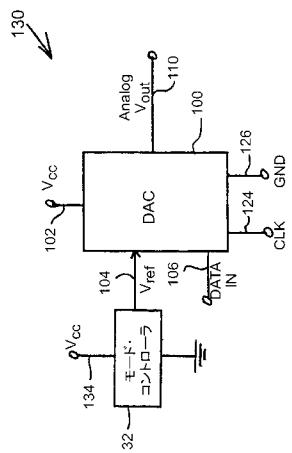

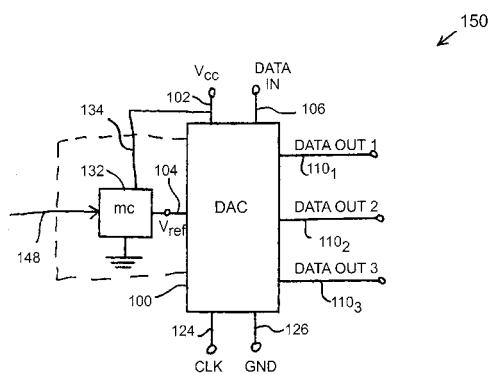

ここで図面、特に図1を参照すると、本発明の一態様による、130で全体を示すデジタル・アナログ変換器システムの簡単化ブロック図表現が示されている。デジタル・アナログ変換器システム130は、デジタル・アナログ変換器 (D A C : Digital to Analog Converter) 100およびモード・コントローラ (m c : mode controller) 132を備えている。デジタル・アナログ変換器 (D A C ) 100は、任意のタイプのデジタル・アナログ変換器 (D A C ) を表す。通常は、デジタル・アナログ変換器 (D A C ) 100は、集積回路 (I C ) であるが、必ずしも I C である必要はない。更に、モード・コントローラ 132は、D A C 100と別個に示してあるが、D A C 100と統合してもよい。従って、デジタル・アナログ変換器 (D A C ) システム130すべてを、I C の一部とすることもできる。

#### 【0011】

デジタル・アナログ変換器 (D A C ) 100は、D A C 100の動作を可能にするのに適した動作電圧または電圧供給を受け取るように動作する電圧供給入力 (V<sub>c c</sub>) 102を有する。D A C 100の電圧供給入力 102に供給される供給電圧は、I C の性質により異なることがある。ただし、通常は、このような電圧は5ボルトと12ボルトの何れかである。当然、D A C 100 (またはD A C システム130が統合型 I C 型式の場合は、D A C システム130) は、異なることがある。

#### 【0012】

また、デジタル・アナログ変換器 (D A C ) 100は、基準電圧 (V<sub>r e f</sub>) を受け取るように動作する電圧基準入力 (V<sub>r e f</sub>) 104も有する。基準電圧 (V<sub>r e f</sub>) は、D A C 100が出力することになる最大電圧を設定する。データ入力 (DATA IN) 106が設けられており、これは、Nビット・デジタル・ワード (データ) を受け取るように動作する。Nビット・デジタル・ワードは、特定のアナログ電圧に変換される。異なるNビット・ワードはそれぞれ、異なるアナログ電圧を供給する。D A C 100は、所定のNビット・デジタル・ワードのセットを受け取るように構成されている。例えば、D A C 100は、3ビット・デジタル・アナログ変換器とすることができます、このこ

10

20

30

40

50

とは、D A C 1 0 0 が、0 0 0 ~ 1 1 1 の 3 ビット・ディジタル・ワード（即ち、 $N = 3$ ）だけしか受け付けないことを意味する。入力データは、直列に入力することができ、その場合には、単一のデータ入力 1 0 6 がある。あるいは、入力データは、並列で入力することもできる。並列入力の場合、各データ・ビットにつき別個のライン（線）があることになる。例えば、3 ビット・ディジタル・アナログ変換器（3 ビット・ワードまたはデータを受け付ける）は、3 つの別々のデータ入力 1 0 6 を有することになる。一般に、ビット数が、D A C の分解能（r e s o l u t i o n）を決定する。通常の分解能は、 $1 / (2^N - 1)$  と表すことができる。

#### 【 0 0 1 3 】

また、ディジタル・アナログ変換器（D A C）1 0 0 は、電圧基準入力 1 0 4 を介して 10

入力された（最大値としての）基準電圧と、データ入力 1 0 6 を介した入力データ（N ビット・ディジタル・ワード）とに依存するアナログ出力電圧を供給するアナログ出力 1 1 0 也有する。D A C 1 0 0 は、アナログ出力電圧をアナログ出力（A n a l o g V\_o\_u\_t）1 1 0 上に供給すると、このアナログ出力電圧は、ディジタル入力ワードが 0 から  $2^N - 1$  まで変化するのに伴って、直線的に 0 から最大基準電圧まで変化する。D A C 1 0 0 は、複式（m u l t i p l y i n g）D A C とすることもでき、その場合、アナログ出力の大きさは、何らかのアナログ入力にも比例する。D A C 1 0 0 は、クロック信号を受け取るように動作するクロック入力（C L K）1 2 4 也有する。また、D A C 1 0 0 は、大地接続（G N D）1 2 6 を介して大地に接続または結合されている。

#### 【 0 0 1 4 】

本発明の一態様によれば、モード・コントローラ 1 3 2 は、電圧基準入力 1 0 4 と基準電圧（V<sub>c c</sub>）との間に接続されている。モード・コントローラ 1 3 2 は、基準電圧入力（V<sub>c c</sub>）1 3 4 を有し、図ではこの基準電圧入力 1 3 4 が、基準電圧（V<sub>c c</sub>）に接続されている。モード・コントローラ 1 3 2 は、2 つの状態またはモードで動作する。一方の状態では、モード・コントローラ 1 3 2 は、基準電圧（V<sub>c c</sub>）に対応する最大出力電圧までの第 1 の分解能で、D A C 1 0 0 が動作できるようにする。第 2 の状態では、モード・コントローラは、最大出力電圧を低減し（即ち、V<sub>c c</sub> の何割かに）、D A C 1 0 0 の分解能を増加させる。モード・コントローラ 1 3 2 もまた大地に結合されている。

#### 【 0 0 1 5 】

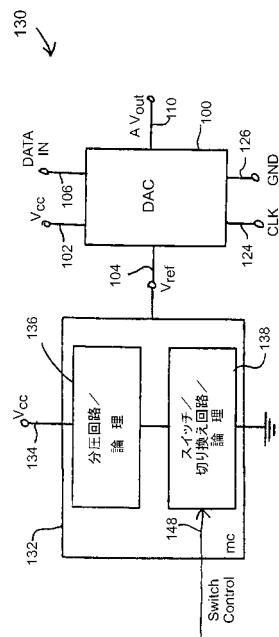

次に、図 2 を参照すると、モード・コントローラ 1 3 2 の様々な要素をブロック形式で 30

示したディジタル・アナログ変換器（D A C）システム 1 3 0 が、示されている。具体的には、一形態でモード・コントローラ 1 3 2 は、分圧回路／論理（V o l t a g e D i v i s i o n C i r c u i t r y / L o g i c）1 3 6 と、スイッチ／切り換え回路／論理（S w i t c h / S w i t c h i n g C i r c u i t r y / L o g i c）1 3 8 を備えている。分圧回路／論理 1 3 6 は、電圧基準入力（V<sub>c c</sub>）1 3 4 を介して電圧基準源（V<sub>c c</sub>）に接続されている。スイッチ／切り換え回路／論理 1 3 8 は、大地に接続され、2 つの状態またはモードで動作する。第 1 の状態またはモードは開回路状態であり、第 2 の状態またはモードは閉回路状態である。

#### 【 0 0 1 6 】

分圧回路／論理（l o g i c）1 3 6 は、スイッチ／切り換え回路／論理 1 3 8 と共に 40

動作し、それにより、スイッチ／切り換え回路／論理 1 3 8 が第 1 の状態（開回路）にあるときは、分圧回路／論理 1 3 6 は、第 1 の分解能で、アナログ電圧出力（A n a l o g V\_o\_u\_t）1 1 0 におけるアナログ出力電圧として基準電圧入力（V<sub>r e f</sub>）1 0 4 に供給される最大基準電圧（V<sub>c c</sub>）の 1 0 0 % を供給するように動作する。更に、分圧回路／論理 1 3 6 は、スイッチ／切り換え回路／論理 1 3 8 と共に動作し、それにより、スイッチ／切り換え回路／論理 1 3 8 が第 2 の状態（閉回路）にあるときは、分圧回路／論理 1 3 6 は、第 1 の分解能よりも大きい第 2 の分解能で、アナログ電圧出力 1 1 0 におけるアナログ出力電圧として基準電圧入力 1 0 4 に供給される最大基準電圧（V<sub>c c</sub>）の何割かを供給するように動作する。

#### 【 0 0 1 7 】

10

20

30

40

50

分圧回路 / 論理 136 が、デジタル・アナログ変換器 (D A C) 100 に（具体的には、電圧基準入力 ( $V_{ref}$ ) 104 に）供給する最大基準電圧 ( $V_{cc}$ ) の割合は、分圧回路 / 論理 136 の回路により決定される。第 1 の分解能は以下の式で計算される。

$$1 / (2^N - 1)$$

第 2 の分解能は、以下の式で計算される。

$$1 / (2^{N+1} - 1)$$

この 2 つの式から、分解能が 2 倍になることがわかる。実のところ、第 2 の分解能は、D A C 100 に対する入力データ・ワードの所定のビット・サイズに応じて、実際には第 1 の分解能の 2 倍よりもわずかに大きい。例えば、D A C 100 が 3 ビット D A C の場合、第 1 の分解能は 1 / 7 であり（即ち、0 から最大基準電圧まで 7 段階ある）、従って、第 2 の分解能は 1 / 15 である（即ち、0 から最大基準電圧の何割かまで 15 段階ある）。後述するように、最大アナログ出力電圧として供給される基準電圧（最大基準電圧）の割合は、回路構成要素の値により決定される。これは、制御点 (control point) または切り換え点 (switchover point) と呼ぶことができる。本発明を 1 つの制御点に関して述べると、多くの制御点があってもよく、あるいは絶えず変化する制御点があってもよい。

10

20

30

30

40

50

### 【0018】

このデジタル・アナログ変換器 (D A C) システムは、効果的に増加した第 2 の分解能を提供することに留意されたい。従って、効果的な、一部をなす、および / または部分的な分解能という用語を適用して、分解能の増加を示すことができる。従って、この D A C システムは、D A C、D A C 構造、または D A C システムの、部分的なまたは何割かの範囲にわたって効果的な分解能増加をもたらす。別の言い方をすれば、本発明は、全動作範囲にわたって D A C、D A C 構造、または D A C システムに対して半ビットの分解能を提供し、あるいは何割かまたは部分的な動作範囲にわたって 1 ビットの分解能を提供することに似ている。

### 【0019】

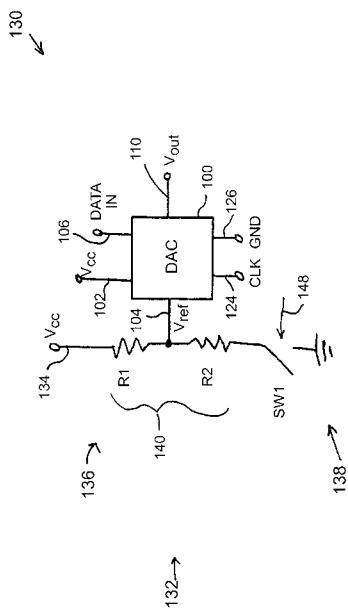

図 3 を参照すると、モード・コントローラ 132 の例示的な回路図を表したもののが示されている。具体的には、分圧回路 / 論理 136 が、分圧器 140 として示されている。例示的な一実施例では、分圧器 140 は、第 1 の抵抗器 R 1 および第 2 の抵抗器 R 2 からなる。第 1 の抵抗器 R 1 は、基準電圧 ( $V_{cc}$ ) に結合されている。基準電圧 ( $V_{cc}$ ) は、例えば、10 ボルトとすることができます。第 2 の抵抗器 R 2 は、切り換え回路 138 に結合されており、切り換え回路 138 は、ここではスイッチ SW 1 を含んでいる。スイッチ SW 1 は、スイッチ制御 (switch control) ライン 148 上に供給されるスイッチ制御信号により制御される。スイッチ SW 1 は、大地に接続されている。スイッチ制御信号は、スイッチ SW 1 を開閉する。

### 【0020】

分圧器 140 は、デジタル・アナログ変換器 (D A C) 100 の基準電圧 ( $V_{ref}$ ) 入力 104 にも接続されている。具体的には、D A C 100 の基準電圧 ( $V_{ref}$ ) 入力 104 は、第 1 の抵抗器 R 1 と第 2 の抵抗器 R 2 との間に接続されている。動作を説明すると、図 3 に示すようにスイッチ SW 1 が開いた位置（開回路）にある場合は、D A C 100 の基準電圧 ( $V_{ref}$ ) 入力 104 に供給される電圧は、第 1 の抵抗器 R 1 の両端の電圧である。第 1 の抵抗器 R 1 の両端の電圧は、基準電圧供給 ( $V_{cc}$ ) であり、従って、基準電圧 ( $V_{ref}$ ) は、 $V_{cc}$  と等しい。スイッチ SW 1 が閉じた位置（閉回路）にある場合は、D A C 100 の基準電圧 ( $V_{ref}$ ) 入力 104 に供給される電圧は、第 1 の抵抗器 R 1 および第 2 の抵抗器 R 2 にわたって分割された電圧であり、これは、以下の式により与えられる。

$$R_1 / (R_1 + R_2)$$

従って、D A C 100 に供給される基準電圧は、抵抗器 R 1 および R 2 の値に依存する。このため、スイッチ SW 1 が閉じているとき、最大アナログ出力電圧は R 1 および R 2 の値に依存する。

## 【0021】

$R_1 = R_2$  のとき、分母の項  $R_1 + R_2$  は、 $R_1 + R_1$  に変えることができ、これは即ち  $2R_1$  である。従って、式  $R_1 / (R_1 + R_2)$  は、 $R_1 / 2R_1$  と書き換えることができ、これを簡単化すると  $1/2$  になる。このため、 $R_1 = R_2$  のとき、DAC100 に供給される最大基準電圧、即ち制御点（および最大アナログ出力電圧）は、基準電圧供給  $V_{cc}$  の  $1/2$ 、即ち  $50\%$  である。一般に、 $R_1 < R_2$  のときは、制御点は  $1/2V_{cc}$  または  $50\%V_{cc}$  よりも小さい（<）。 $R_1 > R_2$  のときは、制御点は  $1/2V_{cc}$  または  $50\%V_{cc}$  よりも大きい（>）。

## 【0022】

通常、抵抗器  $R_1$  および  $R_2$  の値（オーム）は、固定値だが、望むなら、両方とも可変としてもよく、一方を、固定とし他方を可変としてもよい。このようにすれば、DAC100 に供給される基準電圧の制御点は、抵抗器  $R_1$  および抵抗器  $R_2$  が固定値の場合に固定されるのとは異なり、制御することができる。従って、DAC100 に供給される最大基準電圧は、0 をちょうど過ぎた値から基準電圧供給の  $100\%$  までとすることができる。

## 【0023】

図4を参照すると、150で全体を示す、他の実施例のデジタル・アナログ変換器（DAC）システムが示されている。この実施例で、モード・コントローラ（mc）132 が場合により DAC100 と統合されるのが破線で示されている。ただし、モード・コントローラ132は、DAC100と統合してもしなくてもよい。DACシステム150は、前述の DACシステム130 と同様にして動作すると、例外として、DAC100は、第1のデータ・アウト1アナログ電圧出力（DATA OUT1）110<sub>1</sub>、第2のデータ・アウト2アナログ電圧出力（DATA OUT2）110<sub>2</sub>、および第3のデータ・アウト3アナログ電圧出力（DATA OUT3）110<sub>3</sub>を有する。各アナログ電圧出力110<sub>1</sub>、110<sub>2</sub>、110<sub>3</sub>は、デジタル入力ワードに対して個別に同様のアナログ電圧出力を供給する。更に、DACシステム150は、電圧  $V_{cc}$  を DAC100 のための基準電圧および動作電圧に利用する。

## 【0024】

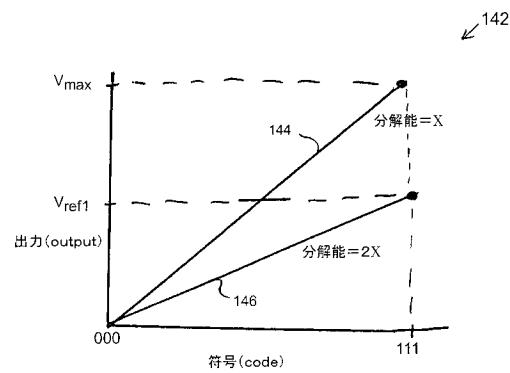

図5は、3ビット・デジタル・アナログ変換器（DAC）を有するこのDACシステムのグラフであって、3ビット・デジタル入力データに応じた出力電圧を示すグラフ142を提供する。出力電圧は、最小値0ボルトから最大値  $V_{max}$  までの範囲にわたる。 $V_{max}$  は、任意の電圧とすることができますが、デジタル入力ワードが、000から111に変化するのに伴ってモード・コントローラ132に供給される基準電圧に対応する。また、 $V_{max}$  は、スイッチSW1が開いた状態のときに DAC100 に供給される基準電圧にも対応する。グラフ142で、電圧  $V_{ref1}$  は、スイッチSW1が閉じており分圧器140が機能しているときの、制御点、即ち、最大基準電圧の割合（percentage）に対応する。

## 【0025】

グラフ142に示す例では、線144は、スイッチSW1が開いた位置にあるときのアナログ出力電圧を表す。デジタル入力ワードが000の場合、アナログ電圧出力は0ボルトである。デジタル入力ワードが111へと進むにつれて、アナログ出力電圧は最大値  $V_{max}$ （即ち、基準電圧の  $100\%$ ）まで増加する。線144の分解能（resolution）は、「X」で表すことができる。

## 【0026】

線146は、スイッチSW1が閉じた位置にあるときのアナログ出力電圧を表す。デジタル入力ワードが000の場合、アナログ電圧出力は0ボルトである。デジタル入力ワードが111へと進むにつれて、アナログ出力電圧は最大値  $V_{ref1}$ （即ち、式  $R_1 / (R_1 + R_2)$  に従った、基準電圧の何割か）まで増加する。線146の分解能は、「2X」と表すことができる。線146の傾斜は、線144の傾斜よりも小さいことがわかり、このことは、0ボルトと最大アナログ出力電圧  $V_{max}$  との間よりも、0ボルトと最

10

20

30

40

50

大アナログ出力電圧  $V_{ref_1}$  との間の方が、段階またはディジタル入力ワード（分解能）ごとの電圧増分が少ないことを示す。

### 【0027】

従って、このD A Cシステムは、NビットD A Cの分解能の切り換えを提供する。具体的には、このD A Cシステムは、既存のNビットD A Cを利用するかまたはNビット用D A C構造を提供しながら、N+1ビットの分解能をD A Cの電圧範囲の何割かにわたって実現できるようにする。3ビットの例を用いると、R2Rはしご形回路網D A Cが、端点を含めた8個の離散はしご点（discrete ladder point）を形成する（離散はしご点のように働く）。4ビット分解能のD A Cが必要な場合、はしご点の数を16個にすることが必要になる。本発明では、3ビットD A C構造を使用して、特定のまたは所定の範囲にわたって4ビット性能を実現することができる。10

### 【0028】

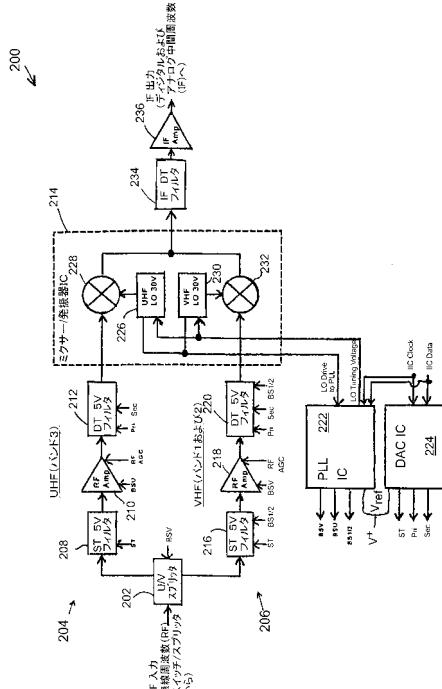

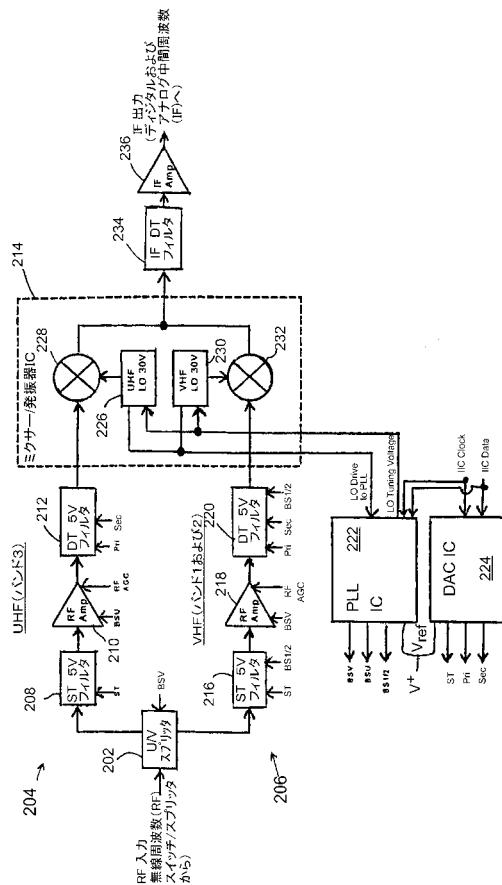

次に図6を参照すると、200で全体を示す、テレビジョン信号受信機（テレビジョン信号）チューナ用の例示的な電子的整合システムのブロック図が示されている。このシステム中で、前述のディジタル・アナログ変換器（D A C）システムを使用することができる。ただし、本明細書で述べるD A Cシステムは、必ずしも電子的整合システム200中で使用する必要はない。電子的整合システム200は、無線周波数（R F）テレビジョン信号（R F信号または入力）を無線周波数（R F）テレビジョン信号源から受信し、中間周波数（I F）出力を供給するように動作する。具体的には、電子的整合システム200は、V H F（より具体的には2つのV H F帯域、即ち、帯域1および帯域2）やU H Fテレビジョン信号など、無線周波数（R F）テレビジョン信号の幾つかの帯域を受信し、選択されたテレビジョン・チャンネルに従って、中間周波数（I F）テレビジョン・チャンネル信号を供給するように動作する。20

### 【0029】

無線周波数（R F）信号は、無線周波数（R F）入力スイッチまたはスプリッタ（s p l i t t e r）を介して供給される有線テレビジョンやアンテナなどの無線周波数（R F）信号源から受信される。受信された無線周波数（R F）信号は、V H F帯域からU H F帯域を分離するように動作するU/V（U H F / V H F）スプリッタ202に入力される。U/Vスプリッタ202は、選択されたチャンネルがV H F帯域テレビジョン信号のとき、制御信号B S V（B S V : Band Select V H F。帯域選択V H F）を受け取る。制御信号B S Vは、位相ロック・ループ（P L L : Phase Lock Loop）222により生成され、ここでは、P L L 222は、P L L I Cの形式で示されている。制御信号B S Vは、チャンネル選択信号に応答してP L L 222により生成される電圧である。30

### 【0030】

電子的整合システム200は、U H F処理部204、V H F処理部206、ミクサー/発振器部214、P L L 222、ディジタル・アナログ変換器（D A C）224を有する。U H F処理部204は、チャンネル選択に応答して特定のU H Fチャンネル（特定のテレビジョン信号）に同調するように動作する。V H F処理部206は、チャンネル選択に応答して、特定のV H F帯域（ここでは、2つのV H F帯域のうちの一方）内の特定のV H Fチャンネル（特定のテレビジョン信号）に同調するように動作する。40

### 【0031】

U H F処理部204は、U/Vスプリッタ202の出力を受け取るようにU/Vスプリッタ202に接続された単同調（S T : Single Tuned）フィルタ208を備えている。具体的には、U H F信号は、単同調フィルタ208によりU/Vスプリッタ202から受け取られる。本発明の一態様によれば、単同調フィルタ208は、0~5ボルトの範囲にわたって動作する。具体的には、単同調フィルタ208は、0~5ボルトの連続的なアナログ電圧にわたって動作する。S Tで示す0~5ボルト信号をD A C 224から受け取る。D A C 224は、チャンネル選択信号に応答して、0~5ボルト信号（即ち、連続的なアナログ0~5ボルト信号）S Tを生成する。電圧信号S Tは、選択されたチ50

チャンネルに単同調フィルタ208が同調するようとする。

【0032】

単同調フィルタ208の出力は、無線周波数(RF)増幅器(amp)210に供給される。無線周波数(RF)増幅器210は、テレビジョン信号受信機により生成される無線周波数(RF)自動利得制御(AGC)信号に従って、単同調フィルタ208からの無線周波数(RF)UHF信号を増幅するよう動作する。無線周波数(RF)増幅器210はまた、PLL222により生成され供給されるUHF帯域選択信号(BSU: Band Select UHF)も受け取るよう動作する。UHF帯域選択信号BSUは、チャンネル選択信号に応答して位相ロック・ループ(PLL)により生成される。本質的に、帯域選択信号BSUは、無線周波数(RF)増幅器210のためのオン/オフ信号である。

10

【0033】

無線周波数(RF)増幅器210の出力は、複同調(DT: Double Tuned)フィルタ212に供給される。本発明の一態様によれば、複同調フィルタ212は、0~5ボルトの範囲にわたって動作する。具体的には、複同調フィルタ212は、0~5ボルトの連続的なアナログ電圧にわたって動作する。PRI(Pri)で示す0~5ボルト信号を、DAC224から受け取る。DAC224は、チャンネル選択信号に応答して、0~5ボルト信号(即ち、連続的なアナログ0~5ボルト信号)PRIを生成する。PRI電圧信号は、選択されたチャンネルに複同調フィルタ212の第1の部分が同調するようする。SEC(Sec)で示す0~5ボルト信号も、DAC224から受け取る。DAC224は、チャンネル選択信号に応答して、0~5ボルト信号(即ち、連続的なアナログ0~5ボルト信号)SECを生成する。SEC電圧信号は、選択されたチャンネルに複同調フィルタ212の第2の部分が同調するようする。

20

【0034】

複同調フィルタ212の出力は、ICの形式で示すミクサー/発振器(mixer/oscillator)214に供給される。ミクサー部と発振器部は、別々としてもよいが、図示の例では結合されている。具体的には、複同調フィルタ212の出力は、ミクサー228に供給される。UHF局部発振器(LO: Local Oscillator)226の出力が、ミクサー228に接続されている。UHF局部発信機(LO)226は、局部発振器(LO)同調電圧信号をPLL222から受け取り、同調された局部発振器信号を生成するよう動作する。LO同調電圧信号は、チャンネル選択信号に応答してPLLにより生成される。LO同調電圧信号は、0~30ボルトのアナログ電圧信号である。また、UHF局部発振器(LO)226は、LO駆動信号の形式でPLL222にファードバックを与える。

30

【0035】

UHFミクサー228は、UHF局部発振器(LO)226からの同調されたUHF局部発振器信号を、複同調フィルタ212の出力信号(選択されたチャンネル)と合成またはミクシング(mixing)する。ミクサー228の出力は、複同調中間周波数(IF)フィルタ234に供給される。複同調中間周波数(IF)フィルタ234は、その出力を中間周波数(IF)増幅器(amp)236に供給する。中間周波数(IF)増幅器236からの增幅された中間周波数(IF)信号(選択されたテレビジョン・チャンネル)は、次いで、テレビジョン信号受信機または他の構成要素の、様々なデジタルおよびアナログ中間周波数(IF)構成要素(図示せず)に中間周波(IF)出力として供給される。

40

【0036】

VHF処理部206は、U/Vスプリッタ202の出力を受け取るようにU/Vスプリッタ202に接続された单(一)同調(ST)フィルタ216を備えている。具体的には、VHF信号は、単同調フィルタ216によりU/Vスプリッタ202から受け取られる。本発明の一態様によれば、単同調フィルタ216は、0~5ボルトの範囲にわたって動作する。具体的には、単同調フィルタ216は、0~5ボルトの連続的なアナログ電圧に

50

わたって動作する。S Tで示す0～5ボルト信号をD A C 2 2 4から受け取る。D A C 2 2 4は、チャンネル選択信号に応答して、0～5ボルト信号（即ち、連続的なアナログ0～5ボルト信号）S Tを生成する。電圧信号S Tは、選択されたチャンネルに単同調フィルタ2 1 6が同調するようとする。

#### 【0037】

更に、単同調フィルタ2 1 6は、P L L 2 2 2により生成されたP L L 2 2 2からの帯域選択（B a n d S e l e c t）信号（B S 1 / 2）を受け取るように動作する。帯域選択信号（B S 1 / 2）は、2つのV H F 帯域のうちの一方を選択する。具体的には、帯域選択信号（B S 1 / 2）は、チャンネル選択信号から得られるオン／オフ電圧信号である。

10

#### 【0038】

単同調フィルタ2 1 6の出力は、無線周波数（R F）増幅器（a m p）2 1 8に供給される。無線周波数（R F）増幅器2 1 8は、テレビジョン信号受信機により生成される無線周波数（R F）自動利得制御（A G C）信号に従って、単同調フィルタ2 1 6からの無線周波数（R F）V H F 信号を増幅するよう動作する。また、無線周波数（R F）増幅器2 1 8は、P L L 2 2 2により生成され供給されるV H F 帯域選択信号（B S V）も受け取るように動作する。V H F 帯域選択信号B S Vは、チャンネル選択信号に応答してP L Lにより生成される。本質的に、帯域選択信号B S Vは、無線周波数（R F）増幅器2 1 8のためのオン／オフ信号である。

#### 【0039】

無線周波数（R F）増幅器2 1 8の出力は、複同調（D T）フィルタ2 2 0に供給される。本発明の一態様によれば、複同調フィルタ2 2 0は、0～5ボルトの範囲にわたって動作する。具体的には、複同調フィルタ2 2 0は、0～5ボルトの連続的なアナログ電圧にわたって動作する。P R I（P r i）で示す0～5ボルト信号をD A C 2 2 4から受け取る。D A C 2 2 4は、チャンネル選択信号に応答して、0～5ボルト信号（即ち、連続的なアナログ0～5ボルト信号）P R Iを生成する。P R I電圧信号は、選択されたチャンネルに複同調フィルタ2 2 0の第1の部分が同調するようする。S E C（S e c）で示す0～5ボルト信号もD A C 2 2 4から受け取る。D A C 2 2 4は、チャンネル選択信号に応答して、0～5ボルト信号（即ち、連続的なアナログ0～5ボルト信号）S E Cを生成する。S E C電圧信号は、選択されたチャンネルに複同調フィルタ2 2 0の第2の部分が同調するようする。

20

#### 【0040】

更に、複同調フィルタ2 2 0は、P L L 2 2 2により生成されたP L L 2 2 2からの帯域選択信号（B S 1 / 2）を受け取るように動作する。帯域選択信号（B S 1 / 2）は、2つのV H F 帯域のうちの一方を選択する。具体的には、帯域選択信号（B S 1 / 2）は、チャンネル選択信号から得られるオン／オフ電圧信号である。帯域選択信号（B S 1 / 2）は、単同調フィルタ2 1 6に供給されるものと同じである。

30

#### 【0041】

複同調フィルタ2 2 0の出力は、I Cの形式で示すミクサー／発振器2 1 4に供給される。ミクサー部と発振器部は別々としてもよいが、図では合成されている。具体的には、複同調フィルタ2 2 0の出力は、ミクサー2 3 2に供給される。V H F 局部発振器（L O）2 3 0の出力が、ミクサー2 3 2に接続されている。V H F 局部発振器（L O）2 3 0は、局部発振器（L O）同調電圧信号をP L L 2 2 2から受け取り、同調された局部発振器信号を生成するよう動作する。L O 同調電圧信号は、チャンネル選択信号に応答してP L Lにより生成される。L O 同調電圧信号は、0～3 0 ボルトのアナログ電圧信号である。また、V H F 局部発振器（L O）2 3 0は、L O 駆動信号の形式でP L L 2 2 2にフィードバックを供給する。

40

#### 【0042】

V H F ミクサー2 3 2は、V H F 局部発振器（L O）2 3 0からの同調されたV H F 局部発振器信号を、複同調フィルタ2 2 0の出力信号（選択されたチャンネル）と合成また

50

はミクシングする。ミクサー 232 の出力は、複同調中間周波数（I F）フィルタ 234 に供給される。複同調 I F フィルタ 234 は、その出力を中間周波数（I F）増幅器（amp）236 に供給する。中間周波数（I F）増幅器 236 からの増幅された中間周波数（I F）信号（選択されたテレビジョン・チャンネル）は、次いでテレビジョン信号受信機または他の構成要素の、様々なデジタルおよびアナログ中間周波数（I F）構成要素（図示せず）に、中間周波（I F）出力として供給される。

#### 【0043】

チャンネル選択信号は、必ずしもそうとは限らないが通常、電子的整合システム 200 を有するテレビジョン信号受信機によりユーザー入力に応答して生成される。チャンネル選択信号は、D A C 224 および P L L 222 に供給される。チャンネル選択信号を提供するための他の方式も考えられるが、図示の電子的整合システム 200 では、I<sup>2</sup>C（または I I C）構成 / プロトコルを利用する。従って、図では、I<sup>2</sup>C クロック・ラインおよび I<sup>2</sup>C データ・ラインが D A C 224 および P L L 222 に接続されている。P L L 222 も D A C 224 も両方とも、0 から最大電圧までの範囲で連続的に変動するアナログ電圧信号を生成し、最大電圧は、D A C 224 の場合は 5 ボルトであり、P L L 222 の場合は 30 ボルトである。

#### 【0044】

更に、本明細書に開示する電子的整合システムまたは電子チューナは、無線周波数（R F）セクションでは、5 ボルト・バラクタを使用し L O（局部発振器）セクションでは、30 ボルト・バラクタを使用するものとして述べているが、他の電圧のバラクタを使用することもできる点に留意されたい。本発明の原理によれば、無線周波数（R F）セクションのための電圧供給（従って、バラクタ）と局部発振器（L O）セクションのための電圧供給（従って、バラクタ）とが単に異なっている。このような差は、無線周波数（R F）セクションのための電圧供給およびバラクタ（即ち、バラクタ電圧容量）が、局部発振器（L O）セクションのための電圧供給およびバラクタ（即ち、バラクタ電圧容量）よりも低いこととして表れることが好ましい。従って、例えば、無線周波数（R F）セクションは、12 ボルトの供給 / バラクタを使用し、局部発振器（L O）セクションは、33 ボルトの供給 / バラクタを使用することもできる。更に、供給電圧および / またはバラクタ電圧は、相関関係にあっても無くてもよい。

#### 【0045】

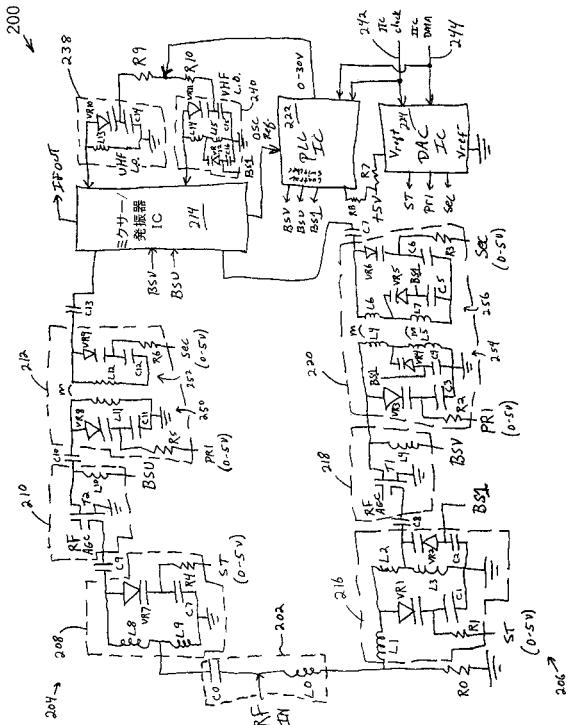

図 7 を参照すると、図 6 の電子的整合システム 200 のブロック図に関する例示的な回路図が示されている。図 7 の回路は、図 6 に関連して述べたように動作することを理解されたい。従って、回路 200 の幾つかの部分だけについて詳細に述べる。最初に、スプリッタ 202 により、具体的にはコンデンサ C 0 およびインダクタ L 0 により、無線周波数入力（R F IN）が分割される。U H F 部が、コンデンサ C 0 を介して分岐し、V H F 部が、インダクタ L 0 を介して分岐する。抵抗器 R 0 が、電荷増強保護 / 除去、および / または避雷を提供する。抵抗器 R 0 は、インダクタ L 0 および大地に結合されている。

#### 【0046】

先に示したように、U H F セクション 204 は、バラクタ電圧制御される単同調フィルタ 208 を有する。単同調フィルタ 208 は、直列のインダクタ L 8 および L 9 を備えており、これらは低電圧（即ち、0 ~ 5 ボルト）バラクタ（バラクタ・ダイオード）V R 7 およびコンデンサ C 7 と並列である。直列のインダクタ L 8 および L 9 と、それらと並列のバラクタ V R 7 およびコンデンサ C 7 は、大地に接続されている。同調電圧信号 S T が、抵抗器 R 4 を介して、バラクタ V R 7 とコンデンサ C 7 との間のノード（node：接点）に供給される。単同調フィルタ 208 は、バラクタ V R 7 に印加される電圧に基づいて電気特性が変化する。このようにして、単同調フィルタ 208 は、入力電圧信号 S T に基づいて特定の U H F チャンネルに同調することができる。

#### 【0047】

単同調フィルタ 208 は、コンデンサ C 9 を介して無線周波数（R F）増幅器 210 に結合されている。増幅器 210 は、デュアル・ゲート N チャネル金属酸化物半導体（M O

10

20

30

40

50

S ) 電界効果トランジスタ ( F E T ) T 2 を備えている。トランジスタ T 2 の一方のゲートにはコンデンサ C 9 が結合され、トランジスタ T 2 の他方のゲートは無線周波数 ( R F ) A G C 信号を受け取る。トランジスタ T 2 のソースは、大地に接続されている。トランジスタ T 2 のドレインには、インダクタ L 1 0 が結合されている。インダクタ L 1 0 は、U H F 帯域選択 ( B S U ) 信号を適時に受け取るために P L L 2 2 2 に結合されている。B S U 信号を加えるあるいは加えないことにより、増幅器が機能し、あるいは機能せず、その結果、信号を通すための伝導または信号を通さないための非伝導がもたらされる。無線周波数 ( R F ) 増幅器 2 1 0 は、コンデンサ C 1 0 を介して複同調フィルタ 2 1 2 に結合されている。

## 【 0 0 4 8 】

複同調フィルタ 2 1 2 は、第 1 の段 ( f i r s t s t a g e ) 2 5 0 を備えており、この第 1 の段 2 5 0 は、第 2 の段 ( s e c o n d s t a g e ) 2 5 2 に対し、それぞれのインダクタ L 1 1 および L 1 2 を介して相互伝導関係にある。第 1 の段 2 5 0 は、低電圧 ( 0 ~ 5 ボルト ) バラクタ V R 8 を備えている。このバラクタ V R 8 は、一方の端でコンデンサ C 1 0 に結合され、他方の端でコンデンサ C 1 1 に結合され、それによりバラクタ V R 8 とコンデンサ C 1 1 とは直列である。直列のバラクタ V R 8 およびコンデンサ C 1 1 は、インダクタ L 1 1 と並列である。同調電圧信号 P R I が、抵抗器 R 5 を介して、バラクタ V R 8 とコンデンサ C 1 1 との間のノード ( 接点 ) に供給される。第 1 の段 2 5 0 は、バラクタ V R 8 に印加される電圧に基づいて電気特性が変化する。

## 【 0 0 4 9 】

複同調フィルタ 2 1 2 は第 2 の段 2 5 2 を備えており、この第 2 の段 2 5 2 は、第 1 の段 2 5 0 に対し、それぞれのインダクタ L 1 1 および L 1 2 を介して相互伝導関係にある。第 2 の段 2 5 2 は、低電圧 ( 0 ~ 5 ボルト ) バラクタ V R 9 を備えている。このバラクタ V R 9 は、一方の端でインダクタ L 1 2 に結合され、他方の端でコンデンサ C 1 2 に結合され、それにより、バラクタ V R 9 とコンデンサ C 1 2 とは直列であり、バラクタ V R 9 およびコンデンサ C 1 2 はインダクタ L 1 2 と並列である。同調電圧信号 S E C が、抵抗器 R 6 を介して、バラクタ V R 9 とコンデンサ C 1 2 との間のノードに供給される。第 2 の段 2 5 2 は、バラクタ V R 9 に印加される電圧に基づいて電気特性が変化する。このようにして、複同調フィルタ 2 1 2 は、入力電圧信号 P R I および S E C に基づいて特定の U H F チャンネルに同調することができる。複同調フィルタ 2 1 2 の出力は、コンデンサ C 1 3 を介してミクサー / 発振器 I C 2 1 4 に供給される。

## 【 0 0 5 0 】

先に示したように、V H F セクション 2 0 6 は、バラクタ電圧制御される単同調フィルタ 2 1 6 を有する。単同調フィルタ 2 1 6 はインダクタ L 1 を備えている。低電圧 ( 即ち 0 ~ 5 ボルト ) バラクタ ( バラクタ・ダイオード ) V R 1 が、一方の端でインダクタ L 1 に結合され、他方の端でコンデンサ C 1 に結合され、それによりバラクタ V R 1 とコンデンサ C 1 は直列である。直列のバラクタ V R 1 およびコンデンサ C 1 は、直列のインダクタ L 2 および L 3 と並列である。コンデンサ C 1 およびインダクタ L 3 は、大地に接続されている。同調電圧信号 S T が、抵抗器 R 1 を介して、バラクタ V R 1 とコンデンサ C 1 との間のノード ( 接点 ) に供給される。単同調フィルタ 2 1 6 は、バラクタ V R 1 に印加される電圧に基づいて電気特性が変化する。このようにして、単同調フィルタ 2 1 6 は、入力電圧信号 S T に基づいて特定の V H F チャンネルに同調することができる。

## 【 0 0 5 1 】

単同調フィルタ 2 1 6 は更に、帯域選択信号 B S 1 に応答して、単同調フィルタ 2 1 6 の帯域同調を変更する。単同調フィルタ 2 1 6 は更に、コンデンサ C 2 と直列の低電圧 ( 0 ~ 5 ボルト ) バラクタ V R 2 も備えている。信号 B S 1 は、バラクタ V R 2 とコンデンサ C 2 との間に加えられる。直列のバラクタ V R 2 およびコンデンサ C 2 は、インダクタ L 3 と並列に配置されている。

## 【 0 0 5 2 】

単同調フィルタ 2 1 6 は、コンデンサ C 8 を介して無線周波数 ( R F ) 増幅器 2 1 8 に

10

20

30

40

50

結合されている。増幅器 218 は、デュアル・ゲートNチャネル金属酸化物半導体(MOS)電界効果トランジスタ(FET)T1を備えている。トランジスタT1の一方のゲートにはコンデンサC8が結合され、トランジスタT1の他方のゲートは無線周波数(RF)AGC信号を受け取る。トランジスタT1のソースは大地に接続されている。トランジスタT1のドレインには、インダクタL4が結合されている。インダクタL4は、VHF帯域選択(BSV)信号を適時に受け取るためにPLL222に結合されている。BSV信号を加えるまたは加えないことにより増幅器が機能しまだ機能せず、その結果、信号を通すための伝導または信号を通さないための非伝導がもたらされる。無線周波数(RF)増幅器218は、複同調フィルタ220に結合されている。

## 【0053】

10

複同調フィルタ220は第1の段254を備えており、この第1の段254は、第2の段256に対し、それぞれの2組のインダクタL4およびL6、L5およびL7を介して相互伝導関係にある。第1の段254は、低電圧(0~5ボルト)バラクタVR3を備えている。このバラクタVR3は、一方の端で増幅器218に結合され、他方の端でコンデンサC3に結合され、それによりバラクタVR3とコンデンサC3とは直列である。直列のバラクタVR3およびコンデンサC3は、直列のインダクタL4およびL5と並列である。同調電圧信号PRIが、抵抗器R2を介して、バラクタVR3とコンデンサC3との間のノードに供給される。第1の段254は、バラクタVR3に印加される電圧に基づいて電気特性が変化する。

## 【0054】

20

複同調フィルタ220の第1の段254は更に、帯域選択信号BS1に応答して、複同調フィルタ220の第1の段254の帯域同調を変更する。第1の段254は更に、コンデンサC4と直列の低電圧(0~5ボルト)バラクタVR4も備えている。信号BS1は、バラクタVR4とコンデンサC4との間に加えられる。直列のバラクタVR4およびコンデンサC4は、インダクタL5と並列に配置されている。

## 【0055】

30

複同調フィルタ220は第2の段256を備えており、この第2の段256は、第1の段254に対し、それぞれのインダクタの対L4およびL6、L5およびL7を介して相互伝導関係にある。第2の段256は、低電圧(0~5ボルト)バラクタVR6を備えている。このバラクタVR6は、一方の端でインダクタL6に結合され、他方の端でコンデンサC6に結合され、それにより、バラクタVR6とコンデンサC6とは直列であり、バラクタVR6およびコンデンサC6はインダクタL6およびL7と並列である。同調電圧信号SECが、抵抗器R3を介して、バラクタVR6とコンデンサC6との間のノードに供給される。第2の段256は、バラクタVR6に印加される電圧に基づいて電気特性が変化する。

## 【0056】

40

複同調フィルタ220の第2の段256は更に、帯域選択信号BS1に応答して、複同調フィルタ220の第2の段256の帯域同調を変更する。第2の段256は更に、コンデンサC5と直列の低電圧(0~5ボルト)バラクタVR5も備えている。信号BS1は、バラクタVR5とコンデンサC5との間に加えられる。直列のバラクタVR5およびコンデンサC5は、インダクタL7と並列に配置されている。このようにして、複同調フィルタ220は、入力電圧信号PRIおよびSEC、並びに帯域選択信号BS1に基づいて、特定の帯域の特定のVHFチャンネルに同調することができる。複同調フィルタ220の出力は、コンデンサC7を介してミクサー/発振器IC214に供給される。

## 【0057】

50

ミクサー/発振器214は、BSVとBSUの何れかの制御信号を受け取って、どちらの局部発振器を利用するかを選択する。更に、PLL222がミクサー発振器214に結合されており、それにより、チャンネル選択信号から得られた同調電圧がUHF局部発振器(LO)同調セクション238およびVHF局部発振器(LO)同調セクション240に供給される。UHF局部発振器(LO)同調セクション238は、チャンネル選択に基

づいて同調をもたらすように動作する。VHF 局部発振器 (LO) 同調セクション 240 は、チャンネル選択に基づいて同調をもたらすように動作する。

#### 【0058】

UHF 局部発振器 (LO) 同調セクション 238 は、コンデンサ C14 と直列する高電圧 (0 ~ 30 ボルト) バラクタ VR10 を備えている。直列のバラクタ VR10 およびコンデンサ C14 は、インダクタ L13 と並列に配置されている。PLL222 からの 0 ~ 30 ボルト同調信号は、抵抗器 R9 を介して、バラクタ VR10 とコンデンサ C14 との間のノードに供給される。これにより、UHF 同調のための同調された信号がミクサー / 発振器 214 に供給される。

#### 【0059】

VHF 局部発振器 (LO) 同調セクション 240 は、コンデンサ C15 と直列する高電圧 (0 ~ 30 ボルト) バラクタ VR11 を備えている。直列のバラクタ VR11 およびコンデンサ C15 は、インダクタの対 L14 および L15 と並列に配置されている。PLL222 からの 0 ~ 30 ボルト同調信号は、抵抗器 R10 を介して、バラクタ VR11 とコンデンサ C15 との間のノード (接点) に供給される。インダクタの対 L14 と L15 の間には、帯域選択信号 BS1 に応答して動作する帯域選択回路がタップされている。帯域選択信号が、バラクタ VR12 とコンデンサ C16 との間に供給される。これにより、VHF 同調のための同調された信号がミクサー / 発振器 214 に供給される。

#### 【0060】

本明細書に示すように、上述したこの DAC システムは、バラクタ・ダイオード (バラクタ) の同調特性により、テレビジョン信号受信機 (テレビジョン信号) チューナ用のこの例示的な電子的整合システム中で使用することが望ましい。具体的には、バラクタ・ダイオードの同調特性は、下側の電圧範囲でより高速なキャパシタンス (および周波数) の変化を有するものである。その結果、このより高速な変化により、必要な分解能 (即ち、より大きい分解能) が設定される。しかし、上側の電圧範囲では、変化はずっと遅く、分解能はより低くなる。より高い分解能の DAC (即ち、より多くのビット) を使用することもできるが、より高い分解能の DAC はより高価である。更に、その場合、より高い分解能の DAC は、より高い電圧では分解能 (および同調帯域内の周波数) を浪費することになる。従って、この切り換え式分解能の DAC では、より低い分解能の DAC を使用して、必要な範囲内だけでより高い分解能の利点を得ることができる。

#### 【0061】

好ましい設計を有するものとして本発明を述べたが、本発明は、本開示の趣旨および範囲の内で更に変更することもできる。従って、本明細書は、本発明の一般原理を用いた本発明のどんな変形、使用、適応も包含するものである。更に、本明細書は、本発明が関係しており特許請求の範囲に含まれるなら、当技術分野における周知のまたは慣例の実施に含まれる本開示からの逸脱も包含するものである。

#### 【0062】

以下に他の実施例を例示する。

##### (1) 無線周波数 (RF) 信号源と、

信号出力点と、

前記無線周波数 (RF) 信号源と前記信号出力点との間に結合され、第 1 および第 2 の信号処理回路をそれぞれ備える信号処理装置とを含む同調装置であって、

前記第 1 および第 2 の信号処理回路が、それぞれの第 1 および第 2 の可同調要素を備え、同調装置は更に

前記第 1 の可同調要素に結合された、第 1 の制御信号を生成するための第 1 のコントローラと、

前記第 2 の可同調要素に結合された、第 2 の制御信号を生成するための第 2 のコントローラとを含み、

前記第 1 の制御信号の偏移範囲が前記第 2 の制御信号の偏移範囲よりも高い同調装置。

##### (2) 前記第 2 の信号処理回路が、第 1 の周波数帯域信号処理回路および第 2 の周波数帯

10

20

30

40

50

域処理回路を含む、(1)に記載の同調装置。

(3) 前記第1の信号処理回路が発振器回路を含み、前記第2の信号処理回路が無線周波数(RF)同調回路を備える、(1)に記載の同調装置。

(4) 前記第1のコントローラが位相ロック・ループを含み、前記第2のコントローラがデジタル・アナログ変換器を含む、(1)に記載の同調装置。

(5) 前記第1の可同調要素が、前記第1の制御信号に応答する第1および第2の局部発振器回路を含み、前記第2の可同調要素が、前記第2の制御信号に応答する第1および第2の可同調フィルタ要素を含む、(1)に記載の同調装置。

(6) 前記第1の可同調フィルタ要素が、選択された周波数を前記第2の制御信号の前記偏移範囲に応答して通過させる第1の単同調の可同調フィルタおよび第1の複同調の可同調フィルタを含み、前記第2の可同調フィルタ要素が、選択された周波数を前記第2の制御信号の前記偏移範囲に応答して通過させる第2の単同調の可同調フィルタおよび第2の複同調の可同調フィルタを含む、(5)に記載の同調装置。 10

(7) 前記第1および第2の単同調の可同調フィルタがそれぞれ、前記第2の制御信号の前記偏移範囲に応答するバラクタを含み、前記第1および第2の複同調の可同調フィルタがそれぞれ、前記第2の制御信号の前記偏移範囲にそれぞれ別々に応答する2つのバラクタを含む、(6)に記載の同調装置。

(8) 無線周波数(RF)信号受信手段と、

信号出力手段と、

前記無線周波数(RF)信号受信手段と前記信号出力手段との間に結合された無線周波数(RF)信号処理手段とを含む同調装置であって、前記無線周波数(RF)信号処理手段が、無線周波数(RF)信号を処理するための第1の無線周波数(RF)信号処理手段および無線周波数(RF)信号を処理するための第2の無線周波数(RF)信号処理手段をそれぞれ備え、 20

前記第1の無線周波数(RF)信号処理手段が第1の無線周波数(RF)信号同調手段を備え、

前記第2の無線周波数(RF)信号処理手段が第2の無線周波数(RF)信号同調手段を備え、同調装置は更に、

前記第1の同調手段に結合された、第1の制御信号を生成するための第1の制御手段と、 30

前記第2の同調手段に結合された、第2の制御信号を生成するための第2の制御手段とを含み、

前記第2の制御手段の偏移範囲が前記第1の制御手段の偏移範囲よりも高い同調装置。

(9) 前記無線周波数(RF)信号を処理するための第1の無線周波数(RF)信号処理手段が、第1の周波数帯域信号を処理する手段および第2の周波数帯域信号を処理する手段を含む、(8)に記載の同調装置。

(10) 前記第2の無線周波数(RF)信号処理手段がミクシング手段を含む、(8)に記載の同調装置。

(11) 前記第2の制御手段が位相ロック・ループ手段を含み、前記第1の制御手段がデジタル・アナログ変換器を含む、(8)に記載の同調装置。 40

(12) 前記第2の同調手段が、前記第2の制御信号に応答して局部発振器信号を生成する第1および第2の手段を含み、前記第1の同調手段が、無線周波数(RF)信号を可同調濾波する第1および第2の手段を含む、(8)に記載の同調装置。

(13) 前記無線周波数(RF)信号を可同調濾波する前記第1の手段が、選択された周波数を前記第1の制御信号の前記偏移範囲に応答して通過させる第1の単同調の可同調フィルタ手段および第1の複同調の可同調フィルタ手段を含み、前記無線周波数(RF)信号を可同調濾波する前記第2の手段が、選択された周波数を前記第1の制御信号の前記偏移範囲に応答して通過させる第2の単同調の可同調フィルタ手段および第2の複同調の可同調フィルタ手段を含む、(12)に記載の同調装置。

(14) 前記第1および第2の単同調の可同調フィルタ手段がそれぞれ、前記第1の制御 50

信号の前記偏移範囲に応答するバラクタを含み、前記第1および第2の複同調の可同調フィルタ手段がそれぞれ、前記第1の制御信号の前記偏移範囲にそれぞれ別々に応答する2つのバラクタを含む、(13)に記載の同調装置。

(15) テレビジョン信号受信機における同調方法であって、

複数の無線周波数(RF)信号を受信するステップと、

第1の偏移範囲を有する第1の制御信号を第1のコントローラにより生成するステップと、

前記複数の無線周波数(RF)信号に前記第1の制御信号に従って同調して、前記無線周波数(RF)信号のうちの選択された1つを得るステップと、

前記第1の偏移範囲よりも高い第2の偏移範囲を有する第2の制御信号を第2のコントローラにより生成するステップと、

前記第2の制御信号に従って局部発振器信号を生成するステップと、

前記局部発振器信号を前記無線周波数(RF)信号のうちの前記選択された1つとミクシングして、IF信号を生成するステップとを含む方法。

(16) 第1の偏移範囲を有する第1の制御信号を第1のコントローラにより生成する前記ステップが、デジタル・アナログ変換器を含む第1のコントローラにより、第1の偏移範囲を有する第1の制御信号を生成するステップを含む、(15)に記載の方法。

(17) 第2の偏移範囲を有する第2の制御信号を第2のコントローラにより生成する前記ステップが、位相ロック・ループを含む第2のコントローラにより、第2の偏移範囲を有する第2の制御信号を生成するステップを含む、(15)に記載の方法。

(18) 前記複数の無線周波数(RF)信号に前記第1の制御信号に従って同調するステップが、単同調の可同調フィルタと複同調の可同調フィルタの第1と第2の対のうちの一方を介して、前記第1の制御信号に従って前記無線周波数(RF)信号のうちの1つを選択するステップを含む、(15)に記載の方法。

(19) 単同調の可同調フィルタと複同調の可同調フィルタの第1と第2の対のうちの一方を介して、前記第1の制御信号に従って前記無線周波数(RF)信号のうちの1つを選択するステップが、バラクタ・ダイオードを介した単同調の可同調フィルタとデュアル・バラクタ・ダイオードを介した複同調の可同調フィルタの第1と第2の対のうちの一方を介して、前記第1の制御信号に従って前記無線周波数(RF)信号のうちの1つを選択するステップを含む、(18)に記載の方法。

【図面の簡単な説明】

【0063】

【図1】本発明の原理によるデジタル・アナログ変換器システムを簡単化したブロック図である。

【図2】図1のデジタル・アナログ変換器システムのブロック図であって、特にモード・コントローラのブロック図を示す図である。

【図3】図1のデジタル・アナログ変換器システムを表す図であって、モード・コントローラの回路図を示す図である。

【図4】デジタル・アナログ変換器システムの他の実施例を示す図である。

【図5】モード・コントローラを備えるかまたは備えない3ビット・デジタル・アナログ変換器の出力電圧とそれに対する入力コードのグラフである。

【図6】デジタル・アナログ変換器システムを使用することのできる、テレビジョン信号チューナ用の電子的整合システムのブロック図である。

【図7】図6の電子的整合システムの例示的な回路図である。

【符号の説明】

【0064】

100 デジタル・アナログ変換器(DAC)

102 電圧供給入力

104 電圧基準入力

106 データ入力

10

20

30

40

50

|                 |                           |    |

|-----------------|---------------------------|----|

| 1 1 0           | アナログ出力                    |    |

| 1 2 4           | クロック入力                    |    |

| 1 2 6           | 大地接続                      |    |

| 1 3 0           | デジタル・アナログ変換器システム          |    |

| 1 3 2           | モード・コントローラ                |    |

| 1 3 4           | 基準電圧入力                    |    |

| 1 3 6           | 分圧回路 / 論理 (ロジック)          |    |

| 1 3 8           | スイッチ / 切り替え回路 / 論理        |    |

| 1 4 0           | 分圧器                       |    |

| 1 4 8           | スイッチ制御ライン                 | 10 |

| 1 5 0           | D A C システム                |    |

| 2 0 0           | 電子的整合システム                 |    |

| 2 0 2           | U / V スプリッタ               |    |

| 2 0 4           | U H F 処理部                 |    |

| 2 0 6           | V H F 処理部                 |    |

| 2 0 8           | 単同調 (S T) フィルタ            |    |

| 2 1 0           | 無線周波数 (R F) 増幅器           |    |

| 2 1 2           | 複同調 (D T) フィルタ            |    |

| 2 1 4           | ミクサー / 発振器部               |    |

| 2 1 6           | 単同調 (S T) フィルタ            | 20 |

| 2 1 8           | 無線周波数 (R F) 増幅器           |    |

| 2 2 0           | 複同調 (D T) フィルタ            |    |

| 2 2 2           | 位相ロック・ループ (P L L)         |    |

| 2 2 4           | デジタル・アナログ変換器 (D A C)      |    |

| 2 2 6           | U H F 局部発振器 (L O)         |    |

| 2 2 8           | ミクサー                      |    |

| 2 3 0           | V H F 局部発振器 (L O)         |    |

| 2 3 2           | ミクサー                      |    |

| 2 3 4           | 複同調 I F フィルタ              |    |

| 2 3 6           | 中間周波数 (I F) 増幅器           | 30 |

| 2 3 8           | U H F 局部発振器 (L O) 同調セクション |    |

| 2 4 0           | V H F 局部発振器 (L O) 同調セクション |    |

| 2 5 0           | 複同調フィルタの第1の段              |    |

| 2 5 2           | 複同調フィルタの第2の段              |    |

| 2 5 4           | 複同調フィルタの第1の段              |    |

| 2 5 6           | 複同調フィルタの第2の段              |    |

| C 0 ~ C 1 6     | コンデンサ                     |    |

| L 0 ~ L 1 5     | インダクタ                     |    |

| R 0 ~ R 1 0     | 抵抗器                       |    |

| V R 1 ~ V R 1 2 | バラクタ                      | 40 |

| T 1             | トランジスタ                    |    |

| T 2             | トランジスタ                    |    |

| B S V           | V H F 帯域選択信号              |    |

| B S U           | U H F 帯域選択信号              |    |

| P R I           | 同調電圧信号                    |    |

| S E C           | 同調電圧信号                    |    |

| S T             | 同調電圧信号                    |    |

| B S 1           | 帯域選択信号                    |    |

| B S 1 / 2       | 帯域選択信号                    |    |

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

---

フロントページの続き

F ターム(参考) 5C025 AA25

5K058 BA05 CA01 CA02 CA03 CA04 CA05 DA02 DA14 EA17 GA03

GA04 GA05 GA11 GA13

5K062 AA07 AA08 AB01 AC02 BC01 BC10 BD02