(19)日本国特許庁(JP)

## (12)特許公報(B2)

(11)特許番号

特許第7348890号

(P7348890)

(45)発行日 令和5年9月21日(2023.9.21)

(24)登録日 令和5年9月12日(2023.9.12)

(51)国際特許分類

H 01 G 4/30 (2006.01)

F I

|        |      |         |

|--------|------|---------|

| H 01 G | 4/30 | 2 0 1 D |

| H 01 G | 4/30 | 3 1 1 D |

| H 01 G | 4/30 | 5 1 6   |

| H 01 G | 4/30 | 5 1 7   |

請求項の数 10 (全14頁)

(21)出願番号 特願2020-182105(P2020-182105)

(22)出願日 令和2年10月30日(2020.10.30)

(65)公開番号 特開2022-72584(P2022-72584A)

(43)公開日 令和4年5月17日(2022.5.17)

審査請求日 令和5年1月20日(2023.1.20)

早期審査対象出願

(73)特許権者 000204284

太陽誘電株式会社

東京都中央区京橋二丁目 7番 19号

(74)代理人 100087480

弁理士 片山 修平

山田 一樹

東京都中央区京橋二丁目 7番 19号 太

陽誘電株式会社内

水野 高太郎

東京都中央区京橋二丁目 7番 19号 太

陽誘電株式会社内

(72)発明者 加藤 洋一

東京都中央区京橋二丁目 7番 19号 太

陽誘電株式会社内

(72)発明者 増田 秀俊

最終頁に続く

(54)【発明の名称】 セラミック電子部品およびその製造方法

## (57)【特許請求の範囲】

## 【請求項1】

セラミックを主分とする複数の誘電体層と、複数の内部電極層と、が積層された積層チップを備え、

前記内部電極層は、Niと、Snと、Auと、を含み、

前記誘電体層の、隣接する前記内部電極層に接する界面部分において、Au濃度よりもSn濃度が高いことを特徴とするセラミック電子部品。

## 【請求項2】

前記内部電極層において、Niに対する、Sn含有量と、Au含有量との合計は、0.01at%以上、95at%以下であることを特徴とする請求項1に記載のセラミック電子部品。

## 【請求項3】

前記内部電極層において、Niに対する、Sn含有量と、Au含有量との合計は、0.2at%以上、10at%以下であることを特徴とする請求項2に記載のセラミック電子部品。

## 【請求項4】

前記内部電極層において、Au含有量は、Sn含有量より少ないことを特徴とする請求項1から請求項3のいずれか一項に記載のセラミック電子部品。

## 【請求項5】

前記内部電極層において、厚さ方向の中心部よりも、前記誘電体層との界面近傍におい

て、Snの濃度が高いことを特徴とする請求項1から請求項3のいずれか一項に記載のセラミック電子部品。

【請求項6】

前記内部電極層において、積層方向の中心部よりも、前記誘電体層との界面近傍において、Auの濃度が高いことを特徴とする請求項1から請求項3のいずれか一項に記載のセラミック電子部品。

【請求項7】

前記誘電体層の厚さ方向において、前記界面部分から内部に向かって、前記Au濃度および前記Sn濃度が徐々に低下するような濃度勾配が形成されていることを特徴とする請求項1から請求項6のいずれか一項に記載のセラミック電子部品。

10

【請求項8】

前記内部電極層において、Niに対するSn含有量と、Au含有量との合計は、0.2at%以上、10at%以下であり、Au含有量は、Sn含有量より少ないことを特徴とする請求項1から請求項7のいずれか一項に記載のセラミック電子部品。

【請求項9】

誘電体グリーンシート上に、Niと、Snと、Auと、を含む内部電極パターンを形成することによって積層単位を形成する工程と、

複数の前記積層単位を積層することによって積層体を形成する工程と、

前記積層体を焼成する工程と、を含み、

前記内部電極パターンは、Ni-Sn-Auの混合物のペーストであるか、NiとSnとAuの個別ターゲットを用いて同時にスパッタしたものであることを特徴とするセラミック電子部品の製造方法。

20

【請求項10】

前記積層単位を形成する工程は、前記誘電体グリーンシートに、真空成膜プロセスによって前記内部電極パターンを成膜する工程であることを特徴とする請求項9に記載のセラミック電子部品の製造方法。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、セラミック電子部品およびその製造方法に関する。

30

【背景技術】

【0002】

積層セラミックコンデンサなどのセラミック電子部品の内部電極には、Ni(ニッケル)が用いられている。焼成工程においては、Niの酸化を防ぐために、雰囲気を還元雰囲気とすることが多い。しかしながら、焼成工程の雰囲気を還元雰囲気にすると、誘電体層に酸素欠陥が生成し、信頼性が劣化するおそれがある。そこで、Niの内部電極にSnを含ませることで、コンデンサの信頼性を向上させる技術が開示されている(例えば、特許文献1,2参照)。

【先行技術文献】

【特許文献】

【0003】

【文献】国際公開第14/024538号

特表2005-505695号公報

40

【発明の概要】

【発明が解決しようとする課題】

【0004】

しかしながら、Niを内部電極に用いると、セラミック電子部品の寿命特性に改善の余地がある。

【0005】

本発明は、上記課題に鑑みなされたものであり、寿命特性を向上させることができるセ

50

ラミック電子部品およびその製造方法を提供することを目的とする。

【課題を解決するための手段】

【0006】

本発明に係るセラミック電子部品は、セラミックを主成分とする複数の誘電体層と、複数の内部電極層と、が積層された積層チップを備え、前記内部電極層は、Niと、Snと、Auと、を含むことを特徴とする。

【0007】

上記セラミック電子部品における前記内部電極層において、Niに対する、Sn含有量と、Au含有量との合計は、0.01at%以上、95at%以下であってもよい。

【0008】

上記セラミック電子部品における前記内部電極層において、Niに対する、Sn含有量と、Au含有量との合計は、0.2at%以上、10at%以下であってもよい。

【0009】

上記セラミック電子部品における前記内部電極層において、Au含有量は、Sn含有量より少なくてもよい。

【0010】

上記セラミック電子部品における前記内部電極層において、厚さ方向の中心部よりも、前記誘電体層との界面近傍において、Snの濃度が高くてよい。

【0011】

上記セラミック電子部品における前記内部電極層において、積層方向の中心部よりも、前記誘電体層との界面近傍において、Auの濃度が高くてよい。

【0012】

本発明に係るセラミック電子部品の製造方法は、誘電体グリーンシート上に、Niと、Snと、Auと、を含む内部電極パターンを形成することによって積層単位を形成する工程と、複数の前記積層単位を積層することによって積層体を形成する工程と、前記積層体を焼成する工程と、を含むことを特徴とする。

【0013】

上記セラミック電子部品の製造方法において、前記積層単位を形成する工程は、前記誘電体グリーンシートに、真空成膜プロセスによって前記内部電極パターンを成膜する工程であってもよい。

【発明の効果】

【0014】

本発明によれば、寿命特性を向上させることができるセラミック電子部品およびその製造方法を提供することができる。

【図面の簡単な説明】

【0015】

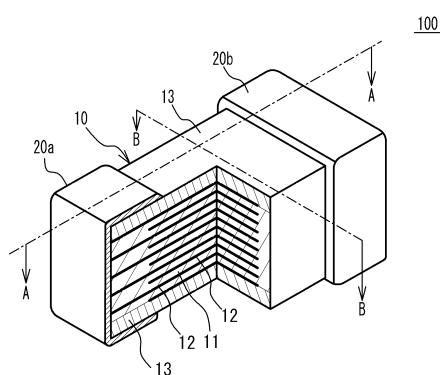

【図1】積層セラミックコンデンサの部分断面斜視図である。

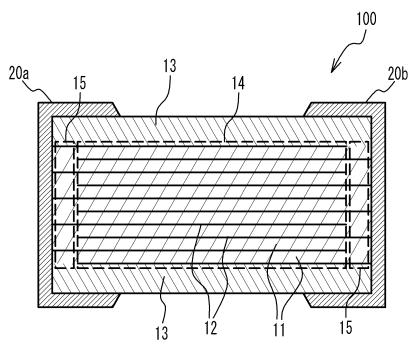

【図2】図1のA-A線断面図である。

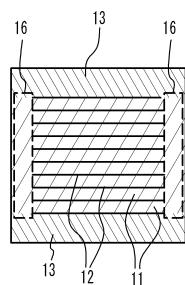

【図3】図1のB-B線断面図である。

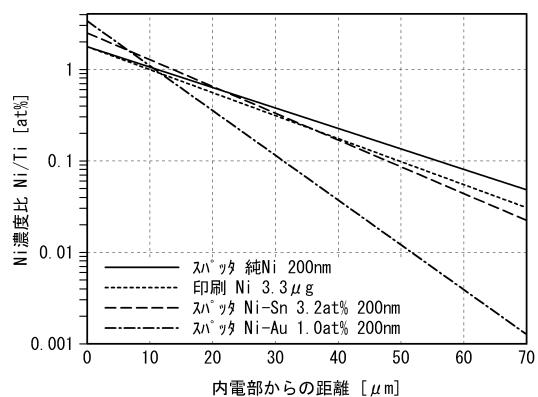

【図4】内部電極層への添加元素がNiの拡散に及ぼす影響を示す図である。

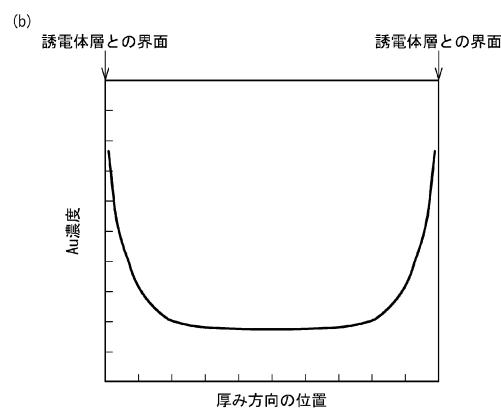

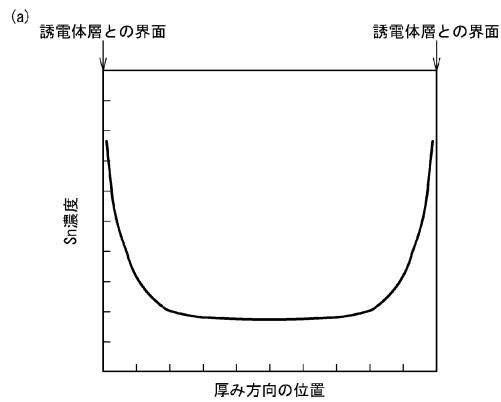

【図5】(a)は内部電極層におけるSn濃度を例示する図であり、(b)は内部電極層におけるAu濃度を例示する図である。

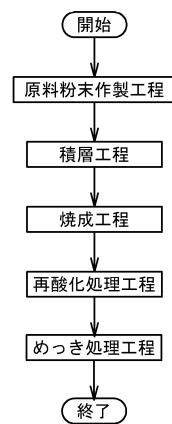

【図6】積層セラミックコンデンサの製造方法のフローを例示する図である。

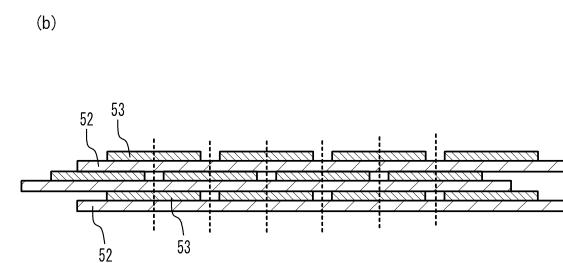

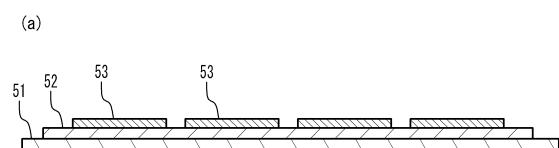

【図7】(a)および(b)は積層工程を例示する図である。

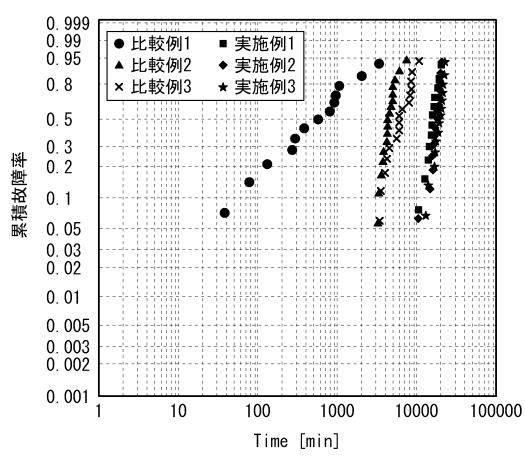

【図8】実施例および比較例について、故障に至るまでの時間と、累積故障率との関係を示すワイブルプロット図である。

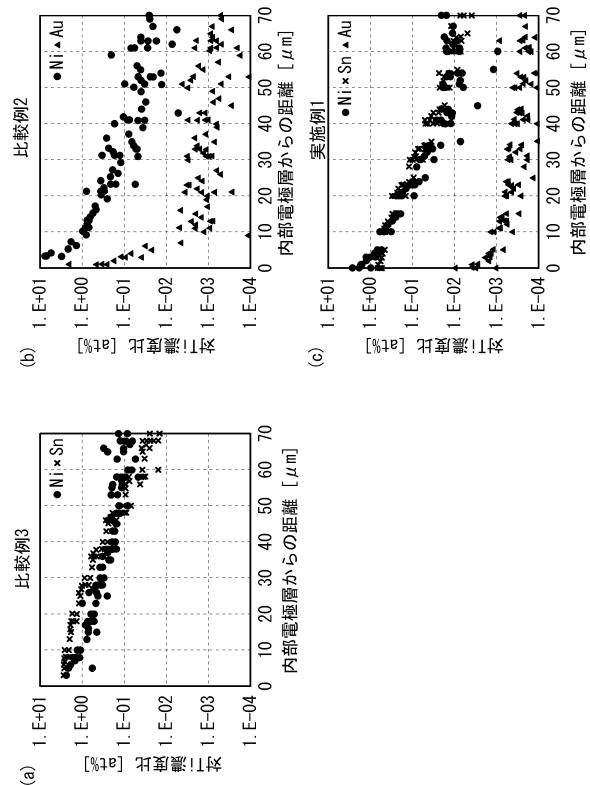

【図9】(a)～(c)は誘電体層におけるNi濃度を示す図である。

【発明を実施するための形態】

【0016】

以下、図面を参照しつつ、実施形態について説明する。

10

20

30

40

50

## 【0017】

## (実施形態)

図1は、実施形態に係る積層セラミックコンデンサ100の部分断面斜視図である。図2は、図1のA-A線断面図である。図3は、図1のB-B線断面図である。図1～図3で例示するように、積層セラミックコンデンサ100は、略直方体形状を有する積層チップ10と、積層チップ10のいずれかの対向する2端面に設けられた外部電極20a, 20bとを備える。なお、積層チップ10の当該2端面以外の4面のうち、積層方向の上面および下面以外の2面を側面と称する。外部電極20a, 20bは、積層チップ10の積層方向の上面、下面および2側面に延在している。ただし、外部電極20a, 20bは、互いに離間している。なお、図1において、X軸方向(第1方向)は、積層チップ10の長さ方向であって、積層チップ10の2端面が対向する方向であり、外部電極20aと外部電極20bとが対向する方向である。Y軸方向(第2方向)は、内部電極層の幅方向である。Z軸方向は、積層方向である。X軸方向と、Y軸方向と、Z軸方向とは、互いに直交している。10

## 【0018】

積層チップ10は、誘電体として機能するセラミック材料を含む誘電体層11と、卑金属材料を含む内部電極層12とが、交互に積層された構成を有する。各内部電極層12の端縁は、積層チップ10の外部電極20aが設けられた端面と、外部電極20bが設けられた端面とに、交互に露出している。それにより、各内部電極層12は、外部電極20aと外部電極20bとに、交互に導通している。その結果、積層セラミックコンデンサ100は、複数の誘電体層11が内部電極層12を介して積層された構成を有する。また、誘電体層11と内部電極層12との積層体において、積層方向の最外層には内部電極層12が配置され、当該積層体の上面および下面是、カバー層13によって覆われている。カバー層13は、セラミック材料を主成分とする。例えば、カバー層13の材料は、誘電体層11とセラミック材料の主成分が同じである。20

## 【0019】

積層セラミックコンデンサ100のサイズは、例えば、長さ0.25mm、幅0.125mm、高さ0.125mmであり、または長さ0.4mm、幅0.2mm、高さ0.2mm、または長さ0.6mm、幅0.3mm、高さ0.3mmであり、または長さ1.0mm、幅0.5mm、高さ0.5mmであり、または長さ3.2mm、幅1.6mm、高さ1.6mmであり、または長さ4.5mm、幅3.2mm、高さ2.5mmであるが、これらのサイズに限定されるものではない。30

## 【0020】

誘電体層11は、例えば、一般式 $ABO_3$ で表されるペロブスカイト構造を有するセラミック材料を主成分とする。なお、当該ペロブスカイト構造は、化学量論組成から外れた $ABO_3$ を含む。例えば、当該セラミック材料として、 $BaTiO_3$ (チタン酸バリウム),  $CaZrO_3$ (ジルコン酸カルシウム),  $CaTiO_3$ (チタン酸カルシウム),  $SrTiO_3$ (チタン酸ストロンチウム), ペロブスカイト構造を形成する $Ba_{1-x-y}Ca_xSr_yTi_{1-z}Zr_zO_3(0 < x < 1, 0 < y < 1, 0 < z < 1)$ 等を用いることができる。1層あたりの誘電体層11の厚みは、例えば、0.05μm以上5μm以下であり、または0.1μm以上3μm以下であり、または0.2μm以上1μm以下である。40

## 【0021】

図2で例示するように、外部電極20aに接続された内部電極層12と外部電極20bに接続された内部電極層12とが対向する領域は、積層セラミックコンデンサ100において電気容量を生じる領域である。そこで、当該電気容量を生じる領域を、容量領域14と称する。すなわち、容量領域14は、異なる外部電極に接続された隣接する内部電極層12同士が対向する領域である。

## 【0022】

外部電極20aに接続された内部電極層12同士が、外部電極20bに接続された内部電極層12を介さずに対向する領域を、エンドマージン15と称する。また、外部電極2

10

20

30

40

50

0 b に接続された内部電極層 1 2 同士が、外部電極 2 0 a に接続された内部電極層 1 2 を介さずに対向する領域も、エンドマージン 1 5 である。すなわち、エンドマージン 1 5 は、同じ外部電極に接続された内部電極層 1 2 が異なる外部電極に接続された内部電極層 1 2 を介さずに対向する領域である。エンドマージン 1 5 は、電気容量を生じない領域である。

#### 【 0 0 2 3 】

図 3 で例示するように、積層チップ 1 0 において、積層チップ 1 0 の 2 側面から内部電極層 1 2 に至るまでの領域をサイドマージン 1 6 と称する。すなわち、サイドマージン 1 6 は、上記積層構造において積層された複数の内部電極層 1 2 が 2 側面側に伸びた端部を覆うように設けられた領域である。サイドマージン 1 6 も、電気容量を生じない領域である。

10

#### 【 0 0 2 4 】

このような積層セラミックコンデンサ 1 0 0 において、内部電極層 1 2 に N i を用いると、誘電体層 1 1 に酸素欠陥が生じるなどして誘電体層 1 1 の信頼性が劣化するおそれがある。例えば、焼成工程の際に N i の酸化を抑制するために還元雰囲気を還元雰囲気とすると、誘電体層 1 1 に酸素欠陥が生じやすい。酸素欠陥が生じた誘電体層 1 1 を薄層化して高電界強度の電圧を印加すると、誘電体層 1 1 の耐久性が不十分となる。この場合、積層セラミックコンデンサ 1 0 0 の寿命が短くなる、寿命にバラツキが生じる、など、寿命特性が劣化するおそれがある。そこで、本実施形態に係る積層セラミックコンデンサ 1 0 0 は、寿命特性を向上させる構成を有している。

20

#### 【 0 0 2 5 】

まず、内部電極層 1 2 は、N i に加えて S n を含んでいる。内部電極層 1 2 が N i と S n を含むことで、積層セラミックコンデンサ 1 0 0 の寿命を向上させることができる。例えば、N i と S n とが合金化することで、内部電極層 1 2 と誘電体層 1 1 との界面の状態が変化することで、積層セラミックコンデンサ 1 0 0 の寿命が向上すると考えられる。

#### 【 0 0 2 6 】

次に、メカニズムは明らかになっていないが、内部電極層 1 2 に含まれる N i が誘電体層 1 1 に拡散すると、積層セラミックコンデンサ 1 0 0 に十分な寿命が得られない傾向が認められている。したがって、内部電極層 1 2 から誘電体層 1 1 への N i の拡散を抑制することが求められる。そこで、本発明者らは、内部電極層 1 2 への添加元素が N i の拡散に及ぼす影響を調べた。

30

#### 【 0 0 2 7 】

まず、4種類のサンプルを用意した。第1サンプルとして、チタン酸バリウムを主成分とする誘電体グリーンシート上に N i からなる内部電極パターン（厚さは 2 0 0 n m ）をスパッタリングで形成したサンプルを用意した。第2サンプルとして、チタン酸バリウムを主成分とする誘電体グリーンシート上に 3 . 3 μ g の N i ペーストを印刷したサンプルを用意した。第3サンプルとして、チタン酸バリウムを主成分とする誘電体グリーンシート上に N i および S n を含む内部電極パターン（ S n が 3 . 2 a t m % で、厚さは 2 0 0 n m ）をスパッタリングで形成したサンプルを用意した。第4サンプルとして、チタン酸バリウムを主成分とする誘電体グリーンシート上に N i および A u を含む内部電極パターン（ A u が 1 . 0 a t m % で、厚さは 2 0 0 n m ）をスパッタリングで形成したサンプルを用意した。

40

#### 【 0 0 2 8 】

各サンプルに対して、酸素分圧  $1 0 ^ { - 5 } a t m \sim 1 0 ^ { - 8 } a t m$  の還元雰囲気中で 1 1 0 0 ~ 1 3 0 0 で焼成を行ない、サンプルを作製した。L a - I C P ( レーザアブレーション融合イオンプラズマ質量分析 ) を用いて、誘電体層における N i 濃度を測定した。内部電極層からの距離と、N i 濃度比である ( N i / T i ) a t m % との関係を測定した。

#### 【 0 0 2 9 】

図 4 は、結果を示す図である。図 4 に示すように、第1サンプル～第3サンプルについては、内部電極層から離れた箇所でも N i 濃度が高くなつた。これは、焼成の際に N i が

50

拡散したからであると考えられる。これに対して、第4サンプルについては、内部電極層から離れた箇所ではNi濃度が低くなつた。これは、焼成の際にNiの拡散が抑制されたからであると考えられる。これらの結果から、内部電極層にAuを添加することで、誘電体層へのNiの拡散が抑制されることが確認された。

#### 【0030】

そこで、本実施形態に係る内部電極層12は、Niに加えてSnを含むとともに、Auを含んでいる。内部電極層12がAuをさらに含むことで、AuがNiの拡散をバリアする機能を有し、誘電体層11へのNiの拡散がより一層抑制される。それにより、誘電体層11の高電界強度の電圧印加に対する耐久性が向上する。その結果、積層セラミックコンデンサ100の寿命が向上する。寿命が向上することによって短い寿命が含まれなくなり、寿命のバラツキも抑制される。そのため、積層セラミックコンデンサ100の寿命特性が向上する。

10

#### 【0031】

内部電極層12の厚みは、例えば、0.01μm以上5μm以下であり、または0.05μm以上3μm以下であり、または0.1μm以上1μm以下である。

#### 【0032】

なお、内部電極層12におけるSnの含有量が少ないと、内部電極層12と誘電体層11との界面の状態を十分に制御できないおそれがある。また、Auの含有量が少ないと、十分にNiの拡散を抑制できないおそれがある。そこで、Sn含有量と、Auの含有量との合計に下限を設けることが好ましい。例えば、内部電極層12において、Niに対する、Sn含有量とAuの含有量との合計は、0.01at%以上であることが好ましく、0.05at%以上であることがより好ましく、0.1at%以上であることがさらに好ましく、0.2at%以上であることがさらに好ましい。

20

#### 【0033】

一方、Sn含有量と、Auの含有量との合計が多いと、融点の低下やコストアップといった不具合が生じるおそれがある。そこで、Sn含有量と、Auの含有量との合計に上限を設けることが好ましい。例えば、内部電極層12において、Niに対する、Sn含有量とAuの含有量との合計は、95at%以下であることが好ましく、50at%以下であることがより好ましく、10at%以下であることがさらに好ましい。

30

#### 【0034】

なお、Sn含有量とAu含有量との合計が0.2at%以上10at%以下であれば、Au含有量がSn含有量より少なくとも内部電極層12と誘電体層11との界面の状態を制御しつつNiの拡散を抑制することができる。そこで、Sn含有量とAu含有量との合計が0.2at%以上10at%以下であれば、Au使用量を減らしてコストを下げる観点から、Au含有量がSn含有量よりも少ないことが好ましい。

#### 【0035】

なお、内部電極層12における誘電体層11との界面近傍において、Sn濃度が高くなっていることが好ましい。信頼性を支配するのは内部電極層全体ではなく、誘電体層11と内部電極層12との界面の近傍のみだからである。そこで、図5(a)で例示するように、内部電極層12においては、厚さ方向の中心部においてはSn濃度が低く、誘電体層11との界面近傍においてはSn濃度が高くなるような濃度勾配が形成されていることが好ましい。また、図5(b)で例示するように、内部電極層12における誘電体層11との界面近傍において、Auの濃度が高くなっていることが好ましい。誘電体層11へのNiの拡散を効率的に抑制できる状態だからである。そこで、内部電極層12においては、積層方向の中心部においてはAuの濃度が低く、誘電体層11との界面近傍においてはAuの濃度が高くなるような濃度勾配が形成されていることが好ましい。

40

#### 【0036】

続いて、積層セラミックコンデンサ100の製造方法について説明する。図6は、積層セラミックコンデンサ100の製造方法のフローを例示する図である。

#### 【0037】

50

## (原料粉末作製工程)

まず、誘電体層 1 1 を形成するための誘電体材料を用意する。誘電体層 1 1 に含まれる A サイト元素および B サイト元素は、通常は  $ABO_3$  の粒子の焼結体の形で誘電体層 1 1 に含まれる。例えば、 $BaTiO_3$  は、ペロブスカイト構造を有する正方晶化合物であって、高い誘電率を示す。この  $BaTiO_3$  は、一般的に、二酸化チタンなどのチタン原料と炭酸バリウムなどのバリウム原料とを反応させてチタン酸バリウムを合成することで得ることができる。誘電体層 1 1 の主成分セラミックの合成方法としては、従来種々の方法が知られており、例えば固相法、ゾル・ゲル法、水熱法等が知られている。本実施形態においては、これらのいずれも採用することができる。

## 【0038】

10

得られたセラミック粉末に、目的に応じて所定の添加化合物を添加する。添加化合物としては、マグネシウム (Mg)、マンガン (Mn)、バナジウム (V)、クロム (Cr)、希土類元素 (イットリウム (Y)、サマリウム (Sm)、ユウロピウム (Eu)、ガドリニウム (Gd)、テルビウム (Tb)、ジスプロシウム (Dy)、ホロミウム (Ho)、エルビウム (Er)、ツリウム (Tm) およびイッテルビウム (Yb)) の酸化物、または、コバルト (Co)、ニッケル、リチウム (Li)、ホウ素 (B)、ナトリウム (Na)、カリウム (K) もしくはケイ素 (Si) を含む酸化物、または、コバルト、ニッケル、リチウム、ホウ素、ナトリウム、カリウムもしくはケイ素を含むガラスが挙げられる。

## 【0039】

20

例えば、セラミック原料粉末に添加化合物を含む化合物を湿式混合し、乾燥および粉碎してセラミック材料を調製する。例えば、上記のようにして得られたセラミック材料について、必要に応じて粉碎処理して粒径を調節し、あるいは分級処理と組み合わせることで粒径を整えてよい。以上の工程により、誘電体材料が得られる。

## 【0040】

## (積層工程)

次に、得られた誘電体材料に、ポリビニルブチラール (PVB) 樹脂等のバインダと、エタノール、トルエン等の有機溶剤と、可塑剤とを加えて湿式混合する。得られたスラリを使用して、例えばダイコータ法やドクターブレード法により、基材 5 1 上に例えば厚み  $0.5 \mu m$  以上  $1.0 \mu m$  以下の誘電体グリーンシート 5 2 を塗工して乾燥させる。基材 5 1 は、例えば、PET (ポリエチレンテレフタレート) フィルムである。

## 【0041】

30

次に、図 7 (a) で例示するように、誘電体グリーンシート 5 2 上に、内部電極パターン 5 3 を成膜する。図 7 (a) では、一例として、誘電体グリーンシート 5 2 上に 4 層の内部電極パターン 5 3 が所定の間隔を空けて成膜されている。成膜手法は、特に限定されるものではないが、例えば、Ni - Sn - Au の混合物を含む電極ペーストを用いる、Ni 金属粉のペーストに Au や Sn を含む成分を混ぜる、合金ターゲットを用いたスパッタなどの真空成膜、個別ターゲットを用いた同時スパッタなどを用いることができる。内部電極パターン 5 3 が成膜された誘電体グリーンシート 5 2 を、積層単位とする。

## 【0042】

40

次に、誘電体グリーンシート 5 2 を基材 5 1 から剥がしつつ、図 7 (b) で例示するように、積層単位を積層する。

## 【0043】

次に、積層単位が積層されることで得られた積層体の上下にカバーシートを所定数 (例えば 2 ~ 10 層) だけ積層して熱圧着させ、所定チップ寸法 (例えば  $1.0 mm \times 0.5 mm$ ) にカットする。図 7 (b) の例では、点線に沿ってカットする。カバーシートは、誘電体グリーンシート 5 2 と同じ成分であってもよく、添加化合物が異なっていてもよい。

## 【0044】

## (焼成工程)

このようにして得られたセラミック積層体を、 $N_2$  霧囲気で脱バインダ処理した後に外部電極 20a, 20b の下地層となる金属ペーストをディップ法で塗布し、酸素分圧 1.0

50

-5 ~ 10 -8 atm の還元雰囲気中で 1100 ~ 1300 で 10 分 ~ 2 時間焼成する。このようにして、積層セラミックコンデンサ 100 が得られる。

【0045】

(再酸化処理工程)

その後、N<sub>2</sub>ガス雰囲気中で 600 ~ 1000 で再酸化処理を行ってもよい。

【0046】

(めっき処理工程)

その後、めっき処理により、外部電極 20a, 20b に、Cu, Ni, Sn 等の金属コーティングを行ってもよい。

【0047】

本実施形態に係る製造方法によれば、内部電極層 12 が Ni に加えて Sn を含むとともに、Au を含むことになる。それにより、得られる積層セラミックコンデンサ 100 の寿命が向上する。寿命が向上することによって短い寿命が含まれなくなり、寿命のバラツキも抑制される。そのため、積層セラミックコンデンサ 100 の寿命特性が向上する。

【0048】

なお、上記各実施形態においては、セラミック電子部品の一例として積層セラミックコンデンサについて説明したが、それに限られない。例えば、パリスタやサーミスタなどの、他の電子部品を用いてもよい。

【実施例】

【0049】

以下、実施形態に係る積層セラミックコンデンサを作製し、特性について調べた。

【0050】

(実施例 1)

チタン酸バリウム粉末に対して添加物を添加し、ボールミルで十分に湿式混合粉碎して誘電体材料を得た。誘電体材料に有機バインダとしてブチラール系、溶剤としてトルエン、エチルアルコールを加えてドクターブレード法にて PET の基材上に誘電体グリーンシートを塗工した。誘電体グリーンシートの厚みは、1.0 μm とした。

【0051】

次に、誘電体グリーンシート上に、Ni - Sn - Au 合金を含むペーストを用いて内部電極パターンを成膜した。Ni / Sn / Au 比は、原子比で 96 / 2 / 2 とした。

【0052】

次に、誘電体グリーンシートを基材から剥がしつつ、積層単位を積層した。積層の際の温度は 80 とした。積層単位の積層後に、4 MPa の圧力かけてプレスした。プレス時間は、5 秒とした。次に、積層単位が積層されることで得られた積層体の上下にカバーシートを所定数だけ積層して静水圧で熱圧着した。静水圧の圧力は 120 MPa とし、温度は 100 とし、プレス時間は 25 秒とした。その後、所定チップ寸法 (1.0 mm × 0.5 mm × 0.5 mm) にカットした。

【0053】

このようにして得られたセラミック積層体を、N<sub>2</sub>雰囲気で脱バインダ処理した後に外部電極の下地層となる金属ペーストをディップ法で塗布し、還元雰囲気下で焼成した。

【0054】

(実施例 2)

Ni / Sn / Au の原子比を 99.6 / 0.2 / 0.2 に変更した他は、実施例 1 と同様の製造条件で積層セラミックコンデンサを作製した。

【0055】

(実施例 3)

Ni / Sn / Au の原子比を 80 / 10 / 10 に変更した他は、実施例 1 と同様の製造条件で積層セラミックコンデンサを作製した。

【0056】

(比較例 1)

10

20

30

40

50

内部電極層に S n も A u も添加しなかった。その他の製造条件は、実施例 1 と同様とした。

【 0 0 5 7 】

( 比較例 2 )

内部電極層に実施例 1 と同じ濃度の A u を添加したものの、 S n を添加しなかった。その他の製造条件は、実施例 1 と同様とした。

【 0 0 5 8 】

( 比較例 3 )

内部電極層に実施例 1 と同じ濃度の S n を添加したものの、 A u を添加しなかった。その他の製造条件は、実施例 1 と同様とした。

10

【 0 0 5 9 】

( 寿命試験 )

実施例 1 ~ 3 および比較例 1 ~ 3 のそれぞれについて、複数のサンプルの故障に至るまでの時間を測定した。測定手法は、 150 / 18 V /  $\mu$ m の直流電界下にて漏れ電流が最小漏れ電流の 10 倍になるまでの時間を測定した。

【 0 0 6 0 】

図 8 は、実施例 1 ~ 3 および比較例 1 ~ 3 のそれぞれについて、故障に至るまでの時間と、累積故障率との関係を示すワイブルプロット図である。表 1 は、図 8 のワイブルプロットの傾きを示す。また、表 1 は、実施例 1 ~ 3 および比較例 1 ~ 3 のそれぞれについて、50 % の個数のサンプルが故障した時間を示す。

20

【 表 1 】

|                  | 比較例1 | 比較例2 | 比較例3 | 実施例1  | 実施例2  | 実施例3  |

|------------------|------|------|------|-------|-------|-------|

| 傾き               | 0.81 | 3.00 | 4.88 | 5.73  | 5.44  | 6.26  |

| 50%故障時間<br>(min) | 530  | 6159 | 4511 | 17163 | 15387 | 18314 |

【 0 0 6 1 】

図 8 および表 1 に示すように、比較例 1 では、ワイブルプロットの傾きが緩慢であり、寿命の短いサンプルが多くなった。また、サンプル間で寿命の差が大きくなかった。これは、内部電極層が S n も A u も含まなかつたからであると考えられる。比較例 2 では、比較例 1 よりは寿命が長くなつたものの、十分な寿命が得られなかつた。これは、内部電極層の N i に S n のみを加えて A u を加えなかつたために、N i の拡散が十分に抑制されなかつたからであると考えられる。比較例 3 では、比較例 1 よりは寿命が長くなつたものの、十分な寿命が得られなかつた。これは、内部電極層の N i に A u のみを加えて S n を加えなかつたために、内部電極層と誘電体層との界面が十分に制御されなかつたからであると考えられる。

30

【 0 0 6 2 】

これに対して、実施例 1 ~ 3 では、どのサンプルについても寿命が十分に長くなつた。また、ワイブルプロットの傾きが大きくなり、寿命のバラツキも抑制された。これは、内部電極層に、 N i に加えて S n および A u の両方を含ませたからであると考えられる。

40

【 0 0 6 3 】

実施例 1 および比較例 2 , 3 に対して、 L a - I C P を用いて、誘電体層における N i 濃度を測定した。図 9 ( a ) は、比較例 3 の結果を示す図である。図 9 ( b ) は、比較例 2 の結果を示す図である。図 9 ( c ) は、実施例 1 の結果を示す図である。図 9 ( a ) に示すように、内部電極層に A u を添加しない場合には、誘電体層中に多くの N i が拡散していた。これに対して、図 9 ( b ) に示すように、 S n の代わりに A u を内部電極層に添加すると、誘電体層への N i の拡散量が抑制されていることがわかる。さらに、図 9 ( c ) に示すように、 S n と A u の両方を内部電極層に添加すると、誘電体層への N i の拡散

50

量がさらに抑制されていることがわかる。このように、内部電極層がS<sub>n</sub>およびA<sub>u</sub>の両方を含むことで、誘電体層へのN<sub>i</sub>の拡散がより一層抑制されたことがわかる。これらの結果が、表1の結果が得られた要因になっているものと考えられる。

#### 【0064】

以上、本発明の実施例について詳述したが、本発明は係る特定の実施例に限定されるものではなく、特許請求の範囲に記載された本発明の要旨の範囲内において、種々の変形・変更が可能である。

#### 【符号の説明】

#### 【0065】

|               |              |    |

|---------------|--------------|----|

| 1 0           | 積層チップ        | 10 |

| 1 1           | 誘電体層         |    |

| 1 2           | 内部電極層        |    |

| 1 3           | カバー層         |    |

| 1 4           | 容量領域         |    |

| 1 5           | エンドマージン      |    |

| 1 6           | サイドマージン      |    |

| 2 0 a , 2 0 b | 外部電極         |    |

| 5 1           | 基材           |    |

| 5 2           | 誘電体グリーンシート   | 20 |

| 5 3           | 内部電極パターン     |    |

| 1 0 0         | 積層セラミックコンデンサ |    |

30

40

50

## 【図面】

## 【図 1】

## 【図 2】

10

## 【図 3】

## 【図 4】

20

30

40

50

【図 5】

【図 6】

【図 7】

【図 8】

10

20

30

40

50

【図 9】

10

20

30

40

50

---

フロントページの続き

東京都中央区京橋二丁目 7 番 19 号 太陽誘電株式会社内

審査官 鈴木 駿平

(56)参考文献 国際公開第 2014 / 024538 (WO, A1)

特開平 04 - 032213 (JP, A)

(58)調査した分野 (Int.Cl., DB名)

H01G 4 / 00 - 4 / 224

H01G 4 / 255 - 4 / 40

H01G 13 / 00 - 13 / 06