(19) 日本国特許庁(JP)

## (12) 公表特許公報(A)

(11) 特許出願公表番号

特表2007-535814

(P2007-535814A)

(43) 公表日 平成19年12月6日(2007.12.6)

|                       |                 |             |

|-----------------------|-----------------|-------------|

| (51) Int.C1.          | F 1             | テーマコード (参考) |

| HO1L 21/20 (2006.01)  | HO1L 21/20      | 5F11O       |

| HO1L 29/786 (2006.01) | HO1L 29/78 618B | 5F152       |

HO1L 29/78 618E

|               |                              | 審査請求 未請求 予備審査請求 未請求 (全 11 頁)                                                   |

|---------------|------------------------------|--------------------------------------------------------------------------------|

| (21) 出願番号     | 特願2007-510751 (P2007-510751) | (71) 出願人 504199127                                                             |

| (86) (22) 出願日 | 平成17年4月5日 (2005.4.5)         | フリースケール セミコンダクター イン                                                            |

| (85) 翻訳文提出日   | 平成18年11月9日 (2006.11.9)       | コーポレイテッド                                                                       |

| (86) 國際出願番号   | PCT/US2005/011552            | アメリカ合衆国 78735 テキサス州                                                            |

| (87) 國際公開番号   | W02005/112094                | オースティン ウィリアム キャノン                                                              |

| (87) 國際公開日    | 平成17年11月24日 (2005.11.24)     | ドライブ ウエスト 6501                                                                 |

| (31) 優先権主張番号  | 10/836,172                   | (74) 代理人 100116322                                                             |

| (32) 優先日      | 平成16年4月30日 (2004.4.30)       | 弁理士 桑垣 衛                                                                       |

| (33) 優先権主張国   | 米国(US)                       | (72) 発明者 オーロースキー、マリウス ケイ。<br>アメリカ合衆国 78739 テキサス州<br>オースティン レッドモンド ロード<br>10813 |

|               |                              | (72) 発明者 バー、アレクサンドル エル。<br>フランス国 F-38920 クロル ア<br>ンパス ド ラ ペラド 51               |

最終頁に続く

(54) 【発明の名称】シリコンゲルマニウムを用いる半導体構造の製造方法

## (57) 【要約】

シリコン層(24, 26, 28)を有する半導体基板を提供する。一実施形態では、基板はシリコン層(24, 26, 28)の下に位置する酸化物層(14)を有するシリコン・オン・インシュレータ(SOI)基板(12, 14, 24, 26, 28)である。シリコン層(24, 26, 28)の上に非晶質または多結晶のシリコンゲルマニウム層(32)を形成する。これに代えて、シリコン層(24, 26, 28)の上部へゲルマニウムを注入して、非晶質シリコンゲルマニウム層(32)を形成する。次に、シリコンゲルマニウム層(32)を酸化して、シリコンゲルマニウム層をシリコンジオキサイド層(34)に変換し、かつシリコン層(24, 26, 28)の少なくとも一部をゲルマニウムリッチシリコン(36, 38)に変換する。次に、ゲルマニウムリッチシリコン(36, 38)を用いるトランジスタ(48, 50, 52)の形成に先立って、シリコンジオキサイド層(34)を除去する。一実施形態では、シリコン層(28)の上、かつ、シリコンゲルマニウム層(32)の下のパターン形成されたマスキング層(30)を用いて、

## 【特許請求の範囲】

## 【請求項 1】

半導体構造の製造方法であって、

半導体基板を準備する基板準備工程と、

非晶質シリコンゲルマニウム含有層および多結晶シリコンゲルマニウム含有層から選択される第1の層を半導体基板の上に形成する第1層形成工程と、

第1の層を酸化させる第1層酸化工程と、第1層酸化工程は第1の層をシリコン含有酸化物層に変換し、かつ、半導体基板のうちの少なくとも一部をゲルマニウムリッチ半導体層に変換することと、からなる方法。

## 【請求項 2】

半導体基板は半導体層の下に位置する埋込酸化物層を含むことと、

第1の層の酸化中、半導体基板の半導体層はゲルマニウムリッチ半導体層へ変換されることと、を含む請求項1に記載の方法。

## 【請求項 3】

半導体基板はシリコン層を含むことと、

半導体基板のうちの前記少なくとも一部は該シリコン層を含むことと、

第1の層の酸化中、半導体基板の該シリコン層はゲルマニウムリッチ半導体層へ変換されることと、を含む請求項1に記載の方法。

## 【請求項 4】

第1層酸化工程は第1の層全体をシリコン含有酸化物層に変換する請求項1に記載の方法。

## 【請求項 5】

シリコン含有酸化物層を除去する工程を含む請求項1に記載の方法。

## 【請求項 6】

ゲルマニウムリッチ半導体層のゲルマニウム含量は約15～50パーセントである請求項1に記載の方法。

## 【請求項 7】

第1層形成工程は第1の層をプランケット堆積する工程を含む請求項1に記載の方法。

## 【請求項 8】

第1層形成工程は半導体基板の上部へゲルマニウムを注入し、該上部を非晶質シリコンゲルマニウム層に変換する工程を含む請求項1に記載の方法。

## 【請求項 9】

半導体基板は第1の分離領域および第2の分離領域を含むことと、ゲルマニウムリッチシリコン層は第1の分離領域と第2の分離領域との間に形成されることと、を含む請求項1に記載の方法。

## 【請求項 10】

第1層形成工程に先立って、半導体基板の上にパターン形成されたマスキング層を形成する工程と、

ゲルマニウムリッチシリコン層はパターン形成されたマスキング層によって露出される半導体基板の部分において形成されることと、を含む請求項1に記載の方法。

## 【請求項 11】

ゲルマニウムリッチ半導体層の上のゲート誘電体と、ゲート誘電体の上のゲートと、ゲルマニウムリッチ半導体層のゲートの下のチャンネルと、チャンネルから側方に離間されている複数のソース／ドレイン領域とを有するトランジスタを形成する工程を含む請求項1に記載の方法。

## 【請求項 12】

ゲルマニウムリッチ半導体層の上に半導体層を形成する工程と、

ゲルマニウムリッチ半導体層の上のゲート誘電体と、ゲート誘電体の上のゲートと、該半導体層のゲートの下のチャンネルと、チャンネルから側方に離間されている複数のソース／ドレイン領域とを有するトランジスタを形成する工程と、を含む請求項1に記載の方

法。

【請求項 1 3】

半導体構造の製造方法であって、シリコン層を含む半導体基板を準備する基板準備工程と、非晶質シリコンゲルマニウム層および多結晶シリコンゲルマニウム層のうちの一方であるシリコンゲルマニウム層を半導体基板のシリコン層上に形成するシリコンゲルマニウム層形成工程と、シリコンゲルマニウム層を酸化させて、シリコンゲルマニウム層をシリコンジオキサイドに変換し、かつ、シリコン層のうちの少なくとも一部をゲルマニウムリッチシリコンに変換するシリコンゲルマニウム層酸化工程と、からなる方法。

10

【請求項 1 4】

シリコンゲルマニウム層形成工程はシリコンゲルマニウム層のブランケット堆積を含む請求項 1 3 に記載の方法。

【請求項 1 5】

第 1 層形成工程は半導体基板のシリコン層の上部へゲルマニウムを注入する工程を含む請求項 1 3 に記載の方法。

【請求項 1 6】

シリコンゲルマニウム層酸化工程の後、変換されたシリコンゲルマニウム層を除去する工程を含む請求項 1 3 に記載の方法。

【請求項 1 7】

シリコン層に複数の分離領域を形成する工程と、該複数の分離領域間のシリコン層の能動部分はゲルマニウムリッチシリコンへ変換されることと、を含む請求項 1 3 に記載の方法。

20

【請求項 1 8】

シリコンゲルマニウム層形成工程に先立って、シリコン層の上にパターン形成されたマスキング層を形成する工程と、

パターン形成されたマスキング層によって露出されるシリコン層の部分はゲルマニウムリッチシリコンへ変換されることと、を含む請求項 1 3 に記載の方法。

【請求項 1 9】

ゲルマニウムリッチシリコンの上のゲート誘電体と、ゲート誘電体の上のゲートと、ゲルマニウムリッチシリコンのゲートの下のチャンネルと、チャンネルから側方に離間されている複数のソース／ドレイン領域とを有するトランジスタを形成する工程を含む請求項 1 3 に記載の方法。

30

【請求項 2 0】

ゲルマニウムリッチシリコンの上に半導体層を形成する工程と、半導体層の上のゲート誘電体と、ゲート誘電体の上のゲートと、半導体層のゲートの下のチャンネルと、チャンネルから側方に離間されている複数のソース／ドレイン領域とを有するトランジスタを形成する工程と、を含む請求項 1 3 に記載の方法。

【請求項 2 1】

半導体基板はシリコン層の下に位置する埋込酸化物層を含む請求項 1 3 に記載の方法。

40

【請求項 2 2】

半導体構造の製造方法であって、半導体基板を準備する基板準備工程と、第 1 の化学種及び第 2 の化学種を含有する化合物を含む第 1 の層を半導体基板の上に形成する第 1 層形成工程と、第 1 の層は非晶質層および多結晶層のうちの一方であることと、

、 第 1 の層を第 1 の化学種を含む除去可能層に変換する第 1 層変換工程と、第 1 層変換工程は第 2 の化学種を下に位置する半導体基板へ移動させることと、からなる方法。

【請求項 2 3】

第 1 層変換工程の後、除去可能層を除去する工程を含む請求項 2 1 に記載の方法。

50

**【請求項 2 4】**

半導体基板に複数の分離領域を形成する工程と、第1層の変換中、第2の化学種は該複数の分離領域間の半導体基板の能動部分へ移動されることと、を含む請求項21に記載の方法。

**【請求項 2 5】**

第1層形成工程に先立って、半導体基板の上にパターン形成されたマスキング層を形成する工程と、第1層の変換中、第2の化学種はパターン形成されたマスキング層によって露出される半導体基板の部分へ移動されることと、を含む請求項21に記載の方法。

**【請求項 2 6】**

第1層変換工程の後、半導体基板の上のゲート誘電体と、ゲート誘電体の上のゲートと、ゲート誘電体の下のチャンネルと、チャンネルから側方に離間されている複数のソース／ドレイン領域とを有するトランジスタを形成する工程を含む請求項21に記載の方法。 10

**【発明の詳細な説明】****【技術分野】****【0001】**

本発明は半導体デバイスに関する。より詳細には、本発明はシリコンゲルマニウムを用いる半導体デバイスに関する。

**【背景技術】****【0002】**

シリコンは集積回路の製造において従来的に用いられる非常に一般的な半導体材料であり、シリコンの利点はよく知られている。最近では、ゲルマニウムを含有するシリコンの利点はさらに重要となり、追求されている。問題点のうちの1つは、高品質なシリコンゲルマニウム結晶、即ち、高品質な単結晶を形成する能力、特に、所望のゲルマニウム濃度にて形成する能力である。高品質シリコン単結晶構造は容易に利用可能であって、低ゲルマニウム濃度のシリコンゲルマニウムと比べてさえも、シリコンゲルマニウムのものよりもはるかに安価である。したがって、シリコンゲルマニウムが競争することは困難である。 20

**【0003】**

しかし、技術的見地からも、10%を超えるゲルマニウム濃度で単結晶のシリコンゲルマニウムをエピタキシャル成長させることは困難である。したがって、30%の範囲に渡る、より望ましい濃度を達成するには、特別な後処理が必要である。一例は10%のシリコンゲルマニウム材料を酸化させることである。これは、シリコンを消費し、未使用のゲルマニウムをシリコンゲルマニウム層の残りの部分へ拡散させることによって、ゲルマニウム濃度を増大させる効果を有する。これは、時間を消費し成長に費用を要するシリコンゲルマニウムが比較的厚い層に成長することを必要とするため、高価である。 30

**【発明の開示】****【発明が解決しようとする課題】****【0004】**

したがって、高品質かつ費用効果的である単結晶のシリコンゲルマニウムを形成する方法の必要が存在する。

**【課題を解決するための手段】****【0005】**

一態様では、単結晶シリコン層から開始し、シリコンゲルマニウムを用いることによって、能動半導体が得られる。このシリコン層においては、比較的安価なシリコンゲルマニウムの層が形成される。この層は多結晶又は非晶質の層の堆積によって、或いはシリコン層へゲルマニウムを注入することによって、形成可能である。次に、この比較的安価なシリコンゲルマニウム層は酸化される。これは、下に位置する単結晶シリコン層へゲルマニウムを拡散する効果を有する。これによって、下に位置する単結晶層はシリコンゲルマニウムとなる。単結晶層のゲルマニウム濃度は、比較的安価なシリコンゲルマニウム層におけるゲルマニウム濃度と、厚さとの選択によって決定される。得られるのは、能動半導体として用いられ得る所望のゲルマニウム厚さのシリコンゲルマニウム半導体、又は、変形 40

したシリコン層をエピタキシャル成長させるシリコンゲルマニウム半導体である。

【発明を実施するための最良の形態】

【0006】

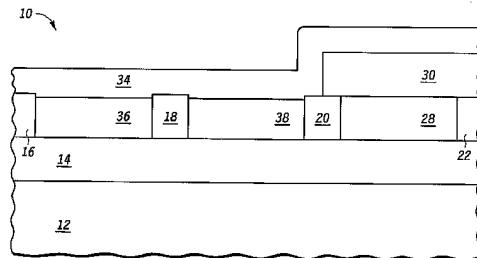

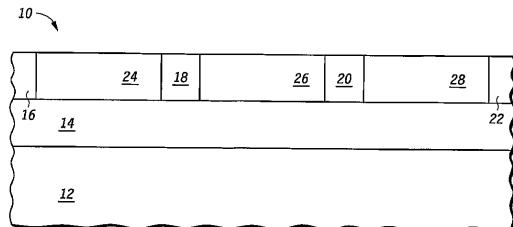

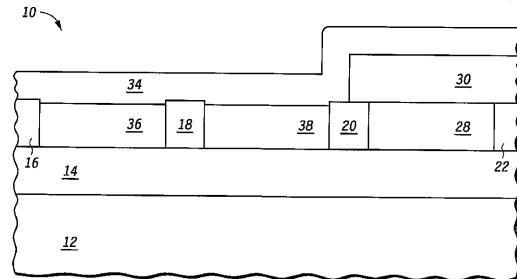

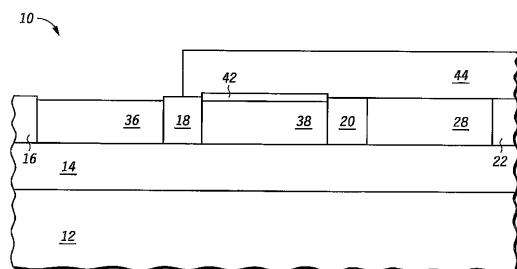

図1には、半導体構造10を示す。半導体構造10はシリコンの半導体層12、半導体層12上の埋込酸化物14、トレンチ分離領域16、トレンチ分離領域18、トレンチ分離領域20、トレンチ分離領域22、トレンチ分離領域16と18との間の能動領域24、トレンチ分離領域18と20との間の能動領域26、およびトレンチ分離領域20と22との間の能動領域28からなる。能動領域24～28は単結晶シリコンである。トレンチ分離領域16～22は酸化物などの絶縁体である。処理のこの段階において、トレンチ分離領域16～22は埋込酸化物14から半導体構造10の表面まで伸びている。同様に、図1に示すように、能動領域24～28は埋込酸化物14から半導体構造10の表面まで伸びている。この構造は、周知のセミコンダクタ・オン・インシュレータ(SOI)技術を用いて容易に得られる。

【0007】

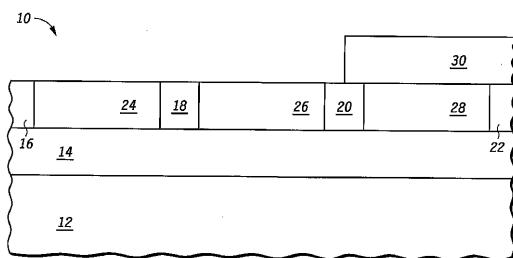

図2には、マスク30の形成後の半導体構造10を示す。マスク30は能動領域28の全部の上に伸びており、かつ、トレンチ分離領域20, 22の一部の上に伸びている。マスク30はそのように配置されているので、能動領域24, 26は露出されている。このマスクは好適には窒化物から形成されるが、別の材料が有効な場合もある。このマスクはそれほど正確である必要はなく、トレンチ分離領域20, 22へ簡単に整合される。これは窒化物の層を堆積し、フォトレジストの層を堆積し、そのフォトレジストをパターン形成し、続いてフォトレジストのパターンにしたがって窒化物をエッチングしてマスク30を残すことによって、形成され得る。

【0008】

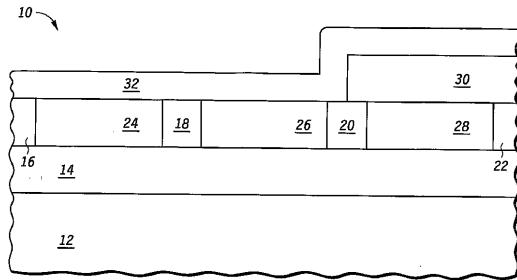

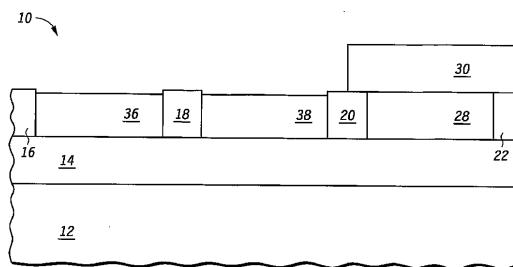

図3には、シリコンゲルマニウム層32の堆積後の半導体構造10を示す。このシリコンゲルマニウム層はブランケット堆積されるため、パターン形成される必要はない。この層32は非晶質層又は多結晶層として堆積されてもよい。非晶質層又は多結晶層は、いずれも単結晶シリコンゲルマニウムをエピタキシャル成長させるより安価に形成される。さらに、このシリコンゲルマニウム層32の堆積に先立って、トレンチ分離領域16～22が形成されている。

【0009】

図4には、図3のシリコンゲルマニウム層32の酸化後の酸化物層34及び能動領域36, 38を示す。この酸化工程によって、シリコンゲルマニウム層32はシリコンを含有する除去可能層である酸化物層34へ変換され、能動領域24, 26へゲルマニウムが拡散されることにより、シリコンゲルマニウムからなる能動領域36, 38がそれぞれ形成される。これによって、能動領域24, 26はゲルマニウムリッチなシリコン領域へ変換される。能動領域28はマスク30のため、シリコンのみのままで残る。能動領域24, 26の厚さが70nm(700オングストローム)であるのに対し、約30%のゲルマニウムにおけるシリコンゲルマニウム層32の有効厚さは、約50nm(約500オングストローム)である。得られる能動領域36, 38の厚さは約50nm(約500オングストローム)である。これらの条件の下では、得られる能動領域36, 38のゲルマニウム濃度は約30%である。能動領域36, 38において30%のゲルマニウム濃度を得るために、厚さ及びゲルマニウム濃度以外の比率を用いることも可能である。また、能動領域36, 38は所望のようにいくぶん異なるゲルマニウム濃度を有してもよい。能動領域36, 38において、ゲルマニウム濃度の所望範囲が15～50%にわたることも可能である。この実施例では、能動領域36, 38の厚さは能動領域24, 26より減少する。この減少量は、酸化工程が実行される長さによって選択されるが、最終のゲルマニウム濃度の計算においても考慮される必要がある。得られる濃度は、最終の能動領域の厚さに対するシリコンゲルマニウム層の厚さの比率にシリコンゲルマニウム層のゲルマニウム濃度を掛け算したものである。

【0010】

10

20

30

40

50

能動領域 3 6 , 3 8 は、元のシリコン構造のためにいくぶん圧縮性である。ゲルマニウムによって結晶格子のシリコンが置換されるので、結晶構造全体はますます圧縮性となる。能動領域 3 6 , 3 8 の上部の酸化中の昇温によって、ある程度の緩和が生じる。したがって、元のシリコン構造からの緩和が存在するが、結晶それ自身はゲルマニウムを含むため、圧縮下にある。シリコンの能動領域 2 4 , 2 6 はトレンチ分離領域 1 6 , 1 8 , 2 0 の酸化物に包囲されているため、この緩和は比較的容易に達成される。圧縮は P チャネルトランジスタ性能に好都合である。

#### 【 0 0 1 1 】

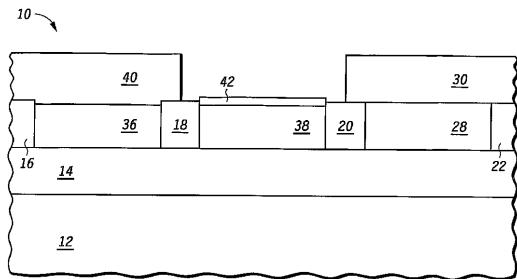

図 5 には、酸化物層 3 4 の除去後の半導体構造 1 0 を示す。これによって、能動領域 3 6 , 3 8 が露出される。随意では、この時点において領域 3 6 , 3 8 の上に薄い酸化物層を形成することが望ましい場合がある。10

#### 【 0 0 1 2 】

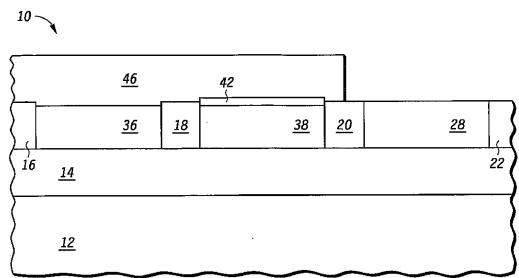

図 6 には、能動領域 3 6 の上のマスク 4 0 の形成後の半導体構造 1 0 を示す。この実施例では、マスク 3 0 は除去されないものとして示す。代替の実施例では、マスク 3 0 は除去され、マスク 4 0 の形成されるときに能動領域 2 8 の上にマスクが再形成される。マスク 3 0 の形成において用いられるのと同じ処理が、マスク 4 0 の形成において用いられてよい。この結果、能動領域 3 8 は露出される。

#### 【 0 0 1 3 】

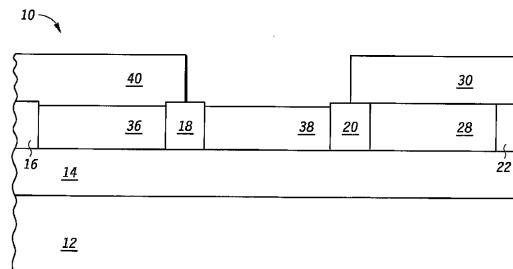

図 7 には、能動領域 3 8 上における、単結晶であるシリコン層 4 2 のエピタキシャル成長後の半導体構造 7 を示す。能動領域 3 8 は、元のシリコン構造から少なくともいくぶん緩和されており、シリコン層 4 2 に対し応力ひずみを生じることによってシリコン層 4 2 を変形させる。変形したシリコン層 4 2 は、N チャネルトランジスタ性能には望ましい。変形の量は約 1 % である。シリコン層 4 2 の形成後、P 型の注入が実行される。注入の実行に先立って、能動的なシリコン層 4 2 の上に薄い酸化物層を形成することが有用な場合もある。この注入によって、続く N チャネルトランジスタの形成のためのバックグラウンドドーピングが提供される。20

#### 【 0 0 1 4 】

図 8 には、マスク 4 0 の除去およびマスク 4 4 の形成後の半導体構造 1 0 を示す。マスク 4 4 は能動領域 3 8 , 2 8 と、これもまた能動領域であるシリコン層 4 2 とを覆う。これによって、能動領域 3 6 が注入のために露出される。マスク 4 4 は完全に新しいマスクであることも可能であり、新しいマスクとマスク 3 0 との組み合わせであることも可能である。このマスクはマスク 3 0 , 4 0 を形成するのと同じように形成されてもよい。注入は N 型であり、この注入によって、続く P チャネルトランジスタの形成のためのバックグラウンドドーピングが提供される。この能動領域が少なくともある程度の圧縮応力の下にあることは、P チャネル性能に有利である。30

#### 【 0 0 1 5 】

図 9 には、マスク 4 4 の除去、及び能動領域 3 6 , 3 8 とシリコン層 4 2 との上のマスク 4 6 の形成後の半導体構造 1 0 を示す。これによって、従来型の単結晶シリコンである能動領域 2 8 が露出される。したがって、能動領域 2 8 は最も一般的に使用される型のトランジスタを製造するために利用可能である。したがって、半導体構造 1 0 においては、一般的な大量生産におけるトランジスタ型の利点が利用可能である。40

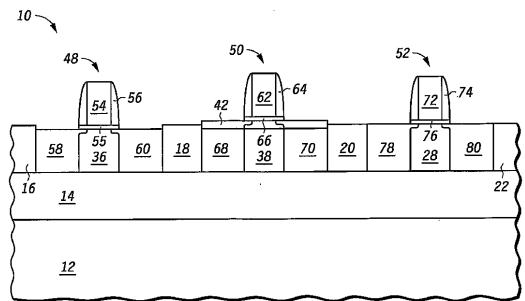

#### 【 0 0 1 6 】

図 1 0 には、能動領域 3 6 , 3 8 , 2 8 内及び上における、それぞれトランジスタ 4 8 , 5 0 , 5 2 の形成の後の半導体構造 1 0 を示す。トランジスタ 5 0 はシリコン層 4 2 内にも形成される。P チャネルであるトランジスタ 4 8 は、能動領域 3 6 の上のゲート 5 4 、能動領域 3 6 とゲート 5 4 との間のゲート誘電体、能動領域 3 6 内の第 1 のソース / ドレイン 5 8 、ソース / ドレイン 5 8 から離間されている能動領域 3 6 内の第 2 のソース / ドレイン 6 0 、およびゲート 5 4 の周囲のサイドウォールスペーサ 5 6 からなる。ソース / ドレイン 5 8 , 6 0 は P 型である。N チャネルであるトランジスタ 5 0 は、能動領域 3 8 とシリコン層 4 2 との上のゲート 6 2 、ゲート 6 2 とシリコン層 4 2 との間のゲート誘電体である。トランジスタ 4 8 は、能動領域 3 6 の上のゲート 5 4 とゲート 5 4 との間のゲート誘電体である。50

電体 6 6、層 4 2 および能動領域 6 8 内のソース / ドレイン 6 8、ソース / ドレイン領域 6 8 から離間されており、かつ、能動領域 3 8 およびシリコン層 4 2 内のソース / ドレイン 7 0、およびゲート 6 2 の周囲のサイドウォールスペーサ 6 4 からなる。ソース / ドレイン 6 8, 7 0 は N 型である。トランジスタ 5 2 は N チャネルであることも P チャネルであることも可能であり、能動領域 2 8 の上のゲート 7 2、ゲート 7 2 と能動領域 2 8 との間のゲート誘電体 7 6、能動領域 2 8 内のソース / ドレイン領域 7 8、能動領域 2 8 内のソース / ドレイン 8 0、及びゲート 7 2 の周囲のサイドウォールスペーサ 7 4 からなる。ソース / ドレイン 7 8, 8 0 は P 型であることも N 型であることも可能である。トランジスタ 5 2 によって、この記載の処理へ従来の N および P チャネルトランジスタを比較的簡単に組み込み可能であることが示される。

10

#### 【0017】

明細書においては、本発明を特定の実施形態に関して記載した。しかしながら、添付の特許請求の範囲において述べる本発明の範囲から逸脱することなく、様々な修正および変更を行なうことが可能であることが、当業者には認識される。例えば、この手法においてゲルマニウム及びシリコンとは異なる半導体材料を用いて、この結果を達成し得る。したがって、明細書及び図面は限定的な意味ではなく例示的な意味に捉えられるものであり、そうした修正全てが本発明の範囲内に含まれることが意図されるものである。

#### 【0018】

上述においては、利点、他の長所および課題の解決策を特定の実施形態に関して記載した。さらなる利点の一例は、シリコングルマニウム能動領域の形成前にトレンチ分離領域の形成が可能であることによって、シリコングルマニウム領域におけるトレンチ分離領域の形成に必要となり得るような、これらのトレンチ分離領域の形成に必要とされる余分な開発が存在しないことである。

20

#### 【図面の簡単な説明】

#### 【0019】

【図 1】本発明の第 1 の実施形態による処理の第 1 の段階における半導体構造の断面図。

【図 2】処理の続く段階における図 1 の半導体構造の断面図。

【図 3】処理の続く段階における図 2 の半導体構造の断面図。

【図 4】処理の続く段階における図 3 の半導体構造の断面図。

30

【図 5】処理の続く段階における図 4 の半導体構造の断面図。

【図 6】処理の続く段階における図 5 の半導体構造の断面図。

【図 7】処理の続く段階における図 6 の半導体構造の断面図。

【図 8】処理の続く段階における図 7 の半導体構造の断面図。

【図 9】処理の続く段階における図 8 の半導体構造の断面図。

【図 10】処理の続く段階における図 9 の半導体構造の断面図。

【図1】

FIG. 1

【図2】

FIG. 2

【図3】

FIG. 3

【図4】

FIG. 4

【図5】

FIG. 5

【図7】

FIG. 7

【図6】

FIG. 6

【図8】

FIG. 8

【図9】

FIG. 9

【図10】

FIG. 10

## 【国際調査報告】

60700580015

## INTERNATIONAL SEARCH REPORT

International application No.

PCT/US05/11552

## A. CLASSIFICATION OF SUBJECT MATTER

IPC: H01L 21/31 (2006.01)

USPC: 438/758

According to International Patent Classification (IPC) or to both national classification and IPC

## B. FIELDS SEARCHED

Minimum documentation searched (classification system followed by classification symbols)

U.S. : 438/758,311,149,291,752,753,758,770,933 ; 257/411,582 ; H01L 21/00,21/336

Documentation searched other than minimum documentation to the extent that such documents are included in the fields searched

Electronic data base consulted during the international search (name of data base and, where practicable, search terms used)

## C. DOCUMENTS CONSIDERED TO BE RELEVANT

| Category * | Citation of document, with indication, where appropriate, of the relevant passages | Relevant to claim No. |

|------------|------------------------------------------------------------------------------------|-----------------------|

| X          | US 20040051140 A1 (BHATTACHARYYA) 18 March 2004 fig                                | 1-16,19-21            |

| X          | US 20030013305 A1 (SUGII et al) 16 Jan 2003 (16.01.2003) the whole document        | 22-23,25-26           |

| Y          | US 20030096490 A1 (BORLAND et al) 22 May 2003 (05.22.2003)<br>the whole document   | 1-16,19-23,25-26      |

Further documents are listed in the continuation of Box C. See patent family annex.

|                                        |                                                                                                                                                                                                                                              |

|----------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Special categories of cited documents: |                                                                                                                                                                                                                                              |

| "A"                                    | document defining the general state of the art which is not considered to be of particular relevance                                                                                                                                         |

| "B"                                    | earlier application or patent published on or after the international filing date                                                                                                                                                            |

| "L"                                    | document which may throw doubt on priority claim(s) or which is cited to establish the publication date of another citation or other special reason (as specified)                                                                           |

| "O"                                    | document referring to an oral disclosure, use, exhibition or other means                                                                                                                                                                     |

| "P"                                    | document published prior to the international filing date but later than the priority date claimed                                                                                                                                           |

| "T"                                    | later document published after the international filing date or priority date and not in conflict with the application but cited to understand the principle or theory underlying the invention                                              |

| "X"                                    | document of particular relevance; the claimed invention cannot be considered novel or cannot be considered to involve an inventive step when the document is taken alone                                                                     |

| "Y"                                    | document of particular relevance; the claimed invention cannot be considered to involve an inventive step when the document is combined with one or more other such documents, such combination being obvious to a person skilled in the art |

| "Z"                                    | document member of the same patent family                                                                                                                                                                                                    |

Date of the actual completion of the international search

02 March 2007 (02.03.2007)

Date of mailing of the international search report

29 MAR 2007

Name and mailing address of the ISA/US

Mail Stop PCT, Attn: ISA-US

Commissioner for Patents

P.O. Box 1450

Alexandria, Virginia 22313-1450

Facsimile No. (571) 273-3201

Authorized officer

Thinh T Nguyen *for Beal*

Telephone No. 571-272-1790

Form PCT/ISA/210 (second sheet) (April 2005)

29.8.2007

---

フロントページの続き

(81)指定国 AP(BW,GH,GM,KE,LS,MW,MZ,NA,SD,SL,SZ,TZ,UG,ZM,ZW),EA(AM,AZ,BY,KG,KZ,MD,RU,TJ,TM),EP(AT,BE,BG,CH,CY,CZ,DE,DK,EE,ES,FI,FR,GB,GR,HU,IE,IS,IT,LT,LU,MC,NL,PL,PT,RO,SE,SI,SK,TR),OA(BF,BJ,CF,CG,CI,CM,GA,GN,GQ,GW,ML,MR,NE,SN,TD,TG),AE,AG,AL,AM,AT,AU,AZ,BA,BB,BG,BR,BW,BY,BZ,CA,CH,CN,CO,CR,CU,CZ,DE,DK,DM,DZ,EC,EE,EG,ES,FI,GB,GD,GE,GH,GM,HR,HU,ID,IL,IN,IS,JP,KE,KG,KM,KP,KR,KZ,LK,LR,LS,L,T,LU,LV,MA,MD,MG,MK,MN,MW,MX,MZ,NA,NI,NO,NZ,OM,PG,PH,PL,PT,RO,RU,SC,SD,SE,SG,SK,SL,SM,SY,TJ,TM,TN,TR,TT,TZ,UA,UG,US,UZ,VC,VN,YU,ZA,ZM,ZW

(72)発明者 サダカ、マリアム ジー .

アメリカ合衆国 7 8 7 3 8 テキサス州 オースティン ナバ ドライブ 3 1 1 9

(72)発明者 ホワイト、テッド アール .

アメリカ合衆国 7 8 7 3 1 テキサス州 オースティン ローレルウッド ドライブ 6 5 0 8

F ターム(参考) 5F110 AA16 BB04 CC02 DD05 DD13 EE31 GG01 GG02 GG19 GG25

GG33 GG34 GG42 NN62

5F152 LM09 MM04 NN03 NN15 NN29 NQ03 NQ04

【要約の続き】

ゲルマニウムリッチシリコン(36, 38)を選択的に形成する。これに代えて、分離領域を用いて、ゲルマニウムリッチシリコンが形成される基板の局所的領域を画定する。