(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第5384483号

(P5384483)

(45) 発行日 平成26年1月8日(2014.1.8)

(24) 登録日 平成25年10月11日(2013.10.11)

(51) Int.Cl.

F 1

H03K 19/173 (2006.01)

H03K 19/173 101

G06F 17/50 (2006.01)

G06F 17/50 654M

H03K 17/00 (2006.01)

H03K 17/00 E

請求項の数 16 (全 14 頁)

(21) 出願番号 特願2010-510350 (P2010-510350)

(86) (22) 出願日 平成20年5月30日 (2008.5.30)

(65) 公表番号 特表2010-530660 (P2010-530660A)

(43) 公表日 平成22年9月9日 (2010.9.9)

(86) 國際出願番号 PCT/US2008/006831

(87) 國際公開番号 WO2008/150435

(87) 國際公開日 平成20年12月11日 (2008.12.11)

審査請求日 平成23年5月30日 (2011.5.30)

(31) 優先権主張番号 11/809,613

(32) 優先日 平成19年5月31日 (2007.5.31)

(33) 優先権主張国 米国(US)

(73) 特許権者 597035274

シノプシス、 インコーポレイテッド

S Y N O P S Y S, I N C.

アメリカ合衆国 カリフォルニア 940

43-4033, マウンテンビュー, イ

ースト ミドルフィールド ロード 70

0

(74) 代理人 100092093

弁理士 辻居 幸一

(74) 代理人 100082005

弁理士 熊倉 賢男

(74) 代理人 100067013

弁理士 大塚 文昭

(74) 代理人 100086771

弁理士 西島 孝喜

最終頁に続く

(54) 【発明の名称】マルチブレクサを設計する方法及び装置

## (57) 【特許請求の範囲】

## 【請求項1】

実行時に、データ処理システムが、

第1マルチブレクサの表現を受け取るステップと、

前記第1マルチブレクサの表現を前記第1マルチブレクサのパーティションニュートラル表現へと分解するステップであって、前記パーティションニュートラル表現は、(a)複数の3状態ドライバ、(b)ワイヤードORアレイ、又は(c)ワイヤードANDアレイの1つを含む、前記分解するステップと、

少なくとも1つの集積回路の部分の間で前記第1マルチブレクサのパーティションニュートラル表現をパーティション化して、前記パーティションニュートラル表現から複数の第2マルチブレクサを生成し、集積回路の第1の部分に前記複数の第2マルチブレクサの1つを配置し、集積回路の第2の部分に前記複数の第2マルチブレクサの他の1つを配置するステップと、

を備えた方法を遂行するようにさせる実行可能なプログラムインストラクションを含むマシン読み取り可能な記憶媒体。

## 【請求項2】

前記複数の第2マルチブレクサは、第1サブセットのマルチブレクサ及び第2サブセットのマルチブレクサを含み、第1サブセットのマルチブレクサは、集積回路(I C)の第1部分に配置されるように設計されると共に、第2サブセットのマルチブレクサは、I Cの第2部分に配置されるように設計され、第1サブセットは、1つ以上のマルチブレクサ

を含み、そして第2サブセットは、1つ以上のマルチプレクサを含む、請求項1に記載の記憶媒体。

**【請求項3】**

前記第1マルチプレクサの表現は、RTLネットリスト内のレジスタ転送レベル(RTL)形態にあり、そして前記変換は、自動的に遂行される、請求項1に記載の記憶媒体。

**【請求項4】**

前記方法は、前記第1マルチプレクサのデコードロジックを複製するステップを更に備えた、請求項1に記載の記憶媒体。

**【請求項5】**

第1マルチプレクサの表現を受け取るステップと、

10

前記第1マルチプレクサの表現を前記第1マルチプレクサのパーティションニュートラル表現へと分解するステップであって、前記パーティションニュートラル表現は、(a)複数の3状態ドライバ、(b)ワイヤードORアレイ、又は(c)ワイヤードANDアレイの1つを含む、前記分解するステップと、

少なくとも1つの集積回路の部分の間で前記第1マルチプレクサのパーティションニュートラル表現をパーティション化して、前記パーティションニュートラル表現から複数の第2マルチプレクサを生成し、集積回路の第1の部分に前記複数の第2マルチプレクサの1つを配置し、集積回路の第2の部分に前記複数の第2マルチプレクサの他の1つを配置するステップと、

を備えたマシン具現化方法。

20

**【請求項6】**

第1マルチプレクサの表現を受け取る手段と、

前記第1マルチプレクサの表現を前記第1マルチプレクサのパーティションニュートラル表現へと分解する手段であって、前記パーティションニュートラル表現は、(a)複数の3状態ドライバ、(b)ワイヤードORアレイ、又は(c)ワイヤードANDアレイの1つを含む、前記分解する手段と、

少なくとも1つの集積回路の部分の間で前記第1マルチプレクサのパーティションニュートラル表現をパーティション化して、前記パーティションニュートラル表現から複数の第2マルチプレクサを生成し、集積回路の第1の部分に前記複数の第2マルチプレクサの1つを配置し、集積回路の第2の部分に前記複数の第2マルチプレクサの他の1つを配置する手段と、

を備えたマシン。

30

**【請求項7】**

実行時に、データ処理システムが、

出力を有する第1マルチプレクサの表現を受け取るステップと、

前記第1マルチプレクサの表現を第2マルチプレクサの複数の表現へと分解するステップであって、第2マルチプレクサは、前記第1マルチプレクサの出力に一致する共通出力において、第2マルチプレクサとその共通の出力との間にマルチプレクサを介在せずに、一緒に結合されるようなステップと、

前記第2マルチプレクサを少なくとも1つの集積回路の部分と部分との間でパーティション化し、集積回路の第1の部分に前記複数の第2マルチプレクサの1つを配置し、集積回路の第2の部分に前記複数の第2マルチプレクサの他の1つを配置するステップと、

を備えた方法を遂行するようにさせる実行可能な実行可能なプログラムインストラクションを含むマシン読み取り可能な記憶媒体。

40

**【請求項8】**

前記第2マルチプレクサの複数の表現は、前記第1マルチプレクサのパーティションニュートラル形態である、請求項7に記載の記憶媒体。

**【請求項9】**

出力を有する第1マルチプレクサの表現を受け取るステップと、

前記第1マルチプレクサの表現を第2マルチプレクサの複数の表現へと分解するステッ

50

プであって、第2マルチブレクサは、前記第1マルチブレクサの出力に一致する共通出力において、第2マルチブレクサとその共通の出力との間にマルチブレクサを介在せずに、一緒に結合されるようなステップと、

前記第2マルチブレクサを少なくとも1つの集積回路の部分と部分との間でパーティション化し、集積回路の第1の部分に前記複数の第2マルチブレクサの1つを配置し、集積回路の第2の部分に前記複数の第2マルチブレクサの他の1つを配置するステップと、を備えたマシン具現化方法。

#### 【請求項10】

出力を有する第1マルチブレクサの表現を受け取る手段と、

前記第1マルチブレクサの表現を第2マルチブレクサの複数の表現へと分解する手段であって、第2マルチブレクサは、前記第1マルチブレクサの出力に一致する共通出力において、第2マルチブレクサとその共通の出力との間にマルチブレクサを介在せずに、一緒に結合されるような手段と、

前記第2マルチブレクサを少なくとも1つの集積回路の部分と部分との間でパーティション化し、集積回路の第1の部分に前記複数の第2マルチブレクサの1つを配置し、集積回路の第2の部分に前記複数の第2マルチブレクサの他の1つを配置する手段と、を備えたマシン。

#### 【請求項11】

実行時に、データ処理システムが、

N入力加算器であるパーティションニュートラル分解を行うことのできる第1ロジックコンポーネントの表現を受け取るステップと、

前記第1ロジックコンポーネントの表現を、前記N入力加算器をワイヤーのバスとして表現するパーティションニュートラル表現へと分解するステップと、

少なくとも1つの集積回路の部分の間で前記パーティションニュートラル表現をパーティション化して前記パーティションニュートラル表現から複数のロジックコンポーネントを生成し、集積回路の第1の部分に前記複数のロジックコンポーネントの1つを配置し、集積回路の第2の部分に前記複数のロジックコンポーネントの他の1つを配置し、前記複数のロジックコンポーネントが共に結合されて前記第1ロジックコンポーネントの結果を与えるステップと、

を備えた方法を遂行するようにさせる実行可能なプログラムインストラクションを含むマシン読み取り可能な記憶媒体。

#### 【請求項12】

前記方法は、前記第1マルチブレクサの選択ラインを駆動するロジックを含むように前記第1マルチブレクサのデコードロジックを拡張することを更に含む、請求項1に記載の記憶媒体。

#### 【請求項13】

前記拡張は、前記変換の前に行われ、更に、前記拡張は、複製されるべき制御ロジックを定義するようにカットされた信号を含む、請求項12に記載の記憶媒体。

#### 【請求項14】

前記第1マルチブレクサの選択ラインを駆動するロジックを含むように前記第1マルチブレクサのデコードロジックを拡張することを更に含む、請求項5に記載の方法。

#### 【請求項15】

前記拡張は、前記変換の前に行われ、更に、前記拡張は、複製されるべき制御ロジックを定義するようにカットされた信号を含む、請求項14に記載の方法。

#### 【請求項16】

前記方法は、各パーティション内のパーティションニュートラル表現をRTL(レジスタ転送レベル)コンポーネントへと変換することを更に含む、請求項1に記載の記憶媒体。

【発明の詳細な説明】

#### 【技術分野】

10

20

30

40

50

**【0001】**

本発明は、一般的に、集積回路設計の分野に係り、より詳細には、回路のハードウェア記述言語での記述のような集積回路の記述を使用することで開始する合成プロセスのようなマシン具現化自動プロセスによる集積回路の設計に係る。

**【背景技術】****【0002】**

VLSI（超大規模集積）技術の規模で回路を設計する場合、設計者は、コンピュータ支援設計技術をしばしば利用する。複雑なデジタル又はアナログ回路のような複雑な回路の設計及びシミュレーションを支援するように回路を記述するために、ハードウェア記述言語（HDL）のような標準言語が開発されている。VHDL及びVerilogのような多数のハードウェア設計言語が工業標準として進化してきた。VHDL及びVerilogは、アブストラクトデータ形式を使用して、ゲートレベル、レジスタ転送レベル（RTL）又は振舞いレベルでハードウェアモデルを定義できるようにする汎用ハードウェア記述言語である。装置技術が進歩し続けるにつれて、より新しい装置及び設計スタイルで使用するようにHDLを適応させるために種々の製品設計ツールが開発されている。

10

**【0003】**

HDLコンパイラーを使用して回路を設計するときに、設計者は、HDLソースコードで回路エレメントを記述し、次いで、ソースコードをコンパイルして、合成RTLネットリストを作成することがしばしばある。RTLネットリストは、回路エレメントの概略表現に対応する。合成功回路エレメントを含む回路は、タイミング関係を改善し且つ不必要的又は冗長なエレメントを排除するようにしばしば最適化される。このような最適化は、典型的に、異なるゲート形式に置き換えるか、或いは回路内でゲートを結合し排除することを含む。RTLネットリストのようなRTL記述を、フィールドプログラマブルゲートアレイ（FPGA）のターゲットアーキテクチャーのような集積回路の特定の所定アーキテクチャーへマッピングする前に、最適化を行うことができる。この技術で知られているように、FPGAの異なるベンダーは、ファンクションを具現化するための特定の集積回路がベンダーごとに相違し得るという点で、しばしば異なるアーキテクチャーを有する。独特のアーキテクチャーを有するFPGAのベンダーは、例えば、Xilinx及びAlteraである。集積回路のコンピュータ支援設計のための種々の方法及びシステムが米国特許第6,438,735号、第6,449,762号、及び第6,973,632号に説明されており、これらは、全て、参考としてここに援用する。

20

**【0004】**

2つ以上のFPGA集積回路のような2つ以上の集積回路で設計を具現化することがしばしば望まれる。これは、単一のFPGA上の利用可能リソースには適合できないほど設計が複雑で且つ大規模なときにしばしば必要となる。又、これは、ASIC（特定用途向け集積回路）の設計にも有用である。益々多くのASIC設計者が、多数のFPGAで設計を具現化することにより、それらの設計をしばしば試作しテストしている。ASIC設計の複雑さは、設計に必要な全てのファンクションを具現化するのに多数のFPGAが要求されることもある程である。これは、設計者がそれらの設計を多数のFPGAにパーティション化するよう努力しなければならないことを意味し、これを行うために従来技術には多数のツール及び方法が存在する。自動プロセスを通じてパーティション化するための技術が、例えば、米国特許第6,438,735号に説明されており、これは、設計を複数のFPGAへパーティション化するための他の従来技術も説明している。RTLコンポーネントレベルで自動パーティション化を遂行するソフトウェアツールは、例えば、カリフォルニア州サンベールのシンプリシティ社からの製品Certifyである。技術的にマップされたネットリストレベルで自動パーティション化を遂行するツールは、例えば、オースピー・デベローペメント社からのAuspy Partition System IIである。

30

**【0005】**

パーティション化のための既存の技術でも、大きな幅を有し且つ潜在的に多数の入力が

40

50

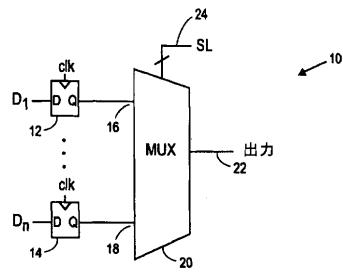

あってその1つが選択されて出力となるようなマルチプレクサ（MUX）をパーティション化することは困難である。マルチプレクサは、良く知られた回路エレメントであり、マルチプレクサの一例が図1Aに示されている。図1Aは、クロックされたデータをマルチプレクサ20の入力16及び18へと駆動させるデータドライバ12及び14を備えた回路10を示す。マルチプレクサ20への入力は、2つ以上あってもよいことが明らかである。例えば、データドライバによりマルチプレクサ20へ各自駆動される20個の入力があってもよい。マルチプレクサ20は、その出力22に出力値を発生し、この出力値は、マルチプレクサがその出力22へ接続するために入力の1つを選択するようにさせる選択ライン24に生じるデータにより決定される。

## 【0006】

10

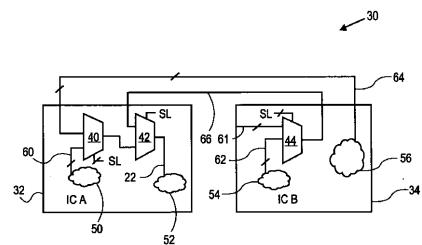

大きなマルチプレクサをパーティション化するには、典型的に、少なくとも3つの小さなマルチプレクサを生成する必要がある。これら小さなマルチプレクサの2つは、2つの異なる入力グループから各自1つの入力を選択する（2つの選択された入力を発生する）ように作用し、それら2つの選択された入力は、次いで、第3のマルチプレクサにより選択される。図1B及び1Cは、大きなマルチプレクサを3つの小さなマルチプレクサへとパーティション化する一例を示す。

## 【0007】

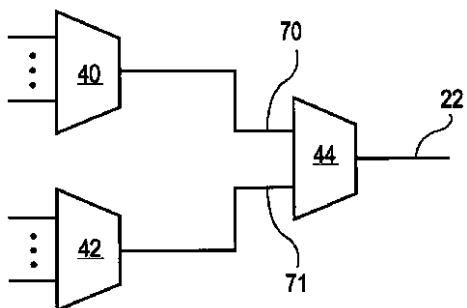

図1Bに示す設計30の場合には、マルチプレクサは、2つの異なる集積回路32及び34において3つのマルチプレクサ40、42及び44へとパーティション化されている。2つの異なる集積回路上のマルチプレクサは、マルチラインバス64及びワイヤ66により一緒に結合される。マルチプレクサ40及び44は、実際には、オリジナルマルチプレクサへの2つの異なる入力グループ間を選択して、2つの出力を与え、これらの出力がマルチプレクサ42によって選択される。各マルチプレクサは、この技術で知られたようにマルチプレクサの対応出力へ接続されるべき入力を選択する選択ロジック又は選択ラインの制御のもとにある。選択ラインは、典型的に、この技術で知られたように、デコードロジックによって駆動される。図1Bに示すように、ロジック50及び56は、マルチプレクサ40へ入力を与え、一方、ロジック54は、バス62（複数のラインを含む）を経て、マルチプレクサ44へ入力を与える。又、マルチプレクサ44は、バス61（複数のラインを含む）から別の入力も受け取る。ロジック50は、バス60を通してマルチプレクサ40へ結合され、そしてロジック56は、バス64を通してマルチプレクサ40へ結合される。マルチプレクサ40の出力は、マルチプレクサ42の入力の1つへ結合され、そしてマルチプレクサ44の出力は、マルチプレクサ42の他方の入力として結合され、このマルチプレクサは、これら2つの入力間を選択して、ライン22を経てその出力を駆動し、ロジック52を駆動する。マルチプレクサ40、42及び44の各自に対して、各データ入力及び各データ出力はバス（複数のラインを含む）であり、そしてマルチプレクサによるスイッチングは、入力バス間を切り換える。図1Bに示す例は、種々のロジックエレメント及びマルチプレクサを2つ以上の集積回路間に配列し又はパーティション化する種々の仕方の1つであることが明らかであろう。しかしながら、各々の場合に、パーティション化されたマルチプレクサにより具現化されるロジックを保存するために、マルチプレクサ42を駆動する入力を、マルチプレクサ42に対して一緒にグループ編成しなければならない。換言すれば、マルチプレクサ42を駆動する入力は、マルチプレクサ40又は44を駆動するのに使用できず、むしろ、パーティション化されたマルチプレクサの適切な論理的ファンクションを維持してオリジナルマルチプレクサと同じ論理的マルチプレクシングを与えるためにはマルチプレクサツリーにおける最後のマルチプレクサを駆動するのに使用されねばならない。図1Cは、複数の集積回路の複雑さを伴わずにこの関係を示している。特に、入力70及び72は、マルチプレクサ44によりパーティション化されねばならない。ここでは、例えば、入力70及び71のためのドライバは、マルチプレクサ44でパーティション化されねばならない。これは、パーティション化動作を複雑化する傾向がある。

## 【発明の概要】

20

30

40

50

**【発明が解決しようとする課題】**

**【0008】**

チップへのパーティション化の前に大きなマルチプレクサを含む回路においてロジック合成が遂行される場合には、それにより得られる回路が、ロジック合成システムによって選択されるマルチプレクサ分解に基づきマルチプレクサのドライバをグループ編成する。多数の異なる分解が考えられ、即ち小さなマルチプレクサのツリー、アンド・オア分解、及びFPGA特定コンポーネントを使用した特殊目的分解が考えられる。分解されたマルチプレクサがチップにわたってパーティション化される場合は、選択される分解により、パーティション間の過剰な相互接続使用が生じ得る。他方、マルチプレクサが分解される前にパーティション化が行われる場合は、マルチプレクサに接続される全ての信号が单一のチップ内で使用できねばならず、これも、パーティション間に過剰な相互接続を引き起こすことになる。部分的な解決策は、マルチプレクサコンポーネントを単一ビット巾のマルチプレクサへスライスすることである。この部分的解決策は、Certifyで具現化されている。これは、多数の入力をもつマルチプレクサをパーティション化する上で助けとならず、又、スライスにわたり共有されるマルチプレクサのためのデコーディングロジックに伴う異なるパーティション化の問題を生じさせる。従って、マルチプレクサの分解及びパーティション化の同時解決策が必要とされる。10

**【課題を解決するための手段】**

**【0009】**

本発明は、集積回路を設計するための方法及び装置を開示する。本発明の1つの態様によれば、集積回路を設計するためのここに例示する方法は、第1マルチプレクサの表現を受け取り、その第1マルチプレクサの表現を第1マルチプレクサのパーティションニュートラル表現へと変換し、そしてその第1マルチプレクサのパーティションニュートラル表現をパーティション化して、複数の第2マルチプレクサを生成することを含む。一実施形態の1つの具現化において、複数の第2マルチプレクサは、第1サブセットのマルチプレクサ及び第2サブセットのマルチプレクサを含み、第1サブセットのマルチプレクサは、第1集積回路に配置されるように設計されると共に、第2サブセットのマルチプレクサは、第2集積回路に配置されるように設計され、第1サブセットは、1つ以上のマルチプレクサを含み、そして第2サブセットは、1つ以上のマルチプレクサを含む。他の具現化において、複数の第2マルチプレクサは、第1サブセットのマルチプレクサ及び第2サブセットのマルチプレクサを含み、第1サブセットのマルチプレクサは、集積回路の第1部分に配置されるように設計されると共に、第2サブセットのマルチプレクサは、集積回路の第2部分に配置されるように設計される。第1マルチプレクサの表現は、RTLネットリスト内のレジスタ転送レベル(RTL)形態にあり、そして変換は、人間の介在なしにマシンにより自動的に遂行される。少なくとも幾つかの実施形態において、パーティションニュートラル表現は、(a)複数の3状態ドライバ、(b)ワイヤードORアレイ、又は(c)ワイヤードANDアレイ、の1つ以上を含む。少なくとも幾つかの実施形態において、この方法は、更に、集積回路の記述をHDLでコンパイルして第1マルチプレクサの表現を生成することを含み、そしてこの方法は、更に、第2マルチプレクサの選択ラインを与えるために第1マルチプレクサのデコードロジックを複製することを含む。203040

**【0010】**

本発明の別の態様によれば、ここに例示する方法は、出力を有する第1マルチプレクサの表現を受け取り、第1マルチプレクサの表現を第2マルチプレクサの複数の表現へと分解し、第2マルチプレクサは、第1マルチプレクサの出力に一致する共通出力において、第2マルチプレクサとその共通の出力との間にマルチプレクサを介在せずに、一緒に結合され、そして第2マルチプレクサを少なくとも1つの集積回路の部分間でパーティション化することを含む。少なくとも幾つかの実施形態では、第2マルチプレクサの複数の表現は、第1マルチプレクサのパーティションニュートラル形態である。パーティション化は、複数の集積回路間で行われてもよいし、又は同じ集積回路の間取り部分のような異なる部分間で行われてもよい。少なくとも幾つかの実施形態では、第1マルチプレクサの表現50

は、R T Lネットリスト内のレジスタ転送レベル形態にあり、そして分解は、人間の介在なしにマシンにより自動的に遂行される。少なくとも幾つかの実施形態において、第2マルチプレクサの複数の表現は、(a)複数の3状態ドライバ、(b)ワイヤードORアレイ、又は(c)ワイヤードANDアレイ、の1つ以上の形態にある。本発明の幾つかの実施形態は、マルチプレクサに関して説明するが、パーティションニュートラル分解を受け容れるいかなるコンポーネントに適用することもできる。例えば、N入力の加算器は、そのドライバの値を加算するワイヤのアブストラクトバスとして表現することができる。Nが2より大きいとすれば、N入力の加算器は、パーティション化の前にこのようなバスへと分解される。パーティション化の後に、加算器の複数の入力が同じパーティションにある場合には、これらの入力がM入力R T L加算器へとリフォームされ、ここで、Mは、そのパーティションにおけるオリジナル加算器入力の数である。加算器の推定エリアをそのドライバへ分配することにより、パーティション化のためのエリアの良好な近似をなすことができる。パーティション化ソフトウェアは、最終的な和が生じる行先パーティションにおいて入力カウントを考慮するために若干の変更を必要とする。というのは、それが、ソースパーティションの出力カウントの和に等しい入力カウントを有するからである。マルチプレクサのパーティション化と同様に、同時の分解及びパーティション化解決策は、ワイヤ本数を著しく減少することができる。

#### 【0011】

又、本発明は、本発明の1つ以上の実施形態に基づいて集積回路を設計することのできるデジタル処理システムのような装置も開示する。又、本発明は、データ処理システムのようなマシンがここに述べる1つ以上的方法を実行するようにさせることでここに述べる方法に基づいて集積回路を設計するのに使用できるコンピュータ読み取り可能な媒体又はマシン読み取り可能な媒体のような装置も開示する。

#### 【0012】

本発明の他の特徴は、添付図面及び以下の詳細な説明から明らかとなろう。

#### 【0013】

本発明は、同様の要素が同じ参照番号で示された添付図面に一例として示されるが、これに限定されない。

#### 【図面の簡単な説明】

#### 【0014】

【図1A】マルチプレクサを含む回路の一例を示す。

【図1B】単一のマルチプレクサを複数のマルチプレクサへパーティション化することにより生じる1セットのマルチプレクサの構成例を示す。

【図1C】1つのマルチプレクサを複数のマルチプレクサへパーティション化することにより生じる1セットのマルチプレクサの別の例を示す。

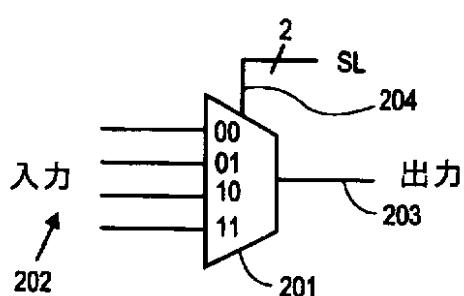

【図2A】本発明の一実施形態によりパーティション化される前のマルチプレクサの一例を示す。

【図2B】本発明の一実施形態によるマルチプレクサのパーティションニュートラル形態の一例を示す。

【図2C】図2Bに示されたパーティションニュートラルマルチプレクサをパーティション化した結果の一例を示すもので、図2Cに示すパーティションは、2つの集積回路にわたっている。別の実施形態では、パーティションは、同じ集積回路の部分、例えば、同じ集積回路の間取り部分にわたってもよい。

#### 【図3】本発明の一実施形態による方法を例示するフローチャートである。

#### 【図4】本発明の一実施形態によるマシン読み取り可能な媒体の一例を示す。

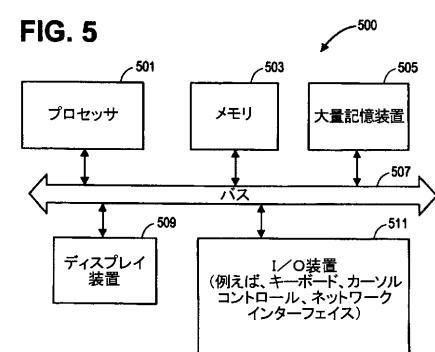

【図5】本発明の1つ以上の実施形態を具現化するのに使用できるデータ処理システムのブロック図である。

#### 【発明を実施するための形態】

#### 【0015】

集積回路又は複数の集積回路を設計するための方法及び装置をここに開示する。以下の

10

20

30

40

50

説明において、説明上、本発明を完全に理解するために多数の特定の細部について述べる。しかしながら、当業者であれば、本発明は、これらの特定の細部を伴わずに実施できることが明らかであろう。他の点について、良く知られた構造、プロセス及び装置は、過度な細部を伴わずに説明をなすために、ブロック図で示すか又は概略を述べる。

#### 【0016】

本発明の幾つかの実施形態の一般的な例を、図2A、2B及び2Cを参照して、以下に説明する。本発明の多数の実施形態は、HDL設計合成ソフトウェアに使用するよう意図されるが、本発明は、必ずしもこのような用途に限定されない。他の言語及びコンピュータプログラムの使用も考えられるが、本発明の実施形態は、HDL合成システム、特に、FPGAのベンダー特有アーキテクチャーのようなベンダー特有テクノロジー/アーキテクチャーを有する集積回路に使用するように設計されたもの、に関して説明される。しかしながら、本発明のある実施形態は、他の形式の集積回路、例えば、ASICにも使用できることが理解されよう。10

#### 【0017】

図2Aは、4つの入力202を有し且つ出力203を与えるマルチプレクサ201を示す。動作に際し、マルチプレクサ201は、4つの入力のうちの1つを、出力203を駆動するのに使用される入力として選択する。特定入力の選択は、この技術で知られたようにデコードロジックにより典型的に駆動される選択ライン204の制御のもとにある。本発明の少なくとも幾つかの実施形態によれば、マルチプレクサ201は、マルチプレクサのオリジナル表現より容易にパーティション化できる表現を与えるために、単一のマルチプレクサとしてのその初期表現から、そのマルチプレクサのパーティションニュートラル表現へと変換又は分解される。20

#### 【0018】

図2Bは、オリジナルマルチプレクサ201のパーティションニュートラル表現の一例を示す。この特定のパーティションニュートラル表現は、オリジナルマルチプレクサの出力203を与えるために共通の出力において3状態ドライバの出力を結合することにより形成される。3状態ドライバの各々は、オリジナルの4つの入力202の1つを受け取り、又、3状態ドライバの各々は、イネーブル入力を含み、これは、対応するデコードロジックに結合される。その対応するデコードロジックは、次いで、デコードロジックに入力を与えるオリジナル選択ライン204の全部又はサブセットに結合される。図2Bに示すように、3状態ドライバ217は、00入力を受け取り、そして3状態ドライバ217のイネーブル入力を通してデコードロジック225に結合される。同様に、3状態ドライバ215は、入力01を受け取り、そして3状態ドライバ215のイネーブル入力を経てデコードロジック227に結合される。3状態ドライバ213は、10入力を受け取るように結合され、そして3状態ドライバ213のイネーブル入力を経てデコードロジック229へ結合され、又、3状態ドライバ211は、入力11に結合されると共に、3状態ドライバ211のイネーブル入力を経てデコードロジック231にも結合される。全部で4つのこれら3状態ドライバの出力は、一緒に結合されて、出力203を与える。30

#### 【0019】

各3状態ドライバのためのデコードロジックは、3状態ドライバの1つだけがその出力を駆動する一方、他の3状態ドライバは、対応するデコードロジックに結合されたイネーブル入力により高インピーダンス状態にセットされるように具現化される。例えば、選択ラインが、マルチプレクサによる出力として00入力を選択すべきであると指定する場合には、デコードロジック225は、3状態ドライバ217をセットして、3状態ドライバ217の入力がその出力、ひいては、出力203を駆動するようとする。というのは、他の全ての3状態ドライバ215、213及び211がそれらのイネーブル入力をセットして、それらの出力が高インピーダンス状態になるようとするからである。例えば、デコードロジック227は、3状態ドライバ215のイネーブル入力が3状態ドライバ215の出力を高インピーダンス状態にセットするようにさせる。同様に、デコードロジック229及びデコードロジック231は、各々、3状態ドライバ213及び211に対して同様4050

の状態を生じさせる。これは、3状態ドライバ217からの出力が、出力203を駆動できるようにする。

#### 【0020】

このパーティションニュートラル設計では、自動設計システムは、入力をマルチプレクサの特定部分と一致させることに関して心配する必要がない。デコードロジックは、従来技術と同様、デコードする入力を考慮し続けねばならないが、これは、従来技術と相違がない。図2Bに示す形態のようなこのパーティションニュートラル表現は、異なる集積回路間、又は図2Cに示す同じ集積回路の異なる部分間に分散される複数のマルチプレクサへと分解することができる。これらの分散されたマルチプレクサの出力は、オリジナルマルチプレクサの出力に一致する共通出力において、パーティション化されたマルチプレクサとその共通出力との間にマルチプレクサを介在させずに、一緒に結合されることが明らかである。換言すれば、第1レベルのマルチプレクサからの出力とマルチプレクサのツリーからの最終出力との間にマルチプレクサを介在するようなマルチプレクサのツリーはない。これは、ツリーに類似した図1Cに示すマルチプレクサのセットを、以下に述べる図2Cに示すマルチプレクサのセットと比較することにより、明らかとなる。

10

#### 【0021】

図2Cは、図2Bに示すマルチプレクサのパーティションニュートラル表現を2つの集積回路251と253との間でパーティション化する一例を示す。3状態ドライバ217及び215は、それに対応するデコードロジックと共に、集積回路251に配置され、そして集積回路251のロジック261により駆動される。同時に、3状態ドライバ213及び211は、それに対応するデコードロジックと共に、集積回路253に配置され、又、3状態ドライバ213及び211に入力を与えるロジック263も配置される。全部で4つの3状態ドライバの出力は、2つの集積回路の外部で、これら2つの集積回路を結合するプリント回路板（又は他の基板）上のワイヤで一緒に結合されて、出力203を与える。この出力は、次いで、設計に基づき、1つ以上の集積回路へ戻されて、付加的なロジックを駆動する。少なくとも幾つかの実施形態では、集積回路の境界に通常存在する3状態ドライバ、例えば、集積回路のボンディングパッドを駆動する3状態ドライバを使用して、マルチプレクサのパーティションニュートラル表現を具現化できることが明らかであろう。特に、種々の集積回路上の充分な入力／出力ピンがこのような用途に利用できる場合には、集積回路の境界の3状態ドライバを使用してパーティションニュートラル表現を形成することができる。

20

#### 【0022】

ワイヤードORアレイ又はワイヤードANDアレイを使用してマルチプレクサのパーティションニュートラル表現を具現化することのできる別のパーティションニュートラル表現もあることが明らかであろう。

30

#### 【0023】

マルチプレクサのデコードロジックは、マルチプレクサの制御ラインに供給するロジックを含むように拡張することができる。これは、マルチプレクサの制御ラインに直結される信号の数より手前のロジックを通してカットされる信号が狭いとき、又は新たなカットを他のマルチプレクサと共有できるときに、特に効果的である。従って、この新たな潜在的により狭い又はより多くの共有カットのブール関数により各入力がイネーブルされる。マルチプレクサのパーティションニュートラル分解形態が生成されると、分解の各断片が、必要な制御信号に接続して、ブール関数を桁上げする。ほとんどの場合、制御又はデコードロジックを複数のパーティションへと複製するエリアオーバーヘッドは、パーティション間で送信されねばならない制御信号の数を減少することによりパーティション間の相互接続部に得られる節約よりも重要度が著しく低い。

40

#### 【0024】

図3は、本発明の一実施形態による方法の一例を示す。オペレーション301において、回路設計の表現が生成される。例えば、表現は、回路設計のHDL記述を、少なくとも1つのマルチプレクサを含むRTLネットリストへコンパイルすることによって生成され

50

る。オペレーション 303 では、マルチブレクサが、マルチブレクサのパーティションニュートラル形態へと変換される。例えば、マルチブレクサは、その RTL 形態から、3 状態ドライバを使用してパーティションニュートラル形態をもつマルチブレクサを生成する形態へと変換される。任意であるが、集積回路の境界にある 3 状態ドライバを使用して、この形態を具現化してもよい。他の実施形態では、ワイヤード OR アレイ又はワイヤード AND アレイを使用して、マルチブレクサのパーティションニュートラル形態を具現化してもよい。オペレーション 305において、マルチブレクサのパーティションニュートラル形態は、複数のマルチブレクサへとパーティション化されて、マルチブレクサを、異なる集積回路上に配置するか、又は同じ集積回路の異なる部分、例えば、同じ集積回路の異なる間取りエリアに配置することができるようになる。次いで、オペレーション 307において、パーティション化されたマルチブレクサに対してデコードロジックが複製される。それに続くオペレーション 307 では、回路の配置及びルーティングが、他のオペレーション、例えば、最適化オペレーションや、RTL をテクノロジーに依存するアーキテクチャー、例えば、フィールドプログラマブルゲートアレイ集積回路のような集積回路のターゲットアーキテクチャーへとマッピングすることを含むオペレーションと共に、遂行することができる。

10

#### 【0025】

図 4 は、本発明の 1 つ以上的方法を具現化するのに使用できるマシン読み取り可能な媒体又はコンピュータ読み取り可能な媒体の一例を示す。例えば、マシン読み取り可能な媒体は、データ処理システムにより実行されたときに、データ処理システムが、ここに述べる 1 つ以上の方法を遂行するようにさせる実行可能なコンピュータプログラムインストラクションを含む。マシン又はコンピュータ読み取り可能な媒体は、CD-ROM 又は DVD-ROM 又は磁気ハードディスク又は他のディスク或いは記憶装置に配置することができる。媒体は、複数のコンポーネント、及び図 4 の媒体 400 には示されない他のコンポーネントを含んでもよい。図 4 に示す例では、設計のための HDL ソース記述がコード 401 として示されている。HDL コンパイラ 403 は、HDL ソースを、例えば、テクノロジーに依存する RTL ネットリスト 405 へとコンパイルする実行可能なプログラムインストラクションを含む。パーティション化ルーチン 407 を使用して、設計の種々のコンポーネントが複数の集積回路にわたってパーティション化されるように、テクノロジー独立の RTL ネットリストをパーティション化することができる。パーティション化ルーチンは、パーティションニュートラル変換ルーチン 409 を含むか又は呼び出すことができ、このルーチン 409 は、図 3 に示すような方法を具現化するもので、マルチブレクサのパーティションニュートラル形態を生成し、次いで、その形態を、複数の集積回路にわたって、或いは同じ集積回路の複数の部分、例えば、同じ集積回路の複数の間取り部分にわたって複数のマルチブレクサへとパーティション化することができる。媒体 400 は、テクノロジーマッピングルーチン 413 を更に含み、これは、パーティション化されたテクノロジー独立の RTL ネットリストから、パーティション化された設計を、テクノロジーに依存するネットリストへとマップし、このネットリストは、次いで、従来の配置及びルーティングツールを通して処理されて、特定集積回路ベンダーのターゲットアーキテクチャー、例えば、Xilinx の FPGA のターゲットアーキテクチャーに対する最終的なネットリスト又は設計を生成することができる。媒体 400 は、最適化ルーチン 411 を更に含み、これは、設計を、それがパーティション化された後又はそれがパーティション化される前に、最適化するのに使用できる。

20

30

40

#### 【0026】

図 5 は、媒体 400 を使用して、ここに述べる 1 つ以上的方法を遂行することのできるデータ処理システムの一例を示す。データ処理システム 500 は、1 つ以上のプロセッサ 501 を備え、これは、バス 507 を経てメモリ 503 へ結合される。プロセッサ 501 及びメモリ 503 は、大量記憶装置 505 にも結合され、これは、ハードディスク或いは他の不揮発性又は揮発性記憶装置を表す。一実施形態において、大量記憶装置は、図 4 に示す媒体 400 を含む磁気ハードドライブでよい。又、データ処理システムは、ディスプ

50

レイ装置 509、及び 1 つ以上の入力装置 511 も備え、入力装置は、例えば、キーボード、カーソル制御装置、及びネットワークインターフェイス、例えば、イーサネットインターフェイス又はワイヤレスインターフェイスを含む。図 5 に示すデータ処理装置のアーキテクチャーは、例示の目的で設けられたものに過ぎず、本発明に関連して使用されるコンピュータシステム又は他のデータ処理システムは、この特定のアーキテクチャーに限定されないことが明らかであろう。

#### 【 0 0 2 7 】

以上、本発明は、その特定の実施形態を参照して説明された。特許請求の範囲に規定された本発明の広い精神及び範囲から逸脱せずに種々の変更がなされることが明らかであろう。従って、明細書及び添付図面は、例示のためのもので、それに限定するためのものではない。

10

#### 【 符号の説明 】

#### 【 0 0 2 8 】

201 : マルチプレクサ

202 : 入力

203 : 出力

204 : 選択ライン

211、213、215、217 : 3 状態ドライバ

225、227、229 : デコードロジック

20

251、253 : 集積回路

261、263 : ロジック

401 : 設計のための H D L ソース記述

403 : H D L コンパイラー

405 : テクノロジー独立の R T L ネットリスト

407 : パーティション化ルーチン

409 : パーティションニュートラル変換ルーチン

411 : 最適化ルーチン

413 : テクノロジーマッピングルーチン

501 : プロセッサ

30

503 : メモリ

505 : 大量記憶装置

507 : バス

509 : ディスプレイ装置

511 : I / O 装置

【図 1 A】

FIG. 1A

【図 1 B】

FIG. 1B

【図 1 C】

FIG. 1C

【図 2 A】

FIG. 2A

【図 2 B】

FIG. 2B

【図2C】

FIG. 2C

【図3】

FIG. 3

【図4】

FIG. 4

【図5】

FIG. 5

---

フロントページの続き

(74)代理人 100109070

弁理士 須田 洋之

(74)代理人 100109335

弁理士 上杉 浩

(74)代理人 100141553

弁理士 鈴木 信彦

(72)発明者 マケルヴェイン ケニス エス

アメリカ合衆国 カリフォルニア州 94025 メンロ パーク メイ ブラウン アベニュー

1160

審査官 柳下 勝幸

(56)参考文献 特開2000-036737(JP,A)

(58)調査した分野(Int.Cl., DB名)

H03K 19/173

G06F 17/50

H03K 17/00