등록특허 10-2722474

(19) 대한민국특허청(KR)

(12) 등록특허공보(B1)

(45) 공고일자 2024년10월25일

(11) 등록번호 10-2722474

(24) 등록일자 2024년10월23일

- (51) 국제특허분류(Int. Cl.)

*G01N 23/201* (2018.01) *G01B 15/00* (2006.01)

*G01N 23/20* (2018.01) *G03F 7/20* (2006.01)

*H01L 21/66* (2006.01) *H01L 21/67* (2006.01)

- (52) CPC특허분류

*G01N 23/201* (2013.01)

*G01B 15/00* (2023.02)

- (21) 출원번호 10-2023-7021732(분할)

- (22) 출원일자(국제) 2018년05월29일

심사청구일자 2023년06월27일

- (85) 번역문제출일자 2023년06월27일

- (65) 공개번호 10-2023-0098728

- (43) 공개일자 2023년07월04일

- (62) 원출원 특허 10-2019-7038446

원출원일자(국제) 2018년05월29일

심사청구일자 2021년05월28일

- (86) 국제출원번호 PCT/US2018/034935

- (87) 국제공개번호 WO 2018/222613

국제공개일자 2018년12월06일

- (30) 우선권주장

62/512,297 2017년05월30일 미국(US)

(뒷면에 계속)

- (56) 선행기술조사문현

US06879051 B1\*

US20160202193 A1\*

JP2007285923 A

US20150204802 A1

\*는 심사관에 의하여 인용된 문현

전체 청구항 수 : 총 13 항

심사관 : 정치영

(54) 발명의 명칭 X-선 산란계측을 이용한 깊은 구조체들에 대한 프로세스 모니터링

**(57) 요약**

고 종횡비 반도체 구조체들의 x-선 산란계측 측정들에 기초하여, 프로세스 파라미터들, 구조 파라미터들, 또는 들 다의 값들을 추정하기 위한 방법들 및 시스템들이 본 명세서에서 제시된다. x-선 산란계측 측정들은 제조 프로세스 흐름의 하나 이상의 단계에서 수행된다. 진행 중인 반도체 제조 프로세스 흐름의 수율 개선을 가능하게 (뒷면에 계속)

**대 표 도**

해주기 위해 측정들이 신속하게 그리고 충분한 정확도로 수행된다. 프로세스 보정들은 관심 파라미터들의 측정된 값들에 기초하여 결정되고, 보정들은 프로세스 툴의 하나 이상의 프로세스 제어 파라미터를 변경하기 위해 프로세스 툴에 전달된다. 일부 예들에서, 진행 중인 제조 프로세스 단계를 제어하기 위해 웨이퍼가 프로세싱되는 동안 측정들이 수행된다. 일부 예들에서, X-선 산란계측 측정들은 특정의 프로세스 단계 이후에 수행되고 프로세스 제어 파라미터들이 미래의 디바이스들의 프로세싱을 위해 업데이트된다.

## (52) CPC특허분류

*G01N 23/20083* (2013.01)

*G03F 7/70525* (2023.05)

*G03F 7/70616* (2023.05)

*H01L 21/67253* (2013.01)

*H01L 22/12* (2013.01)

*H01L 22/20* (2013.01)

*G01B 2210/56* (2013.01)

*G01N 2223/054* (2013.01)

*G01N 2223/6116* (2013.01)

---

## (30) 우선권주장

62/572,566 2017년10월16일 미국(US)

15/990,749 2018년05월28일 미국(US)

## 명세서

### 청구범위

#### 청구항 1

웨이퍼 프로세싱 시스템으로서,

제조 프로세스 흐름의 제1 프로세스 단계에서 반도체 웨이퍼 상의 하나 이상의 구조체를 프로세싱하도록 구성된 웨이퍼 프로세싱 툴; 및

x-선 산란계측 기반 계측 시스템

을 포함하며, 상기 x-선 산란계측 기반 계측 시스템은:

상기 제1 프로세스 단계에서 상기 하나 이상의 구조체를 포함하는 측정 스폿으로 지향되는 x-선 조명 광량을 제공하도록 구성된 x-선 조명 소스;

상기 x-선 조명 광량에 응답하여 상기 반도체 웨이퍼를 통해 투과된 x-선 광량을 검출하도록 구성된 검출기; 및 컴퓨팅 시스템

을 포함하고, 상기 컴퓨팅 시스템은:

상기 검출된 x-선 광량에 기초하여 상기 하나 이상의 구조체와 연관된 하나 이상의 관심 파라미터의 값을 결정하고;

웨이퍼 프로세싱 툴로 하여금 상기 웨이퍼 프로세싱 툴의 하나 이상의 프로세스 제어 파라미터의 값을 조정하게 하는 상기 하나 이상의 관심 파라미터의 상기 값을 표시를 상기 웨이퍼 프로세싱 툴에 전달하도록 구성되는 것인, 웨이퍼 프로세싱 시스템.

#### 청구항 2

제1항에 있어서, 상기 웨이퍼 프로세싱 툴은, 예칭 프로세스, 퇴적 프로세스, 및 리소그래피 프로세스 중 임의 것인, 웨이퍼 프로세싱 시스템.

#### 청구항 3

제1항에 있어서, 상기 x-선 조명 광량은, 복수의 입사각들, 방위각들, 또는 둘 다에서 상기 측정 스폿으로 지향되는 것인, 웨이퍼 프로세싱 시스템.

#### 청구항 4

제1항에 있어서, 상기 x-선 조명 소스는 또한, 복수의 상이한 에너지 레벨에서 측정 스폿으로 지향되는 상기 x-선 조명 광량을 제공하도록 구성되는 것인, 웨이퍼 프로세싱 시스템.

#### 청구항 5

제1항에 있어서, 상기 x-선 조명 소스는 상기 x-선 조명 광량을 제공하고, 상기 검출기는, 상기 웨이퍼 프로세싱 툴이 상기 제1 프로세스 단계를 실행하는 동안 상기 x-선 광량을 검출하는 것인, 웨이퍼 프로세싱 시스템.

#### 청구항 6

제1항에 있어서, 상기 하나 이상의 프로세스 제어 파라미터의 값을 조정하는 것은, 상기 웨이퍼 프로세싱 툴이 상기 제1 프로세스 단계를 실행하는 동안 발생하는 것인, 웨이퍼 프로세싱 시스템.

#### 청구항 7

제1항에 있어서, 상기 웨이퍼 프로세싱 툴은 제조 프로세스 환경을 포함하는 제조 프로세스 챔버를 포함하고, 상기 반도체 웨이퍼는 상기 제조 프로세스 챔버 내부에 배치되고 프로세스 간격 동안 상기 제조 프로세스 환경에 노출되며, 상기 x-선 조명 소스는 상기 x-선 조명 광량을 제공하고, 상기 검출기는 상기 프로세스 간격 동안

상기 x-선 광량을 검출하는 것인, 웨이퍼 프로세싱 시스템.

#### 청구항 8

제1항에 있어서, 상기 x-선 조명 소스는 상기 x-선 조명 광량을 제공하고, 상기 검출기는, 상기 웨이퍼 프로세싱 툴이 상기 제1 프로세스 단계를 실행한 후에 상기 x-선 광량을 검출하는 것인, 웨이퍼 프로세싱 시스템.

#### 청구항 9

제1항에 있어서, 상기 하나 이상의 관심 파라미터의 상기 값들은 상기 제1 프로세스 단계에서 결정되고, 상기 웨이퍼 프로세싱 툴에 전달되는 상기 하나 이상의 관심 파라미터의 상기 값들의 상기 표시는, 상기 웨이퍼 프로세싱 툴로 하여금 상기 하나 이상의 구조체의 제조 프로세스 흐름에서 상기 제1 프로세스 단계에 후속하는 제2 프로세스 단계에서 상기 웨이퍼 프로세싱 툴의 상기 하나 이상의 프로세스 제어 파라미터의 값을 조정하게 하는 것인, 웨이퍼 프로세싱 시스템.

#### 청구항 10

제1항에 있어서, 상기 하나 이상의 관심 파라미터의 상기 값들은 상기 제1 프로세스 단계에서 결정되며, 상기 웨이퍼 프로세싱 툴에 전달되는 상기 하나 이상의 관심 파라미터의 상기 값들의 상기 표시는, 상기 웨이퍼 프로세싱 툴로 하여금 상기 제1 프로세스 단계에서 상기 웨이퍼 프로세싱 툴의 상기 하나 이상의 프로세스 제어 파라미터의 값을 조정하게 하는 것인, 웨이퍼 프로세싱 시스템.

#### 청구항 11

제1항에 있어서, 상기 하나 이상의 관심 파라미터의 상기 값을 결정하는 것은, 모델 기반 측정 모델, 트레이닝된 신호 응답 계측(SRM) 측정 모델, 또는 단층 촬영 측정 모델에 기초하는 것인, 웨이퍼 프로세싱 시스템.

#### 청구항 12

제1항에 있어서, 상기 하나 이상의 구조체는, 3차원 NAND 구조체 또는 동적 랜덤 액세스 메모리(DRAM) 구조체를 포함하는 것인, 웨이퍼 프로세싱 시스템.

#### 청구항 13

x-선 산란계측 기반 계측 시스템으로서,

제조 프로세스 흐름의 제1 프로세스 단계에서 하나 이상의 구조체를 포함하는 측정 스폿 쪽으로 지향되는 x-선 조명 광량을 제공하도록 구성된 x-선 조명 소스;

상기 x-선 조명 광량에 응답하여 반도체 웨이퍼를 통해 투과된 x-선 광량을 검출하도록 구성된 검출기; 및 명령어들을 저장하는 비일시적 컴퓨터 판독가능한 매체

를 포함하고, 상기 명령어들은, 하나 이상의 프로세서에 의하여 실행될 때, 상기 하나 이상의 프로세서로 하여금:

상기 검출된 x-선 광량에 기초하여 상기 하나 이상의 구조체와 연관된 하나 이상의 관심 파라미터의 값을 결정하고;

웨이퍼 프로세싱 툴로 하여금 상기 웨이퍼 프로세싱 툴의 하나 이상의 프로세스 제어 파라미터의 값을 조정하게 하는 상기 하나 이상의 관심 파라미터의 상기 값들의 표시를 상기 웨이퍼 프로세싱 툴에 전달하게

하는 것인, x-선 산란계측 기반 계측 시스템.

### 발명의 설명

#### 기술 분야

[0001] 관련 출원의 상호 참조

[0002] 본 특허 출원은 2017년 5월 30일자로 출원된, 발명의 명칭이 "Process Monitoring for Deep Structures Using X-Ray Scatterometry"인 미국 가특허 출원 제62/512,297호로부터 그리고 2017년 10월 16일자로 출원된, 발명의

명칭이 "Process Monitoring for Deep Structures Using X-Ray Scatterometry"인 미국 가특허 출원 제62/572,566호로부터 35 U.S.C. § 119에 따른 우선권을 주장하며, 각각의 주제는 그 전체가 참고로 본 명세서에 포함된다.

[0003] 기술 분야

[0004] 설명된 실시예들은 계측 시스템들 및 방법들에 관한 것이며, 보다 상세하게는 제조 프로세스 단계를 거치는 반도체 구조체들의 개선된 측정을 위한 방법들 및 시스템들에 관한 것이다.

## 배경 기술

[0005] 로직 및 메모리 디바이스들과 같은 반도체 디바이스들은 전형적으로 시료에 적용되는 프로세싱 단계들의 시퀀스에 의해 제조된다. 반도체 디바이스들의 다양한 피쳐들(features) 및 다수의 구조적 레벨들(structural levels)은 이러한 프로세싱 단계들에 의해 형성된다. 예를 들어, 그 중에서도, 리소그래피는 반도체 웨이퍼 상에 패턴을 생성하는 것을 수반하는 하나의 반도체 제조 프로세스이다. 반도체 제조 프로세스들의 부가의 예들은 화학 기계적 폴리싱, 에칭, 퇴적(deposition), 및 이온 주입을 포함하지만, 이들로 제한되지 않는다. 다수의 반도체 디바이스들은 단일 반도체 웨이퍼 상에 제조되고 이어서 개별 반도체 디바이스들로 분리될(separated) 수 있다.

[0006] 계측 프로세스들은 보다 높은 수율을 도모하기 위해 반도체 제조 프로세스 동안 다양한 단계들에서 웨이퍼들 상의 결함들을 검출하는 데 사용된다. 산란계측(scatterometry) 및 반사계측(reflectometry) 구현들 및 연관된 분석 알고리즘들을 포함하는 다수의 계측 기반 기술들은 통상적으로 나노스케일 구조체들의 임계 치수들, 막 두께들, 조성 및 다른 파라미터들을 특성화하는 데 사용된다. x-선 산란계측 기술들은 샘플 파괴의 위험 없이 높은 처리량의 가능성을 제공한다.

## 발명의 내용

### 해결하려는 과제

[0007] 전통적으로, 광학 산란계측 임계 치수(scatterometry critical dimension, SCD) 측정들은 박막들 및/또는 반복된 주기적인 구조체들로 이루어져 있는 타깃들에 대해 수행된다. 디바이스 제조 동안, 이러한 막들 및 주기적인 구조체들은 전형적으로 실제 디바이스 기하구조(device geometry) 및 재료 구조 또는 중간 디자인을 나타낸다. 디바이스들(예컨대, 로직 및 메모리 디바이스들)이 보다 작은 나노미터-스케일 치수들을 향해 감에 따라, 특성화가 더욱 어려워진다. 복잡한 3차원 기하구조 및 다양한 물리적 속성들을 가진 재료들을 통합한 디바이스들은 특성화 어려움에 기여한다. 예를 들어, 현대의 메모리 구조체들은, 종종, 광학 방사선(optical radiation)이 하부 층들(bottom layers)까지 침투(penetrates)하는 것을 어렵게 만드는 고종횡비 3차원 구조체들이다. 적외선 내지 가시 광을 이용하는 광학 계측 툴들은 반투명 재료들의 많은 층들에 침투할 수 있지만, 양호한 침투 깊이(depth of penetration)를 제공하는 보다 긴 파장들은 작은 이상들(anomalies)에 대해 충분한 감도를 제공하지 못한다. 그에 부가하여, 복잡한 구조체들(예컨대, FinFET들)을 특성화하는 데 요구되는 파라미터들의 개수의 증가는 파라미터 상관(parameter correlation)의 증가를 가져온다. 그 결과, 타깃을 특성화하는 파라미터들이, 종종, 이용 가능한 측정들을 통해 확실하게 분리될(decoupled) 수 없다.

[0008] 일 예에서, 스택에서의 교호하는 재료들 중 하나로서 폴리실리콘을 활용하는 3D FLASH 디바이스들에 대한 침투 이슈들을 극복하려는 시도에서 보다 긴 파장들(예컨대, 근적외선)이 이용되었다. 그렇지만, 3D FLASH의 미러형 구조체(mirror like structure)는 조명이 필름 스택 내로 보다 깊게 전파될 때 본질적으로 광 강도의 감소를 야기한다. 이것은 깊이에 따른 감도 손실 및 상관 이슈들을 야기한다. 이 시나리오에서, 광학 SCD는 높은 감도와 낮은 상관을 갖는 계측 치수들의 축소된 세트를 성공적으로 추출할 수 있을 뿐이다.

[0009] 다른 예에서, 불투명한 하이-k 재료들이 현대의 반도체 구조체들에 점점 더 많이 이용되고 있다. 광학 방사선은 이러한 재료들로 구성된 층들에 종종 침투할 수 없다. 그 결과, 엘립소미터들(ellipsometers) 또는 반사계측들(reflectometers)과 같은 박막 산란계측 툴들을 이용한 측정들이 점점 더 어려워지고 있다.

[0010] 이러한 과제들(challenges)에 응답하여, 보다 복잡한 광학 계측 툴들이 개발되었다. 예를 들어, 다수의 조명 각도들, 보다 짧은 조명 파장들, 보다 넓은 범위들의 조명 파장들, 및 반사된 신호들로부터의 보다 완전한 정보 취득을 갖는(예컨대, 보다 전통적인 반사율 또는 엘립소메트릭(ellipsometric) 신호들에 부가하여 다수의 뮈勒(Mueller) 매트릭스 요소들을 측정하는) 툴들이 개발되었다. 그렇지만, 이러한 접근법들은 많은 고도의 타깃들

(advanced targets)(예컨대, 복잡한 3D 구조체들, 10 nm보다 작은 구조체들, 불투명한 재료들을 이용하는 구조체들) 및 측정 응용분야들(예컨대, 라인 에지 조도(line edge roughness) 및 라인 폭 조도(line width roughness) 측정들)과 연관된 근본적인 과제들을 확실하게 극복하지 못하였다.

[0011] 광학적 방법들은 프로세스 단계들 사이의 프로세스 변수의 비파괴적 트래킹을 제공할 수 있지만, 광학적 방법들이 독립적으로 구별할 수 없는 프로세스 드리프트에 직면하여 정확도를 유지하기 위해 파괴적 방법들에 의한 정기적 캘리브레이션(regular calibration)이 요구된다.

[0012] 원자력 현미경들(atomic force microscopes)(AFM)과 스캐닝 터널링 현미경들(scanning-tunneling microscopes)(STM)은 원자 분해능(atomic resolution)을 달성할 수 있지만, 그들은 시료의 표면을 프로빙(probe)할 수 있을 뿐이다. 그에 부가하여, AFM 및 STM 현미경들은 긴 스캐닝 시간들을 요구한다. 스캐닝 전자 현미경들(scanning electron microscopes)(SEM)은 중간 분해능 레벨들을 달성하지만, 충분한 깊이까지 구조체들에 침투할 수 없다. 따라서, 고종횡비 홀들은 잘 특성화되지 않는다. 그에 부가하여, 시료의 요구된 대전(charging)은 이미징 성능에 악영향을 미친다. X-선 반사계들은 고 종횡비 구조체들을 측정할 때 그들의 유효성을 제한하는 침투 이슈들을 또한 겪는다.

[0013] 침투 깊이 이슈들을 극복하기 위해, TEM, SEM 등과 같은 전통적인 이미징 기술들은 집속 이온 빔(focused ion beam, FIB) 머시닝, 이온 밀링, 블랭킷 또는 선택적 에칭 등과 같은 파괴적 샘플 준비(destructive sample preparation) 기술들과 함께 이용된다. 예를 들어, 투과 전자 현미경들(transmission electron microscopes)(TEM)은 높은 분해능 레벨들을 달성하고 임의의 깊이들을 프로빙할 수 있지만, TEM은 시료의 파괴적 절편화(destructive sectioning)를 요구한다. 재료 제거 및 측정의 여러 번의 반복들은 일반적으로 3차원 구조체 전반에 걸쳐 중요한 계측 파라미터들을 측정하는 데 요구된 정보를 제공한다. 그러나, 이러한 기술들은 샘플 파괴 및 긴 프로세스 시간들을 요구한다. 이러한 유형들의 측정들을 완료하기 위한 시간 및 복잡도는 에칭 및 계측 단계들의 드리프트로 인한 큰 부정확성을 유입시키는데, 그 이유는 측정 중인 웨이퍼에 대한 프로세스가 완료되고 나서 오랜 후에 측정 결과들이 이용가능하게 되기 때문이다. 따라서, 측정 결과들은 추가의 프로세싱 및 지연된 피드백으로 인한 바이어스들(biases)을 겪는다. 그에 부가하여, 이러한 기술들은 레지스트레이션 에러들(registration errors)을 유입시키는 수많은 반복들을 요구한다. 요약하면, 디바이스 수율은 SEM 및 TEM 기술들에 요구되는 길고 파괴적인 샘플 준비에 의해 부정적인 영향을 받는다.

[0014] 반도체 디바이스 제조에서, 에칭 프로세스들 및 퇴적 프로세스들은 반도체 웨이퍼 상의 디바이스 패턴 프로파일 및 레이아웃을 정의하기 위한 주요 단계들(critical steps)이다. 따라서, 피측정 구조체들(measured structures)의 충실도(fidelity) 및 웨이퍼에 걸친 그들의 균일성을 보장하기 위해 막들 및 패터닝된 구조체들을 측정하는 것이 중요하다. 게다가, 진행 중인 프로세스를 제어하기 위해 그리고 웨이퍼에 걸쳐 요구된 패턴 또는 막 균일성을 유지하도록 설정들을 조정하기 위해 측정 결과들을 신속하게 제공하는 것이 중요하다.

[0015] 대부분의 예들에서, 반도체 제조 프로세스의 정밀한 모니터링은 하나 이상의 독립형(stand-alone, SA) 계측 시스템에 의해 수행된다. SA 계측 시스템들은 보통 최고의 측정 성능을 제공한다. 그렇지만, 웨이퍼가 측정을 위해 프로세스 툴로부터 제거되어야만 한다. 진공에서 수행되는 프로세스들의 경우, 이것은 상당한 지연을 야기한다. 그 결과, SA 계측 시스템들은 프로세스 툴들, 특히 진공을 수반하는 프로세스 툴에 신속한 측정 피드백을 제공할 수 없다. 다른 예들에서, 통합된 계측 시스템들 또는 센서들은, 프로세스 단계가 완료된 후에 그러나 웨이퍼를 프로세스 툴로부터 제거하지 않고서 웨이퍼들을 측정하기 위해, 프로세스 장비에 종종 부착된다. 다른 예들에서, 인-시츄(in-situ, IS) 계측 시스템들 또는 센서들이 프로세스 툴의 프로세싱 챔버 내부에서 이용된다. 게다가, IS 계측 시스템은 프로세스(예컨대, 에칭 프로세스, 퇴적 프로세스 등) 동안 웨이퍼를 모니터링하고 측정 중인 제조 단계를 수행하는 프로세스 툴에 피드백을 제공한다.

[0016] 일 예에서, 반응성 이온 에칭 프로세스를 거치는 구조체들은 인-시츄로(in-situ) 모니터링된다. 일부 제조 단계들에서, 에칭 프로세스는 노출된 층을 완전히 관통하게 에칭하고 이어서 하부 층(lower layer)의 실질적인 에칭이 발생하기 전에 종료되도록 요구받는다. 전형적으로, 이러한 프로세스 단계들은 방출 분광법 기술(emission spectroscopy technique)을 사용하여 챔버에 존재하는 플라스마의 스펙트럼 시그니처를 모니터링함으로써 제어된다. 노출된 층이 관통하게 에칭되고 에칭 프로세스가 하부 층과 반응하기 시작할 때, 플라스마의 스펙트럼 시그니처의 뚜렷한 변화가 발생한다. 스펙트럼 시그니처의 변화가 방출 분광법 기술에 의해 측정되고, 스펙트럼 시그니처의 측정된 변화에 기초하여 에칭 프로세스가 중단된다.

[0017] 다른 제조 단계들에서, 에칭 프로세스는 노출된 층을 부분적으로 관통하여 특정된 에칭 깊이까지 에칭하고, 노출된 층을 완전히 관통하게 에칭하기 전에 종료되도록 요구받는다. 이러한 유형의 에칭 프로세스는 "블라인드

에칭(blind etch)"이라고 흔히 지칭된다. 현재, 부분적으로 에칭된 층들을 통한 에칭 깊이의 측정은 거의 수직 입사 스펙트럼 반사계측(near-normal incidence spectral reflectometry)에 기초한다.

[0018] 현재의 인-시츄 센서들은 막 두께들에 대한 별크 변화들(bulk changes)을 모니터링할 수 있을 뿐이며 깊은 3-D 구조체들의 프로세싱으로부터 결과되는 복잡한 프로파일들과 잘 상관되지 않는다.

[0019] 일반적으로, 광학, 음향 및 전자 빔 툴들의 조합들을 사용하는 많은 프로세스 모니터링 방법들이 있다. 이러한 기술들은 디바이스를 직접, 특수 설계된 타깃들, 또는 특정 모니터 웨이퍼들을 측정한다. 그렇지만, 비용 효율적이고 적시의 방식으로 고 종횡비 구조체들의 관심 파라미터들을 측정할 수 없는 것은, 특히 웨이퍼의 메모리 섹터에서, 낮은 수율을 결과한다.

[0020] 요약하면, 많은 반도체 구조체들의 증가된 깊이 및 피처 크기의 지속적인 감소들은 독립형 시스템들 및, 이온 주입 및 에칭 툴들과 같은, 프로세스 툴들과 통합된 것들을 포함한, 계측 시스템들에 어려운 요구사항들을 부과한다. 따라서, 높은 디바이스 수율을 유지하기 위해 고 종횡비 구조체들을 측정하기 위한 개선된 계측 시스템들 및 방법들이 요구된다.

### 과제의 해결 수단

[0021] 고 종횡비 반도체 구조체들의 x-선 산란계측 측정들에 기초하여, 프로세스 파라미터들, 구조 파라미터들, 또는 둘 다의 값을 추정하기 위한 방법들 및 시스템들이 본 명세서에서 제시된다. x-선 산란계측 측정들은 제조 프로세스 흐름의 하나 이상의 단계에서 수행된다. 예시적인 프로세스 단계들은 에칭, 퇴적, 및 리소그래피 프로세스들을 포함한다. 진행 중인 반도체 제조 프로세스 흐름의 수율 개선을 가능하게 해주기 위해 측정들이 신속하게 그리고 충분한 정확도로 수행된다. 일부 예들에서, 진행 중인 제조 프로세스를 제어하기 위해 웨이퍼가 프로세싱되는 동안 측정들이 수행된다.

[0022] 일 양태에서, SAXS(small-angle scatterometry) 계측 시스템은 웨이퍼 프로세싱 툴과 통합되고, 관심 파라미터들의 측정된 값을 웨이퍼 프로세싱 툴을 제어하기 위한 피드백으로서 제공된다. 일부 실시예들에서, 투과 SAXS 측정 시스템(transmission SAXS measurement system)이 이용된다. 다른 실시예들에서, 반사 SAXS 측정 시스템(reflective SAXS measurement system)이 이용된다.

[0023] 일부 실시예들에서, SAXS 계측 시스템은 에칭, 퇴적, 또는 리소그래피 툴과 같은 웨이퍼 프로세싱 툴과 통합된다. 다른 실시예들에서, SAXS 계측 시스템은 독립형 툴로서 구성된다.

[0024] 추가의 양태에서, SAXS 시스템은 측정 모델을 사용한 프로세스 중의(under process) 웨이퍼들의 산란계측 측정들에 기초하여 하나 이상의 관심 파라미터(예컨대, 프로세스 파라미터 값, 구조 파라미터 값, 또는 둘 다)의 값을 추정한다.

[0025] 다른 추가의 양태에서, 프로세스 보정들은 관심 파라미터들의 측정된 값을 기초하여 결정되고, 보정들은 프로세스 툴의 하나 이상의 프로세스 제어 파라미터를 변경하기 위해 프로세스 툴에 전달된다(communicated). 일부 실시예들에서, 피측정 구조체에 대해 프로세스가 실행되고 있는 동안 SAXS 측정들이 수행되고 프로세스 제어 파라미터들이 업데이트된다. 일부 실시예들에서, 특정의 프로세스 단계 이후에 SAXS 측정들이 수행되고, 그 프로세스 단계에 의한 미래의 디바이스들의 프로세싱을 위해 그 프로세스 단계와 연관된 프로세스 제어 파라미터들이 업데이트된다. 일부 실시예들에서, 특정의 프로세스 단계 이후에 SAXS 측정들이 수행되고, 후속 프로세스 단계에 의한 피측정 디바이스 또는 다른 디바이스들의 프로세싱을 위해 후속 프로세스 단계와 연관된 프로세스 제어 파라미터들이 업데이트된다.

[0026] 제조 중인 특정의 고 종횡비 구조체의 측정 빈도수는 모니터링된 프로세스 파라미터의 안정성에 의존한다. 더욱이, 요구된 측정 시간의 길이는 모니터링된 프로세스 변수의 변화들에 대한 산란 감도(scattering sensitivity)에 의존한다. 산란 신호를 인-시츄로 측정하는 것은 프로세스 조건들의 가장 빠른 측정을 그러나 가장 높은 불확실성으로 제공한다. 반면에, 보다 긴 측정 시간들은 측정된 파라미터들의 보다 큰 정밀도 및 확실성을 제공한다. 일반적으로, 전체 산란 체적(entire scattering volume)에 영향을 미치는 프로세스 파라미터들(예컨대, 에칭 시간)은 가장 빠르게 모니터링될 수 있는 반면, 다른 파라미터들(예컨대, 에칭 프로파일의 사소한 편차들)은 이동 평균 또는 보다 긴 측정 시간 중 어느 하나가 의미있는 결과들을 달성할 것을 요구한다. 따라서, 이러한 파라미터들은 보다 느리게(on a slower basis) 제어될 수 있을 뿐이다.

[0027] 전술한 바는 요약이고 따라서, 필요에 따라, 세부사항의 단순화들, 일반화들 및 생략들을 포함하며; 결론적으로, 본 기술분야의 통상의 기술자는 요약이 예시적인 것에 불과하고 어떠한 식으로든 제한하는 것이 아

님을 이해할 것이다. 본 명세서에 설명된 디바이스들 및/또는 프로세스들의 다른 양태들, 발명적 특징들 (inventive features), 및 장점들은 본 명세서에 기재된 비제한적인 상세한 설명에서 명백해질 것이다.

### 도면의 간단한 설명

[0028]

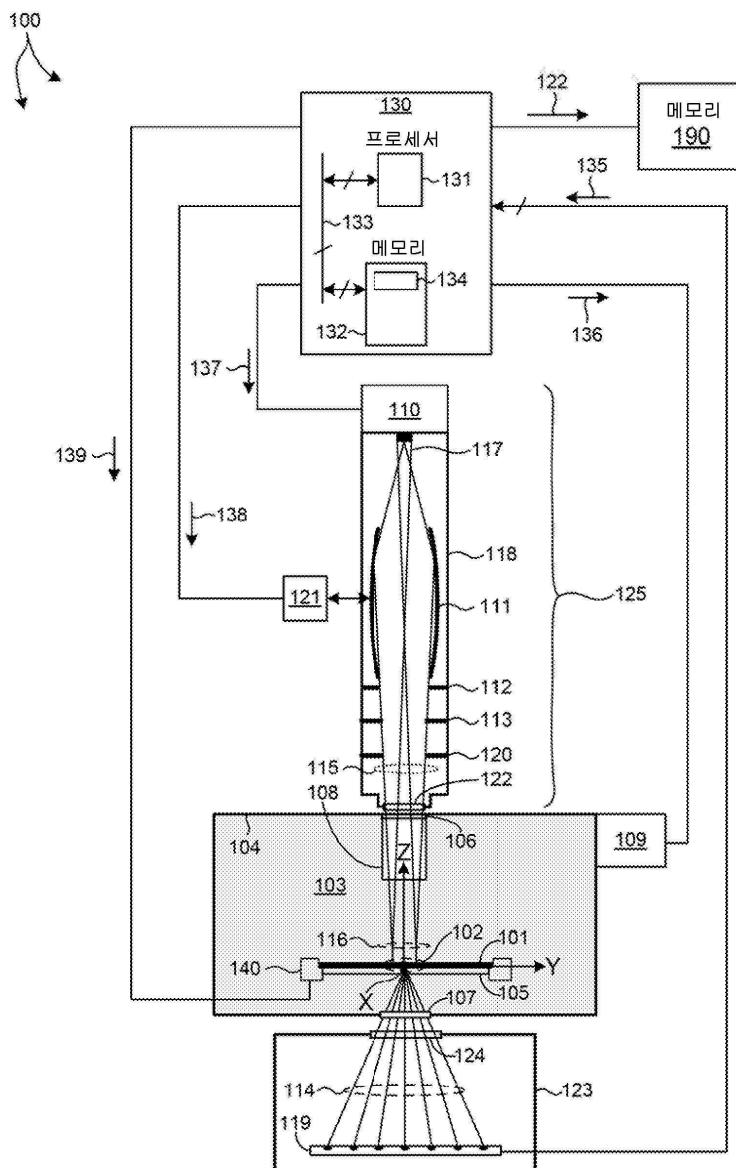

도 1은 프로세스 중의 웨이퍼 상에 배치된 반도체 구조체들의 x-선 산란계측 측정들에 기초하여 예칭 프로세스를 모니터링하기 위한 예시적인 웨이퍼 프로세싱 시스템(100)을 묘사한다.

도 2는 입사각( $\Theta$ ) 및 방위각( $\phi$ )에 의해 설명되는 특정의 배향으로 웨이퍼에 입사하는 x-선 조명 빔을 예시하는 다이어그램이다.

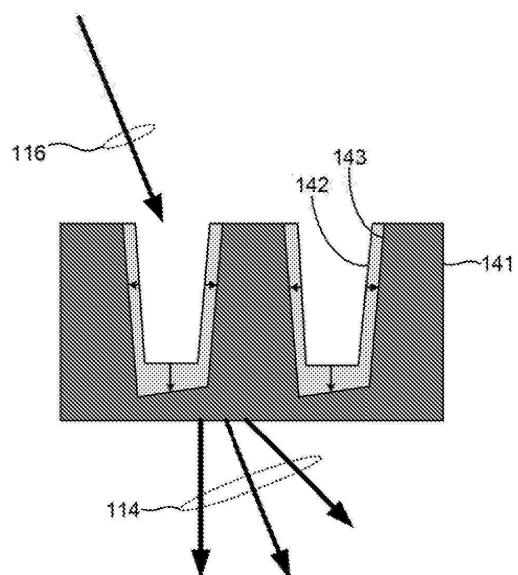

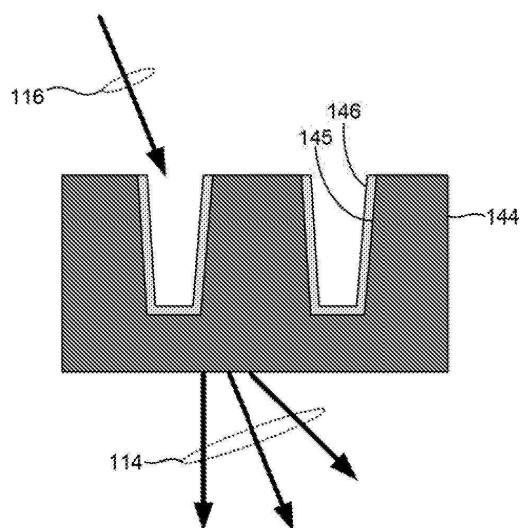

도 3은 일 실시예에서 예칭 프로세스를 거치는 2개의 홀 퍼처(hole features)를 포함하는 반도체 구조체를 예시하는 다이어그램이다.

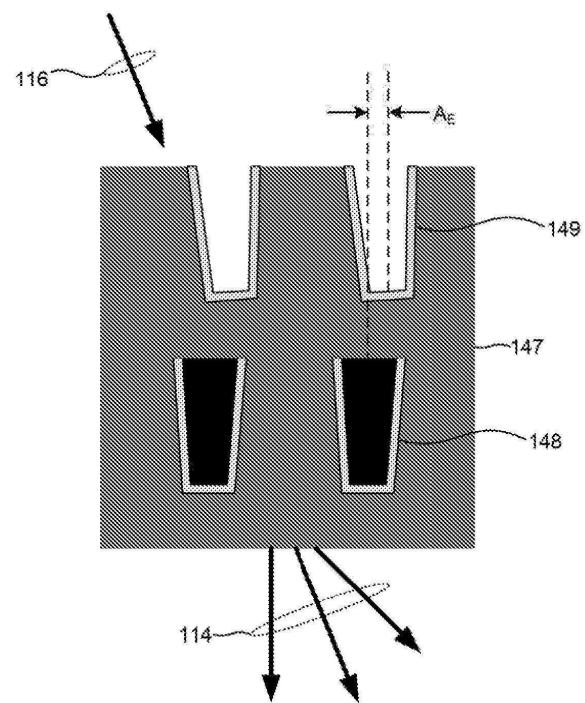

도 4는 다른 실시예에서 퇴적 프로세스를 거치는 2개의 홀 퍼처를 포함하는 반도체 구조체를 예시하는 다이어그램이다.

도 5는, 각각이 2개의 홀 퍼처를 포함하는, 2개의 층을 포함하는 반도체 구조체를 예시하는 다이어그램이다.

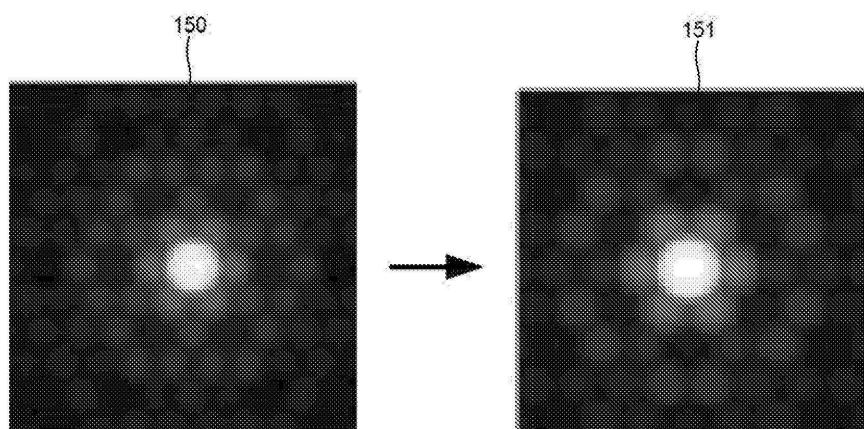

도 6은 예칭된 홀의 크기의 변화들을 예시하는 산란 이미지들을 묘사한다.

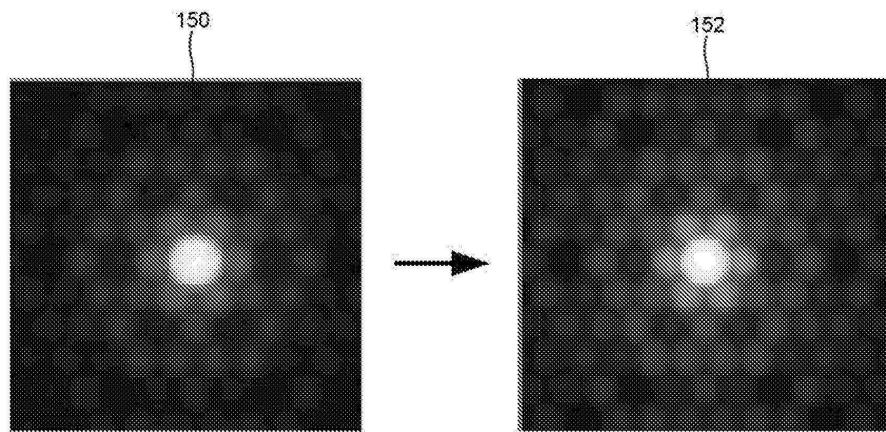

도 7은 예칭된 홀의 깊이의 변화들을 예시하는 산란 이미지들을 묘사한다.

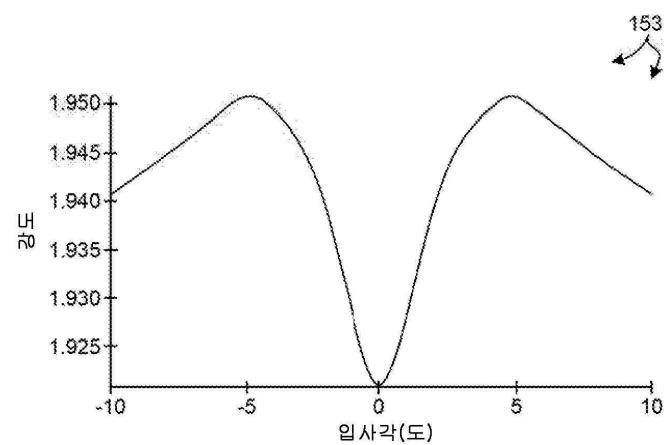

도 8은 입사각( $\Theta$ )의 함수로서의 제로 차수 빔의 산란 효율( $S_{00}$ )의 플롯을 묘사한다.

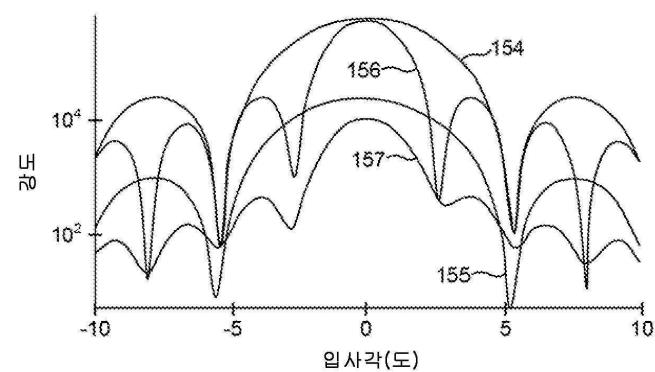

도 9는 입사각( $\Theta$ )의 함수로서의 몇 개의 고차의 산란 효율을 묘사한다.

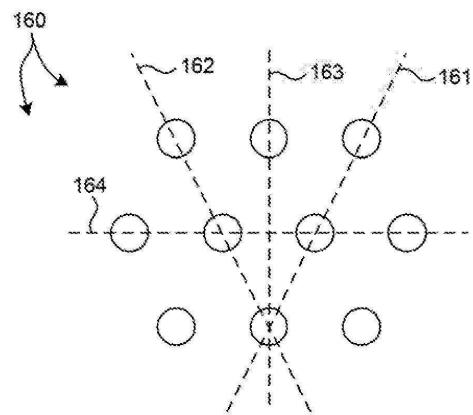

도 10은 고 종횡비 홀 구조체들의 어레이의 평면도(top view)를 묘사한다.

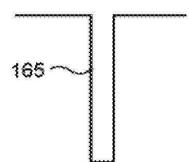

도 11a는 이상적인 고 종횡비 홀 구조체의 측면도를 예시하는 다이어그램이다.

도 11b는 틸팅된(tilted) 홀 구조체의 측면도를 예시하는 다이어그램이다.

도 11c는 점진적으로 틸팅된(progressively tilted) 홀 구조체의 측면도를 예시하는 다이어그램이다.

도 12a 내지 도 12c는 본 명세서에서 설명되는 바와 같이 측정을 거치는 전형적인 3D FLASH 메모리 디바이스의 등각도(isometric view), 평면도, 및 단면도를, 제각기, 묘사한다.

도 13은 프로세스 중의 웨이퍼 상에 배치된 반도체 구조체들의 반사 x-선 산란계측 측정들에 기초하여 예칭 프로세스를 모니터링하기 위한 예시적인 웨이퍼 프로세싱 시스템(200)을 묘사한다.

도 14는 예시적인 모델 구축 및 분석 엔진(180)을 예시하는 다이어그램이다.

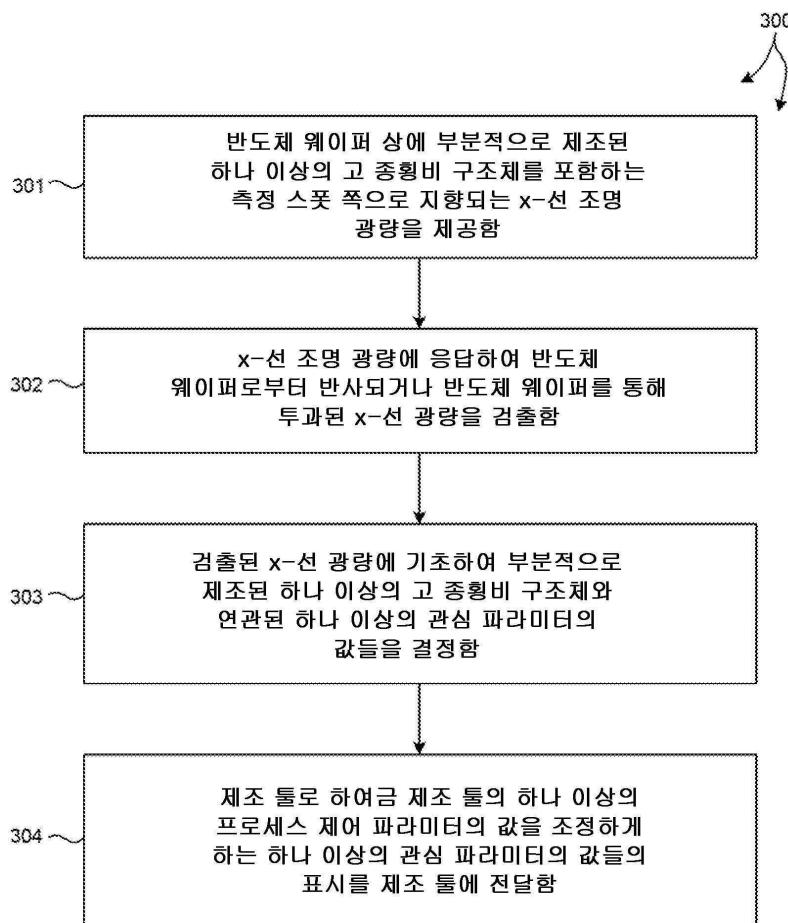

도 15는 소각 x-선 산란계측(small angle X-Ray scatterometry) 측정들에 기초하여 고 종횡비 구조체들에 대한 반도체 제조 프로세스를 제어하기 위한 방법(300)의 플로차트를 예시한다.

### 발명을 실시하기 위한 구체적인 내용

[0029]

본 발명의 배경 예들 및 일부 실시예들에 대해 이제 상세히 언급될 것이고, 이들의 예들이 첨부 도면들에 예시된다.

[0030]

부분적으로 제조된 고 종횡비 반도체 구조체들의 x-선 산란계측 측정들에 기초하여, 프로세스 파라미터들, 구조파라미터들, 또는 둘 다의 값들을 추정하기 위한 방법들 및 시스템들이 본 명세서에서 제시된다. 고 종횡비 구조체들의 x-선 산란계측 측정들은 제조 프로세스 흐름의 하나 이상의 단계에서 수행된다. 예시적인 프로세스 단계들은 예칭, 퇴적, 및 리소그래피 프로세스들을 포함한다. 진행 중인 반도체 제조 프로세스 흐름의 수율 개선을 가능하게 해주기 위해 측정들이 신속하게 그리고 충분한 정확도로 수행된다. 일부 예들에서, 진행 중인 프로세스를 제어하기 위해 웨이퍼가 프로세싱되는 동안 수행되는 측정들이 사용된다. 고 종횡비 구조체들은 입사 x-선들을 효율적으로 산란시키기에 충분한 전체 산란 체적 및 재료 콘트라스트를 포함한다. 수집된 산란 x-선들은 피측정 디바이스들의 관심 구조 파라미터들의 정확한 추정을 가능하게 해준다. x-선 에너지는 최소한의 신호 오염을 갖는 광학 경로에서 실리콘 웨이퍼에 침투하여 가스들을 프로세싱하기에 충분히 높다.

[0031]

고도화된 반도체 제조 노드들의 디바이스 수율은 계속 어려움을 겪고 있으며, 복잡한 고 종횡비(깊은 3차원) 구조체들의 디바이스 수율이 특히 그렇다. x-선 산란계측에 기초한 실시간 모니터링 및 프로세스 제어는 SEM,

TEM 등과 같은 전통적인 파괴적 기술들과 비교하여 비용 효과적인 방식으로 고 종횡비 구조체들의 제조를 위한 프로세스 제어를 가능하게 해준다.

[0032] x-선 산란계측 측정들은 측정 중의 샘플을 파괴하지 않으면서 높은 처리량으로 고 종횡비 구조체들의 관심 구조 파라미터들의 정확한 추정치들을 제공한다. 측정 감도는 침투 깊이에 의해 크게 영향을 받지 않아, 피측정 반도체 구조체의 수직 스택(vertical stack) 내에 깊숙이 위치된 구조체들의 정확한 측정을 가능하게 해준다. 더욱이, 플라스마 프로세싱 환경을 통해 전파되는 x-선 방사선은 광학 방사선과 비교하여 플라스마 프로세스에 의해 생성된 전자기 필드들로 인한 신호 오염에 대해 상대적으로 둔감하다.

[0033] 일 양태에서, SAXS(small-angle scatterometry) 계측 시스템은 웨이퍼 프로세싱 툴과 통합되고, 관심 파라미터들의 측정된 값들은 웨이퍼 프로세싱 툴을 제어하기 위한 피드백으로서 제공된다.

[0034] 도 1은 프로세스 중의 웨이퍼 상에 배치된 반도체 구조체들의 x-선 산란계측 측정들에 기초하여 에칭 프로세스를 모니터링하기 위한 예시적인 웨이퍼 프로세싱 시스템(100)을 묘사한다. 묘사된 실시예에서, T-SAXS(transmission, small-angle scatterometry) 계측 시스템은 에칭 프로세스 툴과 통합된다. 관심 파라미터들의 측정된 값들은 에칭 프로세스 툴을 제어하기 위한 피드백으로서 제공된다.

[0035] 웨이퍼 프로세싱 시스템(100)은 x-선 산란계(x-ray scatterometer) 및 프로세스 환경(103)을 포함하는 프로세스 챔버(104)를 포함한다. 반도체 웨이퍼(101)는 프로세스 챔버(104) 내에 위치된다. 웨이퍼(101)는 웨이퍼 척(105)에 부착되고 웨이퍼 스테이지(140)에 의해 프로세스 챔버(104) 및 x-선 산란계에 대해 위치결정된다.

[0036] 일부 실시예들에서, 웨이퍼 스테이지(140)는 x-선 산란계에 의해 제공되는 조명에 대해 웨이퍼(101)를 위치결정하기 위해 회전 이동과 병진 이동(예컨대, X 방향으로의 병진 이동 및 Y-축을 중심으로 한 회전 이동)을 결합시킴으로써 웨이퍼(101)를 XY 평면에서 이동시킨다. 일부 다른 실시예들에서, 웨이퍼 스테이지(140)는 x-선 산란계에 의해 제공되는 조명에 대해 웨이퍼(101)를 위치결정하 위해 2개의 직교 병진 이동(예컨대, X 방향으로의 이동 및 Y 방향으로의 이동)을 결합시킨다. 일부 실시예들에서, 웨이퍼 스테이지(140)는 6개의 자유도에서 x-선 산란계에 의해 제공된 조명에 대한 웨이퍼(101)의 위치를 제어하도록 구성된다. 일반적으로, 시료 위치결정 시스템(140)은 고니오미터(goniometer) 스테이지들, 헥사포드(hexapod) 스테이지들, 각도 스테이지들, 및 선형 스테이지들을 포함하지만 이들로 제한되지 않는, 원하는 선형 및 각도 위치결정 성능을 달성하기 위해 기계적 요소들의 임의의 적당한 조합을 포함할 수 있다.

[0037] 일부 실시예들에서, 웨이퍼 프로세싱 시스템(100)은 웨이퍼 스테이지(140)를 포함하지 않는다. 이 실시예들에서, 웨이퍼 핸들링 로봇(도시되지 않음)은 프로세스 챔버(104) 내부의 웨이퍼 척(105) 상에 웨이퍼(101)를 위치시킨다. 웨이퍼(101)는 웨이퍼 핸들링 로봇으로부터 진공 프로세스 환경(103)과 호환되는 정전 웨이퍼 척(electrostatic wafer chuck)(105) 상으로 이송된다. 이 실시예들에서, x-선 산란계에 의해 수행되는 측정들은 웨이퍼 척(105) 상에 웨이퍼(101)를 클램핑시킨 후에 x-선 산란계의 시야 내의 웨이퍼(101)의 부분으로 제한된다. 이러한 의미에서, 웨이퍼 스테이지(140)는 임의적(optional)이다. 이 한계를 극복하기 위해, 웨이퍼 프로세싱 시스템(100)은, 각각이 웨이퍼(101)의 상이한 영역을 측정하는, 다수의 x-선 산란계 시스템들을 포함할 수 있다.

[0038] 일 실시예에서, 프로세스 챔버(104)는 반응성 이온 에칭 시스템의 요소이다. 이 실시예에서, 프로세스 환경(103)은 웨이퍼(101)의 표면 상의 노출된 재료를 에칭 제거하는(etches away) 라디오 주파수 유도 플라스마(radio frequency induced plasma)를 포함한다.

[0039] 도 1에 묘사된 바와 같이, x-선 산란계의 광학 요소들은 프로세스 챔버(104)의 외부에 위치된다. 에칭 프로세스 및 퇴적 프로세스 둘 다의 프로세스 챔버에 이온화된 입자들이 존재한다. 프로세스에 의해 유도된 자기 필드들을 교란시키는 것을 피하기 위해 광학 요소들은 웨이퍼로부터 충분히 멀리 떨어져 위치되어야만 한다. 그에 부가하여, 이온화된 입자들이 프로세스 챔버 내에 위치된 광학 요소들 상에 축적될 수 있으며, 따라서 프로세스 챔버 내에 광학 요소들을 포함시키는 것은 실용적이지 않다.

[0040] 묘사된 실시예에서, SAXS 계측 툴(100)은 x-선 조명 소스(110), 포커싱 광학계(111), 빔 발산 제어 슬릿(112), 중간 슬릿(113), 및 빔 세이프 슬릿 메커니즘(120)을 포함하는 x-선 조명 서브시스템(125)을 포함한다. x-선 조명 소스(110)는 T-SAXS 측정들에 적당한 x-선 방사선을 발생시키도록 구성된다. 일부 실시예들에서, x-선 조명 소스(110)는 0.01 나노미터 내지 1 나노미터의 파장들을 발생시키도록 구성된다. 일반적으로, 고처리량 인라인 계측(high-throughput, inline metrology)을 가능하게 해주기에 충분한 풍력스 레벨들로 고휘도 x-선들을 발생시킬 수 있는 임의의 적당한 고휘도 x-선 조명 소스가 T-SAXS 측정들을 위한 x-선 조명을 공급하기 위해 고

려될 수 있다. 일부 실시예들에서, x-선 소스는 x-선 소스가 상이한 선택가능한 파장들의 x-선 방사선을 전달할 수 있게 해주는 튜닝가능한 모노크로메이터(tunable monochromator)를 포함한다.

[0041] 일부 실시예들에서, 15keV보다 큰, 또는 17keV보다 큰 광자 에너지를 갖는 방사선을 방출하는 하나 이상의 x-선 소스는 x-선 소스가 디바이스 전체는 물론 웨이퍼 기판 및 임의의 개체 요소들을 통한 충분한 투과를 가능하게 해주는 파장들의 광을 공급하도록 보장하는 데 사용된다. 개체 요소들은 하나 이상의 윈도(예컨대, 베릴륨, 사파이어, 다이아몬드 등으로 제조된 윈도들)을 포함할 수 있다. 개체 요소들은 웨이퍼(101)와 검출기(119) 사이의 산란 x-선 방사선의 경로에, 웨이퍼 척(105), 로드 포트(load port), 또는 스테이지(140)의 요소들과 같은, 구조체들을 또한 포함할 수 있다. 구조 플라스틱 재료들을 통한 투과는 산란 신호들의 과도한 오염의 위험이 없다. 웨이퍼 척(105), 스테이지(140), 또는 로드 포트의 구조 요소들을 통한 개구들(apertures) 또는 윈도들은 신호 오염을 최소화하는 데 이용될 수 있다. 예를 들어, 웨이퍼에서의 x-선 스폷은 50 내지 200 마이크로미터 정도로 작을 수 있다. 웨이퍼에 가까이 위치된 요소들의 경우, 산란된 차수들(scattered orders)의 오염을 최소화하는 데 요구되는 개구의 크기는 최소이다. 그렇지만, 관심의 산란된 차수들과 연관된 유한 산란 각도들로 인해 웨이퍼로부터의 거리가 증가함에 따라 요구된 개구 크기가 증가한다.

[0042] 예시적인 x-선 소스들은 x-선 방사선을 자극하기 위해 고체 또는 액체 타깃들을 충격(bombard)하도록 구성된 전자 빔 소스들을 포함한다. 고휘도 액체 금속 x-선 조명을 발생시키기 위한 방법들 및 시스템들은 2011년 4월 19일자로 KLA-Tencor Corp.에게 등록된 미국 특허 제7,929,667호에 설명되어 있으며, 이 미국 특허 전체는 본 명세서에 참고로 포함된다.

[0043] 비제한적인 예로서, x-선 조명 소스(110)는 입자 가속기 소스(particle accelerator source), 액체 애노드 소스(liquid anode source), 회전 애노드 소스(rotating anode source), 고정식 고체 애노드 소스(stationary, solid anode source), 마이크로포커스 소스(microfocus source), 마이크로포커스 회전 애노드 소스(microfocus rotating anode source), 플라스마 기반 소스(plasma based source), 및 역 콤프턴 소스(inverse Compton source) 중 임의의 것을 포함할 수 있다. 일 예에서, 미국 캘리포니아주 팔로 알토 소재의 Lyncean Technologies, Inc.로부터 입수 가능한 역 콤프턴 소스가 고려될 수 있다. 역 콤프턴 소스들은 일정 범위의 광자 에너지들에 걸쳐 x-선들을 생성할 수 있다는 부가의 장점을 가지며, 그에 의해 x-선 소스가 상이한 선택가능한 파장들의 x-선 방사선을 전달할 수 있게 해준다.

[0044] 일부 예들에서, 컴퓨팅 시스템(130)은 x-선 조명 소스(110)로 하여금 원하는 에너지 레벨의 x-선 방사선을 방출하게 하는 커맨드 신호들(137)을 x-선 조명 소스(110)에 전달한다. 측정 중인 고 종횡비 구조체들에 관한 추가 정보와 함께 측정 데이터를 취득하기 위해 에너지 레벨이 변경된다.

[0045] x-선 조명 소스(110)는 유한한 측면 치수들(즉, 빔 축에 직교하는 영이 아닌 치수들)을 가지는 소스 영역에 걸쳐 x-선 방출을 생성한다. 포커싱 광학계(111)는 소스 방사선을 시료(101) 상에 위치된 계측 타깃 상에 포커싱 시킨다. 유한한 측면 소스 치수는 소스의 에지들로부터 오는 광선들(117)에 의해 정의되는 타깃 상의 유한한 스폷 크기(102)를 결과한다. 일부 실시예들에서, 포커싱 광학계(111)는 타원 형상의 포커싱 광학 요소들을 포함한다.

[0046] 빔 발산 제어 슬릿(112)은 포커싱 광학계(111)와 빔 세이핑 슬릿 메커니즘(120) 사이의 빔 경로에 위치된다. 빔 발산 제어 슬릿(112)은 측정 중인 시료에 제공되는 조명의 발산을 제한한다. 부가의 중간 슬릿(113)은 빔 발산 제어 슬릿(112)과 빔 세이핑 슬릿 메커니즘(120) 사이의 빔 경로에 위치된다. 중간 슬릿(113)은 부가의 빔 세이핑을 제공한다. 그렇지만, 일반적으로, 중간 슬릿(113)은 임의적이다.

[0047] 빔 세이핑 슬릿 메커니즘(120)은 빔 경로에서 시료(101) 이전에 위치된다. 일부 실시예들에서, 빔 세이핑 슬릿 메커니즘(120)은 다수의 독립적으로 작동되는 빔 세이핑 슬릿들을 포함한다. 일 실시예에서, 빔 세이핑 슬릿 메커니즘(120)은 4개의 독립적으로 작동되는 빔 세이핑 슬릿을 포함한다. 이 4개의 빔 세이핑 슬릿은 들어오는 빔(incoming beam)(115)의 일 부분을 효과적으로 차단하고 박스 형상의 조명 단면을 가지는 조명 빔(116)을 발생시킨다.

[0048] 일반적으로, x-선 광학계는 x-선 방사선을 세이핑하여 시료(101) 쪽으로 지향시킨다. 일부 예들에서, x-선 광학계는 시료(101)에 입사하는 x-선 빔을 단색화(monochromatize)하기 위한 x-선 모노크로메이터를 포함한다. 일부 예들에서, x-선 광학계는 x-선 빔을 다층 x-선 광학계를 사용하여 1 밀리라디안 미만의 발산으로 시료(101)의 측정 영역(102) 상으로 콜리메이팅 또는 포커싱시킨다. 이러한 예들에서, 다층 x-선 광학계는 빔 모노크로메이터로서도 기능한다. 일부 실시예들에서, x-선 광학계는 하나 이상의 x-선 콜리메이팅 미러(x-ray

collimating mirrors), x-선 개구(x-ray apertures), x-선 빔 스톱(x-ray beam stops), 굴절 x-선 광학계(refractive x-ray optics), 존 플레이트들(zone plates)과 같은 회절 광학계, 몬텔 광학계(Montel optics), 스침 입사 타원체 미러들(grazing incidence ellipsoidal mirrors)과 같은 거울반사 x-선 광학계(specular x-ray optics), 중공 모세관 x-선 도파관들(hollow capillary x-ray waveguides)과 같은 다중모세관 광학계(polycapillary optics), 다층 광학계 또는 시스템, 또는 이들의 임의의 조합을 포함한다. 추가 세부사항들은 미국 특허 공개 제2015/0110249호에 설명되어 있으며, 이 미국 특허 공개의 내용은 그 전체가 본 명세서에 참고로 포함된다.

[0049] 일부 실시예들에서, x-선 조명 소스(110), 포커싱 광학계(111), 슬릿들(112 및 113), 또는 이들의 임의의 조합은 제어된 대기 환경(예컨대, 가스 퍼지 환경(gas purge environment))에서 유지된다. 그렇지만, 일부 실시예들에서, 이 요소들 중 임의의 것 사이의 그리고 그 내에서의 광학 경로 길이는 길고, 공기 중에서의 x-선 산란은 검출기 상의 이미지에 노이즈를 제공한다(contributes). 따라서 일부 실시예들에서, x-선 조명 소스(110), 포커싱 광학계(111), 및 슬릿들(112 및 113) 중 임의의 것은 국소화된 진공 환경에서 유지된다. 도 1에 묘사된 실시예에서, 포커싱 광학계(111), 슬릿들(112 및 113), 및 빔 세이핑 슬릿 메커니즘(120)은 배기된 비행 튜브(evacuated flight tube)(118) 내의 제어된 환경(예컨대, 진공)에서 유지된다. 조명 빔(116)은 프로세스 챔버(104)의 윈도(106)에의 입사 이전에 비행 튜브(118)의 끝에 있는 윈도(122)를 통과한다. 일부 실시예들에서, 비행 튜브(118)는 비행 튜브(118) 내에 유지된 진공 환경으로부터 프로세스 환경(103)을 분리시키는 윈도에 의해 프로세스 챔버(104)와 통합된다.

[0050] 웨이퍼(101)에의 입사 후에, 산란 x-선 방사선(114)은 윈도(107)를 통해 프로세스 챔버(104)를 빠져나간다. 일부 실시예들에서, 프로세스 챔버(104)와 검출기(119) 사이의 광학 경로 길이(즉, 수집 빔 경로)는 길고, 공기 중에서의 x-선 산란은 검출기 상의 이미지에 노이즈를 제공한다. 따라서, 양호한 실시예들에서, 프로세스 챔버(104)와 검출기(119) 사이의 수집 빔 경로 길이의 상당 부분은 진공 윈도(예컨대, 진공 윈도(124))에 의해 그 환경으로부터 분리된 국소화된 진공 환경에서 유지된다. 일부 실시예들에서, 진공 챔버(123)는 진공 챔버(123) 내에 유지된 진공 환경으로부터 프로세스 환경(103)을 분리시키는 윈도에 의해 프로세스 챔버(104)와 통합된다. 일부 실시예들에서, x-선 검출기(119)는 프로세스 챔버(104)와 검출기(119) 사이의 빔 경로 길이와 동일한 국소화된 진공 환경에서 유지된다. 예를 들어, 도 1에 묘사된 바와 같이, 진공 챔버(123)는 검출기(119) 및 프로세스 챔버(104)와 검출기(119) 사이의 빔 경로 길이의 상당 부분을 둘러싸는 국소화된 진공 환경을 유지한다.

[0051] 일부 다른 실시예들에서, x-선 검출기(119)는 제어된 대기 환경(예컨대, 가스 퍼지 환경)에서 유지된다. 이것은 검출기(119)로부터 열을 제거하는 데 유리할 수 있다. 그렇지만, 이 실시예들에서, 프로세스 챔버(104)와 검출기(119) 사이의 빔 경로 길이의 상당 부분을 진공 챔버 내의 국소화된 진공 환경에서 유지하는 것이 바람직하다. 일반적으로, 진공 윈도들은 x-선 방사선에 실질적으로 투명한 임의의 적당한 재료(예컨대, 캡톤(Kapton), 베릴륨(Beryllium) 등)로 구성될 수 있다.

[0052] 도 1에 묘사된 실시예에서, 조명 광은 프로세스 챔버(104)의 가스 인젝터 시스템(108)의 하나 이상의 윈도 요소(106)를 통과한다. 가스 인젝터 시스템(108)은 윈도 요소(106)로부터 프로세스 챔버(104) 내로 연장된다. 일부 실시예에서, 윈도 요소(106)와 웨이퍼(101) 사이의 거리는 대략 300 밀리미터이고 가스 인젝터 시스템(108)은 윈도 요소들(106)로부터 웨이퍼(101)를 향해 대략 150 밀리미터 연장된다. 가스 인젝터 시스템(108)은 이온화된 가스 입자들이 윈도 요소들(106)에 충돌하여 이들을 오염시키는 것을 방지하기 위해 x-선 조명 경로를 따라 가스 흐름을 유입시킨다. 예시적인 가스 인젝터 시스템들은 미국 캘리포니아주 프리몬트 소재의 LAM Research Corporation에 의해 제조된다.

[0053] x-선 검출기(119)는 시료(101)로부터 산란되는 x-선 방사선(114)을 수집하고 T-SAXS 측정 모달리티(measurement modality)에 따라 입사 x-선 방사선에 민감한 시료(101)의 속성들을 나타내는 출력 신호들(135)을 발생시킨다. 일부 실시예들에서, 시료 위치결정 시스템(140)이 각도 분해된(angularly resolved) 산란 x-선들을 생성하도록 시료(101)를 위치시키고 배향시키는 동안, 산란 x-선들(114)이 x-선 검출기(119)에 의해 수집된다.

[0054] 일부 실시예들에서, T-SAXS 시스템은 높은 다이내믹 레인지(예컨대,  $10^5$  초과)를 갖는 하나 이상의 광자 계수 검출기(photon counting detectors)를 포함한다. 일부 실시예들에서, 단일 광자 계수 검출기는 검출된 광자들의 위치 및 개수를 검출한다.

[0055] 일부 실시예들에서, x-선 검출기는 하나 이상의 x-선 광자 에너지를 분해하고 시료의 속성들을 나타내는 각각의 x-선 에너지 성분에 대한 신호들을 생성한다. 일부 실시예들에서, x-선 검출기(119)는 CCD 어레이, 마이크로채

널 플레이트(microchannel plate), 포토다이오드 어레이, 마이크로스트립 비례 계수기(microstrip proportional counter), 가스 충전 비례 계수기(gas filled proportional counter), 신틸레이터(scintillator), 또는 형광 재료 중 임의의 것을 포함한다.

[0056] 이러한 방식으로, 검출기 내에서의 X-선 광자 상호작용들은 픽셀 위치 및 카운트 개수(number of counts)에 부가하여 에너지에 의해 구별된다. 일부 실시예들에서, X-선 광자 상호작용들은 X-선 광자 상호작용의 에너지를 미리 결정된 상한 임계 값 및 미리 결정된 하한 임계 값과 비교함으로써 구별된다. 일부 실시예에서, 이 정보는 추가 프로세싱 및 (예컨대, 메모리(190)에의) 저장을 위해 출력 신호들(135)을 통해 컴퓨팅 시스템(130)에 전달된다.

[0057] 추가의 양태에서, T-SAXS 시스템은 산란 광의 하나 이상의 회절 차수에 기초하여 시료의 속성들(예컨대, 구조파라미터 값들)을 결정하는 데 이용된다. 도 1에 묘사된 바와 같이, 시스템(100)은 검출기(119)에 의해 발생된 신호들(135)을 취득하고 취득된 신호들에 적어도 부분적으로 기초하여 시료의 속성들을 결정하며 결정된 관심파라미터들(122)을 메모리(예컨대, 메모리(190))에 저장하는 데 이용되는 컴퓨팅 시스템(130)을 포함한다. 일부 실시예들에서, 컴퓨팅 시스템(130)은 측정 모델을 사용하여 프로세스 중의 웨이퍼들의 산란계측 측정들에 기초하여 하나 이상의 관심 파라미터의 값들을 직접 추정하는 프로세스 제어 계측 엔진으로서 구성된다.

[0058] 다른 양태에서, T-SAXS에 기초한 계측은 측정된 데이터를 이용하여 미리 결정된 측정 모델의 역해법(inverse solution)에 의해 샘플의 치수들을 결정하는 것을 수반한다. 측정 모델은 몇 개의(10개 정도의) 조정가능한 파라미터를 포함하며 시료의 기하구조 및 광학 속성들 및 측정 시스템의 광학 속성들을 나타낸다. 역해법(method of inverse solve)은 모델 기반 회귀, 단층 촬영(tomography), 머신 러닝, 또는 이들의 임의의 조합을 포함하지만, 이들로 제한되지 않는다. 이러한 방식으로, 타깃 프로파일 파라미터들은 측정된 산란 x-선 강도들과 모델링된 결과들 사이의 에러들을 최소화하는 파라미터화된 측정 모델의 값들에 대한 해를 구하는 것에 의해 추정된다.

[0059] 일부 실시예들에서, 측정 모델은 측정 중인 타깃으로부터의 산란을 나타내는 이미지들을 발생시키는 측정의 전자기 모델(예컨대, 본 웨이브 모델(Born Wave Model))이다. 예를 들어, 도 6 및 도 7에 묘사된 이미지들(150내지 152)은 측정 중인 타깃으로부터의 산란을 나타내는 이미지들이다. 모델링된 이미지들은 프로세스 제어 파라미터들(예컨대, 예칭 시간, 예칭 틸트(etch tilt), 예칭 선택도, 퇴적 속도 등)에 의해 파라미터화될 수 있다. 모델링된 이미지들은 측정된 고 종횡비 구조체의 구조 파라미터들(예컨대, 높이, 상이한 높이들에서의 직경, 다른 구조체들에 대한 홀의 정렬, 홀 피처의 진직도(straightness), 홀 피처의 동심도(concentricity), 깊이의 함수로서의 퇴적된 층들의 두께, 특정의 홀 피처를 가로지르는 또는 상이한 홀 피처들 사이의 퇴적된 층들의 균일성 등)에 의해 또한 파라미터화될 수 있다.

[0060] 측정된 산란 이미지들은 관심 파라미터들 중 하나 이상의 관심 파라미터의 값들을 추정하기 위해 역 해법(inverse solve)을 수행함으로써 제조 프로세스를 모니터링하는 데 이용된다. 이 예들에서, 역 해법은 측정된 이미지들과 가장 가깝게 매칭하는 모델링된 산란 이미지들을 발생시키는 프로세스 파라미터들, 기하학적 파라미터들, 또는 둘 다의 값들에 대한 해를 구한다. 일부 예들에서, 회귀법들(예컨대, 그레이디언트 하강(gradient descent) 등)을 사용하는 측정 모델을 사용하여 산란 이미지들의 공간이 탐색된다. 일부 예들에서, 미리 계산된 이미지들의 라이브러리가 발생되고, 모델링된 이미지들과 측정된 이미지들 사이의 최상의 매치(best match)를 결과하는 관심 파라미터들 중 하나 이상의 관심 파라미터의 값들을 구하기 위해 라이브러리가 탐색된다.

[0061] 일부 다른 예들에서, 산란 이미지들의 많은 샘플들과 공지된 프로세스 조건들, 기하학적 파라미터 값들, 또는 둘 다를 관련시키기 위해 머신 러닝 알고리즘에 의해 측정 모델이 트레이닝된다. 이러한 방식으로, 트레이닝된 측정 모델은 측정된 산란 이미지들을 프로세스 파라미터들, 기하학적 파라미터들, 또는 둘 다의 추정된 값들에 매핑한다. 일부 예들에서, 트레이닝된 측정 모델은 실제 측정들과 관심 파라미터들 사이의 직접적인 함수 관계를 정의하는 신호 응답 계측(signal response metrology, SRM) 모델이다.

[0062] 일반적으로, 본 명세서에서 설명되는 트레이닝된 모델들 중 임의의 것은 신경 네트워크 모델로서 구현된다. 다른 예들에서, 트레이닝된 모델들 중 임의의 것은 선형 모델, 비선형 모델, 다항식 모델, 응답 표면 모델(response surface model), 서포트 벡터 머신 모델, 결정 트리 모델, 랜덤 포레스트 모델(random forest model), 딥 네트워크 모델(deep network model), 컨볼루션 네트워크 모델(convolutional network model), 또는 다른 유형들의 모델들로서 구현될 수 있다.

[0063] 일부 예들에서, 본 명세서에서 설명되는 트레이닝된 모델들 중 임의의 것은 모델들의 조합으로서 구현될 수 있

다. 모델 트레이닝 및 반도체 측정들을 위한 트레이닝된 측정 모델들의 사용에 대한 부가의 설명은 Pandev 등의 미국 특허 공개 제2016/0109230호에 제공되어 있으며, 이 미국 특허 공개의 내용은 그 전체가 참고로 본 명세서에 포함된다.

[0064] 일부 다른 예들에서, 예상된(preconceived) 기하형태 및 재료 분포를 포함하지 않는 자유형 모델(free-form model)은 측정 중인 구조체의 기하형태 및 재료 파라미터들을 설명한다. 일부 예들에서, 모델은, 각각이 독립적으로 조정가능한 재료 파라미터 값(예컨대, 전자 밀도, 흡수율, 또는 복소 굴절률)을 갖는, 많은 작은 복셀들(체적 요소들)을 포함한다. 일부 다른 실시예들에서, 재료 속성들은 구분적으로 일정(piecewise constant)하다. 각각의 상이한 재료와 연관된 속성들은 선형적으로(a priori) 결정된다. 상이한 재료들 사이의 경계들은 자유 곡면들(free-form surfaces)이며, 이러한 곡면들은 레벨 설정 알고리즘에 의해 결정될 수 있다.

[0065] 측정된 산란계측 데이터는 샘플의 이미지를 계산하는 데 사용된다. 일부 예들에서, 이미지는 전자 밀도, 흡수율, 복소 굴절률, 또는 이러한 재료 특성들의 조합의 2차원(2-D) 맵이다. 일부 예들에서, 이미지는 전자 밀도, 흡수율, 복소 굴절률, 또는 이러한 재료 특성들의 조합의 3차원(3-D) 맵이다. 이 맵은 상대적으로 적은 물리적 제약조건들을 사용하여 발생된다. 이러한 기술들은 Sezginer 등의 미국 특허 공개 제2015/0300965호에 더욱 상세히 설명되어 있으며, 이 미국 특허 공개의 주제는 그 전체가 참고로 본 명세서에 포함된다.

[0066] 측정된 파라미터 값들의 정밀도 및 정확도를 증가시키기 위해 큰 범위들의 입사각 및 방위각에서 측정들을 수행하는 것이 바람직하다. 이 접근법은 다양한 대각 평면외 배향들(large-angle, out of plane orientations)을 포함하도록 분석에 이용가능한 데이터 세트들의 개수 및 다양성을 확장함으로써 파라미터들 간의 상관들을 감소시킨다. 예를 들어, 법선 배향(normal orientation)에서, T-SAXS는 피처의 임계 치수를 분해할 수 있지만, 피처의 측벽 각도 및 높이에 대체로 둔감하다. 그렇지만, 넓은 범위의 평면외 각도 배향들에 걸쳐 측정 데이터를 수집하는 것에 의해, 피처의 측벽 각도 및 높이가 분해될 수 있다. 다른 예들에서, 큰 범위들의 입사각 및 방위각에서 수행되는 측정들은 고 종횡비 구조체들을 그들의 전체 깊이에 걸쳐 특성화하기에 충분한 분해능 및 침투 깊이를 제공한다.

[0067] 웨이퍼 표면 법선에 대한 x-선 입사각의 함수인 회절 방사선의 강도의 측정들이 수집된다. 다수의 회절 차수들에 포함된 정보는 전형적으로 고려 중인 각각의 모델 파라미터 간에 고유하다. 따라서, x-선 산란은 작은 에러들 및 감소된 파라미터 상관을 갖는 관심 파라미터들의 값들에 대한 추정 결과들을 산출한다.

[0068] 반도체 웨이퍼(101)의 표면 법선에 대한 조명 x-선 빔(116)의 각각의 배향이 x-선 조명 빔(115)에 대한 웨이퍼(101)의 임의의 2개의 각도 회전에 의해 설명되거나, 그 반대도 마찬가지이다. 일 예에서, 배향은 웨이퍼에 고정된 좌표계와 관련하여 설명될 수 있다. 도 2는 입사각( $\Theta$ ) 및 방위각( $\Phi$ )에 의해 설명되는 특정의 배향에서 웨이퍼(101)에 입사하는 x-선 조명 빔(116)을 묘사한다. 좌표 프레임 XYZ는 계측 시스템(예컨대, 조명 빔(116))에 고정되고 좌표 프레임 X'Y'Z'은 웨이퍼(101)에 고정된다. Y 축은 웨이퍼(101)의 표면과 평면 내에(in plane) 정렬된다. X 및 Z는 웨이퍼(101)의 표면과 정렬되지 않는다. Z'은 웨이퍼(101)의 표면에 수직(normal)인 축과 정렬되고, X' 및 Y'은 웨이퍼(101)의 표면과 정렬된 평면에 있다. 도 2에 묘사된 바와 같이, x-선 조명 빔(116)은 Z-축과 정렬되며 따라서 XZ 평면 내에 놓인다. 입사각( $\Theta$ )은 XZ 평면에서의 웨이퍼의 표면 법선에 대한 x-선 조명 빔(116)의 배향을 나타낸다. 게다가, 방위각( $\Phi$ )은 X'Z' 평면에 대한 XZ 평면의 배향을 나타낸다.  $\Theta$ 와  $\Phi$ 는, 함께, 웨이퍼(101)의 표면에 대한 x-선 조명 빔(116)의 배향을 일의적으로 정의한다. 이 예에서, 웨이퍼(101)의 표면에 대한 x-선 조명 빔의 배향은 웨이퍼(101)의 표면에 수직인 축(즉, Z' 축)을 중심으로 한 회전 및 웨이퍼(101)의 표면과 정렬된 축(즉, Y 축)을 중심으로 한 회전에 의해 설명된다. 일부 다른 예들에서, 웨이퍼(101)의 표면에 대한 x-선 조명 빔의 배향은 웨이퍼(101)의 표면과 정렬된 제1 축 및 웨이퍼(101)의 표면과 정렬되고 제1 축에 수직인 다른 축을 중심으로 한 회전에 의해 설명된다.

[0069] 일 양태에서, 웨이퍼 프로세싱 시스템(100)은 조명 빔(116)에 대해 6개의 자유도에서 시료(101)를 능동적으로 위치결정하도록 구성된 시료 위치결정 시스템(140)을 포함한다. 그에 부가하여, 시료 위치결정 시스템(101)은 시료(101)를 정렬시키고 조명 빔(116)에 대해 큰 범위의 입사각들(예컨대, 적어도 70도) 및 방위각(예컨대, 적어도 190도)에 걸쳐 시료(101)를 배향시키도록 구성된다. 일부 실시예들에서, 시료 위치결정 시스템(140)은 시료(101)의 표면과 평면 내에 정렬된 큰 범위의 회전 각도들(예컨대, 적어도 70도)에 걸쳐 시료(101)를 회전시키도록 구성된다. 이러한 방식으로, 시료(101)의 각도 분해된 측정들이 시료(101)의 표면 상의 임의의 개수의 위치들 및 배향들에 걸쳐 x-선 산란계에 의해 수집된다. 일 예에서, 컴퓨팅 시스템(130)은 시료(101)의 원하는 위치를 지시하는 커맨드 신호들(139)을 시료 위치결정 시스템(140)에 전달한다. 이에 응답하여, 시료 위치결정

시스템(140)은 시료(101)의 원하는 위치결정을 달성하기 위해 시료 위치결정 시스템(140)의 다양한 액추에이터들에 대한 커맨드 신호들을 발생시킨다.

[0070] 일부 다른 실시예들에서, x-선 산란계 시스템은 측정 중인 웨이퍼에 대해 회전하도록 구성된다. 이 실시예들에서, 웨이퍼는 XY 평면에서 이동되고, x-선 산란계의 광학 요소들은 웨이퍼(101) 상의 조명 빔(116)의 입사 지점(point of incidence)을 중심으로 회전된다.

[0071] 피측정 시료의 산란 효율은 추출된 산란 강도들을 입사각들의 세트  $\{\theta, \phi\}$ 에 대한 계측 타깃의 기하형태 및 재료들과 관련시킨다. 도 8은 입사각( $\theta$ )의 함수로서의 제로 차수 빔의 산란 효율( $S_{00}$ )의 플롯(153)을 묘사한다. 타깃을 통한 투과가 증가된 경로 길이로 인해 보다 높은 입사각들에서 감소하기 때문에  $S_{00}$ 은 입사각에 의존한다. 그에 부가하여, 입사각이 타깃의 산란과 정렬될 때(예컨대, 수직 입사) 에너지가 제로 차수(zero order)를 떠나 보다 높은 회절 차수들에 들어가기 때문에  $S_{00}$ 은 입사각에 의존한다.

[0072] 도 9는 입사각( $\theta$ )의 함수로서의 몇 개의 고차의 산란 효율을 묘사한다. 플롯라인(154)은  $S_{11}$ 을 묘사하고, 플롯라인(155)은  $S_{13}$ 을 묘사하며, 플롯라인(156)은  $S_{20}$ 을 묘사하고, 플롯라인(157)은  $S_{22}$ 를 묘사한다. 모든 상위 차수들에 대한 산란 강도는 전형적으로 산란 깊이 또는 밀도에 의존한다. 일반적으로, 제로 차수의 산란 진폭은 산란 깊이가 증가함에 따라 감소하는 반면, 하나 걸러 하나의 산란 차수의 산란 진폭은 산란 깊이가 증가함에 따라 증가한다.

[0073] 다른 양태에서, 프로세스 보정들은 관심 파라미터들(예컨대, 임계 치수, 오버레이, 높이, 측벽 각도 등)의 측정된 값들에 기초하여 결정되고, 보정들은 프로세스 툴(예컨대, 리소그래피 툴, 에칭 툴, 퇴적 툴 등)의 하나 이상의 프로세스 제어 파라미터를 변경하기 위해 프로세스 툴에 전달된다. 일부 실시예들에서, 피측정 구조체에 대해 프로세스가 실행되고 있는 동안 SAXS 측정들이 수행되고 프로세스 제어 파라미터들이 업데이트된다. 일부 실시예들에서, 특정의 프로세스 단계 이후에 SAXS 측정들이 수행되고, 그 프로세스 단계에 의한 미래의 디바이스들의 프로세싱을 위해 그 프로세스 단계와 연관된 프로세스 제어 파라미터들이 업데이트된다. 일부 실시예들에서, 특정의 프로세스 단계 이후에 SAXS 측정들이 수행되고, 후속 프로세스 단계에 의한 피측정 디바이스 또는 다른 디바이스들의 프로세싱을 위해 후속 프로세스 단계와 연관된 프로세스 제어 파라미터들이 업데이트된다.

[0074] 일부 예들에서, 본 명세서에서 설명된 측정 방법들에 기초하여 결정되는 측정된 파라미터들의 값들은 원하는 에칭 깊이를 달성하도록 에칭 시간을 조정하기 위해 에칭 툴에 전달될 수 있다. 유사한 방식으로, 에칭 파라미터들(예컨대, 에칭 시간, 확산도(diffusivity) 등) 또는 퇴적 파라미터들(예컨대, 시간, 농도 등)이, 제각기, 에칭 툴들 또는 퇴적 툴들에 능동 피드백을 제공하기 위해 측정 모델에 포함될 수 있다. 일부 예들에서, 측정된 디바이스 파라미터 값들에 기초하여 결정되는 프로세스 파라미터들에 대한 보정들이 프로세스 툴에 전달될 수 있다. 일 실시예에서, 컴퓨팅 시스템(130)은 계측 시스템(101)으로부터 수신되는 측정된 신호들(135)에 기초하여 프로세스 동안 하나 이상의 관심 파라미터의 값들을 결정한다. 그에 부가하여, 컴퓨팅 시스템(130)은 하나 이상의 관심 파라미터의 결정된 값들에 기초하여 제어 커맨드들(136)을 프로세스 제어기(109)에 전달한다. 제어 커맨드들(136)은 프로세스 제어기(109)로 하여금 프로세스의 상태를 변경하게(예컨대, 에칭 프로세스를 중지시키게, 확산도를 변경하게 등) 한다. 일 예에서, 제어 커맨드(136)는 원하는 에칭 깊이가 측정될 때 프로세스 제어기(109)로 하여금 에칭 프로세스를 중지시키게 한다. 다른 예에서, 제어 커맨드(136)는 프로세스 제어기(109)로 하여금 CD 파라미터의 측정된 웨이퍼 균일성을 개선시키도록 에칭 속도를 변경하게 한다.

[0075] 일반적으로, 입사 x-선 조명이 주기적인 피쳐들과 상호작용할 때, x-선 조명은 코히런트하게 산란되어 겹출기(119) 상에 회절 이미지(예컨대, 도 6 및 도 7에 묘사된 이미지들(150 내지 152)을 생성한다. 프로세스 툴이 적절히 튜닝될 때 원하는 산란 이미지 또는 산란 이미지들의 시퀀스가 달성된다. 그렇지만, 측정된 이미지들이 원하는 이미지 또는 원하는 이미지들의 시퀀스로부터 벗어날 때, 이러한 편차들은 프로세스 툴 드리프트 및 프로세스 툴을 다시 적절히 튜닝시키는 데 요구되는 프로세스 제어 변수들에 대한 보정들을 나타낸다.

[0076] 도 3은 에칭 프로세스를 거치는 2개의 홀 피쳐를 포함하는 반도체 구조체(141)를 예시하는 다이어그램이다. 도 3에 묘사된 바와 같이, 홀의 초기 프로파일(142)은 에칭 프로세스에 의해 확대된 프로파일(143)로 변경된다. 도 3에 묘사된 바와 같이, x-선 조명(116)은 관심 타깃에 있는 구조체(141) 쪽으로 지향된다. 이 입사 위치는 디바이스 수율에 아주 중요한(critical) 프로세스의 양태들을 가장 잘 나타내도록 선택된다. 에칭 프로세스가 진행됨에 따라, 홀 피쳐들의 깊이 및 홀 피쳐들의 폭이 변한다.

[0077] 도 4는 퇴적 프로세스를 거치는 2개의 홀 피쳐를 포함하는 반도체 구조체(144)를 예시하는 다이어그램이다. 도

4에 묘사된 바와 같이, 홀의 초기 프로파일(145)은 퇴적 프로세스에 의해 축소된 프로파일(145)로 변경된다. 도 4에 묘사된 바와 같이, x-선 조명(116)은 관심 타깃에 있는 구조체(144) 쪽으로 지향된다. 이 입사 위치는 디바이스 수율에 아주 중요한 프로세스의 양태들을 가장 잘 나타내도록 선택된다. 퇴적 프로세스가 진행됨에 따라, 홀 피처들의 깊이 및 홀 피처들의 폭이 변한다.

[0078] 도 6은 예칭된 홀의 크기의 변화들을 예시하는 산란 이미지들(150 및 151)을 묘사한다. 예칭된 홀 피처가 예칭 프로세스 동안 크기가 변할 때, 예칭된 피처의 공간 푸리에 변환이 변하여 회절 패턴의 변화를 야기한다. 차수들에 걸친 강도 패턴이 축소됨(shrinks) 때, 이는 피처 크기가 증가하고 있음(예컨대, 홀 피처의 직경이 증가하고 있음)을 나타낸다. 홀 직경의 원하지 않는 증가를 피하기 위해, 프로세스 제어 파라미터(예컨대, 예칭 시간)가 홀 직경의 원하지 않는 증가를 방지하도록 조정된다.

[0079] 도 7은 예칭된 홀의 깊이의 변화들을 예시하는 산란 이미지들(150 및 152)을 묘사한다. 예칭된 홀이 예칭 프로세스 동안 깊어지거나 퇴적 프로세스 동안 보다 얕아지게 될 때, 예칭된 피처의 공간 푸리에 변환이 변하여 검출된 회절 패턴의 강도의 변화를 야기한다. 차수들에 걸친 강도가 증가할 때, 이는 홀 깊이가 증가하고 있음을 나타내거나, 이와 반대로, 차수들에 걸친 강도가 감소할 때, 이는 홀 깊이가 감소하고 있음을 나타낸다. 홀 깊이의 원하지 않는 변화를 피하기 위해, 프로세스 제어 파라미터(예컨대, 예칭 시간, 바이어스 전압 등)가 홀 깊이의 원하지 않는 변화를 방지하도록 조정된다.

[0080] 도 5는, 각각이 2개의 홀 피처를 포함하는, 2개의 총을 포함하는 반도체 구조체(147)를 예시하는 다이어그램이다. 제1 총은 충전된(filled) 홀(148)을 포함한다. 제2 총은 충전되지 않은(unfilled) 홀(149)을 포함한다. 도 5에 묘사된 바와 같이, 제2 총의 홀(149)은 틸팅되고 제1 총의 충전된 홀(148)에 대해 정렬 에러 거리(alignment error distance, AE)만큼 오프셋된다. 도 5에 묘사된 바와 같이, x-선 조명(116)은 관심 타깃에 있는 구조체(147) 쪽으로 지향된다. 이 입사 위치는 디바이스 수율에 아주 중요한(critical) 프로세스의 양태들을 가장 잘 나타내도록 선택된다.

[0081] 프로세싱된 구조체(즉, 홀(149))에 대한 하부 구조체(즉, 홀(148))로부터 검출된 산란의 위상은 정렬 에러 거리(AE)의 표시를 제공한다. x-선 조명(116)의 입사각에 대한 프로세싱된 구조체로부터의 산란은 홀(149)의 틸트의 표시를 제공한다. 이러한 측정된 신호들은, 함께, 오버레이 에러 및 틸트의 추정을 가능하게 해준다. 차례로, 에지 배치 에러들은 틸트를 보정하기 위해 예칭 툴의 프로세스 제어 파라미터들을 보정하는 것 및 오버레이 에러를 보정하기 위해 리소그래피 툴의 프로세스 제어 파라미터들을 보정하는 것에 의해 보정된다. 오버레이 및 홀 틸트의 모니터링에 대한 부가의 설명은 미국 특허 출원 제2015/0117610호에서 제공되며, 이 미국 특허 출원의 주제는 그 전체가 본 명세서에 참고로 포함된다.

[0082] 일반적으로, 계측 타깃은 계측 타깃의 최대 높이 치수(즉, 웨이퍼 표면에 수직인 치수)를 최대 측면 범위 치수(maximum lateral extent dimension)(즉, 웨이퍼 표면과 정렬된 치수)로 나눈 것으로서 정의되는 종횡비에 의해 특성화된다. 일부 실시예들에서, 측정 중인 계측 타깃은 적어도 20의 종횡비를 갖는다. 일부 실시예들에서, 계측 타깃은 적어도 40의 종횡비를 갖는다.

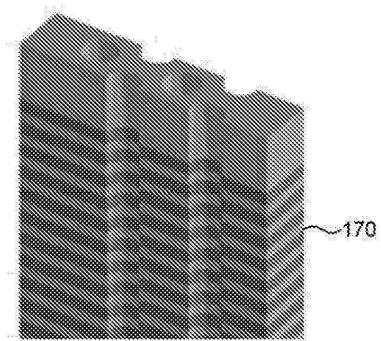

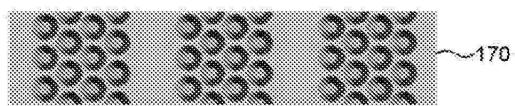

[0083] 도 12a 내지 도 12c는 본 명세서에서 설명되는 방식으로 측정을 거치는 전형적인 3D FLASH 메모리 디바이스(170)의 등각도, 평면도, 및 단면도를, 제각기, 묘사한다. 메모리 디바이스(170)의 총 높이(또는 등가적으로 깊이)는 1 내지 수 마이크로미터의 범위이다. 메모리 디바이스(170)는 수직으로 제조된 디바이스이다. 메모리 디바이스(170)와 같은, 수직으로 제조된 디바이스는 본질적으로 종래의 평면 메모리 디바이스를 90도 회전시켜, 비트 라인과 셀 스트링을 수직으로(웨이퍼 표면에 수직으로) 배향한다. 충분한 메모리 용량을 제공하기 위해, 상이한 재료들의 많은 수의 교호 층들이 웨이퍼 상에 퇴적된다. 이것은 패터닝 프로세스가 100 나노미터 이하의 최대 측면 범위를 갖는 구조체들에 대해 수 마이크론의 깊이들까지 잘 수행될 것을 요구한다. 그 결과, 25 대 1 또는 50 대 1의 종횡비들이 드문 일이 아니다.

[0084] 도 10은 고 종횡비 홀 구조체들의 어레이(160)의 평면도를 묘사한다. 도 10에 묘사된 바와 같이, 홀 구조체들의 어레이(160)는 (도면으로 들어가고 도면으로부터 나오게 연장되는) 평면들(161, 162, 163, 및 164)을 따라 가장 가깝게 패터닝된다. 일부 실시예들에서, 고 종횡비 구조체들의 어레이가 가장 가깝게 패터닝되는 평면들 내에 놓이는 측정 중인 웨이퍼의 표면에 대한 입사 x-선 조명 빔의 배향들에서 본 명세서에서 설명된 바와 같이 고 종횡비 구조체들의 측정들을 수행하는 것이 바람직하다. 도 10에 묘사된 예에서, 홀 구조체들의 어레이가 가장 가깝게 패터닝되는 평면들(161, 162, 163, 및 164) 내의 홀 구조체들의 어레이(160)에 x-선 조명을 제공하는 것이 바람직하다.

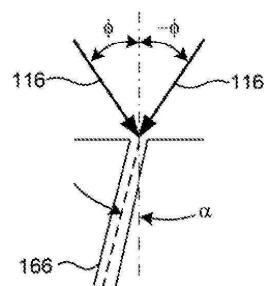

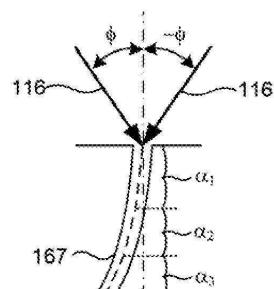

- [0085] 도 11a는 이상적인 고 종횡비 홀 구조체(165)의 측면도를 묘사한다. 도 11b는 털팅된 홀 구조체(166)의 측면도를 묘사한다. 도 11c는 점진적으로 털팅된 홀 구조체(167)의 측면도를 묘사하며, 여기서 털트 정도(degree of tilt)는 깊이에 따라 점진적으로 증가한다. 많은 예들에서, 홀 구조체들(166 및 167)은 바람직하지 않다. 일부 실시예들에서, 홀 구조체들(166 및 167)과 비슷한 홀 구조체들은 본 명세서에서 설명된 바와 같이 T-SAXS 측정들에 의해 특성화된다. 일 예에서, 홀 구조체(166)는 털트각 파라미터( $\alpha$ )에 의해 특성화된다. 게다가, x-선 조명 빔(116)은, 예를 들어, 도 2를 참조하여 설명된 바와 같이, 표면 법선에 대해 각도( $\phi$ )로 그리고 반대 각도(- $\phi$ )로 홀 구조체(166)에 제공된다. 일부 실시예들에서, 이 2개의 조명 시나리오에서 발생하는 측정된 T-SAX 신호들의 차이들은 털트각( $\alpha$ )을 정확하게 추정하기에 충분한 신호 정보를 제공한다.

- [0086] 다른 예에서, 홀 구조체(167)는 다수의 털트각 파라미터( $\alpha_1$ ,  $\alpha_2$ , 및  $\alpha_3$ )에 의해 구분적으로 특성화된다. 이와 유사하게, x-선 조명 빔(116)은, 예를 들어, 도 2를 참조하여 설명된 바와 같이, 표면 법선에 대해 각도( $\phi$ )로 그리고 반대 각도(- $\phi$ )로 홀 구조체(167)에 제공된다. 일부 실시예들에서, 이 2개의 조명 시나리오에서 발생하는 측정된 T-SAX 신호들의 차이들은 털트각들( $\alpha_1$ ,  $\alpha_2$ , 및  $\alpha_3$ )을 정확하게 추정하기에 충분한 신호 정보를 제공한다.

- [0087] 도 1에 묘사된 실시예에서, T-SAXS 계측 시스템은 프로세스 툴과 통합되고, 프로세스가 수행되는 동안 측정 결과들을 프로세스 툴에 제공한다. 그렇지만, 일반적으로, T-SAXS 계측 시스템은 독립형 툴로서 구현될 수 있다. 이 실시예들에서, 프로세스 단계가 완료되어야 하고 웨이퍼(101)가 측정을 위해 독립형 T-SAXS 툴로 이송되어야 한다. 프로세스 제어 변수들에 대한 변경들은 후속 웨이퍼들의 프로세싱을 위해 프로세스 툴에 전달된다.

- [0088] 제조 중인 특정의 고 종횡비 구조체의 측정 빈도수는 모니터링된 프로세스 파라미터의 안정성에 의존한다. 더욱이, 요구된 측정 시간의 길이는 모니터링된 프로세스 변수의 변화들에 대한 산란 감도에 의존한다. 산란 신호를 인-시츄로 측정하는 것은 프로세스 조건들의 가장 빠른 측정을 그러나 가장 높은 불확실성으로 제공한다. 반면에, 보다 긴 측정 시간들은 측정된 파라미터들의 보다 큰 정밀도 및 확실성을 제공한다. 일반적으로, 전체 산란 체적(entire scattering volume)에 영향을 미치는 프로세스 파라미터들(예컨대, 애칭 시간)은 가장 빠르게 모니터링될 수 있는 반면, 다른 파라미터들(예컨대, 애칭 프로파일의 사소한 편차들)은 이동 평균 또는 보다 긴 측정 시간 중 어느 하나가 의미있는 결과들을 달성할 것을 요구한다. 따라서, 이러한 파라미터들은 보다 느리게 제어될 수 있을 뿐이다. 측정들이 인-시츄로 수행되든 독립형 툴에서 수행되든 간에 감도와 요구된 측정 시간 사이의 트레이드오프가 존재한다. 그렇지만, 보다 긴 측정들은 그 특정의 측정을 위해 설계된 보다 안정적인 독립형 툴에서 전형적으로 보다 정확하게 수행된다.

- [0089] 도 1이 투과 SAXS 측정 시스템을 묘사하지만, 일반적으로, 반사 SAXS 측정 시스템이 얇은 피처들을 측정하는 데 이용될 수 있다.

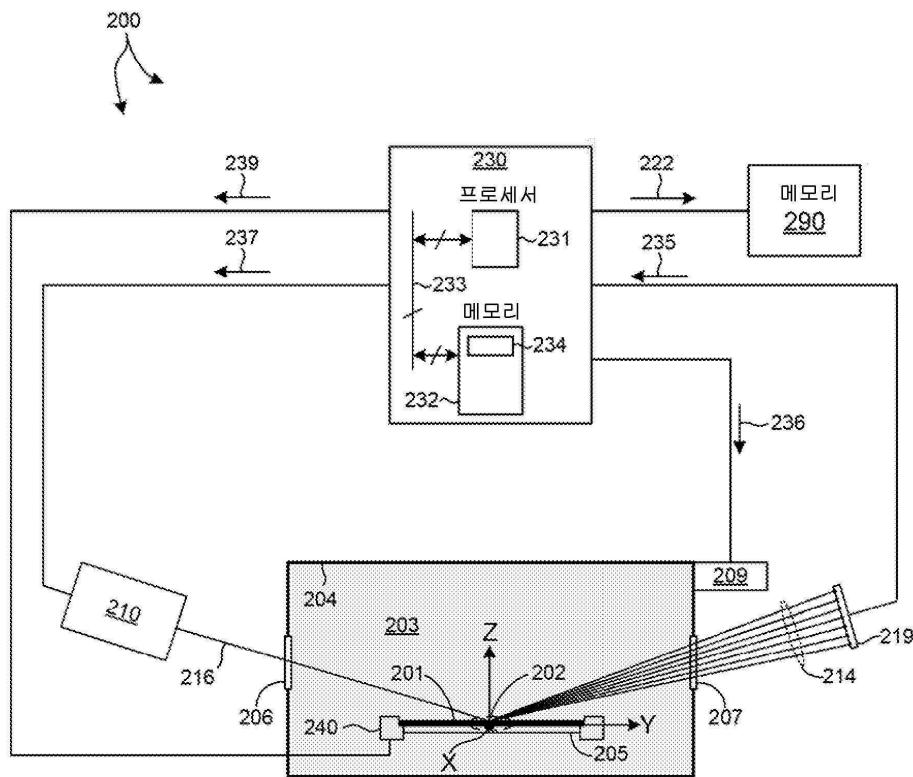

- [0090] 도 13은 프로세스 중의 웨이퍼 상에 배치된 반도체 구조체들의 x-선 산란계측 측정들에 기초하여 애칭 프로세스를 모니터링하기 위한 예시적인 웨이퍼 프로세싱 시스템(200)을 묘사한다. 일 양태에서, 반사 산란계측 계측 시스템은 애칭 프로세스 툴과 통합된다. 관심 파라미터들의 측정된 값들은 애칭 프로세스 툴을 제어하기 위한 피드백으로서 제공된다.

- [0091] 웨이퍼 프로세싱 시스템(200)은 반사 x-선 산란계 및 프로세스 환경(203)을 포함하는 프로세스 챔버(204)를 포함한다. 반도체 웨이퍼(201)는 프로세스 챔버(204) 내에 위치된다. 웨이퍼(201)는 웨이퍼 척(205)에 부착되고 웨이퍼 스테이지(240)에 의해 프로세스 챔버(204) 및 x-선 산란계에 대해 위치결정된다.

- [0092] 일 실시예에서, 프로세스 챔버(204)는 반응성 이온 애칭 시스템의 요소이다. 이 실시예에서, 프로세스 환경(203)은 웨이퍼(201)의 표면 상의 노출된 재료를 애칭 제거하는 라디오 주파수 유도 플라스마를 포함한다.

- [0093] 묘사된 실시예에서, SAXS 계측 시스템은 도 1을 참조한 조명 소스(110)의 설명과 유사한 반사 SAXS 측정들에 적당한 x-선 방사선을 발생시키도록 구성된 x-선 조명 소스(210)를 포함한다.

- [0094] 일부 예들에서, 컴퓨팅 시스템(130)은 x-선 조명 소스(210)로 하여금 원하는 에너지 레벨의 x-선 방사선을 방출하게 하는 커맨드 신호들(237)을 x-선 조명 소스(210)에 전달한다. 측정 중인 고 종횡비 구조체들에 관한 추가 정보와 함께 측정 데이터를 취득하기 위해 에너지 레벨이 변경된다.

- [0095] 조명 빔(216)은 프로세스 챔버(204)의 원도(206)를 통하여 측정 스풋(201) 위의 시료(201)를 조명한다. 웨이퍼(201)에의 입사 후에, 산란 x-선 방사선(214)은 원도(207)를 통해 프로세스 챔버(204)를 빠져나간다. 일부 실시예들에서, 프로세스 챔버(204)와 겸출기(219) 사이의 광학 경로 길이(즉, 수집 빔 경로)는 길고, 공기 중에

서의 x-선 산란은 검출기 상의 이미지에 노이즈를 제공한다. 따라서, 양호한 실시예들에서, 프로세스 챔버(204)와 검출기(219) 사이의 수집 빔 경로 길이의 상당 부분은 국소화된 진공 환경에서 유지된다.

[0096] x-선 검출기(219)는 시료(201)로부터 산란되는 x-선 방사선(214)을 수집하고 반사 T-SAXS 측정 모달리티에 따라 입사 x-선 방사선에 민감한 시료(201)의 속성을 나타내는 출력 신호들(235)을 발생시킨다. 일부 실시예들에서, 시료 위치결정 시스템(240)이 컴퓨팅 시스템(230)으로부터 시료 위치결정 시스템(240)에 전달된 커맨드 신호들(239)에 따라 각도 분해된 산란 x-선들을 생성하도록 시료(201)를 위치시키고 배향시키는 동안, 산란 x-선들(214)이 x-선 검출기(219)에 의해 수집된다.

[0097] 추가의 양태에서, 컴퓨팅 시스템(230)은 산란 광의 하나 이상의 회절 차수에 기초하여 웨이퍼(201)의 속성들(예컨대, 구조 파라미터 값들)을 결정하는 데 이용된다. 도 13에 묘사된 바와 같이, 시스템(200)은 검출기(219)에 의해 발생된 신호들(235)을 취득하고 취득된 신호들에 적어도 부분적으로 기초하여 시료의 속성을 결정하며 관심 파라미터들의 결정된 값들의 표시(222)를 메모리(예컨대, 메모리(290))에 저장하는 데 이용되는 컴퓨팅 시스템(230)을 포함한다. 일부 실시예들에서, 컴퓨팅 시스템(230)은 측정 모델을 사용하여 프로세스 중의 웨이퍼들의 산란계측 측정들에 기초하여 하나 이상의 관심 파라미터의 값들을 직접 추정하는 프로세스 제어 계측 엔진으로서 구성된다.

[0098] 그에 부가하여, 컴퓨팅 시스템(130)은 하나 이상의 관심 파라미터의 결정된 값들에 기초하여 제어 커맨드들(236)을 프로세스 제어기(209)에 전달한다. 제어 커맨드들(236)은 프로세스 제어기(209)로 하여금 프로세스의 상태를 변경하게(예컨대, 애칭 프로세스를 중지시키게, 확산도를 변경하게 등) 한다.

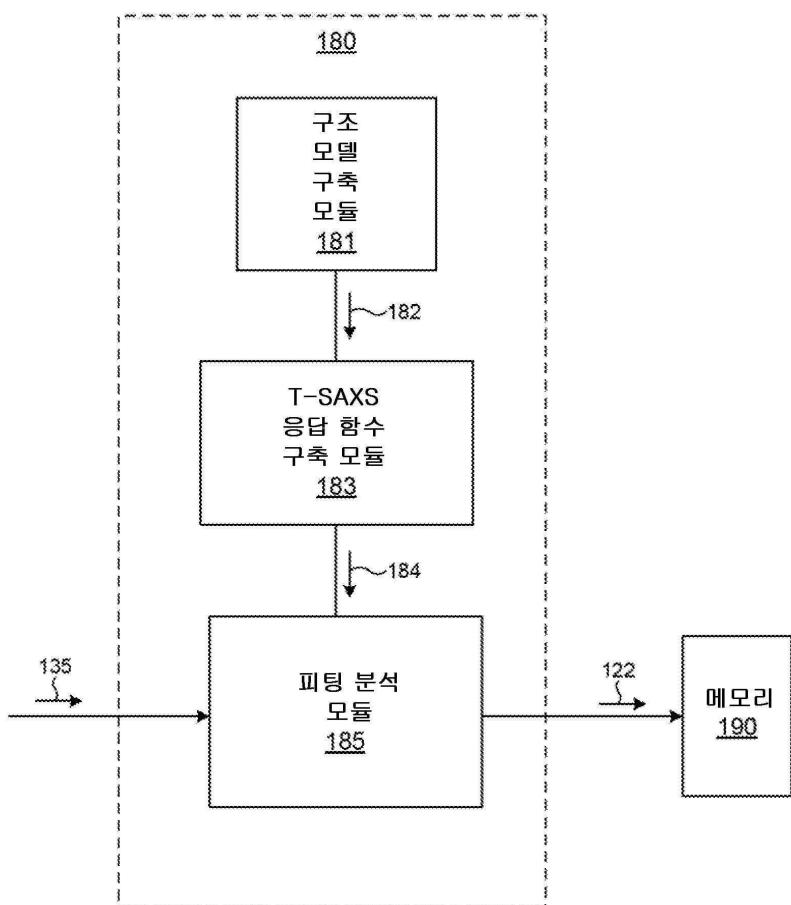

[0099] 도 14는 컴퓨팅 시스템(130)에 의해 구현된 예시적인 모델 구축 및 분석 엔진(180)을 예시하는 다이어그램이다. 도 14에 묘사된 바와 같이, 모델 구축 및 분석 엔진(180)은 시료의 측정된 구조체의 구조 모델(182)을 발생시키는 구조 모델 구축 모듈(181)을 포함한다. 일부 실시예들에서, 구조 모델(182)은 시료의 재료 속성을 또한 포함한다. 구조 모델(182)은 T-SAXS 응답 함수 구축 모듈(183)에 대한 입력으로서 수신된다. T-SAXS 응답 함수 구축 모듈(183)은 구조 모델(182)에 적어도 부분적으로 기초하여 T-SAXS 응답 함수 모델(184)을 발생시킨다. 일부 예들에서, T-SAXS 응답 함수 모델(183)은 x-선 폼 팩터들(x-ray form factors)에 기초하며,

## 수학식 1

$$F(\vec{q}) = \int \rho(\vec{r}) e^{-i\vec{q} \cdot \vec{r}} d\vec{r}$$

[0100] 여기서  $F$ 는 폼 팩터이고,  $q$ 는 산란 벡터이며,  $\rho(r)$ 은 구면 좌표들(spherical coordinates)로 된 시료의 전자밀도이다. x-선 산란 강도는 그러면 수학식 2에 의해 주어진다.

## 수학식 2

$$I(\vec{q}) = F^* F$$

[0103] T-SAXS 응답 함수 모델(184)은 피팅 분석 모듈(fitting analysis module)(185)에 대한 입력으로서 수신된다. 피팅 분석 모듈(185)은 모델링된 T-SAXS 응답을 대응하는 측정된 데이터(135)와 비교하여 시료의 기하학적 속성들은 물론 재료 속성을 결정한다.

[0104] 일부 예들에서, 실험 데이터에 대한 모델링된 데이터의 피팅은 카이 제곱 값(chi-squared value)을 최소화함으로써 달성된다. 예를 들어, T-SAXS 측정들의 경우, 카이 제곱 값은 수학식 3으로서 정의될 수 있다.

### 수학식 3

$$\chi^2_{\text{SAXS}} = \frac{1}{N_{\text{SAXS}}} \sum_j N_{\text{SAXS}} \frac{(S_j^{\text{SAXS model}}(v_1, \dots, v_L) - S_j^{\text{SAXS experiment}})^2}{\sigma_{\text{SAXS}, j}^2}$$

[0105] 여기서,  $S_j^{\text{SAXS experiment}}$  는 "채널"  $j$ 에서의 측정된 T-SAXS 신호들(126)이고, 여기서 인덱스  $j$ 는 회절 차수, 에너지, 각도 좌표 등과 같은 시스템 파라미터들의 세트를 나타낸다.  $S_j^{\text{SAXS model}}(v_1, \dots, v_L)$ 는, 구조체(타깃) 파라미터들의 세트( $v_1, \dots, v_L$ )에 대해 평가된, "채널"  $j$ 에 대한 모델링된 T-SAXS 신호( $S_j$ )이며, 여기서 이러한 파라미터들은 기하학적 속성들(CD, 측벽 각도, 오버레이 등) 및 재료 속성들(전자 밀도 등)을 나타낸다.  $\sigma_{\text{SAXS}, j}$ 는 제  $j$  채널과 연관된 불확실성이다.  $N_{\text{SAXS}}$ 는 x-선 계측에서의 채널들의 총수이다.  $L$ 은 계측 타깃을 특성화하는 파라미터들의 개수이다.

[0107] 수학식 3은 상이한 채널들과 연관된 불확실성들이 상관되지 않는다고 가정한다. 상이한 채널들과 연관된 불확실성들이 상관되는 예들에서는, 불확실성들 사이의 공분산(covariance)이 계산될 수 있다. 이러한 예들에서, T-SAXS 측정들을 위한 카이 제곱 값은 수학식 4로서 표현될 수 있고,

### 수학식 4

$$\chi^2_{\text{SAXS}} = \frac{1}{N_{\text{SAXS}}} \left( \vec{S}_j^{\text{SAXS, model}}(v_1, \dots, v_M) - \vec{S}_j^{\text{SAXS, experiment}} \right)^T V_{\text{SAXS}}^{-1} \left( \vec{S}_j^{\text{SAXS, model}}(v_1, \dots, v_M) - \vec{S}_j^{\text{SAXS, experiment}} \right)$$

[0109] 여기서,  $V_{\text{SAXS}}$ 는 SAXS 채널 불확실성들의 공분산 행렬이고,  $T$ 는 전치행렬(transpose)을 나타낸다.

[0110] 일부 예들에서, 피팅 분석 모듈(185)은 T-SAXS 응답 모델(184)을 이용하여 T-SAXS 측정 데이터(135)에 대한 피팅 분석을 수행함으로써 적어도 하나의 시료 파라미터 값을 분해한다. 일부 예들에서,  $\chi^2_{\text{SAXS}}$ 는 최적화되어 있다.

[0111] 위에서 설명된 바와 같이, T-SAXS 데이터의 피팅은 카이 제곱 값을 최소화함으로써 달성된다. 그렇지만, 일반적으로, T-SAXS 데이터의 피팅은 다른 함수들에 의해 달성될 수 있다.

[0112] T-SAXS 계측 데이터의 피팅은 관심의 기하학적 및/또는 재료 파라미터들에 대한 감도를 제공하는 임의의 유형의 T-SAXS 기술에 유리하다. 시료와의 T-SAXS 빔 상호작용을 설명하는 적절한 모델들이 사용되는 한, 시료 파라미터들은 결정적(예컨대, CD, SWA 등) 또는 통계적(예컨대, 측벽 조도(sidewall roughness)의 rms 높이, 조도 상관 길이(roughness correlation length) 등)일 수 있다.

[0113] 일반적으로, 컴퓨팅 시스템(130)은, RTCD(Real Time Critical Dimensioning)를 이용하여, 실시간으로 모델 파라미터들에 액세스하도록 구성되거나, 시료(101)와 연관된 적어도 하나의 시료 파라미터 값의 값을 결정하기 위해 미리 계산된 모델들의 라이브러리들에 액세스할 수 있다. 일반적으로, 시료의 할당된 CD 파라미터들과 측정된 시료와 연관된 CD 파라미터들 사이의 차이를 평가하기 위해 어떤 형태의 CD-엔진이 사용될 수 있다. 시료 파라미터 값을 계산하기 위한 예시적인 방법들 및 시스템들은 2010년 11월 2일자로 KLA-Tencor Corp.에게 등록된 미국 특허 제7,826,071호에 설명되어 있으며, 이 미국 특허 전체는 본 명세서에 참고로 포함된다.

[0114] 일부 예들에서, 모델 구축 및 분석 엔진(180)은 피드 사이드웨이 분석(feed sideways analysis), 피드 포워드 분석(feed forward analysis), 및 병렬 분석(parallel analysis)의 임의의 조합에 의해 측정된 파라미터들의

정확도를 개선시킨다. 피드 사이드웨이 분석은 동일한 시료의 상이한 영역들 상에서 다수의 데이터 세트들을 취하고 제1 데이터 세트로부터 결정되는 공통 파라미터들을 분석을 위해 제2 데이터 세트 상으로 전달하는 것을 말한다. 피드 포워드 분석은 상이한 시료들 상에서 데이터 세트들을 취하고 공통 파라미터들을 단계별 사본의 정확한 파라미터 피드 포워드 접근법(stepwise copy exact parameter feed forward approach)을 사용하여 후속 분석들로 순방향으로 전달하는 것을 말한다. 병렬 분석은, 피팅 동안 적어도 하나의 공통 파라미터가 커플링되는, 다수의 데이터세트들에 대한 비선형 피팅 방법론의 병렬 또는 동시 적용을 말한다.

- [0115] 다중 툴 및 구조 분석(multiple tool and structure analysis)은 회귀(regression), 룩업 테이블(즉, "라이브러리" 매칭), 또는 다수의 데이터세트들의 다른 피팅 절차에 기초한 피드 포워드, 피드 사이드웨이, 또는 병렬 분석을 말한다. 다중 툴 및 구조 분석을 위한 예시적인 방법들 및 시스템들은 2009년 1월 13일자로 KLA-Tencor Corp.에게 등록된 미국 특허 제7,478,019호에 설명되어 있으며, 이 미국 특허 전체는 본 명세서에 참고로 포함된다.

- [0116] 다른 양태에서, 프로세스 툴과 통합된 하나 이상의 SAXS 시스템은 프로세스 간격 동안 웨이퍼의 다수의 상이한 영역들을 측정하도록 구성된다. 일부 실시예들에서, 각각의 측정된 관심 파라미터와 연관된 웨이퍼 균일성 값은 웨이퍼에 결친 각각의 관심 파라미터의 측정된 값들에 기초하여 결정된다.

- [0117] 일부 실시예들에서, 다수의 계측 시스템들이 프로세스 툴과 통합되고 계측 시스템들은 프로세스 동안 웨이퍼에 걸쳐 상이한 영역들을 동시에 측정하도록 구성된다. 일부 실시예들에서, 프로세스 툴과 통합된 단일 계측 시스템은 프로세스 동안 웨이퍼의 다수의 상이한 영역들을 순차적으로 측정하도록 구성된다.

- [0118] 일부 실시예들에서, 본 명세서에서 설명된 바와 같이 프로세스를 거치는 반도체 디바이스들의 SAXS 기반 계측을 위한 방법들 및 시스템들은 메모리 구조체들의 측정에 적용된다. 이 실시예들은 주기적이고 평면인 구조체들에 대한 임계 치수(CD), 막, 및 조성 계측을 가능하게 해준다.

- [0119] 본 명세서에서 설명된 바와 같은 산란계측 측정들은 다양한 반도체 구조체들의 특성들을 결정하는 데 사용될 수 있다. 예시적인 구조체들은 FinFET들, 나노와이어들 또는 그레핀과 같은 저차원 구조체들, 10 nm 이하(sub 10 nm) 구조체들, 리소그래피 구조체들, 기판 관통 비아들(through substrate vias, TSV들), DRAM, DRAM 4F2, FLASH, MRAM과 같은 메모리 구조체들 및 고 종횡비 메모리 구조체들을 포함하지만, 이들로 제한되지 않는다. 예시적인 구조적 특성들은 라인 에지 조도, 라인 폭 조도, 기공 크기, 기공 밀도, 측벽 각도, 프로파일, 임계 치수, 피치, 두께, 오버레이와 같은 기하학적 파라미터들, 및 전자 밀도, 조성, 결정립 구조(grain structure), 모폴로지(morphology), 응력, 변형(strain), 및 원소 ID(elemental identification)와 같은 재료 파라미터들을 포함하지만 이들로 제한되지 않는다. 일부 실시예들에서, 계측 타깃은 주기적인 구조체이다. 일부 다른 실시예들에서, 계측 타깃은 비주기적이다.

- [0120] 일부 예들에서, 스핀 전달 토크 랜덤 액세스 메모리(STT-RAM), 3차원 NAND 메모리(3D-NAND) 또는 수직 NAND 메모리(V-NAND), 동적 랜덤 액세스 메모리(DRAM), 3차원 FLASH 메모리(3D-FLASH), 저항성 랜덤 액세스 메모리(Re-RAM), 및 상변화 랜덤 액세스 메모리(PC-RAM)를 포함하지만, 이들로 제한되지 않는 고 종횡비 반도체 구조체들의 임계 치수들, 두께들, 오버레이, 및 재료 속성들의 측정들은 본 명세서에서 설명된 바와 같은 T-SAXS 측정 시스템들을 이용하여 수행된다.

- [0121] 일부 예들에서, 측정 모델들은 미국 캘리포니아주 밀피타스 소재의 KLA-Tencor Corporation으로부터 입수가능한 SpectraShape® 임계 치수 계측 시스템의 요소로서 구현된다. 이러한 방식으로, 산란 이미지들이 시스템에 의해 수집된 직후에 모델이 생성되어 바로 사용할 준비가 된다.

- [0122] 일부 다른 예들에서, 측정 모델들은 오프라인으로, 예를 들어, 미국 캘리포니아주 밀피타스 소재의 KLA-Tencor Corporation으로부터 입수가능한 AcuShape® 소프트웨어를 구현하는 컴퓨팅 시스템에 의해 구현된다. 결과적인 모델들은 측정들을 수행하는 계측 시스템에 의해 액세스가능한 AcuShape® 라이브러리의 요소로서 통합될 수 있다.

- [0123] 도 15는 적어도 하나의 신규의 양태에서 프로세스 동안 계측 측정들을 수행하는 방법(300)을 예시한다. 방법(300)은 본 발명의 도 1 및 도 13에 예시된 SAXS 계측 시스템들과 같은 계측 시스템에 의한 구현에 적당하다. 일 양태에서, 방법(300)의 데이터 프로세싱 블록들이 컴퓨팅 시스템(130)의 하나 이상의 프로세서, 컴퓨팅 시스템(230), 또는 임의의 다른 범용 컴퓨팅 시스템에 의해 실행되는 미리 프로그래밍된 알고리즘을 통해 수행될 수 있다는 것이 인식된다. 도 1 및 도 13에 묘사된 계측 시스템들의 특정의 구조적 양태들이 제한들을 나타내지 않으며 단지 예시적인 것으로 해석되어야 한다는 것이 본 명세서에서 인식된다.

- [0124] 블록(301)에서, x-선 조명 광량이 반도체 웨이퍼 상에 부분적으로 제조된 하나 이상의 고 종횡비 구조체를 포함하는 측정 스폿에 제공된다.

- [0125] 블록(302)에서, x-선 조명 광량에 응답하여 반도체 웨이퍼로부터 반사되거나 반도체 웨이퍼를 통해 투과된 x-선 광량이 검출된다.

- [0126] 블록(303)에서, 부분적으로 제조된 하나 이상의 고 종횡비 구조체와 연관된 하나 이상의 관심 파라미터의 값들이 검출된 x-선 광량에 기초하여 결정된다.

- [0127] 블록(304)에서, 제조 툴로 하여금 제조 툴의 하나 이상의 프로세스 제어 파라미터의 값을 조정하게 하는 하나 이상의 관심 파라미터의 값들의 표시가 제조 툴에 전달된다.

- [0128] 추가의 실시예에서, 시스템(100)은 본 명세서에서 설명된 방법들에 따라 수집되는 산란계측 측정 데이터에 기초하여 반도체 구조체들의 측정들을 수행하는 테 이용되는 하나 이상의 컴퓨팅 시스템(130)을 포함한다. 하나 이상의 컴퓨팅 시스템(130)은 하나 이상의 검출기, 능동 광학 요소, 프로세스 제어기 등에 통신가능하게 커플링될 수 있다. 일 양태에서, 하나 이상의 컴퓨팅 시스템(130)은 웨이퍼(101)의 구조체들의 산란계측 측정들과 연관된 측정 데이터를 수신하도록 구성된다.

- [0129] 본 개시내용 전반에 걸쳐 설명된 하나 이상의 단계가 단일 컴퓨터 시스템(130) 또는, 대안적으로, 다종 컴퓨터 시스템(130)에 의해 수행될 수 있음이 인식되어야 한다. 더욱이, 시스템(100)의 상이한 서브시스템들은 본 명세서에서 설명된 단계들의 적어도 일 부분을 수행하기에 적당한 컴퓨터 시스템을 포함할 수 있다. 따라서, 전술한 설명은 본 발명에 대한 제한으로서 해석되어서는 안되며 단지 예시로서 해석되어야 한다.

- [0130] 그에 부가하여, 컴퓨터 시스템(130)은 본 기술분야에 공지된 임의의 방식으로 분광계들(spectrometers)에 통신 가능하게 커플링될 수 있다. 예를 들어, 하나 이상의 컴퓨팅 시스템(130)은 산란계들과 연관된 컴퓨팅 시스템들에 커플링될 수 있다. 다른 예에서, 산란계들은 컴퓨터 시스템(130)에 커플링된 단일 컴퓨터 시스템에 의해 직접 제어될 수 있다.

- [0131] 시스템(100)의 컴퓨터 시스템(130)은 유선 및/또는 무선 부분들을 포함할 수 있는 전송 매체에 의해 시스템의 서브시스템들(예컨대, 산란계들 및 이와 유사한 것)로부터 데이터 또는 정보를 수신 및/또는 취득하도록 구성될 수 있다. 이러한 방식으로, 전송 매체는 컴퓨터 시스템(130)과 시스템(100)의 다른 서브시스템들 사이의 데이터 링크로서 역할할 수 있다.

- [0132] 시스템(100)의 컴퓨터 시스템(130)은 유선 및/또는 무선 부분들을 포함할 수 있는 전송 매체에 의해 다른 시스템들로부터 데이터 또는 정보(예컨대, 측정 결과들, 모델링 입력들, 모델링 결과들 등)를 수신 및/또는 취득하도록 구성될 수 있다. 이러한 방식으로, 전송 매체는 컴퓨터 시스템(130)과 다른 시스템들(예컨대, 메모리 온-보드 시스템(100), 외부 메모리, 또는 다른 외부 시스템들) 사이의 데이터 링크로서 역할할 수 있다. 예를 들어, 컴퓨팅 시스템(130)은 데이터 링크를 통해 저장 매체(즉, 메모리(132) 또는 외부 메모리(190))로부터 측정 데이터를 수신하도록 구성될 수 있다. 예를 들어, 본 명세서에서 설명된 산란계들을 사용하여 획득된 산란 이미지들은 영구적 또는 반영구적 메모리 디바이스(예컨대, 메모리(132) 또는 외부 메모리)에 저장될 수 있다. 이 점에서, 산란계측 이미지들은 온-보드 메모리로부터 또는 외부 메모리 시스템으로부터 임포트될(imported) 수 있다. 더욱이, 컴퓨터 시스템(130)은 데이터를 전송 매체를 통해 다른 시스템들에게 송신할 수 있다. 예를 들어, 컴퓨터 시스템(130)에 의해 결정되는 측정 모델 또는 추정된 파라미터 값은 전달되어 외부 메모리에 저장될 수 있다. 이 점에서, 측정 결과들이 다른 시스템으로 익스포트될(exported) 수 있다.

- [0133] 컴퓨팅 시스템(130)은 개인 컴퓨터 시스템, 메인프레임 컴퓨터 시스템, 워크스테이션, 이미지 컴퓨터, 병렬 프로세서, 또는 본 기술분야에 공지된 임의의 다른 디바이스를 포함할 수 있지만, 이들로 제한되지 않는다. 일반적으로, 용어 "컴퓨팅 시스템"은 메모리 매체로부터의 명령어들을 실행하는, 하나 이상의 프로세서를 가지는 임의의 디바이스를 포함하도록 광의적으로 정의될 수 있다.

- [0134] 본 명세서에서 설명된 것들과 같은 방법들을 구현하는 프로그램 명령어들(134)은 유선, 케이블, 또는 무선 전송 링크와 같은 전송 매체를 통해 전송될 수 있다. 예를 들어, 도 1에 예시된 바와 같이, 메모리(132)에 저장된 프로그램 명령어들(134)은 버스(133)를 통해 프로세서(131)에게 전송된다. 프로그램 명령어들(134)은 컴퓨터 판독가능 매체(예컨대, 메모리(132))에 저장된다. 예시적인 컴퓨터 판독가능 매체들은 판독 전용 메모리, 랜덤 액세스 메모리, 자기 또는 광학 디스크, 또는 자기 테이프를 포함한다. 요소들(231 내지 234)을 포함하는, 컴퓨팅 시스템(230)은, 본 명세서에서 설명된 바와 같이, 요소들(131 내지 134)을, 제각기, 포함하는 컴퓨팅 시스

템(130)과 유사하다.

- [0135] 본 명세서에서 설명된 바와 같이, 용어 "임계 치수"는 구조체의 임의의 임계 치수(예컨대, 하부 임계 치수, 중간 임계 치수, 상부 임계 치수, 측벽 각도, 그레이팅 높이 등), 임의의 2개 이상의 구조체 사이의 임계 치수(예컨대, 2개의 구조체 사이의 거리), 및 2개 이상의 구조체 사이의 변위(예컨대, 오버레이하는 그레이팅 구조체들 사이의 오버레이 변위 등)를 포함한다. 구조체들은 3차원 구조체들, 패터닝된 구조체들, 오버레이 구조체들 등을 포함할 수 있다.

- [0136] 본 명세서에서 설명된 바와 같이, 용어 "임계 치수 응용(critical dimension application)" 또는 "임계 치수 측정 응용(critical dimension measurement application)"은 임의의 임계 치수 측정을 포함한다.

- [0137] 본 명세서에서 설명된 바와 같이, 용어 "계측 시스템"은 임계 치수 계측, 오버레이 계측, 초점/선량 계측, 및 조성 계측과 같은 측정 응용들을 포함한, 임의의 양태에서 시료를 특성화하는 데 적어도 부분적으로 이용되는 임의의 시스템을 포함한다. 그렇지만, 그러한 기술 용어들은 본 명세서에서 설명된 바와 같은 용어 "계측 시스템"의 범위를 제한하지 않는다. 그에 부가하여, 계측 시스템은 패터닝된 웨이퍼들 및/또는 패터닝되지 않은 웨이퍼들의 측정을 위해 구성될 수 있다. 계측 시스템은 LED 검사 툴, 에지 검사 툴, 배면 검사 툴, 매크로 검사 툴, 또는 다중 모드 검사 툴(하나 이상의 플랫폼으로부터의 데이터를 동시에 포함함), 및 임계 치수 데이터에 기초한 시스템 파라미터들의 캘리브레이션으로부터 이득을 보는 임의의 다른 계측 또는 검사 툴로서 구성될 수 있다.

- [0138] 임의의 반도체 프로세싱 툴(예컨대, 검사 시스템 또는 리소그래피 시스템) 내에서 시료를 측정하는 데 사용될 수 있는 반도체 측정 시스템에 대한 다양한 실시예들이 본 명세서에서 설명된다. 용어 "시료"는 본 기술분야에 공지된 수단에 의해 프로세싱될(예컨대, 인쇄되거나 결합들이 있는지 검사될) 수 있는 웨이퍼, 레티클, 또는 임의의 다른 샘플을 지칭하기 위해 본 명세서에서 사용된다.

- [0139] 본 명세서에서 사용되는 바와 같이, 용어 "웨이퍼"는 일반적으로 반도체 또는 비-반도체 재료로 형성된 기판들을 지칭한다. 예들은 단결정 실리콘, 갈륨 비화물, 및 인듐 인화물을 포함하지만, 이들로 제한되지 않는다. 그러한 기판들은 반도체 제조 설비들에서 흔히 발견되고 그리고/또는 프로세싱될 수 있다. 일부 경우들에서, 웨이퍼는 기판만(즉, 베어 웨이퍼(bare wafer))을 포함할 수 있다. 대안적으로, 웨이퍼는 기판 상에 형성된 상이한 재료들의 하나 이상의 층을 포함할 수 있다. 웨이퍼 상에 형성된 하나 이상의 층은 "패터닝되거나" 또는 "패터닝되지 않을" 수 있다. 예를 들어, 웨이퍼는 반복가능한 패턴 피처들을 갖는 복수의 다이들을 포함할 수 있다.

- [0140] "레티클"은 레티클 제조 프로세스의 임의의 스테이지에서의 레티클이거나, 또는 반도체 제조 설비에서 사용하기 위해 출시될(released) 수 있거나 출시되지 않을 수 있는 완성된 레티클일 수 있다. 레티클, 또는 "마스크"는, 실질적으로 불투명한 영역들이 상부에 형성되어 어떤 패턴으로 구성되는, 실질적으로 투명한 기판으로서 일반적으로 정의된다. 기판은, 예를 들어, 비정질  $\text{SiO}_2$ 와 같은 유리 재료를 포함할 수 있다. 레티클은 레티클 상의 패턴이 레지스트에 전사될 수 있도록 리소그래피 프로세스의 노광 단계 동안 레지스트로 피복된 웨이퍼(resist-covered wafer) 위에 배치될 수 있다.

- [0141] 웨이퍼 상에 형성되는 하나 이상의 층은 패터닝되거나 또는 패터닝되지 않을 수 있다. 예를 들어, 웨이퍼는, 각각이 반복가능한 패턴 피처들을 갖는, 복수의 다이들을 포함할 수 있다. 그러한 재료 층들의 형성 및 프로세싱은 궁극적으로는 완성된 디바이스들을 결과할 수 있다. 많은 상이한 유형들의 디바이스들이 웨이퍼 상에 형성될 수 있으며, 용어 웨이퍼는, 본 명세서에서 사용되는 바와 같이, 본 기술분야에 공지된 임의의 유형의 디바이스가 상부에 제조되고 있는 웨이퍼를 포괄하도록 의도된다.

- [0142] 하나 이상의 예시적인 실시예에서, 설명되는 기능들은 하드웨어, 소프트웨어, 펌웨어, 또는 이들의 임의의 조합으로 구현될 수 있다. 소프트웨어로 구현되는 경우, 기능들은 하나 이상의 명령어 또는 코드로서 컴퓨터 판독 가능 매체 상에 저장되거나 컴퓨터 판독 가능 매체를 통해 전송될 수 있다. 컴퓨터 판독 가능 매체들은 한 장소로부터 다른 장소로의 컴퓨터 프로그램의 전송을 용이하게 하는 임의의 매체를 포함한 통신 매체들 및 컴퓨터 저장 매체들 둘 다를 포함한다. 저장 매체들은 범용 또는 특수 목적 컴퓨터에 의해 액세스될 수 있는 임의의 이용가능한 매체들일 수 있다. 제한이 아닌 예로서, 그러한 컴퓨터 판독 가능 매체들은 RAM, ROM, EEPROM, CD-ROM 또는 다른 광학 디스크 스토리지, 자기 디스크 스토리지 또는 다른 자기 스토리지 디바이스들, 또는 원하는 프로그램 코드 수단을 명령어들 또는 데이터 구조들의 형태로 운반하거나 저장하는 데 사용될 수 있고 범용 또는 특수 목적 컴퓨터, 또는 범용 또는 특수 목적 프로세서에 의해 액세스될 수 있는 임의의 다른 매체를 포함할

수 있다. 또한, 임의의 접속(connection)이 컴퓨터 판독가능 매체라고 적절히 지칭된다. 예를 들어, 소프트웨어가 동축 케이블, 광섬유 케이블, 연선(twisted pair), DSL(digital subscriber line), 또는 적외선, 라디오, 및 마이크로파와 같은 무선 기술들을 사용하여 웹사이트, 서버, 또는 다른 원격 소스로부터 전송되는 경우, 동축 케이블, 광섬유 케이블, 연선, DSL, 또는 적외선, 라디오, 및 마이크로파와 같은 무선 기술들은 매체의 정의에 포함된다. 본 명세서에서 사용되는 바와 같은, 디스크(disk) 및 디스크(disc)는 CD(compact disc), 레이저 디스크(laser disc), 광학 디스크(optical disc), DVD(digital versatile disc), 플로피 디스크(floppy disk) 및 블루레이 디스크(blu-ray disc)를 포함하고, 여기서 디스크들(disks)은 보통 데이터를 자기적으로 재생하는 반면, 디스크들(disks)은 데이터를 레이저들을 사용하여 광학적으로 재생한다. 상기한 것들의 조합들이 컴퓨터 판독가능 매체들의 범위 내에 또한 포함되어야 한다.

[0143]

비록 몇몇 특정 실시예들이 교수적인 목적들을 위해 위에서 설명되었지만, 이 특허 문서의 교시들은 일반적인 적용가능성(general applicability)을 가지며 위에서 설명된 특정 실시예들로 제한되지 않는다. 그에 따라, 설명된 실시예들의 다양한 피처들의 다양한 수정들, 개조들(adaptations), 및 조합들이 청구범위에 기재된 바와 같은 본 발명의 범위를 벗어나지 않으면서 실시될 수 있다.

## 도면

### 도면1

도면2

도면3

도면4

도면5

도면6

도면7

도면8

도면9

도면10

도면11a

도면11b

도면11c

도면 12a

도면 12b

도면 12c

### 도면13

### 도면 14

## 도면15