(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第6053690号

(P6053690)

(45) 発行日 平成28年12月27日(2016.12.27)

(24) 登録日 平成28年12月9日(2016.12.9)

|                          |                    |

|--------------------------|--------------------|

| (51) Int.Cl.             | F 1                |

| HO 1 L 21/3205 (2006.01) | HO 1 L 21/88 Z     |

| HO 1 L 21/768 (2006.01)  | HO 1 L 21/88 T     |

| HO 1 L 23/522 (2006.01)  | HO 1 L 27/04 D     |

| HO 1 L 21/822 (2006.01)  | HO 1 L 21/92 602 J |

| HO 1 L 27/04 (2006.01)   |                    |

請求項の数 18 (全 15 頁) 最終頁に続く

|               |                               |

|---------------|-------------------------------|

| (21) 出願番号     | 特願2013-544804 (P2013-544804)  |

| (86) (22) 出願日 | 平成23年12月16日 (2011.12.16)      |

| (65) 公表番号     | 特表2014-501446 (P2014-501446A) |

| (43) 公表日      | 平成26年1月20日 (2014.1.20)        |

| (86) 國際出願番号   | PCT/US2011/065355             |

| (87) 國際公開番号   | W02012/083110                 |

| (87) 國際公開日    | 平成24年6月21日 (2012.6.21)        |

| 審査請求日         | 平成26年12月12日 (2014.12.12)      |

| (31) 優先権主張番号  | 12/970,464                    |

| (32) 優先日      | 平成22年12月16日 (2010.12.16)      |

| (33) 優先権主張国   | 米国(US)                        |

|               |                                                                                                                       |

|---------------|-----------------------------------------------------------------------------------------------------------------------|

| (73) 特許権者     | 390020248<br>日本テキサス・インスツルメンツ株式会社<br>東京都新宿区西新宿六丁目24番1号                                                                 |

| (73) 特許権者     | 507107291<br>テキサス インスツルメンツ インコーポ<br>レイテッド<br>アメリカ合衆国 テキサス州 75265<br>-5474 ダラス メイル ステイショ<br>ン 3999 ピーオーボックス 655<br>474 |

| (74) 上記1名の代理人 | 100098497<br>弁理士 片寄 恒三                                                                                                |

最終頁に続く

(54) 【発明の名称】エレクトロマイグレーション耐性フィードライン構造を有するICデバイス

## (57) 【特許請求の範囲】

## 【請求項1】

集積回路デバイスであって、

能動回路要素を含む頂部表面を有する基板と、

頂部金属層と前記頂部金属層の下の相互接続金属層とを含むメタライゼーションスタッフであって、前記相互接続金属層がボンドパッドに結合される少なくとも1つのトレースを含む、前記メタライゼーションスタッフと、

前記ボンドパット上のボンディング特徴と、

を含み、

前記トレースが、均一トレース部と前記ボンドパッドまで延びるパターン化されたトレース部とを含み、前記パターン化されたトレース部が、互いに電気的に並列である少なくとも3つのサブトレースを含む、デバイス。

## 【請求項2】

請求項1に記載のデバイスであって、

前記サブトレースが異なる幅と異なる長さとを有し、等しいサブトレース電流を生成するため各サブトレースが実質的に等しい数のスクエアを有し、その数が、前記サブトレースの各々に対するスクエアの数が前記サブトレースに対するスクエアの平均数の±20パーセントの範囲内であるように実質的に定義される、デバイス。

## 【請求項3】

請求項1に記載のデバイスであって、

10

20

前記サブトレースが異なる幅と異なる長さとを有し、等しいサブトレース電流を生成するためには各サブトレースが多数のスクエアを有し、前記サブトレースの各々を通して導通される前記ボンディング特徴に提供される電流密度が、前記ボンディング特徴に提供される平均電流密度の±20パーセントの範囲内である、デバイス。

【請求項4】

請求項1に記載のデバイスであって、

前記サブトレースがその周囲に沿って前記ボンドパッドに接し、前記サブトレースが前記周囲に沿って互いから実質的に等しい分離を有する、デバイス。

【請求項5】

請求項1に記載のデバイスであって、

前記サブトレースが少なくとも10サブトレースを含む、デバイス。

【請求項6】

請求項1に記載のデバイスであって、

前記ボンドパッドが前記頂部金属層を含む、デバイス。

【請求項7】

請求項1に記載のデバイスであって、

前記ボンディング特徴が、はんだバンプ、基板貫通バイア、ピラー、スタッド又は中に複数の金属粒子を有する有機ボンディング材料を含む、デバイス。

【請求項8】

請求項1に記載のデバイスであって、

前記サブトレースのそれぞれ1つと前記ボンディング特徴との間の誘電体層内の複数のバイアを更に含む、デバイス。

【請求項9】

請求項1に記載のデバイスであって、

前記ボンドパッドと前記ボンディング特徴との間の電流スプレッド層と、

前記ボンドパッドと前記電流スプレッド層との間の誘電体層と、

を更に含み、

前記誘電体層が、前記ボンドパッドと前記電流スプレッド層との間の個別のコンタクトを提供する複数のバイアを含む、デバイス。

【請求項10】

請求項9に記載のデバイスであって、

前記サブトレースの少なくとも1つにより提供されるバスに関連付けられるスクエアの数が、前記サブトレースに対するスクエアの平均数±20パーセントの範囲の外側にあるように、前記サブトレースが寸法され、前記サブトレースの各々を通して導通される前記ボンディング特徴に、前記ボンディング特徴に提供される平均電流密度±20パーセントの範囲内の電流密度が供給されるように、前記バイアのそれぞれのバイアが寸法される、デバイス。

【請求項11】

請求項1に記載のデバイスであって、

前記少なくとも一つのトレースが複数の独立トレースを含み、前記複数の独立トレースが、少なくとも3つのサブトレースに分割する第1のパターン化されたトレース部を含む第1のトレースと、少なくとも3つの第2のサブトレースに分割する第2のパターン化されたトレース部を含む第2のトレースとを含む、デバイス。

【請求項12】

請求項1に記載のデバイスであって、

前記ボンディング特徴がはんだバンプを含む、デバイス。

【請求項13】

集積回路デバイスであって、

能動回路要素を含む頂部表面を有する基板と、

頂部金属層と前記頂部金属層の下の相互接続金属層とを含むメタライゼーションスタッ

10

20

30

40

50

クであって、前記相互接続金属層が、前記頂部金属層を含むボンドパッドに結合する少なくとも一つのトレースを含む、前記メタライゼーションスタックと、

前記ボンドパッド上に形成されるアンダーバンプメタライゼーション層と、

前記アンダーバンプメタライゼーション層上に形成されるはんだバンプと、

を含み、

前記トレースが、前記ボンドパッドまで延びるパターン化されたトレース部を含み、前記パターン化されたトレース部が、互いに電気的に並列である少なくとも3つのサブトレースに分割する、デバイス。

#### 【請求項14】

集積回路デバイスを形成する方法であって、

10

能動回路要素を含む頂部表面を有する基板を提供することと、

頂部金属層と前記頂部金属層の下の相互接続金属層とを含むメタライゼーションスタックを形成することであって、前記相互接続金属層が、互いに電気的に並列である少なくとも3つのサブトレースを含むパターン化されたトレース部を含む少なくとも1つのトレースを含む、前記メタライゼーションスタックを形成することと、

前記少なくとも3つのサブトレースに結合されるボンドパッドを形成することと、

前記ボンドパット上にボンディング特徴を形成することと、

を含み、

前記パターン化されたトレース部が、互いに電気的に並列である少なくとも3つのサブトレースを含む、方法。

20

#### 【請求項15】

請求項14に記載の方法であって、

前記ボンドパッドが前記頂部金属層を含む、方法。

#### 【請求項16】

請求項14に記載の方法であって、

前記サブトレースがその周囲に沿って前記ボンドパッドに接し、前記サブトレースが前記周囲に沿って前記サブトレースの近隣に対する実質的に等しい分離を有する、方法。

#### 【請求項17】

請求項14に記載の方法であって、

前記ボンドパッドと前記ボンディング特徴との間の電流スプレッド層を形成することと

30

、前記ボンドパッドと前記電流スプレッド層との間に誘電体層を形成することと、

前記誘電体層に各々前記ボンドパッドと前記電流スプレッド層との間の個別のコンタクトを提供する複数のバイアを形成することと、

を更に含む、方法。

#### 【請求項18】

請求項14に記載の方法であって、

前記ボンディング特徴がはんだバンプを含む、方法。

#### 【発明の詳細な説明】

##### 【技術分野】

40

##### 【0001】

開示される実施例は、エレクトロマイグレーション(EM)性能を改善するフィードライン構造を含む集積回路(IC)デバイスに関する。

##### 【背景技術】

##### 【0002】

ICは概して、基板、基板の上側上に形成される能動回路要素、及び能動回路要素の上の交互の金属配線層とレベル間誘電体層(ILD)とを含むバックエンドオブライン(BEOL)構造を含む。金属配線層は、能動回路要素と外部接続との間の電気的接続を提供する種々の相互接続を含む。能動回路要素における、又ははんだバンプが単にパススルーの一部である(例えば、スタックされたダイ/パッケージのため)場合に相互接続が受動

50

的役割をする状況におけるノードからなど、半導体デバイスの最後の（例えば、頂部）金属配線レベルと別のデバイスとの間の接続を提供するためにはんだバンプ（又ははんだボール）が通常用いられる。一般的なタイプのはんだバンプは、フリップチップデバイスの接合のためによく用いられる、制御されたコラプスチップ接続（C4）はんだバンプである。

#### 【0003】

より小さなデバイスをつくるため特徴（例えば、パッド、配線、相互接続、バイア）の寸法が縮小されるにつれて、信頼性のため課されるEMに基づく制約に起因して、最大許容電流密度は急激に減少する。EMは、金属特徴を介して流れる電流に起因して金属特徴の原子が転置される既知の現象である。

10

#### 【0004】

フリップチップデバイスなどのICデバイスは、ますます高い電流搬送能力を要し、これは時折10アンペアまたはそれ以上のレベルまで達する。はんだは、銅及びアルミニウムなどの従来の金属相互接続に比べて、著しく低い電流密度処理能力を有することが知られている。例えば、はんだは、比較的低いEM電流制限（例えば、従来のはんだに対する典型的なEM制限電流密度は、 $10^4 \text{ A/cm}^2$ 辺りであり、銅及びアルミニウムのものの約100倍低い）を有する。各フリップチップはんだバンプの電流搬送能力は、EM制約に起因してはんだバンプを介する電流密度を制限するようにこの電流を供給するために用いられるはんだバンプの最小数を設定する。従来のフリップチップはんだバンププロセスは、はんだバンプの断面エリアにわたる電流分布不均一性をこうむり、これは、はんだのEMに基づく劣化を加速させ、電流分布がより均一である場合より早期に欠陥を生じさせる。

20

#### 【0005】

従来のフリップチップバンプ配置の一例は、頂部金属層から形成されるアルミニウムボンドパッドへの銅フィードライン、パッドの上の開口（誘電体開口）を含む誘電体（例えば、ポリイミド）層、誘電体層及び誘電体開口の上の厚い（例えば、 $2 \mu\text{m}$ 厚み）ニッケルのアンダーバンプメタライゼーション（UBM）層、及びUBMの上のはんだバンプを含む。この配置は、はんだバンプの断面エリアにわたる著しい電流分布不均一性をこうむる。

#### 【0006】

30

1つの側から来るフィードライン電流を備えたはんだバンプの場合、UBMに近接するはんだバンプエリアにおけるピーク電流は、はんだバンプの全断面エリアの約10%のみである断面エリアの一部の上に存在し得る。これは、はんだのEM電流密度制限を超えることに起因して最初に無効になる（void）、はんだバンプにおける電流密集領域である。この領域が無効になると、その次のはんだエリアがピーク電流分布を搬送し得、次に無効となる。この無効化パターンは、誘電体開口の上の全はんだバンプが無効となるまで続く。この時点で、誘電体の上のUBMの外側環が無効となり始め、最終的に開回路となる。

#### 【0007】

この問題に対する解決策の一つは、UBM内に厚い銅スタッドを付加することに関与し、これは、電流がはんだバンプの断面エリアにわたって広がることを助ける。この既知の解決策は、処理工程を付加し、それが典型的なスタッド寸法に対し均一な電流密度を与えることができないため最小限の有効性しかない。そのため、処理工程を付加することなく又はフィードライン構造を実装するために必要とされるエリアを著しく増大させることなく、電流をはんだバンプ又は他のボンディング特徴の断面エリアにわたって一層均一にさせ得る、ボンディング特徴配置への新しいフィードラインが必要とされている。

40

#### 【発明の概要】

#### 【0008】

開示される実施例は、ボンディング特徴に流れる電流をその断面エリアにわたって一層均一にさせる、ボンディング特徴に対するエレクトロマイグレーション（EM）耐性フィードライン構造を有する集積回路（IC）デバイスを説明する。このような電流スプレッ

50

ド実施例は、はんだバンプなどのボンディング特徴におけるEM誘導無効化を解決するか又は少なくとも著しく低減する。

#### 【0009】

ボンディング特徴へのフィードライントレースを、少なくとも3つの電気的に並列なサブトレースであって、それぞれのサブトレースパスが、(i)複数のフィード電流を実質的に等しい電流にするように適切なライン寸法とすること(即ち、一層長いラインは幅広く、一層短いラインは幅がより狭い)、及び(ii)サブトレースの各々を介して導通されるボンディング特徴に提供される電流密度が実質的に等しいこと、のうち少なくとも1つを有するサブトレースパスに分割することにより、ボンディング特徴の断面エリアにわたってより良好な電流の分布(一層少ない電流密集)に起因してEMに基づく問題なく、一層高い総電流レベルがボンディング特徴により扱われ得る。開示される実施例は概して、如何なる処理工程も付加しない。10

#### 【0010】

例えば、開示されるフィード構造は、従来の单一入力フィードライントレース(例えば、端から端まで10ミクロン幅のトレース)を、複数のサブトレース(例えば、8、12、16個、又は更に多くのサブトレース)を含むパターン化されたトレース部を含むトレースで置き換えることができる。一実施例において、サブトレースの各々を介して導通されるボンディング特徴に提供される電流密度は実質的に等しい。本明細書において用いられるように、サブトレースの各々を介して導通されるボンディング特徴に提供される「実質的に等しい電流密度」は、各々、ボンディング特徴に提供される平均電流密度プラス又はマイナス20パーセントの範囲内である電流密度を指す。20

#### 【0011】

別の実施例において、これらのサブトレースは異なる幅及び異なる長さを有し、それぞれのサブトレースは、各々実質的に等しい数のスクエアを有する。本明細書において用いられるように、「実質的に等しい数のスクエア」が、実質的に等しいサブトレース電流を生成し、全てサブトレースのスクエアの平均数プラス又はマイナス20パーセントの範囲内であり、一実施例においてサブトレースのスクエアの平均数プラス又はマイナス10パーセントの範囲内である、サブトレースの各々によって提供されるパスに関連付けられる多数のスクエアを指す。

#### 【0012】

本明細書においてエッジフィード実施例と称する一実施例において、サブトレースは、誘電体開口の上のボンディング特徴のエッジ(周囲)の下のエリアがフィードラインサブトレースコンタクトの等しい分布を有するように、すなわち、ボンドパッドの下のその近隣に対する各フィードラインサブトレース間の分離(間隔)が実質的に均一であるよう<sup>30</sup>に、分布され得る。この実施例において、「実質的に等しい分離」とは、全て複数のサブトレースに対する平均周囲間隔距離プラス又はマイナス20パーセントの範囲内である、サブトレース間の周囲に沿った距離を指す。この実施例においてスクエアの数、ひいては、各フィードラインサブトレースの抵抗、が実質的に等しくされ得るため、均一なトレース部における電流がそれ自体を、それが利用可能なボンディング特徴へのサブトレースパスの各々間で実質的に等しく分割し得る。そのため、エッジフィード実施例では、ボンディング特徴の下の周囲はそれへの均一な電流を呈し、ボンディング特徴(例えば、はんだバンプ)における一層均一な電流分布が概して達成される。40

#### 【0013】

本明細書においてエリアフィード実施例と称する一実施例において、ボンディング特徴の実質的に全エリアが電流で満たされる。この実施例において、ボンドパッドは、ボンドパッドの下の又はボンドパッドの上の実質的に全エリアにわたって分布されるバイアを有する。この実施例において、バイアパターンがボンドパッド(例えば、ボンドパッドとI BMパッドとの間)の上の誘電体層に提供され得るか、又はバイアパターンは、ボンドパッド(例えば、フィードラインサブトレースとボンドパッドとの間)の下の誘電体内にあり得る。エリアフィード実施例は、エッジフィード実施例と組み合わされてもよい。50

## 【図面の簡単な説明】

## 【0014】

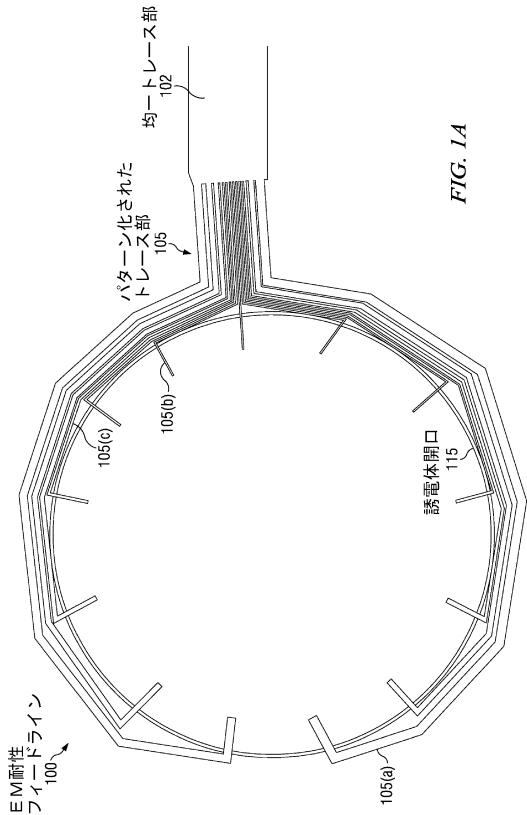

【図1A】図1Aは、例示の一実施例に従った、ボンディング特徴の下の誘電体開口の周囲にわたって実質的に等しい分布を有する、実質的に等しいサブトレース電流を提供する少なくとも3つのサブトレースを有する例示のエレクトロマイグレーション(EM)耐性フィードライン構造の表示を示す。

## 【0015】

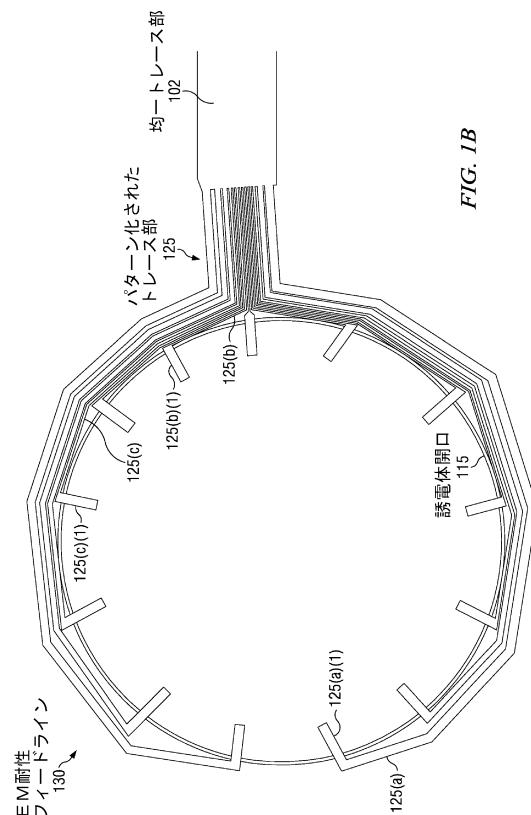

【図1B】図1Bは、例示の一実施例に従った、実質的に等しいサブトレース電流及び実質的に等しいサブトレース電流密度の両方だけでなく、ボンディング特徴の下の誘電体開口の周囲にわたって実質的に等しい物理的分布も提供する、少なくとも3つのサブトレースを有する例示EM耐性フィードライン構造の表示を示す。10

## 【0016】

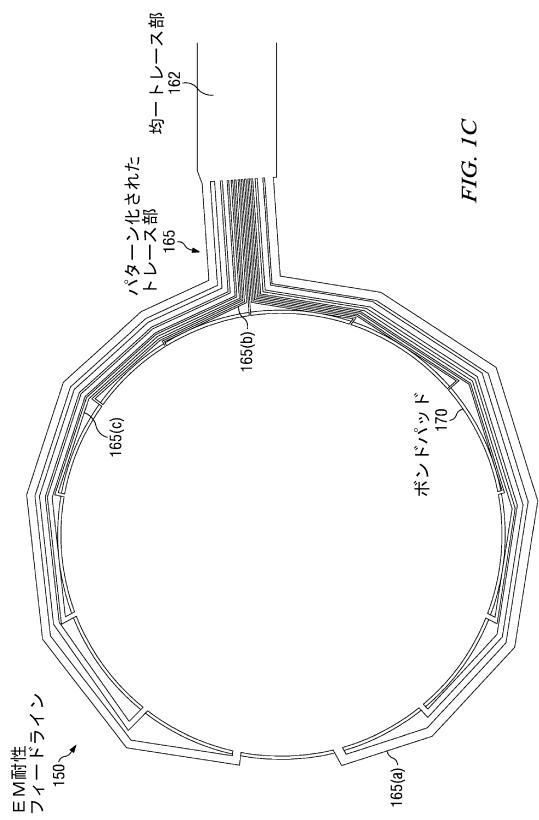

【図1C】図1Cは、例示の一実施例に従った、複数のサブトレース及びボンドパッドの両方を提供する単一の金属層を有し、サブトレースが、その周囲に沿ってボンドパッドに実質的に等しいサブトレース電流を提供する、例示のEM耐性フィードライン構造の表示を示す。

## 【0017】

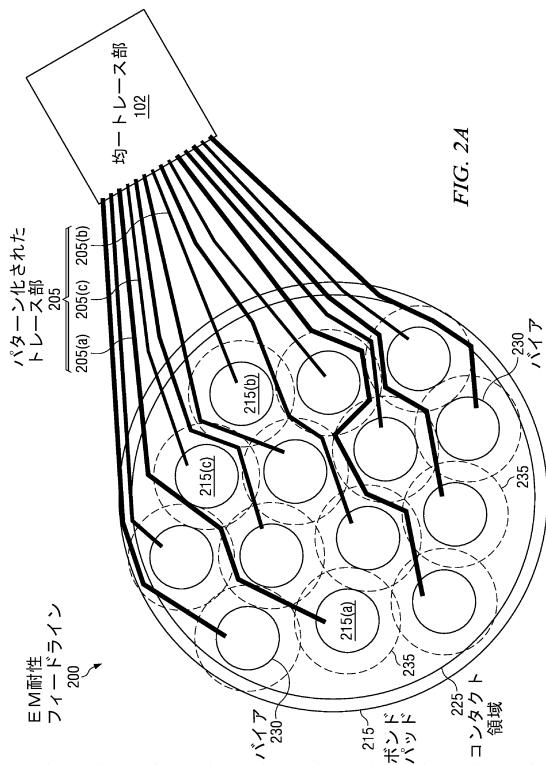

【図2A】図2Aは、例示の一実施例に従った、ボンドパッドの上のボンディング特徴の全エリアにわたって分布されるその上にバイアを有するボンドパッドへのコンタクト領域において結合される実質的に等しいサブトレース電流を提供する少なくとも3つのサブトレースを有する、例示のEM耐性フィードライン構造の表示を図示する。20

## 【0018】

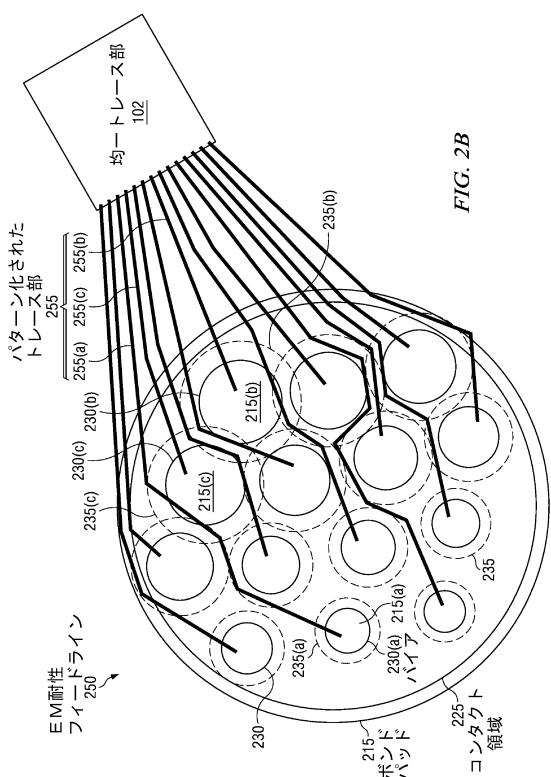

【図2B】図2Bは、例示の一実施例に従った、ボンドパッドの上のボンディング特徴の全エリアにわたって分布されるその上にバイアを有するボンドパッドへのコンタクト領域において結合される少なくとも3つのサブトレースを有する例示のEM耐性フィードライン構造の表示を図示し、サブトレース電流は、サブトレースのスクエアの平均数プラス又はマイナス20パーセントの外側の範囲を有し、バイアは、ボンディング特徴に実質的に等しい電流密度を提供するような寸法にされる。

## 【0019】

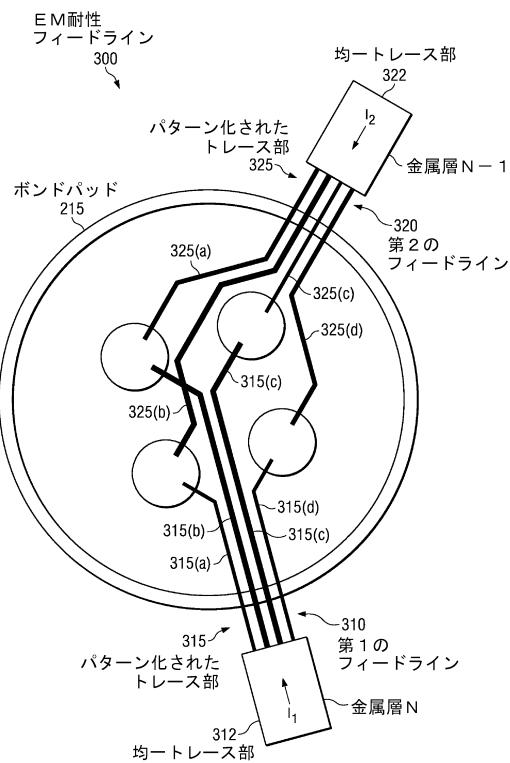

【図3】図3は、例示の一実施例に従った、いずれも同じボンドパッドに結合されている、均一トレース部を含む第1の独立フィードラインと、均一トレース部を含む第2の独立フィードラインとを有する例示のEM耐性フィードライン構造を示す。これらのフィードラインは、各々パターン化されたトレース部を含み、パターン化されたトレース部は各々、実質的に等しいサブトレース電流を提供するような寸法とされる4つのサブトレースを含む。30

## 【0020】

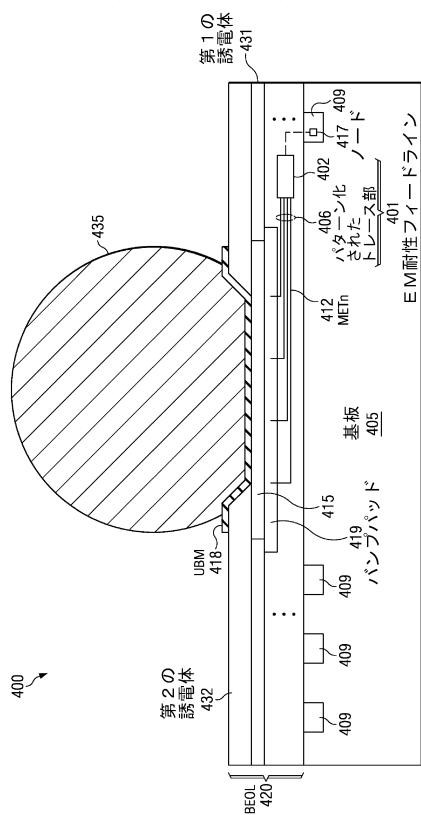

【図4】図4は、例示の一実施例に従った、頂部金属層、及びボンドパッド上のボンディング特徴を含むボンドパッドに結合される実質的に等しいサブトレース電流を提供する少なくとも3つのサブトレースを含む、開示されるEM耐性フィードライン構造を含む相互接続金属層を含むバックエンドオブライイン(BEOL)メタライゼーションスタックを含む例示のICデバイスを示す。40

## 【0021】

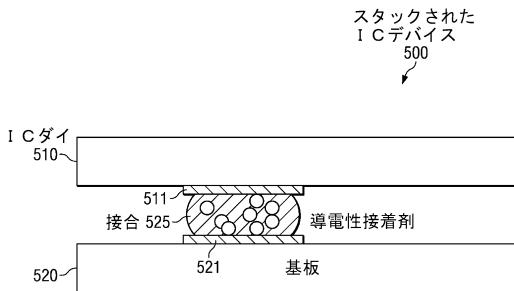

【図5】図5は、例示の一実施例に従った、金属/有機ボンディング材料を含む接合により基板にボンディングされる実質的に等しいサブトレース電流を提供する少なくとも3つのサブトレースを含む開示されるEM耐性フィードライン構造を有するICダイを含むスタックされたICデバイスを示す。

## 【発明を実施するための形態】

## 【0022】

図1Aは、例示の一実施例に従った、ボンディング特徴の下の誘電体開口115の周囲にわたって実質的に等しい分布を有する、実質的に等しいサブトレース電流を提供する少50

なくとも3つのサブトレースを有するエッジフィードを提供する例示のEM耐性フィードライン構造100を示す。図1Aに1つの大型の誘電体開口115を示すが、開示される実施例は、後に形成されるボンディング特徴の下に、代わりにより小さな誘電体開口のアレイを、又は両方を含んでもよい。ボンディング特徴は、本明細書において概してはんだバンプとして記載する。しかし、ボンディング特徴は更に、基板貫通バイア(TSV)、ピラー(例えば、銅ピラー)、スタッド(例えば、金スタッド)、又は中に複数の金属粒子を有する有機ボンディング材料を含み得る。

#### 【0023】

EM耐性フィードライン構造100は、電気的に並列であり、ボンドパッド上のボンディング特徴を含む、後に形成される金属スタッカ(図示せず)の下に示される誘電体開口115の周囲に沿って電気的コンタクトを提供するように分布する、少なくとも3つのサブトレース105(a)、105(b)、105(c)などを含む、パターン化されたトレース部105に結合される均一(即ち、従来の)トレース部102を含む。後に形成される金属スタッカは誘電体開口115の上にあり得、これは、一つの特定の実施例において、はんだボール/Niアンダーバンプメタライゼーション(UMB)/Alボンドパッドを含み得る。

#### 【0024】

それぞれ複数のフィードラインサブトレース105(a)、105(b)、105(c)などは、サブトレースによって提供されるそれぞれのバスに関連付けられる多数のスクエアが、全て、複数のサブトレースに対するスクエアの平均数プラス又はマイナス20パーセント(±20%)の範囲内となるような寸法とされるため、EM耐性フィードライン構造100により実質的に等しいサブトレース電流が提供される。図1Aに示す最も長いサブトレースであるサブトレース105(a)は、最も幅広いサブトレースでもあり、図示される最も短いサブトレースであるサブトレース105(b)は最も幅が狭いサブトレースでもあり、サブトレース105(c)は、中間の長さ及び中間のライン幅を有して示されるサブトレースであることが分かる。パターン化されたトレース部105におけるサブトレースは全て、それらのそれぞれのバス長さに沿って一定のライン幅を有して示されているが、それぞれのサブトレースのスクエアの結果の数が上述のよう数値的範囲であれば、実質的に等しいサブトレース電流を提供するためライン幅は一定である必要はないことに注意されたい。

#### 【0025】

図1Aは、エッジフィード実施例は、ボンディング特徴(例えば、はんだバンプ)に結合するための従来の単一フィードライン配置に比べて、要する余分のメタライゼーションエリアがわずかであることを示す。図1Aに示すエッジフィード実施例は、上にあるボンディング特徴(例えばはんだバンプ)において改善された電流スプレッドを提供するため、この実施例により、同じEM電流性能に対するデバイスの上側金属層における全体的により小さな金属エリア要件をもたらすために用いられるボンディング特徴のためのエリアが低減され得、そのためICデバイスに対しコスト削減を提供する。

#### 【0026】

ウエハチップスケールパッケージ(WSCP)に適用される場合、均一トレース部102及びパターン化されたトレース部105はいずれもリダイレクト層(RDL)から形成され得る。この実施例において、パターン化されたトレース部105は、IC上のボンドパッドの上にあるRDLパッドに結合し、UMBパッドがRDLパッド上にあり得、はんだバンプがUMBパッド上にあり得る。この実施例において、誘電体開口115は、ポリイミド層内の開口など、RDLとUMBとの間の誘電体内の開口であり得る。

#### 【0027】

上述のように、幾つかの開示される実施例は、サブトレースの各々を介して導通されるボンディング特徴に提供される、実質的にマッチングされたサブ電流及び実質的にマッチングされた電流密度の両方を提供し得る。例えば、図1Bは、例示の一実施例に従った、実質的に等しいサブトレース電流及び実質的に等しいサブトレース電流密度の両方を提供

10

20

30

40

50

し、更に、ボンディング特徴の下の誘電体開口 115 の周囲にわたって実質的に等しい物理的分布も提供する、少なくとも 3 つのサブトレース 125 (a)、125 (b)、125 (c) を有する例示 EM 耐性フィードライン構造 130 の表示を示す。従来技術で知られているように、ボンディング特徴の下の誘電体開口 115 に入る電流密度 (J) は、サブトレースコンタクトにおける電流 (I) をコンタクトのエリア (A) で除算することにより分かり、 $J = I / A$  により与えられる。その末端部 125 (a) (1) で幅が拡げられてないことを示す、サブトレース 125 (a) などの一層長いサブトレースに比べて、サブトレース 125 (b) などの狭いサブトレースは、誘電体開口 115 に延びるその末端部 125 (b) (1) で著しく幅が広げられており、それにより、それぞれのサブトレースの幅が、誘電体開口 115 に延びるそれらの末端部において同じ幅又はほぼ同じ幅となるようにされることが分かる。中間のライン幅を有するサブトレース 125 (c) は、その末端部 125 (c) (1) の適度な幅の広がりを示す。それぞれのサブトレースにおける電流が互いにマッチングされ、それらのコンタクトにおけるエリアも同じであるため、電流密度マッチングが提供される。

#### 【0028】

図 1C は、例示の一実施例に従った、ボンドパッドの周囲に沿って実質的に等しい分布を有するボンドパッド 170 をフィードする実質的に等しいサブトレース電流を提供する、少なくとも 3 つのサブトレース 165 (a)、165 (b)、165 (c) などを有するパターン化されたトレース部 165 に結合される均一トレース部 162 を含む例示の EM 耐性フィードライン構造 150 を示す。この実施例において、フィードライン構造 150 及びボンドパッド 170 は全て同じ金属層から形成される。この金属層は、金属相互接続層、頂部金属層、又は RDL であり得る。

#### 【0029】

図 2A は、例示の一実施例に従った、ボンドパッドのエリアにわたってコンタクト領域 225 内で結合される実質的に等しいサブトレース電流を提供する少なくとも 3 つのサブトレースを有するエリアフィード実施例を示し、複数のバイア 230 がボンドパッド 215 上の誘電体層内に形成される、例示の EM 耐性フィードライン構造 200 を示す。EM 耐性フィードライン構造 200 は、

均一トレース部 102、及び複数のサブトレース 205 (a)、205 (b)、205 (c) などを含むパターン化されたトレース部 205 を含む。複数のサブトレース 205 (a)、205 (b)、205 (c) などは、複数のサブトレースの各々によって提供されるパスに関連付けられる多数のスクエアが全て、複数のサブトレースに対するスクエアの平均数プラス又はマイナス 20 パーセントの範囲内であるような寸法とされる。

#### 【0030】

コンタクト領域 225 において、それぞれのサブトレース 205 (a)、205 (b)、205 (c) は、サブトレース 205 (a)、205 (b)、205 (c) とボンドパッド 215 との間の誘電体層内に形成される、単一の誘電体開口 (図 1A に示す誘電体開口 115 など) 又は複数のバイアを用いてボンドパッド 215 と接することができる。ボンドパッド 215 は、それぞれの有効なボンドパッド部 215 (a)、215 (b)、215 (c) を画定する位置でその上の誘電体層から形成されるバイア 230 を含む例示の円形のバイアパターンを有する。フィード電流がボンドパッド部からコンタクト領域 225 内のボンドパッド 215 の上にあり得る例示の 2ミクロン厚みのニッケル UBM 層 (図示せず) へ横切るため、破線のリングとして示される外側リング 235 (a)、235 (b)、235 (c) は、ボンドパッド部 215 (a)、215 (b)、215 (c) を超えて拡がる電流を表す。図 2A に示すように、コンタクト領域 225 の上の UBM 層の殆ど全エリアは、その上に配置され得るボンディング特徴 (例えばはんだバンプ) のため電流をスプレッドさせ、ボンディング特徴 (例えばはんだバンプ) の全断面エリアにわたって均一な電流分布を仮想的に保証する。

#### 【0031】

この実施例において、ボンドパッド 215 が、UBM を下にある金属 (例えば、銅) サ

10

20

30

40

50

ブトレースのパターン化されたトレース部 205 に結合することができる例えば、アルミニウム層を含む、頂部金属層が効果的にパターン化される。このパターン化は、ボンドパッド 215 の上の開口が、金属パターン化要件に応じて、これらに限定されないが、円又はスクエアを含む種々の形状に形づくられ得る、バイアのアレイを含むように実行され得る。バイアのエリアは、バイアのエリアがボンドパッド金属及び UBM 金属の厚みが増大するにつれて増大するように、ボンドパッド金属及びその上の UBM 金属の厚みに基づき得る。例えば、ボンドパッド 215 上の UBM を含み、バイア 230 が円である実施例において、バイア 230 の直径は、 UBM 厚みの 2 倍プラスボンドパッド金属厚みの 2 倍プラス又はマイナス 20 パーセントであり得る。そのため、 1 ミクロン厚みのボンドパッド 215 及び 2 ミクロン厚み UBM 層では、バイア 230 は、直径 6 ミクロンプラス又はマイナス直径の 20 パーセントであり得る。10

#### 【 0032 】

隣接するバイア 230 間の間隔も、上にある金属厚みに基づき得る。例えば、バイア間隔は、次のバイアまでの最大距離が UBM 金属厚みの 2 倍プラス又はマイナス 20 パーセントであるようにされ得る。そのため、 2 ミクロン厚みの UBM の場合、バイア間距離は 4 ミクロンプラス又はマイナス 20 パーセントであり得る。

#### 【 0033 】

各バイア 230 はこのように、スクエアの数、ひいては各サブトレースの抵抗、が実質的に等しいが、ボンディング特徴スタック（例えば、 UBM 上のはんだバンプ）の抵抗にボンドパッド 215 の上のバイア抵抗を加えた合計より著しく高くなるような方式で、均一トレース部 102 から個別のサブトレース 205 (a) 、 205 (b) 、 205 (c) によりフィードされる。そのため直径 35 ミクロンの、ボンドパッド 215 と UBM との間の従来の誘電体（例えばポリイミド）のバイア開口（例えば、はんだバンプ開口）、及び 1 ミクロンのボンドパッド層（例えばアルミニウム）及び 2 ミクロンの UBM （例えば、ニッケル）では、ボンドパッドの上の従来の単一の誘電体開口を、図 2A に示すような 14 個の個々のフィードラインサブトレースを備えた 14 個の 6 ミクロンの円形のバイア 230 で置き換えることができる。バイアは、サブトレース 205 (a) 、 205 (b) 、 205 (c) のより簡単なルーティングがこれを助けることを可能にするために非対称に形づくられ得る。有効なボンドパッド部 215 (a) 、 215 (b) 、 215 (c) に対するサブトレース 205 (a) 、 205 (b) 、 205 (c) の全体的な（加算された）幅は、ボンディング特徴（例えば、はんだバンプ）に対する総抵抗を最小化するため均一トレース部 102 のものと等しくされ得る。2030

#### 【 0034 】

別の実施例において、図 2A に示すフィードライン構造 200 に比べて、同様であるが高められた電流スプレッドフィードライン構造を生じるように、図 2A に示すようなボンドパッド 215 の上のバイアの代わりに、サブトレースとボンドパッド 215 との間のコントラクト領域 225 にバイアパターンが形成され得る。この実施例は、ボンドパッド 215 上の UBM 層を含む実施例において、それが UBM 層に達する前に、電流がボンドパッド 215 （例えば、 1 μm のアルミニウム）の厚みを横断するため、付加的な電流スプレッドの利点を有する。40

#### 【 0035 】

UBM 上のボンディング特徴のための図 2A に示すエリアフィード実施例は、 UBM においてボンディング特徴インタフェースまでの実質的に全ボンディング特徴断面にわたって均一な電流分布を提供する。この実施例は、標準的なバンプフィード構造に比べて、占める余分なメタライゼーションエリアはあるとしても非常にわずかであり、ボンディング特徴に対する全体的なエリアを小さくする、一層小さなバンプ構造の利点を有する。ボンディング特徴における電流分布の改善された均一性と金属フィード構造の低減されたエリアとを組み合わせると、同じ EM 電流性能に対する IC デバイスの上側金属層における全体的により小さな金属エリア要件をもたらし、そのため IC デバイスに対するコスト削減となる。50

## 【0036】

図2Bは、例示の一実施例に従った、ボンドパッド215にコンタクト領域225内で結合される少なくとも3つのサブトレース255(a)、255(b)及び255(c)を有し、複数のバイア230(a)、230(b)及び230(c)が、ボンドパッド215のエリアにわたって分布されるボンドパッド215上の誘電体層内に形成される、例示のEM耐性フィードライン構造250を示す。ここで、前記サブトレース電流は、サブトレースに対するスクエアの平均数プラス又はマイナス20パーセントの外側の範囲を有し、バイアは、ボンドパッドの上のボンディング特徴に実質的に等しい電流密度を提供するような寸法にされる。この実施例において、バイア230(a)、230(b)及び230(c)は、一層高い電流となる255(b)などの一層短いサブトレースが、より小さなバイアエリアを有するサブトレース255(a)など一層低い電流を搬送するサブトレースに比べて、一層大きいエリアのバイアエリアに結合されるような寸法とされる。外側リングが、それらの対応するバイア230(a)、230(b)及び230(c)のサイズを反映するサイズを有する235(a)、235(b)、235(c)として示されており、電流が、ボンドパッド部から、典型的にコンタクト領域225におけるボンドパッド215の上にあるその上の(図示せず)金属層へ横切るため、電流がボンドパッド部215(a)、215(b)、215(c)を超えて拡がることを示す。

## 【0037】

開示される実施例は更に、同じボンディング特徴(例えば、はんだバンプ)に結合される2つ又はそれ以上の独立フィードライン(即ち、IC上の異なるノードから)があるIC設計に適用することもできる。フィードが電流均一性を最大化させることと組み合わされるべきか、又は各入力ラインでの予期される電流ローディングに基づいて分割されるべきかの判定は自由裁量で成され得る。そのため、均一な分割のため、サブトレースに分けられる前に独立フィードラインが共につながれ得る。各独立フィードラインから予期される電流が設計により既知である場合、ボンディング特徴にフィードするコンタクトバイアの数は、ボンディング特徴のエリアにわたる均一な電流分布をもたらすように入力ライン毎に分割され得る。そのため、各ラインで等しい電流の2つの独立フィードラインがある場合、バイアの半分がフィードラインの一つに、バイアの半分が他方のフィードラインに割り当てられ得る。

## 【0038】

図3は、例示の一実施例に従った、いずれもボンドパッド215に結合される、均一トレース部312を含む第1の独立フィードライン310と、均一トレース部322を含む第2の独立フィードライン320とを有する例示のEM耐性フィードライン構造300を示す。フィードライン310及び320は、各々パターン化されたトレース部315及び325を含み、パターン化されたトレース部315及び325は各々、実質的に等しいサブトレース電流を提供する4つのサブトレース315(a)～(d)及び325(a)～(d)を含む。第1のフィードライン310及び第2のフィードラインは、異なる金属相互接続から形成されて示されている。第1のフィードライン310は、金属層N(例えば、第7のレベル金属)から形成されて示されており、第2のフィードライン320は、金属層N-1(例えば第6のレベル金属)から形成されて示されている。第1のフィードライン310は、I<sub>1</sub>のフィード電流をフィードするよう示されており、第2のフィードライン320は電流I<sub>2</sub>をフィードするよう示されている。I<sub>1</sub>及びI<sub>2</sub>は概して等しい電流ではない。

## 【0039】

図4は、図1Aに示す誘電体開口115に類似する誘電体開口又は複数のバイア(図示せず)によるなど、METn(例えば、銅バンプパッド)を含むバンプパッド419に結合する複数のサブトレースを含む均一トレース部402及びパターン化されたトレース部406を含む、開示されるEM耐性フィードライン401を含むMETn412として示される頂部相互接続金属層を含むバックエンドオブライン(BEOL)メタライゼーションスタック420を含む例示のICデバイス400を示す。BEOLスタック420は、

第1の誘電体層431及び第2の誘電体層432を更に含む。ICデバイス400は、能動回路要素409を有する基板405を含み、能動回路要素におけるノード417が、B EOL420を介する接続により均一トレース部402に結合されて示されている。

#### 【0040】

頂部金属層(例えば、アルミニウム)から形成されるボンドパッド415がバンプパッド419の上にあり、電流スプレッド層を提供するUBMパッドがボンドパッド415上にあり、はんだバンプ435として示されるボンディング特徴がUBMパッド418の上有る。図4に示すMETn412はEM耐性フィードラインを提供するように示されているが、IC400上の任意の金属相互接続層は概して、下にある金属相互接続層など、EM耐性フィードラインを提供するために用いられ得る。或るボンディング特徴では、図示されるUBMパッド418は必要とされない可能性があることに注意されたい。例えば、ボンディング特徴が銅ピラーであるとき、銅ピラーは、銅ボンドパッド直上に形成され得る。

10

#### 【0041】

図5は、例示の一実施例に従った、金属/有機ボンディング材料を含む接合525によりパッド521を有する基板520にボンディングされるパッド511に結合されるフリップチップ配置に開示されるEM耐性フィードライン構造を有するICダイ510を含むスタックされたICデバイス500を示す。開示される実施例は、特に、開示されるフィードライン構造によって提供される接合525の実質的に全断面エリアにわたって提供される電流スプレッドにより示される金属/有機ボンディング材料などの低EM抵抗を備えたボンディング材料に有用であり得る。

20

#### 【0042】

開示される実施例は、ボンディング特徴に結合される任意のフィードライン構造に適用され得る。ボールを含むW CSPは単なる1つの例である。開示される実施例の恩恵を受け得る他のフィード構造には、TSV対RDL対リモートパッド配置が含まれる。

#### 【0043】

2つの異なるリファレンス構造に対し、いずれも、ボンドパッドに結合される実質的に等しいサブトレース電流を提供するような寸法にされた14個のフィードラインサブトレースを備え、ボンドパッド上の2ミクロンのNi UMB及びUBM上のはんだバンプを備えた、図1Aに示すEM耐性フィードライン構造100(エッジフィード)、図2Aに示すEM耐性フィードライン構造200(エリアフィード)に対し、ブラックの式から得た故障までの平均時間(MTTF)パラメータを用いてEM性能を比較するためにシミュレーションが実行された。第1のリファレンス構造は、それらの長さにわたって同じ均一サブトレース幅を有することを除けば、フィードライン構造200と同等の14個のフィードラインサブトレースを含み、第2のリファレンス構造は、ボンドパッド上の同じ層スタックを備えた従来の单一フィードライン配置を含む。ブラックの式(下記)は、EMに起因する半導体回路のMTTFのための数学的モデルである。

30

$$MTTF = Awj^{-n}e^{(-Q/kT)}$$

ここで、Aは定数であり、jは電流密度であり、nはモデルパラメータであり、QはeV(電子ボルト)でのアクティベーションエネルギーであり、kはボルツマン定数であり、TはKでの絶対温度であり、wは金属ライン/ワイヤの幅である。

40

#### 【0044】

実行されたシミュレーションに基づいて、全てそれぞれの長さにわたって同じ均一ライン幅を有する14個のフィードラインサブトレースを有する第1のリファレンス構造は、従来の单一フィードライン配置に比べて約20~40%のはんだ寿命の改善を提供した。これに対し、図1Aに示すフィードライン構造100は、200~300%のはんだ寿命の改善を提供することが分かった。図2Aに示すフィードライン構造200は、一桁以上、すなわち、>1,000%、のはんだ寿命の改善を提供することが分かった。

#### 【0045】

サブトレースを、サブトレース電流にマッチングするような寸法とすることを含む開示

50

される実施例により得られることが分かったM T T F性能インパクトの大きさは、改善の大きさに基づく臨界を示す予期しない結果を証明した。具体的には、エッジフィード実施例でははんだ寿命の200~300%の改善、及びエリアフィード実施例では>1,000%のはんだ寿命の改善であり、いずれも、差の度合いではなく、種類の差が適切に考慮されるべきであるため、従来のフィードライン構造だけではなく第1のリファレンス構造から達成される結果に対して著しい改善を表す。

#### 【0046】

ウエハ半導体基板上に形成される能動回路要素は、一般的に、トランジスタ、ダイオード、キャパシタ、及びレジスタを含む回路要素だけでなく、これらの種々の回路要素を相互接続する信号ライン及び他の電気的導体を含み、IC回路機能を提供するように構成される。本明細書において用いられるように「IC回路機能を提供する」とは、例えば、特定用途向け集積回路(A S I C)、デジタルシグナルプロセッサ、無線周波数チップ、メモリ、マイクロコントローラ及びシステムオンチップ、又はそれらの組み合わせを含み得るICからの回路機能を指す。開示される実施例は、種々のデバイス及び関連する製品を形成する種々のプロセス・フローに統合することが可能である。半導体基板は、その中に種々の要素を及び/その又は上に層を含み得る。これらは、障壁層、他の誘電体層、デバイス構造、能動要素、及びソース領域、ドレイン領域、ピットライン、ベース、エミッタ、コレクタ、導電性ライン、導電性ビアなどを含む受動要素を含み得る。また、バイポーラ、CMOS、BiCMOS、及びMEMSを含む種々のプロセスにおいて、開示される実施例を用いることができる。10 20

#### 【0047】

本開示に関連する習熟者であれば、説明した例示の実施例に変形が成され得ること、及び本発明の特許請求の範囲内で他の実施例を実装し得ることが分かるであろう。

【図1A】

【図1B】

【図1C】

【図2A】

【図2B】

【図3】

FIG. 3

【図4】

【図5】

---

フロントページの続き

(51)Int.Cl. F I

H 01 L 21/60 (2006.01)

(72)発明者 グレゴリー イー ハワード

アメリカ合衆国 75074 テキサス州 プラノ, グランドブルック レーン 4200

(72)発明者 パトリック トンプソン

アメリカ合衆国 75098 テキサス州 ワイリー, ラーゴ グランデ トレイル 306

審査官 佐藤 靖史

(56)参考文献 米国特許出願公開第2008/0026560(US, A1)

特開2007-013063(JP, A)

特開2010-251754(JP, A)

(58)調査した分野(Int.Cl., DB名)

H 01 L 21/88

27/04

21/92