US00RE41039E

### (19) United States

### (12) Reissued Patent

#### **Forthun**

### (10) Patent Number: US RE41,039 E

### (45) Date of Reissued Patent: Dec. 15, 2009

# (54) STACKABLE CHIP PACKAGE WITH FLEX CARRIER

- (75) Inventor: John A. Forthun, Glendora, CA (US)

- (73) Assignee: **Entorian Technologies, LP**, Austin, TX (US)

- (21) Appl. No.: 10/974,046

- (22) Filed: Oct. 26, 2004

#### Related U.S. Patent Documents

#### Reissue of:

(64) Patent No.: 6,473,308

Issued: Oct. 29, 2002

Appl. No.: 09/838,773

Filed: Apr. 19, 2001

#### U.S. Applications:

- (63) Continuation of application No. 09/482,294, filed on Jan. 13, 2000, now Pat. No. 6,262,895.

- (51) Int. Cl. H05K 1/00 (2006.01) H01R 12/00 (2006.01) H05K 1/11 (2006.01) H01L 23/10 (2006.01)

#### (56) References Cited

#### U.S. PATENT DOCUMENTS

3,411,122 A 11/1968 Schillier et al. 3,436,604 A 4/1969 Hyltin

(Continued)

#### FOREIGN PATENT DOCUMENTS

| DE | 004215467 A1 | 11/1992 |

|----|--------------|---------|

| DE | 004214102 A1 | 12/1992 |

| EP | 0426-303 A2  | 10/1990 |

| JР | 359088863 A  | 5/1984  |

| IP | 60-254762 A  | 12/1985 |

| JP | 3641047659 A    | 3/1986  |

|----|-----------------|---------|

| JP | 62-230027 A     | 8/1987  |

| JP | 4209562         | 7/1992  |

| JP | 4-4368167 A     | 12/1992 |

| JP | 50-29534 A      | 2/1993  |

| JP | 63-153849 A     | 6/1998  |

| JP | 2000/307029 A   | 11/2000 |

| JP | 2001/077294 A   | 3/2001  |

| JP | 2001/085592 A   | 3/2001  |

| JP | 2001/332683 A   | 11/2001 |

| JP | 2003/037246 A   | 2/2003  |

| JP | 2003/086760 A   | 3/2003  |

| JP | 2003/086761 A   | 3/2003  |

| JP | 2003/309246 A   | 10/2003 |

| JP | 2003/309247 A   | 10/2003 |

| JP | 2003/347475 A   | 12/2003 |

| JP | 2003/347503 A   | 12/2003 |

| WO | WO 03/037053 A1 | 5/2003  |

|    |                 |         |

#### OTHER PUBLICATIONS

Flexible Printed Circuit Technology—A Versatile Interconnection Option. (Website 2 pages) Fjelstad, Joseph. Dec. 3, 2002.

#### (Continued)

Primary Examiner—Hae Moon Hyeon (74) Attorney, Agent, or Firm—Fish & Richardson P.C.

#### (57) ABSTRACT

A stackable integrated circuit chip package comprising a flex circuit. The flex circuit itself comprises a flexible substrate having opposed, generally planar top and bottom surfaces. Disposed on the top surface is a first conductive pad array, while disposed on the bottom surface is a second conductive pad array and third and fourth conductive pad arrays which are positioned on opposite sides of the second conductive pad array and electrically connected thereto. The chip package further comprises an integrated circuit chip which is electrically connected to the first and second conductive pad arrays, and hence to the third and fourth conductive pad arrays. The substrate is wrapped about at least a portion of the integrated circuit chip such that the third and fourth conductive pad arrays collectively define a fifth conductive pad array which is electrically connectable to another stackable integrated circuit chip package.

#### 8 Claims, 3 Drawing Sheets

# US RE41,039 E Page 2

| U                          | J.S. PATEN       | T DOCUMENTS                   | 5,361,228                  | A 11/1994 | Adachi et al.                 |

|----------------------------|------------------|-------------------------------|----------------------------|-----------|-------------------------------|

| 2.654.204                  | 4/105/           | ) G 1                         | 5,375,041                  | A 12/1994 | McMahon 361/749               |

| 3,654,394 A                |                  | 2 Gordon                      | 5,386,341                  | A 1/1995  | Olson et al.                  |

| 3,766,439 A                |                  | 3 Isaacson<br>2 Waisanburgan  | 5,394,303                  | A 2/1995  | Yamaji                        |

| 3,772,776 A<br>3,983,547 A |                  | 3 Weisenburger<br>5 Almasi    | 5,397,916                  |           | Normington                    |

| 4,079,511 A                |                  | 3 Grabbe                      | 5,428,190                  |           | Stopperan 174/261             |

| 4,288,841 A                |                  | l Gogal                       | 5,438,224                  | A 8/1995  | Papageorge et al.             |

| 4,406,508 A                |                  | 3 Sadigh-Behzadi              | 5,448,511                  |           | Paurus et al                  |

| 4,466,183 A                |                  | 4 Burns                       | 5,477,082                  | A 12/1995 | Buckley, III et al.           |

| 4,513,368 A                |                  | 5 Houseman                    | 5,484,959                  | A 1/1996  | Burns                         |

| 4,587,596 A                |                  | 5 Bunnell                     | 5,502,333                  |           | Bertin et al.                 |

| 4,645,944 A                | <b>A</b> 2/198′  | 7 Uya                         | 5,514,907                  |           | Moshayedi et al.              |

| 4,696,525 A                | <b>A</b> 9/198′  | 7 Coller et al.               | 5,523,619                  | A 6/1996  | McAllister et al.             |

| 4,712,129 A                | <b>A</b> 12/198′ | 7 Orcutt                      | 5,523,695                  |           |                               |

| 4,722,691 A                |                  | Gladd et al.                  | 5,572,065                  |           |                               |

| 4,733,461 A                |                  | Nakano                        | 5,588,205                  |           |                               |

| 4,758,875 A                |                  | B Fujisaki et al.             | 5,594,275                  |           | Kwon et al.                   |

| 4,763,188 A                |                  | 3 Johnson                     | 5,612,570                  |           | Eide et al.                   |

| 4,821,007 A                |                  | Fields et al.                 | 5,631,193                  |           | Difrancesco                   |

| 4,823,234 A                |                  | 9 Konishi et al.<br>9 Berhold | 5,642,055 A<br>3,746,934 A |           |                               |

| 4,833,568 A<br>4,839,717 A |                  | Phy et al.                    | 5,646,446                  |           | Nicewarner, Jr. et al.        |

| 4,862,249 A                |                  | O Carlson                     | 5,654,877                  |           |                               |

| 4,891,789 A                |                  | Quattrini et al.              | 5,657,537                  |           | Saia et al.                   |

| 4,911,643 A                |                  | Perry et al.                  | 5,677,569                  |           | Choi et al.                   |

| 4,953,060 A                |                  | ) Lauffer et al.              | 5,729,894                  |           | Rostoker et al.               |

| 4,956,694 A                |                  | ) Eide                        | 5,744,827                  |           | Jeong et al.                  |

| 4,983,533 A                | <b>A</b> 1/199   |                               | 5,751,553                  | A 5/1998  | Clayton                       |

| 4,985,703 A                | <b>A</b> 1/199   | l Kaneyama                    | 5,763,296                  | A 6/1998  | Casati et al.                 |

| 5,012,323 A                | <b>A</b> 4/199   | l Farnworth                   | 5,764,497                  |           | Mizumo et al.                 |

| 5,016,138 A                |                  | l Woodman                     | 5,776,797                  |           | Nicewarner, Jr. et al 438/107 |

| 5,034,350 A                |                  | Marchisi                      | 5,778,522                  |           |                               |

| 5,041,015 A                |                  | Travis                        | 5,778,552                  |           |                               |

| 5,041,902 A                |                  | McShane                       | 5,783,464                  |           |                               |

| 5,057,903 A                |                  |                               | 5,789,815                  |           | Tessier et al.                |

| 5,064,782 A                |                  | l Nishiguchi<br>l Newman      | 5,801,439 A<br>5,804,870 A |           | Fujisawa et al.               |

| 5,068,708 A<br>5,081,067 A |                  | 2 Shimizu et al.              | 5,805,422                  |           | Otake et al                   |

| 5,099,393 A                |                  | 2 Bentlage et al.             | 5,835,988                  |           |                               |

| 5,104,820 A                |                  | 2 Go et al.                   | 5,841,721                  |           | Kwon et al.                   |

| 5,117,282 A                |                  | 2 Salatino 357/81             | 5,869,353                  |           | Levy et al.                   |

| 5,122,862 A                |                  | 2 Kajihara et al.             | 5,895,970                  |           | Miyoshi et al.                |

| 5,138,430 A                |                  | 2 Gow, 3rd et al.             | 5,899,705                  |           | Akram                         |

| 5,138,434 A                |                  | 2 Wood et al.                 | 5,917,709                  | A 6/1999  | Johnson et al.                |

| 5,158,912 A                | <b>A</b> 10/1992 | 2 Kellerman et al.            | 5,922,061                  | A 7/1999  | Robinson                      |

| 5,159,434 A                | <b>A</b> 10/1992 | 2 Kohno et al.                | 5,925,934                  |           | Lim                           |

| 5,159,535 A                | <b>A</b> 10/1992 | 2 Desai et al.                | 5,926,369                  |           | Ingraham et al 361/699        |

| 5,168,926 A                |                  | 2 Watson et al.               | 5,949,657                  |           | Karabatsos                    |

| 5,198,888 A                |                  | 3 Sugano et al.               | 5,950,304                  |           | Khandros et al 29/831         |

| 5,198,965 A                |                  | 3 Curtis et al.               | 5,953,215                  |           | Karabatsos                    |

| 5,214,307 A                |                  | B Davis                       | 5,959,839                  |           |                               |

| 5,219,794 A                |                  |                               | 5,963,427 A<br>5,973,395 A |           | Bollesen<br>Suzuki et al.     |

| 5,222,014 A<br>5,224,023 A |                  | S Lin<br>3 Smith et al.       | 5,995,370                  |           | Nakamori                      |

| 5,229,916 A                |                  | Frankeny et al.               | 6,002,167                  |           | Hatano et al.                 |

| 5,239,198 A                |                  | 3 Lin et al.                  | 6,002,589                  |           | Perino et al.                 |

| 5,240,588 A                |                  | 3 Uchida                      | 6,014,316                  |           | Eide                          |

| 5,241,454 A                |                  | 3 Ameen et al.                | 6,028,352                  |           |                               |

| 5,243,133 A                |                  | 3 Engle et al.                | 6,028,365                  |           | Akram et al 257/778           |

| 5,247,423 A                |                  | 3 Lin et al.                  | 6,034,878                  |           |                               |

| 5,252,855 A                |                  | 3 Ogawa et al.                | 6,040,624                  |           | Chambers et al.               |

| 5,252,857 A                |                  | 3 Kane et al.                 | 6,072,233                  |           | Corisis et al.                |

| 5,259,770 A                |                  | Bates et al.                  | 6,084,293                  | A 7/2000  | Ohuchi                        |

| 5,261,068 A                |                  | 3 Gaskins et al.              | 6,084,294                  | A 7/2000  | Tomita                        |

| 5,262,927 A                | A 11/1993        | 3 Chia et al.                 | 6,097,087                  |           | Farnworth et al.              |

| 5,276,418 A                |                  | 1 Klosowiak et al.            | 6,121,676                  |           | ě.                            |

| 5,281,852 A                |                  | Normington 257/685            | RE36,916 I                 |           | Moshayedi                     |

| 5,289,062 A                |                  | 4 Wyland                      | 6,157,541                  |           | Hacke                         |

| 5,313,097 A                |                  | Haj-Ali-Ahmadi et al.         | 6,165,817                  |           | Akram                         |

| 5,347,428 A                |                  | Carson et al.                 | 6,172,874 I                |           | Bartilson                     |

| 5,357,478 A                | A 10/1994        | 4 Kikuda et al.               | 6,178,093 1                | D1 1/2001 | Bhatt et al.                  |

| 6 107 652 D1 | 2/2001  | Ch+ -1                  | 6 976 974 D2 4/2005 U                                         |

|--------------|---------|-------------------------|---------------------------------------------------------------|

| 6,187,652 B1 |         | Chou et al.             | 6,876,074 B2 4/2005 Kim                                       |

| 6,205,654 B1 | 3/2001  | Burns                   | 6,884,653 B2 4/2005 Larson                                    |

| 6,208,521 B1 | 3/2001  | Nakatsuka 361/749       | 6,891,729 B2 5/2005 Ko et al.                                 |

| 6,222,737 B1 | 4/2001  | Ross                    | 6,908,792 B2 6/2005 Bruce et al.                              |

| 6,225,688 B1 |         | Kim et al 257/686       | 6,914,324 B2 7/2005 Rapport et al.                            |

| 6,233,650 B1 |         | Johnson et al.          | 6,919,626 B2 7/2005 Burns                                     |

|              |         |                         |                                                               |

| 6,234,820 B1 |         | Perino et al.           | 2001/0006252 A1 7/2001 Kim et al.                             |

| 6,262,895 B1 | 7/2001  | Forthun                 | 2001/0013423 A1 8/2001 Dalal et al.                           |

| 6,265,660 B1 | 7/2001  | Tandy                   | 2001/0015487 A1 8/2001 Forthun                                |

| 6,266,252 B1 | 7/2001  | Karabatsos              | 2001/0035572 A1 11/2001 Isaak                                 |

| 6,281,577 B1 | 8/2001  | Oppermann et al 257/724 | 2001/0040793 A1 11/2001 Inaba                                 |

| 6,285,560 B1 | 9/2001  |                         | 2002/0006032 A1 1/2002 Karabatsos                             |

|              |         | •                       |                                                               |

| 6,288,907 B1 | 9/2001  |                         | <b>y</b>                                                      |

| 6,300,679 B1 |         | Mukerji et al 257/738   | 2002/0048849 A1 4/2002 Isaak                                  |

| 6,303,981 B1 | 10/2001 |                         | 2002/0076919 A1 6/2002 Peters et al.                          |

| 6,310,392 B1 | 10/2001 | Burns                   | 2002/0101261 A1 8/2002 Karabatsos                             |

| 6,313,998 B1 | 11/2001 | Kledzik                 | 2002/0139577 A1 10/2002 Miller                                |

| 6,316,825 B1 | 11/2001 | Park et al.             | 2002/0164838 A1 11/2002 Moon et al.                           |

| 6,323,060 B1 | 11/2001 | Isaak 438/109           | 2002/0180022 A1 12/2002 Emoto                                 |

| 6,329,708 B1 | 12/2001 | Komiyama                |                                                               |

| 6,336,262 B1 |         | Dalal et al.            | 2003/0016710 A1 1/2003 Kamoto                                 |

| 6,351,029 B1 | 2/2002  |                         | 2003/0045025 A1 3/2003 Coyle et al.                           |

| 6,360,433 B1 | 3/2002  |                         | 2003/0049886 A1 3/2003 Salmon                                 |

| 6,368,896 B2 |         | Farnworth et al.        | 2003/0081392 A1 5/2003 Cady et al.                            |

| · / /        |         |                         | 2003/0107118 A1 6/2003 Pflughaupt et al.                      |

| 6,376,769 B1 |         | Chung 174/522           | 2003/0109078 A1 6/2003 Takahashi et al.                       |

| 6,392,162 B1 |         | Karabatsos              | 2003/0168725 A1 9/2003 Warner et al.                          |

| 6,410,857 B1 |         | Gonya                   | 2004/000708 A1 1/2004 Rapport et al.                          |

| 6,426,240 B2 |         | Isaak                   |                                                               |

| 6,426,549 B1 |         | Isaak 257/686           | 2004/0021211 A1 2/2004 Damberg                                |

| 6,426,560 B1 | 7/2002  | Kawamura et al.         | 2004/0031972 A1 2/2004 Pflughaupt et al.                      |

| 6,433,418 B1 | 8/2002  | Fujisawa et al.         | 2004/0045159 A1 3/2004 DiStefano et al.                       |

| 6,444,490 B2 |         | Bertin et al.           | 2004/0065963 A1 4/2004 Kamazos                                |

| 6,444,921 B1 | 9/2002  | Wang et al 174/260      | 2004/0075991 A1 4/2004 Haba et al.                            |

| 6,446,158 B1 | 9/2002  | Karabatsos              | 2004/0099938 A1 5/2004 Kang et al.                            |

| 6,449,159 B1 | 9/2002  | Haba                    | 2004/0104470 A1 6/2004 Bang et al.                            |

| 6,452,826 B1 | 9/2002  | Kim et al.              | 2004/0115866 A1 6/2004 Bang et al.                            |

| 6,462,412 B2 |         | Kamei et al.            | 2004/0150107 A1 8/2004 Cha et al.                             |

| 6,465,877 B1 |         | Farnworth et al.        |                                                               |

| 6,465,893 B1 |         | Khandros et al 257/777  |                                                               |

| 6,473,308 B2 | 10/2002 |                         | 2004/0203190 A1 10/2004 Pflughapt et al.                      |

| 6,486,544 B1 |         | Hashimoto               | 2004/0217461 A1 11/2004 Damberg                               |

| 6,489,178 B2 |         | Coyle et al.            | 2004/0217471 A1 11/2004 Haba                                  |

| 6,489,687 B1 |         | Hashimoto               | 2004/0238931 A1 12/2004 Haba et al.                           |

|              |         |                         | 2004/0245617 A1 12/2004 Damberg et al.                        |

| 6,492,718 B2 | 12/2002 |                         | 2005/0018495 A1 1/2005 Bhakta et al.                          |

| 6,509,639 B1 | 1/2003  |                         | 2005/0035440 A1 2/2005 Mohammed                               |

| 6,514,793 B2 | 2/2003  |                         | 2005/0040508 A1 2/2005 Lee                                    |

| 6,528,870 B2 |         | Fukatsu et al.          | 2005/0133897 A1 6/2005 Baek et al.                            |

| 6,552,910 B1 |         | Moon et al.             |                                                               |

| 6,560,117 B2 | 5/2003  |                         | OTHER RIPLICATIONS                                            |

| 6,572,387 B2 |         | Burns et al.            | OTHER PUBLICATIONS                                            |

| 6,576,992 B1 | 6/2003  | Cady et al.             |                                                               |

| 6,588,095 B2 | 7/2003  | Pan                     | Die Products: Ideal IC Packaging for Demanding Applica-       |

| 6,590,282 B1 | 7/2003  | Wang et al.             |                                                               |

| 6,600,222 B1 |         | Levardo                 | tions—Advanced packaging that's no bigger than the die        |

| 6,614,664 B2 | 9/2003  |                         | itself brings together high performance and high reliabliity  |

| 6,620,651 B2 |         | He et al.               | with small size and low cost. (Website 3 pages with 2 fig-    |

| 6,627,984 B2 |         | Bruce et al.            | ures) Larry Gilg and Chris Windsor. Dec. 23, 2002. Pub-       |

| 6,657,134 B2 |         | Spielberger et al.      | lished on Internet.                                           |

| 6,660,561 B2 | 12/2003 | 1 0                     | noned on memer.                                               |

| 6,677,670 B2 |         | Kondo                   | Chip Scale Review Online—An Independent Journal Dedi-         |

| , ,          |         |                         | cated to the Advancement of Chip-Scale Electrons. (Website    |

| 6,683,377 B1 |         | Shim et al.             | 9 pages) Fjelstad, Joseph, Pacific Consultants L.L.C., Pub-   |

| 6,690,584 B2 |         | Uzuka et al.            |                                                               |

| 6,699,730 B2 |         | Kim et al.              | lished Jan. 2001 on Internet.                                 |

| 6,707,684 B1 |         | Andric et al.           | Florible Thinking Exemining the Florible Circuit Tongs        |

| 6,709,893 B2 |         | Moden et al.            | Flexible Thinking Examining the Flexible Circuit Tapes.       |

| 6,768,660 B2 |         | Kong et al.             | (Website 2 pages) Fjelstad, Joseph., Published Apr. 20, 2000  |

| 6,781,240 B2 | 8/2004  |                         | on Internet.                                                  |

| 6,803,651 B1 | 10/2004 |                         | D. D. D. J. J. J. 400 D. V. El. 3.11. D. V.                   |

| 6,812,567 B2 |         | Kim et al.              | Ron Bauer, Intel. "Stacked-CSP Delivers Flexibility, Reli-    |

| 6,833,984 B1 |         | Belgacem                | ablilty, and Space–Saving Capabilities", vol. 3, Spring 2002. |

| 6,849,949 B1 |         | Lyu et al.              | Published on the Internet.                                    |

|              |         |                         |                                                               |

Tessera Introduces uZ ä—Ball Stacked Memory Package for Computing and Portable Electronic Products Joyce Smaragdis, Tessera Public Relations, Sandy Skees, MCA PR (www.tessera.com/news\_events/press\_coverage.cfm); 2 figures that purport to be directed to the uZä—Bali Stacked Memory p Package Published Jul. 17, 2002 in San Jose, Ca.

Denise-Pac Microsystems, Breaking Space Barriers, 3-D Technology 1993.

1993 Proceedings, 42nd Electronic Components & Technology Conference, May 18–20, 1992.

Research Disclosure, Organic Card Device Carrier, 31318, May 1990, No. 313.

IBM Technical Disclosure Bulletin, vol. 23, No. 12, May 1981

IBM Technical Disclosure Bulletin, vol. 20, No. 11A, Apr. 1978.

IBM Technical Disclosure Bulletin, vol. 32, No. 38, Aug. 1989.

Orthogonal Chip Mount—A 3D Hybrid Wafer Scale Integration, International Electron Device Meeting IEDM Technical Digest, Washington, D.C., Dec. 6–9, 1987.

# STACKABLE CHIP PACKAGE WITH FLEX CARRIER

Matter enclosed in heavy brackets [ ] appears in the original patent but forms no part of this reissue specification; matter printed in italics indicates the additions made by reissue.

# CROSS-REFERENCE TO RELATED APPLICATIONS

The present Application is a continuation of U.S. application Ser. No. 09/482,294 entitled STACKABLE CHIP PACKAGE WITH FLEX CARRIER filed Jan. 13, 2000 now U.S. Pat. No. 6,262,895.

# STATEMENT RE: FEDERALLY SPONSORED RESEARCH/DEVELOPMENT

(Not Applicable)

#### BACKGROUND OF THE INVENTION

The present invention relates generally to chip stacks, and more particularly to a stackable integrated circuit chip package including a flex circuit which allows multiple chip packages to be quickly, easily and inexpensively assembled into a chip stack having a minimal profile.

Multiple techniques are currently employed in the prior art to increase memory capacity on a printed circuit board. Such techniques include the use of larger memory chips, if available, and increasing the size of the circuit board for purposes of allowing the same to accommodate more memory devices or chips. In another technique, vertical plug-in boards are used to increase the height of the circuit board to allow the same to accommodate additional memory devices or chips.

Perhaps one of the most commonly used techniques to increase memory capacity is the stacking of memory devices into a vertical chip stack, sometimes referred to as 3D packaging or Z-Stacking. In the Z-Stacking process, from two (2) to as many as eight (8) memory devices or other integrated circuit (IC) chips are interconnected in a single component (i.e., chip stack) which is mountable to the "footprint" typically used for a single package device such as a packaged chip. The Z-Stacking process has been found to be volumetrically efficient, with packaged chips in TSOP (thin small outline package) or LCC (leadless chip carrier) form generally being considered to be the easiest to use in relation thereto. Though bare dies or chips may also be used in the Z-Stacking process, such use tends to make the stacking process more complex and not well suited to automation.

In the Z-Stacking process, the IC chips or packaged chips must, in addition to being formed into a stack, be electrically interconnected to each other in a desired manner. There is known in the prior art various different arrangements and techniques for electrically interconnecting the IC chips or packaged chips within a stack. Examples of such arrangements and techniques are disclosed in Applicant's U.S. Pat. Nos. 4,956,694 entitled INTEGRATED CIRCUIT CHIP STACKING issued Sep. 11, 1990, 5,612,570 entitled CHIP STACK AND METHOD OF MAKING SAME issued Mar. 18, 1997, and 5,869,353 entitled MODULAR PANEL STACKING PROCESS issued Feb. 9, 1999.

The various arrangements and techniques described in these issued patents and other currently pending patent 65 applications of Applicant have been found to provide chip stacks which are relatively easy and inexpensive to 2

manufacture, and are well suited for use in a multitude of differing applications. The present invention provides yet a further alternative arrangement and technique for forming a chip stack which involves the use of stackable integrated circuit chip packages including flex circuits. The inclusion of the flex circuits in the chip packages of the present invention provides numerous advantages in the assembly of the chip stack, including significantly greater ease in achieving and maintaining the alignment between the chip packages within the stack. Additionally, the use of the flex circuits allows for the assembly of the chip packages into a chip stack which has a minimal profile.

#### BRIEF SUMMARY OF THE INVENTION

In accordance with the present invention, there is provided a stackable integrated circuit chip package. The chip package comprises a flex circuit which itself comprises a flexible substrate having opposed, generally planar top and bottom surfaces. The substrate is preferably fabricated from a polyamide which has a thickness of several mils or less, and may have a thickness down to about 1 mil. The substrate preferably has a generally rectangular configuration defining a pair of longitudinal peripheral edge segments and a pair of lateral peripheral edge segments. Disposed on the top surface of the substrate is a first conductive pad array, while disposed on the bottom surface is a second conductive pad array. The first and second conductive pad arrays extend between the longitudinal peripheral edge segments in spaced relation to the lateral peripheral edge segments. Also disposed on the bottom surface of the substrate on opposite sides of the second conductive pad array are third and fourth conductive pad arrays which extend between the longitudinal peripheral edge segments along respective ones of the lateral peripheral edge segments. The third and fourth conductive pad arrays are each electrically connected to the second conductive pad

In the chip package of the present invention, the first conductive pad array preferably comprises a first set of pads, with the second conductive pad array preferably comprising a second set of pads which are arranged in an identical pattern to the first set of pads such that the pads of the first set are aligned (i.e., in registry with) respective ones of the pads of the second set. Similarly, the third conductive pad array comprises a third set of pads, with the fourth conductive pad array comprising a fourth set of pads. The third and fourth sets of pads are preferably arranged on the bottom surface of the substrate in patterns which are mirror images to each other. The pads of the third and fourth sets are electrically connected to respective ones of the pads of the second set through the use of conductive tracings.

The pads of the first through fourth sets and conductive tracings are preferably fabricated from very thin copper having a thickness in the range of from about 5 microns to about 25 microns through the use of conventional etching techniques. Advantageously, the use of the thin copper for the pads and conductive tracings allows for etching line widths and spacings down to a pitch of about 4 mils which substantially increases the routing density. The pads and tracings collectively define a conductive pattern of the flex circuit. Extending through the substrate between respective pairs of the pads of the first and second sets are a plurality of crossslits, the use of which will be described in more detail below.

In addition to the flex circuit, the chip package of the present invention comprises an integrated circuit chip which is electrically connected to the first and second conductive pad arrays, and hence to the third and fourth conductive pad

arrays by virtue of their electrical connection to the second conductive pad array via the conductive tracings. The integrated circuit chip preferably comprises a flip chip device or a fine pitch BGA (ball grid array) device having a body which is of a generally rectangular configuration defining opposed, generally planar top and bottom surfaces, a pair of longitudinal sides, and a pair of lateral sides. Protruding from the bottom surface of the body are a plurality of generally semi-spherically shaped conductive contacts which are preferably arranged in an identical pattern to the first and second sets of pads. In the present chip package, the electrical connection of the integrated circuit chip to the first and second conductive pad arrays is facilitated by the insertion of the conductive contacts into the cross-slits of respective ones of the pads of the first set, and advancement therethrough to protrude from respective ones of the pads of the second set and hence the bottom surface of the substrate.

In the chip package of the present invention, the substrate is wrapped about at least a portion of the integrated circuit chip such that the third and fourth conductive pad arrays collectively define a fifth conductive pad array which is electrically connectable to another stackable integrated circuit chip package. The fifth conductive pad array comprises the third and fourth sets of pads which, when the substrate is wrapped about the integrated circuit chip, are arranged in an identical pattern to the first and second sets of pads. The substrate is wrapped about the longitudinal sides of the body such that the fifth conductive pad array extends over the top surface of the body and the third and fourth sets of pads making up the fifth conductive pad array are in substantial alignment or registry with respective pairs of the first and second sets of pads.

The substrate is preferably sized relative to the integrated circuit chip such that the lateral peripheral edge segments of the substrate extend along the top surface of the body in 35 generally parallel relation to each other and are separated by a narrow gap, with the lateral sides of the body being substantially flush with respective ones of the longitudinal peripheral edge segments of the substrate. As such, the integrate circuit chip is positioned upon the central portion of the 40 substrate (which includes the first and second conductive pad arrays thereon), with the opposed end portions of the substrate (which include the third and fourth conductive pad arrays thereon) being wrapped about the integrated circuit chip so as to cover the top surface of the body thereof. These 45 end portions of the substrate are preferably attached to the top surface of the body through the use of an adhesive. Additionally, the chip package may be provided with a pair of heat sinks which are attached to respective ones of the lateral sides of the body of the integrated circuit chip.

In addition to the end portions of the substrate being adhesively secured to the top surface of the body of the integrated circuit chip, the conductive contacts of the integrated circuit chip are preferably soldered to respective ones of the pads of the second set. In this respect, each of the conductive contacts may be pre-coated with solder paste or flux prior to the placement of the integrated circuit chip upon the first conductive pad array, with the application of heat to the chip package subsequent to the flex circuit being wrapped about the integrated circuit chip effectuating the soldering of the conductive contacts to the second set of pads, and hence the conductive pattern of the flex circuit.

Advantageously, those portions of the conductive contacts protruding from the pads of the second set and hence the bottom surface of the substrate may be electrically connected to respective ones of the conductive pads of a printed circuit board, or to respective ones of the third and fourth

4

sets of pads of the fifth conductive pad array of another identically configured stackable integrated circuit chip package. In this respect, multiple chip packages of the present invention may be stacked upon one another, with solder paste or flux being pre-applied to the third and fourth sets of pads of the fifth conductive pad array prior to the stacking of another chip package thereupon such that the subsequent application of heat to the stack facilitates the desired electrical connection of the chip packages to each other. The engagement between the exposed portions of the conductive contacts and the third and fourth sets of pads of the fifth conductive pad array performs a self-aligning function during the soldering process, thus simply requiring that the longitudinal and lateral edges of the chip packages in the stack be aligned with each other prior to the application of heat thereto.

Those of ordinary skill in the art will recognize that the flex circuit need not necessarily be provided with the first conductive pad array in that the conductive contacts of the integrated circuit chip may be advanced through the crossslits within the substrate and electrically mounted via soldering to only the pads of the second set forming the second conductive pad array. Additionally, the flex circuit may be adapted to be usable in conjunction with a bare die device by eliminating the cross-slits and electrically connecting the pads of the first set forming the first conductive pad array to respective ones of the pads of the second set forming the second pad array through the use of vias.

#### BRIEF DESCRIPTION OF THE DRAWINGS

These, as well as other features of the present invention, will become more apparent upon reference to the drawings wherein:

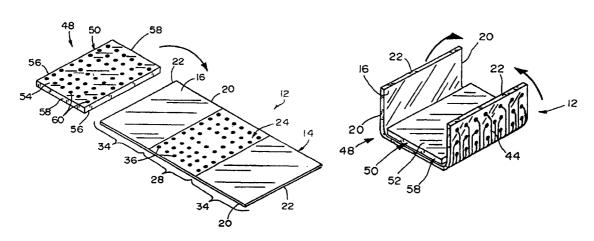

FIG. 1 is a top perspective view of the stackable integrated circuit chip package constructed in accordance with the present invention;

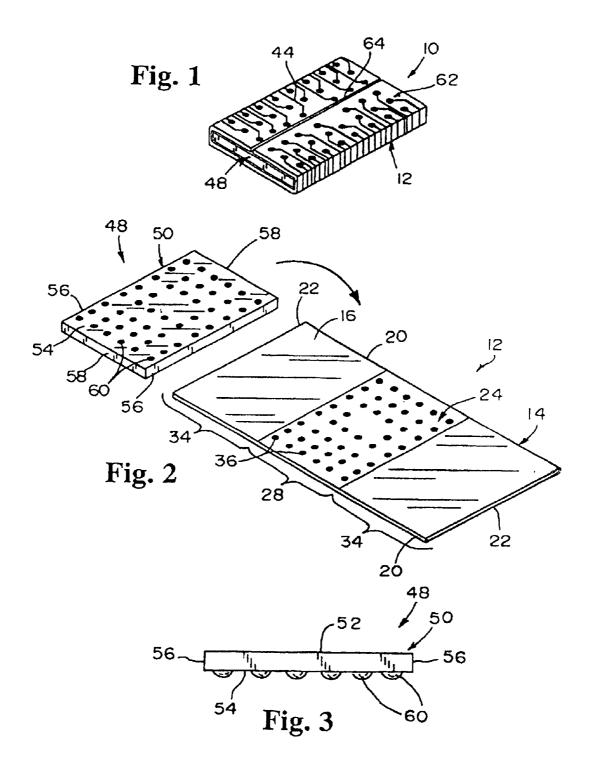

FIG. 2 is a top perspective view of the flex circuit and integrated circuit chip components of the chip package shown in FIG. 1;

FIG. 3 is a side-elevational view of the integrated circuit chip shown in FIG. 2;

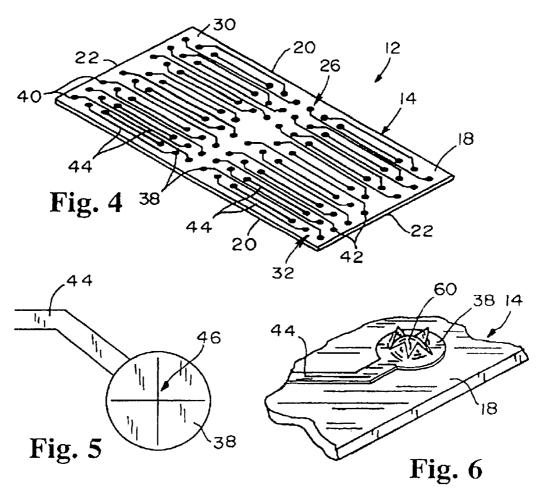

FIG. 4 is a top perspective view of the bottom surface of the flex circuit of the present chip package, the top surface thereof being perspectively shown in FIG. 2;

FIG. 5 is an enlarged view of one of the conductive pads of the flex circuit;

FIG. 6 is a partial perspective view of the present chip package, illustrating the manner in which the integrated circuit chip thereof is electrically connected to the conductive pattern of the flex circuit;

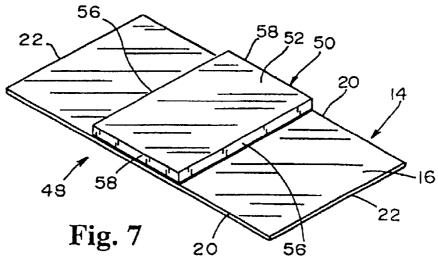

FIG. 7 is a top perspective view illustrating an initial step in the sequence of assembling the present chip package;

FIG. **8** is a perspective view illustrating one of the steps in the sequence of assembling the present chip package;

FIG. 9 is a top perspective view of a chip stack including multiple chip packages of the present invention; and

FIG. 10 is a top perspective view of a chip stack similar to that shown in FIG. 9 with the further inclusion of heat sinks on each of the chip packages.

#### DETAILED DESCRIPTION OF THE INVENTION

Referring now to the drawings wherein the showings are for purposes of illustrating a preferred embodiment of the present invention only, and not for purposes of limiting the

same, FIG. 1 perspectively illustrates a stackable integrated circuit chip package 10 constructed in accordance with the present invention. Referring now to FIGS. 2 and 4, the chip package 10 comprises a flex circuit 12 which itself comprises a flexible substrate 14 having a generally planar top surface 16 and a generally planar bottom surface 18. The substrate 14 preferably has a generally rectangular configuration defining a pair of longitudinal peripheral edge segments 20 and a pair of lateral peripheral edge segments 22. The substrate 14 is preferably fabricated from a polyamide which has a thickness of several mils or less, and may have a thickness down to about 1 mil.

Disposed on the top surface 16 of the substrate 14 is a first conductive pad array 24, while disposed on the bottom surface 18 is a second conductive pad array 26. The first and 15 second conductive pad arrays 24, 26 are located upon a central portion 28 of the substrate 14 and extend between the longitudinal peripheral edge segments 20 in spaced relation to the lateral peripheral edge segments 22. 20 Also disposed on the bottom surface 18 of the substrate 14 on opposite 20 sides of the second conductive pad array 26 is a third conductive pad array 30 and a fourth conductive pad array 32. The third and fourth conductive pad arrays 30, 32 are located upon respective ones of an opposed pair of end portions 34 of the substrate 14 and extend between the longitudinal peripheral edge segments 20 along respective ones of the lateral peripheral edge segments 22. The third and fourth conductive pad arrays 30, 32 are each electrically connected to the second conductive pad array 26 in a manner which will be described in more detail below.

In the chip package 10, the first conductive pad array 24 preferably comprises a first set of pads 36, with the second conductive pad array 26 preferably comprising a second set of pads 38 which are arranged in an identical pattern to the first set of pads 36 such that the pads 36 of the first set are 35 aligned (i.e., in registry with) respective ones of the pads 38 of the second set. Similarly, the third conductive pad array 30 comprises a third set of pads 40, with the fourth conductive pad array 32 comprising a fourth set of pads 42. The on the bottom surface 18 of the substrate 14 in patterns which are mirror images to each other. The pads 40, 42 of the third and fourth sets are electrically connected to respective ones of the pads 38 of the second set through the use of conductive tracings 44.

The pads 36, 38, 40, 42 of the first through fourth sets and conductive tracings 44 are preferably fabricated from very thin copper having a thickness in the range of from about 5 microns to about 25 microns through the use of conventional etching techniques. Advantageously, the use of the thin cop- 50 per for pads 36, 38, 40, 42 and conductive tracings 44 allows for etching line widths and spacings down to a pitch of about 4 mils which substantially increases the routing density on the flex circuit 12. The pads 36, 38, 40, 42 and conductive tracings 44 collectively define a conductive pattern of the 55 flex circuit 12. As seen in FIG. 5, extending through the substrate 14 between respective pairs of the pads 36, 38 of the first and second sets are a plurality of crossslits 46, the use of which will be described in more detail below.

Referring now to FIGS. 2 and 3, in addition to the flex 60 circuit 12, the chip package 10 of the present invention comprises an integrated circuit chip 48 which is electrically connected to the first and second conductive pad arrays 24, 26, and hence to the third and fourth conductive pad arrays 30, 32 by virtue of their electrical connection to the second con- 65 ductive pad array 26 via the conductive tracings 44. The integrated circuit chip 48 preferably comprises a flip chip

device or a fine pitch BGA (ball grid array) device, and includes a rectangularly configured body 50 defining a generally planar top surface 52, a generally planar bottom surface 54, a pair of longitudinal sides 56, and a pair of lateral sides 58. Protruding from the bottom surface 54 of the body 50 are a plurality of generally semi-spherically shaped conductive contacts 60 which are preferably arranged in an identical pattern to each of the first and second sets of pads 36, 38. As seen in FIGS. 5 and 6 and as will also be discussed in more detail below, in the chip package 10, the electrical connection of the integrated circuit chip 48 to the first and second conductive pad arrays 24, 26 is facilitated by the insertion of the conductive contacts 60 into the cross-slits 46 of respective ones of the pads 36 of the first set, and advancement therethrough to protrude from respective ones of the pads 38 of the second set and hence the bottom surface 18 of the central portion 28 of the substrate 14.

As best seen in FIGS. 1 and 8, in the chip package 10 of the present invention, the flex circuit 12, and more particularly the substrate 14 thereof, is wrapped about at least a portion of the integrated circuit chip 48 such that the third and fourth conductive pad arrays 30, 32 collectively define a fifth conductive pad array 62 which is electrically connectable to another stackable integrated circuit chip package 10. The fifth conductive pad array 62 comprises the third and fourth sets of pads 40, 42 which, when the substrate 14 is wrapped about the integrated circuit chip 48, are arranged in an identical pattern to each of the first and second sets of pads 36, 38. The substrate 14 is wrapped about the longitudinal sides 56 of the body 50 of the integrated circuit chip 48 such that the fifth conductive pad array 62 extends over the top surface 52 of the body 50 and the third and fourth sets of pads 40, 42 making up the fifth conductive pad array 62 are in substantial alignment or registry with respective pairs of the first and second sets of pads 36, 38. As such, in assembling the chip package 10, the integrated circuit chip 48 is initially positioned upon the top surface 16 of the central portion 28 of the substrate 14, with the opposed end portions 34 of the substrate 14 thereafter being wrapped about the third and fourth sets of pads 40, 42 are preferably arranged 40 engagement circuit chip 48 so as to substantially cover the top surface 52 of the body 50 thereof. 52 of the body 50 and the third and fourth sets of pads 40, 42 making up the fifth conductive pad array 62 are in substantial alignment or registry with respective pairs of the first and second sets of pads 45 36, 38. As such, in assembling the chip package 10, the integrated circuit chip 40 is initially positioned upon the top surface 16 of the central portion 28 of the substrate 14, with the opposed end portions 34 of the substrate 14 thereafter being wrapped about the integrated circuit chip 48 so as to substantially cover the top surface 52 of the body 50 thereof.

As is most apparent from FIG. 1, the substrate 14 is preferably sized relative to the integrated circuit chip 48 such that when the substrate 14 is wrapped about the integrated circuit chip 48, the lateral peripheral edge segments 22 extend along the top surface 52 of the body 50 in generally parallel relation to each other and are separated by a narrow gap 64, and the lateral sides 58 of the body 50 are substantially flush with respective ones of the longitudinal peripheral edge segments 20 of the substrate 14. As will be recognized, the top surface 16 of the substrate 14 at the end portions 34 thereof is in direct, abutting contact with the body 50 of the integrated circuit chip 48. The end portions 34 of the substrate 14 are preferably attached to the top surface 52 of the body 50 through the use of an adhesive. Additionally, as seen in FIG. 10, since the substrate 14 is wrapped about only the longitudinal peripheral edge segments 20 of the body 14 thus leaving the lateral peripheral

edge segments 22 uncovered, the chip package 10 may be provided with a pair of heat sinks 66 which are attached to respective ones of the lateral sides 58 of the body 50 of the integrated circuit chip 48.

In addition to the end portions 34 of the substrate 14 being adhesively secured to the top surface 52 of the body 50 of the integrated circuit chip 48, the conductive contacts 60 of the integrated circuit chip 48 are preferably soldered to respective ones of the pads 38 of the second set. To facilitate such soldering, each of the conductive contacts 60 may be precoated with solder paste or flux prior to the placement of the integrated circuit chip 48 upon the first conductive pad array 24, with the application of heat to the chip package 10 subsequent to the flex circuit 12 being wrapped about the integrated circuit chip 48 effectuating the soldering of the conductive contacts 60 to the second set of pads 38, and hence the conductive pattern of the flex circuit 12.

As is apparent from the aforementioned discussion regarding the structural attributes of the chip package 10, the preferred method of assembling the same comprises the ini- 20 tial step of fabricating the flex circuit 12 to include a desired conductive pattern thereon. The integrated circuit chip 48 is then positioned upon the first conductive pad array 24 in the above-described manner, with sufficient pressure being applied to the body 50 of the integrated circuit chip 48 as is 25 needed to facilitate the advancement of the conductive contacts 60 thereof through the cross-slits 46 so as to protrude from the pads 38 of the second set. As indicated above, the conductive contacts 60 of the integrated circuit chip 48 are preferably pre-coated with solder paste or flux. Thereafter, 30 the substrate 14 of the flex circuit 12 is tightly wrapped about the body 50 of the integrated circuit chip 48 in the above-described manner, with the end portions 34 of the substrate 14 then being adhesively secured to the top surface 52 of the body 50 to facilitate the formation of the fifth 35 conductive pad array 62 which extends over the top surface 52 of the body 50. As will be recognized, the second conductive pad array 26 extends over the bottom surface 54 of the body 50, as does the first conductive pad array 24. However, only the second and fifth conductive pad arrays 26, 62 are 40 exposed due to the manner in which the substrate 14 is wrapped about the integrated circuit chip 48. As will be discussed in more detail below, heat is typically not applied to the chip package 10 until the same is incorporated into a chip stack including at least one additional chip package 10.

Referring now to FIGS. 9 and 10, two or more chip packages 10 of the present invention may be assembled into a chip stack 68. In the chip stack 68, multiple chip packages 10 are stacked upon one another such that those portions of the conductive contacts 60 protruding from the flex circuit 50 12 in each of the chip packages 10 other than for the lowermost chip package 10 are engaged to respective ones of the third and fourth sets of pads 40, 42 of the fifth conductive pad array 62 of another chip package 10. The subsequent application of heat to the chip stack 68 facilitates a soldering 55 process wherein the integrated circuit chips 48 of the chip packages 10 are securely mounted to respective ones of the flex circuits 12 and electrically connected to the conductive pattern thereof, and the conductive contacts 60 of the chip packages 10 other than for the lowermost chip package 10 60 are electrically connected to the fifth conductive pad array 62 of another chip package 10 in a manner securely mounting the chip packages 10 to each other to form the chip stack **68**. To increase the strength of the electrical connections between the chip packages 10 within the chip stack 68, the 65 third and fourth sets of pads 40, 42 of the fifth conductive pad array 62 in each chip package 10 may include additional

8

quantities of solder paste or flux pre-applied thereto prior to the stacking of another chip package 10 thereupon.

Advantageously, the engagement between the exposed portions of the conductive contacts 60 of one chip package 10 and the third and fourth sets of pads 40, 42 of the fifth conductive pad array 62 of another chip package 10 performs a self-aligning function during the soldering process, thus simply requiring that the longitudinal and lateral edges of the chip packages 10 in the chip stack 68 be aligned with each other prior to the application of heat thereto. Though not shown, the chip packages 10 in the chip stack 68 will typically be clamped to one another prior to the application of heat thereto for purposes of maintaining the longitudinal and lateral edges of the chip packages 10 in proper registry. Such clamping may be facilitated through the use of a clip which is secured to the flex circuits 12 of the uppermost and lowermost chip packages 10 within the chip stack 68. If the chip packages 10 within the chip stack 68 are provided with the heat sinks 66 as shown in FIG. 10, such clip may be applied to the heat sinks 66 of the uppermost and lowermost chip packages 10 within the chip stack 68. Those portions of the conductive contacts 60 protruding from flex circuit 12 in the lowermost chip package 10 within the chip stack 68 may be electrically connected to respective ones of the conductive pads of a printed circuit board or mother board.

Those of ordinary skill in the art will recognize that the flex circuit 12 of the chip package 10 need not necessarily be provided with the first conductive pad array 24 in that the conductive contacts 60 of the integrated circuit chip 48 may be advanced through the cross-slits 46 within the substrate 14 and electrically mounted via soldering to only the pads 38 of the second set forming the second conductive pad array 26. Additionally, the flex circuit 12 may be adapted to be usable in conjunction with a bare die device by eliminating the cross-slits 46 and electrically connecting the pads 36 of the first set forming the first conductive pad array 24 to respective ones of the pads 38 of the second set forming the second conductive pad array 34 through the use of vias.

Additional modifications and improvements of the present invention may also be apparent to those of ordinary skill in the art. Thus, the particular combination of parts and steps described and illustrated herein is intended to represent only one embodiment of the present invention, and is not intended to serve as limitations of alternative devices within the spirit and scope of the invention.

What is claimed is:

- 1. A stackable integrated circuit chip package, comprising:

- a flex circuit including a flexible substrate and a conductive pattern formed thereon, the flexible substrate having a central portion and an opposed end portions, the conductive pattern starting from the central portion and terminating at the opposed end portions; and

- an integrated circuit chip electrically connected to the conductive pattern at the central portion;

- the flex circuit being wrapped about at least a portion of the integrated circuit chip such that the conductive pattern is electrically connectable to at least one other stackable integrated circuit chip package.

- 2. A method of assembling a stackable integrated circuit chip package, comprising the steps of:

- (a) providing a flex circuit including a flexible substrate having a conductive pattern formed thereon, the flexible substrate defining a central portion and an opposed end portions, the conductive pattern starting from the central portion and terminating at the opposed end portions;

- (b) electrically connecting an integrated circuit chip to the conductive pattern at the central portion of the flexible substrate:

- (c) wrapping at least one end portion about the integrated circuit chip such that the conductive pattern is electrically connectable to at least one other stackable integrated circuit chip package; and

- (d) securing the integrated circuit chip and the flex circuit to each other

- 3. The method of claim 2 wherein step (c) comprises:

- (1) soldering the integrated circuit chip to the conductive pattern; and

- (2) adhesively affixing portions of the substrate of the flex circuit to the integrated circuit chip.

- 4. The method of claim 2 further comprising the step of:

- (d) electrically connecting the conductive pattern to another stackable integrated circuit chip package.

- 5. A stackable integrated circuit chip package, comprising: a flex circuit including a flexible substrate and a conductive pattern formed thereon, the flexible substrate having a central portion and opposed end portions, the conductive pattern being electrically connected to first and second conductive pad arrays disposed on the central portion on opposite surfaces of the flex substrate and to a third conductive pad array disposed on one of the opposed end portions; and an integrated circuit chip electrically connected to the conductive pattern at the central portion and the first conductive pad array, the flex circuit being wrapped about at least a portion of the integrated circuit chip to expose the third conductive pad array.

- 6. A method of assembling a stackable integrated circuit chip package, comprising the steps of: (a) providing a flex circuit including a flexible substrate and a conductive pattern formed thereon, the flexible substrate having a central 35 portion and opposed end portions, the conductive pattern being electrically connected to first and second conductive pad arrays disposed on the central portion on opposite surfaces of the flex substrate and to a third conductive pad array disposed on one of the opposed end portions; (b) electrically 40 connecting an integrated circuit chip to the conductive pat-

10

tern at the central portion and the first conductive pad array; (c) wrapping the flex circuit about at least a portion of the integrated circuit chip to expose the third conductive pad array; and (d) securing the integrated circuit chip and the flex circuit to each other.

7. A stackable integrated circuit chip package, comprising: a flex circuit including a flexible substrate and a conductive pattern formed thereon, the flexible substrate having a central portion and opposed end portions, the conductive pattern being electrically connected to a central portion conductive pad array disposed on the central portion of the flex substrate and to plural conductive pads disposed on one of the opposed end portions; mad an integrated circuit chip electrically connected to the conductive pattern at the cen-15 tral portion conductive pad array; the flex circuit being wrapped about at least a portion of the integrated circuit chip such that the plural conductive pads disposed on one of the opposed end portions are exposed; and the plural conductive pads disposed on one of the opposed end portions defining an end portion conductive pad array that is electrically connectable to the contacts of another integrated circuit chip.

8. A method of assembling a stackable integrated circuit chip package, comprising the steps of: (a) providing a flex circuit including a flexible substrate and a conductive pattern formed thereon, the flexible substrate having a central portion and opposed end portions, the conductive pattern being electrically connected to a central portion conductive pad array disposed on the central portion of the flux substrate and to plural conductive pads disposed on one of the opposed end portions; (b) electrically connecting an integrated circuit chip to the conductive pattern at the central portion conductive pad array; (c) wrapping the flex circuit about the integrated circuit chip such that the plural conductive pads disposed on one of the opposed end portions are exposed and define an end portion conductive pad array that is electrically connectable to the contacts of another integrated circuit chip; and (d) securing the integrated circuit chip and the flex circuit to each other.

\* \* \* \* :