(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第5955616号

(P5955616)

(45) 発行日 平成28年7月20日(2016.7.20)

(24) 登録日 平成28年6月24日(2016.6.24)

(51) Int.Cl.

H01L 21/8242 (2006.01)

H01L 27/108 (2006.01)

F 1

H01L 27/10 321

請求項の数 4 (全 25 頁)

(21) 出願番号 特願2012-90014 (P2012-90014)

(22) 出願日 平成24年4月11日 (2012.4.11)

(65) 公開番号 特開2012-231132 (P2012-231132A)

(43) 公開日 平成24年11月22日 (2012.11.22)

審査請求日 平成27年4月7日 (2015.4.7)

(31) 優先権主張番号 特願2011-91530 (P2011-91530)

(32) 優先日 平成23年4月15日 (2011.4.15)

(33) 優先権主張国 日本国 (JP)

(73) 特許権者 000153878

株式会社半導体エネルギー研究所

神奈川県厚木市長谷398番地

(72) 発明者 齋藤 利彦

神奈川県厚木市長谷398番地 株式会社

半導体エネルギー研究所内

審査官 上田 智志

最終頁に続く

(54) 【発明の名称】半導体記憶装置

## (57) 【特許請求の範囲】

## 【請求項 1】

ビット線と、ワード線と、ソース線と、共通配線と、第1のトランジスタと、第2のトランジスタと、酸化物半導体をチャネル領域に用いた第3のトランジスタと、キャパシタと、を有し、

前記第1のトランジスタのソースまたはドレインの一方を前記第2のトランジスタのソースまたはドレインの一方と接続し、

前記第1のトランジスタのゲートを前記第3のトランジスタのソースまたはドレインの一方、および前記キャパシタを構成する一対の容量電極の一方と接続し、

前記第1のトランジスタのソースまたはドレインの他方、および前記第3のトランジスタのソースまたはドレインの他方を前記ビット線と接続し、

前記第3のトランジスタのゲートを前記ワード線と接続し、

前記第2のトランジスタのゲート、およびソースまたはドレインの他方を前記ソース線と接続し、

前記キャパシタを構成する前記一対の容量電極の他方を前記共通配線と接続し、

前記共通配線は接地し、

前記共通配線は上面から見て網状であり、前記共通配線が形成する網の目に前記第3のトランジスタが設けられ、

前記第3のトランジスタは、ソース電極およびドレイン電極と、少なくとも前記ソース電極および前記ドレイン電極の上面と接する酸化物半導体膜と、前記酸化物半導体膜上に

10

20

設けられたゲート絶縁膜と、前記ゲート絶縁膜を介して前記酸化物半導体膜と重畳するゲート電極と、前記ソース電極、前記ドレイン電極、前記酸化物半導体膜、前記ゲート絶縁膜および前記ゲート電極を覆って設けられた絶縁膜と、を有し、

前記キャパシタは、前記ドレイン電極および前記共通配線を一対の容量電極とし、少なくとも前記絶縁膜を誘電体膜とすることを特徴とする半導体記憶装置。

【請求項2】

請求項1において、

前記ソース電極および前記ドレイン電極間の空間を埋める絶縁膜が設けられることを特徴とする半導体記憶装置。

【請求項3】

10

請求項2において、

前記ゲート絶縁膜、または前記ソース電極および前記ドレイン電極間の空間を埋める前記絶縁膜が加熱処理により酸素を放出する絶縁膜であることを特徴とする半導体記憶装置。

【請求項4】

請求項3において、

前記絶縁膜は、温度が250以上450以下の範囲における酸素の拡散係数が、前記ゲート絶縁膜、または前記ソース電極および前記ドレイン電極間の空間を埋める前記絶縁膜と比べて小さいことを特徴とする半導体記憶装置。

【発明の詳細な説明】

20

【技術分野】

【0001】

トランジスタなどの半導体素子を含む回路を有する半導体記憶装置に関する。

【背景技術】

【0002】

半導体記憶装置は、電力の供給がなくなると記憶内容が失われる揮発性のものと、電力の供給がなくなっても記憶内容は保持される不揮発性のものとに大別される。

【0003】

揮発性の半導体記憶装置の代表的な例としては、DRAM (Dynamic Random Access Memory) がある。DRAMは、半導体記憶装置を構成するトランジスタを選択し、該トランジスタと接続するキャパシタに電荷を蓄積することで、情報を記憶する。

【0004】

DRAMでは、情報を読み出すと同時にキャパシタの電荷が失われるため、情報の読み出しの度に再度の書き込みが必要となる。また、DRAMを構成するトランジスタがオフ状態のとき、ソースおよびドレイン間のリーク電流（オフ電流）などによって電荷が失われるため、データの保持期間が短い。このため、所定の周期で書き込み動作（リフレッシュ動作）が必要となり、消費電力が増大してしまう。また、電力の供給がなくなるとデータが失われるため、長期間のデータの保持には、例えば磁性材料や光学材料を利用した別の記憶装置が必要となる。

30

【0005】

揮発性の半導体記憶装置の別の例としてはSRAM (Static Random Access Memory) がある。SRAMは、フリップフロップなどの回路を用いて記憶内容を保持するため、リフレッシュ動作が不要であり、この点においてはDRAMより有利である。しかし、フリップフロップなどの回路を用いているため、記憶容量あたりの単価が高くなるという問題がある。また、電力の供給がなくなると記憶内容が失われるという点については、DRAMと同様である。

【0006】

不揮発性の半導体記憶装置の代表例としては、フラッシュメモリがある。フラッシュメモリは、トランジスタのゲート電極とチャネル形成領域との間にフローティングゲートを有

40

50

し、当該フローティングゲートに電荷を保持させることで記憶を行うため、データの保持期間は極めて長く、揮発性の半導体記憶装置で必要なリフレッシュ動作が不要であるという利点を有している（特許文献1参照。）。

#### 【0007】

しかし、書き込みの際に生じるトンネル電流によって半導体記憶装置を構成するゲート絶縁膜が劣化するため、所定回数の書き込みによって半導体記憶装置が機能しなくなるという問題が生じる。この問題の影響を緩和するために、例えば、各半導体記憶装置の書き込み回数を均一化する手法が採られるが、これを実現するためには複雑な周辺回路が必要になってしまう。そして、このような手法を採用しても、根本的な寿命の問題が解消するわけではない。つまり、フラッシュメモリは、情報の書き換え頻度が高い用途の半導体記憶装置には向きである。

10

#### 【0008】

また、フローティングゲートに電荷を保持させるため、または電荷を除去するために高い電圧が必要となる。また、そのための回路も必要である。さらに、電荷の保持または除去のためには比較的長い時間を要し、書き込み、消去の高速化が容易ではないという問題もある。

#### 【先行技術文献】

##### 【特許文献】

##### 【0009】

##### 【特許文献1】特開昭57-105889号公報

20

##### 【発明の概要】

##### 【発明が解決しようとする課題】

##### 【0010】

電力の供給がない状況でもデータの保持が可能かつ、書き込み回数にも制限がない、新たな構造の半導体記憶装置を提供することを目的の一つとする。

##### 【0011】

さらに、上述の新たな構造の半導体記憶装置の集積度を高め、単位面積あたりの記憶容量を増加させることを目的の一つとする。

##### 【0012】

また、半導体記憶装置の有する個々のメモリセルの静電破壊を防止し、半導体記憶装置の歩留まりを向上させることを目的の一つとする。

30

##### 【課題を解決するための手段】

##### 【0013】

本発明の一態様である半導体記憶装置は、ビット線と、ワード線と、ソース線と、共通配線と、第1のトランジスタと、第2のトランジスタと、酸化物半導体を用いた第3のトランジスタと、キャパシタと、を有し、第1のトランジスタのソースまたはドレインの一方が第2のトランジスタのソースまたはドレインの一方と接続し、第1のトランジスタのゲートが第3のトランジスタのソースまたはドレインの一方、およびキャパシタを構成する一対の容量電極の一方と接続し、第1のトランジスタのソースまたはドレインの他方および第3のトランジスタのソースまたはドレインの他方がビット線と接続し、第3のトランジスタのゲートがワード線と接続し、第2のトランジスタのゲートおよびソースまたはドレインの他方がソース線と接続し、キャパシタを構成する一対の容量電極の他方が共通配線と接続し、共通配線は接地する（GND）。また、共通配線は上面から見て網状に設けられ、第3のトランジスタはその網の目部分に設けられる。

40

##### 【0014】

「網状」とは、導電膜などが縦、横に交差する形状をいう。また、「網の目」とは、縦、横に交差する形状の隙間をいう。

##### 【0015】

このようにして設けられた半導体記憶装置は、第3のトランジスタによってキャパシタに電荷が充電され、該電荷によって第1のトランジスタのオンオフを制御し、第1のトラン

50

ジスタがオンならデータ1、第1のトランジスタがオフならデータ0としている。後述するが、第3のトランジスタはオフ電流が極めて小さいため、キャパシタに充電された電荷を長期間に渡って保持することができる。

【0016】

第3のトランジスタは、一対の電極と、少なくとも一対の電極の上面と接する酸化物半導体膜と、酸化物半導体膜上に設けられた第1の絶縁膜と、第1の絶縁膜を介して酸化物半導体膜と重畳するゲート電極と、一対の電極、酸化物半導体膜、第1の絶縁膜およびゲート電極を覆って設けられた第2の絶縁膜と、を有する。

【0017】

キャパシタは、第3のトランジスタの一対の電極の一方および共通配線を一対の容量電極とし、少なくとも第2の絶縁膜を誘電体膜とする。したがって、キャパシタは、第3のトランジスタの一対の電極の一方の側面に沿って設けられる。そのため、一対の電極の厚さを調整することでキャパシタの表面積を大きくすることができ、上面から見た単位面積あたりの容量を大きくすることができる。なお、共通配線は網状の導電膜とも呼ぶ。

10

【0018】

なお、「一対の容量電極」とは、キャパシタの容量を形成する一対の電極をいう。また、「誘電体膜」とは、キャパシタの一対の容量電極間にある膜をいい、一対の容量電極間に電圧を印加することで分極が生じる。

【0019】

なお、共通配線が網状に第3のトランジスタを覆って設けられたため、容量電極の他方としての機能だけではなく、ガードリングとしての機能を有することになる。ガードリングとしての機能を有するため、個々のメモリセルの静電破壊を防止することができ、歩留まりが高く、信頼性の高い半導体記憶装置を得ることができる。

20

【0020】

一対の電極は第3のトランジスタのソース電極およびドレイン電極として機能する。また、第1の絶縁膜は第3のトランジスタのゲート絶縁膜として機能する。

【0021】

なお、一対の電極間の空間を埋める第3の絶縁膜を設けても構わない。なお、一対の電極間の空間を埋める第3の絶縁膜を、一対の電極に挟まれる領域に第3の絶縁膜を設けると言い換てもよい。第3の絶縁膜を設けることにより、酸化物半導体膜および第1の絶縁膜が、一対の電極の形成する段差を乗り越えて形成されなくてもよいために酸化物半導体膜および第1の絶縁膜の被覆性が向上し、ゲート電極と一対の電極との間に生じるリーコンデンサー電流を低減することができる。ただし、第3の絶縁膜を設けないからといって、必ずしもゲート電極と一対の電極との間でリーコンデンサー電流が生じるわけではない。酸化物半導体膜および第1の絶縁膜の被覆性は、成膜方法および一対の電極の形状に起因する。例えば、一対の電極がテーパー角を有することにより、一対の電極が形成する段差における酸化物半導体膜および第1の絶縁膜の被覆性が向上することもある。

30

【0022】

なお、第1の絶縁膜および第3の絶縁膜の少なくとも一方が加熱処理により酸素を放出する絶縁膜であると好ましい。

40

【0023】

第1の絶縁膜または第3の絶縁膜から酸化物半導体膜に酸素が供給されることで、酸化物半導体膜と第1の絶縁膜または第3の絶縁膜との界面準位密度を低減できる。この結果、トランジスタの動作などに起因して、酸化物半導体膜と第1の絶縁膜または第3の絶縁膜との界面にキャリアが捕獲されることを抑制することができ、電気特性の劣化の少ないトランジスタを得ることができる。

【0024】

さらに、酸化物半導体膜の酸素欠損に起因して電荷が生じる場合がある。一般に酸化物半導体膜の酸素欠損は、一部がドナーとなりキャリアである電子を放出する。この結果、トランジスタのしきい値電圧がマイナス方向にシフトしてしまう。第1の絶縁膜または第3

50

の絶縁膜から酸化物半導体膜に酸素が十分に供給されることにより、しきい値電圧がマイナス方向へシフトする要因である、酸化物半導体膜の酸素欠損を低減することができる。

【0025】

第1の絶縁膜および第3の絶縁膜の少なくともいずれかに加熱処理により酸素を放出する絶縁膜を用いる場合、第2の絶縁膜として放出された酸素が透過しない（第1の絶縁膜、第3の絶縁膜よりも酸素の拡散係数が小さい）絶縁膜を用いると好ましい。第2の絶縁膜が上記のような性質を有することにより、第1の絶縁膜、第3の絶縁膜から放出された酸素の半導体記憶装置から外方拡散していく量を低減することができる。ただし、本発明の一態様は、加熱処理により酸素を放出する絶縁膜の側面が網状の導電膜に囲まれているため、網状の導電膜が酸素を透過しない場合、第2の絶縁膜を設けない構成としても構わない。

10

【0026】

酸化物半導体膜として、バンドギャップが2.5eV以上、好ましくは3.0eV以上の材料を選択すればよい。バンドギャップを前述の範囲とすることによって、トランジスタのオフ電流を小さくすることができる。なお、本発明の一態様を、バンドギャップが前述の範囲に入り、かつ半導体特性を示す酸化物半導体ではない材料に置き換えて適用しても構わない。

【0027】

また、酸化物半導体膜は、間接的または直接的にキャリアを生成する不純物（水素、アルカリ金属、アルカリ土類金属、希ガス、窒素、リンおよびホウ素など）が極少なくなるよう高純度化されていると好ましい。さらに、酸素欠損を極力低減することが好ましい。酸化物半導体膜中の不純物および酸素欠損を低減することによって、酸化物半導体膜中におけるキャリアの生成が低減され、トランジスタのオフ電流を小さくすることができる。

20

【0028】

このように、第3のトランジスタのオフ電流を小さくすることで、キャパシタに蓄積される電荷の長期間に渡って保持することができ、不揮発性の半導体記憶装置が得られる。

【発明の効果】

【0029】

キャパシタの電位を制御するトランジスタのオフ電流を小さくすることで、キャパシタに蓄積される電荷を長期間に渡って保持することができ、不揮発性の半導体記憶装置を提供する。

30

【0030】

また、キャパシタを第3のトランジスタの一対の電極の一方の側面に沿って設けることで、キャパシタの占有面積を増大させずキャパシタの容量を増大することができ、集積度の高い半導体記憶装置が提供できる。

【0031】

また、網状の導電膜によって、個々のメモリセルの静電破壊を防止でき、歩留まりが高く、信頼性の高い半導体記憶装置を提供できる。

【図面の簡単な説明】

【0032】

40

【図1】本発明の一態様に係る半導体記憶装置の例を示す上面図および断面図。

【図2】本発明の一態様に係る半導体記憶装置の例を示す回路図。

【図3】図1に示す半導体記憶装置の作製方法の例を示す断面図。

【図4】図1に示す半導体記憶装置の作製方法の例を示す断面図。

【図5】本発明の一態様に係る半導体記憶装置の図1とは異なる例を示す断面図。

【図6】本発明の一態様に係るCPUの具体例を示すブロック図およびその一部の回路図。

【図7】本発明の一態様に係る電子機器の例を示す斜視図。

【発明を実施するための形態】

【0033】

50

以下では、本発明の実施の形態について図面を用いて詳細に説明する。ただし、本発明は以下の説明に限定されず、その形態および詳細を様々に変更し得ることは、当業者であれば容易に理解される。また、本発明は以下に示す実施の形態の記載内容に限定して解釈されるものではない。なお、図面を用いて発明の構成を説明するにあたり、同じものを指す符号は異なる図面間でも共通して用いる。なお、同様のものを指す際にはハッチパターンを同じくし、特に符号を付さない場合がある。

【0034】

以下、本発明の説明を行うが、本明細書で用いる用語について簡単に説明する。まず、トランジスタのソースとドレインについては、本明細書においては、一方をドレインと呼ぶとき他方をソースとする。すなわち、電位の高低によって、それらを区別しない。従って、本明細書において、ソースとされている部分をドレインと読み替えることもできる。

10

【0035】

また、電圧は、ある電位と基準の電位（例えばグラウンド電位）との電位差のことを示す場合が多い。よって、電圧を電位に置き換えることができる。また、電位VH、電位VD、電位GNDなどのように電位を表記したとしても、厳密に電位VH、電位VDD、電位GNDとなっていことがある。よって、電位VH、電位VDD、電位GNDは、電位VH近傍、電位VDD近傍、電位GND近傍と置き換えることができる。なお、「接続する」と「GNDに接続する」は同義である。

【0036】

本明細書においては、「接続する」と表現される場合であっても、現実の回路においては、物理的な接続部分がなく、配線が延在している場合だけのこともある。

20

【0037】

なお、第1、第2として付される序数詞は便宜上用いるものであり、工程順または積層順を示すものではない。また、本明細書において発明を特定するための事項として固有の名称を示すものではない。

【0038】

なお、本明細書では、マトリクスにおいて特定の行や列、位置を扱う場合には、符号に座標を示す記号をつけて、例えば、「メモリセルMC\_n\_m」、「ピット線BL\_m」というように表記するが、特に、行や列、位置を特定しない場合や集合的に扱う場合、またはどの位置にあるか明らかである場合には、「メモリセルMC」、「ピット線BL」、または、単に「メモリセル」、「ピット線」というように表記することもある。

30

【0039】

（実施の形態1）

本実施の形態では、本発明の一態様を適用した半導体記憶装置について説明する。

【0040】

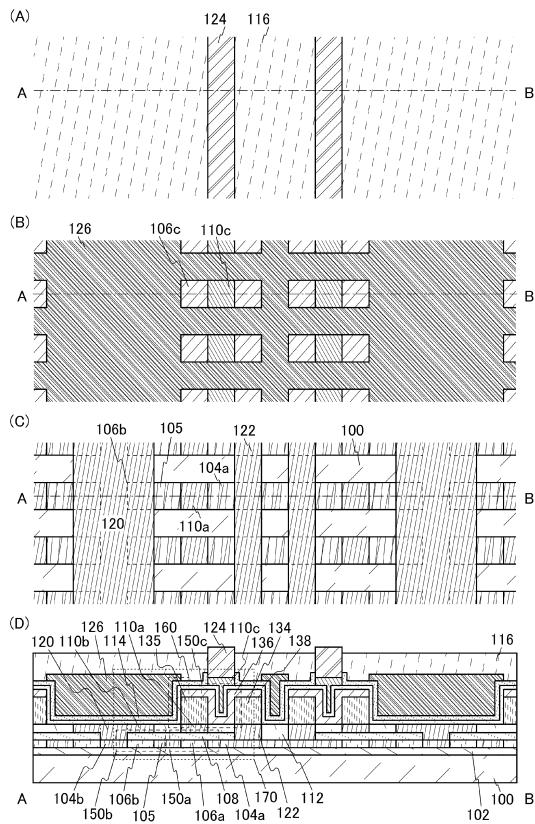

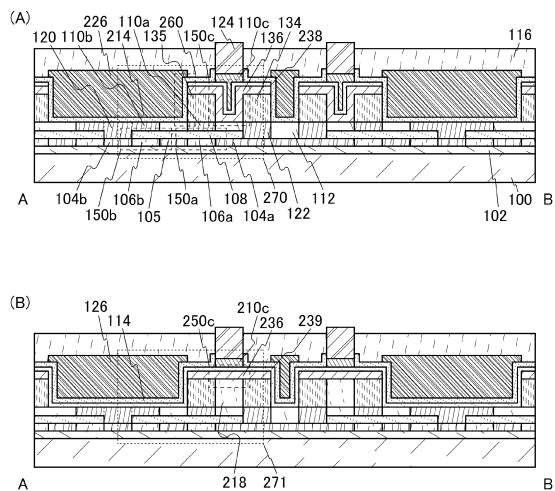

図1(A)乃至図1(C)は半導体記憶装置であるメモリセルアレイの一部を切り取った各階層における上面図である。図1(A)乃至図1(C)における一点鎖線A-Bに対応する断面A-Bを図1(D)に示す。なお、上面側の層が図1(A)であり、基板100側の層が図1(C)である。また、図1(B)は、図1(A)と図1(C)との間の層である。上面図では簡単のため一部の膜（例えば第1の絶縁膜102、第2の絶縁膜108、第3の絶縁膜112、第4の絶縁膜138および第5の絶縁膜114など）を省略して示す。

40

【0041】

図1(D)に示す断面A-Bについて説明する。

【0042】

図1(D)に示すメモリセルアレイはメモリセル170およびメモリセル170と同様のメモリセルを有する。メモリセル170は、基板100と、基板100上に設けられた第1の絶縁膜102と、第1の絶縁膜102上に設けられた、低抵抗領域104a、低抵抗領域104b、低抵抗領域105、チャネル形成領域106aおよびチャネル形成領域106bを含む半導体膜と、該半導体膜上に設けられた、低抵抗領域104aおよび低抵抗

50

領域 104b を露出する開口部の設けられた第 2 の絶縁膜 108 と、第 2 の絶縁膜 108 上に設けられた、ゲート電極 110a、ゲート電極 110b および第 3 の絶縁膜 112 と、ゲート電極 110a およびゲート電極 110b と同一層かつ同一材料で形成され、低抵抗領域 104a と接するピット線 122 と、ゲート電極 110a 上に設けられたドレイン電極 135 と、ピット線 122 上に設けられたソース電極 134 と、少なくともソース電極 134 およびドレイン電極 135 の上面と接する酸化物半導体膜 136 と、ゲート電極 110b、ソース電極 134、ドレイン電極 135 および酸化物半導体膜 136 を覆って設けられた第 4 の絶縁膜 138 と、第 4 の絶縁膜 138 を介して酸化物半導体膜 136 と重畳するゲート電極 110c と、ゲート電極 110c を露出する開口部を有し、第 4 の絶縁膜 138 を覆って設けられた第 5 の絶縁膜 114 と、第 5 の絶縁膜 114 上に設けられ、ゲート電極 110c と重畳しない網状の導電膜 126 と、ゲート電極 110c を露出する開口部を有し、第 5 の絶縁膜 114 および網状の導電膜 126 を覆って設けられた第 6 の絶縁膜 116 と、ゲート電極 110c と接し、第 6 の絶縁膜 116 上に設けられたワード線 124 と、を有する。

10

## 【0043】

図 1 (D) に示すメモリセル 170 は、ソース線 120、ピット線 122、ワード線 124、第 1 のトランジスタ 150a、第 2 のトランジスタ 150b、第 3 のトランジスタ 150c およびキャパシタ 160 を有する。

## 【0044】

低抵抗領域 105 は、第 1 のトランジスタ 150a のドレイン領域および第 2 のトランジスタ 150b のドレイン領域となる。

20

## 【0045】

チャネル形成領域 106a およびチャネル形成領域 106b は、それぞれ第 1 のトランジスタ 150a および第 2 のトランジスタ 150b のチャネルとなる。

## 【0046】

低抵抗領域 104a および低抵抗領域 104b は、それぞれ第 1 のトランジスタ 150a のソース領域および第 2 のトランジスタ 150b のソース領域となる。

## 【0047】

ピット線 122 は、第 1 のトランジスタ 150a のソース領域および第 3 のトランジスタ 150c のソース電極 134 と接続する。

30

## 【0048】

第 2 の絶縁膜 108 は、第 1 のトランジスタ 150a のゲート絶縁膜および第 2 のトランジスタ 150b のゲート絶縁膜となる。

## 【0049】

ソース線 120 は、第 2 のトランジスタ 150b におけるゲート電極 110b およびソース領域（低抵抗領域 104b）と接続している。なお、図におけるソース線 120 およびゲート電極 110b の間の破線は、便宜上示しているだけであり、ソース線 120 およびゲート電極 110b を形成する層は同じもので構わない。

## 【0050】

第 4 の絶縁膜 138 は、第 3 のトランジスタ 150c のゲート絶縁膜となる。

40

## 【0051】

第 4 の絶縁膜 138 および第 5 の絶縁膜 114 は、キャパシタ 160 の誘電体膜となる。

## 【0052】

網状の導電膜 126 および第 3 のトランジスタ 150c のドレイン電極 135 は、キャパシタ 160 を構成する一対の容量電極となる。網状の導電膜 126 は、図 1 (B) に示すように網状に設けられる。そのため、第 3 のトランジスタ 150c のドレイン電極 135 の 3 側面と対向しており、単に 1 側面と対向するだけのキャパシタと比較して容量を大きくすることができる。また、ドレイン電極 135 の側面の面積は、ドレイン電極 135 を厚くすることで大きくすることができる。ドレイン電極 135 を厚く設けても、キャパシタ 160 の面積は変わらないため、キャパシタの占有面積は増大させず、キャパシタの容

50

量を増大することができ、メモリセル 170 を複数組み合わせたメモリセルアレイの集積度の高めることができる。

【0053】

第1のトランジスタ 150a のゲート電極 110a は、第3のトランジスタ 150c のドレイン電極 135 と接続する。

【0054】

網状の導電膜 126 は共通配線としての機能を有し、GND に接続される。また、その形状から個々のメモリセルが静電破壊することを防止するガードリングとしての機能を有する。

【0055】

図 1 (D) では、簡略化のため各層はテーパー角を有さない形状にて示しているが、これに限定されるものではない。各層はテーパー角を有していても構わない。

10

【0056】

なお、本明細書において、「A は B を覆って設けられた」とは、A が B の側面および上面を覆う形状を有することをいう。また、A と B との間に、A および B とは異なる C がある場合についても、「A は B を覆って設けられた」と表記する。なお、C は単層とは限らず、積層であっても構わない。

【0057】

また、本明細書において、「A 上に設けられた B」とは、少なくとも、A の上面と一部が接して B が設けられることをいう。同様に、「A と重畳する B」とは、上面図において A に対して B の一部または全部が重なって設けられることをいう。

20

【0058】

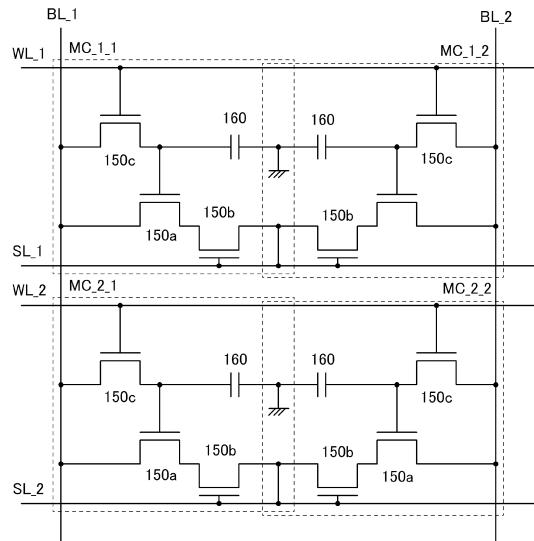

次に、メモリセルアレイの回路構成について図 2 を用いて説明する。

【0059】

メモリセルアレイは、メモリセル MC (メモリセル 170 に対応) がマトリクス状に配置され、ワード線 WL (ワード線 124 に対応)、ビット線 BL (ビット線 122 に対応) およびソース線 SL (ソース線 120 に対応) に電位を印加することで動作する。

【0060】

メモリセル MC は、ビット線 BL と第1のトランジスタ 150a のソースと第3のトランジスタ 150c のソースとが接続しており、ワード線 WL と第3のトランジスタ 150c のゲートとが接続しており、ソース線 SL と第2のトランジスタ 150b のゲートおよびソースとが接続しており、第1のトランジスタ 150a のドレインと第2のトランジスタ 150b のドレインとが接続しており、第1のトランジスタ 150a のゲートと第3のトランジスタ 150c のドレインとキャパシタ 160 の一対の容量電極の一方とが接続しており、キャパシタ 160 を構成する一対の容量電極の他方と GND とが接続している。

30

【0061】

メモリセル MC\_1\_1 およびメモリセル MC\_1\_2 は、ビット線 BL\_1 を共有しており、メモリセル MC\_1\_1 およびメモリセル MC\_1\_2 は、ワード線 WL\_1 およびソース線 SL\_1 を共有している。即ち、各列でビット線 BL を、各行でワード線 WL およびソース線 SL を共有している。また、メモリセル MC\_1\_1 およびメモリセル MC\_1\_2 の第2のトランジスタ 150b のソース同士は接続している。

40

【0062】

ここで、図 1 (D) に示すメモリセル 170 およびメモリセル 170 と同様のメモリセルは、例えば、図 2 におけるメモリセル MC\_1\_1 およびメモリセル MC\_1\_2 に対応する。

【0063】

次に、メモリセルアレイへのデータの書き込み方法を示す。

【0064】

データの書き込みは行ごとに行う。ここでは、メモリセル MC\_1\_1 およびメモリセル MC\_1\_2 からデータを書き込む。

50

## 【0065】

まず、ワード線WL\_1を電位VH (VDDよりも第3のトランジスタ150cのしきい値電圧(Vth)以上高い電位)とし、ワード線WL\_2、ソース線SL\_1およびソース線SL\_2を電位GNDとする。次に、データ1を書き込むメモリセルMCがある列に対応するビット線BLを電位VDDとし、データ0を書き込むメモリセルMCがある列に対応するビット線BLを電位GNDとする。このようにすることで、データ1を書き込むメモリセルMCのキャパシタ160の電位はVDDとなり、データ0を書き込むメモリセルMCのキャパシタ160の電位はGNDとなる。

## 【0066】

次に、行を移動して、同様の方法でメモリセルMC\_2\_1およびメモリセルMC\_2\_2にデータを書き込む。 10

## 【0067】

以上のような方法で、メモリセルアレイにデータを書き込むことができる。

## 【0068】

次に、メモリセルアレイに書き込んだデータの保持方法を示す。

## 【0069】

書き込んだデータの保持は、ワード線WL\_1、ワード線WL\_2、ビット線BL\_1、ビット線BL\_2、ソース線SL\_1およびソース線SL\_2を浮遊電位(フロートともいう。)とする。または、ワード線WL\_1、ワード線WL\_2、ビット線BL\_1、ビット線BL\_2、ソース線SL\_1およびソース線SL\_2をGND(またはGND以下)とする。 20

## 【0070】

以上のような方法で、メモリセルアレイに書き込んだデータを保持することができる。

## 【0071】

次に、メモリセルアレイに保持されたデータを読み出す方法を示す。

## 【0072】

保持されたデータの読み出しは行ごとに行う。ここでは、メモリセルMC\_1\_1およびメモリセルMC\_1\_2からデータを読み出す。

## 【0073】

まず、ソース線SL\_1を電位VDDとし、ソース線SL\_2、ワード線WL\_1およびワード線WL\_2を電位GNDとする。こうすることで、第2のトランジスタ150bがオンする。なお、図示しないが、ビット線BL\_1およびビット線BL\_2は、プルダウン回路と接続する。プルダウン回路と接続することによって、ビット線BLに何も接続していないとき、ビット線BLを電位GNDに固定することができる。即ち、メモリセルMCがデータ1を保持しているとき、第1のトランジスタ150aがオンし、ビット線BLが電位VDDとなる。または、メモリセルMCがデータ0を保持しているとき、第1のトランジスタ150aがオフしているため、ビット線BLは電位GNDとなる。こうしてビット線BLの電位によってデータを読み出すことができる。 30

## 【0074】

次に、行を移動して、同様の方法でメモリセルMC\_2\_1およびメモリセルMC\_2\_2にデータを読み出す。 40

## 【0075】

以上のような方法で、メモリセルアレイに保持されたデータを読み出すことができる。

## 【0076】

酸化物半導体膜136は、厚さが1nm以上40nm以下とする。好ましくは、5nm以上15nm以下とする。特に、チャネル長が30nm以下のトランジスタでは、酸化物半導体膜136の厚さを5nm程度とすることで、短チャネル効果を抑制でき、安定な電気的特性を有することができる。

## 【0077】

酸化物半導体膜136として、例えば、In-Sn-Ga-Zn-O系の材料や、In- 50

Ga-Zn-O系の材料、In-Sn-Zn-O系の材料、In-Al-Zn-O系の材料、Sn-Ga-Zn-O系の材料、Al-Ga-Zn-O系の材料、Sn-Al-Zn-O系の材料や、In-Zn-O系の材料、Sn-Zn-O系の材料、Al-Zn-O系の材料、Zn-Mg-O系の材料、Sn-Mg-O系の材料、In-Mg-O系の材料、In-Ga-O系の材料や、In-O系の材料、Sn-O系の材料、Zn-O系の材料などを用いればよい。ここで、例えば、In-Ga-Zn-O系の材料は、インジウム(In)、ガリウム(Ga)、亜鉛(Zn)を有する酸化物、という意味であり、その組成比は特に問わない。また、InとGaとZn以外の元素を含んでいてもよい。

#### 【0078】

酸化物半導体膜136としてIn-Zn-O系の材料を用いる場合、原子数比で、In/Zn=0.5以上50以下、好ましくはIn/Zn=1以上20以下、さらに好ましくはIn/Zn=1.5以上15以下とする。Znの原子数比を前述の範囲とすることで、トランジスタの電界効果移動度を向上させることができる。ここで、化合物の原子数比がIn:Zn:O=X:Y:Zのとき、Z>1.5X+Yとすると好ましい。

10

#### 【0079】

酸化物半導体膜136として、化学式 $InMO_3(ZnO)_m$ ( $m > 0$ )で表記される材料を用いてもよい。ここで、Mは、Ga、Al、MnおよびCoから選ばれた一または複数の金属元素を示す。例えば、Mとして、Ga、GaおよびAl、GaおよびMnまたはGaおよびCoなどを用いてもよい。

#### 【0080】

酸化物半導体膜136は、トランジスタのオフ電流を低減するため、バンドギャップが2.5eV以上、好ましくは3.0eV以上の材料を選択する。ただし、酸化物半導体膜に代えて、バンドギャップが前述の範囲である半導体性を示す材料を用いても構わない。

20

#### 【0081】

酸化物半導体膜136は、水素、アルカリ金属およびアルカリ土類金属などが低減され、極めて不純物濃度の低い酸化物半導体膜である。そのため、酸化物半導体膜136をチャネル領域に用いたトランジスタはオフ電流を小さくできる。

#### 【0082】

酸化物半導体膜136中の水素濃度は、 $5 \times 10^{19} \text{ cm}^{-3}$ 未満、好ましくは $5 \times 10^{18} \text{ cm}^{-3}$ 以下、より好ましくは $1 \times 10^{18} \text{ cm}^{-3}$ 以下、さらに好ましくは $5 \times 10^{17} \text{ cm}^{-3}$ 以下とする。

30

#### 【0083】

アルカリ金属は酸化物半導体を構成する元素ではないため、不純物である。アルカリ土類金属も、酸化物半導体を構成する元素ではない場合において、不純物となる。特に、アルカリ金属のうちナトリウム(Na)は、絶縁膜中に拡散して $Na^+$ となる。また、Naは、酸化物半導体膜内において、酸化物半導体を構成する金属と酸素の結合を分断する、または、その結合中に割り込む。その結果、例えば、しきい値電圧がマイナス方向にシフトすることによるノーマリオン化、電界効果移動度の低下などの、トランジスタ特性の劣化が起こり、加えて、特性のばらつきも生じる。この不純物によりもたらされるトランジスタ特性の劣化と、特性のばらつきは、酸化物半導体膜中の水素濃度が十分に低い場合において顕著に現れる。従って、酸化物半導体膜中の水素濃度が $1 \times 10^{18} \text{ cm}^{-3}$ 以下、より好ましくは $1 \times 10^{17} \text{ cm}^{-3}$ 以下である場合には、上記不純物の濃度を低減することが望ましい。具体的に、Na濃度の測定値は、 $5 \times 10^{16} \text{ cm}^{-3}$ 以下、好ましくは $1 \times 10^{16} \text{ cm}^{-3}$ 以下、更に好ましくは $1 \times 10^{15} \text{ cm}^{-3}$ 以下とするとよい。同様に、リチウム(Li)濃度の測定値は、 $5 \times 10^{15} \text{ cm}^{-3}$ 以下、好ましくは $1 \times 10^{15} \text{ cm}^{-3}$ 以下とするとよい。同様に、カリウム(K)濃度の測定値は、 $5 \times 10^{15} \text{ cm}^{-3}$ 以下、好ましくは $1 \times 10^{15} \text{ cm}^{-3}$ 以下とするとよい。

40

#### 【0084】

以上に示した酸化物半導体膜136を用いることでトランジスタのオフ電流を小さくできる。例えば、チャネル長が3μm、チャネル幅が1μmのときのトランジスタのオフ電流

50

を  $1 \times 10^{-18}$  Å 以下、または  $1 \times 10^{-21}$  Å 以下、または  $1 \times 10^{-24}$  Å 以下とすることができる。そのため、データの保持特性に優れ、消費電力の小さい半導体記憶装置を作製することができる。

【0085】

酸化物半導体膜 136 として、単結晶、多結晶（ポリクリスタルともいう。）または非晶質などの状態をとる。

【0086】

好ましくは、酸化物半導体膜 136 は、 C AAC - OS ( C Axis Aligned Crystalline Oxide Semiconductor ) 膜とする。

【0087】

C AAC - OS 膜は、完全な単結晶ではなく、完全な非晶質でもない。C AAC - OS 膜は、非晶質相に結晶部および非晶質部を有する結晶 - 非晶質混相構造の酸化物半導体膜である。なお、当該結晶部は、一辺が 100 nm 未満の立方体内に収まる大きさであることが多い。また、透過型電子顕微鏡（TEM: Transmission Electron Microscope）による観察像では、C AAC - OS 膜に含まれる非晶質部と結晶部との境界は明確ではない。また、TEM によって C AAC - OS 膜には粒界（グレインバウンダリーともいう。）は確認できない。そのため、C AAC - OS 膜は、粒界に起因する電子移動度の低下が抑制される。

【0088】

C AAC - OS 膜に含まれる結晶部は、c 軸が C AAC - OS 膜の被形成面の法線ベクトルまたは上面の法線ベクトルに平行な方向に揃い、かつ a b 面に垂直な方向から見て三角形状または六角形状の原子配列を有し、c 軸に垂直な方向から見て金属原子が層状または金属原子と酸素原子とが層状に配列している。なお、異なる結晶部間で、それぞれ a 軸および b 軸の向きが異なっていてもよい。本明細書において、単に垂直と記載する場合、85° 以上 95° 以下の範囲も含まれることとする。また、単に平行と記載する場合、-5° 以上 5° 以下の範囲も含まれることとする。

【0089】

なお、C AAC - OS 膜において、結晶部の分布が一様でなくてもよい。例えば、C AAC - OS 膜の形成過程において、酸化物半導体膜の上面側から結晶成長させる場合、被形成面の近傍に対し上面の近傍では結晶部の占める割合が高くなることがある。また、C AAC - OS 膜へ不純物を添加することにより、当該不純物添加領域において結晶部が非晶質化することもある。

【0090】

C AAC - OS 膜に含まれる結晶部の c 軸は、C AAC - OS 膜の被形成面の法線ベクトルまたは上面の法線ベクトルに平行な方向に揃うため、C AAC - OS 膜の形状（被形成面の断面形状または上面の断面形状）によっては互いに異なる方向を向くことがある。なお、結晶部の c 軸の方向は、C AAC - OS 膜が形成されたときの被形成面の法線ベクトルまたは上面の法線ベクトルに平行な方向となる。結晶部は、成膜することにより、または成膜後に加熱処理などの結晶化処理を行うことにより形成される。

【0091】

C AAC - OS 膜を用いたトランジスタは、可視光や紫外光の照射による電気特性の変動を低減することが可能である。よって、当該トランジスタは、信頼性が高い。

【0092】

C AAC - OS 膜は、下地となる膜が平坦であると形成されやすい。具体的には、平均面粗さ（Ra）が 1 nm 以下、好ましくは 0.3 nm 以下となるように下地となる膜を設ける。なお、Ra は、JIS B 0601 で定義されている中心線平均粗さを面に対して適用できるよう三次元に拡張したものであり、「基準面から指定面までの偏差の絶対値を平均した値」と表現でき、数式（1）にて定義される。

【0093】

10

20

30

40

## 【数1】

$$Ra = \frac{1}{S_0} \int_{y1}^{y2} \int_{x1}^{x2} |f(x, y) - Z_0| dx dy \quad (1)$$

## 【0094】

なお、数式1において、 $S_0$ は、測定面（座標 $(x_1, y_1)$   $(x_1, y_2)$   $(x_2, y_1)$   $(x_2, y_2)$ ）で表される4点によって囲まれる長方形の領域）の面積を指し、 $Z_0$ は測定面の平均高さを指す。Raは原子間力顕微鏡（AFM: Atomic Force Microscope）にて評価可能である。10

## 【0095】

基板100に大きな制限はないが、少なくとも、後の熱処理に耐えうる程度の耐熱性を有している必要がある。例えば、ガラス基板、セラミック基板、石英基板、サファイア基板などを、基板100として用いてもよい。また、シリコンや炭化シリコンなどの単結晶半導体基板、多結晶半導体基板、シリコンゲルマニウムなどの化合物半導体基板、SOI（Silicon On Insulator）基板などを適用することも可能であり、これらの基板上に半導体素子が設けられたものを、基板100として用いると好ましい。20

## 【0096】

また、基板100として、可とう性基板を用いてもよい。その場合は、可とう性基板上に直接的にトランジスタを作製する。なお、可とう性基板上にトランジスタを設ける方法としては、非可とう性の基板上にトランジスタを作製した後、トランジスタを剥離し、可とう性基板である基板100に転置する方法もある。その場合には、非可とう性基板とトランジスタとの間に剥離層を設けるとよい。20

## 【0097】

第1の絶縁膜102は、酸化シリコン、酸化窒化シリコン、窒化酸化シリコン、窒化シリコン、酸化アルミニウム、窒化アルミニウム、酸化ハフニウム、酸化ジルコニウム、酸化イットリウム、酸化ランタン、酸化タンタルおよび酸化マグネシウムの一種以上を選択して、単層または積層で用いればよい。30

## 【0098】

低抵抗領域104a、低抵抗領域104b、低抵抗領域105、チャネル形成領域106aおよびチャネル形成領域106bを含む半導体膜は、シリコン、ゲルマニウム、ガリウムヒ素、炭化シリコンまたは窒化ガリウムを用いて、非晶質膜、微結晶膜、多結晶膜または単結晶膜で設ければよい。または、酸化物半導体膜136と同様の方法および同様の材料で形成することができる。なお、低抵抗領域104a、低抵抗領域104bおよび低抵抗領域105は、前述の材料からなる半導体膜の一部に対し、抵抗値を低減する作用を有する不純物を選択的に添加することで設ければよい。

## 【0099】

第2の絶縁膜108は、第1の絶縁膜102と同様の方法および同様の材料によって形成すればよい。40

## 【0100】

ゲート電極110a、ゲート電極110b、ソース線120およびビット線122は同一層かつ同一材料であり、例えば、Al、Ti、Cr、Co、Ni、Cu、Y、Zr、Mo、Ag、TaおよびW、それらの窒化物、酸化物ならびに合金から一種以上選択し、単層または積層で設ければよい。

## 【0101】

第3の絶縁膜112は、第1の絶縁膜102と同様の方法および同様の材料によって形成すればよい。なお、第3の絶縁膜112と、ゲート電極110a、ゲート電極110b、ソース線120およびビット線122との上面の高さが概略一致していると、後に形成す50

る第3のトランジスタ150cおよびキャパシタ160が作製しやすくなるため好ましい。

【0102】

ソース電極134およびドレイン電極135は、ゲート電極110a、ゲート電極110b、ソース線120およびビット線122と同様の方法および同様の材料によって形成すればよい。

【0103】

ドレイン電極135は、その3側面に沿ってキャパシタ160が設けられる。そのため、ドレイン電極135の厚さが厚いほど、キャパシタ160の容量は大きくなる。ただし、ドレイン電極135の厚さを厚くしすぎると、後に形成する層の被覆性を低下させてしまうことがある。そのため、ドレイン電極135の幅を1とするとき、ドレイン電極135の厚さは0.5以上10以下、好ましくは1以上4以下とする。

【0104】

第4の絶縁膜138は、第1の絶縁膜102と同様の方法および同様の材料によって形成すればよい。

【0105】

なお、第3の絶縁膜112および第4の絶縁膜138の少なくとも一方は、加熱処理により酸素を放出する絶縁膜を用いると好ましい。加熱処理により酸素を放出する膜を用いることで、酸化物半導体膜136および酸化物半導体膜136の界面近傍に生じる欠陥を修復することができ、トランジスタの電気特性の劣化を抑制できる。

【0106】

「加熱処理により酸素を放出する」とは、TDS (Thermal Desorption Spectroscopy: 昇温脱離ガス分光法) 分析にて、酸素原子に換算しての酸素の放出量が $1.0 \times 10^{18} \text{ cm}^{-3}$ 以上、特に $3.0 \times 10^{20} \text{ cm}^{-3}$ 以上であることをいう。

【0107】

ここで、TDS分析を用いた酸素の放出量の測定方法について、以下に説明する。

【0108】

TDS分析したときの気体の全放出量は、放出ガスのイオン強度の積分値に比例する。そしてこの積分値と標準試料との比較により、気体の全放出量を計算することができる。

【0109】

例えば、標準試料である所定の密度の水素を含むシリコンウェハのTDS分析結果、および絶縁膜のTDS分析結果から、絶縁膜の酸素分子の放出量( $N_{O_2}$ )は、数式(2)で求めることができる。ここで、TDS分析で得られる質量数32で検出されるガスの全てが酸素分子由来と仮定する。質量数32のものとしてほかに $CH_3OH$ があるが、存在する可能性が低いものとしてここでは考慮しない。また、酸素原子の同位体である質量数17の酸素原子および質量数18の酸素原子を含む酸素分子についても、自然界における存在比率が極微量であるため考慮しない。

【0110】

$$N_{O_2} = N_{H_2} / S_{H_2} \times S_{O_2} \times \quad (2)$$

【0111】

$N_{H_2}$ は、標準試料から脱離した水素分子を密度で換算した値である。 $S_{H_2}$ は、標準試料をTDS分析したときのイオン強度の積分値である。ここで、標準試料の基準値を、 $N_{H_2} / S_{H_2}$ とする。 $S_{O_2}$ は、絶縁膜をTDS分析したときのイオン強度の積分値である。は、TDS分析におけるイオン強度に影響する係数である。数式(2)の詳細に関しては、特開平6-275697公報を参照する。なお、上記絶縁膜の酸素の放出量は、電子科学株式会社製の昇温脱離分析装置EMD-WA1000S/Wを用い、標準試料として $1 \times 10^{16} \text{ atoms/cm}^3$ の水素原子を含むシリコンウェハを用いて測定した。

【0112】

10

20

30

40

50

また、TDS分析において、酸素の一部は酸素原子として検出される。酸素分子と酸素原子の比率は、酸素分子のイオン化率から算出することができる。なお、上述の  $N_{O_2}$  は酸素分子のイオン化率を含むため、酸素分子の放出量を評価することで、酸素原子の放出量についても見積もることができる。

【0113】

なお、 $N_{O_2}$  は酸素分子の放出量である。酸素原子に換算したときの放出量は、酸素分子の放出量の2倍となる。

【0114】

上記構成において、加熱処理により酸素を放出する膜は、酸素が過剰な酸化シリコン ( $SiO_x$  ( $X > 2$ ))) であってもよい。酸素が過剰な酸化シリコン ( $SiO_x$  ( $X > 2$ ))) とは、シリコン原子数の2倍より多い酸素原子を単位体積当たりに含むものである。単位体積当たりのシリコン原子数および酸素原子数は、ラザフォード後方散乱法により測定した値である。

10

【0115】

第3の絶縁膜112および第4の絶縁膜138から酸化物半導体膜136に酸素が供給されることで、酸化物半導体膜136と第3の絶縁膜112との界面準位密度、または酸化物半導体膜136と第4の絶縁膜138との界面準位密度を低減できる。この結果、トランジスタの動作などに起因して、酸化物半導体膜136と第3の絶縁膜112との界面、または酸化物半導体膜136と第4の絶縁膜138の界面にキャリアが捕獲されることを抑制することができ、電気特性の劣化の少ないトランジスタを得ることができる。

20

【0116】

さらに、酸化物半導体膜136の酸素欠損に起因して電荷が生じる場合がある。一般に酸化物半導体膜の酸素欠損は、一部がドナーとなりキャリアである電子を放出する。この結果、トランジスタのしきい値電圧がマイナス方向にシフトしてしまう。第3の絶縁膜112および第4の絶縁膜138から酸化物半導体膜136に酸素が十分に供給されることにより、しきい値電圧がマイナス方向へシフトする要因である、酸化物半導体膜の酸素欠損を低減することができる。

【0117】

ゲート電極110cは、ゲート電極110a、ゲート電極110b、ソース線120およびビット線122と同様の方法および同様の材料によって形成すればよい。

30

【0118】

第5の絶縁膜114は、第3の絶縁膜112および第4の絶縁膜138と比べて、温度が250以上450以下の範囲における酸素の拡散係数が小さい材料を用いればよい。このような構成とすることで、第3の絶縁膜112および第4の絶縁膜138から酸素が放出された際、第3のトランジスタ150cの外側に拡散していく酸素の量を低減することができる。

【0119】

なお、第5の絶縁膜114は、第3の絶縁膜112および第4の絶縁膜138の材料として列挙した材料の中から適宜選択することができる。ただし、第3の絶縁膜112および第4の絶縁膜138として選択した材料によりも、温度が250以上450以下の範囲における酸素の拡散係数が小さい材料を用いる。例えば、第3の絶縁膜112および第4の絶縁膜138として、酸化シリコン膜を用いる場合、第5の絶縁膜114として酸化アルミニウム膜を用いればよい。酸化アルミニウム膜は、酸素が透過しにくいだけでなく、水もほとんど透過しない性質を有する。そのため、水がトランジスタ140の外部から浸入することを抑制でき、半導体記憶装置の信頼性を高めることができる。酸化アルミニウム膜は5nm以上200nm以下、好ましくは20nm以上100nm以下で設ければよい。

40

【0120】

網状の導電膜126は、ゲート電極110a、ゲート電極110b、ソース線120およびビット線122と同様の方法および同様の材料によって形成すればよい。

50

## 【0121】

第6の絶縁膜116は、第1の絶縁膜102と同様の方法および同様の材料によって形成してもよい。第6の絶縁膜116は、ポリイミド膜、アクリル膜またはエポキシ膜などの樹脂材料としてもよく、単層または積層で設ける。なお、第6の絶縁膜116の上面は平坦であることが好ましいが、これに限定されない。第6の絶縁膜116の上面に、下地の形状による凹凸が形成されていても構わない。

## 【0122】

ワード線124は、ゲート電極110a、ゲート電極110b、ソース線120およびビット線122と同様の方法および同様の材料によって形成すればよい。ワード線124は、第6の絶縁膜116および第5の絶縁膜114に設けられた開口部を介して、ゲート電極110cと接続される。

10

## 【0123】

以上に示すメモリセル170は、ドレイン電極135の3側面に沿ってキャパシタ160が形成されるため、大きな容量とすることができます。

## 【0124】

また、網状の導電膜126はGNDに接続されており、その形状から個々のメモリセルが静電破壊することを防止するガードリングとしての機能を有する。

## 【0125】

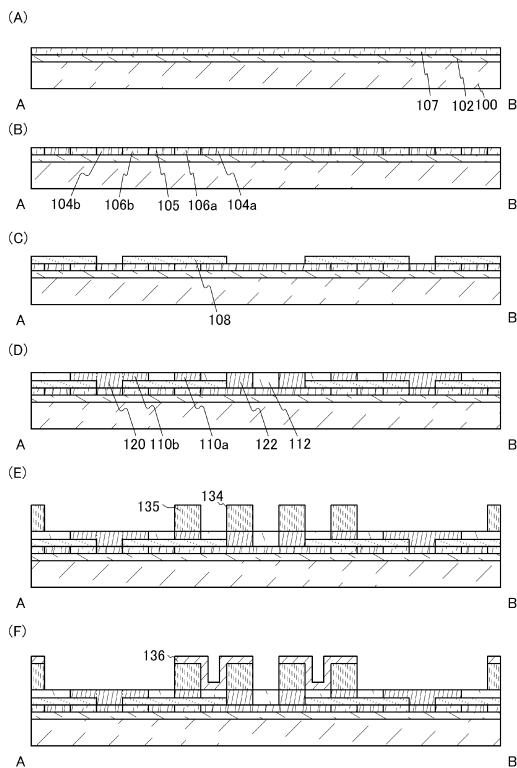

次に、図1に示すメモリセルアレイの作製方法について、図3および図4を用いて説明する。

20

## 【0126】

まず、基板100上に第1の絶縁膜102、半導体膜107をこの順に形成する（図3（A）参照。）。なお、基板100上には、別途半導体素子が設けられていてもよく、第1の絶縁膜102は、この半導体素子を作製する際に設けられても構わない。

## 【0127】

第1の絶縁膜102は、スパッタリング法、蒸着法、プラズマ化学気相成長法（PCVD法）、パルスレーザー堆積法（PLD法）、原子層堆積法（ALD法）または分子線エピタキシー法（MBE法）などを用いて成膜すればよい。なお、第1の絶縁膜102は、基板100の材料によっては熱酸化法を用いて形成しても構わない。

## 【0128】

半導体膜107は、スパッタリング法、蒸着法、PCVD法、PLD法、ALD法またはMBE法などを用いて成膜すればよい。なお、半導体膜107として、基板100にSOI基板のような半導体基板に設けられた半導体膜を適用しても構わない。

30

## 【0129】

次に、半導体膜107上に、フォトリソグラフィ法によってレジストマスクを形成し、該レジストマスクを用いて、半導体膜107の抵抗値を低減する作用を有する不純物を選択的に添加し、低抵抗領域104a、低抵抗領域104bおよび低抵抗領域105を形成する。なお、同時にチャネル形成領域106aおよびチャネル形成領域106bが形成される（図3（B）参照。）。このような作用を有する不純物材料として、半導体膜107がシリコン膜である場合、リン、ホウ素またはヒ素などがある。なお、半導体膜107への不純物の添加は、半導体膜107の形成後に限らず、後述する、第2の絶縁膜108の形成後に第2の絶縁膜108をマスクに添加し、さらにゲート電極110a、ゲート電極110b、ソース線120およびビット線122の形成後にゲート電極110a、ゲート電極110b、ソース線120およびビット線122をマスクに添加しても構わない。第2の絶縁膜108をマスクに半導体膜107への不純物を添加し、またゲート電極110a、ゲート電極110b、ソース線120およびビット線122をマスクに、半導体膜107へ不純物を添加することで、不純物添加のためのフォトリソグラフィ工程を削減できる。

40

## 【0130】

次に、第2の絶縁膜108を成膜し、該絶縁膜上にフォトリソグラフィ法によってレジス

50

トマスクを形成し、該レジストマスクを用いて第2の絶縁膜108に低抵抗領域104aおよび低抵抗領域104bを露出する開口部を形成する(図3(C)参照。)。

【0131】

次に、スパッタリング法、蒸着法、P C V D法、P L D法、A L D法またはM B E法などを用いて導電膜を成膜する。次に、導電膜上にフォトリソグラフィ法によってレジストマスクを形成し、該レジストマスクを用いて導電膜を加工して、ゲート電極110a、ゲート電極110b、ソース線120およびビット線122を形成する。

【0132】

次に、絶縁膜を成膜する。該絶縁膜を、化学機械研磨(C M P : C h e m i c a l M e c h a n i c a l P o l i s h i n g)処理またはエッティング処理することにより、ゲート電極110a、ゲート電極110b、ソース線120およびビット線122を露出させ、第3の絶縁膜112を形成する(図3(D)参照。)。このとき、これらの層が形成する上面が平坦化されると好ましい。

【0133】

次に、導電膜を成膜し、該導電膜を加工してソース電極134およびドレイン電極135を形成する(図3(E)参照。)。

【0134】

次に、スパッタリング法、蒸着法、P C V D法、P L D法、A L D法またはM B E法などを用いて酸化物半導体膜を成膜する。このとき、250以上450以下の温度で加熱処理を行いながら酸化物半導体膜を成膜すると、C A A C - O S膜が形成されやすい。または、酸化物半導体膜の成膜後に450以上基板の歪み点未満の温度、好ましくは600以上700以下の温度で加熱処理を行ってもよい。次に、酸化物半導体膜上にフォトリソグラフィ法によってレジストマスクを形成し、該レジストマスクを用いて酸化物半導体膜を加工して、酸化物半導体膜136を形成する(図3(F)参照。)。

【0135】

酸化物半導体膜をスパッタリング法によって成膜する場合、成膜室の排気は、ドライポンプなどの粗引きポンプと、スパッタイオンポンプ、ターボ分子ポンプおよびクライオポンプなどの高真空ポンプとを適宜組み合わせて行うとよい。ターボ分子ポンプは大きいサイズの分子の排気が優れる一方、水素や水の排気能力が低い。そこで、水の排気能力の高いクライオポンプおよび水素の排気能力の高いスパッタイオンポンプを組み合わせることが有効となる。

【0136】

酸化物半導体膜を成膜する成膜室に存在する吸着物は、吸着しているために成膜室の圧力に影響しないが、成膜室を排気した際のガス放出の原因となる。そのため、排気能力の高いポンプを用いて、成膜室に存在する吸着物をできる限り脱離し、予め排気しておくことが重要である。なお、吸着物の脱離を促すために、成膜室をベーキングしてもよい。ベーキングすることで吸着物の脱離速度を10倍程度大きくすることができる。ベーキングは100以上450以下で行えばよい。このとき、不活性ガスを導入しながら吸着物の除去を行うと、排気するだけでは脱離しにくい水などの脱離速度をさらに大きくすることができる。なお、導入する不活性ガスをベーキングの温度と同程度に加熱することで、吸着物の脱離速度をさらに高めることができる。また、ベーキングと同時にダミー成膜を行うことでも吸着物の脱離速度をさらに高めることができる。ここで、ダミー成膜とは、ダミー基板に対してスパッタリングによる成膜を行うことで、ダミー基板および成膜室内壁に膜を堆積させ、成膜室内の不純物および成膜室内壁の吸着物を膜中に閉じこめることをいう。ダミー基板は、放出ガスの少ない材料が好ましく、例えば基板100と同様の材料を用いてもよい。

【0137】

また、露点が-95以下、好ましくは露点が-110以下の成膜ガスを用いると、酸化物半導体膜中の水素濃度を低減できる。

【0138】

10

20

30

40

50

このようにして酸化物半導体膜を成膜することで、酸化物半導体膜への水素の混入を抑制できる。さらには、同様の成膜室を用いて、酸化物半導体膜と接する膜を成膜することで、酸化物半導体膜に接する膜から酸化物半導体膜へ水素が混入することを抑制できる。この結果、電気特性のばらつきの少ない、信頼性の高いトランジスタを作製することができる。

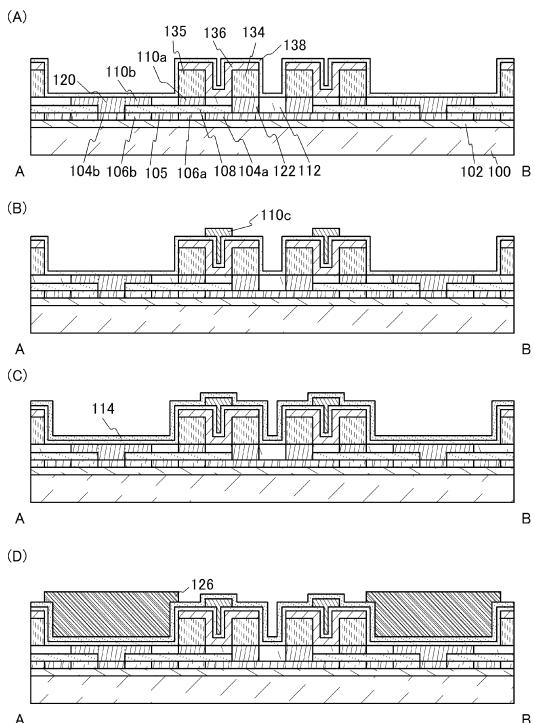

【0139】

次に、第4の絶縁膜138を成膜する(図4(A)参照。)。

【0140】

次に、導電膜を成膜し、該導電膜を加工してゲート電極110cを形成する(図4(B)参照。)。

10

【0141】

次に、第5の絶縁膜114を成膜する(図4(C)参照。)。

【0142】

次に、導電膜を成膜し、該導電膜を加工して網状の導電膜126を形成する(図4(D)参照。)。

【0143】

次に、第6の絶縁膜116を成膜し、第6の絶縁膜116および第5の絶縁膜114にゲート電極110cを露出する開口部を形成する。次に、第6の絶縁膜116上に、第6の絶縁膜116に設けられた開口部を介してゲート電極110cと接続するワード線124を形成する。以上の工程によって図1に示すメモリセルアレイを作製することができる。

20

【0144】

なお、酸化物半導体膜が成膜された後、第4の絶縁膜138が成膜された後、および第5の絶縁膜114が成膜された後の少なくともいずれかのタイミングで加熱処理を行うと好み。加熱処理を行うことによって、第3の絶縁膜112または第4の絶縁膜138より酸素が放出され、酸化物半導体膜(または酸化物半導体膜136)中、または酸化物半導体膜(または酸化物半導体膜136)が形成する界面近傍の酸素欠損を低減することができる。加熱処理は、250以上450以下の温度で行えばよい。なお、同様の加熱処理をメモリセルアレイの作製後に行っても構わない。

【0145】

なお、ソース電極134およびドレイン電極135に対して、逆スパッタリング処理などのプラズマ処理を行っても構わない。このような処理を行うことによって、ソース電極134およびドレイン電極135の上端部を曲面形状にでき、その後形成する酸化物半導体膜136、第3の絶縁膜112、ゲート電極110cおよび網状の導電膜126の被覆性を高めることができる。

30

【0146】

以上のように作製されたメモリセルアレイを構成するメモリセル170は、オフ電流の小さい第3のトランジスタ150cおよび小面積かつ大容量のキャパシタ160により、書き込まれたデータを長期間に渡って保持することができる。また、電力の供給を止めてもデータが保持されるため、消費電力を小さくすることができる。

【0147】

40

また、キャパシタ160を第3のトランジスタ150cのドレイン電極135の3側面に沿って設けることで、キャパシタの占有面積を増大させず、キャパシタの容量を増大することができ、集積度の高い半導体記憶装置が提供できる。

【0148】

また、網状の導電膜126が設けられることによって、個々のメモリセルの静電破壊を防止でき、半導体記憶装置の歩留まりおよび信頼性を高めることができる。

【0149】

本実施の形態は、他の実施の形態と適宜組み合わせて用いることができる。

【0150】

(実施の形態2)

50

本実施の形態では、実施の形態1とは異なる構造のメモリセルからなるメモリセルアレイについて図5を用いて説明する。

【0151】

図5(A)に示すメモリセル270は、第4の絶縁膜238が酸化物半導体膜136上のみに設けられる点でメモリセル170とは異なる。即ち、第4の絶縁膜238の上面形状と酸化物半導体膜136の上面形状とが概略一致する構造となる。

【0152】

第4の絶縁膜238が酸化物半導体膜136上のみに設けられることによってキャパシタ260はキャパシタ160と異なる形状になる。具体的には、網状の導電膜126、第4の絶縁膜138および第5の絶縁膜114が、それぞれ網状の導電膜226、第4の絶縁膜238および第5の絶縁膜214で示す構造となる。

10

【0153】

第4の絶縁膜238が酸化物半導体膜136上のみに設けられることによって、キャパシタ260の誘電体膜は第5の絶縁膜214のみとなる。そのため、キャパシタ260は、キャパシタ160と比べて容量を大きくすることができる。結果、メモリセル270は、メモリセル170と比べて、書き込まれたデータをさらに長期間に渡って保持することができる。

【0154】

網状の導電膜226、第4の絶縁膜238および第5の絶縁膜214は、それぞれ網状の導電膜126、第4の絶縁膜138および第5の絶縁膜114と同様の方法および同様の材料で形成すればよい。

20

【0155】

なお、第1のトランジスタ150a、第2のトランジスタ150bおよび第3のトランジスタ150cの構造に変更はない。

【0156】

図5(B)に示すメモリセル271は、ソース電極134およびドレイン電極135の間を埋める第7の絶縁膜218を有する点でメモリセル170とは構造が異なる。

【0157】

第7の絶縁膜218を有することによって、第3のトランジスタ250cは第3のトランジスタ150cと異なる形状になる。具体的には、酸化物半導体膜136、第4の絶縁膜138およびゲート電極110cが、それぞれ酸化物半導体膜236、第4の絶縁膜239およびゲート電極210cで示す構造となる。ここで、第7の絶縁膜218があるために、酸化物半導体膜236、第4の絶縁膜238およびゲート電極210cを、ソース電極134およびドレイン電極135が形成する段差を乗り越えない構造とすることができる。そのため、段差が起因となるリーク電流、段切れが生じにくい構造とすることができる。結果、半導体記憶装置の歩留まりを高めることができる。

30

【0158】

第7の絶縁膜218は、第1の絶縁膜102と同様の方法および同様の材料で形成すればよい。また、第7の絶縁膜218を加熱処理により酸素を放出する絶縁膜とすれば、より電気特性の劣化の少ない第3のトランジスタ250cを得ることができる。

40

【0159】

酸化物半導体膜236およびゲート電極210cは、それぞれ酸化物半導体膜136およびゲート電極110cと同様の方法および同様の材料で形成すればよい。

【0160】

なお、第1のトランジスタ150a、第2のトランジスタ150bおよびキャパシタ160の構造に変更はない。

【0161】

なお、図5(B)において、第4の絶縁膜239が酸化物半導体膜236上のみに設けられても構わない。

【0162】

50

本実施の形態を適用することにより、実施の形態1と比べて書き込まれたデータを長期間に渡って保持でき、また歩留まりの高い半導体記憶装置を得ることができる。

【0163】

本実施の形態は、他の実施の形態と適宜組み合わせて用いることができる。

【0164】

(実施の形態3)

実施の形態1または実施の形態2で示した半導体記憶装置を少なくとも一部に用いてCPU(Central Processing Unit)を構成することができる。

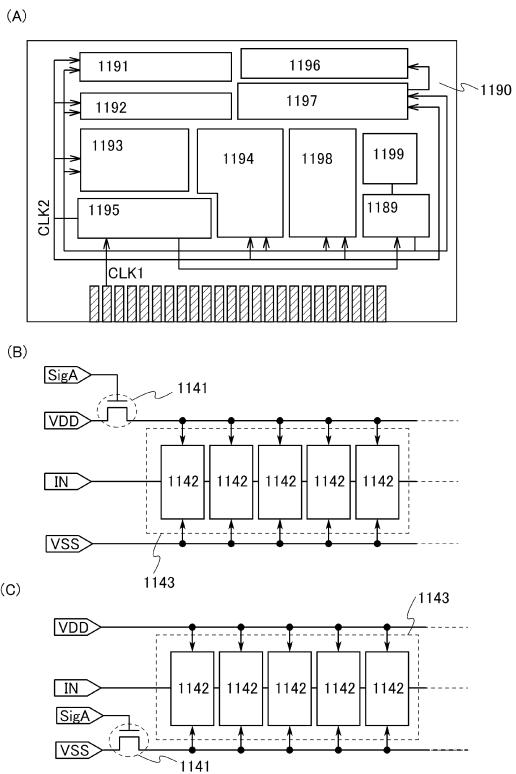

【0165】

図6(A)は、CPUの具体的な構成を示すブロック図である。図6(A)に示すCPUは、基板1190上に、演算回路(ALU: Arithmetic logic unit)1191、ALUコントローラ1192、インストラクションデコーダ1193、インターフェースコントローラ1194、タイミングコントローラ1195、レジスタ1196、レジスタコントローラ1197、バスインターフェース(Bus I/F)1198、書き換え可能なROM1199、およびROMインターフェース(ROM I/F)1189を有している。基板1190は、半導体基板、SOI基板、ガラス基板などを用いる。ROM1199およびROMインターフェース1189は、別チップに設けてもよい。もちろん、図6(A)に示すCPUは、その構成を簡略化して示した一例にすぎず、実際のCPUはその用途によって多種多様な構成を有している。

【0166】

バスインターフェース1198を介してCPUに入力された命令は、インストラクションデコーダ1193に入力され、デコードされた後、ALUコントローラ1192、インターフェースコントローラ1194、レジスタコントローラ1197、タイミングコントローラ1195に入力される。

【0167】

ALUコントローラ1192、インターフェースコントローラ1194、レジスタコントローラ1197、タイミングコントローラ1195は、デコードされた命令に基づき、各種制御を行う。具体的にALUコントローラ1192は、ALU1191の動作を制御するための信号を生成する。また、インターフェースコントローラ1194は、CPUのプログラム実行中に、外部の入出力装置や、周辺回路からの割り込み要求を、その優先度やマスク状態から判断し、処理する。レジスタコントローラ1197は、レジスタ1196のアドレスを生成し、CPUの状態に応じてレジスタ1196の読み出しや書き込みを行う。

【0168】

また、タイミングコントローラ1195は、ALU1191、ALUコントローラ1192、インストラクションデコーダ1193、インターフェースコントローラ1194、およびレジスタコントローラ1197の動作のタイミングを制御する信号を生成する。例えばタイミングコントローラ1195は、基準クロック信号CLK1を元に、内部クロック信号CLK2を生成する内部クロック生成部を備えており、クロック信号CLK2を上記各種回路に供給する。

【0169】

図6(A)に示すCPUでは、レジスタ1196に、半導体記憶装置が設けられている。レジスタ1196の半導体記憶装置には、実施の形態1または実施の形態2に示す半導体記憶装置を用いることができる。

【0170】

図6(A)に示すCPUにおいて、レジスタコントローラ1197は、ALU1191からの指示に従い、レジスタ1196における保持動作の選択を行う。すなわち、レジスタ1196が有する半導体記憶装置において、位相反転素子によるデータの保持を行なうか、容量素子によるデータの保持を行なうかを、選択する。位相反転素子によるデータの保持が選択されている場合、レジスタ1196内の半導体記憶装置への、電源電圧の供給が行われる。容量素子におけるデータの保持が選択されている場合、容量素子へのデータの書き

10

20

30

40

50

換えが行われ、レジスタ 1196 内の半導体記憶装置への電源電圧の供給を停止することができる。

【0171】

電源停止に関しては、図 6 (B) または図 6 (C) に示すように、半導体記憶装置群と、電源電位 VDD または電源電位 VSS の与えられているノード間に、スイッチング素子を設けることにより行うことができる。以下に図 6 (B) および図 6 (C) の回路の説明を行う。

【0172】

図 6 (B) および図 6 (C) では、半導体記憶装置への電源電位の供給を制御するスイッチング素子に、酸化物半導体を活性層に用いたトランジスタを含む記憶回路の構成の一例を示す。

10

【0173】

図 6 (B) に示す記憶装置は、スイッチング素子 1141 と、半導体記憶装置 1142 を複数有する半導体記憶装置群 1143 とを有している。具体的に、各半導体記憶装置 1142 には、実施の形態 1 または実施の形態 2 に示す半導体記憶装置を用いることができる。半導体記憶装置群 1143 が有する各半導体記憶装置 1142 には、スイッチング素子 1141 を介して、ハイレベルの電源電位 VDD が供給されている。さらに、半導体記憶装置群 1143 が有する各半導体記憶装置 1142 には、信号 IN の電位と、ローレベルの電源電位 VSS の電位が与えられている。

【0174】

20

図 6 (B) では、スイッチング素子 1141 として、酸化物半導体などのバンドギャップの大きい半導体を活性層に有するトランジスタを用いており、該トランジスタは、そのゲートに与えられる信号 Sig A によりスイッチングが制御される。なお、スイッチング素子 1141 として、第 3 のトランジスタ 150c または第 3 のトランジスタ 250c を用いてもよい。

【0175】

なお、図 6 (B) では、スイッチング素子 1141 がトランジスタを一つだけ有する構成を示しているが、これに限定されず、トランジスタを複数有していてもよい。スイッチング素子 1141 が、スイッチング素子として機能するトランジスタを複数有している場合、上記複数のトランジスタは並列に接続されていてもよいし、直列に接続されていてもよいし、直列と並列が組み合わされて接続されていてもよい。

30

【0176】

また、図 6 (C) には、半導体記憶装置群 1143 が有する各半導体記憶装置 1142 に、スイッチング素子 1141 を介して、ローレベルの電源電位 VSS が供給されている、記憶装置の一例を示す。スイッチング素子 1141 により、半導体記憶装置群 1143 が有する各半導体記憶装置 1142 への、ローレベルの電源電位 VSS の供給を制御することができる。

【0177】

半導体記憶装置群と、電源電位 VDD または電源電位 VSS の与えられているノード間に、スイッチング素子を設け、一時的に CPU の動作を停止し、電源電圧の供給を停止した場合においてもデータを保持することが可能であり、消費電力の低減を行うことができる。例えば、パーソナルコンピュータのユーザーが、キーボードなどの入力装置への情報の入力を停止している間でも、CPU の動作を停止することができ、それにより消費電力を低減することができる。

40

【0178】

ここでは、CPU を例に挙げて説明したが、DSP (Digital Signal Processor)、カスタム LSI、FPGA (Field Programmable Gate Array) などの LSI にも応用可能である。

【0179】

本実施の形態は、上記実施の形態と適宜組み合わせて実施することが可能である。

50

## (実施の形態 4 )

本実施の形態では、実施の形態 1 乃至実施の形態 3 の少なくともいずれかを適用した電子機器の例について説明する。

## 【 0 1 8 0 】

図 7 ( A ) は携帯型情報端末である。筐体 9 3 0 0 と、ボタン 9 3 0 1 と、マイクロフォン 9 3 0 2 と、表示部 9 3 0 3 と、スピーカ 9 3 0 4 と、カメラ 9 3 0 5 と、を具備し、携帯型電話機としての機能を有する。本発明の一態様は、電子機器の内部にある C P U およびメモリモジュールに適用することができる。

## 【 0 1 8 1 】

図 7 ( B ) は、デジタルスチルカメラである。筐体 9 3 2 0 と、ボタン 9 3 2 1 と、マイクロフォン 9 3 2 2 と、表示部 9 3 2 3 と、を具備する。本発明の一態様は、電子機器の内部にあるメモリモジュールに適用することができる。 10

## 【 0 1 8 2 】

本発明の一態様を用いることで、電子機器の品質を高めることができる。また消費電力を低減し、信頼性を高めることができる。

## 【 0 1 8 3 】

本実施の形態は、他の実施の形態と適宜組み合わせて用いることができる。

## 【 符号の説明 】

## 【 0 1 8 4 】

|         |             |    |

|---------|-------------|----|

| 1 0 0   | 基板          | 20 |

| 1 0 2   | 第 1 の絶縁膜    |    |

| 1 0 4 a | 低抵抗領域       |    |

| 1 0 4 b | 低抵抗領域       |    |

| 1 0 5   | 低抵抗領域       |    |

| 1 0 6 a | チャネル形成領域    |    |

| 1 0 6 b | チャネル形成領域    |    |

| 1 0 7   | 半導体膜        |    |

| 1 0 8   | 第 2 の絶縁膜    |    |

| 1 1 0 a | ゲート電極       |    |

| 1 1 0 b | ゲート電極       | 30 |

| 1 1 0 c | ゲート電極       |    |

| 1 1 2   | 第 3 の絶縁膜    |    |

| 1 1 4   | 第 5 の絶縁膜    |    |

| 1 1 6   | 第 6 の絶縁膜    |    |

| 1 2 0   | ソース線        |    |

| 1 2 2   | ビット線        |    |

| 1 2 4   | ワード線        |    |

| 1 2 6   | 網状の導電膜      |    |

| 1 3 4   | ソース電極       |    |

| 1 3 5   | ドレイン電極      | 40 |

| 1 3 6   | 酸化物半導体膜     |    |

| 1 3 8   | 第 4 の絶縁膜    |    |

| 1 5 0 a | 第 1 のトランジスタ |    |

| 1 5 0 b | 第 2 のトランジスタ |    |

| 1 5 0 c | 第 3 のトランジスタ |    |

| 1 6 0   | キャパシタ       |    |

| 1 7 0   | メモリセル       |    |

| 2 1 0 c | ゲート電極       |    |

| 2 1 4   | 第 5 の絶縁膜    |    |

| 2 1 8   | 第 7 の絶縁膜    | 50 |

|         |                |    |

|---------|----------------|----|

| 2 2 6   | 網状の導電膜         |    |

| 2 3 6   | 酸化物半導体膜        |    |

| 2 3 8   | 第4の絶縁膜         |    |

| 2 3 9   | 第4の絶縁膜         |    |

| 2 5 0 c | 第3のトランジスタ      |    |

| 2 6 0   | キャパシタ          |    |

| 2 7 0   | メモリセル          |    |

| 2 7 1   | メモリセル          |    |

| 1 1 4 1 | スイッチング素子       |    |

| 1 1 4 2 | 半導体記憶装置        | 10 |

| 1 1 4 3 | 半導体記憶装置群       |    |

| 1 1 8 9 | ROMインターフェース    |    |

| 1 1 9 0 | 基板             |    |

| 1 1 9 1 | ALU            |    |

| 1 1 9 2 | ALUコントローラ      |    |

| 1 1 9 3 | インストラクションデコーダ  |    |

| 1 1 9 4 | インターフラップコントローラ |    |

| 1 1 9 5 | タイミングコントローラ    |    |

| 1 1 9 6 | レジスタ           |    |

| 1 1 9 7 | レジスタコントローラ     | 20 |

| 1 1 9 8 | バスインターフェース     |    |

| 1 1 9 9 | ROM            |    |

| 9 3 0 0 | 筐体             |    |

| 9 3 0 1 | ボタン            |    |

| 9 3 0 2 | マイクロフォン        |    |

| 9 3 0 3 | 表示部            |    |

| 9 3 0 4 | スピーカ           |    |

| 9 3 0 5 | カメラ            |    |

| 9 3 2 0 | 筐体             |    |

| 9 3 2 1 | ボタン            | 30 |

| 9 3 2 2 | マイクロフォン        |    |

| 9 3 2 3 | 表示部            |    |

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

---

フロントページの続き

(56)参考文献 特開2002-093178(JP,A)

特開2007-123861(JP,A)

特開平01-091447(JP,A)

特開平04-239766(JP,A)

特開平04-067670(JP,A)

特開昭61-088554(JP,A)

特開2007-220818(JP,A)

特開2010-166030(JP,A)

特開昭57-105889(JP,A)

米国特許出願公開第2007/0072439(US,A1)

(58)調査した分野(Int.Cl., DB名)

H01L 21/8242

H01L 27/108