**República Federativa do Brasil**

Ministério do Desenvolvimento, Indústria

e do Comércio Exterior

Instituto Nacional da Propriedade Industrial

**(11) PI 0014726-5 B1**

\* B R P I D 0 1 4 7 2 6 B 1 \*

**(22) Data do Depósito: 11/10/2000**

**(45) Data de Concessão: 06/10/2015**

**(RPI 2335)**

---

**(54) Título: DISPOSITIVO DE DIGITALIZAÇÃO E PROCESSAMENTO DE SINAL DE TELEVISÃO ANALÓGICO E DIGITAL**

**(51) Int.Cl.: H04N 9/66**

**(30) Prioridade Unionista: 13/10/1999 US 60/159,149**

**(73) Titular(es): THOMSON LICENSING S.A.**

**(72) Inventor(es): ERIC STEPHEN CARLSGAARD, MARK FRANCIS RUMREICH, JOHN SIDNEY STEWART**

"DISPOSITIVO DE DIGITALIZAÇÃO E PROCESSAMENTO DE

SINAL DE TELEVISÃO ANALÓGICO E DIGITAL"

A presente invenção refere-se a dispositivos para o processamento de sinais analógicos e/ou digitais, e, mais 5 particularmente, a circuitos integrados que utilizam freqüências de relógio múltiplas para a digitalização e processamento de vários sinais analógicos e/ou digitais.

Os circuitos integrados, ou ICs, são extensivamente usados em todos os tipos de dispositivos 10 eletrônicos. Quanto mais complexos se tornam estes dispositivos eletrônicos, mais aumenta o número de ICs necessários para realizar todas as funções requeridas e/ou as funções de diversos ICs são combinadas em um único IC. Mesmo que múltiplas funções sejam consolidadas em um único 15 IC, é desejável reduzir-se a complexidade interna do IC.

As televisões atuais utilizam muitos ICs diferentes para o processamento de sinais de televisão tanto analógicos como digitais a partir de fontes terrestres e não terrestres. Espera-se que a próxima geração de televisões 20 digitais/analógicas, no entanto, apresente níveis ainda maiores de integração do que as televisões atuais. Níveis maiores de integração se traduzem em menos ICs, uma vez que os processos realizados por diversos ICs individuais são combinados em um IC. No entanto, vários obstáculos se 25 apresentam no caminho de se combinar o processamento de receptores de sinal de televisão analógico com os receptores requeridos para os sinais de televisão digitais.

Um problema com relação à integração de ICs de processamento de sinal de televisão analógico e digital é que diferentes fontes de vídeo (tanto analógicas como digitais) podem requerer conversores analógico para digital (A/D) para correrem em diferentes velocidades de amostragem. Os sinais de televisão analógicos se baseiam em freqüências presas em linha ou em freqüências de croma sub-portadoras presas, enquanto os sinais de televisão modulados digitalmente (digitais) se baseiam em suas próprias velocidades símbolo. Da mesma forma, a tecnologia A/D atual produz uma comunicação cruzada digital que afeta, de um modo adverso, o desempenho A/D quando relógios assíncronos estão presentes.

É conhecido usar-se demoduladores digitais sozinhos que utilizam uma interpolação digital para uma operação fora de freqüência. Da mesma forma, um segundo processamento de canal para sinais analógicos é realizado com uma freqüência de amostra assíncrona. Neste último caso, no entanto, o canal principal fica preso a um parâmetro do sinal de televisão analógico que entra, como, por exemplo, os pulsos de sincronização horizontais ou de rajada de cor.

A publicação WO 98/46027 apresenta um sistema decodificador de cor de múltiplos padrões que inclui um relógio de cristal assíncrono externo para demodular todas as variantes do sistema de cor PAL/NTSC, sem digitalizar o sinal de crominância analógico. Em um método apresentado de demodulação de um sinal de crominância analógico, os sinais de quadratura digitais são gerados para demodular o sinal de

crominância analógico a fim de se obter os sinais de diferença de cor demodulado analógicos. Um sinal de erro de fase digital é fornecido a partir de pelo menos um dos sinais de diferença de cor demodulados analógicos. O sinal 5 de erro de fase digital é digitalmente filtrado de modo a se obter um sinal de controle de fase para a geração de sinais de quadratura digital.

A Patente U.S. N° 5.367.337 apresenta um aparelho e método para o recebimento e amostragem de um sinal de 10 imagem de vídeo que entra de forma assíncrona, e em seguida processando o sinal de modo a recuperar a imagem de vídeo, incluindo o formato de vídeo, para conversão em um formato de vídeo pré-selecionado. A patente apresenta a super-amostragem no processamento a fim de detectar o formato de 15 vídeo.

A Patente U.S. N° 5.808.691 apresenta um aparelho para a sintetização de um sinal digital periódico tendo uma freqüência que é especificada pela freqüência de um sinal de referência periódico que é assíncrono com relação a um 20 relógio de amostragem do sinal digital periódico. Em uma modalidade preferida, um sistema de vídeo digital sintetiza uma sub-portadora de cor digital e sincronizado a uma freqüência de referência de um oscilador de cristal que é assíncrono com relação a um relógio de sistema digital para 25 o sistema de vídeo digital.

A presente invenção é um IC de sistema único que realiza a digitalização e o processamento simultâneos de múltiplos sinais analógicos e/ou digitais, usando uma fonte

de freqüência comum que não fica presa a um parâmetro do sinal que entra. Sendo assim, uma amostragem e processamento de alto desempenho de todos os sinais que entram podem ser obtidos.

5           A presente invenção provê uma decodificação de vídeo analógica padrão para dois canais usando uma única freqüência de referência (relógio de referência) que não fica presa a nenhum dos dois sistemas. Ou seja, o relógio de referência não se baseia em, ou fica presa a, nenhum sistema. Ou seja, o relógio de referência não se baseia em, ou fica preso a, uma característica que se prende a nenhum sinal de entrada. Os dois processadores de sinal digital, para sinais de televisão terrestre e via satélite, são modificados de modo a executar o processamento com base na 10 mesma freqüência de referência. A presente invenção provê a operação de freqüência síncrona de todos os processadores de sinal A/Ds e digitais dos múltiplos canais a fim de impedir 15 a amostragem e processamento errôneos do sinal que entra.

Em uma forma da presente invenção, um único 20 relógio de referência de uma freqüência particular é entrado em um gerador de relógio que gera todas as freqüências operacionais (sinais de relógio) necessárias por parte dos conversores A/D e por parte do circuito/lógica de decodificação no IC. O relógio de referência é independente, 25 por exemplo, não fica preso a nenhuma característica de sincronização dos sinais de entrada.

Uma vez que existe apenas um relógio de referência a partir do qual todas as demais freqüências de amostragem e

processamento são geradas, os A/Ds poderão operar com um alto desempenho, até 10 bits de precisão, com pouco a nenhum ruído digital. Isto, de modo geral, não é possível com freqüências de amostragem assíncronas, uma vez que as "zonas silenciosas", necessárias para a amostragem da entrada analógica, não mais existem. No entanto, com as múltiplas freqüências de amostragem tendo como base um único relógio de referência (ou freqüência) da presente invenção, estas zonas silenciosas entre as transições digitais são preservadas.

Uma seção de circuito/lógica do IC em questão, que processa sinais de televisão de radiodifusão via satélite (digital) usa um interpolador para processar um sinal que entra a uma freqüência relativa à velocidade de símbolo apropriada (por exemplo, 40 MHz) mesmo que as amostras presentes possam ser tomadas em uma freqüência diferente (por exemplo, 54 MHz). Um procedimento similar é usado para sinais de televisão de banda lateral residual (VSB) ou digital terrestre, nos quais duas vezes a velocidade símbolo é uma freqüência apropriada (por exemplo, 21,54 MHz) enquanto a freqüência de amostragem (sinal de relógio) é maior do que a freqüência em particular (por exemplo, 27 MHz). O processamento de sinal de televisão analógico é também obtido em freqüência em particular (por exemplo, 18 MHz) para cada canal. Mesmo que as amostras de sinal de televisão analógico não estejam presas à velocidade de linha de entrada, a freqüência horizontal é determinada com uma precisão de sub-amostra para cada canal. Um conversor de

velocidade de amostra final tem uma freqüência (por exemplo, de 27 MHz) que corresponde a uma freqüência para luma (por exemplo, 13,5 MHz) mais uma freqüência para cada um dos sinais de diferença de cor (por exemplo, 6,75 MHz). Isto 5 provê linhas não tremidas de saída de dados. Além disso, um demodulador de croma do presente IC usa um oscilador de tempo discreto digital (DTO) preso ao sinal de rajada de croma de entrada para cada um dos sinais de entrada. Sendo assim, todo o processamento digital é obtido usando-se 10 relógios síncronos ao invés do caráter assíncrono inerente às várias seções de processamento de circuito e lógica, como, por exemplo, por meio de quatro tipos de sistemas de sinal de televisão.

A presente invenção apresenta também o uso duplo 15 da maior parte do circuito digital na seção dupla de processamento de sinal de NTSC. O decodificador de cor digital (DCD) realiza todas as funções de processamento de sinal necessárias para a decodificação de um vídeo de NTSC que inclui a filtragem de pente de modo a separar luma e 20 croma, a demodulação de croma de modo a gerar os sinais de diferença de cor, a separação de sinal de sincronização (*sync*), a conversão de velocidade de amostra (SRC) a uma freqüência de interface padrão, e a divisão de dados de intervalo de bloqueio vertical (VBI). O intervalo VBI 25 tipicamente inclui *closed caption*, informações de controle e velocidade parentais de *chip* em V, um guia de programa, dados de tele-texto, e coisa do gênero. Todas estas funções são incluídas tanto para o vídeo de canal principal como

para o segundo vídeo de canal, que é geralmente para uma imagem *picture in picture* (PIP).

De acordo com um outro aspecto da presente invenção, o decodificador DCD combina os dois canais, 5 duplicando apenas os componentes de armazenagem de dados presentes requeridos para os dois canais, e usa os mesmos circuitos para a maior parte do processamento ao correr em duas vezes a freqüência de amostragem e de relógio requerida e dos canais de interrupção a cada ciclo de relógio. Sendo 10 assim, por exemplo, cada canal de 18 MHz é processado a cada outro ciclo de relógio a 36 MHz.

Em uma outra forma, a presente invenção inclui uma seção de processamento de sinal analógico e um gerador de relógio. A seção de processamento de sinal analógico é 15 operável no sentido de processar os sinais analógicos tendo um componente de sincronização, como, por exemplo, um pulso de sincronização horizontal ou coisa do gênero. O gerador de relógio é operável no sentido de produzir sinais de sincronização internos com base em um sinal de referência 20 externo para uso pela seção de processamento de sinal analógico, na qual o sinal de referência externo é independente do componente de sincronização dos sinais analógicos.

Em uma outra forma, a presente invenção inclui uma 25 seção de processamento de sinal analógico, uma seção de processamento de sinal digital, um primeiro conversor A/D associado à seção de processamento de sinal analógico, e um segundo conversor A/D associado à seção de processamento de

sinal digital. O circuito integrado inclui ainda um gerador de relógio operável no sentido de prover o primeiro e o segundo sinais de relógio para o primeiro e segundo conversores analógicos para digitais respectivamente a 5 partir de um único sinal de relógio de referência, no qual o primeiro e o segundo sinais de relógio provêm uma operação síncrona do primeiro e do segundo conversores analógicos para digitais.

Em uma outra forma ainda, a presente invenção 10 inclui uma seção de processamento de sinal analógico, uma seção de processamento de sinal digital, e um gerador de relógio. O gerador de relógio é operável no sentido de produzir múltiplos sinais de relógio de diferentes freqüências para uso por parte das seções de processamento 15 analógicas e digitais, nas quais o gerador de relógio usa um único sinal de relógio de referência de uma dada freqüência independente de qualquer característica de sincronização do sinal analógico e/ou digital de entrada. As seções de processamento de sinal analógico e digital processam seus 20 respectivos sinais analógicos e digitais simultaneamente.

A presente invenção é descrita com referência aos desenhos em anexo, nos quais:

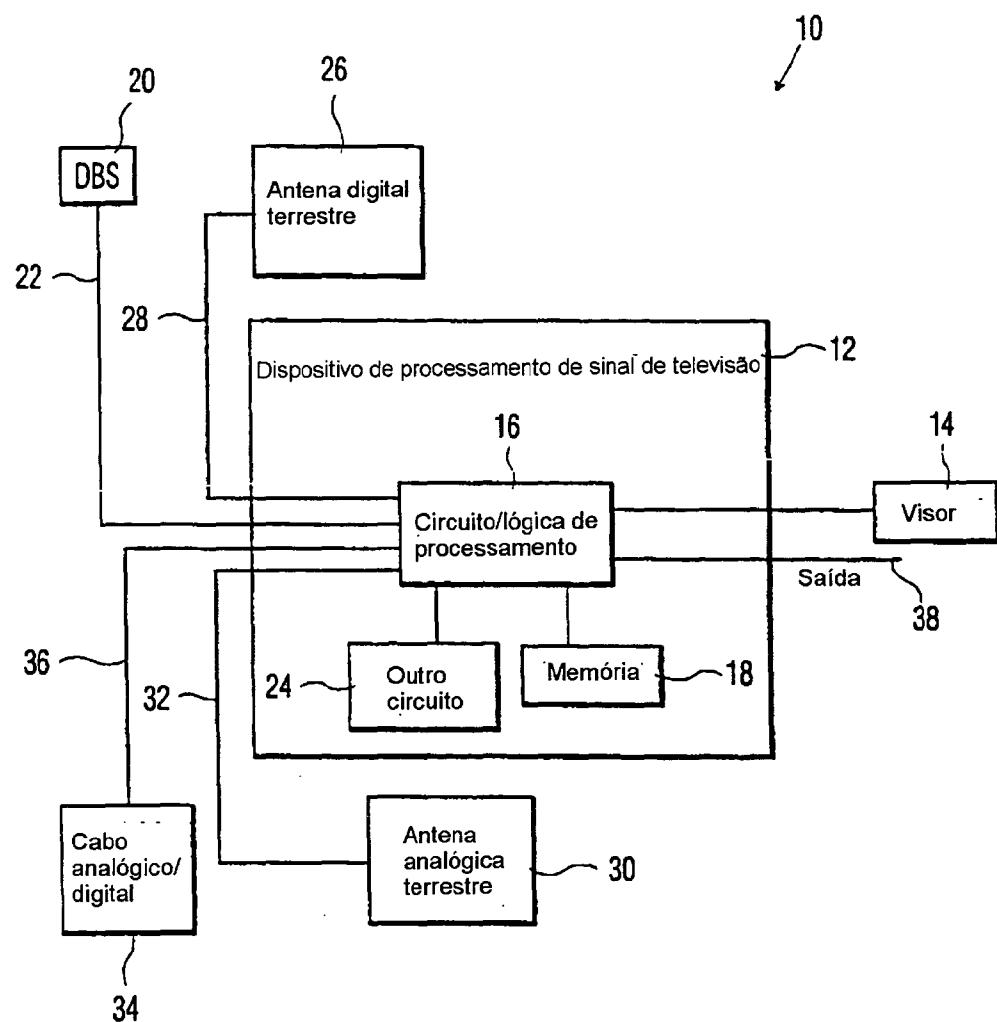

A Figura 1 é um diagrama de bloco de um sistema exemplar no qual o presente IC pode ser usado;

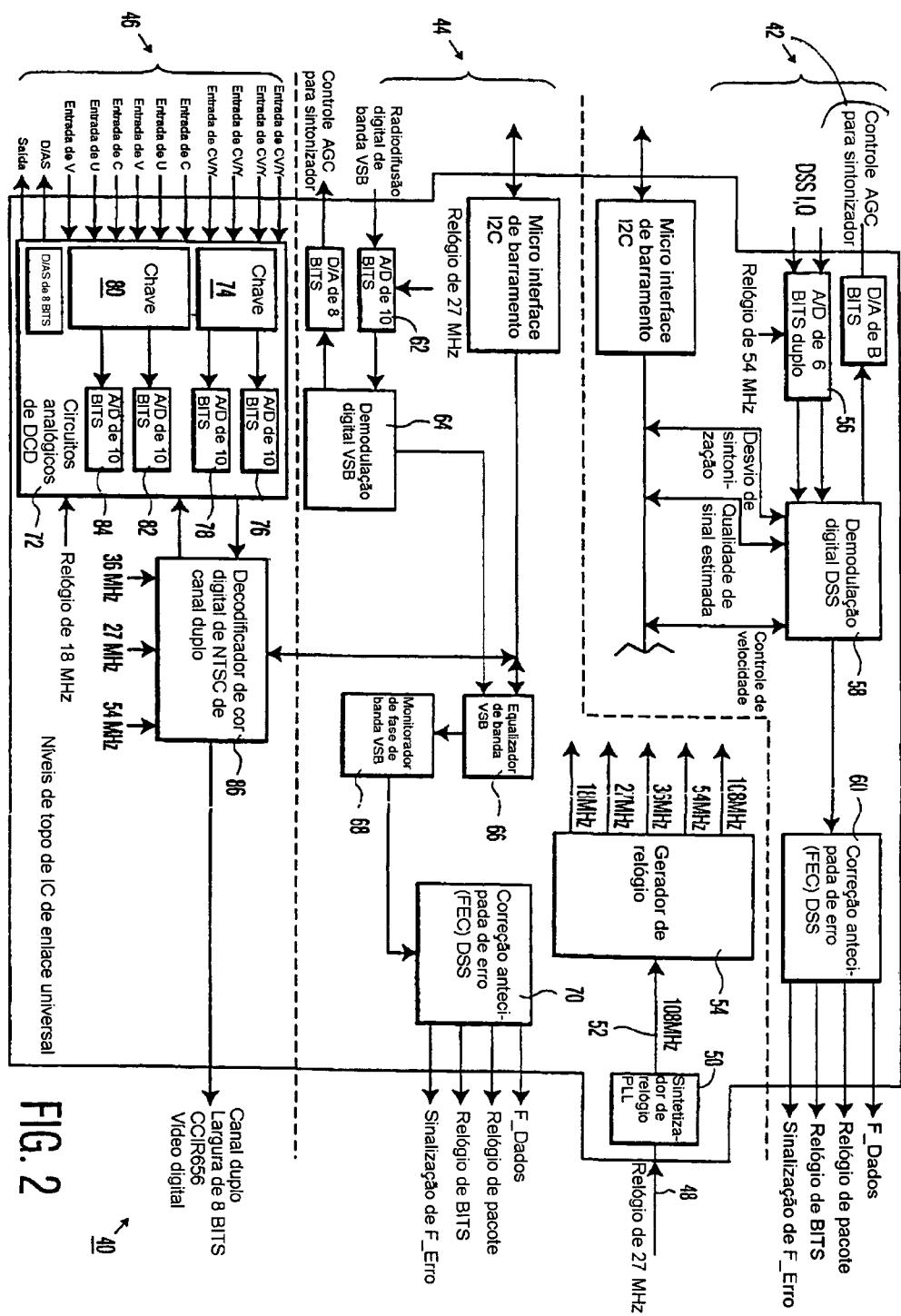

A Figura 2 é um diagrama de bloco do IC usado no sistema exemplar da Figura 1, incorporando uma modalidade d 25 presente invenção;

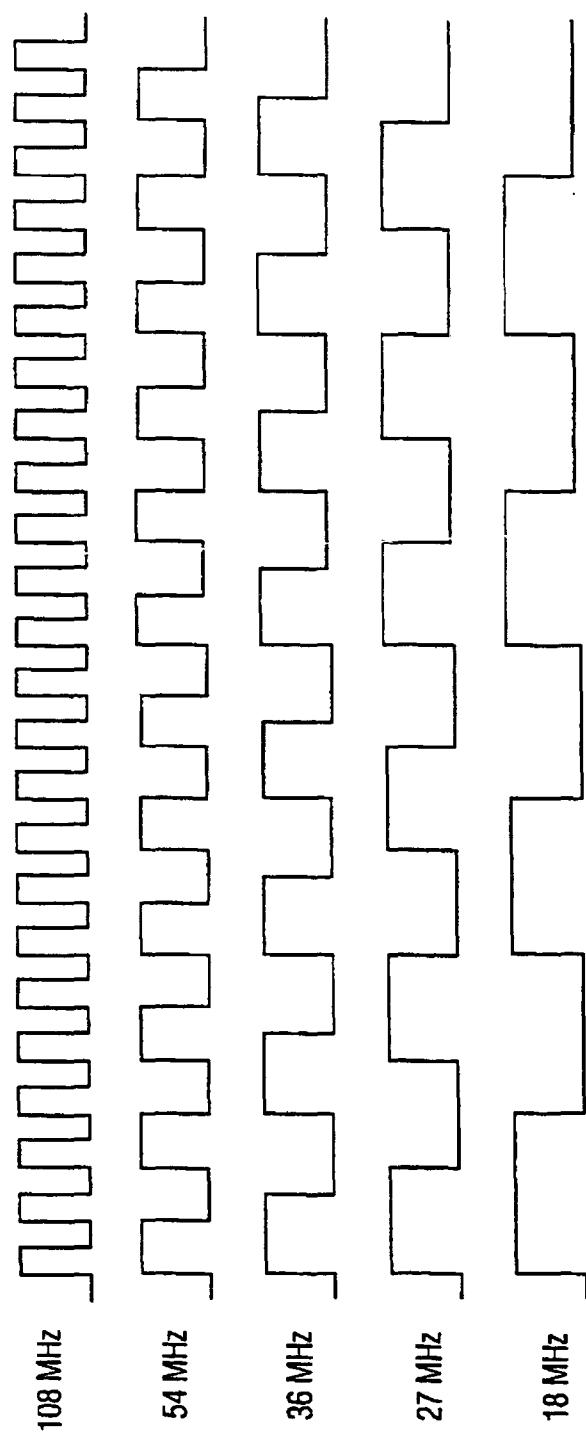

A Figura 3 é um gráfico mostrando as várias freqüências digitais usadas no IC da Figura 2;

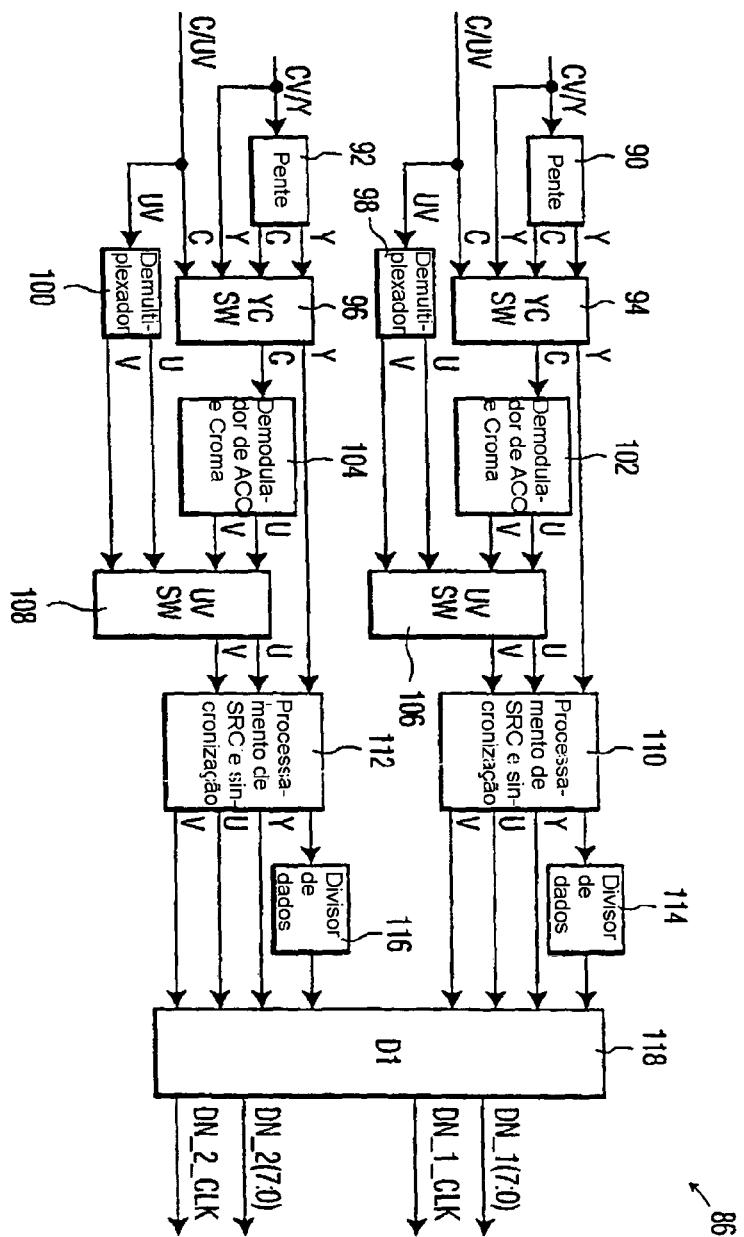

A Figura 4 é um diagrama de bloco do decodificador de cor digital do IC da Figura 2; e

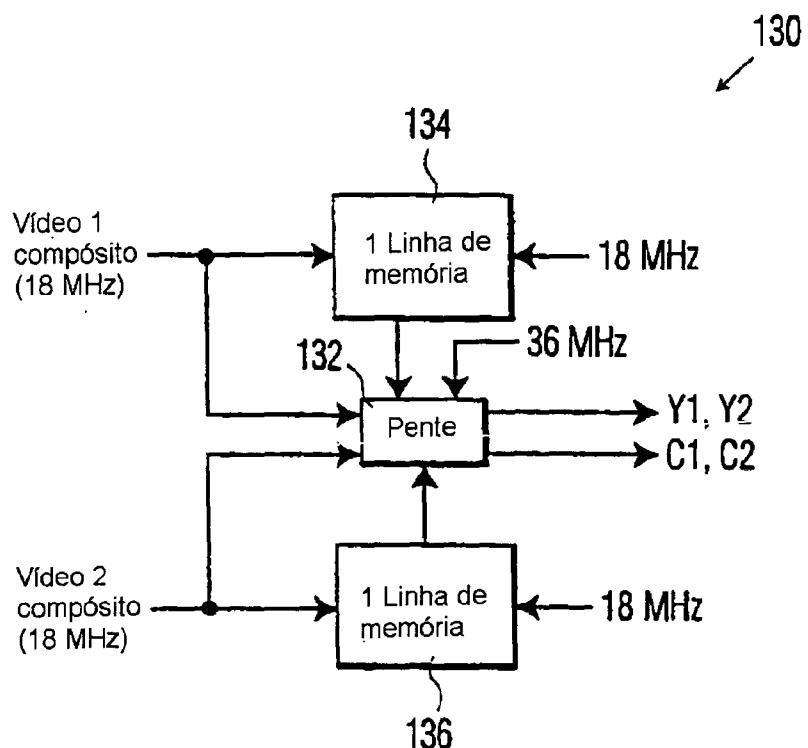

5 A Figura 5 é um diagrama de bloco de uma implementação de filtro de pente do IC da Figura 2.

Caracteres de referência correspondentes indicam peças correspondentes em todas as diversas vistas.

Com referência à Figura 1, é ilustrado um diagrama 10 de bloco de um sistema 10 adequado para o uso de um IC de acordo com a presente invenção. O sistema 10 compreende uma pluralidade de circuitos integrados (ICs) para o processamento de sinais e/ou de dados e informações, em que pelo menos um IC requer múltiplos relógios, freqüências de 15 relógio, ou sinais de relógio/de sincronização para um funcionamento apropriado. Este tipo de IC pode ser chamado de um IC de múltiplos relógios. Deve-se apreciar que o sistema 10 é um ambiente/aplicação exemplar que utiliza o presente IC de múltiplos relógios. O IC de múltiplos 20 relógios do sistema 10, de acordo com os princípios aqui apresentados, pode assumir muitas formas e/ou realizar muitas funções, conforme conhecidas àqueles versados na técnica.

No sistema 10, o IC de múltiplos relógios realiza 25 um processamento de sinal de televisão para uma variedade de formatos de sinal de televisão a partir de uma variedade e fontes. Em poucas palavras, o IC processador de sinal de televisão de múltiplos relógios que incorpora a presente

invenção é adaptado/operável para processar sinais de televisão via satélite digitais, sinais de televisão digitais (incluindo de distribuição a cabo) terrestres, e sinais de televisão analógicos (incluindo de distribuição a cabo) terrestres. Estes sinais analógicos e digitais podem ser providos em vários esquemas de codificação e/ou modulação.

O sistema 10 inclui um dispositivo de processamento de sinal de televisão 12, que pode ser um 10 aparelho de televisão, um conversor *set-top box*, ou coisa do gênero (coletivamente "aparelho de televisão"). O dispositivo de processamento de sinal de televisão 12 inclui um circuito/lógica de processamento 16 para a decodificação de um sinal de televisão recebido. O circuito/lógica de 15 processamento 16 operável para decodificar e processar sinais ou transmissões de televisão de áudio e vídeo analógicos modulados digitalmente ("sinais de televisão digital") a partir do sistema de Satélite de Radiodifusão Direta (DBS) 20 modulado usando, por exemplo, o formato de 20 modulação/codificação de QPSK (Chave de Mudança de Fase de Quadratura). O circuito/lógica de processamento 16 é também operável no sentido de decodificar e processar sinais de televisão digitais a partir de uma antena de Televisão Digital Terrestre (DTV) 26. Estes sinais de televisão podem 25 ser digitalmente modulados usando um formato de modulação / codificação VSB (de Banda Lateral Residual).

O circuito/lógica de processamento 16 é também operável no sentido de processar sinais de televisão de

áudio e vídeo analógicos ("sinais de televisão analógicos") a partir de uma antena analógica terrestre 30 recebida via uma trajetória ou linha de sinal 32, assim como sinais de televisão analógicos a partir de um sistema CATV (de televisão a cabo) 34. O formato de modulação/codificação dos sinais de televisão analógicos é tipicamente o NTSC, outros formatos, porém, podem ser usados. O processamento de sinais de televisão analógicos tipicamente inclui a digitalização dos sinais de entrada através de um circuito apropriado, 10 software, e/ou outros componentes. Os sinais de televisão digitais a partir do sistema CATV 34 podem ainda ser decodificados e processados. Deve-se apreciar que o aparelho de televisão 12 é adaptado para receber e processar sinais de televisão analógicos e/ou digitais a partir de outras 15 fontes além daquela mostrada.

O dispositivo de processamento de sinal de televisão 12 tipicamente inclui ainda uma memória 18, que inclui instruções de programa armazenados (ou seja, um software) para o controle da operação do dispositivo de 20 processamento de sinal de televisão 12. O circuito/lógica 24 é provido para outra funcionalidade do dispositivo de processamento de sinal de televisão 12, funcionalidade esta não necessária para o entendimento ou prática da presente invenção, não sendo, portanto, descrita em detalhe.

25 O sistema 10 inclui ainda um visor 14 que é acoplado ao circuito/lógica de processamento 16, e adequado para a exibição da porção de vídeo do sinal de televisão (ou qualquer OSD do mesmo). No caso de um conversor *set-top box*,

ou coisa do gênero, o visor 14 é associado a um visor de um aparelho de televisão anexo. A saída 38 pode ainda ser provida de modo a suprir áudio e/ou vídeo a partir do dispositivo de processamento 12 para um outro dispositivo 5 incluindo um gravador de vídeo ou coisa do gênero.

O dispositivo de processamento de sinal de televisão 12 pode ser uma televisão analógica/digital incluindo, mas não se limitando a uma HDTV DTV-320 (Televisão de Alta Definição) fabricada pela Thomson 10 Consumer Electronics, Inc. de Indianápolis, Indiana, uma televisão digital, como, por exemplo, uma televisão digital de alta definição (HDTV), um conversor *set-top box* capaz de utilizar sinais de televisão analógicos/digitais, um dispositivo de armazenagem de sinal de televisão, ou 15 qualquer outro dispositivo que possa processar várias formas de sinais de televisão.

De acordo com um aspecto da presente invenção, pelo menos um dentre a pluralidade de ICs do sistema 10 é um IC de múltiplos relógios. O IC de múltiplos relógios 20 utilizado no circuito/lógica de processamento 16 do aparelho de televisão 12 é conhecido como um IC de Enlace Universal, e é ilustrado na Figura 2. O IC de enlace universal 40 é um circuito integrado de um desenho de sinal mixado, isto é, ele tem um circuito de processamento de sinal de televisão 25 tanto analógico como digital, e incorpora, ou integra, diversas funções de processamento de sinal de televisão em um único IC.

Com referência à Figura 2, é mostrado um diagrama de bloco do Enlace Universal do IC de Enlace Universal 40 usado no aparelho de televisão 12. Os sinais de múltiplos relógios de diferentes freqüências são gerados pelo IC de Enlace Universal 40 usando um único sinal de relógio de referência gerado externamente de uma dada freqüência. O IC de Enlace Universal 40 inclui um pino I/O 48 que recebe o sinal de relógio de referência gerado externamente. Na presente modalidade, o IC de Enlace Universal 40 usa um sinal de relógio de referência de 27 MHz provido externamente. Outras freqüências de sinal de relógio de referência externo podem ser usadas de acordo com os princípios aqui apresentados.

Notavelmente, o sinal de relógio de referência externo não se baseia nas, ou fica preso a, quaisquer características que se prendem, por exemplo, a um pulso de sincronização ou rajada de cor, a um sinal de televisão que entra (análogo ou digital). Ao invés disso, o sinal de relógio de referência externo é escolhido no sentido de prover uma fácil multiplicação e divisão do mesmo de modo a gerar os sinais de relógio de freqüências apropriadas a fim de acomodar as exigências de freqüência de sinal de sincronização das várias seções ou blocos de circuito/lógica do IC de Enlace Universal 40.

No IC de Enlace Universal 40, o sinal de relógio de referência externa é provido para o sintetizador de Loop Travado em Fase (PLL) 50, que produz um sinal de relógio de saída de uma dada freqüência na saída/linha 52. Aqui, o

5 sinal de relógio de saída PLL é escolhido para ser de 108 MHz e pode ser considerado um sinal de relógio de referência interno. Todos os sinais de relógio requeridos restantes são gerados a partir deste sinal de relógio de referência interno.

O sinal de relógio de referência interno de 108 MHz é provido no gerador de relógio 54, que contém o circuito/lógica apropriado para gerar as freqüências de múltiplos relógios. O número atual de sinais de relógio produzido pelo gerador de relógio 54 depende das necessidades de sinal de relógio do IC em particular. No IC de Enlace Universal 40, o gerador de relógio 54 produz quatro (4) sinais de relógio de diferentes freqüências e um (1) sinal de relógio da mesma freqüência que o sinal de relógio de referência interno. Cada sinal de relógio gerado é em seguida roteado para a seção apropriada do bloco de circuito/lógica.

De acordo com a presente invenção, a freqüência de relógio de referência de IC interna gerada pelo sintetizador de relógio PLL 50 é uma freqüência múltipla da freqüência de relógio de referência externa. Mais particularmente, a freqüência de relógio de referência de IC interna é de preferência um número múltiplo inteiro da freqüência de relógio de referência externa. A freqüência de relógio de referência de IC interna é também escolhida de tal modo que possa ser dividida na pluralidade de sinais ou freqüências de relógio de IC utilizáveis pelas várias seções ou relógios de circuito/lógica.

No presente caso, a freqüência de sinal de relógio de referência interna é de 108 MHz, que é quatro (4) vezes a freqüência de sinal de relógio de referência externa de 27 MHz. O gerador de relógio 54 em seguida produz um sinal de 5 relógio de 54 MHz, que é uma metade (1/2) do sinal de relógio de IC interno de 108 MHz, um sinal de relógio de 36 MHz, que vem a ser um terço (1/3) do sinal de relógio de IC interno de 108 MHz, um sinal de relógio de 27 MHz que vem a ser um quarto (1/4) do sinal de relógio de IC interno de 108 10 MHz, e um sinal de relógio de 18 MHz que vem a ser um sexto (1/6) do sinal de relógio de IC interno de 108 MHz. Portanto, o gerador de relógio 54 gera 4 sub-relógios que são sub-harmônicos do relógio interno principal sem mudança de fase.

15. Um outro fator na determinação das freqüências dos sinais de relógio internos são as velocidades da amostragem, ou das velocidades de sincronização, para as várias seções de blocos de circuito/lógica do IC de Enlace Universal 40. Conforme indicado acima, o IC de Enlace Universal 40 inclui 20 três seções principais. As três seções principais são: a seção "Satlink" 42, operável no sentido de receber e demodular/decodificar sinais de televisão transmitidos via satélite; a seção "de enlace de VSB (Banda Lateral Residual)" 44 operável no sentido de receber e 25 demodular/decodificar sinais digitais gerais transmitidos via terrestre e/ou sinais digitais de alta definição (HDTV); e a seção de "DCD" (Decodificador de Cor Digital) 46, que vem a ser um bloco de circuito/lógica operável no sentido de

prover sinais de comutação, de demodulação de croma, ou outro processamento de sinal de sinais (análogicos) de NTSC. O IC de Enlace Universal 40 provê diversos sistemas de decodificação/demodulação separados, incluindo um primeiro 5 sistema para um sinal de televisão analógico principal, um segundo sistema para um sinal de televisão analógico auxiliar (como, por exemplo, uma imagem PIP ou *picture in picture* e/ou uma imagem POP *picture on picture*), um terceiro sistema para sinais de televisão via satélite digitais, e um 10 quarto sistema para sinais de televisão terrestres digitais. As seções 42, 44, e 46 operam independentemente e em paralelo. Devido à natureza dos vários sinais, várias porções de circuito/lógica das seções ou blocos de circuito/lógica requerem diferentes freqüências de 15 sincronização ou amostragem diferentes.

A seção Satlink 42 recebe uma entrada I, Q em um conversor A/D de "x bits" apropriado. Em particular, as entradas I e Q são providas para um conversor A/D de 6 bits duplo 56 que é sincronizado ou amostrado usando o sinal de 20 relógio de 54 MHz. O bloco de demodulação 58 e o bloco de Correção Antecipada de Erros (FEC) 60 processam ainda mais o sinal de televisão digital de radiodifusão via satélite. Em particular, o bloco de demodulação 58 e o bloco de FECHAMENTO 60 usa um interpolador para processar o sinal 25 (digital) de radiodifusão via satélite em uma freqüência relativa à velocidade de símbolo apropriada aos sinais de televisão digitais de radiodifusão via satélite. No presente caso, a freqüência de velocidade de símbolo apropriada é de

40 MHz. O conversor A/D de 6 bits duplo 56, no entanto, utiliza o sinal de relógio de IC de 54 MHz para sincronizar ou amostrar (superamostrar) o sinal de televisão que entra, mesmo que este requeira apenas um sinal de relógio ou amostragem de 40 MHz. O relógio de 54 MHz provê um aumento de trinta e cinco porcento (35%) na freqüência de relógio ou amostragem sobre a freqüência de relógio ou amostragem necessária.

Similar à seção Satlink 42, a seção de VSB 44 10 recebe o sinal de televisão de radiodifusão digital de VSB através de um conversor A/D de "x bits" apropriado. A seção de VSB 44 recebe o sinal de VSB através de um conversor A/D de 10 bits sincronizado com o sinal de relógio de 27 MHz. O bloco de demodulação 64, o bloco de equalizador 66, o bloco 15 monitorador de fase 68, e o bloco de Correção Antecipada de Erro (FEC) 70 processam ainda o sinal de televisão digital de radiodifusão terrestre. Em particular, o bloco de demodulação 64, o bloco equalizador 66, o bloco monitorador de fase 68, e o bloco de Correção FEC 70 processa o sinal de 20 Banda VSB em duas vezes uma freqüência relativa à velocidade de símbolo para os sinais de televisão digitais de radiodifusão de VSB (isto é, terrestre). No presente caso, a freqüência de velocidade de símbolo apropriada é de 10,77 MHz, portanto duas vezes a freqüência de velocidade de 25 símbolo apropriada é de 21,54 MHz. O conversor A/D de 10 bits 62, no entanto, utiliza o sinal de relógio de IC de 27 MHz para sincronizar ou amostrar (superamostrar) o sinal de telefone que entra, mesmo que ele requeira apenas um sinal

de relógio ou amostragem de 21,54 MHz. O relógio de 27 MHz provê um aumento de aproximadamente vinte e cinco porcento (25%) na freqüência de relógio ou amostragem sobre a freqüência de amostragem requerida.

5                   Na seção de decodificador DCD 46, a amostragem analógica é realizada usando o sinal de relógio de 18 MHz para cada canal do sinal de televisão analógico. Mesmo que estas amostras não estejam presas a uma característica do sinal de televisão de entrada, esta freqüência horizontal é

10 determinada com a precisão de sub-amostra para cada canal. A seção de decodificador DCD 46 é operável no sentido de receber dois sinais de televisão analógicos (isto é, um para o canal principal e o outro para a imagem PIP ou POP) na seção de circuitos analógicos 72. Os quatro (4) sinais CV/Y

15 da mesma são entrados para a chave 74 que envia de maneira apropriada os sinais para os dois conversores A/D de 10 bits 76 e 78. Os dois conjuntos de C, U, e V INS separados dos mesmos são entrados para a chave 80 que envia de maneira apropriada o sinal para os dois conversores A/D de 10 bits

20 82 e 84. As saídas destes quatro conversores A/D de 10 bits 76, 78, 82, 84 são entradas para o decodificador de cor digital NTSC de canal duplo 86. A conversão de velocidade de amostra final é realizada em 27 MHz (seqüenciais em 13,5 MHz para luma e 6,75 MHz para cada um dos sinais de diferença de

25 cor). Isto provê linhas não tremidas de saída de dados. Além disso, o demodulador de croma usa um oscilador de tempo discreto digital (DTO) que fica preso ao sinal de rajada de croma que entra para cada um dos sinais que entram.

Todo o processamento de sinal de processamento e digital A/D é realizado usando relógios síncronos apesar do caráter assíncrono inerente destes quatro sistemas de sinalização. Ainda, cada freqüência de sinal de relógio de 5. IC gerado pelo gerador de relógio 54 é igual a ou superior à freqüência de sinal de relógio/amostragem requerida para a própria operação da porção apropriada do circuito/lógica. Esta superamostragem pode ser acomodada para mais adiante no processamento do sinal particular. Os efeitos indesejáveis 10 gerados pela operação síncrona das seções de processador A/D e de sinal podem ser compensados pelas seções de demodulação de croma 102 e 104, e pelos processadores de SRC e sincronização 110 e 112. As técnicas para a remoção de tais efeitos são bem conhecidas àqueles versados na técnica e não 15 serão apresentadas em detalhes no presente documento.

Uma vez que existe apenas um sinal de relógio de referência a partir do qual todas as demais freqüências de amostragem e processamento são geradas, os A/Ds serão capazes de operar com alto desempenho (isto é, com uma 20 precisão de até 10 bits) e terão pouco ou nenhum ruído digital. Isto não será possível com as freqüências de amostragem assíncronas, uma vez que as "zonas silenciosas" necessárias para a amostragem do sinal analógico não mais existem. No entanto, com as múltiplas freqüências de 25 amostragem com base no mesmo relógio, as zonas silenciosas entre as transições digitais são preservadas (vide Figura 3).

Um outro aspecto da presente invenção é o uso duplo de porções do circuito digital para o processamento de sinais de televisão NTSC. A este respeito, faz-se referência à Figura 4, que ilustra um diagrama de bloco do bloco de decodificador DCD 86. O bloco de decodificador DCD 86 realiza todas as funções de processamento de sinal necessárias para os dois sinais de televisão (analógicos) NTSC. O bloco de decodificador DCD 86 inclui filtros de pente duplos 90 e 92 para a separação de luma e croma dos dois sinais de televisão analógicos de entrada que entram para as respectivas chaves de luma e croma 94 e 96. As respectivas chaves de luma e croma 94 e 96 são cada qual sincronizadas em 36 MHz (duas vezes a freqüência requerida de 18 MHz para um único canal) de tal modo que cada um dos componentes de croma e luma do canal seja comutado em cada relógio. Sendo assim, cada canal de 18 MHz é processado em cada ciclo de relógio um sim outro não a 36 MHz.

Os componentes de croma são entrados para os respectivos blocos de demodulação de ACC e croma 102 e 109. Os componentes UV são neste momento encaminhados para os demultiplexadores 98 e 100 a fim de se obter os respectivos componentes U e V separados. As saídas U e V dos módulos de demodulação de croma 102 e 104 (sinais de diferença de cor) são combinadas com as saídas U e V dos respectivos demultiplexadores 98 e 100 nas respectivas chaves UV 106 e 108, que novamente são sincronizadas em 36 MHz (duas vezes a freqüência requerida de 18 MHz para um único canal) de tal modo que cada um dos componentes de croma e luma do canal

seja comutado em cada relógio. Sendo assim, cada canal de 18 MHz é processado em cada ciclo de relógio, um sim, outro não, a 36 MHz.

Os componentes de luma e UV são encaminhados para 5 os respectivos conversores de velocidade de amostra e para os blocos de separação de sinal de sincronização (sync) 110 e 112 a fim de produzir um sinal com uma freqüência de interface padrão. Além disso, o fracionamento de dados de intervalo de bloqueio vertical (VBI) é realizado pelos 10 divisores de dados 114 e 116, nos quais as informações de *closed caption*, as informações de controle parentais de "chip em v", os dados de teletexto, as informações de guia de programa, ou coisa do gênero, são obtidos. As saídas dos respectivos conversores de velocidade de amostra e dos 15 processadores de sincronização 110 e 112, e os respectivos divisores de dados 114 e 116 são entrados para o processador de vídeo 118 a fim de suprir o vídeo de canal principal e o segundo vídeo de canal (auxiliar). O segundo vídeo de canal é tipicamente usado para imagens PIP ou POP. Conforme antes 20 observado, os efeitos indesejáveis de se usar um único relógio de referência são compensados nas seções de demodulação de croma 102 e 104, e nos processadores de SRC e de sincronização 110 e 112.

Com referência à Figura 5, é mostrado um diagrama 25 de bloco, de modo geral designado com a referência numérica 130, da implementação de filtro de pente com um uso duplo da maior parte dos circuitos lógicos do bloco de decodificador DCD 86 de acordo com um aspecto da presente invenção. O

primeiro vídeo compósito de uma freqüência de sincronização ou amostragem de 18 MHz é entrado para um dispositivo de armazenagem de dados 134 que prende uma linha do vídeo e para um filtro de pente 132. Ao mesmo tempo, o segundo vídeo compósito de uma freqüência de sincronização ou amostragem de 18 MHz é entrado para um dispositivo de armazenagem de dados 136 que prende uma linha do vídeo e para o filtro de pente 132. Os dispositivos de armazenagem de dados 134 e 136 são cada qual sincronizados na velocidade de amostragem de 18 MHz. O filtro de pente 132 é sincronizado em duas vezes 18 MHz ou a 36 MHz. Desta maneira, o filtro de pente 132 processa, alternativamente, a saída dos dispositivos de armazenagem de dados 134 e 136.

Sendo assim, ao invés de dois circuitos completamente diferentes, o bloco de decodificador DCD 86 combina os dois canais, duplicando somente os componentes de armazenagem de dados correntes. O bloco de decodificador DCD 86 também usa os mesmos circuitos para a maior parte do processamento ao operar duas vezes os canais de freqüência e de comutação requeridos em cada relógio.

Conquanto a presente invenção tenha sido descrita como tendo um desenho preferido e/ou configuração, a presente invenção pode ser ainda modificada dentro do espírito e âmbito desta apresentação. O presente pedido, portanto, pretende cobrir as partidas desta apresentação conforme adentrem à prática conhecida ou usual da técnica à qual a presente invenção pertence e recaiam nos limites das reivindicações em anexo. Em particular, a presente invenção

é aplicável a outros circuitos nos quais haja pré-requisitos para se operar os sistemas com diferentes exigências de freqüência, nos quais se deseja operar os sistemas/circuitos no mesmo espaço de silício, especialmente os com circuitos 5 A/Ds ou outros circuitos analógicos, além do circuito/lógica digital.

## REIVINDICAÇÕES

1. Aparelho de processamento de sinal, compreendendo:

uma entrada de sinal para o recebimento de um

5 sinal analógico tendo uma característica de sincronização;

um primeiro gerador de relógio para a geração de um sinal de relógio de referência, o sinal de relógio de referência sendo independente da característica de sincronização do sinal analógico;

10 um segundo gerador de relógio, acoplado ao primeiro gerador de relógio, para a produção de uma pluralidade de outros sinais de relógio em resposta ao sinal de relógio de referência; e

uma seção de processamento de sinal, acoplada à

15 entrada de sinal e ao segundo gerador de relógio, para a amostragem e processamento do sinal analógico de acordo com uma velocidade de amostragem e um padrão de sinal apropriado, a seção de processamento de sinal tendo uma pluralidade de conversores analógicos para digitais (A/D)

20 que são sincronizados pelos respectivos sinais dentre a pluralidade de outros sinais de relógio, onde

os conversores A/D são sincronizados pelos respectivos sinais dentre a pluralidade de outros sinais de relógio, os quais são independentes da característica de

25 sincronização do sinal analógico e possuem uma freqüência igual à velocidade de amostragem, por meio do que a corrupção do sinal analógico por parte do ruído digital no aparelho é evitada, sendo que a seção de processamento de

sinal é adaptada no sentido de processar dois sinais analógicos separados, cada um dos dois sinais analógicos separados tendo respectivas características de sincronização, e o sinal de relógio de referência é 5 independente de ambas características de sincronização e

10 **CARACTERIZADO** pelo fato de que a seção de processamento de sinal processa os dois sinais analógicos separados usando um único canal de processamento, o único canal de processamento sendo sincronizado por um outro sinal de relógio que tem uma frequência de sinal de pelo menos duas vezes a velocidade de sincronização requerida e necessária para o processamento de um único sinal dentre os 15 sinais analógicos.

2. Aparelho de processamento de sinal, de acordo com a reivindicação 1, **CARACTERIZADO** pelo fato de que os 20 sinais analógicos são sinais de televisão.

3. Aparelho de processamento de sinal, de acordo com a reivindicação 1, **CARACTERIZADO** pelo fato de que a seção de processamento de sinal é ainda operável no sentido de processar um sinal de entrada digital tendo uma 25 característica de sincronização, e o sinal de relógio de referência é independente da característica de sincronização do sinal de entrada digital.

4. Aparelho de televisão, compreendendo:

25 uma entrada de sinal para o recebimento de um sinal de televisão tendo uma característica de sincronização;

um primeiro gerador de sinal de relógio para a produção de um sinal de relógio de referência que é independente da característica de sincronização do sinal de televisão;

5                   um segundo gerador sinal de relógio, acoplado ao primeiro gerador de sinal de relógio, para a produção de uma pluralidade de outros sinais de relógio em resposta ao sinal de relógio de referência;

10                  um processador de sinal, acoplado à entrada de sinal e ao segundo gerador de sinal de relógio, para a amostragem e processamento do sinal de entrada de acordo com um padrão de sinal apropriado e provendo um sinal de saída adequado para exibição em dispositivo de visor, o processador de sinal incluindo uma pluralidade de 15 conversores analógicos para digitais (A/D) acoplados ao segundo gerador de sinal de relógio; e

uma saída de sinal, acoplada ao processador de sinal, para o recebimento e acoplamento do sinal de saída a um dispositivo de visor, onde

20                  os conversores A/D do processador de sinal são sincronizados pelos respectivos sinais dentre a pluralidade de outros sinais de relógio, que são independentes da característica de sincronização do sinal de entrada, e possuem uma frequência igual à velocidade de amostragem por 25 meio do que a corrupção do sinal analógico por parte do ruído digital no aparelho é evitada, sendo que a seção de processamento de sinal é adaptada no sentido de processar dois sinais analógicos separados, cada um dos dois sinais

analógicos separados tendo respectivas características de sincronização, e o sinal de relógio de referência é independente das características de sincronização e

**CARACTERIZADO** pelo fato de que a seção de 5 processamento de sinal analógico processa os dois sinais analógicos separados usando um único canal de processamento, e o único canal de processamento é sincronizado por um sinal de relógio interno que tem uma frequência de sinal de pelo menos duas vezes a velocidade de sincronização requerida e 10 necessária para o processamento de um único sinal dentre os sinais analógicos.

5. Método para o processamento de sinais de entrada tendo componentes de sincronização, o método compreendendo as etapas de:

15 receber um sinal de entrada tendo um componente de sincronização;

gerar um sinal de relógio de referência, o sinal de relógio de referência sendo independente da característica de sincronização do sinal de entrada;

20 gerar uma pluralidade de outros sinais de relógio com base no sinal de relógio de referência;

converter o sinal de entrada analógico em um sinal digital usando conversores analógicos para digitais (A/D) que são sincronizados usando um sinal dentre a pluralidade 25 de outros sinais de relógio; e

decodificar o sinal digital convertido de acordo com um sinal de televisão apropriado padrão usando o circuito/lógica de decodificação de modo a prover um sinal

de saída adequado para exibição, o circuito/lógica de decodificação sendo sincronizado por pelo menos um sinal dentre a pluralidade de outros sinais de relógio, onde

5 os conversores A/D e o circuito/lógica de decodificação são sincronizados pelos respectivos sinais dentre a pluralidade de outros sinais de relógio, que são independentes da característica de sincronização do sinal de entrada e têm uma frequência igual à velocidade de amostragem, por meio do que a corrupção do sinal analógico 10 por parte do ruído digital é evitada, e

**CARACTERIZADO** pelo fato de que:

a etapa de receber compreende o recebimento de dois sinais de entrada analógicos, cada qual tendo uma respectiva característica de sincronização;

15 a etapa de converter compreende a conversão dos dois sinais de entrada analógicos nos respectivos sinais digitais; e

a etapa de decodificar compreende a decodificação dos dois sinais digitais de modo a prover dois sinais de 20 saída usando um único canal de processamento que é sincronizado por um sinal de relógio interno que tem uma frequência de pelo menos duas vezes a velocidade de sincronização requerida e necessária para o processamento de um único sinal analógico.

25 6. Método, de acordo com a reivindicação 5,

**CARACTERIZADO** pelo fato de que:

a etapa de receber compreende ainda um sinal de entrada digital tendo uma característica de sincronização, e

a etapa de decodificar compreende ainda a decodificação do sinal de entrada digital usando o circuito/lógica de decodificação que é sincronizado por um respectivo sinal dentre os sinais de relógio internos que 5 são independentes da característica de sincronização do sinal de entrada digital.

7. Método, de acordo com a reivindicação 5, **CARACTERIZADO** pelo fato de que:

a etapa de receber compreende o recebimento de um 10 sinal de televisão analógico.

FIG. 1

Fig. 2

FIG. 3

FIG. 4

FIG. 5

## RESUMO

### "DISPOSITIVO DE DIGITALIZAÇÃO E PROCESSAMENTO DE SINAL DE TELEVISÃO ANALÓGICO E DIGITAL"

Um dispositivo de digitalização e processamento de sinal de televisão analógico e digital que realiza a digitalização e processamento de funções usando uma fonte de freqüência de referência comum usada para gerar múltiplos sinais de sub-relógio, no qual a fonte de freqüência de referência é independente de qualquer característica de sincronização do sinal de entrada. Para o processamento de sinal analógico de canal duplo, a fonte de freqüência comum não fica presa a nenhum sinal de canal ou de entrada. O processamento de sinal digital é realizado com base na mesma fonte de freqüência de referência comum. Com vantagem, a presente invenção permite que todos os conversores analógicos para digitais e que o circuito/lógica de decodificação necessários para a digitalização e processamento simultâneos de diversos sinais de televisão analógicos e digitais sejam integrados a um único circuito integrado, como também elimina os circuitos de geração de freqüência duplicados.