(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第3917193号

(P3917193)

(45) 発行日 平成19年5月23日(2007.5.23)

(24) 登録日 平成19年2月16日(2007.2.16)

(51) Int.C1.

F 1

HO3M 3/02 (2006.01)

HO3M 3/02

請求項の数 3 (全 7 頁)

(21) 出願番号 特願平11-516482

(86) (22) 出願日 平成10年8月3日(1998.8.3)

(65) 公表番号 特表2001-505038 (P2001-505038A)

(43) 公表日 平成13年4月10日(2001.4.10)

(86) 國際出願番号 PCT/IB1998/001187

(87) 國際公開番号 WO1999/012264

(87) 國際公開日 平成11年3月11日(1999.3.11)

審査請求日 平成17年8月3日(2005.8.3)

(31) 優先権主張番号 97202657.9

(32) 優先日 平成9年8月29日(1997.8.29)

(33) 優先権主張国 歐州特許庁(EP)

(73) 特許権者

コーニンクレッカ フィリップス エレクトロニクス エヌ ヴィ

オランダ国 5621 ベーアー アインドーフェン フルーネヴアウツウェッハ

1

(74) 代理人

弁理士 杉村 興作

(74) 代理人

弁理士 杉村 純子

(72) 発明者

フアン デル ズワン エリック ユルヘン

オランダ国 5656 アーアー アインドーフェン プロフ ホルストラーン 6

最終頁に続く

(54) 【発明の名称】利得精度を改善したシグマ-デルタ変調器

## (57) 【特許請求の範囲】

## 【請求項 1】

アナログ入力信号をディジタル出力信号に変換するシグマ - デルタ変調器であつて：

- アナログ入力信号に応答して増幅入力信号を供給する第1利得段を具えている入力回路網と；

- 前記増幅入力信号と増幅帰還信号との比較結果に応答して差信号を供給する手段と；

- 前記差信号をろ波し且つろ波した差信号を供給するフィルタリング手段と；

- 前記ろ波した差信号をサンプリングすると共に量子化し、且つディジタル出力信号を供給する出力端子を有している手段と；

- 前記ディジタル出力信号をアナログ帰還信号に変換するディジタル - アナログ変換器及び前記アナログ帰還信号に応答して前記増幅帰還信号を供給する第2利得段を具えている帰還回路網と；

を具えているシグマ - デルタ変調器において、当該シグマ - デルタ変調器がさらに：

- 前記第1利得段と前記第2利得段とを規則に入れ替える交換手段；

を具え、該交換手段が、前記アナログ入力信号及び増幅帰還信号を受信する入力端子を有すると共に前記第1及び第2利得段の各入力端子に結合されて、これらの各入力端子にアナログ入力信号及び増幅帰還信号を規則に入れ替えて供給する出力端子を有している第1スイッチング手段を具えていることを特徴とするシグマ - デルタ変調器。

## 【請求項 2】

前記第1及び第2利得段が、反転出力端子及び非反転出力端子を有する差動トランスコン

10

20

ダクタを具え、前記第1利得段の反転出力端子と、前記第2利得段の非反転出力端子とを第1ノードにて相互接続して、第1減算信号を前記フィルタリング手段に供給し、且つ前記第1利得段の非反転出力端子と、前記第2利得段の反転出力端子とを第2ノードにて相互接続して、第2減算信号を前記フィルタリング手段に供給するようにしたことを特徴とする請求の範囲1に記載のシグマ・デルタ変調器。

### 【請求項3】

前記第1減算信号と、前記第2減算信号とを入れ替える第2スイッチング手段も具えていることを特徴とする請求の範囲2に記載のシグマ・デルタ変調器。

### 【発明の詳細な説明】

本発明は、アナログ入力信号をデジタル出力信号に変換するシグマ・デルタ変調器であ

10

って：

- アナログ入力信号に応答して増幅入力信号を供給する第1利得段を具えている入力回路網と；

- 前記増幅入力信号と増幅帰還信号との比較結果に応答して差信号を供給する手段と；

- 前記差信号をろ波し且つろ波した差信号を供給するフィルタリング手段と；

- 前記ろ波した差信号をサンプリングすると共に量子化し、且つデジタル出力信号を供給する出力端子を有している手段と；

- 前記デジタル出力信号をアナログ帰還信号に変換するデジタル・アナログ変換器及び前記アナログ帰還信号に応答して前記増幅帰還信号を供給する第2利得段を具えている帰還回路網と；

20

を具えているシグマ・デルタ変調器に関するものである。

斯種のシグマ・デルタ変調器は既知であり、1994年にKluwer Academic出版社により出版されたRudy van de Passe著による“Integrated analog-to-digital and digital-to-analog converters”の第11章に記載されている。シグマ・デルタ変調技法は、アナログ入力信号を低分解能で高量子化ノイズを有する量子化手段によってオーバサンプリングして高分解能で、しかも低量子化ノイズのデジタル出力信号に変換する技法である。デジタル信号は同じ低分解能のデジタル・アナログ変換器によってアナログ帰還信号に再変換され、且つ減算段にてアナログ入力信号から差し引かれる。これら2つの信号の差をアナログループフィルタにてろ波して、量子化手段へ供給する。アナログ信号のベースバンド周波数に対して十分に高いループ利得を用いることによって、デジタル出力信号におけるベースバンド内の量子化ノイズを、このベースバンド以上の量子化ノイズが高くなることは犠牲にして、低くするようにする。しかし、デジタルフィルタ技法により、ベースバンド以上のノイズは、例えばオーバサンプリングしたS D Mデジタル出力信号を所望な低いサンプリング速度にて高い分解能の（ビット数が多い）デジタル信号に変換するデシメーティングフィルタによって有効に抑圧することができる。

30

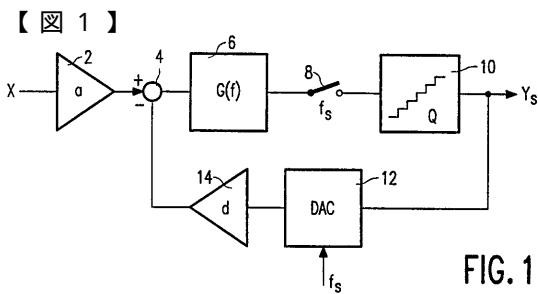

図1はS D Mのブロック図を示す。アナログ入力信号Xは入力回路網にて増幅又はバッファされ、この入力回路網の利得を、利得がaの第1利得段によって示してある。アナログ帰還信号が入力信号から差し引かれ、この差が低域ループフィルタG(f)にてろ波されて、サンプリング速度f<sub>s</sub>にてサンプリングされ、且つ量子化器Qによって量子化される。量子化器の分解能は1ビット又は多ビットとすることができます。帰還回路網では、デジタル出力信号Y<sub>s</sub>が量子化器Qと同じ分解能を有するデジタル・アナログ変換器D A Cによってアナログ帰還信号に再変換される。帰還回路網のアナログ利得を、利得がdの第2利得段として示してある。後に示すように、低周波入力（即ち、サンプリング速度f<sub>s</sub>よりも遙かに小さい周波数）の場合には、信号利得がa / dとなる。量子化ノイズはループフィルタ特性G(f)の逆数によって“整形”される。

40

或る用途、例えば楽器のような用途にとっては、S D Mの正確な利得a / dが重要である。しかし、利得段aとdの利得の不整合により、総合利得が正確でなくなり、所望値からずれてしまい、これらの利得が互いに異なる或るオフセットを含むことになるため、差信号がオフセット及びひずみを有することになる。

本発明の目的は、精度を改善したS D Mを提供することにある。このために、本発明は冒

50

頭にて述べたようなシグマ - デルタ変調器において、当該シグマ - デルタ変調器がさらに：

- 前記第1利得段と前記第2利得段とを規則的に入れ替える交換手段；

を具え、該交換手段が、前記アナログ入力信号及び増幅帰還信号を受信する入力端子を有すると共に前記第1及び第2利得段の各入力端子に結合されて、これらの各入力端子にアナログ入力信号及び増幅帰還信号を規則的に入れ替えて供給する出力端子を有している第1スイッチング手段を具えていることを特徴とする。

第1利得段aと第2利得段dとを規則的に入れ換える（“チョッピング”）ことにより、双方の利得段の差異及び不整合もチョッピング周波数で変調される。双方の利得段の実効値がaとdとの平均値となるため、SDMの利得が正確に単位利得となる。チョッピング周波数で差信号に高周波のリップルが存在するが、チョッピング周波数は当面の関連する周波数帯域以外の周波数に選定することができるため、このようなリップルは無効なものとなる。

10

完全に差動式の回路を用いることにより、好ましくは第1及び第2利得段に差動トランスコンダクタを用いることにより、さらに改善することができる。この場合の入力信号と帰還信号との減算は、トランスコンダクタの互いに反対の差動出力信号を相互接続することによって簡単に行なうことができる。

本発明の上述した特徴及び他の特徴及び利点を添付図面を参照して実施例につき説明して明らかにするに、ここに：

図1は従来のシグマ - デルタ変調器の回路図であり；

20

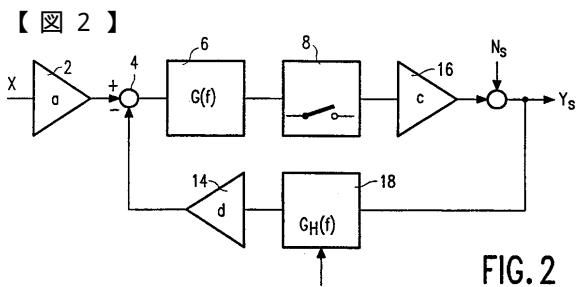

図2は図1のシグマ - デルタ変調器のリニアモデルの回路図であり；

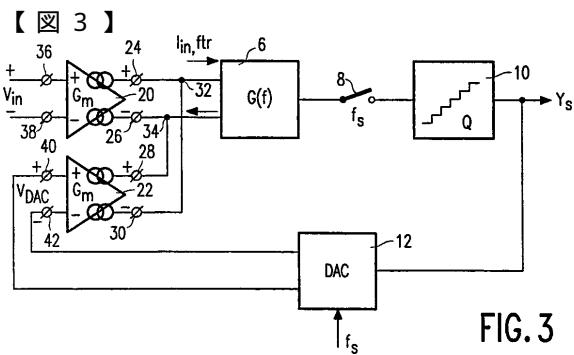

図3は入力回路網及び帰還回路網に完全に差動式のトランスコンダクタを用いる従来のシグマ - デルタ変調器の回路図であり；

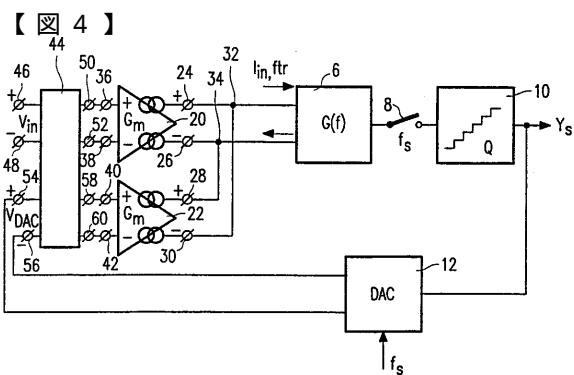

図4は本発明によるシグマ - デルタ変調器の第1実施例の回路図であり；

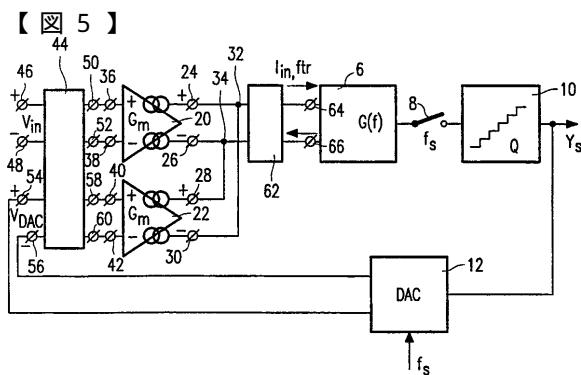

図5は本発明によるシグマ - デルタ変調器の第2実施例の回路図であり；

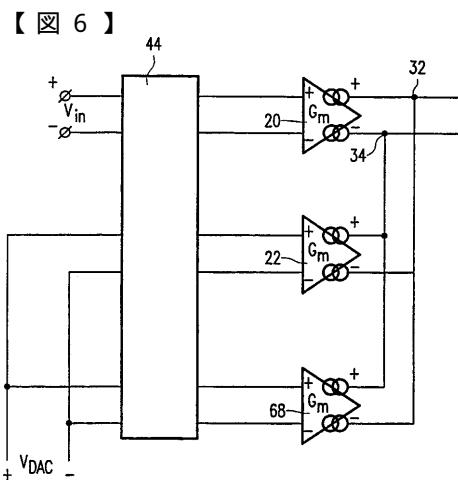

図6は本発明によるシグマ - デルタ変調器の第3実施例の一部を示す回路図である。

図面及び好適実施例の説明では、同じく、又は極めて似ているものに同様な参照記号を用いている。

図1は通常のシグマ - デルタ変調器(SDM)の回路図を示す。アナログ入力信号Xは入力回路網にて増幅されるか、又はバッファされ、この入力回路網の利得を利得がaの第1利得段2によって示してある。減算器4では、増幅又はバッファされた入力信号からアナログ帰還信号が差し引かれ、その差が伝達特性G(f)を有する低域ループフィルタ6にてろ波されて、サンプリング回路8によりサンプリング速度f<sub>s</sub>にてサンプリングされてから、1ビット又は多ビット分解能を有する量子化器10によって量子化されて、デジタル出力信号Y<sub>s</sub>として出力される。帰還回路網では、デジタル出力信号Y<sub>s</sub>が量子化器10と同じ分解能を有するデジタル - アナログ変換器(DAC)12によってアナログ帰還信号に再変換される。帰還回路網のアナログ利得を、利得がdの第2利得段14として示してある。

30

図1のSDMは通常図2に示すようにモデル化される。1ビット又は多ビットの分解能を有することができる量子化器10は、利得がcの利得段16と相加性のホワイトノイズN<sub>s</sub>とによりてモデル化される。帰還DAC12はホールド段18及び利得がdの利得段14としてモデル化することができる。なお、図2のシステムは混合連続 - 時間 / 離散 - 時間システムである。離散 - 時間信号をデジタル出力信号Y<sub>s</sub>及び相加性ノイズN<sub>s</sub>のように指数Sにて示してある。サンプリング回路8は連続 - 時間域からの入力信号を離散 - 時間域の信号に変換する。サンプリング回路の出力信号の周波数スペクトルはサンプリング周波数で繰り返す。ホールド段18の保持機能は、離散 - 時間域からの入力信号を連続 - 時間域の信号に変換する。周波数域における保持機能をsincフィルタG<sub>H</sub>(f)によって示しており、このフィルタはサンプリング周波数f<sub>s</sub>の多数倍の個所にノッチを有する低域通過特性を有する。図2のSDMのデジタル出力信号Y<sub>s</sub>は次のように表わすことができる

40

$$Y_s(f) = \frac{a \cdot c G(f)}{1 + cdG(f)G_H(f)} X(f) + \frac{1}{1 + cdG(f)G_H(f)} \cdot N_s(f) \quad (1)$$

低周波に対して、保持機能  $G_H(f)$  はほぼ単位利得を呈し、しかもループフィルタ  $G(f)$  が低域フィルタであるため、 $c d G(f) >> 1$  であるから、式(1)は次のように単純化される。

$$Y_s(f) \approx \frac{a}{d} X(f) + \frac{1}{dG(f)} \cdot N_s(f) \quad (2)$$

低周波入力、即ちサンプリング速度  $f_s$  よりも遙かに小さい周波数に対しては、信号利得が  $a / d$  となる。ノイズはループフィルタ特性  $G(f)$  の逆数によって「整形」される。

幾つかの用途、例えば楽器の用途にとって、S D M の正確な利得  $a / d$  が重要である。実際にシリコンで実現するのに利得  $a$  と  $d$  の最適な整合を得るために、 $a$  を  $d$  の整数倍としてか、又はその逆として選定するのが賢明である。

図3は、第1利得段2及び第2利得段14を共に等しい相互コンダクタンス  $G_m$  を有する完全に差動式の入力トランスコンダクタ20と、完全に差動式の帰還トランスコンダクタ22とで実現して、S D Mの信号利得が単位利得となるようにする具体例を示す。トランスコンダクタ20は正の入力端子36及び負の入力端子38と、正の出力端子24及び負の出力端子26とを有しており、トランスコンダクタ22は正の入力端子40、負の入力端子42、正の出力端子28及び負の出力端子30を有している。この場合のアナログ入力信号と帰還信号との減算は、第1ノード32にて、入力トランスコンダクタ20の正の出力端子24を帰還トランスコンダクタ22の負の出力端子30に相互接続し、且つ第2ノード34にて、入力トランスコンダクタ20の負の出力端子26を帰還トランスコンダクタ22の正の出力端子28に相互接続することにより簡単に行なうことができる。これにより得られる第1及び第2ノード32及び34を経て流れる差電流がループフィルタ6の入力電流を成し、この入力電流は次のように表わされる。

$$I_{in,fir} = G_m(v_{in} - v_{DAC}) \quad (3)$$

ここに、 $v_{in}$  は入力トランスコンダクタ20の差動入力端子36と38における差分アナログ入力信号であり、 $v_{DAC}$  は帰還トランスコンダクタ22の差動入力端子40と42における差分帰還信号である。

トランスコンダクタ20と22の不整合のために、利得が単位利得からずれたりする。これらの利得は互いに異なる所定のオフセットも含むため、差電流  $I_{in,fir}$  がオフセット及び偶数調波のひずみを有することになる。さらに、トランスコンダクタ20と22との非対称性は、入力トランスコンダクタ20がシングルエンデッドの入力端子を有し（他方の入力端子は基準電圧に接続される）、これに対し、帰還トランスコンダクタ22がそれとは違った方法で用いられる場合にも導入される。これによってもオフセット及び偶数調波ひずみが生成される。

図4は図3と同じ S D M の構成を示すが、これにはスイッチング回路44を拡張させてある。このスイッチング回路44は、差分入力電圧  $v_{in}$  を受電する正の入力端子46及び負の入力端子48と、入力トランスコンダクタ20の正の入力端子36及び負の入力端子38にそれぞれ接続される出力端子50及び52とを有している。スイッチング回路44はさらに、差分帰還電圧  $v_{DAC}$  を受電するための正の入力端子54及び負の入力端子56と、帰還トランスコンダクタ22の正の入力端子40及び負の入力端子42にそれぞれ接続される出力端子58及び60とを有している。

トランスコンダクタ20と22をスイッチング回路又はチョッピング44により規則的に入れ替える（“チョッピング”）ことにより、両トランスコンダクタ間の差をチョッピング周波数で変調させる。双方のトランスコンダクタの相互コンダクタンスの実効値が平均値  $G_{m,a}$  及び  $G_{m,b}$  となるため、S D Mの利得が正確に単位利得となる。差分電流  $I_{in,fir}$  に（チョッピング周波数にて）高周波のリップルがあっても、チョッピング周波数を当面の関連する周波数帯域以外の周波数に選定して、斯かるリップルを無効なものとすることができます

10

20

30

40

50

。減算を行なう必要があるから、トランスコンダクタ 2 0 及び 2 2 の出力端子は図 3 に示したと同じように交差結合させる。

差分電流  $I_{in, ftr}$  の正しい位相を維持するために、チョッピングは次のように行わなければならない。

- チョッピングクロック周期の第 1 半部の期間中は、正の入力端子 4 6 が出力端子 5 0 に接続され、負の入力端子 4 8 が出力端子 5 2 に接続され、正の入力端子 5 4 が出力端子 5 8 に接続され、且つ負の入力端子 5 6 が出力端子 6 0 に接続されるようにする。

- チョッピングクロック周期の第 2 半部の期間中には、正の入力端子 4 6 が出力端子 6 0 に接続され、負の入力端子 4 8 が出力端子 5 8 に接続され、正の入力端子 5 4 が出力端子 5 2 に接続され、且つ負の入力端子 5 6 が出力端子 5 0 に接続されるようにする。 10

オフセット及び偶数調波ひずみ並びにフリッカーノイズを低減させるために、チョッピングプロセスはノード 3 2 及び 3 4 とループフィルタ 6 の入力端子 6 4 及び 6 6 との間に第 2 チョッパ 6 2 を付加することによって拡張させることができる。これを図 5 に示してある。第 2 チョッパ 6 2 はトランスコンダクタ 2 0 及び 2 2 の減算出力信号を入れ替える。差分電流  $I_{in, ftr}$  の正しい位相を維持するために、この場合には、チョッピングを次のように行わなければならない。

- チョッピングクロック周期の第 1 半部の期間中は、正の入力端子 4 6 が出力端子 5 0 に接続され、負の入力端子 4 8 が出力端子 5 2 に接続され、正の入力端子 5 4 が出力端子 5 8 に接続され、且つ負の入力端子 5 6 が出力端子 6 0 に接続され、さらに、第 2 チョッパ 6 2 によって、第 1 ノード 3 2 が入力端子 6 4 に接続され、且つ第 2 ノード 3 4 が入力端子 6 6 に接続されるようにする。 20

- チョッピングクロック周期の第 2 半部の期間中には、正の入力端子 4 6 が出力端子 5 8 に接続され、負の入力端子 4 8 が出力端子 6 0 に接続され、正の入力端子 5 4 が出力端子 5 0 に接続され、且つ負の入力端子 5 6 が出力端子 5 2 に接続され、さらに、第 2 チョッパ 6 2 によって、第 1 ノード 3 2 が入力端子 6 6 に接続され、且つ第 2 ノード 3 4 が入力端子 6 4 に接続されるようにする。帰還トランスコンダクタ 2 2 に並列に、同じ相互コンダクタンス  $G_m$  を有する 1 個以上のトランスコンダクタをさらに付加することによって、単位利得以外の総合利得を得ることができる。図 6 は第 2 の帰還トランスコンダクタ 6 8 を付加した例を示す。トランスコンダクタ 2 2 と 6 8 の対応する出力端子を相互接続するため、帰還回路網での総合相互コンダクタンスは  $2 G_m$  となる。両トランスコンダクタ 2 2 及び 6 8 は D A C 1 2 から差分帰還電圧  $V_{DAC}$  を受電する。スイッチング回路 4 4 は差分帰還電圧  $V_{DAC}$  に接続される別の組の正及び負の入力端子と、第 2 帰還トランスコンダクタ 6 8 の入力端子に接続される別の組の出力端子とで拡張される。この際、チョッピング期間は、3 つのトランスコンダクタ 2 0 , 2 2 及び 6 8 が循環的に入れ替わる 3 つの期間に分けられる。入力トランスコンダクタ 2 0 に並列に 1 個以上のトランスコンダクタを加えることができる。 30

FIG.1

FIG.2

FIG.3

FIG.4

FIG.5

FIG.6

---

フロントページの続き

(72)発明者 デイクマンス アイス カレル

オランダ国 5656 アーアー アインドーフェン プロフ ホルストラーン 6

審査官 高野 洋

(56)参考文献 特開平08-265158(JP,A)

特開平05-160735(JP,A)

特開平08-154058(JP,A)

特開平09-186601(JP,A)

特開平08-256059(JP,A)

国際公開第97/026708(WO,A1)

特開平02-226818(JP,A)

特開平06-177769(JP,A)

(58)調査した分野(Int.Cl., DB名)

H03M 3/02