(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第6226839号

(P6226839)

(45) 発行日 平成29年11月8日(2017.11.8)

(24) 登録日 平成29年10月20日(2017.10.20)

(51) Int.Cl.

F 1

|              |           |             |        |      |

|--------------|-----------|-------------|--------|------|

| HO1L 21/336  | (2006.01) | HO1L 29/78  | 29/78  | 301X |

| HO1L 29/78   | (2006.01) | HO1L 29/78  | 29/78  | 301G |

| HO1L 21/8238 | (2006.01) | HO1L 29/78  | 29/78  | 301S |

| HO1L 27/092  | (2006.01) | HO1L 27/092 | 27/092 | G    |

| HO1L 29/49   | (2006.01) | HO1L 29/58  | 29/58  | G    |

請求項の数 13 外国語出願 (全 23 頁) 最終頁に続く

(21) 出願番号

特願2014-183997 (P2014-183997)

(22) 出願日

平成26年9月10日 (2014.9.10)

(65) 公開番号

特開2015-73095 (P2015-73095A)

(43) 公開日

平成27年4月16日 (2015.4.16)

審査請求日

平成29年3月14日 (2017.3.14)

(31) 優先権主張番号

14/045,680

(32) 優先日

平成25年10月3日 (2013.10.3)

(33) 優先権主張国

米国(US)

早期審査対象出願

(73) 特許権者 512144771

エーエスエム アイピー ホールディング

ビー. ブイ.オランダ国 1322 エーピー アルメ

ーレ フェルステルケルシュトラート 8

(74) 代理人 100118256

弁理士 小野寺 隆

(72) 発明者 シエ チー

オランダ国 1322 エーピー アルメ

ーレ フェルステルケルシュトラート 8

(72) 発明者 マチカウトサン ヴラジーミル

オランダ国 1322 エーピー アルメ

ーレ フェルステルケルシュトラート 8

最終頁に続く

(54) 【発明の名称】ワイヤーベース半導体装置を製造する方法

## (57) 【特許請求の範囲】

## 【請求項 1】

電子デバイスを製造する方法であって、

トランジスタを形成するステップを備え、前記トランジスタを形成するステップは、

半導体基板に層のスタックを形成するステップであって、前記スタックは、

第1の誘電体層と、

前記第1の誘電体層に亘る第1のスペーサ層と、

前記第1のスペーサ層に亘る第2の誘電体層と、

前記第2の誘電体層に亘る第2のスペーサ層と、

前記第2のスペーサ層に亘る第3の誘電体層と、

を備える、ステップと、

前記スタックを貫通する垂直に延びるホールをエッティングするステップと、

前記ホールを半導体で充填するステップと、

前記第1の誘電体層の少なくとも一部を選択的に除去し、前記第1のスペーサ層の直

下に延びる第1の埋め込み空間を形成するステップと、

前記第1の埋め込み空間を導体で充填し、下部ソース/ドレインコンタクトを形成す

るステップと、

前記第2の誘電体層の少なくとも一部を選択的に除去し、前記第2のスペーサ層の直

下に延びる第2の埋め込み空間を形成するステップと、

前記第2の埋め込み空間を導体で充填し、ゲートを形成するステップと、

10

20

を備える方法。

【請求項 2】

前記第3の誘電体層の少なくとも一部を選択的に除去し、第3の埋め込み空間を形成するステップと、

前記第3の埋め込み空間を導体で充填し、上部ソース／ドレインコンタクトを形成するステップと、を更に備える請求項1に記載の方法。

【請求項 3】

前記第2の埋め込み空間を導体で充填する前に、前記第2の埋め込み空間を誘電体層でライニングするステップを更に備える請求項2に記載の方法。

【請求項 4】

前記第1の誘電体層を選択的に除去することは、前記ホールにおける前記半導体を露出し、前記第1の埋め込み空間を充填する導体は、前記半導体に接触する請求項3に記載の方法。

10

【請求項 5】

前記第3の誘電体層を選択的に除去することは、前記ホールにおける前記半導体を露出し、前記第3の埋め込み空間を充填する導体は、前記半導体に接触する請求項4に記載の方法。

【請求項 6】

前記第1の埋め込み空間を充填する導体、前記第2の埋め込み空間を充填する導体及び前記第3の埋め込み空間を充填する導体は、同一平面の部分を規定するためにそれぞれ上部に延びる請求項2に記載の方法。

20

【請求項 7】

前記ホールは、15nm以下の直径を有する請求項1に記載の方法。

【請求項 8】

前記ホールを半導体で充填した後に、前記ホールにおける前記半導体をドープするステップを更に備える請求項1に記載の方法。

【請求項 9】

電子デバイスを製造する方法であって、

トランジスタを形成するステップを備え、前記トランジスタを形成するステップは、

前記トランジスタのチャネル領域を形成するステップであって、前記チャネル領域は、ワイヤによって規定される、ステップと、

30

前記トランジスタのソース／ドレインコンタクトを形成するステップであって、

第1の埋め込み空間を形成するステップと、

前記第1の埋め込み空間を第1の誘電体層でライニングするステップと、

前記第1の埋め込み空間を第1の導体で充填するステップと、を含むステップと、

前記トランジスタのゲートコンタクトを形成するステップであって、

前記第1の誘電体層により前記第1の導体から隔てられる第2の埋め込み空間を形成するステップと、

前記第2の埋め込み空間を第2の導体で充填するステップと、を含むステップと、を備え、

40

前記第2の埋め込み空間を充填する前に、前記第2の埋め込み空間を第2の誘電体層でライニングするステップを更に備え、

前記第2の誘電体層は、前記第1の誘電体層よりも高い誘電定数を有する、方法。

【請求項 10】

前記第1の埋め込み空間を前記第1の誘電体層でライニングするステップは、前記第1の埋め込み空間の垂直に延びる側壁を誘電体でライニングするステップを含む請求項9に記載の方法。

【請求項 11】

電子デバイスを製造する方法であって、

トランジスタを形成するステップを備え、前記トランジスタを形成するステップは、

50

前記トランジスタのチャネル領域を形成するステップであって、前記チャネル領域は、ワイヤによって規定される、ステップと、

前記トランジスタのソース／ドレインコンタクトを形成するステップであって、

第1の埋め込み空間を形成するステップと、

前記第1の埋め込み空間を第1の誘電体層でライニングするステップと、

前記第1の埋め込み空間を第1の導体で充填するステップと、を含むステップと、

前記トランジスタのゲートコンタクトを形成するステップであって、

前記第1の誘電体層により前記第1の導体から隔てられる第2の埋め込み空間を形成するステップと、

前記第2の埋め込み空間を第2の導体で充填するステップと、を含むステップと、

前記トランジスタの他のソース／ドレインコンタクトを形成するステップであって、

第3の埋め込み空間を形成するステップと、

前記第3の埋め込み空間を第3の導体で充填するステップと、を含むステップと、を備える方法。

#### 【請求項 1 2】

前記第1の導体、前記第2の導体及び前記第3の導体は、同一の金属を含む請求項11に記載の方法。

#### 【請求項 1 3】

前記第1の導体、前記第2の導体及び前記第3の導体は、遷移金属窒化物を含む請求項12に記載の方法。

10

20

#### 【発明の詳細な説明】

##### 【技術分野】

##### 【0001】

本発明は、半導体工程に関するものであり、特に、トランジスタのような半導体装置の形成に関するものである。

##### 【背景技術】

##### 【0002】

集積回路用の演算能力を増加させる継続的な需要のために、集積回路を形成する半導体装置の密度は、継続的に増加している。これらのより高密度なデバイスを製造するために、半導体装置のサイズは、継続的に減少されている。

30

##### 【発明の概要】

##### 【発明が解決しようとする課題】

##### 【0003】

トランジスタは、このようなデバイスの一例である。しかし、トランジスタがより小さくなると、様々な問題が生じる。例えば、トランジスタのサイズを小さくすることにより、構成されるフィーチャーのサイズが小さくなる。その結果、デバイスの信頼性のある動作を実現するために、トランジスタが晒される電圧は、減少する。トランジスタの閾値電圧も同様に減少する。トランジスタを動作するために使用可能な電圧振幅の大きさも減少し、トランジスタを完全に“オフ”にすることを困難にする。よって、トランジスタの継続的な微細化は、望まれないリーク電流を増加させる一因となっている。

40

##### 【0004】

したがって、デバイスサイズの継続的な減少を容易にする半導体装置構造及び製造方法の継続的な需要が存在する。

##### 【課題を解決するための手段】

##### 【0005】

一態様の例では、半導体装置を製造する方法を提供する。前記方法は、単結晶シリコン基板を提供するステップを備える。スペーサ層によって隔てられる3つの酸化物層を含む層のスタックは、基板に亘って形成される。垂直ナノワイヤホールは、単結晶基板へスタックダウンでエッチングされる。エピタキシャルプロセスを用いてナノワイヤホールを充

50

填することにより、ナノワイヤは、形成される。

【0006】

別の態様の例では、半導体装置を製造する方法を提供する。前記方法は、シリコン基板を提供するステップを備える。誘電体スタックは、前記基板に形成され、誘電体スタックは、複数の誘電体層を備える。隣接する誘電体層は、隣接する誘電体層とは異なる材料で形成されるスペーサ層によって隔てられる。垂直に延びるホールは、誘電体スタックを通じて形成される。前記ホールは、エピタキシャル堆積を行うことによって充填され、ホールを充填する材料は、ワイヤを形成する。

【図面の簡単な説明】

【0007】

10

本発明のこれら及び他の特徴を好ましい実施形態の図面を参照して記載するが、それらは本発明を例示するためであり、本発明を限定するものではない。図面は必ずしも縮尺通りではない。また、同一の数字は、全体を通じて同一の部材を示す。

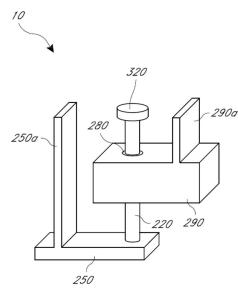

【図1】図1は、垂直なワイヤ-ベーストランジスタの斜視図の例である。

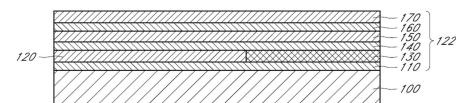

【図2A】図2Aは、基板の概略断面図である。

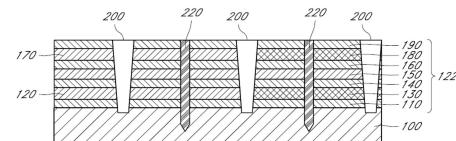

【図2B】図2Bは、誘電体スタックの一部を形成するためにエッチストップ及び誘電体層を形成した後の図2Aの基板の概略断面図である。

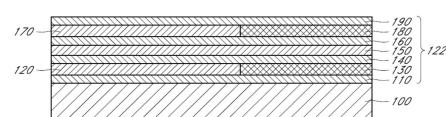

【図3】図3は、誘電体層の一部を、異なるドーピングがされた誘電体で置換した後の図2Bの基板の概略断面図である。

【図4】図4は、誘電体スタックの追加部分を形成するためにスペーサ層及び追加誘電体層を形成した後の図3の基板の概略断面図である。

20

【図5】図5は、誘電体スタックの追加部分を形成するために追加スペーサ層及び追加誘電体層を形成した後の図4の基板の概略断面図である。

【図6】図6は、誘電体層の一部を異なるドーピングがされた誘電体で置換し、追加スペーサ層を堆積した後の図5の基板の概略断面図である。

【図7A】図7Aは、側面エッチストップを形成した後の図6の基板の概略断面図である。

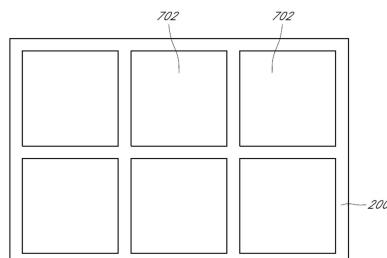

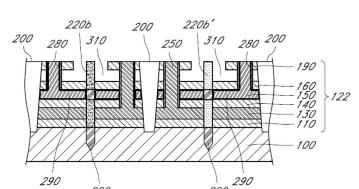

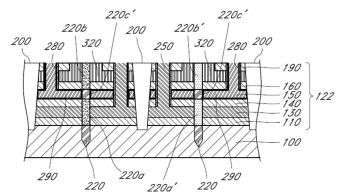

【図7B】図7Bは、図7Aの構造の概略的なトップ-ダウンビューである。

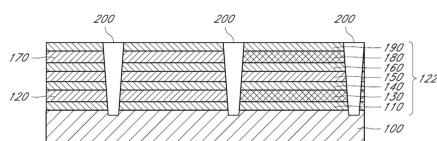

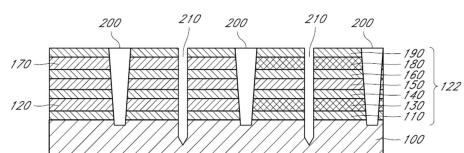

【図8】図8は、誘電体スタックに開口をエッチングした後の図7A及び7Bの構造の概略断面図である。

30

【図9】図9は、垂直に延びるワイヤを形成するために誘電体スタックにおいて開口を形成した後の図8の構造の概略断面図である。

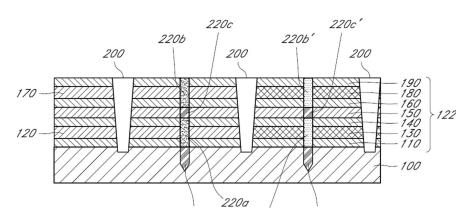

【図10】図10は、誘電体スタックにおいて開口を充填する材料をドーピングした後の図9の構造の概略断面図である。

【図11】図11は、下部コンタクトを規定するための開口を形成した後の図10の構造の概略断面図である。

【図12】図12は、下部コンタクトを規定するための開口をライニングした後の図11の構造の概略断面図である。

【図13】図13は、開口の底部においてライナーを除去した後の図12の構造の概略断面図である。

40

【図14】図14は、露出された誘電体層の一部を除去した後の図13の構造の概略断面図である。

【図15】図15は、下部コンタクトを形成するために導電材料で、埋め込み開口空間を充填した後の図14の構造の概略断面図である。

【図16】図16は、ゲートを規定するための開口を形成した後の図15の構造の概略断面図である。

【図17】図17は、ライナーで開口を内張りした後の図16の構造の概略断面図である。

【図18】図18は、ライナーの底部をエッチングした後の図17の構造の概略断面図である。

50

【図19】図19は、開口によって露出された誘電体層の一部を除去した後に形成される埋め込み開口空間を示す図18の構造の概略断面図である。

【図20】図20は、埋め込み開口空間において誘電体ライナーを形成した後の図19の構造の概略断面図である。

【図21】図21は、ゲートを形成するために導電材料で埋め込み開口空間を充填した後の図20の構造の概略断面図である。

【図22】図22は、上部コンタクトを規定するための開口を形成した後の図21の構造の概略断面図である。

【図23】図23は、埋め込み開口空間を形成するために開口によって露出された誘電体層の一部を除去した後の図22の構造の概略断面図である。

【図24】図24は、上部コンタクトを形成するために導電材料で埋め込み開口空間を充填した後の図23の構造の概略断面図である。

【図25】図25は、図24の構造の概略的な断面トップダウンビューである。

【発明を実施するための形態】

【0008】

トランジスタスケールが、25nm以下（例えば、15nm以下又は10nm以下）の限界寸法（critical dimensions）を下回ると、次第に短くなるチャネル長を通じて流れる電流は、制御がより困難になり、高い密度は、トランジスタと電気的に接触するためのスペースを減少させてしまう。その結果、トランジスタ電気的な振る舞いは、低下し、製造の信頼性及びトランジスタへのコンタクトの形成が困難になる。

【0009】

ワイヤの複数の側面を包囲する又はワイヤの複数の側面に延びるゲートを有する垂直なワイヤ-ベーストランジスタは、優れたトランジスターアーキテクチャを提供する。図1は、垂直なワイヤ-ベーストランジスタ10の概略的な斜視図の一例である。ドープされた半導体材料のワイヤ220は、チャネル領域を形成し、その周囲のゲート290は、導電材料によって形成される。ワイヤ220及びゲート290は、ゲート誘電体280によって隔てられる。図示されるように、ゲート290は、ゲートコンタクトを形成するために上部に延びる部位290aを有する。図示されるように、ゲートは、ワイヤ220の周辺部の周りに完全に広がることが好ましい。下部コンタクト250は、ワイヤ220の下端との電気的な接触を提供する。下部コンタクト250は、下部コンタクトとの電気的な接触を形成するための上部に延びる部位250aを有する。上部コンタクト320は、ワイヤ220の上端との電気的な接触を提供する。下部コンタクト250及び上部コンタクト320は、ソース/ドレインコンタクトとして機能することが理解されるであろう。本明細書で用いられているように、用語「ワイヤ（wire）」は、細長い導電体又はその幅よりも長い長さを有する半導電性構造であることも理解されるであろう。ワイヤの長さに対して垂直な断面で見られるように、断面形状は、任意の形状であってもよい。いくつかの実施形態では、断面形状は円形である。

【0010】

図1をさらに参照すると、垂直に延びるワイヤは、ゲートが横方向に延びる従来のデバイスで使用可能なものよりも長いチャネルを提供することができる一方で、小さなフットプリントも提供し、これは、従来のデバイスと同じか又は小さい。ワイヤの複数の側面を包囲する又はワイヤの複数の側面に沿って延びるゲートと組み合わせることで、これらの垂直なデバイスは、電流フローの改善された制御を提供することができる。また、垂直に延びるワイヤは、コンタクトを形成するためにワイヤに隣接するより大きな面積を残すことができ、それにより、これらのトランジスタを含む集積回路の他のデバイスとの信頼性のある接続を容易にする。

【0011】

本明細書で記載される一部の実施形態では、一般的な、垂直に延びる、ワイヤ-ベースのデバイスを形成するための方法を提供する。誘電体層のスタックは、基板に亘って形成されるスペーサ層によって隔てられる。一部の実施形態では、2又はそれ以上、又は3又

10

20

30

40

50

はそれ以上の誘電体層は、誘電体層を隔てるスペーサ層により、提供される。誘電体層は、各スペーサ層の上部又は下部に配置されてもよい。垂直に延びる開口は、誘電体層に形成され、開口は、垂直に延びるワイヤを形成するために充填される。一部の実施形態では、エピタキシャル堆積によって充填がなされる。ワイヤへの上部及び／又は下部コンタクトは、誘電体層の一部、隣接するワイヤの上部及び／又は下部の一部を、導電性材料で置換することにより形成される。導電性材料では、誘電体スタックの上面に延びる開口を塞ぎ、それにより、その表面での電気的な接触を形成する。3又はそれ以上の誘電体が提供される場合、ワイヤの中間部に隣接する誘電体層も導電性材料で置換されてもよく、これは、誘電体層の上面へ延び、電気的な接触を形成する。この中間コンタクト構造は、誘電体によってワイヤから隔てられ、トランジスタゲートとして機能する。

10

#### 【0012】

一部の実施形態では、ワイヤは、ドライブ-イン アニール (drive-in anneal) 時に、隣接するドープされた誘電体領域からワイヤへドーパントを打ち込むことによりドープされてもよい。他の一部の実施形態では、ワイヤは、成膜直後 (as-deposited) にドープされてもよい。

#### 【0013】

ワイヤによって形成されるデバイスは、誘電体材料で充填される、横方向分離トレンチを用いて他のデバイスから横方向（水平方向）に分離され、横方向のエッチストップ及び分離壁を形成してもよい。横方向のエッチストップは、デバイスが収容される分離セルを個別に規定する。一部の実施形態では、横方向のエッチストップは、材料の複数の層を含んでもよい。例えば、ライナーは、横方向のエッチストップの外壁を形成し、本明細書で説明される誘電体層のエッチングに用いられるエッチング液に耐性があつてもよい。横方向のエッチストップ内部は、別の誘電体で形成されてもよい。

20

#### 【0014】

セルに隣接するトランジスタは、P-MOS及びN-MOS構造を含む相補型金属酸化物半導体 (complementary metal oxide semiconductor (CMOS)) 構造を形成してもよい。一部の実施形態では、P-MOS及びN-MOS構造のそれぞれのワイヤは、異なる半導体材料で形成されてもよい。

#### 【0015】

各種のコンタクト及びトランジスタゲートを含む、本明細書に記載される各種の層及び材料は、原子層堆積 (atomic layer deposition (ALD)) によって堆積されてもよいことが理解されるであろう。本明細書で説明される各種のALDに対して、堆積される基板表面は、堆積サイクルで、互いに反応する前駆体に交互に露出されてもよく、堆積サイクルは、反応生成物の層（例えば、単層 (monolayer)）を形成するために、堆積面で第1の前駆体を吸収し、その後、第2の互いに反応する前駆体による、吸収された前駆体の反応を含む。サイクルは繰り返され、単層は、堆積された材料が所望の厚さに到達するまで互いに堆積される。一部の実施形態では、基板を収容する堆積チャンバへ一時的に分離したパルスで前駆体を流すことによって、交互の露出がなされる。他の一部の実施形態では、チャンバへの前駆体の流れの停止及び開始によって異なる時間で堆積チャンバへ前駆体をパルスすることなく、基板及び／又はリアクタ部材の移動によって、交互の露出がなされる。各堆積サイクルは、第1及び第2の前駆体に加えて、他の反応種を含むことができる事が理解されるであろう。他の一部の実施形態では、堆積サイクルで用いられる前駆体は、時間で変化してもよい。

30

#### 【0016】

本明細書で説明されるように、一部の実施形態では、ワイヤ-ベースデバイスは、トランジスタのような半導体装置である。上部及び下部コンタクトは、ソース／ドレインコンタクトとして機能することができ、中間導電材料は、誘電体によってワイヤから隔てられることができ、ゲートとして機能することができる。他の一部の実施形態では、誘電体層の一又はそれ以上は、省略されてもよく、又は一又はそれ以上の誘電体層の置換は、省略されてもよい。このような場合、前記方法は、ワイヤの上部及び／又は下部にコンタクト

40

50

を有する垂直に延びる導電性又は半導電性ワイヤを有する他のデバイスを形成するために適用されてもよい。

【0017】

上記で述べたように、有利には、前記方法によって形成されるデバイスは、小さな領域以外を塞ぐ一方で、デバイスによって塞がれる領域の大部分をコンタクトの形成に用いることが可能となる。これは、デバイスとコンタクトの形成されやすさ及びデバイスの最終的な信頼性を改善することができる。例えば、一部の実施形態では、トランジスタは、約25nm以下、約15nm以下又は約10nm以下の限界寸法を有するセルを占有してもよい。また、トランジスタが形成される実施形態では、ゲートは、ワイヤの複数の側面に形成されてもよく、又はワイヤの周辺部を完全に取り囲んで形成されてもよい。このような配置は、ワイヤを通じる電流フローの制御を改善することができる。また、本明細書で説明されるように、各コンタクト及びゲートは、誘電体によって隔てられた、異なるレベルで形成されることができる。誘電体は、エッチャントへ露出及びこのような露出によって生じる変更及び損傷から、ゲートを含む他の以前に形成された構造を有利に保護してもよい。

10

【0018】

ここで図2Aを参照すると、基板100の模式的な断面図が示される。基板100は、例えば、半導体ウェーハのような（単体、又は半導体ウェーハ上又はその下に形成される材料を含む他の材料とのアセンブリにおける）バルク半導体材料及び（例えば、他の材料とのアセンブリにおける）半導体材料層を含む、半導体材料を含む半導体基板であってよい。一部の実施形態では、基板は、シリコンウェーハを含む。基板は、アイソレーション構造、ドープ領域及び/又は同一又は他のレベルの電子デバイスのような各種の特徴を含むことが理解されるであろう。

20

【0019】

一部の実施形態の第1の段階では、誘電体スタックは、基板100に形成されてもよい。図2Bは、誘電体スタック122の一部を形成するためにエッチストップ層110及び誘電体層120を形成した後の図2Aの構造の概略的な断面図である。本明細書の文脈では、用語「層（layer）」は、特段の指示がない限り、单一又は複数の両方を含する。層は、下にある基板の一部又は全部を覆ってもよい。

【0020】

30

図2Bを続けて参照すると、エッチストップ層110は、誘電体層120を除去するために後に用いられるエッティング液に耐性のある材料で形成されてもよい。例えば、エッチストップ層110は、シリコン窒化物で形成されてもよく、誘電体層120は、シリコン酸化物で形成されてもよい。層110及び120のそれぞれは、例えば、化学気相堆積（CVD）プロセス又は原子層堆積（ALD）プロセスのような気相前駆体を用いる堆積プロセスによって堆積されてもよい。このようなプロセス、特に、ALDプロセスは、約25nm以下の限界寸法のような微細な電子デバイス向けに望まれる厚さで均一かつコンフォーマルな層を形成する利点を有することができる。

【0021】

一部の実施では、誘電体層120は、例えば、燐、砒素、アンチモン、ボロン、ゲルマニウム又はインジウムでドープされてもよい。一部の実施では、ドーパントは、ボロンのようなp型ドーパントである。ドーパントは、例えば、ドーパント種のイオン注入又はガス状ドーパント種の拡散によって誘電体層120に組み込まれてもよいことが理解されるであろう。

40

【0022】

一部の他の実施形態では、ドーパントは、層が形成された成膜直後（as-deposited）に誘電体層120へ組み込まれてもよい。例えば、誘電体層120は、基板が、異なる時間で、交互かつ順次2又はそれ以上の前駆体に露出される原子層堆積時にドープされてもよい。交互の前駆体は、層120を形成する化合物のための前駆体を含み、ドーパント前駆体も含む。堆積サイクルは、少なくとも一度、基板を各前駆体に実質的に単

50

独で露出することを含む。複数の堆積サイクルは、所望の総厚に到達するまで、堆積された層のビルトアップするように行われる。基板は、また、堆積サイクル時に、酸素、窒素、アルゴン、ヘリウム、水素又はフッ素プラズマのようなプラズマに露出されてもよい。一部の実施形態では、各種のドーパントプロファイルは、いくつかの堆積サイクルのみにおいて基板をドーパントに露出することにより、層120内に形成されることができる。例えば、層120の上部及び下部サブレイヤーを形成する堆積サイクルは、ドーパント前駆体を除外してもよく、それにより、これらの層をドーパントフリーで形成することができる。これらのドーパントフリーサブレイヤーは、層120にドーパントを封入することを目的としており、下部及び覆っている層へ所望のドーパント拡散を低減してもよい。

## 【0023】

10

誘電体層120の一部は、相補型金属酸化物半導体(CMOS)構造を形成するために反対の型にドープされた誘電体層によって置き換えられてもよい。図3は、異なるドープがなされた誘電体層で誘電体層の一部を置換した後の図2Bの構造の概略的な断面図である。一部の実施形態では、誘電体層120の一部は、除去されてもよく、別の誘電体層は、層120の除去された部分を置き換えるために堆積され、他の誘電体層は、層120とは反対の型でドープされた誘電体層130を形成するようにドープされる。層120の一部を除去することは、層120に亘ってマスクをパターニングすることによって実行され、層120のマスク保護部分が維持される一方で、層120の露出される部分は、除去される。例えば、層120がシリコン酸化物で形成されるフッ化炭素エッチングのような、層120を形成する材料のためのエッチング選択は、層120の露出された部分を選択的に除去するように実行されてもよい。誘電体層130は、層120が除去された領域に順次堆積されてもよい。誘電体層130は、層120に対して反対の型でドープされる。層120と同様に、誘電体層130は、成膜直後(as-deposited)にドープされてもよく、又は当該層の堆積後にドープされてもよい。層120がp型のドーパントを含む場合、層130は、燐のようなn型ドーパントでドープされてもよい。一部の実施形態では、層120及び130は、異なる材料で形成されてもよく、これは、同一のエッチング化学物質を層120及び130の両方のエッチングのために用いられることを可能にすることにより、エッチングプロセスのような後の処理に利点を提供してもよい。層130を形成する材料は、そのように形成される層130の後に層120に亘って広がってもよいことが理解されるであろう。化学機械研磨(CMP)プロセスは、下部構造の形成のために水平面を形成するに行われてもよい。

20

## 【0024】

30

誘電体スタック122の形成は、材料の追加の層の形成を継続する。図4は、スペーサ層140及び追加誘電体層150を形成した後の図3の構造の概略的な断面図である。スペーサ層140は、誘電体層120及び130の材料とは異なり、かつ誘電体層120及び130を除去するためのエッチングに耐性がある材料で形成されてもよい。一部の実施形態では、スペーサ層140は、誘電体材料で形成され、スペーサ層140は、エッチストップ層110を形成する材料と同一材料であってもよい。例えば、スペーサ層140は、シリコン窒化物で形成されてもよい。一部の実施形態では、誘電体層150は、シリコン酸化物で形成されてもよい。層140及び150の一方又は両方は、例えば、CVD又はALDによって形成されてもよいことが理解されるであろう。また、誘電体スタック122の様々な層は、説明の簡素化のために、スペーサ層及び誘電体層と呼ばれてもよいことが理解されるであろう。しかし、スペーサ層及び誘電体層のいずれも誘電体材料で形成されてもよい。

40

## 【0025】

本明細書にさらに説明されるように、誘電体層150の厚さは、誘電体スタック122形成されるトランジスタにおけるチャネルの長さを決定してもよい。一部の実施形態では、誘電体層150の厚さは、約3-30nm、約3-15nm又は約3-10nmである。一部の実施形態では、誘電体層150は、ALDによって堆積され、ALDは、膜厚の

50

特別に優れた制御を提供することができ、よって、この厚さによって定義されるチャネル長を制御することができる。

【0026】

追加の層は、誘電体スタック 122 に順次追加されてもよい。図 5 は、誘電体スタック 122 の追加部分を形成するために追加スペーサ層 160 及び追加誘電体層 170 を形成した後の図 4 の構造の概略的な断面図である。スペーサ層 160 及び誘電体層 170 は、それぞれ、本明細書で説明される層 140 及び 150 と同様に形成されてもよい。一部の実施形態では、スペーサ層 160 及び 140 は、同一材料で形成されてもよい、及び／又は誘電体層 150 及び 170 は、同一材料で形成されてもよい。

【0027】

一部の実施形態では、誘電体層 170 は、ドープされてもよい。例えば、誘電体層 170 は、誘電体層 120 と同様にドープされてもよく、例えば、ボロンのような p 型のドーパントを含んでもよい。層 120 と同様に、ドーピングは、イオン注入、ガス状ドーパント種の拡散のような各種のプロセス、及び／又は誘電体層 170 が堆積されるときのドーパントの取り込みによってなされてもよい。

【0028】

誘電体スタック 122 は、追加層を順次増加させてもよい。図 6 は、誘電体層の一部を異なるドープがなされた誘電体層 180 で置換し、追加スペーサ層 190 を順次堆積した後の図 5 の構造の概略的な断面図である。ドープされた誘電体層 180 は、ドープされた誘電体層 130 と同様に形成されてもよい。例えば、層 170 の一部は、除去され、その後、ドープされた誘電体層 180 で置換されてもよく、これは、成膜直後 (a s - d e p o s i t e d) にドープされる、又はドープされない層 180 の堆積後にドープされてもよい。層 170 及び 180 は、また、後の処理のために平滑な水平面を形成するために CMP プロセスにさらされてもよい。誘電体層 170 が p 型でドープされる一部の実施形態では、誘電体層 180 は、n 型ドーパントでドープされてもよい。

【0029】

続いて図 6 を参照すると、追加スペーサ層 190 は、ドープされた誘電体層 170 及び 180 に亘って形成されてもよい。一部の実施形態では、スペーサ層 190 は、層 170 及び 180 をエッチングするために後に用いられるエッチング化学物質に耐性のある材料で形成される。例えば、スペーサ層 190 は、スペーサ層 160 及び 140 及び／又はエッチング層 110 を形成するために用いられる同一の材料で形成されてもよい。誘電体層 170 及び 180 がシリコン酸化物で形成される一部の実施形態では、スペーサ層 190 は、シリコン窒化物で形成されてもよい。

【0030】

よって、続いて図 6 を参照すると、誘電体スタック 122 は、複数の誘電体層 120、130、150、170 及び 180 で形成され、かつこれらの誘電体層を隔てる複数のスペーサ層 140、160 及び 190 で形成されてもよい。本明細書で述べられるように、一部の実施形態では、スペーサ層 140、160 及び 190 は、誘電体層 120、130、150、170 及び 180 の一部を除去するために後に用いられるであろうエッチングに耐性のある材料で形成されてもよい。よって、スペーサ層 140、160、190 及びエッチング層 110 は、エッチング層として機能してもよい。スペーサ層 140、160、190 及びエッチング層 110 を形成する材料は、また、誘電体材料で形成されてもよく、かつ後の形成される導電部品間に電気的な絶縁を提供するために機能してもよい。一部の実施形態では、図示されるように、層 120 及び 130 と、層 170 及び 180 とは、同一の垂直レベルで堆積され、かつ反対の型でドープされてもよい。

【0031】

次に、一部の実施形態の第 2 の段階では、横方向エッチング (l a t e r a l e t c h s t o p s) は、誘電体スタック 122 を個別の領域に分割するように形成され、これらの個別の領域における電子デバイスの製造を容易にする。図 7A は、横方向エッチング層 200 を形成した後の図 6 の構造の概略的な断面図である。横方向エッチスト

10

20

30

40

50

ツプ 200 は、誘電体スタック 122 の上面の保護マスク露出部分で、誘電体スタック 122 に亘る保護マスク（図示せず）を堆積及びパターニングすることによって形成されてもよい。トレンチは、指向性エッチング（例えば、異方性エッチング）によってこれらの部分にエッチングされてもよい。トレンチは、誘電体層 120、130、150、170 及び 180 の一部を除去するために後に用いられるエッチングに耐性のある材料で順次充填されてもよい。一部の実施形態では、エッチストップ 200 は、層 110、140、160 又は 190 を含む他のエッチストップ層と同様の材料で形成されてもよい。例えば、エッチストップ 200 は、シリコン窒化物で形成されてもよい。

#### 【0032】

エッチストップ 200 が、簡素化のために、ハッチング無しで図示されているが、エッチストップ 200 は、単一の均一な材料を含んでもよく、又は 2 又はそれ以上の異なる材料を含んでもよい。例えば、エッチストップ 200 は、エッチストップ層として機能するライナー及びエッチストップ 200 の堆積の残りの部分を充填する別の材料を含む、材料の一又はそれ以上の層を含んでもよい。有利には、ライナーは、所望のエッチストップ特性を有するように選択されてもよく、フィラーは、エッチストップの堆積を完全に充填する及び / 又は高い堆積レートを提供するように選択されてもよい。一部の実施形態では、ライナーは、シリコン窒化物で形成されてもよく、フィラーは、シリコン酸化物で形成されてもよい。ライナーは、CVD 又は ALD によって堆積されてもよい。有利には、ALD は、非常に優れた、高いコンフォーマリティ及び均一性を提供することができる。フィラーもまた、CVD 又は ALD によって堆積されてもよい。有利には、CVD は、プロセススループットを増大させるために高い堆積レートを提供してもよい。横方向エッチストップ 200 が充填された後、誘電体スタック 122 に亘って広がる残りの材料は、例えば、CMP プロセスによって除去されてもよい。

#### 【0033】

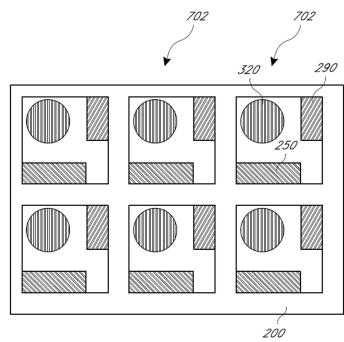

横方向エッチストップ 200 は、個々のセルを線引きする側壁を構築してもよく、個々のセルのそれぞれは、電子デバイスを含むであろう。図 7B は、図 7A の概略的なトップダウンビューである。図示されるように、図 7A の横方向エッチストップ 200 は、セル 702 のそれぞれの周りの連続的な境界を形成してもよい。形状は、セル 702 の閉じたパッキングを提供するように選択されてもよい。一部の実施形態では、図示されるように、横方向エッチストップは、セル 702 に対して矩形又は正方形を規定してもよい。一部の他の実施形態では、セルは、六角形状を有してもよい。他の任意の形状も必要に応じて規定されてもよいことが理解されるであろう。

#### 【0034】

一部の実施形態の第 3 の段階では、ワイヤは、誘電体スタック 122 において形成される。図 8 は、誘電体スタック 122 におけるワイヤを実現するために開口 210 をエッチングした後の図 7A 及び 7B の構造の概略的な断面図である。開口 210 は、誘電体スタック 122 のマスクを露出するいくつかの領域で、誘電体スタック 122 に亘ってマスク（図示せず）を堆積及びパターニングすることによって形成されてもよい。誘電体スタック 122 の露出された領域は、開口 210 を規定するために指向性エッチングを用いてエッチングされ、開口 210 は、基板 100 へ延びてもよい。

#### 【0035】

開口 210 は、その後、ワイヤ 220 を形成するために充填される。図 9 は、誘電体スタック 122 の開口 210 を充填された後の図 8 の構造の概略的な断面図である。一部の実施形態では、開口は、シリコン（Si）、ゲルマニウム（Ge）、III-V 族材料（つまり、周期律表の III 族及び V 族からの元素を含む材料）、及び / 又はそれらの混合物のような半導体材料で充填される。半導体材料は、材料が開口 210 に優先的に堆積されるエピタキシャル堆積によって開口 210 へ堆積されてもよい。有利には、開口 210 の狭い幅及び相対的に大きい深さ、及び開口 210 の側壁を形成する誘電体は、アスペクト比トラッピングの現象を利用することによって、良質なエピタキシャル構造を製造することができる。一部の実施形態では、ワイヤ 220 は、いわゆるナノワイヤであっても

10

20

30

40

50

よく、数十ナノメートル以下のオーダーの幅を有する。例えば、ワイヤ220は、約30 - 300 nm又は約50 - 200 nmの長さ(又は高さ)、及び約3 - 20 nm、3 - 15 nm又は3 - 10 nmの幅を有してもよい。

#### 【0036】

続いて図9を参照すると、開口210(図8)のそれぞれは、同一材料で充填され、それにより、同一材料のワイヤ220を形成する。一部の他の実施形態では、異なるワイヤ220は、異なる材料を含んでもよい。例えば、第1のドーパント型を有する層130及び180を通過するような開口210のいくつかは、一時的な、犠牲材料で充填されてもよく、一方で、第2のドーパント型の層130及び180を通過するような他の開口210は、第1の半導体材料で充填される。したがって、犠牲材料は除去され、新たに露出される開口210は、第2の半導体材料で充填される。有利には、異なる材料で異なる開口210を充填する能力は、材料が使用される状況との良好な互換性を有する材料の選択を可能にすることができる。例えば、ワイヤ220のいくつかは、シリコンで形成されてもよいが、一方でワイヤ220の他の部分は、ゲルマニウム又はIII-V族材料で形成される。一部の実施形態では、Geは、P-MOS構造のワイヤのために使用されることができ、 $In_xGa_{1-x}As$ ( $0 < x < 1$ )は、N-MOS構造のワイヤを形成するために使用されることができる。

#### 【0037】

一部の他の実施形態では、個々のワイヤ220は、ワイヤ220内の異なるレベルにおいて配置される異なる材料により、異なる材料の組み合わせで形成されてもよい。例えば、シリコンは、ワイヤ220の上部、中間又は下部の1つ又は2つを形成してもよく、一方で、ゲルマニウム又はIII-V族材料は、ワイヤ220の他の部分の一つはそれ以上を形成してもよい。このような実施形態では、各種の材料は、開口210に順次堆積されてもよい。一部の実施形態では、異なる材料は、ワイヤの歪を生じ、それにより、電荷キャリア移動度を増加させる。ワイヤ220が、異なる状況(例えば、それらが後に異なってドープされる)で配置されてもよいため、異なるワイヤ220は、それらが使用されるであろう状況と互換するために選択される材料の異なるシーケンスを含んでもよい。

#### 【0038】

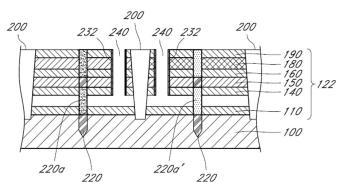

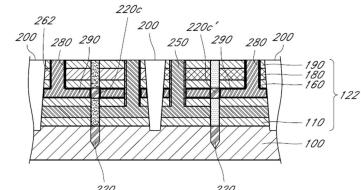

ワイヤ220は、その後、ドープされてもよい。図10は、誘電体スタック122のワイヤ220をドープした後の図9の構造の概略的な断面図である。一部の実施形態では、ワイヤ220は、誘電体スタック122がアニールされるドライブ-インアニール(drive-in anneal)によってドープされてもよく、誘電体層120、170及び130、180のドーパントを、これらの層と接触するワイヤ220に打ち込む又は拡散させる。図示されるように、ドープの後、図示された構造の左側のワイヤ220は、ドープ領域220a及び220bを含む。一部の実施形態では、ドライブ-インアニール(drive-in anneal)は、ドーパントが、左ワイヤ220の中間部220cへ適切に拡散される前に、停止される。同様に、右ワイヤ220は、ドープされた部分220a'及び220b'、及び実質的にドープされない中間部220c'を含む。一部の実施形態では、実質的にドープされない中間部220c及び220c'は、チャネル領域として機能してもよく、かつ約30 nm以下、約20 nm以下又は約5 - 15 nm以下の高さを有してもよい。

#### 【0039】

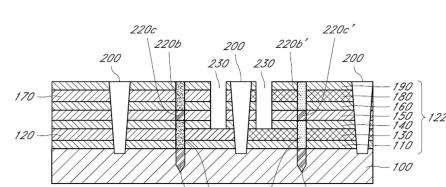

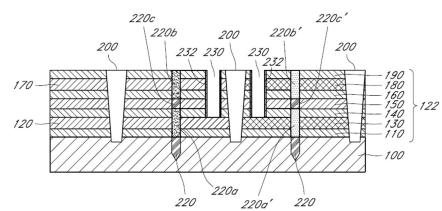

一部の実施形態の第4の段階では、ワイヤ220とインタラクトするコンタクト及び導電構造は、形成される。図11は、下部コンタクトを規定するための開口230を形成した後の図10の構造の概略的な断面図である。開口230は、誘電体スタック122に亘ってマスク(図示せず)を堆積及びパターニングすることによって形成されてもよい。誘電体スタック122は、マスクの開口を通じて指向性エッチングでエッチングされ、それにより、開口230を形成する。指向性エッチングは、一つはそれ以上のエッチング化学物質を使用し、当該層で又は当該層においてストップすることにより層を露出する用に構成されることが理解されるであろう。

## 【0040】

開口 230 の壁は、その後、ライナーでリンクされる。図 12 は、ライナー 232 で開口 230 を内張りした後の図 11 の構造の概略的な断面図である。開口 230 は、誘電体層 120 及び 130 へアクセス可能なように機能し、それにより、これらの層をエッチャントへ露出させ、除去させることを可能にする。ライナー 232 は、開口 230 の側面で層を保護するように堆積される。また、ライナー 232 は、後に形成される導電構造間の横方向の電気的な絶縁を提供するために機能してもよく、このような絶縁を提供するために十分な厚さであることが好ましい。一部の実施形態では、ライナー 232 は、ALD によって形成され、ALD は、形成される高いコンフォーマリティ、均一性、及びステップカバレッジを可能にする。一部の実施形態では、ライナー 232 を形成する材料は、層 110 及び 140 を形成する材料と同一である。例えば、ライナー 232 は、シリコン窒化物で形成されてもよい。10

## 【0041】

ライナー 232 は、また、開口 230 の底部に内張りされ、層 120 及び 130 へのアクセスをブロックすることが理解されるであろう。開口 230 の底部におけるライナー 232 の一部は、後のエッティングのために層 120 及び 130 へのアクセスを提供するために除去されてもよい。図 13 は、開口 230 の底部におけるライナー 232 を除去した後の図 12 の構造の概略的な断面図である。この除去は、ライナー 232 を指向性エッティングにさらすことによって行われてもよく、指向性エッティングは、開口 230 の側面におけるライナー 232 の一部に対する開口 230 の底部におけるライナー 232 の一部を好ましく除去する。よって、誘電体層 120 及び 130 は、開口 230 の底部において露出されてもよい。20

## 【0042】

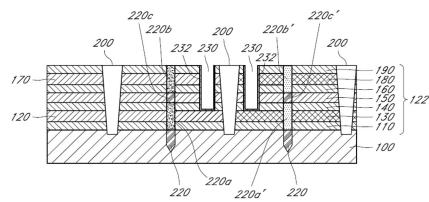

露出された誘電体層 120 及び 130 は、続いて、例えば、これらの層を形成する材料のためのウェットエッティング選択を用いて選択的に除去されてもよい。図 14 は、誘電体スタック 122 の上面下に延びる開口空間 (open volumes) 240 を残すために、露出された誘電体層 120 及び 130 を除去した後の図 13 の構造の概略的な断面図である。これらの開いた空間 240 は、また、埋め込み開口空間 (buried open volumes) ともよばれる。ワイヤ 220 の底部 220a 及び 220a' は、埋め込み開口空間 240 において露出される。横方向エッチストップ 200、エッチストップ 110 及びスペーサ層 140 は、誘電体層 120 及び 130 を除去するために使用されるエッチャントを閉じ込めてよいことが理解されるであろう。よって、埋め込み開口空間 240 は、各セル 702 内及び各セルの特定のレベル内に閉じ込められてもよい。図 14 及び以下の図の多くは、図示の簡素化のために、2 つのセル 702 に注目することが理解されるであろう。しかし、本明細書で開示されるプロセスは、このようなセル 702 のアレイのそれぞれに適用されてもよい。例えば、図 13 及び 14 に示されるセル 702 の左及び / 又は右側に、別のセルが存在する場合、別の開口 230 は、それらのセルに形成されてもよいことが理解される。30

## 【0043】

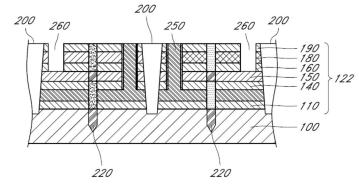

コンタクトは、続いて、下部 220a 及び 220a' になされてもよい。図 15 は、下部コンタクト 250 を形成するために導電性材料で埋め込み開口空間 240 を充填した後の図 14 の構造の概略的な断面図である。下部コンタクト 250 は、ワイヤ 220a の下部 220a 及び 220a' と接触し、かつ、構造の上面へ延びてあり、他の回路との電気的な接触がなされる。下部コンタクト 250 は、制限されず、RuO<sub>2</sub>、IrO<sub>2</sub>、W、Ir、Pt、SrRuO<sub>3</sub>、Rh、Pd、Ag、Cu、Re、Os 又は Au 又はそれらの混合物、又は NbN、ZrN、HfN、MoN<sub>x</sub>、WN<sub>x</sub>、VN、又は TaN 又はそれらの混合物のような貴金属、貴金属の酸化物又は窒化物で形成されてもよい。好ましくは、下部コンタクトは、Ti、Ta、Nb、W、Ni 又はそれらの混合物のような遷移金属、又は TiN、TaN、NbN 及び WN 又はそれらの混合物のような遷移金属窒化物で形成される。一部の実施形態では、下部コンタクト 250 は、ALD によって形成されてもよ4050

い。ALDは、堆積サイクルごとのほぼ自己限定層 (self-limited layer) (例えば、単一層)での前駆体を堆積することができるが理解されるであろう。複数の堆積サイクルは、空間240を完全に充填するように実行されてもよい。このような、単一層ごとの (monolayer-by-monolayer) 成長は、堆積レートが局所的な前駆体濃度に密接に関連する他の堆積プロセスで生じたとき、開口240のネックでの堆積をピンチオフせずに、下部コンタクト250を形成する材料が、埋め込み空間240を完全に充填することを可能にする。

#### 【0044】

トランジスタが製造される実施形態では、ゲートは、続いて形成されてもよい。図16は、ゲートを規定するための開口260を形成した後の図15の構造の概略的な断面図である。エッチマスク (図示せず) は、誘電体スタック122に亘って形成され、誘電体スタック122は、開口260を形成するために指向性エッチングを用いてエッチマスクを通じてエッチングされる。指向性エッチングは、誘電体層150上又は誘電体層150内で停止し、それにより、露出された層150の一部を残す。

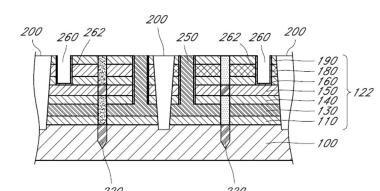

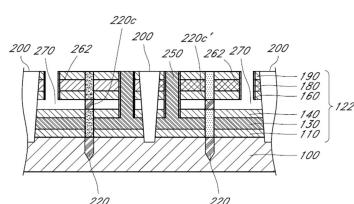

#### 【0045】

ライナーは、層150の一部を除去するために用いられる、後のエッチングからこれらの壁を保護するために、開口260の壁に堆積される。図17は、ライナー262で開口260をライニングした後の図16の構造の概略的な断面図である。一部の実施形態では、ライナー262は、ALDによって形成される。ライナー262を形成する材料は、層110、140及びライナー232 (図12) を形成する材料と同一であってもよい。例えば、ライナー262は、シリコン窒化物で形成されてもよい。

#### 【0046】

ライナー262の底部が、開口260の底部を覆うため、ライナー262の底部は、エッチャントが、下にある誘電体層150にアクセス可能となるように除去されてもよい。図18は、ライナー262の底部をエッチングした後の図17の構造の概略的な断面図である。エッチングは、指向性エッチングであってもよく、これは、ライナー262の底部を選択的に除去する一方で、開口260の側壁のライナー262を残す。よって、誘電体層150は、開口260の底部に露出されたまま残る。

#### 【0047】

図19は、開口260によって露出された誘電体層150の一部を除去した後に形成される埋め込み開口空間270を示す図18の構造の概略的な断面図である。誘電体層150は、当該層を形成する材料のためのウェットエッチング選択により選択的に除去されてもよい。得られた埋め込み空間270は、露出されるワイヤ220の中間部220c及び220c'を残す。

#### 【0048】

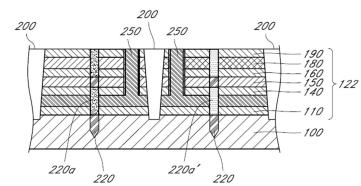

中間部220c及び220c'は、チャネル領域として機能し、ゲート誘電体によりゲートから隔てられることが理解されるであろう。有利には、このゲート誘電体は、誘電体内に埋め込み空間270の壁を単に内張りすることにより、形成されてもよい。図20は、埋め込み開口空間270の誘電体ライナー280を形成した後の図19の構造の概略的な断面図である。一部の実施形態では、誘電体ライナー280は、ALDによって形成されてもよく、ALDは、中間部220c及び220c'の側面の信頼性のあるカバレッジを提供する一方で、良好な厚さ制御を維持することができる。

#### 【0049】

誘電体ライナー280は、好ましくは、(シリコン酸化物よりも高い誘電率を有する) hig h - k 誘電体材料で形成される。hig h - k 誘電体材料の例は、ハフニウム酸化物のような、ハフニウム (Hf) を含む化合物を含む。hig h - k 誘電体材料の他の例は、ジルコニウム (Zr)、イットリウム (Y)、アルミニウム (Al) 又はチタニウム (Ti) の酸化物を含む。一部の実施形態では、誘電体ライナー280のALD堆積は、金属及び酸素前駆体それぞれへの埋め込み開口空間270の交互かつ連続的な露出を含む。一部の実施形態では、ハロゲン化金属が金属前駆体として用いられ、例えば、化学式M

10

20

30

40

50

$X_n$  を有する化合物では、Mが金属であり、Xが、フッ化物、塩化物、臭化物又はヨウ化物のようなハロゲン化物であり、nがMの価数に等しく、例えば、MがTiである場合、 $TiCl_4$ 、 $TiBr_4$  及び $TiI_4$  である。一部の実施形態では、金属ハロゲン化前駆体は、 $AlCl_3$ 、 $HfCl_4$ 、 $HfI_4$ 、 $SiCl_4$ 、 $SiBr_4$ 、 $SiI_4$ 、 $SiF_4$ 、 $ZrCl_4$  及び $ZrI_4$  を含む。金属前駆体は、埋め込み開口空間270の壁にほぼ単一の分子層ではなく形成されるように提供されてもよい。金属の層は、その後、特に制限されないが、酸素、プラズマ励起酸素、原子状酸素、オゾン、水、酸素／水素、水素／二酸化炭素、一酸化窒素( $NO$ )、二酸化窒素( $NO_2$ )、亜酸化窒素( $N_2O$ )、過酸化水素( $H_2O_2$ )等を含む酸素前駆体と反応される。金属及び酸素前駆体への交互の露出は、誘電体ライナー280が所望の厚さに到達するまで継続することができる。 10

#### 【0050】

一部の実施形態では、誘電体材料は、例えば、ジルコニウムを含むハフニウム酸化物のような、上記で述べた材料の組み合わせを含んでもよい。一部の実施形態では、 $high-k$  誘電体は、これらの酸化物の2又はそれ以上の構成層によって形成されるナノラミネートである(例えば、ナノラミネートは、ハフニウム酸化物及びシリコン酸化物の層を含んでもよい)。例えば、これらの酸化物は、金属及び酸素前駆体へ交互に露出するALDによって形成されてもよい。ナノラミネートは、異なる堆積サイクルで使用される金属前駆体を変更することにより形成されてもよい。

#### 【0051】

一部の実施形態では、 $high-k$  誘電体は、 $GeO_2$ 、 $GeAlO_x$ 、 $Al_2O_3$ 、 $AlSiO_x$  及び $TaSiO_x$  又はそれらの任意の組み合わせを含むことができる。 20

#### 【0052】

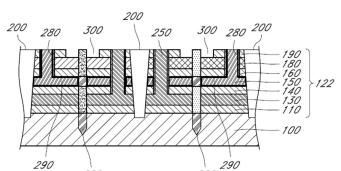

導電性材料は、ゲートを形成するために開口空間270へ堆積されてもよい。図21は、ゲート290を形成するために導電性材料で埋め込み開口空間270を充填した後の図20の構造の概略的な断面図である。各ゲート290は、ワイヤ220の1つの周辺部の周りに完全に広がることが好ましい。一部の他の実施形態では、ゲート290は、ワイヤ290の周囲に部分的に広がってもよい。導電性材料は、構造の上面に広がっており、他の回路との電気的な接触を可能にする。一部の実施形態では、導電性材料は、金属である。金属の例は、制限されず、Ni、Fe、Co、Cu、Ag、Cr、V、Mn、Zn、Sn、Pb、Bi、In、及びCdを含む。一部の実施形態では、導電性材料は、Ti、Ta、W、TiC、TaC、WC、TiN、TaN、WN、TiAlC又はTaAlC又はそれらの混合物である。 30

#### 【0053】

導電性材料は、ALD、電気化学堆積(例えば、電気めっき)、無電解めっき、シードなしめっき、CVD、超臨界流体からの反応性堆積(例えば、溶媒として超臨界二酸化炭素 $CO_2$ を用いる化学流体堆積(chemical fluid deposition(CFD)))、又はそれらの組み合わせによって堆積されてもよい。例えば、一部の実施形態では、シード層は、ALDによって堆積され、残りの層は、電気化学堆積によって堆積されてもよい。

#### 【0054】

一部の実施形態では、ゲート290の少なくとも一部は、金属酸化物を形成することによって堆積され、その後、金属層を残すために金属酸化物を還元する。金属酸化物は、例えば、CVD又はALDによって形成されてもよい。一部の実施形態では、金属酸化物は、ALDによって形成され、埋め込み開口空間270は、金属及び酸素前駆体へ交互に露出され、それにより、金属酸化物を形成する。酸化物は、金属を形成するために還元される。 40

#### 【0055】

一部の他の実施形態では、金属ゲートは、複数の金属を含む混合酸化物を堆積するために、ALD時に2つの異なる前駆体を用いて形成されてもよい。混合酸化物は、その後、混合金属を形成するために還元される。例えば、それぞれ完全に混合された酸化ALDサ 50

イクルは、第1の金属を含む第1の材料を単層になるまで形成する第1の堆積サブサイクルと、第2の金属を含む第2の材料を単層になるまで形成する第2の堆積サブサイクルと、を含んでもよい。第1及び第2の堆積サブサイクルは、完全なALDサイクルを構築する。各完全なALDサイクルの第1の堆積サブサイクル及び第2の堆積サブサイクルの数は、所望の堆積を実現するために変更されてもよい。一部の実施形態では、形成された混合酸化物は、第2の金属よりも第1の金属を多く含む。一部の実施形態では、混合金属酸化物の金属の少なくとも80%、少なくとも90%、少なくとも95%、少なくとも97%、少なくとも98%又は少なくとも99.5%は、第1の金属である。一部の実施形態では、混合金属酸化物の金属の約30-80%又は約40-60%は、第2の金属である。一部の実施形態では、第1の金属は、Ni、Fe、Co、Cu、Ag、Cr、V、Mn、Zn、Sn、Pb、Bi、In及びCdからなる群から選択され、第2の金属は、Pt、Ni、Pd、Rh、Ru及びCoからなる群から選択される。有利には、混合酸化物の形成は、酸化物が、一つの金属のみを含む酸化物よりも低い温度で酸化されることが可能となる。

#### 【0056】

堆積に続いて、金属酸化物は、還元されてもよい。一部の実施形態では、還元剤は、水素雰囲気で導入されることができる。一部の実施形態では、金属酸化物は、水素含有雰囲気で少なくとも部分的に還元され、これは、H<sub>2</sub>、NH<sub>3</sub>、N<sub>2</sub>H<sub>4</sub>、水素含有プラズマ、水素ラジカル、水素原子又はそれらの混合物を含むことができる。一部の実施形態では、混合金属酸化物は、一又はそれ以上の反応性有機化合物と接触してもよく、反応性有機化合物は、アルコール(-OH)、アルデヒド(-CHO)及びカルボン酸(-COOH)の群から選択された少なくとも1つの官能基を含む。一部の実施形態では、基板は、水素環境で還元され、有機還元剤と接触する。

#### 【0057】

一部の実施形態では、金属酸化物は、金属層を形成するために還元され、これは、その後、埋め込み開口空間270への追加の金属の電気化学堆積のためのシード層として用いられる。

#### 【0058】

一部の他の実施形態では、CFDは、埋め込み空間の金属を堆積するために行われる。超臨界流体(supercritical fluid(SCF))は、その臨界温度及び臨界圧力を超える物質であることが理解されるであろう。例えば、CO<sub>2</sub>は、温度が約+30を超え、かつ圧力が約73.75barを超えるとき、超臨界流体となる。質量移動は、超臨界流体により迅速になる。動粘度は、通常の液体よりもほぼ1つの次数の大きさで小さくなり、超臨界流体の表面張力は、無視できる。超臨界流体の拡散係数は、通常の液体よりもほぼ1つの次数の大きさで大きくなる。有利には、輸送特性は、ガス状のものと類似する一方で、密度は、液体の密度に近い。SCFsは、非常に狭い開口を浸透し、様々な化合物に溶解する。銅を含む金属は、溶媒に加えられるキレート化合物を用いて、超臨界CO<sub>2</sub>に溶解することができる(典型的な条件は、約+60、約150bar)。超臨界流体は、その後、除去され、金属を残す。有機金属銅化合物は、また、超臨界CO<sub>2</sub>に溶解することができる。PCT公報WO03/053895、A. Cabanas et al. in J. Chemistry of Materials, vol. 15(15) (2003), pp. 2910-2916, E. Kondoh et al. in Microelectronic Engineering, vol. 64(14) (2002) pp. 495-499、及びJ. M. Blackburn et al. in Science, vol. 294(5540) (2001) pp. 141-145は、超臨界CO<sub>2</sub>からの銅の堆積の例として挙げられる。

#### 【0059】

堆積された導電性材料は、金属以外の導体であることが理解されるであろう。一部の実施形態では、導電性材料は、導電性ポリマーでありうる。例示的な導電性ポリマーは、ヨ

ウ素をドープしたポリアセチレン、ポリアニリン、ポリピロール又はポリチオフェンを含むが、これに限定されない。ポリマーは、熱硬化性ポリマーの場合にトレンチ及びビアに射出成形ができる。別の実施形態では、モノマーは、トレンチ及びビアを充填する電気伝導ポリマーを形成するために、in situで重合及びドープされる。例えば、一実施形態では、開口の表面は、 $Ti(OOC_4H_9)_4 / Al(C_2H_5)_3$ のようなチーグラー・ナッタ触媒の分子層又は重合プロセスを促進する他の化合物でコートされる。ヨウ素を放出するヨウ素又はヨウ素化合物への基板の露出は、反応チャンバへのアセチレンガスの導入前、又は反応アセチレンガスの導入時のインターバルのいずれかで行われる。その後、開口は、(モノマーとして)アセチレンガスへ露出され、開口は、ヨウ素でドープされたポリアセチレンで充填される。ポリアセチレンの液相合成は、例えば、H. Shirakawa et al. in J. C. S. Chem. Comm. (1977)、pp. 578-580及びB. Lesiak et al. in Polish J. Chem. 74 (2000) pp. 847-865によって説明されている。これらの文献で説明されている触媒は、ビア及びトレンチの表面でのガス状モノマーからドープされた導電性ポリマーの合成に適用される。

#### 【0060】

一部の他の実施形態では、導電性材料は、カーボンナノチューブでありうる。例えば、相対的に短いカーボンナノチューブビットは、例えば、超臨界 $CO_2$ のような流体に懸濁され、埋め込み空間に導入される。その後、流体は、反応チャンバの圧力を低くすることにより気化され、カーボンナノチューブビットは、ファンデルワールス相互作用により互いに接着する。その後、電流は、カーボンナノチューブを通じて流れることが可能になる。カーボンナノチューブ導体の電気伝導性は、非常に高い電流密度に耐えうる連続的なカーボンナノチューブワイヤーが形成されるという理由で、電流の処理時に改善する。電流によるカーボンナノチューブ同士の「溶接」は、K. Jiang et al. in Nature, 419 (2002) p. 801により提案されており、これは、本明細書に参照によって援用される。

#### 【0061】

他の実施形態では、導体250は、ナノ金属パウダーから製造されることができる。好適なナノ金属パウダーは、Argonide Corporation, 291 Power Court, Sanford, Fla.、USAによって販売されている。好ましくは、一実施形態では、ナノ金属パウダーは、超臨界 $CO_2$ のような不活性液体のスラリーとして懸濁され、その後、埋め込み空間へ導入される。液体は、反応チャンバの圧力をゆっくりと下げることにより構造から除去される。その後、基板は、焼結プロセスを開始するために約200-300に加熱される。ナノ金属粒子は、共に融合し、埋め込み空間を通じて広がる連続的な導体を形成する。粒子の大きさ分布が、フラクタル状、例えば、3つの異なる大きさレベルであるナノ金属パウダーの混合物を選択することが有益である。このような混合物の使用は、埋め込み空間への金属粒子の非常に密なパッキングを可能にする。これは、最小の粒子(例えば、直径約1-3nm)は、中間サイズの粒子(例えば、直径約5-8nm)の間の穴を充填することができ、かつ中間サイズの粒子は、大きなサイズの粒子(例えば、直径約10-20nm)の間の穴を充填することができるためである。この場合、焼結プロセスの前の粒子間の空のスペースはわずかしかないため、焼結プロセスは、導体の堆積を実質的に減少させない。

#### 【0062】

一部の実施形態では、導電性材料は、また、ポーラロンスレッド(polaron threads)を含む超伝導体から製造されることもできる。L. Grigorovらは、米国特許第5,777,292号で教示しており、その開示は、参照によって本明細書に援用され、ポーラロンを有する導体の形成は、材料を通じて伝導スレッド(conducting threads)を形成する。より詳細なポーラロン導体は、ウェブページ <http://www.ultracconductors.com>に示されている。材料における付随する局所的な歪を有する電子は、ポーラロンと呼ばれる。頻繁に、ポー

10

20

30

40

50

ラロンは、材料の不純物によって捕捉される。ポーラロンは、それ自体の周囲にポテンシャル井戸を生成する。ポーラロンの電子は、ポーラロンが連鎖している場合、電気のキャリアとして移動及び機能することができる。有利には、超伝導体の抵抗は、室温を超える場合でさえ、銅と超伝導体との抵抗の間にある。また、極小 R C リレーが得られ、コンタクト抵抗は、無視できる。

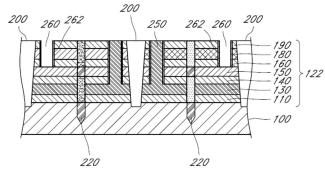

#### 【0063】

ここで、図 22 を参照すると、ワイヤ 220 のための上部コンタクトは、続いて形成される。図 22 は、上部コンタクトを規定するための開口 300 を形成した後の図 21 の構造の概略的な断面図である。エッチマスク（図示せず）は、誘電体スタック 122 に亘って形成され、スペーサ層 190 は、開口 300 を形成するために指向性エッチングを用いて、エッチマスクを通じてエッチングされる。スペーサ層 190 が十分に薄い一部の他の実施形態では、ウェットエッチングが用いられてもよい。エッチングは、誘電体層 170 及び 180 上又は誘電体層 170 及び 180 内で停止し、それにより、露出されたこれらの層を残す。

10

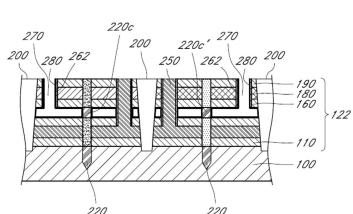

#### 【0064】

誘電体層 170 及び 180 の一部は、続いて除去される。図 23 は、開口 300 によって露出される誘電体層 170 及び 180 の一部を除去した後の図 22 の構造の概略的な断面図である。誘電体層 170 及び 180 は、これらの層を形成する材料のためのウェットエッチング選択により選択的に除去されてもよい。得られる埋め込み空間 310 は、露出されるワイヤー 220 の上部 220b 及び 220b' を残す。一部の他の実施形態では、ウェットエッチングに替えて、誘電体層 170 及び 180 をエッチングするために指向性エッチングが用いられる。このような場合、開口空間 310 は、埋め込み空間ではないが、スペーサ層 190 の開口 300（図 22）の幅と同様の幅を有するトレーナーであってよい。

20

#### 【0065】

開口空間 310 は、続いて、上部 220b 及び 220b' への上部コンタクトを形成するために導体材料で充填されてもよい。図 24 は、上部コンタクト 320 を形成するために、導体材料で埋め込み開口空間 310 を充填した後の図 23 の構造の概略的な断面図である。一部の実施形態では、導体材料は、制限されず、Ru、RuO<sub>2</sub>、IrO<sub>2</sub>、W、Ir、Pt、SrRuO<sub>3</sub>、Rh、Pd、Ag、Cu、Re、Os 又は Au 又はそれらの混合物、又は NbN、ZrN、HfN、MoN<sub>x</sub>、WN<sub>x</sub>、VN、又は TaN 又はそれらの混合物のような貴金属、貴金属の酸化物又は窒化物で形成されてもよい。一部の実施形態では、上部コンタクト 250 は、好ましくは、Ti、Ta、Nb、W、Ni 又はそれらの混合物のような遷移金属、又は TiN、TaN、NbN 及び WN 又はそれらの混合物のような遷移金属窒化物で形成される。一部の実施形態では、上部コンタクト 320 は、ALD によって形成されてもよい。上部コンタクト 320 は、ワイヤー 220 の上部 220b 及び 220b' と接触し、かつ構造の上面に広がっており、他の回路との接触がなされてもよい。

30

#### 【0066】

図 25 は、図 24 の構造の概略的なトップダウンビューである。図示されるように、横方向エッチストップ 200 は、複数のセル 702 を隔て、複数のセル 702 のそれぞれは、トランジスタのような半導体を含んでもよい。図 25 は、半導体デバイスへの様々なコンタクトの位置のためのレイアウトの一例を提供する。上部コンタクト 320、下部コンタクト 250 及びゲート 290 の拡張は、上面に見られてもよく、必要に応じて隔てられてもよく、それらの構造との電気的な接触を容易にする。図示されるように、この上面で、上部コンタクト 320 は、円形形状を有してもよく、上部コンタクト 250 及びゲート 290 は、矩形形状を有してもよい。これらの形状は、任意の形状であってもよく、かつ他の形状も使用されてもよいことが理解されるであろう。好ましくは、断面形状は、上部コンタクト 320、下部コンタクト 250 及びゲート 290 を形成するために除去される様々な層のためのエッチャントの流れを容易にし、かつ他の回路への電気的な接触を容易

40

50

するために選択される。上面でのこれらの構成の位置は、任意の位置であり、かつ他の位置も取り得ることもまた理解されるであろう。好ましくは、前記構成は、短絡の可能性を低減するため、及び他の電気回路と接続する他の構成（例えば、導電性プラグ（図示せず））とのアライメントを容易にするために、十分に離間している。よって、図24及び25は、本明細書に記載の方法によって形成される集積回路の側面部分断面図を提供することが理解されるであろう。

#### 【0067】

各種の変更は、本明細書に記載の方法になされてもよいことが理解されるであろう。本明細書で述べたように、各種の堆積プロセスは、埋め込み空間240、270及び/又は310を充填するために使用されてもよい。一部の実施形態では、全ての空間は、同一の材料で充填されてもよく、同一の堆積プロセスを用いてもよい。一部の別の実施形態では、例えば、コスト、材料特性及び互換性、及び/又は製造の容易さの理由で、異なる材料は、異なる埋め込み空間を充填するための使用されてもよい。例えば、空間270は、ゲート290を形成するために金属で充填されてもよい一方で、空間240及び310は、下部及び上部コンタクト250及び320を形成するために、別の導電材料で形成されてもよい。例えば、他の導電化合物は、 $TiC_{1.4}$ のようなハロゲン化物前駆体及び $NH_3$ のような窒素前駆体を用いるALDによって堆積されるTiNであってもよい。タンゲステン金属のような金属導体の空間のための例示的なALD反応物質は、 $WF_6$ のような金属化合物及びボラン（例えば、ジボラン $B_2H_6$ ）のような還元剤を含む。一部の実施形態では、コンタクト250及び320は、金属のいずれかで形成されてもよく、ゲート290のために本明細書で述べられた堆積プロセスに関連してもよい。例えば、ニッケルは、ALDによって堆積されるコンタクト250及び320を形成するために用いられてもよい。

10

20

30

#### 【0068】

また、一部の実施形態では、反対の型にドープされた層130を形成するために層120の一部を置換すること、及び反対の方にドープされた層180を形成するために層170の一部を置換することではなく、層120及び170の異なる部分は、異なるドープがなされた層120及び130を形成するために異なるドーパントでドープされてもよい。例えば、保護マスクは、一方の型のドーパントでドープされるマスク露出部の開口により、層120に亘って形成及びパターニングされてもよい。それらの露出された領域は、その後、ドープされ、マスクは、続いて、除去され、別のマスクは、形成及びパターニングされ、別のドーパント型でドープされる層120の別の部分を露出する。それらの他の露出された部分は、その後、他の型のドーパントを用いてドープされてもよい。マスクは、その後、除去されてもよい。層170は、異なるドーパントで同様にドープされてもよい。一部の別の実施形態では、異なるドープされた層130及び180は、同様にドープされたワイヤ-ベースデバイスの繰り返しアレイを形成するために省略されてもよい。

#### 【0069】

一部の実施形態では、層120及び/又は170は、ドープされなくてもよく、ドライブ-イン アニール（drive-in anneal）は、ワイヤ220のドープのために使用されない。そうではなく、ワイヤ220は、成膜直後（as-deposited）でドープされてもよい。このような成膜直後のドーピングは、ワイヤ220のドープされた領域とドープされない領域とのシャープな境界を形成することを助け、これは、ワイヤを用いて形成されるトランジスタの電気的な機能性の予測可能性を増大させることができる。

40

#### 【0070】

一部の実施形態では、ワイヤ220は、トンネル電界効果トランジスタ（TFT）を形成してもよい。図10を再度参照すると、同一型のドーパントで上部及び下部220a、220a'及び220b、220b'をドーピングするのではなく、上部及び下部は、異なるドーパントでドープされてもよい。例えば、下部220a、220a'は、p型ドーパントでドープされる一方で、上部220b、220b'は、n型ドーパントでドープ

50

されてもよい。このようなドーピングは、一方のドーパント型で誘電体層 120、130 をドーピングし、かつ他方のドーパント型で誘電体層 170、180 をドーピングすることによりなされてもよい。ドライブ-イン アニールは、その後、本明細書に記載されたように、ワイヤ 220 へドーパントを打ち込むように実行されてもよい。一部の他の実施形態では、ワイヤ 220 は、成膜直後 (as-deposited) に所望のドーパントでドープされる。

#### 【0071】

続いて図 10 を参照すると、一部の実施形態では、相補型 TFEET は、特定レベルで異なるドープがなされたワイヤ部分を有する TFEET によって形成されてもよい。下部 220a 及び 220a' は、異なるドープがされ、上部 220b 及び 220b' は、異なるドープがされ、個々のワイヤ 220 の上部及び下部は、異なるドープがされてもよい。例えば、下部 220a 及び 220a' は、それぞれ、n 及び p 型ドーパントでドープされる一方で、上部 220b 及び 220b' は、それぞれ、p 及び n 型ドーパントでドープされてもよい。ドーピングは、ドライブ-イン アニール (drive-in anneal) 及び / 又は成膜直後 (as-deposited) で行われてもよい。

10

#### 【0072】

一部の実施形態では、個別の TFEET を形成するワイヤ 220 は、2 又はそれ以上の異なる半導体材料を含んでもよい。例えば、下部 220a、220b' 及び中間部 220c は、シリコンで形成されてもよい一方で、上部 220c、220c' は、ゲルマニウムで形成されてもよい。一部の実施形態では、シリコン部分は、n ドープ又はドープされなくともよく、ゲルマニウム部分は、p ドープされてもよく、デバイスを通じて電流を増大させるための利点を提供することができる。一部の他の実施形態では、異なる TFEET は、ワイヤ 220 のための半導体の異なる組み合わせを含んでもよい。例えば、相補型 TFEET を有する一部の実施形態では、ワイヤ 220 の 1 つは、n ドープ及びドープされないシリコン部分を有する p ドープされたゲルマニウムを含んでもよく、相補型ワイヤ 220 は、p ドープ及びドープされないシリコン部分を有する n ドープされたインジウム - 硅素部分を含んでもよい。

20

#### 【0073】

TFET のためのソース / ドレインコンタクト及びゲートは、続いて、コンタクト 230、320 及びゲート 290 を形成するために本明細書で記載されたように形成されてもよいことが理解されるであろう。

30

#### 【0074】

ゲート 290 及びコンタクト 250、320 は、他のシーケンスで形成されうることが理解されるであろう。有利には、エッチストップ層 110 及びスペーサ層 140、160 及び 190 は、他のレベルでの他の構成を保護及び隔離する。例えば、一部の実施形態では、ゲート 290 は、コンタクト 250 及び 320 の後に形成されてもよい。

#### 【0075】

当業者により、本発明から逸脱されない範囲で種々の省略、追加および変形が、本発明の範囲を逸脱しない限り、当業者によりなされうることがわかるであろう。実施形態の特定の特徴及び態様の各種のコンビネーション又はサブコンビネーションがなされ、発明の詳細な説明の範囲内にあることが考慮される。開示された実施形態の各種の特徴及び態様は、順番に、互いに組み合わされる又は構築されることができる。このような変更および変形の全ては、添付の特許請求の範囲により規定されるような、本発明の範囲内で逸脱しないことが意図される。

40

【図1】

【図3】

【図2A】

【図2B】

【図5】

【図6】

【図7A】

【図9】

【図7B】

【図10】

【図8】

【図11】

【図12】

【図15】

【図13】

【図16】

【図14】

【図17】

【図18】

【図21】

【図19】

【図22】

【図20】

【図23】

【図24】

【図25】

---

フロントページの続き

(51)Int.Cl. F I

H 01 L 29/423 (2006.01) H 01 L 29/50 M

H 01 L 29/417 (2006.01)

(72)発明者 マエス ヤン ウィレム

オランダ国 1322エーピー アルメーレ フェルステルケルシュトラート 8

審査官 市川 武宣

(56)参考文献 特開平06-069441 (JP, A)

特開2000-091578 (JP, A)

特開2003-163282 (JP, A)

特開2004-104135 (JP, A)

特開2011-228596 (JP, A)

(58)調査した分野(Int.Cl., DB名)

H 01 L 21/336

H 01 L 21/8238

H 01 L 27/092

H 01 L 29/417

H 01 L 29/423

H 01 L 29/49

H 01 L 29/78