(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第4504714号

(P4504714)

(45) 発行日 平成22年7月14日(2010.7.14)

(24) 登録日 平成22年4月30日(2010.4.30)

(51) Int.Cl.

H04N 5/073 (2006.01)

F 1

H04N 5/073

A

請求項の数 5 (全 18 頁)

(21) 出願番号 特願2004-92187 (P2004-92187)

(22) 出願日 平成16年3月26日 (2004.3.26)

(65) 公開番号 特開2005-278088 (P2005-278088A)

(43) 公開日 平成17年10月6日 (2005.10.6)

審査請求日 平成19年1月5日 (2007.1.5)

(73) 特許権者 000115603

リーダー電子株式会社

神奈川県横浜市港北区綱島東2丁目6番3

3号

(74) 代理人 100089705

弁理士 社本 一夫

(74) 代理人 100076691

弁理士 増井 忠式

(74) 代理人 100075270

弁理士 小林 泰

(74) 代理人 100080137

弁理士 千葉 昭男

(74) 代理人 100096013

弁理士 富田 博行

最終頁に続く

(54) 【発明の名称】外部同期信号生成回路および位相差測定回路

## (57) 【特許請求の範囲】

## 【請求項 1】

外部同期信号を生成する回路であって、該回路は、

外部フレーム同期信号 (F R M \_ S Y N C) 並びにデジタル映像信号のフレーム同期信号 (F R M) 及び水平同期信号 (H B K) を入力する手段と、

外部フレーム同期信号 (F R M \_ S Y N C) とデジタル映像信号のフレーム同期信号 (F R M) との位相差を測定する手段と、

デジタル映像信号の水平同期信号 (H B K) の周期と同じ周期を持つ信号 (E X T \_ H) であって、デジタル映像信号のフレーム同期信号 (F R M) を基準として、前記測定された位相差を有する信号 (E X T \_ H) を生成する手段と、

デジタル映像信号のフレーム同期信号 (F R M) の周期と同じ周期を持つ信号 (E X T \_ F) であって、デジタル映像信号のフレーム同期信号 (F R M) を基準として、前記測定された位相差を有する信号 (E X T \_ F) を生成する手段と、

を備え、

前記生成された信号 (E X T \_ F) 及び (E X T \_ H) が、外部同期信号の外部フレーム・タイミング信号及び外部水平タイミング信号として出力される、回路。

## 【請求項 2】

外部同期信号を生成する回路であって、該回路は、

外部フレーム同期信号 (F R M \_ S Y N C) に位相同期するパルス信号 (F R M \_ S Y N C \_ P S) を生成する手段 (4) と、

デジタル映像信号のフレーム同期信号 ( F R M ) に位相同期するパルス信号 ( F R M \_ P S ) を生成する手段 ( 1 ) と、

デジタル映像信号の水平同期信号 ( H B K ) に位相同期するパルス信号 ( H B K \_ P S ) を生成する手段 ( 5 ) と、

外部フレーム同期信号のパルス信号 ( F R M \_ S Y N C \_ P S ) の位相が、デジタル映像信号のフレーム同期信号のパルス信号 ( F R M \_ P S ) の位相に対して、デジタル映像信号のクロックの周期を単位として、何ドットだけ離れているかを測定する手段 ( 6 ) ( 7 ) と、

外部フレーム同期信号のパルス信号 ( F R M \_ S Y N C \_ P S ) の位相が、デジタル映像信号のフレーム同期信号のパルス信号 ( F R M \_ P S ) の位相に対して、デジタル映像信号の水平同期信号 ( H B K ) の周期を単位として、何ラインだけ離れているかを測定する手段 ( 2 ) ( 3 ) と、

デジタル映像信号の水平同期信号 ( H B K ) の周期と同じ周期を持つ信号 ( E X T \_ H \_ A ) であって、前記測定されたドット数に基づいて、デジタル映像信号のフレーム同期信号のパルス信号 ( F R M \_ P S ) の位相に対して、位相シフトさせられた信号 ( E X T \_ H \_ A ) を生成する手段 ( 9 ) と、

デジタル映像信号のフレーム同期信号 ( F R M ) の周期と同じ周期を持つ信号 ( E X T \_ F \_ A ) であって、前記測定されたライン数に基づいて、デジタル映像信号のフレーム同期信号のパルス信号 ( F R M \_ P S ) の位相に対して、位相シフトさせられた信号 ( E X T \_ F \_ A ) を生成する手段 ( 8 ) と、

前記測定されたドット数に基づいて、前記手段 ( 8 ) によって生成される信号 ( E X T \_ F \_ A ) を、位相シフトさせる手段 ( 10 ) と、

前記手段 ( 10 ) によって位相シフトさせられた信号 ( E X T \_ F ) の位相と、前記手段 ( 9 ) によって生成される信号 ( E X T \_ H \_ A ) の位相とが一致するように、前記手段 ( 9 ) によって生成される信号 ( E X T \_ H \_ A ) を位相シフトさせる手段 ( 11 ) と、

を備え、

前記手段 ( 10 ) によって位相シフトさせられた信号 ( E X T \_ F ) 及び前記手段 ( 11 ) によって位相シフトさせられた信号 ( E X T \_ H ) が、外部同期信号の外部フレーム・タイミング信号及び外部水平タイミング信号として出力される、回路。

### 【請求項 3】

外部同期信号を生成する回路であって、該回路は、

外部フレーム同期信号 ( F R M \_ S Y N C ) の立ち上がりを検出する回路 ( 4 ) であって、外部フレーム同期信号 ( F R M \_ S Y N C ) に位相同期するパルス信号 ( F R M \_ S Y N C \_ P S ) を生成する回路 ( 4 ) と、

デジタル映像信号のフレーム同期信号 ( F R M ) の立ち上がりを検出する回路 ( 1 ) であって、デジタル映像信号のフレーム同期信号 ( F R M ) に位相同期するパルス信号 ( F R M \_ P S ) を生成する回路 ( 1 ) と、

デジタル映像信号の水平同期信号 ( H B K ) の立ち上がりを検出する回路 ( 5 ) であって、デジタル映像信号の水平同期信号 ( H B K ) に位相同期するパルス信号 ( H B K \_ P S ) を生成する回路 ( 5 ) と、

デジタル映像信号の水平同期信号のパルス信号 ( H B K \_ P S ) をリセット信号として用い、デジタル映像信号のクロック数をカウントする第 1 カウンタ ( 6 ) と、

外部フレーム同期信号のパルス信号 ( F R M \_ S Y N C \_ P S ) をイネーブル信号として入力し、外部フレーム同期信号のパルス信号が入力された時点での第 1 カウンタのカウンタ値を保持する第 1 レジスタ ( 7 ) と、

デジタル映像信号のフレーム同期信号のパルス信号 ( F R M \_ P S ) をリセット信号として用い、デジタル映像信号の水平同期信号のパルス信号 ( H B K \_ P S ) の周期の数をカウントする第 2 カウンタ ( 2 ) と、

外部フレーム同期信号のパルス信号 ( F R M \_ S Y N C \_ P S ) をイネーブル信号とし

10

20

30

40

50

て入力し、外部フレーム同期信号のパルス信号が入力された時点での第2カウンタのカウンタ値を保持する第2レジスタ(3)と、

第1カウンタによってカウントされるカウンタ値と、第1レジスタによって保持されるカウント値と一致する期間だけ、HIGH状態を表す信号(EXT\_H\_A)を生成する第1コンパレータ(9)と、

第2カウンタによってカウントされるカウンタ値と、第2レジスタによって保持されるカウント値と一致する期間だけ、HIGH状態を表す信号(EXT\_F\_A)を生成する第2コンパレータ(8)と、

第2コンパレータ(8)の信号(EXT\_F\_A)を、第1コンパレータ(9)の信号(EXT\_H\_A)のタイミングでラッチする第1フリップ・フロップ(10)と、10

第1コンパレータ(9)の信号(EXT\_H\_A)を、デジタル映像信号のクロックのタイミングでラッチする第2フリップ・フロップ(11)と、

を備え、

第1フリップ・フロップ(10)によってラッチされた信号(EXT\_F)及び第2フリップ・フロップ(11)によってラッチされた信号(EXT\_H)が、外部同期信号の外部フレーム・タイミング信号及び外部水平タイミング信号として出力される、回路。

#### 【請求項4】

位相差を測定する回路であって、該回路は、

外部フレーム同期信号(FRM\_SYNC)に位相同期するパルス信号(FRM\_SYNC\_PS)を生成する手段(4)と、20

デジタル映像信号のフレーム同期信号(FRM)に位相同期するパルス信号(FRM\_PS)を生成する手段(1)と、

デジタル映像信号の水平同期信号(HBK)に位相同期するパルス信号(HBK\_PS)を生成する手段(5)と、

外部フレーム同期信号のパルス信号(FRM\_SYNC\_PS)の位相が、デジタル映像信号のフレーム同期信号のパルス信号(FRM\_PS)の位相に対して、デジタル映像信号のクロックの周期を単位として、何ドットだけ離れているかを測定する手段(6)(7)と、

外部フレーム同期信号のパルス信号(FRM\_SYNC\_PS)の位相が、デジタル映像信号のフレーム同期信号のパルス信号(FRM\_PS)の位相に対して、デジタル映像信号の水平同期信号(HBK)の周期を単位として、何ラインだけ離れているかを測定する手段(2)(3)と、30

を備える、回路。

#### 【請求項5】

位相差を測定する回路であって、該回路は、

外部フレーム同期信号(FRM\_SYNC)の立ち上がりを検出する回路(4)であって、外部フレーム同期信号(FRM\_SYNC)に位相同期するパルス信号(FRM\_SYNC\_PS)を生成する回路(4)と、

デジタル映像信号のフレーム同期信号(FRM)の立ち上がりを検出する回路(1)であって、デジタル映像信号のフレーム同期信号(FRM)に位相同期するパルス信号(FRM\_PS)を生成する回路(1)と、40

デジタル映像信号の水平同期信号(HBK)の立ち上がりを検出する回路(5)であって、デジタル映像信号の水平同期信号(HBK)に位相同期するパルス信号(HBK\_PS)を生成する回路(5)と、

デジタル映像信号の水平同期信号(HBK)のパルス信号(HBK\_PS)をリセット信号として用い、デジタル映像信号のクロック数をカウントするドット位相差カウンタ(6)と、

外部フレーム同期信号のパルス信号(FRM\_SYNC\_PS)をイネーブル信号として入力し、外部フレーム同期信号のパルス信号が入力された時点でのドット位相差カウンタのカウンタ値を保持するドット位相差レジスタ(7)と、

デジタル映像信号のフレーム同期信号のパルス信号(FRM\_PS)をリセット信号と50

して用い、デジタル映像信号の水平同期信号のパルス信号（H B K \_ P S）の周期の数をカウントするライン位相差カウンタ（2）と、

外部フレーム同期信号のパルス信号（F R M \_ S Y N C \_ P S）をイネーブル信号として入力し、外部フレーム同期信号のパルス信号が入力された時点でのライン位相差カウンタのカウンタ値を保持するライン位相差レジスタ（3）と、

を備える回路。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、外部同期基準信号から外部同期信号（外部フレーム同期信号及び外部水平同期信号）を生成する回路に関連する。外部同期信号は、例えば、デジタル映像信号（H D - S D I 又は S D - S D I）を波形表示する際にタイミング信号として用いられる。また、本発明は、外部同期信号を生成する過程において、外部同期基準信号とデジタル映像信号との位相差を測定する回路に関連する。

【背景技術】

【0002】

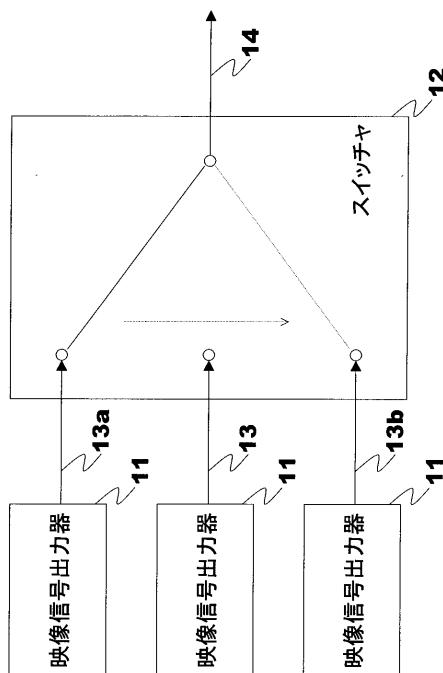

図1は、デジタル映像信号の流れを表す。図1に示すように、放送局においては、複数のデジタル映像信号が、複数の映像信号出力器11からスイッチャ12に入力される。複数のデジタル映像信号のうちの1つのデジタル映像信号は、スイッチャによって、もう1つのデジタル映像信号に切り替えられる。切り替えられたデジタル映像信号（選択された1つのデジタル映像信号14）が、スイッチャから出力される。このような状況において、切り替えられる前に選択されていたデジタル映像信号13aの位相は、切り替えられる後に選択されるデジタル映像信号13bの位相と一致している必要がある。なぜならば、デジタル映像信号のそれぞれは、スイッチング・ポイントを有しており、スイッチング・ポイント以外のポイントでデジタル映像信号13が切り替えられると、スイッチャから出力されるデジタル映像信号14の映像が、切り替えられる毎に乱れてしまうからである。要するに、複数のデジタル映像信号13間の位相が一致していると、複数のデジタル映像信号間のスイッチング・ポイントも一致し、その結果、1つのデジタル映像信号13aが、スイッチャによってもう1つのデジタル映像信号13bに切り替えられるときに、スイッチャから出力されるデジタル映像信号14の映像は、乱れない。

【0003】

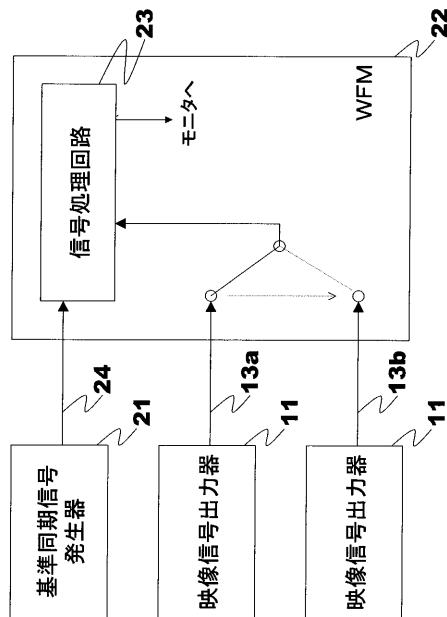

複数のデジタル映像信号間の位相を一致させるために、まず、各デジタル映像信号の位相を測定する必要がある。図2は、各デジタル映像信号の位相を測定するためのシステムの1例を表す。図2に示すように、外部基準同期信号24（アナログ基準同期信号：水平同期信号と垂直同期信号が複合されている信号）が、外部基準同期生成器21からウェーブ・フォーム・モニタ22に入力される。ウェーブ・フォーム・モニタの信号処理回路23において、外部フレーム同期信号（外部の垂直同期信号）が、外部基準同期信号24から分離される。

【0004】

また、2つのデジタル映像信号13a及び13bが、複数の映像信号出力器11からウェーブ・フォーム・モニタ22に入力される。ウェーブ・フォーム・モニタ22において、デジタル映像信号13a又は13bの何れか一方が、信号処理回路23に接続される。以下、デジタル映像信号13aが信号処理回路23に接続されていると想定して、信号処理回路の動作を説明する。信号処理回路23において、デジタル映像信号13aのクロック（パラレル・クロック：P C L K）が、デジタル映像信号13aから再生される。

【0005】

信号処理回路23において、外部基準同期信号24の外部フレーム同期信号に位相同期する外部水平同期信号であって、デジタル映像信号13aの水平同期周期と同じ周期を持つ外部水平同期信号が、外部フレーム同期信号とデジタル映像信号13aのクロックとから生成される。このような信号処理は、以下の特許文献1又は2に開示されている。なお

10

20

30

40

50

、外部フレーム同期信号は、特許文献1又は2のS D T V信号の垂直同期信号に対応し、また、外部水平同期信号は、トリガ信号に対応する。

【0006】

ウェーブ・フォーム・モニタ22において、デジタル映像信号13aのフレーム同期信号（内部フレーム同期信号）及び水平同期信号（内部水平同期信号）の代わりに、外部フレーム同期信号及び外部水平同期信号を用いて、デジタル映像信号13aが波形表示される。このように内部同期信号の代わりに外部同期信号を用いることで、外部基準同期信号24に対するデジタル映像信号13aの位相差が、デジタル映像信号13aの波形表示に反映される。デジタル映像信号13aの波形表示（例えば、デジタル映像信号13aの水平同期信号の起点）を観測することで、デジタル映像信号13aの位相を測定することができる。デジタル映像信号13aが、ウェーブ・フォーム・モニタ22に波形表示されるとき、一般に、マーカーの位置を調整して、デジタル映像信号13aの水平同期信号の起点にマーカーを一致させる。

【0007】

次に、デジタル映像信号13aの代わりに、13bが、信号処理回路23に接続される。デジタル映像信号13aの信号処理と同様にして、外部フレーム同期信号及び外部水平同期信号を用いて、デジタル映像信号13bが波形表示される。外部基準同期信号24に対するデジタル映像信号13bの位相差が、デジタル映像信号13bの波形表示に反映される。デジタル映像信号13bの波形表示（例えば、デジタル映像信号13bの水平同期信号の起点）を観測することで、デジタル映像信号13bの位相を測定することができる。このとき、デジタル映像信号13bの水平同期信号の起点と、デジタル映像信号13aの水平同期信号の起点に一致するマーカーとを観測することにより、デジタル映像信号13aと13bとの相対的な位相差を測定することができる。

【0008】

このような状況において、デジタル映像信号13bの位相を、図示されていない位相調整器（例えば、映像信号出力器11の内部の位相調整回路、映像信号出力器11とウェーブ・フォーム・モニタ22との間に接続される位相調整器など）を用いて調整することができる。デジタル映像信号13bの位相を、ウェーブ・フォーム・モニタ22を見ながら調整して、複数のデジタル映像信号（13a、13b）間の位相を一致させることができる。

【特許文献1】特開平11-215447号公報

【特許文献2】米国特許第6130708号明細書

【発明の開示】

【発明が解決しようとする課題】

【0009】

本発明の目的は、外部同期基準信号とデジタル映像信号との位相差を容易に測定する回路を提供することにある。

本発明のもう1つの目的は、外部同期基準信号とデジタル映像信号との位相差を利用して、外部同期信号（外部フレーム同期信号及び外部水平同期信号）を生成する回路を提供することにある。言い換えれば、本発明のもう1つの目的は、外部水平同期信号の新規な生成手法を提供し、外部フレーム同期信号を再度生成する手法を提供することにある。

【0010】

本発明の他の目的は、特許請求の範囲、発明の詳細な説明および図面を参照することにより、当業者にとって、明らかになるであろう。

【課題を解決するための手段】

【0011】

本発明の外部同期信号を生成する回路は、外部フレーム同期信号（F R M \_ S Y N C ）並びにデジタル映像信号のフレーム同期信号（F R M ）及び水平同期信号（H B K ）を入力する手段と、外部フレーム同期信号（F R M \_ S Y N C ）とデジタル映像信号のフレーム同期信号（F R M ）との位相差を測定する手段と、デジタル映像信号の水平同期信号（

H B K ) の周期と同じ周期を持つ信号 ( E X T \_ H ) であって、デジタル映像信号のフレーム同期信号 ( F R M ) を基準として、前記測定された位相差を有する信号 ( E X T \_ H ) を生成する手段と、デジタル映像信号のフレーム同期信号 ( F R M ) の周期と同じ周期を持つ信号 ( E X T \_ F ) であって、デジタル映像信号のフレーム同期信号 ( F R M ) を基準として、前記測定された位相差を有する信号 ( E X T \_ F ) を生成する手段と、を備え、前記生成された信号 ( E X T \_ F ) 及び ( E X T \_ H ) が、外部同期信号の外部フレーム・タイミング信号及び外部水平タイミング信号として出力される。

【 0 0 1 2 】

具体的には、外部同期信号を生成する回路は、外部フレーム同期信号 ( F R M \_ S Y N C ) の立ち上がりを検出する回路 ( 4 ) であって、外部フレーム同期信号 ( F R M \_ S Y N C ) に位相同期するパルス信号 ( F R M \_ S Y N C \_ P S ) を生成する回路 ( 4 ) と、デジタル映像信号のフレーム同期信号 ( F R M ) の立ち上がりを検出する回路 ( 1 ) であって、デジタル映像信号のフレーム同期信号 ( F R M ) に位相同期するパルス信号 ( F R M \_ P S ) を生成する回路 ( 1 ) と、デジタル映像信号の水平同期信号 ( H B K ) の立ち上がりを検出する回路 ( 5 ) であって、デジタル映像信号の水平同期信号 ( H B K ) に位相同期するパルス信号 ( H B K \_ P S ) を生成する回路 ( 5 ) と、デジタル映像信号の水平同期信号のパルス信号 ( H B K \_ P S ) をリセット信号として用い、デジタル映像信号のクロック数をカウントする第 1 カウンタ ( 6 ) と、外部フレーム同期信号のパルス信号 ( F R M \_ S Y N C \_ P S ) をイネーブル信号として入力し、外部フレーム同期信号のパルス信号が入力された時点での第 1 カウンタのカウンタ値を保持する第 1 レジスタ ( 7 ) と、デジタル映像信号のフレーム同期信号のパルス信号 ( F R M \_ P S ) をリセット信号として用い、デジタル映像信号の水平同期信号のパルス信号 ( H B K \_ P S ) の周期の数をカウントする第 2 カウンタ ( 2 ) と、外部フレーム同期信号のパルス信号 ( F R M \_ S Y N C \_ P S ) をイネーブル信号として入力し、外部フレーム同期信号のパルス信号が入力された時点での第 2 カウンタのカウンタ値を保持する第 2 レジスタ ( 3 ) と、第 1 カウンタによってカウントされるカウンタ値と、第 1 レジスタによって保持されるカウント値と一致する期間だけ、H I G H 状態を表す信号 ( E X T \_ H \_ A ) を生成する第 1 コンパレータ ( 9 ) と、第 2 カウンタによってカウントされるカウンタ値と、第 2 レジスタによって保持されるカウント値と一致する期間だけ、H I G H 状態を表す信号 ( E X T \_ F \_ A ) を生成する第 2 コンパレータ ( 8 ) と、第 2 コンパレータ ( 8 ) の信号 ( E X T \_ F \_ A ) を、第 1 コンパレータ ( 9 ) の信号 ( E X T \_ H \_ A ) のタイミングでラッチする第 1 フリップ・フロップ ( 1 0 ) と、第 1 コンパレータ ( 9 ) の信号 ( E X T \_ H \_ A ) を、デジタル映像信号のクロックのタイミングでラッチする第 2 フリップ・フロップ ( 1 1 ) と、を備える。

【 0 0 1 3 】

本発明の位相差を測定する回路は、外部フレーム同期信号 ( F R M \_ S Y N C ) に位相同期するパルス信号 ( F R M \_ S Y N C \_ P S ) を生成する手段 ( 4 ) と、デジタル映像信号のフレーム同期信号 ( F R M ) に位相同期するパルス信号 ( F R M \_ P S ) を生成する手段 ( 1 ) と、デジタル映像信号の水平同期信号 ( H B K ) に位相同期するパルス信号 ( H B K \_ P S ) を生成する手段 ( 5 ) と、外部フレーム同期信号のパルス信号 ( F R M \_ S Y N C \_ P S ) の位相が、デジタル映像信号のフレーム同期信号のパルス信号 ( F R M \_ P S ) の位相に対して、デジタル映像信号のクロックの周期を単位として、何ドットだけ離れているかを測定する手段 ( 6 ) ( 7 ) と、外部フレーム同期信号のパルス信号 ( F R M \_ S Y N C \_ P S ) の位相が、デジタル映像信号のフレーム同期信号のパルス信号 ( F R M \_ P S ) の位相に対して、デジタル映像信号の水平同期信号 ( H B K ) の周期を単位として、何ラインだけ離れているかを測定する手段 ( 2 ) ( 3 ) と、を備える。

【 0 0 1 4 】

本発明のウェーブ・フォーム・モニタは、位相差を測定する回路と、前記測定されたライン数及びドット数を記憶するメモリ手段とを備え、前記記憶されるライン数及びドット数が、ウェーブ・フォーム・モニタに表示される。

10

20

30

40

50

## 【0015】

ウェーブ・フォーム・モニタはさらに、第1入力として入力されるデジタル映像信号に関するライン数及びドット数と、第2入力として入力されるデジタル映像信号に関するライン数及びドット数との差を算出するCPUを備え、前記算出された差が、第1入力のデジタル映像信号と第2入力のデジタル映像信号との相対的な位相差として、ウェーブ・フォーム・モニタに表示される。

## 【発明を実施するための最良の形態】

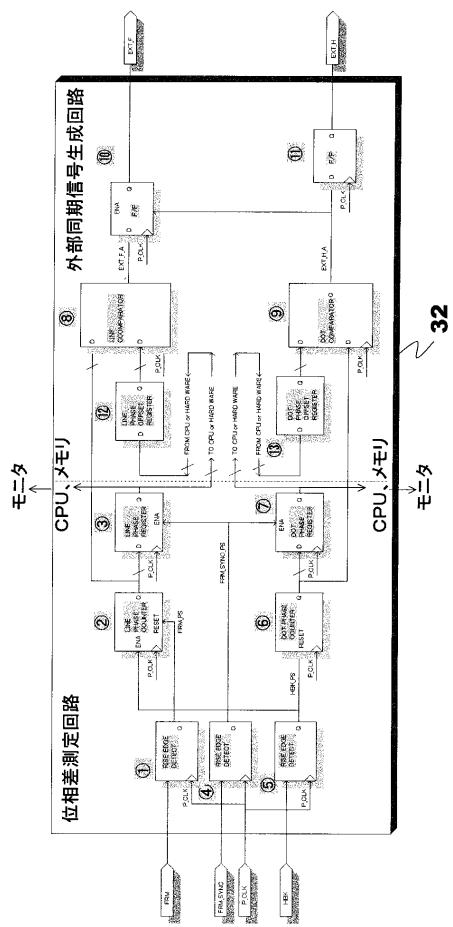

## 【0016】

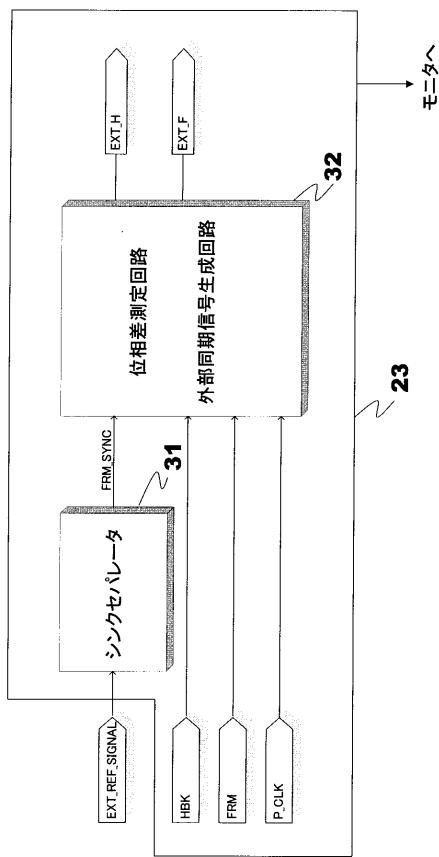

図3は、本発明の外部同期信号生成回路および位相差測定回路を備える、ウェーブ・フォーム・モニタの信号処理回路の一部の概略ブロック図である。図2及び図3に参照すると、外部基準同期信号24(EXT\_REF\_SIGNAL)が、信号処理回路23のシンクセパレータ31に入力される。外部フレーム同期信号(FRM\_SYNC)は、シンクセパレータによって、外部基準同期信号24(EXT\_REF\_SIGNAL)から分離される。

10

## 【0017】

信号処理回路23において、信号処理回路23において、クロック(PCLK)が、デジタル映像信号から再生され、クロック(PCLK)及びデジタル映像信号から、デジタル映像信号13の水平同期信号(HBK)、フレーム同期信号(FRM)が生成される。

## 【0018】

外部フレーム同期信号(FRM\_SYNC)並びにデジタル映像信号の水平同期信号(HBK)、フレーム同期信号(FRM)及びクロック(PCLK)は、本発明の外部同期信号生成回路および位相差測定回路32に入力される。外部フレーム同期信号(FRM\_SYNC)とデジタル映像信号のフレーム同期信号(FRM)との位相差、即ち、外部基準同期信号(EXT\_REF\_SIGNAL)とデジタル映像信号のフレーム同期信号(FRM)との位相差は、位相差測定回路によって、測定される。また、外部フレーム同期信号(又は外部同期基準信号)に位相同期する外部水平タイミング信号(EXT\_H)及び外部フレーム・タイミング信号(EXT\_F)は、外部同期信号生成回路によって、生成される。なお、ウェーブ・フォーム・モニタにおいて、外部水平タイミング信号(EXT\_H)及び外部フレーム・タイミング信号(EXT\_F)を用いて、デジタル映像信号が波形表示される。

20

## 【0019】

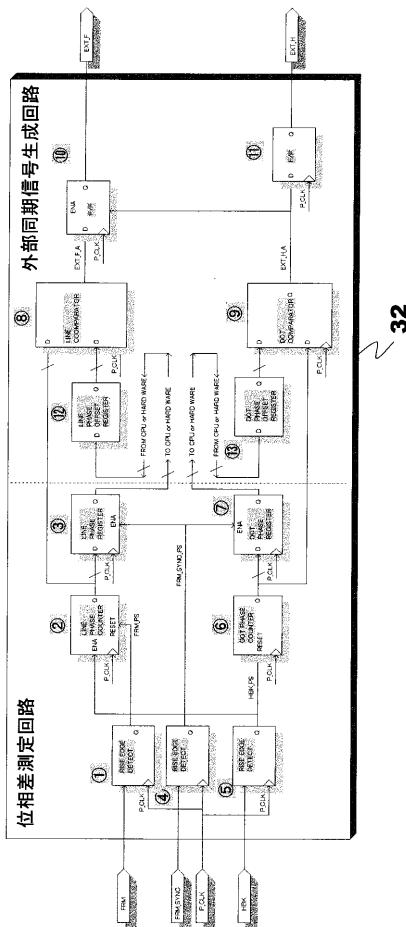

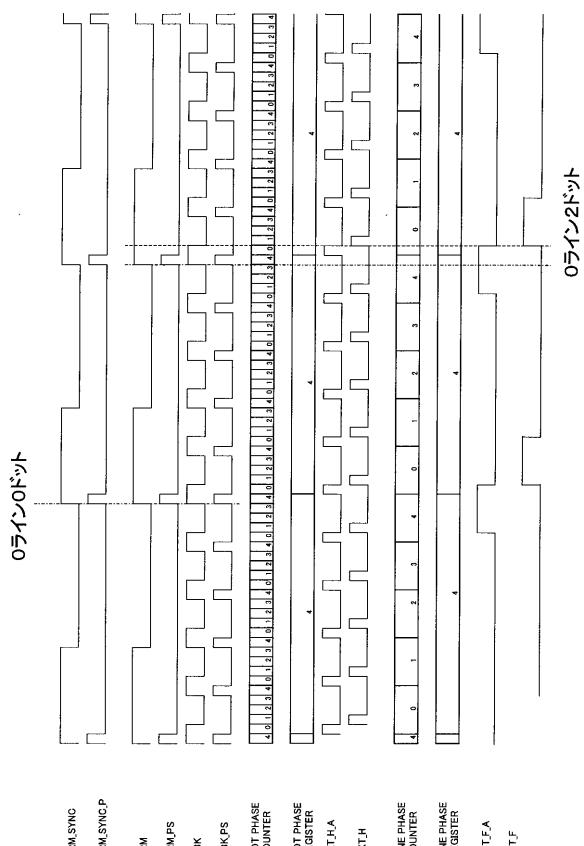

図4は、本発明の外部同期信号生成回路および位相差測定回路の具体的なブロック図であり、図5は、本発明の外部同期信号生成回路および位相差測定回路の中で処理又は生成される信号のタイミング図の1例である。

## 【0020】

なお、タイミング図を簡略化するために、図5において、外部フレーム同期信号(FRM\_SYNC)の周期は、デジタル映像信号のフレーム同期信号(FRM)の周期と同じであり、デジタル映像信号のクロック(PCLK)の周期の25倍(即ち25クロック)である。また、デジタル映像信号の水平同期信号(HBK)の周期は、デジタル映像信号のクロック(PCLK)の周期の5倍(即ち5クロック)である。さらに、外部フレーム同期信号(FRM\_SYNC)の位相は、デジタル映像信号のフレーム同期信号(FRM)の位相と一致している。

30

## 【0021】

## (位相差測定回路)

位相差測定回路は、外部フレーム同期信号(FRM\_SYNC)に位相同期する信号(FRM\_SYNC\_PS)であって、デジタル映像信号の1クロック周期分のパルス幅を持つパルス信号(FRM\_SYNC\_PS)を生成する手段(4)を備える。外部フレーム同期信号(FRM\_SYNC)に位相同期するパルス信号(FRM\_SYNC\_PS)を生成する手段(4)は、具体的には、立ち上がり検出回路(RISE\_EDGE\_DETECT)であり、その回路には、外部フレーム同期信号(FRM\_SYNC)及びデジ

40

50

タル映像信号のクロック (PCLK) が入力され、また、その回路から、外部フレーム同期信号 (FRM\_SYNC) の立ち上がりが検出される毎に、パルス信号 (FRM\_SYNC\_PS) が出力される (図5を参照)。

【0022】

また、位相差測定回路は、デジタル映像信号のフレーム同期信号 (FRM) に位相同期する信号 (FRM\_PS) であって、デジタル映像信号の1クロック周期分のパルス幅を持つパルス信号 (FRM\_PS) を生成する手段 (1) を備える。デジタル映像信号のフレーム同期信号 (FRM) に位相同期するパルス信号 (FRM\_PS) を生成する手段 (1) は、具体的には、立ち上がり検出回路 (RISE\_EDGE\_DETECT) であり、その回路には、デジタル映像信号のフレーム同期信号 (FRM) 及びクロック (PCLK) が入力され、また、その回路から、デジタル映像信号のフレーム同期信号 (FRM) の立ち上がりが検出される毎に、パルス信号 (FRM\_PS) が出力される (図5を参照)。

【0023】

さらに、位相差測定回路は、デジタル映像信号の水平同期信号 (HBK) に位相同期する信号 (HBK\_PS) であって、デジタル映像信号1クロック周期分のパルス幅を持つパルス信号 (HBK\_PS) を生成する手段 (5) を備える。デジタル映像信号の水平同期信号 (HBK) に位相同期するパルス信号 (HBK\_PS) を生成する手段 (5) は、具体的には、立ち上がり検出回路 (RISE\_EDGE\_DETECT) であり、その回路には、デジタル映像信号の水平同期信号 (HBK) 及びクロック (PCLK) が入力され、また、その回路から、デジタル映像信号の水平同期信号 (HBK) の立ち上がりが検出される毎に、パルス信号 (HBK\_PS) が出力される (図5を参照)。

【0024】

位相差測定回路はさらに、外部フレーム同期信号のパルス信号 (FRM\_SYNC\_PS) とデジタル映像信号のフレーム同期信号のパルス信号 (FRM\_PS) との位相差を測定する手段 (6) (7) (2) (3) を備える。具体的には、位相差を測定する手段 (6) (7) (2) (3) は、外部フレーム同期信号のパルス信号 (FRM\_SYNC\_PS) の位相が、デジタル映像信号のフレーム同期信号のパルス信号 (FRM\_PS) の位相に対して、デジタル映像信号の水平同期信号 (HBK) の周期を単位として、どのくらい離れているか、即ち、何ライン何ドットだけ離れているかを測定する。即ち、位相差を測定する手段 (6) (7) (2) (3) は、外部フレーム同期信号のパルス信号 (FRM\_SYNC\_PS) の位相が、デジタル映像信号のフレーム同期信号のパルス信号 (FRM\_PS) の位相に対して、何ラインだけ離れているかを測定 (2) (3) し、何ドットだけ離れているかを測定 (6) (7) する。

【0025】

より具体的には、位相差を測定する手段 (6) (7) (2) (3) は、ドット位相差カウンタ (DOT\_PHASE\_COUNTER) と、ドット位相差レジスタ (DOT\_PHASE\_REGISTER) と、ライン位相差カウンタ (LINE\_PHASE\_COUNTER) と、ライン位相差レジスタ (LINE\_PHASE\_REGISTER) とを備える。

【0026】

ドット位相差カウンタ (DOT\_PHASE\_COUNTER) は、デジタル映像信号の水平同期信号のパルス信号 (HBK\_PS) をリセット信号として入力し、デジタル映像信号のクロック (PCLK) を入力してカウントし、そのカウント値をドット位相差レジスタ (DOT\_PHASE\_REGISTER) に出力する。図5の例において、ドット位相差カウンタ (DOT\_PHASE\_COUNTER) に、デジタル映像信号の水平同期信号のパルス信号 (HBK\_PS) が入力されてから1クロック又は1ドットだけ経過した後に、ドット位相差カウンタは、カウンタ値を「0」にリセットし；1クロック又は1ドットだけさらに経過した後に、ドット位相差カウンタは、カウンタ値を「1」にカウントし；1クロック又は1ドットだけさらに経過した後に、ドット位相差カウンタは、

10

20

30

40

50

カウンタ値を「2」にカウントし；1クロック又は1ドットだけさらに経過した後に、ドット位相差カウンタは、カウンタ値を「3」にカウントし；1クロック又は1ドットだけさらに経過した後にデジタル映像信号の水平同期信号のパルス信号（H B K\_P S）が入力され、ドット位相差カウンタは、カウンタ値を「4」にカウントし；デジタル映像信号の水平同期信号のパルス信号（H B K\_P S）が入力されてから1クロック又は1ドットだけさらに経過した後に、ドット位相差カウンタは、カウンタ値を「0」にリセットする。

【0027】

ドット位相差レジスタ（D O T P H A S E R E G I S T E R）は、デジタル映像信号のクロック（P C L K）を動作クロックとして入力し、外部フレーム同期信号のパルス信号（F R M\_S Y N C\_P S）をイネーブル信号として入力し、ドット位相差カウンタからカウンタ値を入力し、外部フレーム同期信号のパルス信号が入力された時点でのカウンタ値を、保持して出力する。図5の例において、ドット位相差レジスタに、外部フレーム同期信号のパルス信号が入力されたとき、ドット位相差カウンタは、カウンタ値を「4」にカウントしているので、ドット位相差レジスタは、カウンタ値「4」を保持する。

【0028】

上述のように、ドット位相差レジスタによって保持されるカウンタ値は、外部フレーム同期信号のパルス信号（F R M\_S Y N C\_P S）の位相が、デジタル映像信号のフレーム同期信号のパルス信号（F R M\_P S）の位相に対して、デジタル映像信号のクロックの周期を単位として、何ドットだけ離れているかを意味している。図5の例において、ドット位相差レジスタによって保持されるカウンタ値「4」は、外部フレーム同期信号のパルス信号（F R M\_S Y N C\_P S）の位相が、デジタル映像信号のフレーム同期信号のパルス信号（F R M\_P S）の位相に対して、「0」ドットだけ離れていることを意味する。なお、仮に、ドット位相差レジスタによって保持されるカウンタ値が「0」、「1」、「2」及び「3」を表しているとすれば、それらのカウンタ値は、それぞれ、「1」、「2」、「3」及び「4」ドットだけ離れていることを意味する。

【0029】

ライン位相差カウンタ（L I N E P H A S E C O U N T E R）は、デジタル映像信号のフレーム同期信号のパルス信号（F R M\_P S）をリセット信号として入力し、デジタル映像信号の水平同期信号のパルス信号（H B K\_P S）をイネーブル信号として入力し、デジタル映像信号のクロック（P C L K）を動作クロックとして入力し、デジタル映像信号の水平同期信号のパルス信号（H B K\_P S）をカウントし、そのカウント値をライン位相差レジスタ（L I N E P H A S E R E G I S T E R）に出力する。図5の例において、ライン位相差カウンタ（L I N E P H A S E C O U N T E R）に、デジタル映像信号のフレーム同期信号のパルス信号（F R M\_P S）及び水平同期信号のパルス信号（H B K\_P S）が入力されてから1クロック又は1ドットだけ経過した後に、ライン位相差カウンタは、カウンタ値を「0」にリセットし；その後にデジタル映像信号の水平同期信号のパルス信号（H B K\_P S）が入力されてから1クロック又は1ドットだけ経過した後に、ライン位相差カウンタは、カウンタ値を「1」にカウントし；その後にデジタル映像信号の水平同期信号のパルス信号（H B K\_P S）がさらに入力されてから1クロック又は1ドットだけ経過した後に、ライン位相差カウンタは、カウンタ値を「2」にカウントし；その後にデジタル映像信号の水平同期信号のパルス信号（H B K\_P S）がさらに入力されてから1クロック又は1ドットだけ経過した後に、ライン位相差カウンタは、カウンタ値を「3」にカウントし；その後にデジタル映像信号の水平同期信号のパルス信号（H B K\_P S）がさらに入力されてから1クロック又は1ドットだけ経過した後に、ライン位相差カウンタは、カウンタ値を「4」にカウントし；その後にデジタル映像信号のフレーム同期信号のパルス信号（F R M\_P S）及び水平同期信号のパルス信号（H B K\_P S）が入力されてから1クロック又は1ドットだけさらに経過した後に、ライン位相差カウンタは、カウンタ値を「0」にリセットする。

【0030】

10

20

30

40

50

ライン位相差レジスタ (LINE PHASE REGISTER) は、デジタル映像信号のクロック (PCLK) を動作クロックとして入力し、外部フレーム同期信号のパルス信号 (FRM\_SYNC\_PS) をイネーブル信号として入力し、ライン位相差カウンタからカウンタ値を入力し、外部フレーム同期信号のパルス信号が入力された時点でのカウンタ値を、保持して出力する。図5の例において、ドット位相差レジスタに、外部フレーム同期信号のパルス信号が入力されたとき、ライン位相差カウンタは、カウンタ値を「4」にカウントしているので、ライン位相差レジスタは、カウンタ値「4」を保持する。

#### 【0031】

上述のように、ライン位相差レジスタによって保持されるカウンタ値は、外部フレーム同期信号のパルス信号 (FRM\_SYNC\_PS) の位相が、デジタル映像信号のフレーム同期信号のパルス信号 (FRM\_PS) の位相に対して、デジタル映像信号の水平同期信号 (HBK) の周期を単位として、何ラインだけ離れているかを意味している。図5の例において、ライン位相差レジスタによって保持されるカウンタ値「4」は、外部フレーム同期信号のパルス信号 (FRM\_SYNC\_PS) の位相が、デジタル映像信号のフレーム同期信号のパルス信号 (FRM\_PS) の位相に対して、「0」ラインだけ離れていることを意味する。なお、仮に、ドット位相差レジスタによって保持されるカウンタ値が「4」を表し、且つライン位相差レジスタによって保持されるカウンタ値が「0」、「1」、「2」及び「3」を表しているとすれば、それらのカウンタ値は、それぞれ、「1」、「2」、「3」及び「4」ラインだけ離れていることを意味する。(仮に、ドット位相差レジスタによって保持されるカウンタ値が「4」を表さず、且つライン位相差レジスタによって保持されるカウンタ値が「0」、「1」、「2」、「3」及び「4」を表しているとすれば、それらのカウンタ値は、それぞれ、「0」、「1」、「2」、「3」及び「4」ラインだけ離れていることを意味する(図6及びその説明を参照)。)

#### (外部同期信号生成回路)

外部同期信号生成回路の説明を簡略化するため、ドット位相差レジスタによって保持されるカウンタ値を調整する手段(13)及びライン位相差レジスタによって保持されるカウンタ値を調整する手段(12)を省略する。

#### 【0032】

外部同期信号生成回路は、デジタル映像信号の水平同期信号 (HBK) の周期と同じ周期を持つ信号 (EXT\_H\_A) であって、外部フレーム同期信号のパルス信号 (FRM\_SYNC\_PS) の位相がデジタル映像信号のフレーム同期信号のパルス信号 (FRM\_PS) の位相に対して離れているドット数に基づいて、デジタル映像信号のフレーム同期信号のパルス信号 (FRM\_PS) の位相に対して、位相シフトさせられた信号 (EXT\_H\_A) を生成する手段(9)を備える。デジタル映像信号の水平同期信号 (HBK) の周期と同じ周期を持つ信号 (EXT\_H\_A) を生成する手段(9)は、具体的には、ドット位相差カウンタによってカウントされるカウンタ値と、ドット位相差レジスタによって保持されるカウント値とが一致するときに、HIGH状態を表す信号 (EXT\_H\_A) を出力するコンパレータ (DOT\_COMPARATOR) である。そのコンパレータには、ドット位相差カウンタによってカウントされるカウンタ値と、ドット位相差レジスタによって保持されるカウント値とが入力され、また、デジタル映像信号のクロック (PCLK) が動作クロックとして入力される。そのコンパレータから、ドット位相差カウンタによってカウントされるカウンタ値と、ドット位相差レジスタによって保持されるカウント値と一致する期間だけ、HIGH状態を表す信号が出力され、残りの期間には、LOW状態を表す信号が出力される。図5の例において、ドット位相差カウンタ (DOT\_PHASE\_COUNTER) のカウンタ値「4」と、ドット位相差レジスタ (DOT\_PHASE\_REGISTER) のカウンタ値「4」とが一致してから1クロック又は1ドットだけ経過した後に、カウンタ値「4」がカウントされる期間(1クロック)だけ、HIGH状態を表す信号 (EXT\_H\_A) が生成される。

#### 【0033】

また、外部同期信号生成回路は、デジタル映像信号のフレーム同期信号 (FRM) の周

10

20

30

40

50

期と同じ周期を持つ信号 (EXT\_F\_A) であって、外部フレーム同期信号のパルス信号 (FRM\_SYNC\_PS) の位相がデジタル映像信号のフレーム同期信号のパルス信号 (FRM\_PS) の位相に対して離れているライン数に基づいて、デジタル映像信号のフレーム同期信号のパルス信号 (FRM\_PS) の位相に対して、位相シフトさせられた信号 (EXT\_F\_A) を生成する手段 (8) を備える。デジタル映像信号のフレーム同期信号 (FRM) の周期と同じ周期を持つ信号 (EXT\_F\_A) を生成する手段 (8) は、具体的には、ライン位相差カウンタによってカウントされるカウンタ値と、ライン位相差レジスタによって保持されるカウント値とが一致するときに、HIGH状態を表す信号 (EXT\_F\_A) を出力するコンパレータ (LINE\_COMPARATOR) である。そのコンパレータには、ライン位相差カウンタによってカウントされるカウンタ値と、ライン位相差レジスタによって保持されるカウント値とが入力され、また、デジタル映像信号のクロック (PCLK) が動作クロックとして入力される。そのコンパレータから、ライン位相差カウンタによってカウントされるカウンタ値と、ライン位相差レジスタによって保持されるカウント値と一致する期間だけ、HIGH状態を表す信号が出力され、残りの期間には、LOW状態を表す信号が出力される。図5の例において、ライン位相差カウンタ (LINE\_PHASE\_COUNTER) のカウンタ値「4」と、ライン位相差レジスタ (LINE\_PHASE\_REGISTER) のカウント値「4」とが一致してから1クロック又は1ドットだけ経過した後に、カウンタ値「4」がカウントされる期間 (5クロック) だけ、HIGH状態を表す信号 (EXT\_F\_A) が生成される。

【 0 0 3 4 】

ところで、デジタル映像信号のフレーム同期信号（F R M）の周期と同じ周期を持つ信号（E X T\_F\_A）には、外部フレーム同期信号のパルス信号（F R M\_S Y N C\_P S）と、デジタル映像信号のフレーム同期信号のパルス信号（F R M\_P S）との位相差が、完全に反映されていない。即ち、デジタル映像信号のフレーム同期信号（F R M）の周期と同じ周期を持つ信号（E X T\_F\_A）には、外部フレーム同期信号のパルス信号（F R M\_S Y N C\_P S）の位相がデジタル映像信号のフレーム同期信号のパルス信号（F R M\_P S）の位相に対して離れているライン数だけが、反映されている。

[ 0 0 3 5 ]

従って、外部同期信号生成回路は、外部フレーム同期信号のパルス信号 ( F R M \_ S Y N C \_ P S ) の位相がデジタル映像信号のフレーム同期信号のパルス信号 ( F R M \_ P S ) の位相に対して離れているドット数に基づいて、デジタル映像信号のフレーム同期信号 ( F R M ) の周期と同じ周期を持つ信号 ( E X T \_ F \_ A ) を、位相シフトさせる手段 ( 10 ) を備える。デジタル映像信号のフレーム同期信号 ( F R M ) の周期と同じ周期を持つ信号 ( E X T \_ F \_ A ) を位相シフトさせる手段 ( 10 ) は、具体的には、フリップ・フロップ ( F / F ) である。そのフリップ・フロップ ( F / F ) には、コンパレータ ( L I N E C O M P A R A T O R ) の信号 ( E X T \_ F \_ A ) が入力され、デジタル映像信号のクロック ( P C L K ) が動作クロックとして入力され、コンパレータ ( D O T C O M P A R A T O R ) の信号 ( E X T \_ H \_ A ) がイネーブル信号として入力される。そのフリップ・フロップ ( F / F ) は、コンパレータ ( L I N E C O M P A R A T O R ) の信号 ( E X T \_ F \_ A ) を、コンパレータ ( D O T C O M P A R A T O R ) の信号 ( E X T \_ H \_ A ) のタイミングでラッピングする。

[ 0 0 3 6 ]

デジタル映像信号のフレーム同期信号( F R M )の周期と同じ周期を持つ信号( E X T \_ F \_ A )を位相シフトさせる手段( 10 )によって出力される信号は、外部フレーム・タイミング信号( E X T \_ F )であり、外部フレーム・タイミング信号( E X T \_ F )には、外部フレーム同期信号のパルス信号( F R M \_ S Y N C \_ P S )の位相がデジタル映像信号のフレーム同期信号のパルス信号( F R M \_ P S )の位相に対して離れているライン数及びドット数の双方が、反映されている。図5の例において、外部フレーム・タイミング信号( E X T \_ F )は、外部フレーム同期信号のパルス信号( F R M \_ S Y N C \_ P S )に対して、0ライン2ドットの位相差( 0ライン0ドットの位相差及び2ドットの位

相差)を有している。0ライン0ドットの位相差は、外部フレーム同期信号のパルス信号(FRM\_SYNC\_PS)とデジタル映像信号のフレーム同期信号のパルス信号(FRM\_PS)との位相差であり、2ドットの位相差は、コンパレータ(LINE\_COMPARATOR)による1クロック又は1ドットの遅れ及びフリップ・フロップ(F/F)による1クロック又は1ドットの遅れである。

#### 【0037】

ところで、デジタル映像信号の水平同期信号(EXT\_H\_A)の周期と同じ周期を持つ信号(EXT\_H\_A)を生成する手段(9)によって出力される信号(EXT\_H\_A)の位相は、外部フレーム・タイミング信号(EXT\_F)の位相と一致している必要がある。言い換えれば、信号(EXT\_H\_A)は、1クロック又は1ドットの位相遅れを有する必要がある。

#### 【0038】

従って、外部同期信号生成回路は、デジタル映像信号の水平同期信号(EXT\_H\_A)の周期と同じ周期を持つ信号(EXT\_H\_A)を、位相シフトさせる手段(11)を備える。デジタル映像信号の水平同期信号(EXT\_H\_A)の周期と同じ周期を持つ信号(EXT\_H\_A)を位相シフトさせる手段(11)は、具体的には、フリップ・フロップ(F/F)である。そのフリップ・フロップ(F/F)には、コンパレータ(DOT\_COMPARATOR)の信号(EXT\_H\_A)が入力され、デジタル映像信号のクロック(PCLK)が動作クロックとして入力される。そのフリップ・フロップ(F/F)は、コンパレータ(DOT\_COMPARATOR)の信号(EXT\_F\_A)を、1クロック又は1ドットの位相だけ位相シフトさせ、外部水平タイミング信号(EXT\_H)として出力する。

#### 【0039】

上述のように、外部フレーム・タイミング信号(EXT\_F)及び外部水平タイミング信号(EXT\_H)は、外部フレーム同期信号のパルス信号(FRM\_SYNC\_PS)に対して、外部同期信号生成回路の遅延による2ドットの位相差を有している。

#### 【0040】

従って、外部同期信号生成回路は、外部フレーム・タイミング信号(EXT\_F)及び外部水平タイミング信号(EXT\_H)を位相シフトさせる手段(12)(13)を備えてもよい。外部同期信号生成回路の遅延による2ドットの位相差を取り除くために、外部フレーム・タイミング信号(EXT\_F)及び外部水平タイミング信号(EXT\_H)を位相シフトさせる手段(13)は、具体的には、ドット位相差レジスタ(7)によって保持されるカウンタ値を調整し、その値をコンパレータ(DOT\_COMPARATOR)に渡す手段(13)である。その手段(13)は、CPU又はハードウェアによって構成され、ドット位相差レジスタ(7)によって保持されるカウンタ値は、外部同期信号生成回路の遅延による2ドットだけ減算され、コンパレータ(DOT\_COMPARATOR)に出力される。図5の例を参照することによって、当業者は、コンパレータ(DOT\_COMPARATOR)によって出力される信号(EXT\_H\_A)が、外部同期信号生成回路がドット位相差レジスタ(7)によって保持されるカウンタ値を調整する手段(13)を備える前と比べて、2ドットの位相差だけ進むことを容易に理解できるであろう。この結果、外部同期信号生成回路は、外部フレーム・タイミング信号(EXT\_F)及び外部水平タイミング信号(EXT\_H)の双方が、2ドットの位相差だけ進むことを容易に理解できるであろう。

#### 【0041】

なお、仮に、外部フレーム・タイミング信号(EXT\_F)及び外部水平タイミング信号(EXT\_H)が、外部フレーム同期信号のパルス信号(FRM\_SYNC\_PS)に対して、外部同期信号生成回路の遅延以外による位相差(システム全体による位相差)を有しているとすれば、その位相差を取り除くように、ドット位相差レジスタ(7)によって保持されるカウンタ値が調整される。また、その位相差(システム全体による位相差)が、ドット単位の位相差だけでなく、ライン単位の位相差も有する場合、外部同期信号生

10

20

30

40

50

成回路は、ライン位相差レジスタ（3）によって保持されるカウンタ値を調整し、その値をコンパレータ（LINE COMPARATOR）に渡す手段（12）を備えることができる。その手段（12）は、CPU又はハードウェアによって構成される。

【0042】

図6は、本発明の外部同期信号生成回路および位相差測定回路の中で処理又は生成される信号のタイミング図のもう1つの例である。タイミング図を簡略化するために、図5と同様に、図6において、外部フレーム同期信号（FRM\_SYNC）の周期は、デジタル映像信号のフレーム同期信号（FRM）の周期と同じであり、デジタル映像信号のクロック（PCLK）の周期の25倍（即ち25クロック）である。また、デジタル映像信号の水平同期信号（HBK）の周期は、デジタル映像信号のクロック（PCLK）の周期の5倍（即ち5クロック）である。10

【0043】

図5と異なり、図6において、外部フレーム同期信号（FRM\_SYNC）の位相は、デジタル映像信号のフレーム同期信号（FRM）の位相と比べて、2ライン4ドットだけ遅れている。

【0044】

図6の例において、ドット位相差レジスタ（DOT PHASE REGISTER）は、カウンタ値「3」を保持し、その値は、4ドットの位相差を表している。また、ライン位相差レジスタ（LINE PHASE REGISTER）は、カウンタ値「2」を保持する。ドット位相差レジスタによって保持されるカウンタ値が「4」を表していないので、ライン位相差レジスタによって保持されるカウンタ値「2」は、2ラインの位相差を表している。20

【0045】

図6の例において、外部フレーム・タイミング信号（EXT\_F）は、外部フレーム同期信号のパルス信号（FRM\_SYNC\_PS）に対して、3ライン1ドット又は2ライン2ドットの位相差（2ライン4ドットの位相差及び2ドットの位相差）を有している。2ライン4ドットの位相差は、外部フレーム同期信号のパルス信号（FRM\_SYNC\_PS）とデジタル映像信号のフレーム同期信号のパルス信号（FRM\_PS）との位相差であり、2ドットの位相差は、コンパレータ（LINE COMPARATOR）による1クロック又は1ドットの遅れ及びフリップ・フロップ（F/F）による1クロック又は1ドットの遅れである。30

【0046】

外部同期信号生成回路は、外部フレーム・タイミング信号（EXT\_F）及び外部水平タイミング信号（EXT\_H）を位相シフトさせる手段（12）（13）を備えてなくてよい。外部同期信号生成回路が、外部フレーム・タイミング信号（EXT\_F）及び外部水平タイミング信号（EXT\_H）を位相シフトさせる手段（12）（13）を備えない場合、外部フレーム・タイミング信号（EXT\_F）及び外部水平タイミング信号（EXT\_H）は、外部フレーム同期信号のパルス信号（FRM\_SYNC\_PS）に対して、外部同期信号生成回路の遅延による2ドットの位相差を有する。言い換えれば、外部同期信号生成回路から出力される外部フレーム・タイミング信号（EXT\_F）及び外部水平タイミング信号（EXT\_H）は、外部フレーム同期信号のパルス信号（FRM\_SYNC\_PS）と一定の位相差を持って位相同期する。従って、外部同期信号生成回路が、外部フレーム・タイミング信号（EXT\_F）及び外部水平タイミング信号（EXT\_H）を位相シフトさせる手段（12）（13）を備えるか否かに拘わらず、当業者によって、外部フレーム・タイミング信号（EXT\_F）及び外部水平タイミング信号は、それぞれ、外部基準信号（外部フレーム同期信号及び外部水平同期信号）として利用し、デジタル映像信号の波形表示に使用されることを理解できるであろう。40

【0047】

（本発明の特徴の1つ）

本発明の外部同期信号生成回路の特徴の1つは、外部基準同期信号24（EXT\_RE

50

F\_SIGNAL) のフレーム周波数 (フレーム周期) とデジタル映像信号 13 のフレーム周波数 (フレーム周期) とが異なる場合であっても、外部フレーム・タイミング信号 (EXT\_F) を生成できる点である。なぜならば、本発明の外部同期信号生成回路は、外部基準同期信号 24 から外部フレーム同期信号を再度生成するからである。上述の特許文献 1 又は 2 に開示されている信号処理は、外部水平同期信号 (トリガ信号) のみを生成している。

#### 【0048】

外部基準同期信号 24 (EXT\_REF\_SIGNAL) のフレーム周波数 (フレーム周期) とデジタル映像信号 13 のフレーム周波数 (フレーム周期) とが異なる場合、シンクセパレータ 31 は、外部基準同期信号に多重されている 10 フィールド・リファレンス番号 (= フィールド ID) を抽出し、所定の 1 つのフィールド ID のみを持つ外部フレーム同期信号 (FRM\_SYNC) を分離する。10 フィールド・リファレンス番号は、外部基準同期信号に多重されているフィールド ID であり、外部フレーム同期信号 (FRM\_SYNC) の周期と映像信号 13 のフレーム同期信号 (FRM) の周期との最小公倍数の周期で、外部フレーム同期信号 (FRM\_SYNC) が分離され得るように、外部基準同期信号に多重されている。例えば、デジタル映像信号が HD-SDI (フォーマット: 例えば、1080p50 / 23.98、1080p / 23.98 など) であり、外部基準同期信号が NTSC (10 フィールド ID が多重されている NTSC) である場合、デジタル映像信号のフレーム周波数は、23.98 Hz であり、外部基準同期信号のフレーム周波数は、23.98 Hz である。従って、外部基準同期信号の 5 フレーム分の周期は、デジタル映像信号の 4 フレーム分の周期と一致する。シンクセパレータ 31 が、外部基準同期信号から、所定の 1 つのフィールド ID (例えば、フィールド ID = 1) のみを持つ外部フレーム同期信号 (FRM\_SYNC) を分離すると、5 フレーム中の 1 フレームのみが、位相差測定回路に出力される。言い換えれば、位相差測定回路には、外部フレーム同期信号 (FRM\_SYNC) の周期と映像信号 13 のフレーム同期信号 (FRM) の周期との最小公倍数の周期で、外部フレーム同期信号 (FRM\_SYNC) が入力される。当業者にとって、この外部フレーム同期信号 (FRM\_SYNC) によって生成される外部フレーム・タイミング信号及び外部水平タイミング信号は、それぞれ、外部基準信号 (外部フレーム同期信号及び外部水平同期信号) として利用し、デジタル映像信号の波形表示に使用されることを理解できるであろう。

#### 【0049】

(本発明のもう 1 つの実施形態)

図 7 は、本発明の位相差測定回路の具体的なブロック図のもう 1 つの例を表す。図 4 のブロック図と比べて、図 7 の位相差測定回路は、メモリを備える。

#### 【0050】

まず、デジタル映像信号 13a 及び 13b の何れか一方 (例えば、13a) が、例えば ACH 入力として、ウェーブ・フォーム・モニタに入力されると、上述のように、位相差測定回路は、外部フレーム同期信号のパルス信号 (FRM\_SYNC\_PS) とデジタル映像信号 13a のフレーム同期信号のパルス信号 (FRM\_PS) との位相差を測定する手段 (6) (7) (2) (3) を備えるので、その測定した位相差が、例えば CPU によってメモリに記憶される。具体的には、ドット位相差レジスタ (7) 及びライン位相差レジスタ (3) によって保持されるカウンタ値が、メモリに記憶され、ウェーブ・フォーム・モニタに表示される。

#### 【0051】

次に、デジタル映像信号 13a 及び 13b の何れか他方 (例えば、13b) が、例えば BCH 入力として、ウェーブ・フォーム・モニタに入力される。同様に、外部フレーム同期信号のパルス信号 (FRM\_SYNC\_PS) とデジタル映像信号 13b のフレーム同期信号のパルス信号 (FRM\_PS) との位相差がメモリに記憶される。好ましくは、ACH 入力の位相差と BCH 入力の位相差との相対的な差が、例えば CPU によって計算され、メモリに記憶され、また、ウェーブ・フォーム・モニタに表示される。

10

20

30

40

50

## 【0052】

このように、デジタル映像信号 13a と 13b との相対的な位相差を、数値（例えば、ライン数、ドット数）で表示することによって、相対的な位相差を容易に測定することができる。相対的な位相差を表す数値がゼロになるように、位相調整器によって、デジタル映像信号 13a 又は 13b の位相が調整される。

## 【図面の簡単な説明】

## 【0053】

【図 1】デジタル映像信号の流れを表す。

【図 2】各デジタル映像信号の位相を測定するためのシステムの 1 例を表す。

【図 3】本発明の外部同期信号生成回路および位相差測定回路を備える、ウェーブ・フォーム・モニタの信号処理回路の一部の概略ブロック図である。 10

【図 4】本発明の外部同期信号生成回路および位相差測定回路の具体的なブロック図である。

【図 5】本発明の外部同期信号生成回路および位相差測定回路の中で処理又は生成される信号のタイミング図の 1 例である。

【図 6】本発明の外部同期信号生成回路および位相差測定回路の中で処理又は生成される信号のタイミング図のもう 1 つの例である。

【図 7】本発明の位相差測定回路の具体的なブロック図のもう 1 つの例である。

【図 1】

【図 2】

【図3】

【図4】

【図5】

【図7】

---

フロントページの続き

(74)代理人 100120558

弁理士 住吉 勝彦

(72)発明者 鈴木 則行

神奈川県横浜市港北区綱島東2-6-33 リーダー電子株式会社内

審査官 吉川 潤

(56)参考文献 特開平04-207865 (JP, A)

特開平11-215447 (JP, A)

特開平10-133619 (JP, A)

特開昭61-141267 (JP, A)

特開2002-229501 (JP, A)

(58)調査した分野(Int.Cl., DB名)

H04N 5/073

H04N 5/12

G09G 3/20