(19) 日本国特許庁(JP)

## (12) 特 許 公 報(B2)

(11) 特許番号

特許第6486091号

(P6486091)

(45) 発行日 平成31年3月20日(2019.3.20)

(24) 登録日 平成31年3月1日(2019.3.1)

(51) Int.Cl.

F 1

|              |           |             |      |

|--------------|-----------|-------------|------|

| HO1L 29/786  | (2006.01) | HO1L 29/78  | 618E |

| HO1L 27/088  | (2006.01) | HO1L 29/78  | 618B |

| HO1L 21/8234 | (2006.01) | HO1L 29/78  | 617N |

| HO1L 27/06   | (2006.01) | HO1L 29/78  | 612B |

| HO1L 21/822  | (2006.01) | HO1L 27/088 | 331E |

請求項の数 3 (全 55 頁) 最終頁に続く

(21) 出願番号

特願2014-250466 (P2014-250466)

(22) 出願日

平成26年12月11日(2014.12.11)

(65) 公開番号

特開2015-133482 (P2015-133482A)

(43) 公開日

平成27年7月23日(2015.7.23)

審査請求日

平成29年12月6日(2017.12.6)

(31) 優先権主張番号

特願2013-257517 (P2013-257517)

(32) 優先日

平成25年12月12日(2013.12.12)

(33) 優先権主張国

日本国(JP)

(73) 特許権者 000153878

株式会社半導体エネルギー研究所

神奈川県厚木市長谷398番地

(72) 発明者 山崎 舜平

神奈川県厚木市長谷398番地 株式会社

半導体エネルギー研究所内

(72) 発明者 岡崎 健一

栃木県栃木市都賀町升塚161-2 アド

バンスト フィルム ディバイス インク

株式会社内

(72) 発明者 片山 雅博

栃木県栃木市都賀町升塚161-2 アド

バンスト フィルム ディバイス インク

株式会社内

最終頁に続く

(54) 【発明の名称】 半導体装置

## (57) 【特許請求の範囲】

## 【請求項 1】

第1のゲート電極及び第2のゲート電極と、

前記第1のゲート電極上及び前記第2のゲート電極上の第1の絶縁層と、

前記第1の絶縁層上の、前記第1のゲート電極と重なる領域を有する第1の酸化物半導体膜と、

前記第1の酸化物半導体膜上に重なる第3の酸化物半導体膜と、

前記第1の絶縁層上の、前記第2のゲート電極と重なる領域を有する第2の酸化物半導体膜と、

前記第2の酸化物半導体膜上及び前記第3の酸化物半導体膜上の第2の絶縁層と、

前記第2の絶縁層上の、前記第3の酸化物半導体膜と重なる領域を有する第3のゲート電極と、

前記第2の絶縁層上の、前記第2の酸化物半導体膜と重なる領域を有する第3の絶縁層と、

前記第3の酸化物半導体膜と電気的に接続された第1のソース電極及び第1のドレイン電極と、

前記第2の酸化物半導体膜と電気的に接続された第2のソース電極及び第2のドレイン電極と、を有し、

前記第1のゲート電極と、前記第3のゲート電極とは電気的に接続されていることを特徴とする半導体装置。

10

20

**【請求項 2】**

請求項 1において、

前記第 1 の酸化物半導体膜は、前記第 3 の酸化物半導体膜に覆われていることを特徴とする半導体装置。

**【請求項 3】**

請求項 1または請求項 2において、

前記第 1 の酸化物半導体膜、前記第 2 の酸化物半導体膜、及び前記第 3 の酸化物半導体膜はそれぞれ、インジウムと、インジウムと異なる金属元素と、を有し、

前記第 1 の酸化物半導体膜中のインジウムの原子数比は、前記第 2 の酸化物半導体膜中のインジウムの原子数比及び前記第 3 の酸化物半導体膜中のインジウムの原子数比よりも大きいことを特徴とする半導体装置。 10

**【発明の詳細な説明】****【技術分野】****【0001】**

本発明の一形態は、トランジスタを有する半導体装置に関する。

**【0002】**

なお、本発明の一態様は、上記の技術分野に限定されない。本明細書等で開示する発明の一態様の技術分野は、物、方法、または、製造方法に関するものである。または、本発明の一態様は、プロセス、マシン、マニュファクチャ、または、組成物（コンポジション・オブ・マター）に関するものである。そのため、より具体的に本明細書で開示する本発明の一態様の技術分野としては、半導体装置、表示装置、液晶表示装置、発光装置、照明装置、蓄電装置、記憶装置、それらの駆動方法、または、それらの製造方法、を一例として挙げることができる。 20

**【背景技術】****【0003】**

金属酸化物は多様に存在し、様々な用途に用いられている。金属酸化物として酸化インジウムはよく知られた材料であり、例えば、液晶表示装置などでは透明電極材料として用いられている。

**【0004】**

金属酸化物の中には半導体特性を示すものがある。半導体特性を示す金属酸化物は化合物半導体の一種である。化合物半導体とは、2種以上の原子が結合してできる半導体である。一般的に、金属酸化物は絶縁体となる。しかし、金属酸化物を構成する元素の組み合わせによっては、半導体となることが知られている。例えば、酸化タンゲステン、酸化錫、酸化インジウム、酸化亜鉛などは半導体特性を示すことが知られている。また、酸化亜鉛、又はIn-Ga-Zn系酸化物を用いたトランジスタをアクティブマトリクス型表示装置の画素のスイッチング素子などに用いる技術が開示されている（特許文献1及び特許文献2参照）。 30

**【0005】**

また、酸化物半導体が用いられたトランジスタは、アモルファスシリコンを用いたトランジスタに比べて電界効果移動度が高い。そのため、当該トランジスタを用いて、表示装置などの駆動回路を構成することもできる。 40

**【0006】**

表示装置としては、EL（エレクトロルミネセンス）表示装置や、電子ペーパーや、液晶表示装置などがあり、中でも高精細な表示が可能であるアクティブマトリクス型EL表示装置が注目を集めている。アクティブマトリクス型EL表示装置では、画素に複数のスイッチング素子を配置し、そのうちの少なくとも一つのスイッチング素子と電気的に接続する発光素子に電圧を印加することにより、一対の電極から電子および正孔がそれぞれ発光性の有機化合物を含む層に注入され、電流が流れる。そして、それらキャリア（電子および正孔）が再結合することにより、発光性の有機化合物が励起状態を形成し、その励起状態が基底状態に戻る際に発光する。このようなメカニズムから、このような発光素子は、 50

電流励起型の発光素子と呼ばれる。

【0007】

アクティブマトリクス型表示装置の用途は拡大しており、画面サイズの大面積化、高精細化及び高開口率化の要求が高まっている。また、アクティブマトリクス型表示装置の生産方法には高い生産性及び生産コストの低減が求められる。

【先行技術文献】

【特許文献】

【0008】

【特許文献1】特開2007-123861号公報

【特許文献2】特開2007-96055号公報

10

【発明の概要】

【発明が解決しようとする課題】

【0009】

絶縁表面上に複数の異なる回路を形成する場合、回路の機能等に応じて、それらを構成するトランジスタに要求される特性が異なる。アクティブマトリクス型表示装置の場合、画素部のトランジスタには、例えば、優れたスイッチング特性（電流のオンオフ比が大きいこと等）が要求される。駆動回路のトランジスタには、例えば、動作速度が速いことが要求される。表示装置が高精細であればあるほど、画像データの書き込み時間が短くなるため、駆動回路のトランジスタは高速で動作するトランジスタであることが好ましい。

【0010】

20

本発明の一態様の課題は、新規な半導体装置、その作製方法、およびその駆動方法等を提供することにある。例えば、本発明の一態様の課題は、動作速度が向上された半導体装置を提供すること、または、劣化しにくい半導体装置を提供すること、または、複数種類の回路の機能にそれぞれ合わせた複数種のトランジスタを備えた半導体装置を提供することである。

【0011】

なお、複数の課題の記載は、互いの課題の存在を妨げるものではない。なお、本発明の一態様は、これらの課題の全て解決する必要はない。また、明細書、図面、請求項などの記載から、列記した以外の課題が自ずと明らかとなるものであり、これらの課題も本発明の一態様の課題となり得る。

30

【課題を解決するための手段】

【0012】

本発明の一態様は、基板上に、第1および第2のトランジスタを含む第1の回路、および第3のトランジスタを含む第2の回路を有し、第1のトランジスタは、第1の酸化物半導体膜、および第2の酸化物半導体膜の順に積層された第1の半導体層を有し、第2のトランジスタは、第2の酸化物半導体膜を含む第2の半導体層を有し、第3のトランジスタは、第2の酸化物半導体膜を含む第3の半導体層を有し、第1のトランジスタは、ゲートに接続されたバックゲートを有する半導体装置である。

【0013】

40

本発明の一態様は、基板上に、第1および第2のトランジスタを含む第1の回路、および第3のトランジスタを含む第2の回路を有し、第1のトランジスタは、第1の酸化物半導体膜、第2の酸化物半導体膜および第3の酸化物半導体膜の順に積層された第1の半導体層を有し、第2のトランジスタは、第3の酸化物半導体膜を含む第2の半導体層を有し、第3のトランジスタは、第3の酸化物半導体膜を含む第3の半導体層を有し、第1のトランジスタは、ゲートに接続されたバックゲートを有する半導体装置である。

【0014】

上記の態様において第1のトランジスタのチャネル長を、 $2.5 \mu\text{m}$ 未満とすることができる。または第2のトランジスタに、ゲートに接続されたバックゲートを設けることができる。

【発明の効果】

50

## 【0015】

本発明の一態様により、新規な半導体装置、その作製方法、およびその駆動方法等を提供することが可能になる。例えば、本発明の一態様により、動作速度が向上された半導体装置を提供すること、または、劣化しにくい半導体装置を提供することが可能になる。または、例えば、本発明の一態様により、外部接続の端子数が削減され、且つ高画質な表示装置を提供することが可能になる。

## 【0016】

なお、これらの効果の記載は、他の効果の存在を妨げるものではない。また、本発明の一態様は、必ずしも、これらの効果の全てを有する必要はない。また、本発明の一態様について、上記以外の課題、効果、および新規な特徴については、本明細書の記載および図面から自ずと明らかになるものである。10

## 【図面の簡単な説明】

## 【0017】

- 【図1】半導体装置の構成例を説明する図。

- 【図2】半導体装置の構成例を説明する図。

- 【図3】半導体装置の構成例を説明する図。

- 【図4】半導体装置の構成例を説明する図。

- 【図5】半導体装置の構成例を説明する図。

- 【図6】半導体装置の構成例を説明する図。

- 【図7】半導体装置の作製例を説明する図。

- 【図8】半導体装置の作製例を説明する図。

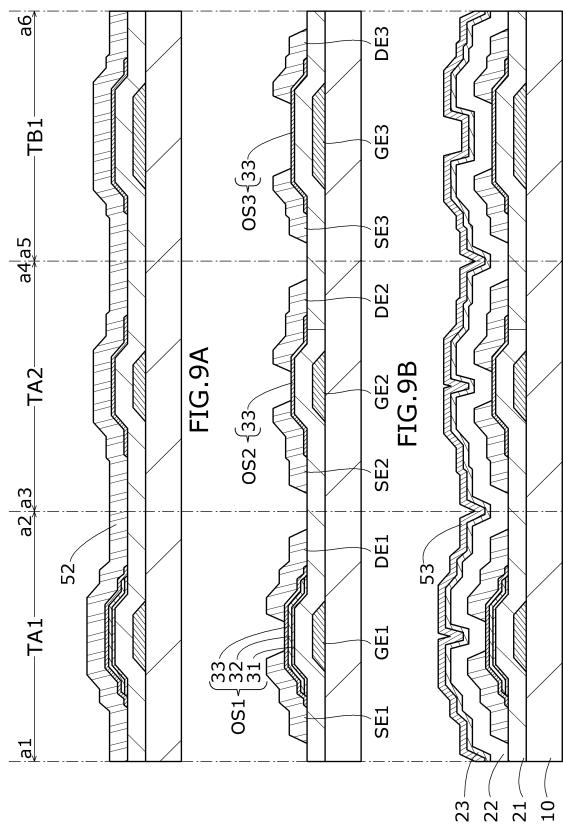

- 【図9】半導体装置の作製例を説明する図。

- 【図10】半導体装置の構成例を説明する図。

- 【図11】半導体装置の構成例を説明する図。

- 【図12】半導体装置の構成例を説明する図。

- 【図13】半導体装置の構成例を説明する図。

- 【図14】半導体装置の構成例を説明する図。

- 【図15】半導体装置の構成例を説明する図。

- 【図16】表示装置の構成例を説明する図。

- 【図17】順序回路の構成例を説明する図。

- 【図18】シフトレジスタの構成例を説明する図。

- 【図19】分配回路の構成例を説明する図。

- 【図20】分配回路の構成例を説明する図。

- 【図21】保護回路の構成例を説明する図。

- 【図22】画素の構成例および駆動方法例を説明する図。

- 【図23】画素の構成例を説明する図。

- 【図24】画素の構成例を説明する図。

- 【図25】画素の構成例を説明する図。

- 【図26】表示装置の構成例を説明する図。

- 【図27】表示装置の構成例を説明する図。

- 【図28】半導体装置の作製例を説明する図。

- 【図29】半導体装置の作製例を説明する図。

- 【図30】半導体装置の作製例を説明する図。

- 【図31】表示装置の構成例を説明する図。

- 【図32】表示装置の回路基板の構成例を説明する図。

- 【図33】情報処理装置の構成例を説明する図。

- 【図34】電子機器の構成例を説明する図。

- 【図35】酸化物半導体の断面T E M像および局所的なフーリエ変換像。

- 【図36】酸化物半導体膜のナノビーム電子回折パターンを示す図、および透過電子回折測定装置の構成例を示す図。

10

20

30

40

50

【図37】透過電子回折測定による構造解析の一例を示す図、および平面TEM像。

【発明を実施するための形態】

【0018】

本明細書等において、半導体装置とは、半導体特性を利用することで機能しうる装置全般を指す。トランジスタおよびダイオードなどの半導体素子をはじめ、半導体回路、演算装置、記憶装置は、半導体装置の一態様である。撮像装置、表示装置、液晶表示装置、発光装置、電気光学装置、発電装置（薄膜太陽電池、有機薄膜太陽電池等を含む）、及び電子機器、電気機器、および機械装置等は、半導体装置を有している場合がある。

【0019】

第1、第2、第3などの序数詞は、順序を表すだけではなく、構成要素の混同を避けるために使用する場合がある。この場合、序数詞の使用は構成要素の個数を限定するものではない。例えば、「第1の」を「第2の」または「第3の」などと適宜置き換えて、発明の一態様を説明することができる。

10

【0020】

本明細書において、「平行」とは、二つの直線が -10°以上10°以下の角度で配置されている状態をいう。従って、-5°以上5°以下の場合も含まれる。また、「垂直」とは、二つの直線が80°以上100°以下の角度で配置されている状態をいう。従って、85°以上95°以下の場合も含まれる。

【0021】

本明細書において、結晶が三方晶または菱面体晶である場合、六方晶系として表す。

20

【0022】

トランジスタにおいて「ソース」や「ドレイン」の機能は、回路動作において電流の方向が変化する場合などには入れ替わることがある。このため、本明細書においては、「ソース」や「ドレイン」の用語は、入れ替えて用いることができるものとする。

【0023】

電圧とは2点間における電位差のことをいい、電位とはある一点における静電場の中にある単位電荷が持つ静電エネルギー（電気的な位置エネルギー）のことをいう。ただし、一般的に、ある一点における電位と基準となる電位（例えば接地電位）との電位差のことを、単に電位もしくは電圧と呼び、電位と電圧が同義語として用いられることが多い。このため、本明細書では特に指定する場合を除き、電位を電圧と読み替えてよいし、電圧を電位と読み替えてよいこととする。

30

【0024】

また、本明細書において、ゲート電圧が0Vの場合、ドレイン電流が流れないとみなすことができるトランジスタを、ノーマリーオフ特性を有するトランジスタと定義する。また、ゲート電圧が0Vの場合、ドレイン電流が流れているとみなすことができるトランジスタを、ノーマリーオン特性を有するトランジスタと定義する。チャネル形成領域が酸化物半導体膜で形成されているトランジスタ（以下、OSトランジスタ）は、主にnチャネル型トランジスタになる。

【0025】

OSトランジスタのチャネル長とは、例えば、トランジスタの上面図において、酸化物半導体膜（またはトランジスタがオン状態のときに酸化物半導体膜の中で電流の流れる部分）とゲート電極とが重なる領域、またはチャネルが形成される領域における、ソース（ソース領域またはソース電極）とドレイン（ドレイン領域またはドレイン電極）との間の距離をいう。なお、一つのトランジスタにおいて、チャネル長が全ての領域で同じ値をとるとは限らない。即ち、一つのトランジスタのチャネル長は、一つの値に定まらない場合がある。そのため、本明細書では、チャネル長は、チャネルが形成される領域における、いずれか一の値、最大値、最小値または平均値とする。

40

【0026】

OSトランジスタにおいて、チャネル幅とは、例えば、酸化物半導体膜（またはトランジスタがオン状態のときに酸化物半導体膜の中で電流の流れている部分）とゲート電極とが

50

重なる領域、またはチャネルが形成される領域における、ソース電極とドレイン電極とが向かい合っている部分の長さをいう。なお、一つのトランジスタにおいて、チャネル幅がすべての領域で同じ値をとるとは限らない。即ち、一つのトランジスタのチャネル幅は、一つの値に定まらない場合がある。そのため、本明細書では、チャネル幅は、チャネルが形成される領域における、いずれか一の値、最大値、最小値または平均値とする。

#### 【0027】

なお、OSトランジスタの構造によっては、実際にチャネルが形成される領域におけるチャネル幅（以下、実効的なチャネル幅とよぶ。）と、トランジスタの上面図において示されるチャネル幅（以下、見かけ上のチャネル幅とよぶ。）と、が異なる場合がある。例えば、立体的な構造を有するトランジスタでは、実効的なチャネル幅が、トランジスタの上面図において示される見かけ上のチャネル幅よりも大きくなり、その影響が無視できなくなる場合がある。例えば、微細かつ立体的な構造を有するトランジスタでは、酸化物半導体膜の上面に形成されるチャネル領域の割合に対して、酸化物半導体膜の側面に形成されるチャネル領域の割合が大きくなる場合がある。その場合は、上面図において示される見かけ上のチャネル幅よりも、実際にチャネルが形成される実効的なチャネル幅の方が大きくなる。

10

#### 【0028】

ところで、立体的な構造を有するトランジスタにおいては、実効的なチャネル幅の、実測による見積もりが困難となる場合がある。例えば、設計値から実効的なチャネル幅を見積もるために、酸化物半導体膜の形状が既知という仮定が必要である。したがって、酸化物半導体膜の形状が正確にわからない場合には、実効的なチャネル幅を正確に測定することは困難である。

20

#### 【0029】

そこで、本明細書では、トランジスタの上面図（レイアウト図）において、酸化物半導体膜とゲート電極とが重なる領域における、ソースとドレインとが向かい合っている部分の長さである見かけ上のチャネル幅を、「囲い込みチャネル幅（SCW：Surround ed Channel Width）」とよぶ場合がある。また、本明細書では、単にチャネル幅と記載した場合には、囲い込みチャネル幅または見かけ上のチャネル幅を指す場合がある。または、本明細書では、単にチャネル幅と記載した場合には、実効的なチャネル幅を指す場合がある。なお、チャネル長、チャネル幅、実効的なチャネル幅、見かけ上のチャネル幅、および囲い込みチャネル幅などは、トランジスタの断面TEM像などを取得し、その画像を解析することなどによって、値を決定することができる。

30

#### 【0030】

トランジスタの電界効果移動度や、チャネル幅当たりの電流値などを計算で求める場合、囲い込みチャネル幅を用いて計算する場合がある。その場合には、実効的なチャネル幅を用いて計算する場合とは異なる値になる場合がある。

#### 【0031】

以下に説明する実施の形態及び実施例において、同一部分または同様の機能を有する部分には、同一の符号または同一のハッチパターンを異なる図面間で共通して用いる場合がある。また、そのような部分については、その繰り返しの説明は省略する場合がある。本明細書で参照する図に記載されている構成要素のサイズ（例えば、膜の厚さ、基板の厚さ、部材の長さ、領域のサイズ等）は、明瞭化のために誇張されている場合がある。よって、必ずしもそのスケールに限定されない。

40

#### 【0032】

以下では、本発明の実施の形態について図面を用いて詳細に説明する。ただし、本発明は以下の説明に限定されず、本発明の趣旨及びその範囲から逸脱することなくその形態及び詳細を様々に変更し得ることは、当業者であれば容易に理解される。従って、本発明は、以下に示す実施の形態の記載内容に限定して解釈されるものではない。

#### 【0033】

また、以下に複数の本発明の実施の形態を示すが、互いの実施の形態を適宜組み合わせる

50

ことが可能である。また、1つの実施の形態の中に、いくつかの構成例が示される場合は、互いに構成例を適宜組み合わせることが可能である。

#### 【0034】

##### (実施の形態1)

本実施の形態では、半導体装置の一例として、チャネル形成領域が酸化物半導体膜で形成されているトランジスタ(OTSトランジスタ)、およびその作製方法等について説明する。また、本実施の形態では、デバイス構造の異なる複数のトランジスタを同一絶縁表面に有する半導体装置について説明する。

#### 【0035】

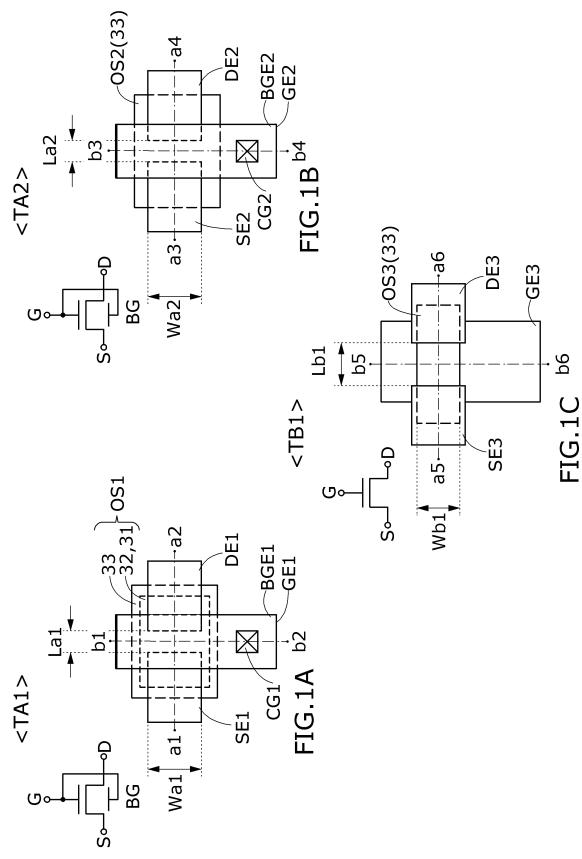

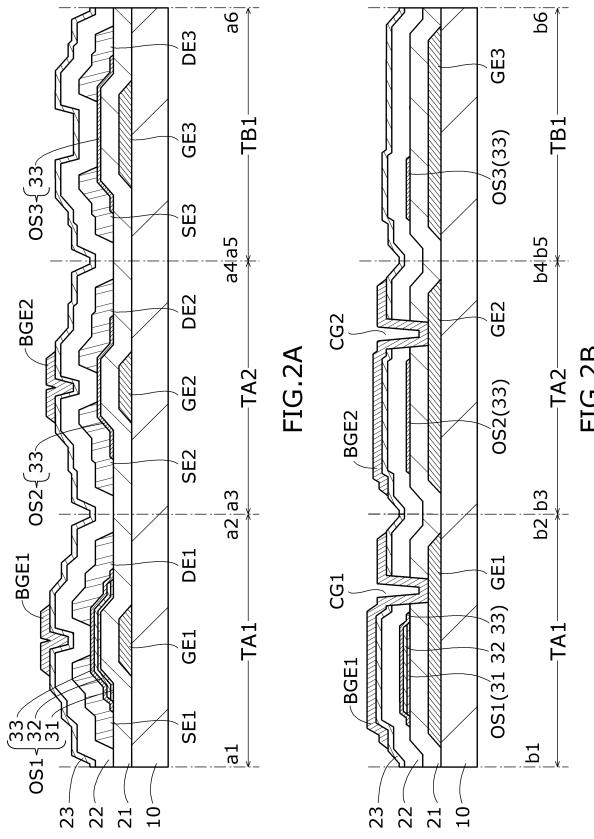

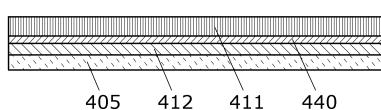

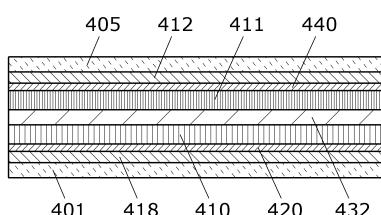

図1A、図1Bおよび図1Cに、デバイス構造の異なる3つのトランジスタ(TA1、TA2、TB1)の上面図(レイアウト図)と、それぞれの回路記号を示す。図2は、トランジスタ(TA1、TA2、TB1)の断面図である。トランジスタTA1のa1-a2線およびb1-b2線による断面図、トランジスタTA2のa3-a4線およびb3-b4線による断面図、ならびにトランジスタTB1のa5-a6線、b5-b6線による断面図を、図2A、図2Bに示す。これらトランジスタのチャネル長方向の断面構造が、図2Aに示され、同チャネル幅方向の断面構造が図2Bに示されている。

#### 【0036】

図2A、図2Bに示すように、トランジスタ(TA1、TA2、TB1)は、同一絶縁表面上に集積されており、これらのトランジスタは、同一の作製工程で作製することが可能である。なお、ここではデバイス構造の明瞭化のため、各トランジスタのゲート(G)、ソース(S)、およびドレイン(D)へ信号や電位を供給するための配線との電気的な接続は省略している。

#### 【0037】

トランジスタTA1(図1A)、トランジスタTA2(図1B)は、ゲート(G)とバックゲート(BG)を有するトランジスタである。トランジスタTA1、トランジスタTA2はバックゲートをゲートに接続した構造である。トランジスタTB1(図1C)は、BGを有さないトランジスタである。図2に示すように、これらのトランジスタ(TA1、TA2、TB1)は、基板10に形成されている。以下、図1、図2を参照して、これらのトランジスタの構成を説明する。

#### 【0038】

##### <トランジスタTA1>

トランジスタTA1は、ゲート電極GE1、ソース電極SE1、ドレイン電極DE1、バックゲート電極BGE1、および酸化物半導体層OTS1を有する。

#### 【0039】

以下の説明において、トランジスタTA1をTA1と呼ぶ、バックゲートをBGと呼ぶ、酸化物半導体層OTS1をOTS1や層OTS1と呼ぶ等、素子や素子の構成要素を省略して呼ぶ場合がある。また、信号、電位、回路などについても同様に省略する場合がある。

#### 【0040】

また、本実施の形態では、OTSトランジスタのチャネル長は、ソース電極とドレイン電極間の距離とする。また、OTSトランジスタのチャネル幅は、酸化物半導体層とゲート電極が重なる領域でのソース電極またはドレイン電極の幅とする。例えば、図1Aに示すように、トランジスタTA1のチャネル長はLa1であり、チャネル幅はWa1である。

#### 【0041】

層OTS1は、絶縁層21を介して電極GE1と重なっている。層OTS1の上面および側面に接して一対の電極(SE1、DE1)が形成されている。図1Aに示すように、層OTS1は、電極GE1および一対の電極(SE1、DE1)と重ならない部分を有している。層OTS1は、チャネル長方向の長さがチャネル長La1よりも長く、かつチャネル幅方向の長さがチャネル幅Wa1よりも長い。

#### 【0042】

層OTS1、電極GE1、電極SE1および電極DE1を覆って、絶縁層22および絶縁層

10

20

30

40

50

23が形成されている。絶縁層23上に電極BGE1が形成されている。電極BGE1は、層OS1および電極GE1と重なるように設けられている。ここでは、一例として、レイアウト図において、電極GE1と同じ形状で、同じ位置に配置されるように電極BGE1を設けている。電極BGE1は、絶縁層21-23を貫通する開口CG1において、電極GE1に接している。この構造により、トランジスタTA1のゲート(G)とバックゲート(BG)が電気的に接続される。

#### 【0043】

図2Bのチャネル幅方向の断面図が示すように、トランジスタTA1は、チャネル形成領域(チャネル)が電極GE1および電極BGE1で囲まれているデバイス構造を有する。そのため、TA1のチャネル形成領域は、電極GE1だけでなく電極BGE1により形成される電場の影響を受けることになる。そのため、バックゲート電極BGE1をゲート電極GE1に接続することで、トランジスタTA1のオン電流を増加させることができる。また、トランジスタTA1の電界効果移動度を向上させることができる。また、トランジスタTA1のしきい値電圧など電気特性の変動を抑えることができる。

10

#### 【0044】

また、バックゲート電極BGE1を設けることで、トランジスタTA1の強度を向上させることができる。基板10の曲げ等の変形に対して、電極BGE1が補強部材となってトランジスタTA1を壊れにくくすることができる。

#### 【0045】

チャネル形成領域を含む層OS1は多層構造であり、ここでは、一例として3つの酸化物半導体膜(31、32、33)でなる3層構造としている。層OS1を構成する酸化物半導体膜は、少なくとも1つ同じ金属元素を含む金属酸化物膜であることが好ましく、Inを含むことが特に好ましい。トランジスタの半導体層を構成することが可能なInを含む金属酸化物としては、In-Ga酸化物、In-M-Zn酸化物(MはAl、Ga、Y、Zr、La、Ce、またはNd)が代表的である。また、このような金属酸化物に他の元素や材料を添加した材料を用いることもできる。

20

#### 【0046】

酸化物半導体膜32は、トランジスタTA1のチャネル形成領域を構成する膜である。また、酸化物半導体膜33は、後述するトランジスタTA2およびトランジスタTB1では、チャネル形成領域を構成する膜である。そのため、トランジスタTA1では酸化物半導体膜32に、トランジスタTA2およびTB1では酸化物半導体膜33にチャネルが形成されるように、酸化物半導体膜31-33の主成分である金属元素の原子数比を調節することが好ましい。

30

#### 【0047】

トランジスタTA1において、酸化物半導体膜32にチャネルが形成されるようにすることで、チャネル形成領域が絶縁層21、絶縁層22に接しないようにすることができる。また、酸化物半導体膜31-33を少なくとも1つ同じ金属元素を含む金属酸化物膜とすることで、酸化物半導体膜32と酸化物半導体膜31の界面、および酸化物半導体膜32と酸化物半導体膜33の界面において、界面散乱が起こりにくくすることができる。これにより、トランジスタTA1の電界効果移動度をトランジスタTA2やトランジスタTB1よりも高くすることができる、また、オン状態でのドレイン電流(オン電流)を増加させることができる。

40

#### 【0048】

##### <トランジスタTA2>

トランジスタTA2は、ゲート電極GE2、ソース電極SE2、ドレイン電極DE2、バックゲート電極BGE2、および酸化物半導体層OS2を有する。電極BGE2は、絶縁層21-23を貫通する開口CG2において電極GE2に接している。トランジスタTA2は、トランジスタTA1の変形例であり、層OS2が酸化物半導体膜33である単層構造である点でトランジスタTA1と異なり、その他については同様である。ここでは、トランジスタTA2のチャネル長La2、チャネル幅Wa2は、トランジスタTA1のチャ

50

ネル長 L a 1、チャネル幅 W a 1 と等しくなるようにしている。

【 0 0 4 9 】

<トランジスタ T B 1 >

トランジスタ T B 1 は、ゲート電極 G E 3、ソース電極 S E 3、ドレイン電極 D E 3 および酸化物半導体層 O S 3 を有する。トランジスタ T B 1 は、トランジスタ T A 2 の変形例である。層 O S 3 は、トランジスタ T A 2 と同様に酸化物半導体膜 3 3 でなる单層構造である。トランジスタ T A 2 とは、バックゲート電極を有していない点で異なる。また、層 O S 3 および電極 ( G E 3、S E 3、D E 3 ) のレイアウトおよびサイズが異なる。図 1 C に示すように、層 O S 3 は、電極 G E 3 と重なっていない領域は、電極 S E 3 または電極 D E 3 の何れかと重なっている。そのため、トランジスタ T B 1 のチャネル幅 W b 1 は 10 層 O S 3 の幅で決定される。チャネル長 L b 1 は、トランジスタ T A 2 と同様、電極 S E 3 と電極 D E 3 間の距離で決定され、ここでは、トランジスタ T A 2 のチャネル長 L a 2 よりも長くしている。

【 0 0 5 0 】

[ 絶縁層 ]

絶縁層 2 1、絶縁層 2 2 および絶縁層 2 3 は、基板 1 0 のトランジスタ ( T A 1、T A 2、T B 1 ) が形成される領域全体に形成される膜である。絶縁層 2 1、2 2 および 2 3 は、単層あるいは複数層の絶縁膜で形成される。絶縁層 2 1 は、トランジスタ ( T A 1、T A 2、T B 1 ) のゲート絶縁層を構成する膜である。また、絶縁層 2 2 および絶縁層 2 3 は、トランジスタ ( T A 1、T A 2、T B 1 ) のバックチャネル側のゲート絶縁層を構成する膜である。また、最上面の絶縁層 2 3 は、基板 1 0 に形成されるトランジスタの保護膜として機能するような材料で形成することが好ましい。絶縁層 2 3 は適宜設ければよい。3 層目の電極 B G E 1 と 2 層目の電極 ( S E 1、D E 1 ) を絶縁するために、これらの間に少なくとも 1 層絶縁膜が存在していればよい。 20

【 0 0 5 1 】

これら絶縁層 2 1 - 2 3 を構成する絶縁膜としては、酸化アルミニウム、酸化マグネシウム、酸化シリコン、酸化窒化シリコン、窒化酸化シリコン、窒化シリコン、酸化ガリウム、酸化ゲルマニウム、酸化イットリウム、酸化ジルコニウム、酸化ランタン、酸化ネオジム、酸化ハフニウムまたは酸化タンタル等でなる膜があげられる。また、これらの絶縁膜は、スパッタリング法、C V D 法、M B E 法、A L D 法または P L D 法を用いて形成することができる。 30

【 0 0 5 2 】

[ 酸化物半導体膜 ]

ここでは、O S トランジスタの半導体層を構成する酸化物半導体膜について説明する。層 O S 1 のように半導体層を多層構造とする場合、これらを構成する酸化物半導体膜は、少なくとも 1 つ同じ金属元素を含む金属酸化物膜であることが好ましく、I n を含むことが好ましい。

【 0 0 5 3 】

例えば、酸化物半導体膜 3 1 が I n - G a 酸化物膜の場合、I n の原子数比を G a の原子数比よりも小さくする。I n - M - Z n 酸化物膜 ( M は A l、G a、Y、Z r、L a、C e、または N d ) の場合、I n の原子数比を M の原子数比よりも小さくする。この場合、Z n の原子数比が最も大きくなるようにすることができる。 40

【 0 0 5 4 】

例えば、酸化物半導体膜 3 2 が I n - G a 酸化物膜の場合、I n の原子数比を G a の原子数比よりも大きくする。I n - M - Z n 酸化物膜の場合、I n の原子数比を M の原子数比よりも大きくする。I n - M - Z n 酸化物膜では、I n の原子数比が M および Z n の原子数比よりも大きくすることが好ましい。

【 0 0 5 5 】

例えば、酸化物半導体膜 3 3 が I n - G a 酸化物膜の場合、I n の原子数比を G a の原子数比と同じにする、または小さくする。I n - M - Z n 酸化物膜の場合、I n の原子数比 50

をMの原子数比と同じにする。この場合、Znの原子数比が、InおよびMよりも大きくなることができる。ここでは、酸化物半導体膜33は、トランジスタTA2、トランジスタTB1のチャネル形成領域を構成する膜である。

#### 【0056】

酸化物半導体膜31-33の原子数比は、スパッタリング法で成膜する場合は、ターゲットの構成材料の原子数比等を調節することで調節可能である。また、CVD法で成膜する場合は、原料ガスの流量比などを調節することで調節可能である。以下、酸化物半導体膜31-33として、スパッタリング法でIn-M-Zn酸化物膜を形成する場合を例に、成膜に使用されるターゲットについて述べる。

#### 【0057】

酸化物半導体膜31のターゲットの金属元素の原子数比をIn : M : Zn = x1 : y1 : z1とすると、x1 / y1は、1 / 6以上1未満であることが好ましい。また、z1 / y1は、1 / 3以上6以下、さらには1以上6以下であることが好ましい。

#### 【0058】

ターゲットの金属元素の原子数比の代表例としては、In : M : Zn = 1 : 3 : 2、In : M : Zn = 1 : 3 : 4、In : M : Zn = 1 : 3 : 6、In : M : Zn = 1 : 3 : 8、In : M : Zn = 1 : 4 : 4、In : M : Zn = 1 : 4 : 5、In : M : Zn = 1 : 4 : 6、In : M : Zn = 1 : 4 : 7、In : M : Zn = 1 : 4 : 8、In : M : Zn = 1 : 5 : 5、In : M : Zn = 1 : 5 : 6、In : M : Zn = 1 : 5 : 7、In : M : Zn = 1 : 5 : 8、In : M : Zn = 1 : 6 : 8等がある。

#### 【0059】

酸化物半導体膜32のターゲットの金属元素の原子数比をIn : M : Zn = x2 : y2 : z2とすると、x2 / y2は、1より大きく6以下であることが好ましい。また、z2 / y2は1より大きく6以下であることが好ましい。ターゲットの金属元素の原子数比の代表例としては、In : M : Zn = 2 : 1 : 1.5、In : M : Zn = 2 : 1 : 2.3、In : M : Zn = 2 : 1 : 3、In : M : Zn = 3 : 1 : 2、In : M : Zn = 3 : 1 : 3、In : M : Zn = 3 : 1 : 4等がある。

#### 【0060】

酸化物半導体膜33のターゲットの金属元素の原子数比をIn : M : Zn = x3 : y3 : z3とすると、x3 / y3は、1 / 6以上1以下であることが好ましい。また、z3 / y3は、1 / 3以上6以下、さらには1以上6以下であることが好ましい。ターゲットの金属元素の原子数比の代表例としては、In : M : Zn = 1 : 1 : 1、In : M : Zn = 1 : 1 : 1.2、In : M : Zn = 1 : 3 : 2、In : M : Zn = 1 : 3 : 4、In : M : Zn = 1 : 3 : 6、In : M : Zn = 1 : 3 : 8、In : M : Zn = 1 : 4 : 4、In : M : Zn = 1 : 4 : 5、In : M : Zn = 1 : 4 : 6、In : M : Zn = 1 : 4 : 7、In : M : Zn = 1 : 4 : 8、In : M : Zn = 1 : 5 : 5、In : M : Zn = 1 : 5 : 6、In : M : Zn = 1 : 5 : 7、In : M : Zn = 1 : 5 : 8、In : M : Zn = 1 : 6 : 8等がある。

#### 【0061】

In-M-Zn酸化物膜の成膜用ターゲットにおいて、金属元素の原子数比をIn : M : Zn = x : y : zとした場合、1 - z / y - 6とすることで、In-M-Zn酸化物膜としてCAAC-OS膜が形成されやすくなるため好ましい。なお、CAAC-OS膜については後述する。

#### 【0062】

酸化物半導体膜31-33としては、キャリア密度の低い酸化物半導体膜を用いる。例えば、酸化物半導体膜31-33として、キャリア密度が $1 \times 10^{17}$ 個/cm<sup>3</sup>以下、好ましくは $1 \times 10^{15}$ 個/cm<sup>3</sup>以下、さらに好ましくは $1 \times 10^{13}$ 個/cm<sup>3</sup>以下、特に好ましくは $8 \times 10^{11}$ /cm<sup>3</sup>以下、さらに好ましくは $1 \times 10^{11}$ /cm<sup>3</sup>以下、さらに好ましくは $1 \times 10^{10}$ /cm<sup>3</sup>以下であり、 $1 \times 10^{-9}$ /cm<sup>3</sup>以上の酸化物半導体膜を用いる。

10

20

30

40

50

## 【0063】

酸化物半導体膜31-33として、不純物濃度が低く、欠陥準位密度の低い酸化物半導体膜を用いることで、さらに優れた電気特性を有するトランジスタを作製することができる。ここでは、不純物濃度が低く、欠陥準位密度の低い（酸素欠損の少ない）ことを高純度真性または実質的に高純度真性とよぶ。高純度真性または実質的に高純度真性である酸化物半導体は、キャリア発生源が少ないため、キャリア密度を低くすることができる場合がある。従って、当該酸化物半導体膜にチャネル領域が形成されるトランジスタは、しきい値電圧がマイナスとなる電気特性（ノーマリーオンともいう。）になることが少ない。また、高純度真性または実質的に高純度真性である酸化物半導体膜は、欠陥準位密度が低いため、トラップ準位密度も低くなる場合がある。また、高純度真性または実質的に高純度真性である酸化物半導体膜は、オフ電流が著しく小さく、チャネル幅が $1 \times 10^6 \mu\text{m}$ でチャネル長Lが $10 \mu\text{m}$ の素子であっても、ソース電極とドレイン電極間の電圧（ドレン電圧）が1Vから10Vの範囲において、オフ電流が、半導体パラメータアナライザの測定限界以下、すなわち $1 \times 10^{-13} \text{ A}$ 以下という特性を得ることができる。従って、当該酸化物半導体膜にチャネル領域が形成されるトランジスタは、電気特性の変動が小さく、信頼性の高いトランジスタとなる。不純物としては、水素、窒素、アルカリ金属、またはアルカリ土類金属等がある。

## 【0064】

酸化物半導体膜に含まれる水素は金属原子と結合する酸素と反応して水になると共に、酸素が脱離した格子（または酸素が脱離した部分）に酸素欠損が形成される。当該酸素欠損に水素が入ることで、キャリアである電子が生成される場合がある。また、水素の一部が金属原子と結合する酸素と結合することで、キャリアである電子を生成する場合がある。従って、水素が含まれている酸化物半導体を用いたトランジスタはノーマリーオン特性となりやすい。

## 【0065】

このため、酸化物半導体膜31-33は酸素欠損と共に、水素ができる限り低減されていることが好ましい。具体的には、酸化物半導体膜31-33において、二次イオン質量分析法（S I M S : Secondary Ion Mass Spectrometry）により得られる水素濃度を、 $5 \times 10^{19} \text{ atoms/cm}^3$ 以下、より好ましくは $1 \times 10^{19} \text{ atoms/cm}^3$ 以下、 $5 \times 10^{18} \text{ atoms/cm}^3$ 未満、好ましくは $1 \times 10^{18} \text{ atoms/cm}^3$ 以下、より好ましくは $5 \times 10^{17} \text{ atoms/cm}^3$ 以下、さらに好ましくは $1 \times 10^{16} \text{ atoms/cm}^3$ 以下とする。

## 【0066】

酸化物半導体膜31-33に第14族元素の一つであるシリコンや炭素が含まれると、膜中の酸素欠損が増加し、これらの膜がn型化してしまう。このため、酸化物半導体膜31-33におけるシリコンや炭素の濃度（S I M Sにより得られる濃度）を、 $2 \times 10^{18} \text{ atoms/cm}^3$ 以下、好ましくは $2 \times 10^{17} \text{ atoms/cm}^3$ 以下とする。

## 【0067】

また、酸化物半導体膜31-33において、S I M Sにより得られるアルカリ金属またはアルカリ土類金属の濃度を、 $1 \times 10^{18} \text{ atoms/cm}^3$ 以下、好ましくは $2 \times 10^{16} \text{ atoms/cm}^3$ 以下にする。アルカリ金属及びアルカリ土類金属は、酸化物半導体と結合するとキャリアを生成する場合があり、トランジスタのオフ電流が増大してしまうことがある。このため、酸化物半導体膜31-33のアルカリ金属またはアルカリ土類金属の濃度を低減することが好ましい。

## 【0068】

酸化物半導体膜31-33に窒素が含まれていると、キャリアである電子が生じ、キャリア密度が増加し、n型化しやすい。そのため窒素が含まれている酸化物半導体を用いたトランジスタはノーマリーオン特性となりやすいので、酸化物半導体膜31-33の窒素含有量はできる限り低減されていることが好ましい、例えば、二次イオン質量分析法により得られる窒素濃度を $5 \times 10^{18} \text{ atoms/cm}^3$ 以下にすることが好ましい。

**【 0 0 6 9 】**

以上、酸化物半導体膜31-33について述べたが、これらに限られず、必要とするトランジスタの半導体特性及び電気特性（電界効果移動度、しきい値電圧等）に応じて適切な組成の酸化物半導体膜を用いればよい。また、必要とするトランジスタの半導体特性及び電気特性を得るために、酸化物半導体膜31-33のキャリア密度や不純物濃度、欠陥密度、金属元素と酸素の原子数比、原子間距離、密度等を適切なものとすることが好ましい。

**【 0 0 7 0 】**

トランジスタTA1は、GaまたはM（MはAl、Ga、Y、Zr、La、Ce、またはNd）の原子数比よりもInの原子数比が大きい酸化物半導体膜32でチャネルが形成されるため、電界効果移動度を高くすることができる。代表的には、その電界効果移動度は、 $10\text{ cm}^2/\text{Vs}$ より大きく $60\text{ cm}^2/\text{Vs}$ 未満、好ましくは $15\text{ cm}^2/\text{Vs}$ 以上 $50\text{ cm}^2/\text{Vs}$ 未満である。そのため、アクティブマトリクス型表示装置の回路にトランジスタTA1を用いる場合は、高速動作が要求される駆動回路に好適である。10

**【 0 0 7 1 】**

チャネル形成領域が酸化物半導体膜33で形成されるトランジスタTA2、TB1は、トランジスタTA1よりも電界効果移動度が低く、その大きさは、 $3\text{ cm}^2/\text{Vs}$ 以上 $10\text{ cm}^2/\text{Vs}$ 以下程度である。トランジスタTA2、TB1は、酸化物半導体膜32を有していないため、トランジスタTA1よりも光によって劣化しにくく、光照射によるオフ電流の増大量が少ない。そのため、チャネル形成領域が酸化物半導体膜33で形成されるトランジスタTA2、TB1は光が照射されるような画素部に好適である。 $10\text{ cm}^2/\text{Vs}$ 以下程度の電界効果移動度とする場合、トランジスタのチャネル長は $2.5\mu\text{m}$ 以上とることができること。

**【 0 0 7 2 】**

トランジスタTA1は、酸化物半導体膜32を有しないトランジスタTA2と比較して、光が照射されるとオフ状態における電流が増大しやすい。そのため、トランジスタTA1は、遮光が十分できない画素部よりも、光の影響が少ない画素部の周辺回路（例えば、駆動回路）に適している。もちろん、トランジスタTA2、TB1のような構成のトランジスタも、駆動回路などの画素部以外の回路に設けることが可能である。20

**【 0 0 7 3 】**

以上、トランジスタ（TA1、TA2、TB1）について述べたが、これらに限られず、必要とするトランジスタの半導体特性及び電気特性に応じて、トランジスタの構成を変更すればよい。例えば、バックゲート電極の有無、酸化物半導体層の積層構造、酸化物半導体層、ゲート電極、ソース電極およびドレイン電極の形状や配置等を適宜変更することができる。以下、トランジスタのいくつかの他の構成例を示す。30

**【 0 0 7 4 】**

<トランジスタTA3、TA4>

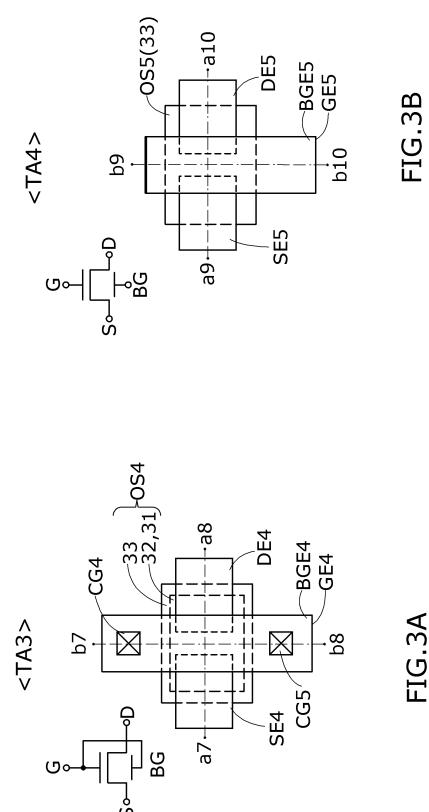

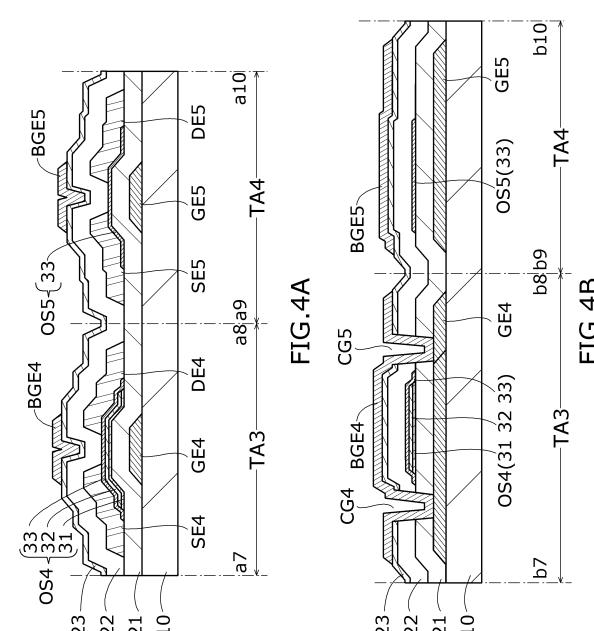

図3A、図3Bに、それぞれ、トランジスタTA3、トランジスタTA4の上面図（レイアウト図）と、その回路記号を示す。図4A、図4Bに、トランジスタTA3のa7-a8線およびb7-b8線による断面図、並びにトランジスタTA4のa9-a10線およびb9-b10線による断面図を示す。40

**【 0 0 7 5 】**

トランジスタTA3は、ゲート電極GE4、酸化物半導体層OS4、ソース電極SE4、ドレイン電極DE4、およびバックゲート電極BGE4を有する。トランジスタTA3は、トランジスタTA1の変形例であり、電極BGE4が、2つの開口CG4、CG5において、電極GE4と接している点がトランジスタTA1と異なり、他はトランジスタTA1と同様である。図4Bに示すように、チャネル幅方向で、層OS4が電極GE4と電極BGE4で囲まれており、トランジスタTA3の強度をより向上させることができる。

**【 0 0 7 6 】**

トランジスタTA4は、ゲート電極GE5、酸化物半導体層OS5、ソース電極SE5、

50

ドレイン電極 D E 5、およびバックゲート電極 B G E 5 を有する。トランジスタ T A 4 は、トランジスタ T A 2 の変形例であり、電極 B G E 5 を電極 G E 5 と接続させず、電極 B G E 5 に、電極 G E 5 と異なる信号や電位を入力可能としている。例えば、電極 G E 5 にトランジスタ T A 4 の導通状態を制御する信号を入力し、電極 B G E 5 にトランジスタ T A 4 のしきい値電圧を補正するような信号や電位を入力することが可能である。

#### 【 0 0 7 7 】

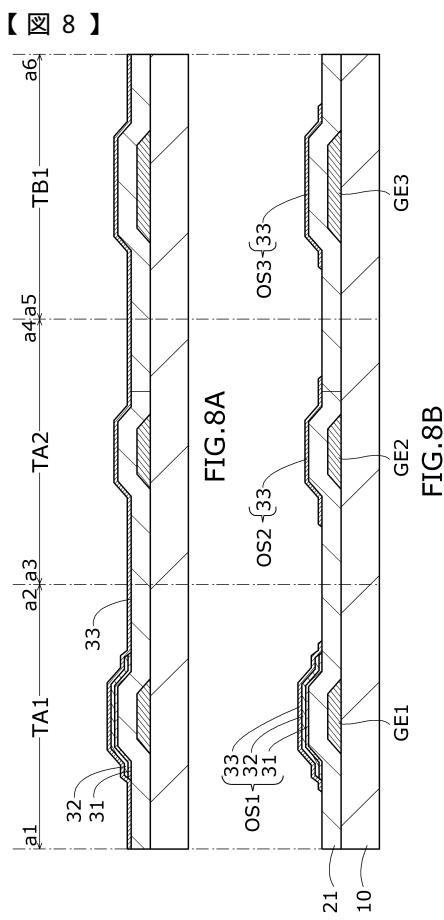

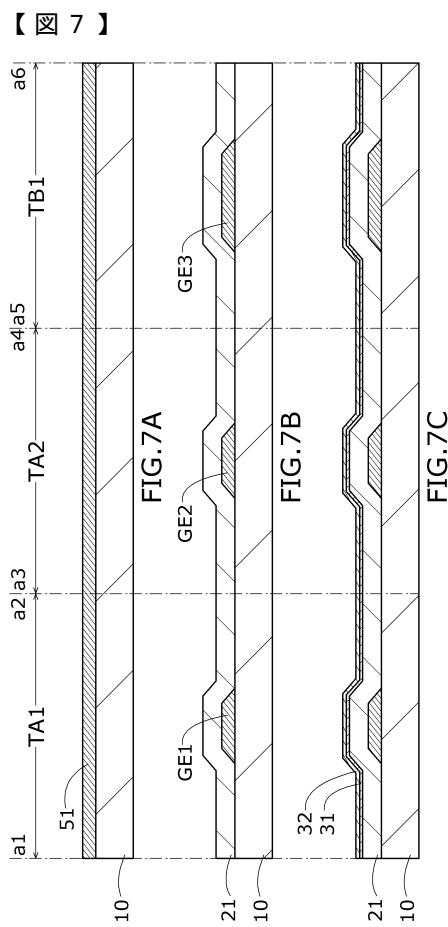

<トランジスタ T C 1、T B 2、T D 1>

図 5 A、図 5 B、図 5 C に、それぞれ、トランジスタ T C 1、トランジスタ T B 2、およびトランジスタ T D 1 の上面図（レイアウト図）と、その回路記号を示す。図 6 A、図 6 B に、トランジスタ T C 1 の a 1 1 - a 1 2 線および b 1 1 - b 1 2 線による断面図、トランジスタ T B 2 の a 1 3 - a 1 4 線および b 1 3 - b 1 4 線による断面図、並びにトランジスタ T D 1 の a 1 5 - a 1 6 線および b 1 5 - b 1 6 線による断面図を示す。

10

#### 【 0 0 7 8 】

トランジスタ T C 1 は、ゲート電極 G E 6、酸化物半導体層 O S 6、ソース電極 S E 6、ドレイン電極 D E 6、およびバックゲート電極 B G E 6 を有する。電極 B G E 6 は開口 C G 6 において電極 G E 6 に接している。トランジスタ T C 1 は、トランジスタ T A 1 の変形例であり、層 O S 6 を 2 層構造としている。層 O S 6 は、酸化物半導体膜 3 2 と酸化物半導体膜 3 3 とでなる。トランジスタ T C 1 もトランジスタ T A 1 と同様に、チャネル形成領域が酸化物半導体膜 3 2 で構成されるトランジスタである。そのため、トランジスタ T C 1 も、トランジスタ T A 1 と同程度に高い電界効果移動のトランジスタであり、代表的には、電界効果移動度が  $10 \text{ cm}^2 / \text{V s}$  より大きく  $60 \text{ cm}^2 / \text{V s}$  未満、好ましくは  $15 \text{ cm}^2 / \text{V s}$  以上  $50 \text{ cm}^2 / \text{V s}$  未満のトランジスタである。よって、トランジスタ T C 1 もトランジスタ T A 1 と同様に、駆動回路のような高速動作させるトランジスタに好適である。

20

#### 【 0 0 7 9 】

トランジスタ T B 2 は、ゲート電極 G E 7、酸化物半導体層 O S 7、ソース電極 S E 7、ドレイン電極 D E 7、およびバックゲート電極 B G E 7 を有する。電極 B G E 7 は開口 C G 7 において電極 G E 7 に接している。トランジスタ T B 2 は、トランジスタ T B 1 の変形例であり、電極 B G E 7 を有する点でトランジスタ T B 1 と異なる。トランジスタ T B 2 は、電極 G E 7 と接続された電極 B G E 7 を有しているため、トランジスタ T B 1 よりもオン電流が高く、電界効果移動度が高く、また機械的な強度が向上されている。

30

#### 【 0 0 8 0 】

トランジスタ T D 1 は、ゲート電極 G E 8、酸化物半導体層 O S 8、ソース電極 S E 8、およびドレイン電極 D E 8 を有する。トランジスタ T D 1 は、トランジスタ T B 1 の変形例であり、層 O S 8 全体が電極 G E 8 に重なっており、電極 G E 8 の端部の外側にある部分を有していない。このように、トランジスタ T D 1 は、層 O S 8 がトランジスタ T B 1 よりも光に曝されにくい構造となっているため、画素部のトランジスタに好適である。

#### 【 0 0 8 1 】

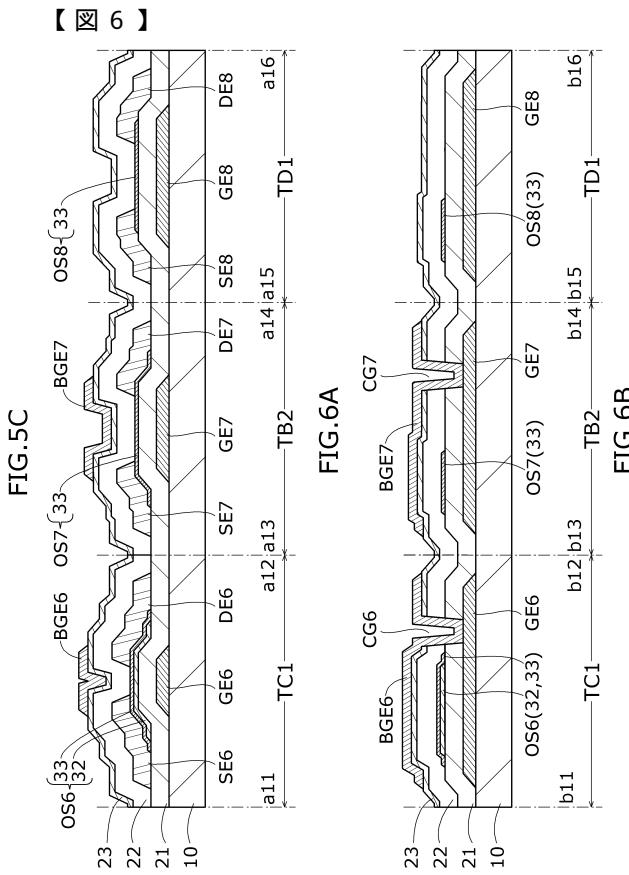

<<トランジスタの作製方法例>>

以下、半導体装置の作製方法の一例を説明する。ここでは、トランジスタ T A 1、トランジスタ T A 2 およびトランジスタ T B 1 を同一の工程で作製する方法の一例を説明する。なお他のトランジスタ T A 3 等も同様に作製することができる。ここでは、図 2 A と同様のトランジスタのチャネル長方向の断面図（図 7 - 図 9）を参照して、トランジスタの作製方法について説明する。

40

#### 【 0 0 8 2 】

トランジスタ T A 1、トランジスタ T A 2 およびトランジスタ T B 1 を構成する膜（絶縁膜、酸化物半導体膜、金属酸化物膜、導電膜等）は、スパッタリング法、化学気相堆積（C V D）法、真空蒸着法、パルスレーザー堆積（P L D）法を用いて形成することができる。あるいは、塗布法や印刷法で形成することができる。成膜方法としては、スパッタリング法、プラズマ化学気相堆積（P E C V D）法が代表的であるが、熱 C V D 法でもよい

50

。熱CVD法の例として、MOCVD（有機金属化学堆積）法やALD（原子層成膜）法を使ってもよい。

#### 【0083】

熱CVD法は、原料ガスと酸化剤を同時にチャンバー内に送り、チャンバー内を大気圧または減圧下とし、基板近傍または基板上で反応させて基板上に堆積させることで成膜を行ってもよい。熱CVD法は、プラズマを発生させない成膜方法であるため、プラズマダメージにより欠陥が生成されることが無いという利点を有する。

#### 【0084】

また、ALD法は、チャンバー内を大気圧または減圧下とし、反応のための原料ガスが順次にチャンバーに導入され、そのガス導入の順序を繰り返すことで成膜を行ってもよい。

10 例えば、それぞれのスイッチングバルブ（高速バルブともよぶ）を切り替えて2種類以上の原料ガスを順番にチャンバーに供給し、複数種の原料ガスが混ざらないように第1の原料ガスと同時またはその後に不活性ガス（アルゴン、或いは窒素など）などを導入し、第2の原料ガスを導入する。なお、同時に不活性ガスを導入する場合には、不活性ガスはキヤリアガスとなり、また、第2の原料ガスの導入時にも同時に不活性ガスを導入してもよい。また、不活性ガスを導入する代わりに真空排気によって第1の原料ガスを排出した後、第2の原料ガスを導入してもよい。第1の原料ガスが基板の表面に吸着して第1の層を成膜し、後から導入される第2の原料ガスと反応して、第2の層が第1の層上に積層されて薄膜が形成される。

#### 【0085】

ガス導入順序を制御しつつ、所望の厚さになるまで複数回繰り返すことで、段差被覆性に優れた薄膜を形成することができる。薄膜の厚さは、ガス導入順序を繰り返す回数によって調節することができるため、精密な膜厚調節が可能であり、微細なトランジスタを作製する場合に適している。

20

#### 【0086】

MOCVD法やALD法などの熱CVD法は、金属膜、半導体膜、無機絶縁膜など様々な膜を形成することができ、例えば、In-Ga-Zn-O膜を成膜する場合には、トリメチルインジウム、トリメチルガリウム、及びジメチル亜鉛を用いる。なお、トリメチルインジウムの化学式は、In(CH<sub>3</sub>)<sub>3</sub>である。また、トリメチルガリウムの化学式は、Ga(CH<sub>3</sub>)<sub>3</sub>である。また、ジメチル亜鉛の化学式は、Zn(CH<sub>3</sub>)<sub>2</sub>である。また、これらの組み合わせに限定されず、トリメチルガリウムに代えてトリエチルガリウム（化学式Ga(C<sub>2</sub>H<sub>5</sub>)<sub>3</sub>）を用いることもでき、ジメチル亜鉛に代えてジエチル亜鉛（化学式Zn(C<sub>2</sub>H<sub>5</sub>)<sub>2</sub>）を用いることもできる。

30

#### 【0087】

例えば、ALDを利用する成膜装置により酸化ハフニウム膜を形成する場合には、溶媒とハフニウム前駆体化合物を含む液体（ハフニウムアルコキシド溶液、代表的にはテトラキスジメチルアミドハフニウム（TDMAH））を気化させた原料ガスと、酸化剤としてオゾン(O<sub>3</sub>)の2種類のガスを用いる。なお、テトラキスジメチルアミドハフニウムの化学式はHf[N(CH<sub>3</sub>)<sub>2</sub>]<sub>4</sub>である。また、他の材料液としては、テトラキス(エチルメチルアミド)ハフニウムなどがある。

40

#### 【0088】

例えば、ALDを利用する成膜装置により酸化アルミニウム膜を形成する場合には、溶媒とアルミニウム前駆体化合物を含む液体（トリメチルアルミニウム（TMA）など）を気化させた原料ガスと、酸化剤としてH<sub>2</sub>Oの2種類のガスを用いる。なお、トリメチルアルミニウムの化学式はAl(CH<sub>3</sub>)<sub>3</sub>である。また、他の材料液としては、トリス(ジメチルアミド)アルミニウム、トリイソブチルアルミニウム、アルミニウムトリス(2,2,6,6-テトラメチル-3,5-ヘプタンジオナート)などがある。

#### 【0089】

例えば、ALDを利用する成膜装置により酸化シリコン膜を形成する場合には、ヘキサクロロジシランを被成膜面に吸着させ、吸着物に含まれる塩素を除去し、酸化性ガス(O<sub>2</sub>)

50

、一酸化二窒素)のラジカルを供給して吸着物と反応させる。

**【0090】**

まず、基板10上に、ゲート電極(GE1、GE2、GE3)を構成する導電膜51を形成する(図7A)。

**【0091】**

**[基板10]**

基板10としては、様々な基板を用いることができ、特定のものに限定されることはない。基板10の一例としては、半導体基板(例えば単結晶基板又はシリコン基板)、SOI基板、ガラス基板、石英基板、プラスチック基板、金属基板、ステンレス・スチール基板、ステンレス・スチール・ホイルを有する基板、タンクステン基板、タンクステン・ホイルを有する基板、可撓性基板、貼り合わせフィルム、纖維状の材料を含む紙、又は基材フィルムなどがある。ガラス基板の一例としては、バリウムホウケイ酸ガラス、アルミニノホウケイ酸ガラス、又はソーダライムガラスなどがある。可撓性基板、貼り合わせフィルム、基材フィルムなどの一例としては、以下のものがあげられる。例えば、ポリエチレンテレフタレート(PET)、ポリエチレンナフタレート(PEN)、ポリエーテルサルファン(PES)に代表されるプラスチックがある。または、一例としては、アクリル等の合成樹脂などがある。または、一例としては、ポリプロピレン、ポリエステル、ポリフッ化ビニル、又はポリ塩化ビニルなどがある。または、一例としては、ポリアミド、ポリイミド、アラミド、エポキシ、無機蒸着フィルム、又は紙類などがある。特に、半導体基板、単結晶基板、又はSOI基板などを用いてトランジスタを製造することによって、特性、サイズ、又は形状などのばらつきが少なく、電流能力が高く、サイズの小さいトランジスタを製造することができる。このようなトランジスタによって回路を構成すると、回路の低消費電力化、又は回路の高集積化を図ることができる。10

**【0092】**

導電膜51を形成する前に、基板10上に下地絶縁膜を形成してもよい。下地絶縁膜としては、酸化シリコン、酸化窒化シリコン、窒化シリコン、窒化酸化シリコン、酸化ガリウム、酸化ハフニウム、酸化イットリウム、酸化アルミニウム、酸化窒化アルミニウム等がある。なお、下地絶縁膜として、窒化シリコン、酸化ガリウム、酸化ハフニウム、酸化イットリウム、酸化アルミニウム等を用いることで、基板10から不純物(代表的にはアルカリ金属、水、水素等)が酸化物半導体層(OS1-OS3)へ拡散するのを抑制することができる。20

**【0093】**

また、基板10として、可撓性基板を用い、トランジスタ(TA1、TA2、TB1)を可撓性基板上に直接形成することができる。トランジスタ(TA1、TA2、TB1)を作製した後、作製に使用した基板を分離して、基板10として可撓性基板を取り付けることもできる。これについては、後述する。

**【0094】**

**[ゲート電極(GE1、GE2、GE3)]**

導電膜51は、単層の導電膜、または2つ以上の導電膜が積層された多層構造の膜である。導電膜51として形成される導電膜は、アルミニウム、クロム、銅、タンタル、チタン、モリブデン、タンクステンから選ばれた金属元素、または上述した金属元素を成分とする合金か、上述した金属元素を組み合わせた合金等で形成することができる。また、マンガン、ジルコニアのいずれか一または複数から選択された金属元素で形成することができる。また、アルミニウムに、チタン、タンタル、タンクステン、モリブデン、クロム、ネオジム、スカンジウムから選ばれた元素の一または複数を組み合わせた合金、もしくは窒化物で形成することができる。また、インジウム錫酸化物、酸化タンクステンを含むインジウム酸化物、酸化タンクステンを含むインジウム亜鉛酸化物、酸化チタンを含むインジウム酸化物、酸化チタンを含むインジウム錫酸化物、インジウム亜鉛酸化物、酸化シリコンを含むインジウム錫酸化物等の透光性を有する金属酸化物で形成することもできる。40

**【0095】**

例えば、導電膜 5 1 として、シリコンを含むアルミニウム膜を形成することができる。導電膜 5 1 を 2 層構造とする場合は、例えば、アルミニウム膜上にチタン膜を形成する、窒化チタン膜上にチタン膜を形成する、窒化チタン膜上にタンゲステン膜を形成する、窒化タンタル膜または窒化タンゲステン膜上にタンゲステン膜を形成すればよい。また、導電膜 5 1 を 3 層構造とする場合は、例えば、チタン膜と、そのチタン膜上にアルミニウム膜を積層し、さらにその上にチタン膜を形成すればよい。

#### 【 0 0 9 6 】

スパッタリング法、真空蒸着法、パルスレーザー堆積 ( P L D ) 法、熱 C V D 法等により導電膜 5 1 を形成することができる。ここでは、導電膜 5 1 として、厚さ 1 0 0 n m のタンゲステン膜をスパッタリング法により形成する。

10

#### 【 0 0 9 7 】

なお、タンゲステン膜は A L D を利用する成膜装置により成膜することができる。この場合には、W F<sub>6</sub> ガスと B<sub>2</sub>H<sub>6</sub> ガスを順次繰り返し導入して初期タンゲステン膜を形成し、その後、W F<sub>6</sub> ガスと H<sub>2</sub> ガスを同時に導入してタンゲステン膜を形成する。なお、B<sub>2</sub>H<sub>6</sub> ガスに代えて S i H<sub>4</sub> ガスを用いてもよい。

#### 【 0 0 9 8 】

導電膜 5 1 上にフォトリソグラフィ工程によりマスク R M 1 ( 図示せず ) を形成する。次に、マスク R M 1 を用いて導電膜 5 1 をエッチングして、ゲート電極 G E 1 - G E 3 を形成する。この後、マスク R M 1 を除去する。

20

#### 【 0 0 9 9 】

ゲート電極 G E 1 - G E 3 の形成は、上記形成方法の他に、電解メッキ法、印刷法、インクジェット法等で行うことが可能である。

#### 【 0 1 0 0 】

##### [ 絶縁層 2 1 ( ゲート絶縁層 ) ]

ゲート電極 G E 1 - G E 3 を覆って、絶縁層 2 1 を形成する ( 図 7 B ) 。絶縁層 2 1 は、単層の絶縁膜あるいは 2 層以上の多層構造の絶縁膜である。絶縁層 2 1 として形成される絶縁膜は、酸化物絶縁膜、窒化物絶縁膜、酸化窒化絶縁膜、および窒化酸化絶縁膜等が挙げられる。なお、本明細書において、酸化窒化物とは、窒素より酸素の含有量が多い材料であり、窒化酸化物とは酸素より窒素の含有量が多い材料とする。

30

#### 【 0 1 0 1 】

絶縁層 2 1 として形成される絶縁膜としては、例えば、酸化シリコン、酸化窒化シリコン、窒化酸化シリコン、窒化シリコン、酸化アルミニウム、酸化ガリウムまたは G a - Z n 系金属酸化物などでなる絶縁膜を形成することができる。また、このような絶縁膜として、ハフニウムシリケート ( H f S i O<sub>x</sub> ) 、窒素が添加されたハフニウムシリケート ( H f S i<sub>x</sub> O<sub>y</sub> N<sub>z</sub> ) 、窒素が添加されたハフニウムアルミネート ( H f A l<sub>x</sub> O<sub>y</sub> N<sub>z</sub> ) 、酸化ハフニウム、酸化イットリウムなどの h i g h - k 材料でなる膜を形成することができる。 h i g h - k 材料を用いることでトランジスタのゲートリーアクションを低減できる。

#### 【 0 1 0 2 】

絶縁層 2 1 はゲート絶縁層を構成する膜であるため、酸化物半導体層 ( O S 1 、 O S 2 、 O S 3 ) とゲート絶縁層との界面特性を向上させるため、絶縁層 2 1 においてこれらの層 ( O S 1 、 O S 2 、 O S 3 ) と接する領域は酸化物絶縁膜あるいは酸化窒化絶縁膜で形成することが好ましい。例えば、絶縁層 2 1 の最上層の膜は、酸化シリコン膜あるいは酸化窒化シリコン膜とすればよい。

40

#### 【 0 1 0 3 】

絶縁層 2 1 の厚さは、例えば 5 n m 以上 4 0 0 n m 以下とすればよい。その厚さは、好ましくは 1 0 n m 以上 3 0 0 n m 以下であり、より好ましくは 5 0 n m 以上 2 5 0 n m 以下である。

#### 【 0 1 0 4 】

##### [ 酸化物半導体層 O S 1 、 O S 2 、 O S 3 ]

絶縁層 2 1 上に酸化物半導体膜 3 1 を形成し、酸化物半導体膜 3 1 上に酸化物半導体膜 3

50

2を形成する(図7C)。酸化物半導体膜32上にフォトリソグラフィ工程によりマスクRM2(図示せず)を形成する。マスクRM2を用いて酸化物半導体膜31および酸化物半導体膜32をエッティングして、層OS1の1層目(31)および2層目(32)を形成する。この後、マスクRM2を除去する。

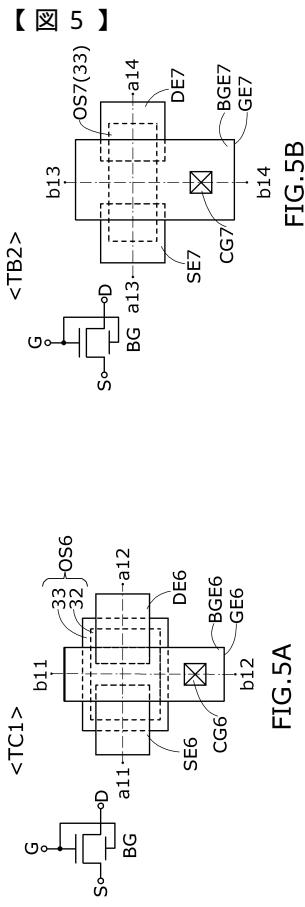

#### 【0105】

絶縁層21および、酸化物半導体膜31、32を覆って、酸化物半導体膜33を形成する(図8A)。酸化物半導体膜33上にフォトリソグラフィ工程によりマスクRM3(図示せず)を形成する。マスクRM3を用いて酸化物半導体膜33をエッティングして、層OS1、層OS2および層OS3を形成する。この後、マスクRM3を除去する(図8B)。

#### 【0106】

スパッタリング法で酸化物半導体膜を形成する場合、プラズマを発生させるための電源装置は、RF電源装置、AC電源装置、DC電源装置等を適宜用いることができる。スパッタリングガスは、希ガス(代表的にはアルゴン)雰囲気、酸素雰囲気、希ガス及び酸素の混合ガスを適宜用いる。なお、希ガス及び酸素の混合ガスの場合、希ガスに対して酸素のガス比を高めることが好ましい。また、ターゲットは、形成する酸化物半導体膜の組成にあわせて、適宜選択すればよい。

#### 【0107】

なお、酸化物半導体膜の形成にスパッタリング法を用いる場合、基板温度を150以上750以下、好ましくは150以上450以下、さらに好ましくは200以上350以下とすることで、酸化物半導体膜31-33として、CAAC-OS膜を形成することができる。また、CAAC-OS膜を成膜するために、以下の条件を適用することが好ましい。

#### 【0108】

成膜時の不純物混入を抑制することで、不純物によって結晶状態が崩れることを抑制できる。例えば、成膜室内に存在する不純物濃度(水素、水、二酸化炭素及び窒素など)を低減すればよい。また、成膜ガス中の不純物濃度を低減すればよい。具体的には、露点が-80以下、好ましくは-100以下である成膜ガスを用いる。また、成膜ガス中の酸素割合を高め、電力を最適化することで成膜時のプラズマダメージを軽減すると好ましい。成膜ガス中の酸素割合は、30体積%以上が好ましく、100体積%がより好ましい。

#### 【0109】

酸化物半導体膜を加熱しながら成膜することで、あるいは酸化物半導体膜を形成した後、加熱処理を行うことで、酸化物半導体膜の水素濃度を $2 \times 10^{20}$ atoms/cm<sup>3</sup>以下、好ましくは $5 \times 10^{19}$ atoms/cm<sup>3</sup>以下、より好ましくは $1 \times 10^{19}$ atoms/cm<sup>3</sup>以下、 $5 \times 10^{18}$ atoms/cm<sup>3</sup>未満、好ましくは $1 \times 10^{18}$ atoms/cm<sup>3</sup>以下、より好ましくは $5 \times 10^{17}$ atoms/cm<sup>3</sup>以下、さらに好ましくは $1 \times 10^{16}$ atoms/cm<sup>3</sup>以下とすることができます。

#### 【0110】

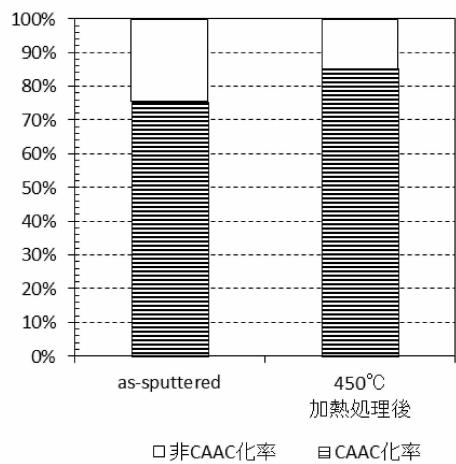

なお、加熱処理を、350より高く650以下、好ましくは450以上600以下で行うことで、後述するCAAC化率が、70%以上100%未満、好ましくは80%以上100%未満、好ましくは90%以上100%未満、より好ましくは95%以上98%以下である酸化物半導体膜を得ることができる。また、水素、水等の含有量が低減された酸化物半導体膜を得ることが可能である。すなわち、不純物濃度が低く、欠陥準位密度の低い酸化物半導体膜を形成することができる。

#### 【0111】

ALDを利用する成膜装置により酸化物半導体膜を形成することができる。例えばIn-Zn-O膜を成膜する場合には、In(CH<sub>3</sub>)<sub>3</sub>ガスとO<sub>2</sub>ガスを順次繰り返し導入してIn-O層を形成し、その後、Ga(CH<sub>3</sub>)<sub>3</sub>ガスとO<sub>2</sub>ガスを同時に導入してGa-O層を形成し、更にその後Zn(CH<sub>3</sub>)<sub>2</sub>とO<sub>2</sub>ガスを同時に導入してZn-O層を形成する。なお、これらの層の順番はこの例に限らない。また、これらのガスを混ぜてIn-Ga-O層やIn-Zn-O層、Ga-Zn-O層などの混合化合物層を形成

10

20

30

40

50

してもよい。なお、 $O_3$  ガスに変えて Ar 等の不活性ガスでバーピングして得られた  $H_2$  ガスを用いてもよいが、H を含まない  $O_3$  ガスを用いる方が好ましい。また、In ( $C H_3$ )<sub>3</sub> ガスにかえて、In ( $C_2H_5$ )<sub>3</sub> ガスを用いてもよい。また、Ga ( $C H_3$ )<sub>3</sub> ガスにかえて、Ga ( $C_2H_5$ )<sub>3</sub> ガスを用いてもよい。また、Zn ( $C H_3$ )<sub>2</sub> ガスを用いてもよい。

#### 【0112】

酸化物半導体膜 32、および酸化物半導体膜 33 は、トランジスタのチャネルが形成される膜であり、その膜厚を 3 nm 以上 200 nm 以下とすることができます。それらの厚さは、好ましくは 3 nm 以上 100 nm 以下であり、さらに好ましくは 30 nm 以上 50 nm 以下である。酸化物半導体膜 31 の膜厚は例えば、3 nm 以上 100 nm 以下とすることができます、好ましくは 3 nm 以上 30 nm 以下であり、より好ましくは 3 nm 以上 15 nm 以下である。酸化物半導体膜 31 は、酸化物半導体膜 32、酸化物半導体膜 33 よりも薄く形成することが好ましい。

#### 【0113】

ここでは、酸化物半導体膜 31、32、33 として、In - Ga - Zn 膜をスパッタリング法で成膜する。これらの成膜に用いられるターゲットの金属元素の原子数比 (In : Ga : Zn) は、例えば、酸化物半導体膜 31 は 1 : 3 : 6 であり、酸化物半導体膜 32 は 3 : 1 : 2 であり、酸化物半導体膜 33 は、1 : 1 : 1 . 2 または 1 : 1 : 1 とすることができます。例えば、酸化物半導体膜 31、32、33 の厚さを、それぞれ、5 nm、35 nm、35 nm とすることができます。

#### 【0114】

##### [ソース電極、ドレイン電極]

絶縁層 21、酸化物半導体層 (OS1、OS2、OS3) を覆って、導電膜 52 を形成する (図 9A)。導電膜 52 は導電膜 51 と同様に形成することができます。ここでは、3 層構造の導電膜 52 を形成する。厚さ 50 nm の銅 - マンガン合金膜、厚さ 400 nm の銅膜、及び厚さ 100 nm の銅 - マンガン合金膜の順に、これらの膜をスパッタリング法により積層する。

#### 【0115】

導電膜 52 上にフォトリソグラフィ工程によりマスク RM4 (図示せず) を形成し、マスク RM4 を用いて、導電膜 52 をエッチングし、電極 (SE1、DE1、SE2、DE2、SE3、DE3) を形成する。そしてマスク RM4 を除去する (図 9B)。図 9B の工程で、トランジスタ (TA1、TA2、TB1) のチャネル長およびチャネル幅が決定される。

#### 【0116】

アクティブマトリクス型表示装置の駆動回路などに用いられるトランジスタのように、高速で動作させるトランジスタには、トランジスタ (TA1、TA2)、あるいはトランジスタ (TA3、TA4、TC1) のように、チャネル長を短くすることが好ましい。このようなトランジスタのチャネル長は、2.5  $\mu m$  未満とすることが好ましい。例えば、2.2  $\mu m$  以下とすればよい。本実施の形態のトランジスタでは、チャネル長はソース電極とドレイン電極間の距離で決定されるため、チャネル長の最小値は、導電膜 52 を加工する精度で制約される。本実施の形態のトランジスタのチャネル長は、例えば、チャネル長は 0.5  $\mu m$  以上とすることができます、または、1.0  $\mu m$  以上とすることができます。

#### 【0117】

##### [絶縁層 22、23]

電極 (SE1、DE1、SE2、DE2、SE3、DE3)、酸化物半導体層 (OS1、OS2、OS3) および絶縁層 21 を覆って、絶縁層 22 を形成し、絶縁層 22 上に絶縁層 23 を形成する (図 9C)。絶縁層 22 および絶縁層 23 は絶縁層 21 と同様に形成することができます。

#### 【0118】

例えば、絶縁層 22 としては、2 層構造の絶縁膜を形成することができます。ここでは、絶

10

20

30

40

50

縁層 2 2 の 1 層目の膜を絶縁膜 2 2 a と呼び、2 層目の膜を絶縁膜 2 2 b と呼ぶこととする。

#### 【 0 1 1 9 】

絶縁膜 2 2 a としては、例えば酸化シリコンなどでなる酸化物絶縁膜、あるいは窒素を含み、且つ欠陥量の少ない酸化物絶縁膜を形成することができる。このような酸化物絶縁膜の代表例としては、酸化窒化シリコン膜、酸化窒化アルミニウム膜等がある。

#### 【 0 1 2 0 】

欠陥の少ない酸化物絶縁膜は、100K 以下の E S R (電子スピン共鳴) 測定で得られたスペクトルにおいて  $g$  値が 2.037 以上 2.039 以下の第 1 のシグナル、 $g$  値が 2.001 以上 2.003 以下の第 2 のシグナル、及び  $g$  値が 1.964 以上 1.966 以下の第 3 のシグナルが観測される。なお、第 1 のシグナル及び第 2 のシグナルのスプリット幅、並びに第 2 のシグナル及び第 3 のシグナルのスプリット幅は、X バンドの E S R 測定において約 5 mT である。また、 $g$  値が 2.037 以上 2.039 以下の第 1 のシグナル、 $g$  値が 2.001 以上 2.003 以下の第 2 のシグナル、および  $g$  値が 1.964 以上 1.966 以下の第 3 のシグナルのスピンの密度合計が、 $1 \times 10^{18}$  spins/cm<sup>3</sup> 未満であり、代表的には  $1 \times 10^{17}$  spins/cm<sup>3</sup> 以上  $1 \times 10^{18}$  spins/cm<sup>3</sup> 未満である。10

#### 【 0 1 2 1 】

なお、上掲の第 1 乃至第 3 のシグナルは、窒素酸化物 ( $\text{NO}_x$ 、 $x$  は 0 以上 2 以下、好ましくは 1 以上 2 以下) 起因のシグナルに相当する。窒素酸化物の代表例としては、一酸化窒素、二酸化窒素等がある。即ち、上掲の第 1 乃至第 3 のシグナルのスピンの密度の合計が少ないほど、酸化物絶縁膜に含まれる窒素酸化物の含有量が少ないと見える。20

#### 【 0 1 2 2 】

絶縁膜 2 2 a が、窒素酸化物の含有量が少ない膜であることで、絶縁膜 2 2 a と層 (O S 1、O S 2、O S 3) との界面におけるキャリアのトラップを低減することが可能である。この結果、トランジスタのしきい値電圧のシフトを低減することが可能であり、トランジスタの電気特性の変動を低減することができる。

#### 【 0 1 2 3 】

また、トランジスタの信頼性向上のため、絶縁膜 2 2 a は、S I M S で測定される窒素濃度が  $6 \times 10^{20} / \text{cm}^3$  以下であることが好ましい。それは、トランジスタの作製工程中に絶縁膜 2 2 a において、窒素酸化物が生成されにくくなるからである。30

#### 【 0 1 2 4 】

絶縁膜 2 2 a として、窒素を含み、且つ欠陥量の少ない酸化物絶縁膜の一例として、C V D 法により酸化窒化シリコン膜を形成することができる。この場合、原料ガスとしては、シリコンを含む堆積性気体及び酸化性気体を用いることが好ましい。シリコンを含む堆積性気体の代表例としては、シラン、ジシラン、トリシラン、フッ化シラン等がある。酸化性気体としては、一酸化二窒素、二酸化窒素等がある。

#### 【 0 1 2 5 】

また、堆積性気体に対する酸化性気体を 20 倍より大きく 100 倍未満、好ましくは 40 倍以上 80 倍以下とし、処理室内の圧力を 100 Pa 未満、好ましくは 50 Pa 以下とする C V D 法を用いることで、絶縁膜 2 2 a として、窒素を含み、且つ欠陥量の少ない酸化物絶縁膜を形成することができる。40

#### 【 0 1 2 6 】

絶縁膜 2 2 b として、例えば、化学量論的組成を満たす酸素よりも多くの酸素を含む酸化物絶縁膜を用いて形成することができる。化学量論的組成を満たす酸素よりも多くの酸素を含む酸化物絶縁膜は、加熱により酸素の一部が脱離する。化学量論的組成を満たす酸素よりも多くの酸素を含む酸化物絶縁膜は、昇温脱離ガス分析 (以下、T D S 分析と呼ぶ。) にて、酸素原子に換算しての酸素の脱離量が  $1.0 \times 10^{18}$  atoms/cm<sup>3</sup> 以上、好ましくは  $3.0 \times 10^{20}$  atoms/cm<sup>3</sup> 以上である酸化物絶縁膜である。なお、上記 T D S 分析時における膜の表面温度としては 100 以上 700 以下、または 150

00 以上 500 以下の範囲が好ましい。

【0127】

絶縁膜22bとしては、厚さが30nm以上500nm以下、好ましくは50nm以上400nm以下の、酸化シリコン、酸化窒化シリコン等を用いることができる。絶縁膜22bとして、化学量論的組成を満たす酸素よりも多くの酸素を含む酸化物絶縁膜を用いて形成する場合、化学量論的組成を満たす酸素よりも多くの酸素を含む酸化物絶縁膜として、CVD法を用いて酸化窒化シリコン膜を形成することができる。

【0128】

絶縁膜22bとして、酸化シリコン膜または酸化窒化シリコン膜を形成する場合、次のような条件で成膜を行うことができる。プラズマCVD装置の真空排気された処理室内に載置された基板を180以上280以下、さらに好ましくは200以上240以下に保持し、処理室に原料ガスを導入して処理室内における圧力を100Pa以上250Pa以下、さらに好ましくは100Pa以上200Pa以下とし、処理室内に設けられる電極に0.17W/cm<sup>2</sup>以上0.5W/cm<sup>2</sup>以下、さらに好ましくは0.25W/cm<sup>2</sup>以上0.35W/cm<sup>2</sup>以下の高周波電力を供給する。

10

【0129】

絶縁層23としては、少なくとも、水素及び酸素のブロッキング効果を有する膜を用いる。さらに、好ましくは、酸素、水素、水、アルカリ金属、アルカリ土類金属等のブロッキング効果を有する。代表的には、窒化シリコンなどの窒化物絶縁膜を形成すればよい。窒化シリコン膜の他、窒化酸化シリコン膜、窒化アルミニウム膜、窒化酸化アルミニウム膜等も用いることができる。

20

【0130】

また、絶縁層23を構成する膜として酸素、水素、水等に対してブロッキング効果を有する酸化物絶縁膜を設けてもよい。このような酸化物絶縁膜としては、酸化アルミニウム、酸化窒化アルミニウム、酸化ガリウム、酸化窒化ガリウム、酸化イットリウム、酸化窒化イットリウム、酸化ハフニウム、酸化窒化ハフニウム等がある。

【0131】

また、絶縁層23の厚さは50nm以上300nm以下とすればよく、好ましくは100nm以上200nm以下である。酸素、水素、水等に対してブロッキング効果を有する絶縁層23を形成することで、酸化物半導体膜31-33から外部への酸素の拡散を防ぎ、また外部から酸化物半導体膜31-33への水素、水等の侵入を防ぐことができる。

30

【0132】

絶縁層23としてプラズマCVD法により窒化シリコン膜を形成する場合、シリコンを含む堆積性気体、窒素、及びアンモニアを原料ガスとして用いることが好ましい。これらの原料ガスを用いることで、プラズマ中でアンモニアが解離し、活性種が発生する。当該活性種が、シリコンを含む堆積性気体に含まれるシリコン及び水素の結合、及び窒素の三重結合を切断する。この結果、シリコン及び窒素の結合が促進され、シリコン及び水素の結合が少なく、欠陥が少なく、緻密な窒化シリコン膜を形成することができる。一方、原料ガスにおいて、窒素に対するアンモニアの量が多いと、シリコンを含む堆積性気体及び窒素それぞれの分解が進まず、シリコン及び水素結合が残存してしまい、欠陥が増大した、且つ粗な窒化シリコン膜が形成されてしまう。これらのため、原料ガスにおいて、アンモニアに対する窒素の流量比を5以上50以下、好ましくは10以上50以下とすることが好ましい。

40

【0133】

絶縁層22を形成した後、加熱処理を行ってもよい。該加熱処理の温度は、代表的には、150以上基板歪み点未満、好ましくは200以上450以下、更に好ましくは300以上450以下とする。当該加熱処理により、絶縁層22の2層目を構成する酸化物絶縁膜に含まれる酸素を、酸化物半導体膜31-33に移動させて、これらに含まれる酸素欠損を低減することができる。加熱処理は、例えば、窒素及び酸素を含む混合ガス雰囲気で、加熱温度350、加熱時間1時間とすればよい。

50

**【 0 1 3 4 】**

また、絶縁層 2 3 を形成した後、酸化物半導体膜 3 1 - 3 3 から水素等を放出させることを目的として加熱処理を行ってもよい。この加熱処理は、例えば、窒素及び酸素を含む混合ガス雰囲気で、加熱温度 3 5 0 ℃、加熱時間 1 時間とすればよい。

**【 0 1 3 5 】****[ バックゲート電極 ]**

フォトリソグラフィ工程により絶縁層 2 3 上にマスク R M 5 ( 図示せず ) を形成し、マスク R M 5 を用いて絶縁層 2 1 - 2 3 をエッチングして、これらを貫通する開口 C G 1 、および開口 C G 2 を形成する ( 図 2 B ) 。マスク R M 5 を除去し、絶縁層 2 3 上に導電膜 5 3 を形成する ( 図 9 C ) 。導電膜 5 3 は導電膜 5 1 と同様に形成することができる。

10

**【 0 1 3 6 】**

フォトリソグラフィ工程により導電膜 5 3 上にマスク R M 6 ( 図示せず ) を形成し、マスク R M 6 を用いて導電膜 5 3 をエッチングして、バックゲート電極 ( B G E 1 、 B G E 2 ) を形成する。そしてマスク R M 6 を除去する ( 図 2 A 、 図 2 B ) 。

**【 0 1 3 7 】**

以上述べたように 6 つのマスク R M 1 - R M 6 を用いて、構造の異なるトランジスタ ( T A 1 、 T A 2 、 T B 1 ) を同一基板上に作製することができる。なお、酸化物半導体層が 2 層構造のトランジスタ ( 例えば、 T C 1 ) と、酸化物半導体層が単層構造のトランジスタ ( 例えば、 T B 1 ) を同一基板上に同時に作製する場合は、図 7 C の工程で、酸化物半導体膜 3 2 のみを形成すればよい。

20

**【 0 1 3 8 】**

以下、トランジスタのいくつかの他の構成例を示す。ここでは、トランジスタ ( T A 1 、 T A 2 、 T B 1 ) と、ゲート電極、酸化物半導体層、ソース電極、ドレイン電極、およびバックゲート電極の積層順序が異なるトランジスタについて説明する。

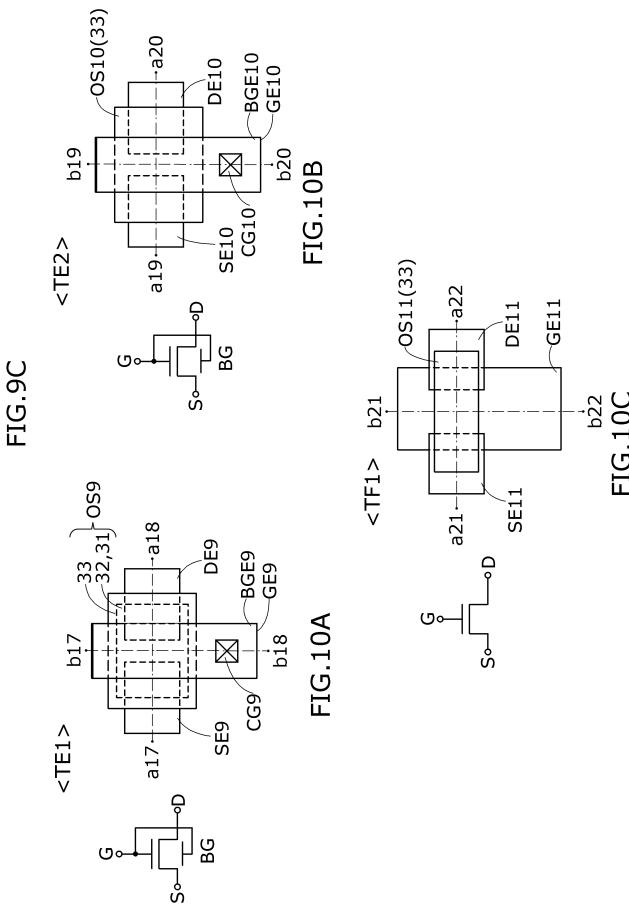

**【 0 1 3 9 】****<トランジスタ T E 1 、 T E 2 、 T F 1 >**

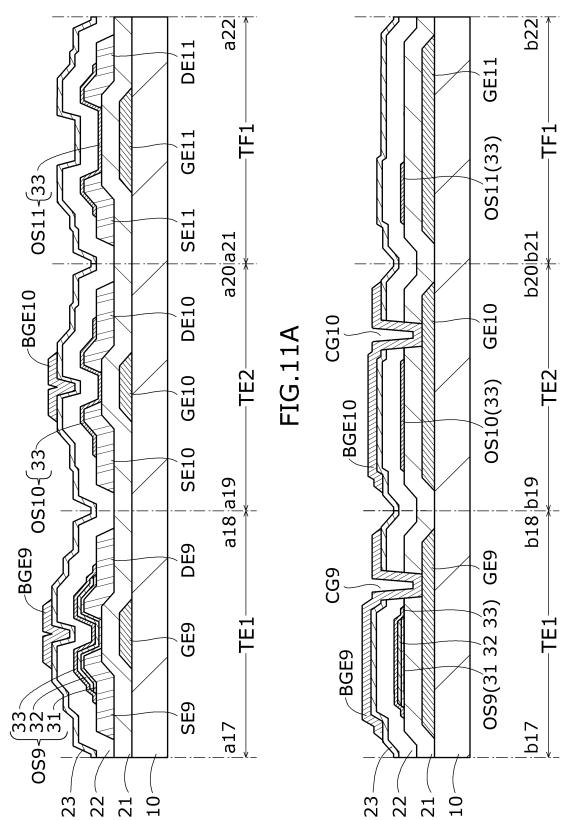

図 1 0 A 、 図 1 0 B 、 図 1 0 C に、それぞれ、トランジスタ T E 1 、トランジスタ T E 2 、トランジスタ T F 1 の上面図 ( レイアウト図 ) と、その回路記号を示す。図 1 1 A 、 図 1 1 B に、トランジスタ T E 1 の a 1 7 - a 1 8 線および b 1 7 - b 1 8 線による断面図、トランジスタ T E 2 の a 1 9 - a 2 0 線および b 1 9 - b 2 0 線による断面図、並びにトランジスタ T F 1 の a 2 1 - a 2 2 線および b 2 1 - b 2 2 線による断面図を示す。

30

**【 0 1 4 0 】**

トランジスタ T E 1 は、トランジスタ T A 1 ( 図 1 A 、 図 2 ) の変形例である。トランジスタ T E 1 は、ゲート電極 G E 9 、酸化物半導体層 O S 9 、ソース電極 S E 9 、ドレイン電極 D E 9 、およびバックゲート電極 B G E 9 を有する。電極 B G E 9 は、開口 C G 9 において電極 G E 9 に接している。トランジスタ T E 1 では、ソース電極 S E 9 およびドレイン電極 D E 9 上に層 O S 9 が形成されている。

**【 0 1 4 1 】**

トランジスタ T E 2 は、トランジスタ T A 2 ( 図 1 B 、 図 2 ) の変形例である。トランジスタ T E 2 は、ゲート電極 G E 1 0 、酸化物半導体層 O S 1 0 、ソース電極 S E 1 0 、ドレイン電極 D E 1 0 、およびバックゲート電極 B G E 1 0 を有する。電極 B G E 1 0 は、開口 C G 1 0 において電極 G E 1 0 に接している。トランジスタ T E 2 では、ソース電極 S E 1 0 およびドレイン電極 D E 1 0 上に層 O S 1 0 が形成されている。

40

**【 0 1 4 2 】**

トランジスタ T F 1 は、トランジスタ T B 1 ( 図 1 C 、 図 2 ) の変形例である。トランジスタ T F 1 は、ゲート電極 G E 1 1 、酸化物半導体層 O S 1 1 、ソース電極 S E 1 1 、およびドレイン電極 D E 1 1 を有する。トランジスタ T F 1 では、ソース電極 S E 1 1 およびドレイン電極 D E 1 1 上に層 O S 1 1 が形成されている。

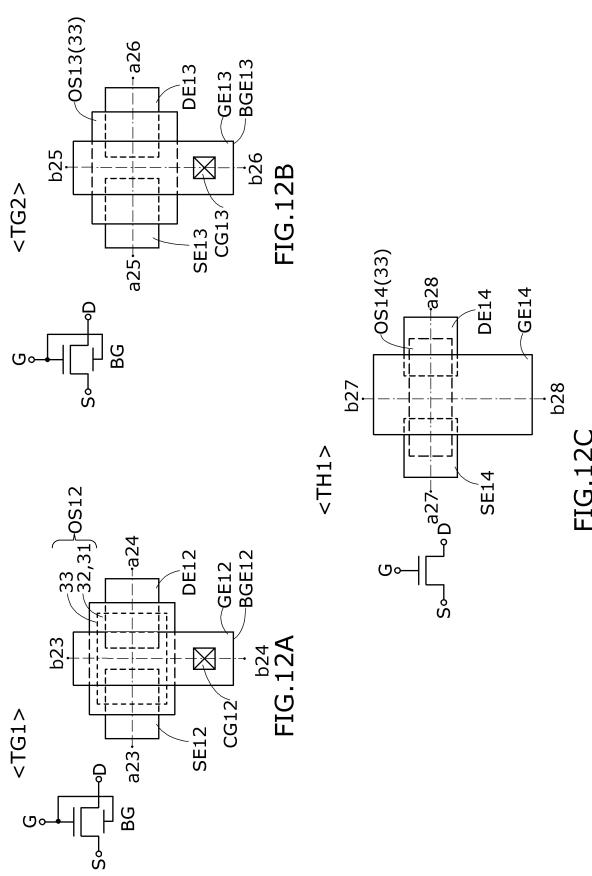

**【 0 1 4 3 】****<トランジスタ T G 1 、 T G 2 、 T H 1 >**

50

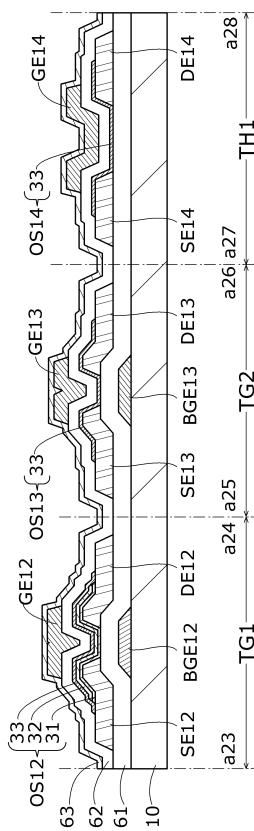

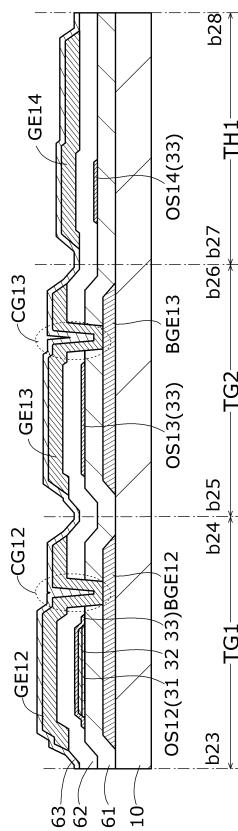

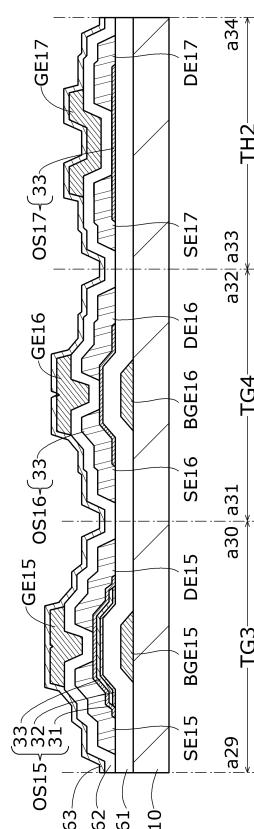

図12A、図12B、図12Cに、それぞれ、トランジスタTG1、トランジスタTG2、トランジスタTH1の上面図（レイアウト図）と、その回路記号を示す。図13A、図13Bに、トランジスタTG1のa23-a24線およびb23-b24線による断面図、トランジスタTG2のa25-a26線およびb25-b26線による断面図、並びにトランジスタTH1のa27-a28線およびb27-b28線による断面図を示す。

#### 【0144】

トランジスタTG1は、トランジスタTA1（図1A、図2）の変形例である。トランジスタTG1は、ゲート電極GE12、酸化物半導体層OS12、ソース電極SE12、ドレイン電極DE12、およびバックゲート電極BGE12を有する。

#### 【0145】

トランジスタTG1では、バックゲート電極BGE12が最も下層に配置されている。電極BGE12上には、絶縁層61を介してソース電極SE12、ドレイン電極DE12が形成されている。ソース電極SE12およびドレイン電極DE12上に層OS12が形成されている。層OS12上に絶縁層62を介してゲート電極GE12が形成されている。電極GE12は、絶縁層61および絶縁層62を貫通する開口CG12において電極BGE12に接している。トランジスタTG1を覆って、絶縁層63が形成されている。絶縁層61-63は、絶縁層21と同様に作製することができる。

#### 【0146】

トランジスタTG2は、トランジスタTA2（図1B、図2）の変形例であり、またトランジスタTG1の変形例である。トランジスタTG2は、ゲート電極GE13、酸化物半導体層OS13、ソース電極SE13、ドレイン電極DE13、およびバックゲート電極BGE13を有する。電極GE13は、絶縁層61および絶縁層62を貫通する開口CG13において電極BGE13に接している。トランジスタTG2は、層OS13が単層（33）である点でトランジスタTG1と異なる。

#### 【0147】

トランジスタTH1は、トランジスタTB1（図1C、図2）の変形例である。トランジスタTH1は、ゲート電極GE14、酸化物半導体層OS14、ソース電極SE14、およびドレイン電極DE14を有する。

#### 【0148】

<トランジスタTG3、TG4、TH2>

図14A、図14B、図14Cに、それぞれ、トランジスタTG3、トランジスタTG4、トランジスタTH2の上面図（レイアウト図）と、その回路記号を示す。図15A、図15Bに、トランジスタTG3のa29-a30線およびb29-b30による断面図、トランジスタTG4のa31-a32線およびb31-b32線による断面図、並びにトランジスタTH2のa33-a34線およびb33-b34線による断面図を示す。

#### 【0149】

トランジスタTG3は、トランジスタTG1（図12A、図13）の変形例である。トランジスタTG3は、ゲート電極GE15、酸化物半導体層OS15、ソース電極SE15、ドレイン電極DE15、およびバックゲート電極BGE15を有する。電極GE15は開口CG15において電極BGE15に接している。トランジスタTG3は、ソース電極SE15およびドレイン電極DE15が層OS15上に形成されている点でTG1と異なる。

#### 【0150】

トランジスタTG4は、トランジスタTG2（図12B、図13）の変形例である。トランジスタTG4は、ゲート電極GE16、酸化物半導体層OS16、ソース電極SE16、ドレイン電極DE16、およびバックゲート電極BGE16を有する。電極GE16は開口CG16において電極BGE16に接している。トランジスタTG4は、ソース電極SE16およびドレイン電極DE16が層OS16上に形成されている点でTG2と異なる。

#### 【0151】

10

20

30

40

50

トランジスタ TH 2 は、トランジスタ TH 1 ( 図 12 C 、図 13 ) の変形例である。トランジスタ TH 2 は、ゲート電極 GE 17 、酸化物半導体層 OS 17 、ソース電極 SE 17 、およびドレイン電極 DE 17 を有する。トランジスタ TH 2 は、ソース電極 SE 17 およびドレイン電極 DE 17 が層 OS 17 上に形成されている点で TH 1 と異なる。

#### 【 0152 】

以上、図 1 - 図 15 を参照して、トランジスタの構成例およびその作製方法について説明したが、本実施の形態に係るトランジスタは、図示されたトランジスタに限定されるものないのは言うもでもなく、これらの構成例からその形態及び詳細を様々に変更することが可能である。

#### 【 0153 】

##### ( 実施の形態 2 )

実施の形態 1 に係るトランジスタを用いて、機能の異なる複数の回路を備えた半導体装置を構成することができる。本実施の形態では、このような半導体装置の一例としてアクティブマトリクス型表示装置について説明する。

#### 【 0154 】

##### < 表示装置の構成例 >

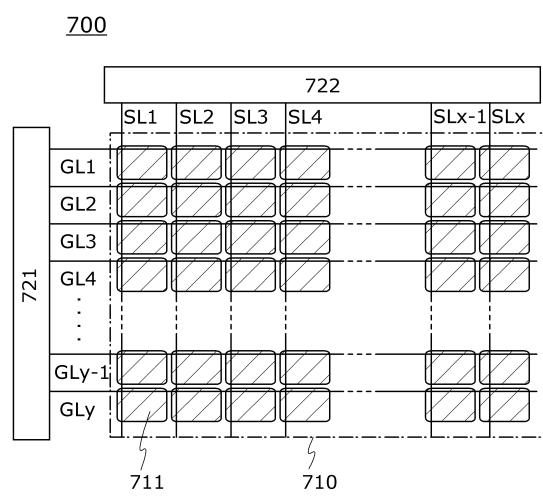

図 16 は、アクティブマトリクス型表示装置の構成の一例を示すブロック図である。図 16 に示すように、アクティブマトリクス型表示装置 700 ( 以下、表示装置 700 と呼ぶ。 ) は、画素部 710 と、駆動回路 721 および駆動回路 722 を有する。なお、以下の説明において、駆動回路 721 と駆動回路 722 を総称して駆動回路部 720 と呼ぶ場合がある。

#### 【 0155 】

画素部 710 には、  $y$  本 (  $y$  は自然数 ) の配線 GL 、  $x$  本 (  $x$  は自然数 ) の配線 SL 、および複数の画素 711 が設けられている。配線 GL は、行ごとに設けられている。 " GL 1 " とは、 1 行目の配線 GL であることを示している。配線 SL は、列ごとに設けられている。 " SL 1 " とは、 1 列目の配線 SL であることを示している。画素 711 は、配線 GL および配線 SL の配列に対応してアレイ状に配置され、対応する行の配線 GL と列の配線 SL に接続されている。例えば、 2 行目 3 列目の画素 711 は、配線 GL 2 と配線 SL 3 に接続されている。

#### 【 0156 】

画素部 710 に設けられる配線の種類及びその数は、画素 711 の構成、数及び配置によって決めることができる。図 16 に示す画素部 710 の場合、  $x$  列  $\times$   $y$  行の画素 711 がマトリクス状に配置されており、配線 SL 1 乃至配線 SL x 、配線 GL 1 乃至配線 GL y が、画素部 710 内に配置されている場合を例示している。

#### 【 0157 】

配線 SL は、駆動回路 722 に接続されている。配線 GL は、駆動回路 721 に接続されている。駆動回路 721 は、ビデオ信号を入力する画素 711 を選択する信号を生成する機能、および、所定のタイミングで同信号を配線 GL へ出力する機能等を有する。駆動回路 722 は、ビデオ信号を生成する機能、および所定のタイミングでビデオ信号を配線 SL に出力する機能などを有する。

#### 【 0158 】

駆動回路 721 の一部の回路、または全てを画素部 710 と同一基板に設けることができる。駆動回路 722 の一部の回路、または全てを画素部 710 と同一基板に設けることができる。駆動回路部 720 において、画素部 710 と同じ基板に集積された回路と、画素部 710 と異なる基板に作製された回路があると、これらを電気的に接続するために、配線および接続端子を画素部 710 と共に設ける必要がある。そのため、表示装置の一部を占有し、電子機器の大きさや表示装置の配置など、設計の自由度を制限してしまう場合がある。また、表示装置 700 の低消費電力化や、製造コストの削減のためにも外部接続端子数を減らすことが望ましい。そのため、駆動回路部 720 を構成する回路は、画素部 710 と同じ工程で同一基板上に作製されることが好ましい。

10

20

30

40

50

**【0159】**

他方、表示装置700の高精細化が求められている。そのため、画素部710の画素数が増えるので、配線G<sub>L</sub>、および配線S<sub>L</sub>の本数も多くなる。画素数が増えることで、駆動回路部720を高速に動作させることが求められる。本実施の形態では、例えば、駆動回路722全体を、画素部710と異なる基板に形成された回路（例えば、ICチップ）としており、この駆動回路722を含むICチップと、配線S<sub>L</sub>とを接続することになる。

**【0160】**

そこで、本実施の形態では、駆動回路部720に用いられる回路であって、画素部と共に作製することが可能な回路の構成例、およびその駆動方法例などについて説明する。

**【0161】**

10

<順序回路の構成例>

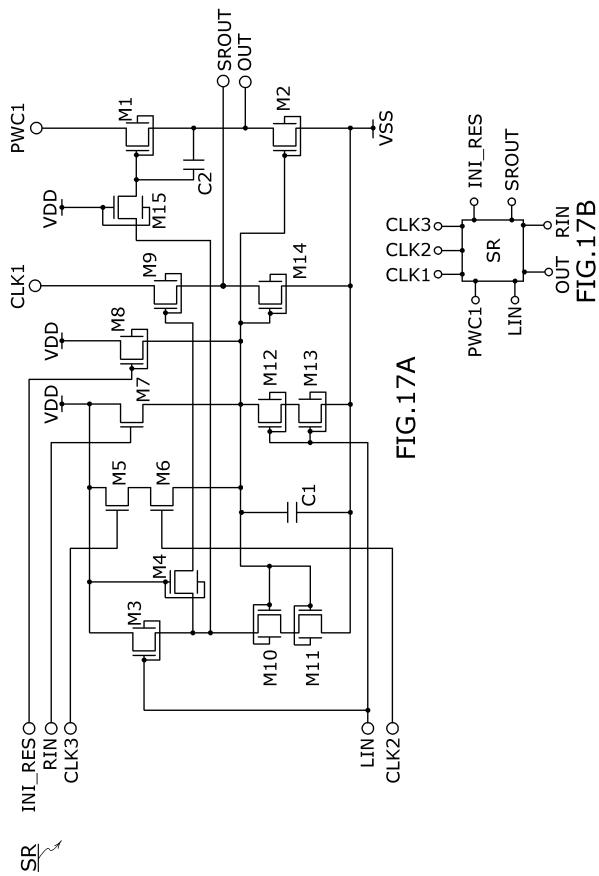

図17Aは、順序回路の構成の一例を示す回路図であり、図17Bは同ブロック図である。

**【0162】**

順序回路SRは、トランジスタM1 - トランジスタM15、容量素子C1、及び容量素子C2を有する。回路SRにおいて、信号(CLK1、CLK2、CLK3、PWC1、LIN、INRES、RIN)が入力信号であり、信号(SROUT、OUT)が出力信号である。また、VDDはハイレベルの電源電位であり、VSSはローレベルの電源電位である。

**【0163】**

20

図17Aにおいて、トランジスタM1 - M15は、それぞれ、1つのトランジスタとして記載されているが、実際の回路においては、並列に接続された複数のトランジスタや、直列に接続された複数のトランジスタで構成されている場合もある。また、容量素子は、トランジスタのソースとドレインを接続したMOS型容量を用いることができる。これは、他の回路図においても同様である。

**【0164】**

図17Aの例では、トランジスタM5 - M7は、バックゲートを有していないトランジスタである。これら以外のトランジスタ(M1 - M4、M8 - M15)は、ゲートに接続されたバックゲートを有するトランジスタである。例えば、トランジスタ(M1 - M4、M8 - M15)に、トランジスタTA1またはトランジスタTA2(図1、図2)を適用し、トランジスタM5 - M7には、バックゲートを設けていないトランジスタTA1またはトランジスタTA2を適用することができる。

30

**【0165】**

全てのトランジスタM1 - M15を、ゲート電極に接続されたバックゲートを有するトランジスタとすることもできる。回路SRにおいて、少なくとも信号OUTの出力端子に接続されているトランジスタ(M1、M2)は、ゲートにバックゲートが接続されたトランジスタであることが好ましい。また、トランジスタ(M1、M2)がトランジスタTA1のように、酸化物半導体膜32を含む多層構造の酸化物半導体層を有するトランジスタであることが、さらに好ましい。これにより、トランジスタ(M1、M2)が、チャネル長が2.5μm未満(さらには、2.2μm未満)の微細なトランジスタであっても、必要な電位レベルの信号OUTをより確実に出力することが可能になる。

40

**【0166】**

なお、本実施の形態では、回路の構成や動作の理解を容易にするため、トランジスタのソースとドレインとして機能する2つの端子(電極)を区別する場合がある。トランジスタのソースとドレインは、トランジスタに供給される電圧によりその機能が入れ替わる場合がある。トランジスタのソースとドレインの区別は、本実施の形態での記載に限定されるものではない。ここでは、OSトランジスタで回路を構成するため、ハイレベルの信号および電源電位が主として入力される端子(電極)をドレインと呼び、ローレベルの信号および電源電位が主として入力される端子(電極)をソースと呼ぶことにする。

**【0167】**

50

トランジスタM1のドレインは、信号PWC1が与えられる配線に接続され、そのソースは信号OUTの出力端子に接続され、そのゲートはトランジスタM15のドレインに接続されている。トランジスタM2のドレインは信号OUTの出力端子に接続され、そのソースはVSSが供給される配線に接続されている。トランジスタM10とトランジスタM11は直列に接続されており、それらのゲートは、トランジスタM2のゲートに接続されている。トランジスタM10のドレインはトランジスタM3のソースに接続され、トランジスタM11のソースはVSSが与えられる配線に接続されている。

#### 【0168】

VDDが与えられる配線に、トランジスタ(M3、M5、M7、M8)のドレイン、トランジスタ(M4、M15)のゲートが接続されている。VSSが与えられる配線に、トランジスタ(M2、M11、M13、M14)のソースが接続されている。CLK1が与えられる配線にトランジスタM9のドレインが接続され、CLK2が与えられる配線にトランジスタM6のゲートが接続され、CLK3が与えられる配線にトランジスタM5のゲートが接続されている。トランジスタM5とトランジスタM6は直列に接続されている。

10

#### 【0169】

信号LINが与えられる配線に、トランジスタ(M3、M12、M13)のゲートが接続されている。トランジスタM12とトランジスタM13は直列に接続されており、トランジスタM12のドレインはトランジスタM2のゲートに接続されている。トランジスタM2のゲートには、トランジスタ(M10、M11、M14)のゲート、トランジスタ(M6、M7、M8)のソースも接続されている。

20

#### 【0170】

信号INIRES与えられる配線に、トランジスタM8のゲートが接続され、信号RINが与えられる配線に、トランジスタM7のゲートが接続されている。トランジスタM4のソースはトランジスタM3のソースに接続され、そのドレインはトランジスタM9のゲートに接続されている。トランジスタM15のソースはトランジスタM3のソースに接続され、そのドレインはトランジスタM1のゲートに接続されている。信号SROUTの出力端子には、トランジスタM9のソースおよびトランジスタM14のドレインが接続されている。信号OUTの出力端子には、トランジスタM1のソースおよびトランジスタM2のドレインが接続されている。

30

#### 【0171】

容量素子C1の一方の端子はVSSが与えられる配線に接続され、他方がトランジスタM2のゲートに接続されている。容量素子C2の一方の端子はトランジスタM1のゲートに接続され、他方が信号OUTの出力端子に接続されている。容量素子C1、C2は適宜設ければよい。

#### 【0172】

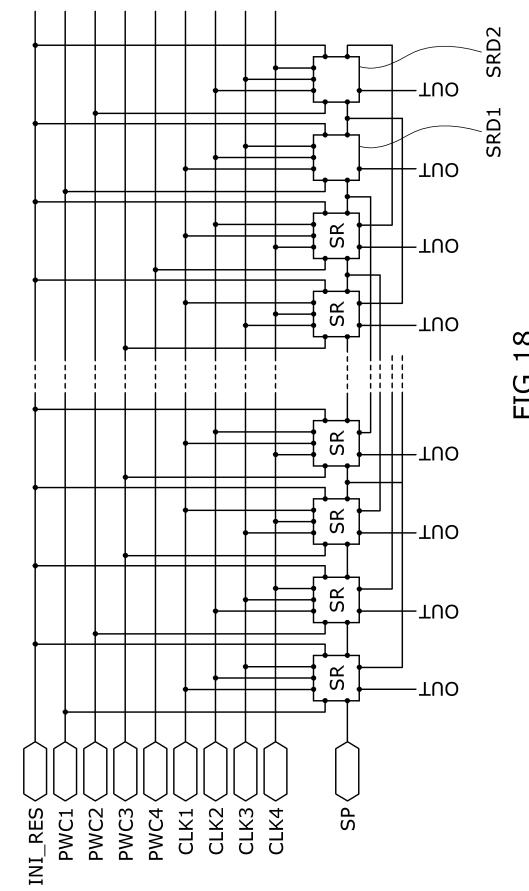

図17Aの順序回路SRを単位回路として、これらを複数段接続することで、パルス信号を出力する機能を備えたシフトレジスタを構成することができる。このようなシフトレジスタの一例を図18に示す。

#### 【0173】

図18の例では、シフトレジスタ750は、y個の順序回路SR(yは2以上の自然数)を有する。y個の順序回路SRは、それぞれ、図17Aに示した順序回路SRと同じ構成を有する。

40

#### 【0174】

図17B、図18に示すように、各段の回路SRには、前段の回路SRの出力信号SROUTが信号LINとして入力される。初段の回路SRには、例えば、信号LINとして、駆動回路部720のスタートパルス信号SPを入力すればよい。また、各段の回路SRには、信号RINとして、2段後ろの回路SRの出力信号SROUTが入力される。そのため、シフトレジスタ750は、最終段の順序回路SRの後段に、2つのダミー順序回路SRD1とSRD2をさらに有する。

#### 【0175】

50

回路 S R D 1 は、  $y - 1$  段目の回路 S R に、 信号 R I N を出力するために設けられており、 回路 S R D 2 は、  $y$  段目の回路 S R に、 信号 R I N を出力するために設けられている。そのため、 回路 ( S R D 1 、 S R D 2 ) には、 回路 S R とは一部構成が異なる。 回路 S R D 1 と回路 S R D 2 には、 トランジスタ M 7 が設けられていない。 すなわち、 回路 ( S R D 1 、 S R D 2 ) は、 トランジスタ M 2 のゲートに V D D の供給を信号 R I N に従って制御する機能が設けられていない点において、 図 17 A に示す順序回路 S R と構成が異なる。

#### 【 0176 】

図 18 に示すように、 シフトレジスタ 750 には、 4 つのクロック信号 C L K 1 - C L K 4 が入力される。 各段の回路 S R には、 図示されているように、 3 つのクロック信号が入力される。 具体的には、  $4m + 1$  段目の回路 S R には、 信号 C L K 1 、 C L K 2 、 及び C L K 3 が入力される。  $4m + 2$  段目の回路 S R には信号 C L K 2 、 C L K 3 、 及び C L K 4 が入力される。  $4m + 3$  段目の回路 S R には、 C L K 3 、 C L K 4 、 及び C L K 1 が入力される。  $4m + 4$  段目の回路 S R には、 C L K 4 、 C L K 1 、 及び C L K 2 が入力される。 ここで、  $m$  は、 回路 S R の総数が  $y$  であることを満たす、 0 以上の整数である。

#### 【 0177 】

シフトレジスタ 750 は、 単極性のトランジスタで構成されているため、 画素部 710 と同一基板に作製することの制約が少ない。 シフトレジスタ 750 を画素部 710 と同じ基板上に同じ作製工程で作製することが可能である。 また、 シフトレジスタ 750 を駆動回路 721 として、 あるいはその回路の一部として用いることができる。 また、 駆動回路 722 を構成する回路の一部として、 シフトレジスタ 750 を用いることも可能である。

#### 【 0178 】

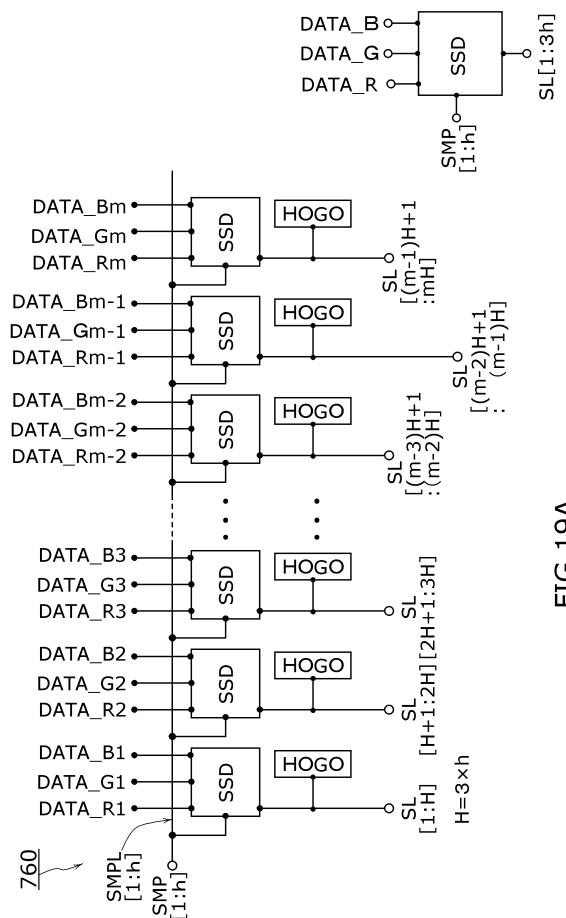

< 分配回路 ( デマルチプレクサ ) の構成例 >

図 19 A は、 分配回路 ( デマルチプレクサ ) の構成の一例を示す回路図であり、 図 19 B は同プロック図である。 分配回路 760 は、 サンプリング信号 ( 制御信号 ) に従って、 1 つの信号を複数の配線に分配する機能を有する回路である。 分配回路 760 は、 駆動回路 722 の最終段に設けられ、 分配回路 760 の出力に配線 S L が接続されている。 分配回路 760 では、  $x$  本の配線 S L から、 順次に  $n$  本の配線 S L を選択し、 それらを電気的に導通させる機能を有する。

#### 【 0179 】

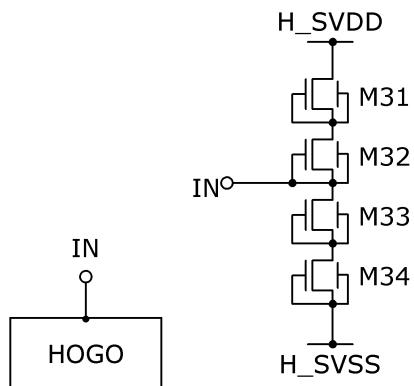

図 19 A に示すように、 分配回路 760 は、  $m$  段の分配回路 S S D を有する。 回路 S S D は、 分配回路 760 の単位回路に相当する。 図 19 B に、 回路 S S D のプロック図を示し、 図 20 に同回路図を示す。 回路 S S D の出力には、 保護回路 H O G O が接続されている。 図 21 A に回路 H O G O のプロック図を示し、 図 21 B に同回路図を示す。

#### 【 0180 】

図 19 A は、 赤色 ( R ) のビデオ信号 D A T A \_ R 、 緑色 ( G ) のビデオ信号 D A T A \_ G 、 青色 ( B ) のビデオ信号 D A T A \_ B を組み合わせて 1 つの画像を表示する構造の表示装置に用いられる分配回路 760 の一例を示している。 図 19 A の例では、 分配回路 760 によって、 1 本のビデオ信号線から、  $h$  本 (  $h$  は 2 以上の整数 ) の配線 S L にビデオ信号を供給可能としている。 よって、 分配回路 760 を駆動回路 722 に設けることで、 配線 S L にビデオ信号を供給するための外部端子数を削減することができる。

#### 【 0181 】

分配回路 760 は、 サンプリング信号 S M P を供給する  $h$  本の配線 S M P L 、  $m$  段の回路 S S D を有する。 回路 S S D は  $H$  ( =  $3 \times h$  ) 個の出力を有し、 それぞれに異なる列の配線 S L が接続されている。 回路 S S D の入力には R G B 別の 3 本のビデオ信号線、 および  $h$  本の配線 S M P L が接続されている。 また、 回路 S S D ごとに 1 つの保護回路 H O G O が設けられており、  $H$  本の配線 S L に 1 つの回路 H O G O が接続されている。

#### 【 0182 】

図 20 に示すように、 回路 S S D は、 3 つのトランジスタ ( M 21 、 M 22 、 M 23 ) を含むスイッチ回路 S W 20 を単位回路とする。 スイッチ回路 S W 20 が、  $h$  段設けられて

10

20

30

40

50

いる。以下、1段目の回路 SW20 の構成について説明する。他の段の回路 SW も同様の構成を有している。

#### 【0183】

1段目の回路 SW20において、トランジスタ M21 は、DATA\_R を供給するビデオ信号線 (VLR) と配線 SL1との導通状態を制御するスイッチである。トランジスタ M22 は、DATA\_G を供給するビデオ信号線 VLG と、配線 SL2 との導通状態を制御するスイッチである。トランジスタ M23 は、DATA\_B を供給するビデオ信号線 VLB と配線 SL3 との導通状態を制御するスイッチである。また、DATA\_R、DATA\_G、および DATA\_B の供給に必要な3本の配線 SL を、配線群の1つの単位とみなすと、1段目の SW20 に接続されている3本の配線 SL は、第1列目の配線群であり、それぞれ、SL[1R]、SL[1G]、SL[1B] と呼ぶことができる。10

#### 【0184】

トランジスタ M21 - M23 のゲートは、信号 SMP1 が入力される配線 SMP\_L に接続される。信号 SMP1 に従って、トランジスタ M21 - M23 は同時にオンとなり、配線 SL1 - SL3 には、それぞれ、DATA\_R、DATA\_G、および DATA\_B が入力される。例えば、h 個の配線 SMP\_L には、それぞれ、回路 SW20 を導通状態とするサンプリング信号が供給される。

#### 【0185】

トランジスタ M21 - M23 のスイッチング動作により、各配線 SL へのビデオ信号が供給されるため、トランジスタ M21 - M23 は、高速で動作すること、オン電流が大きいことが好ましい。そのため、図 20 に示すように、トランジスタ M21 - M23 に、ゲート電極に接続されたバックゲートを設けることが好ましい。また、トランジスタ M21 - M23 を微細化し、チャネル長を 2.5 μm 未満とすることが好ましい。トランジスタ M21 - M23 としては、例えば、図 1、図 2 に示すトランジスタ TA1、TA2、図 5、図 6 に示すトランジスタ TC1 等を適用することができる。特に、駆動回路部 720 において、トランジスタ M21 - M23 は、特に高速で動作させることが要求される。そこで、高い電界効果移動度を得るために、TA1、TC1 のように酸化物半導体層が多層構造であって、酸化物半導体膜 32 を含むトランジスタであることが特に好ましい。20

#### 【0186】

ここでは、3種類のビデオ信号 (DATA\_R、DATA\_G、DATA\_B) で1つのカラー画像を表示する場合を例に、分配回路の構成を説明したが、本発明の形態において、ビデオ信号の数やその色については、これに制限されるものでない。例えば、赤、緑、青および白の4種類のビデオ信号 (DATA\_R、DATA\_G、DATA\_B、DATA\_W) によりカラー画像を表示することもできる。この場合、回路 SSD の入力には、4種類のビデオ信号 (DATA\_R、DATA\_G、DATA\_B、DATA\_W) に対応する4本のビデオ信号線が接続される。またその出力には、これらビデオ信号が供給される4本の配線 SL が接続される。30

#### 【0187】

##### [保護回路の構成例]

保護回路 HOGO は、ダイオード接続されたトランジスタや抵抗素子等で構成することができる。図 21B の例では、回路 HOGO は直列に接続された4つトランジスタ M31 - M34 を有する。各トランジスタ M31 - M34 はダイオード接続されており、またゲートに接続されたバックゲートを有する。これにより、トランジスタ M31 - M34 のオン電流を大きくすることができる。トランジスタ M31 - M34 には、例えば、トランジスタ TA1 (図 1A)、トランジスタ TA2 (図 1B) 等を適用することができる。また配線 GL に対しても、回路 HOGO と同様な保護回路を接続することができる。40

#### 【0188】

以下、有機エレクトロルミネッセンス表示装置 (OLED)、および液晶表示装置 (LCD) の画素部の構成例について説明する。

#### 【0189】

10

20

30

40

50

## &lt; OLED の画素の構成例 &gt;

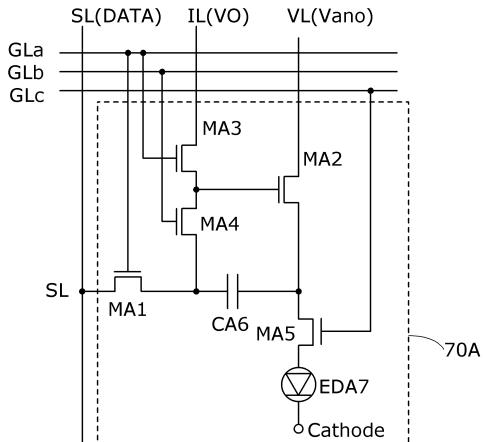

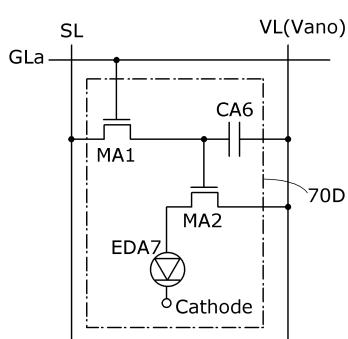

図 22 A は、OLED の画素の構成の一例を示す回路図である。

## 【 0190 】

図 22 A に示すように、画素 70 A は、5 つのトランジスタ MA1 - MA5、容量素子 CA6、発光素子 EDA7 を有する。なお、図 22 A では、トランジスタ MA1 乃至トランジスタ MA5 は、OSトランジスタである。例えば、トランジスタ TB1 ( 図 1C ) や、トランジスタ TD1 ( 図 5C ) 等のように、バックゲートを有さないトランジスタが用いられている。

## 【 0191 】

画素 70 A に、ゲートに接続されたバックゲートを有するトランジスタを設けてもよい。

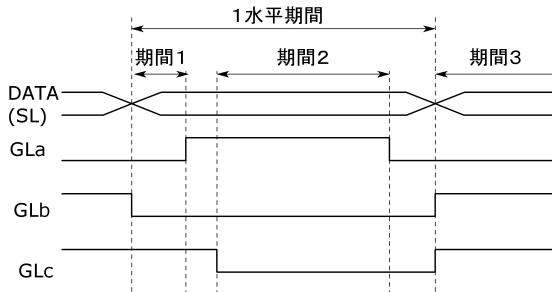

10 例えば、図 23 に示す画素 70 B のように、トランジスタ MA4 を除く、4 つのトランジスタ MA1、MA2、MA3 および MA5 を、バックゲートを有するトランジスタとすることができる。この場合、これらのトランジスタには、例えば、トランジスタ TA2 ( 図 1B )、トランジスタ TB2 ( 図 5B ) などを適用することができる。また、例えば、トランジスタ TD1 ( 図 5C ) にバックゲートをさらに設けた構造のトランジスタを適用することもできる。

## 【 0192 】

トランジスタ MA1 は、配線 SL と容量素子 CA6 の一方の電極間の導通を制御する機能を有する。容量素子 CA6 の他方の電極は、トランジスタ MA2 のソース及びドレインの一方に接続されている。トランジスタ MA3 は、配線 IL とトランジスタ MA2 のゲート間の導通を制御する機能を有する。トランジスタ MA4 は、容量素子 CA6 とトランジスタ MA2 のゲート間の導通を制御する機能を有する。トランジスタ MA5 は、トランジスタ MA2 のソース及びドレインの一方と発光素子 EDA7 の陽極の導通を制御する機能を有する。トランジスタ MA2 は、配線 VL と発光素子 EDA7 の陽極間の導通状態を制御する機能を有している。

## 【 0193 】

発光素子 EDA7 は、陽極、陰極、および陽極と陰極の間に設けられた EL 層を有する。EL 層は、単層または複数の層で構成されていて、これらの層の中に、発光性の物質を含む発光層を少なくとも含んでいる。EL 層は、陰極を基準としたときの、陰極と陽極間の電位差が、発光素子 EDA7 の閾値電圧 Vt h e 以上になったときに供給される電流により、エレクトロルミネッセンスが得られる。エレクトロルミネッセンスには、一重項励起状態から基底状態に戻る際の発光 ( 蛍光 ) と三重項励起状態から基底状態に戻る際の発光 ( リン光 ) とが含まれる。

## 【 0194 】

トランジスタ MA2 のドレイン電流により発光素子 EDA7 の輝度が制御される。画素 70 A では、配線 SL から入力されるビデオ信号 DATA により、トランジスタ MA2 のゲートの電位を制御することで、発光素子 EDA7 の輝度を制御している。

## 【 0195 】

図 22 B は、画素 70 A の動作の一例を示すタイミングチャートである。トランジスタ MA1、MA3、MA4、MA5 の導通状態は、それぞれ、配線 GLa、GLa、GLb、GLc の電位により定まる。配線 GLa、GLb、GLc には、駆動回路 721 から、信号が入力される。配線 SL には、駆動回路 722 から、ビデオ信号 DATA が入力される。配線 VL には電位 Vano が供給される。配線 IL には電位 VO が供給される。

## 【 0196 】

期間 1 では、トランジスタ MA5 が導通状態になる。期間 2 では、トランジスタ MA1 及びトランジスタ MA3 が導通状態となり、トランジスタ MA4 及びトランジスタ MA5 が非導通状態となる。なお、期間 1 から期間 2 に移行する際、配線 GLa の電位をローレベルからハイレベルに遷移させてから、配線 GLc の電位をハイレベルからローレベルに遷移させることが望ましい。期間 3 では、トランジスタ MA4 及びトランジスタ MA5 が導通状態となり、トランジスタ MA1 及びトランジスタ MA3 が非導通状態となる。期間 3

10

20

30

40

50

において、期間 2 に配線 S L に入力されていたビデオ信号 D A T A の電位レベルに応じた輝度で、発光素子 E D A 7 が発光する。

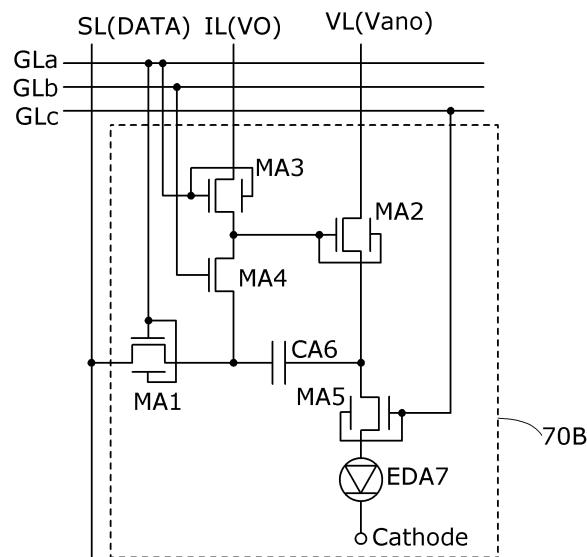

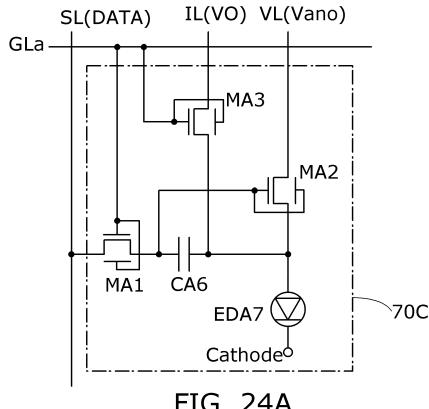

#### 【 0 1 9 7 】

O L E D の画素は、画素 7 0 A ( 図 2 2 A ) 、画素 7 0 B ( 図 2 3 ) に限定されるものではない。画素の他の構成例を図 2 4 に示す。

#### 【 0 1 9 8 】

図 2 4 A に示す画素 7 0 C は、3 つのトランジスタ ( M A 1 、 M A 2 、 M A 3 ) 、容量素子 C A 6 および発光素子 E D A 7 を有する。ここでは、3 つのトランジスタ ( M A 1 、 M A 2 、 M A 3 ) をゲート電極に接続されたバックゲートを有するトランジスタとした例を示している。画素 7 0 C において、3 つのトランジスタ ( M A 1 、 M A 2 、 M A 3 ) の少なくとも 1 つを、バックゲートを有さないトランジスタとすることができます。10

#### 【 0 1 9 9 】

図 2 4 B に示す画素 7 0 D は、2 つのトランジスタ ( M A 1 、 M A 2 ) 、容量素子 C A 6 および発光素子 E D A 7 を有する。ここでは、トランジスタ ( M A 1 、 M A 2 ) がバックゲートを有していないトランジスタである例を示している。画素 7 0 D において、2 つのトランジスタ ( M A 1 、 M A 2 ) の双方、または一方にバックゲートを設けることができる。

#### 【 0 2 0 0 】

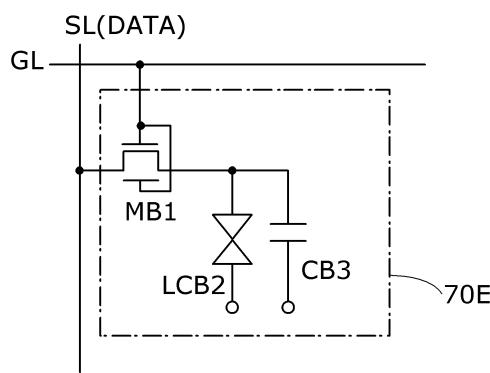

< L C D の画素の構成例 >

図 2 5 は、L C D の画素の構成例を示す回路図である。

20

#### 【 0 2 0 1 】

画素 7 0 E は、トランジスタ M B 1 、液晶素子 L C B 2 、および容量素子 C B 3 を有する。トランジスタ M B 1 のゲートは、配線 G L に接続されている。トランジスタ M B 1 は、配線 S L と液晶素子 L C B 2 との導通状態を制御する機能を有する。液晶素子 L C B 2 は、画素電極と、共通電極と、画素電極と共通電極間に形成される電界が作用する液晶材料とを有する素子である。画素電極と共通電極間の電圧 ( 電位差 ) は、配線 S L から入力されるビデオ信号 D A T A の電位によって決定される。容量素子 C B 3 は画素電極と共通電極間の電圧を保持するための機能を有する。

#### 【 0 2 0 2 】

トランジスタ M B 1 は、例えば、O S トランジスタで構成することができる。図 2 5 の例では、トランジスタ M B 1 をバックゲートがゲートに接続されたトランジスタとしている。トランジスタ M B 1 として、例えば、トランジスタ T B 1 ( 図 1 C ) 、トランジスタ T B 2 ( 図 5 B ) 、トランジスタ T D 1 ( 図 5 C ) 等を適用することができる。30

#### 【 0 2 0 3 】

また、トランジスタ M B 1 を、バックゲートを有していないトランジスタとすることもできる。この場合、トランジスタ M B 1 として、トランジスタ T B 1 ( 図 1 C ) や、トランジスタ T D 1 ( 図 5 C ) 等を適用することができる。

#### 【 0 2 0 4 】

また、画素 7 0 A 、 7 0 B 、 7 0 C 、 7 0 D および 7 0 E において、トランジスタにバックゲートを設ける場合、バックゲートをゲートに接続してもよいし、そのゲートとは異なる信号や電位を供給できるようにしてもよい。

40

#### 【 0 2 0 5 】

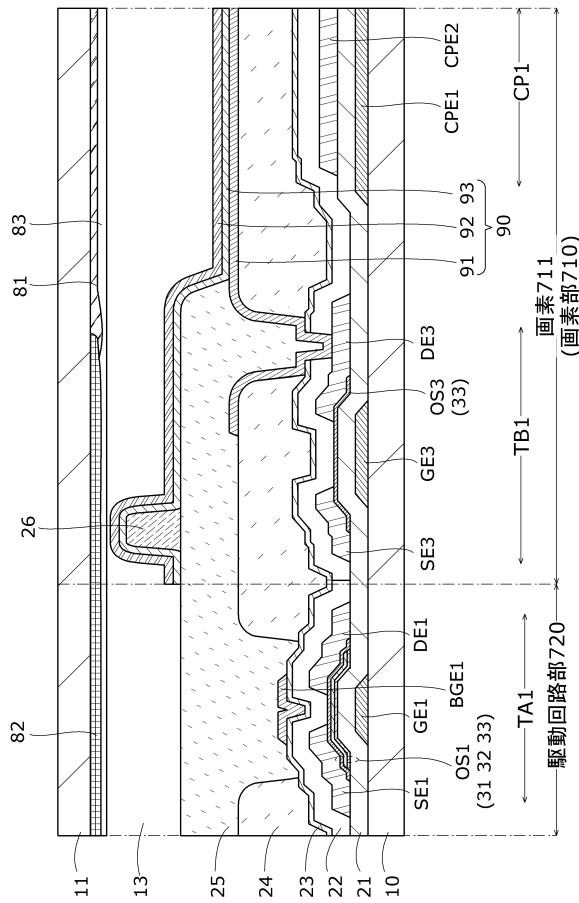

< O L E D の構成例 >

図 2 6 に、表示装置 7 0 0 として、O L E D の構成の一例を示す。なお、図 2 6 は、O L E D の画素部と駆動回路部のデバイス構造を説明するための図であり、O L E D の特定の部位の断面図ではない。

#### 【 0 2 0 6 】

ここでは、基板 1 0 上に、トランジスタ T A 1 、トランジスタ T B 1 、容量素子 C P 1 が形成されている。トランジスタ T A 1 は駆動回路部 7 2 0 に含まれるトランジスタである。トランジスタ T B 1 は画素 7 1 1 に含まれるトランジスタである。また、画素 7 1 1 に

50

は容量素子 C P 1 が形成されている。容量素子 C P 1 は、一対の電極 ( C P E 1、C P E 2 ) を有し、誘電体として絶縁層 2 1 を有する。電極 C P E 1 は、トランジスタ T B 1 のゲート電極 G E 3 等と同じ導電膜 5 1 から作製される電極である。電極 C P E 2 は、トランジスタ T B 1 のソース電極 S E 3 等と同じ導電膜 5 2 から作製される電極である。画素 7 1 1 の構成によって、電極 C P E 1 がゲート電極 G E 3 が一体的に形成される場合がある。また、電極 C P E 2 がソース電極 S E 3 またはドレイン電極 D E 3 と一体的に形成される場合がある。また、回路構成によって、ゲート電極 G E 1 等は、配線として形成されている場合がある。

#### 【 0 2 0 7 】

トランジスタ T A 1、トランジスタ T B 1 および容量素子を覆って、絶縁層 2 4、および絶縁層 2 5 が形成されている。絶縁層 2 5 上に発光素子 9 0 が形成されている。発光素子 9 0 は、電極 9 1、電極 9 2 および E L 層 9 3 を有する。10

#### 【 0 2 0 8 】

電極 9 1 は、絶縁層 2 4 上に形成されており、絶縁層 2 4 に形成された開口において電極 D E 3 と電極 9 1 が接している。電極 9 1 および絶縁層 2 4 を覆って絶縁層 2 5 が形成され、絶縁層 2 5 上に絶縁層 2 6 が形成されている。絶縁層 2 6 を覆って、E L 層 9 3 および電極 9 2 が形成されている。電極 9 1 は、画素 7 1 1 每に分割された導電膜であり、電極 9 2 は画素部 7 1 0 で共通の 1 つの導電膜である。

#### 【 0 2 0 9 】

電極 9 1 としては、例えば、可視光において反射性の高い金属膜が好ましい。該金属膜としては、例えば、アルミニウム、銀、またはこれらの合金等を用いることができる。20

#### 【 0 2 1 0 】

電極 9 2 としては、例えば、可視光において透光性のある導電膜を用いると好ましい。該導電膜としては、例えば、インジウム ( I n )、亜鉛 ( Z n )、錫 ( S n ) の中から選ばれた一種を含む材料を用いるとよい。また、電極 9 2 としては、例えば、酸化タンゲステンを含むインジウム酸化物、酸化タンゲステンを含むインジウム亜鉛酸化物、酸化チタンを含むインジウム酸化物、酸化チタンを含むインジウム錫酸化物、インジウム錫酸化物 ( I T O )、インジウム亜鉛酸化物、酸化シリコンを添加したインジウム錫酸化物などの透光性を有する導電性材料を用いることができる。とくに、電極 9 2 に酸化シリコンを添加したインジウム錫酸化物を用いると、表示装置を折り曲げる際に、電極 9 2 にクラック等が発生しにくいため好適である。30

#### 【 0 2 1 1 】

E L 層 9 3 としては、電極 9 1 と電極 9 2 から注入される正孔と電子とが再結合し発光できる発光材料を用いればよい。また、該発光材料の他に、正孔注入層、正孔輸送層、電子輸送層、電子注入層などの機能層を必要に応じて形成してもよい。

#### 【 0 2 1 2 】

絶縁層 2 4、および絶縁層 2 5 は平坦化膜として機能させることが好ましい。また絶縁層 2 6 は基板 1 0 と基板 1 1 間のギャップを維持するためのするスペーサとして機能させることができる。絶縁層 2 4 - 2 6 としては、フォトポリマー、感光性アクリル、感光性ポリイミド等の感光性樹脂材料で形成することが好ましい。また、絶縁層 2 4 - 2 6 としては、C V D 法やスパッタ法などにより形成することのできる酸化シリコン膜等の無機絶縁材料で形成してもよい。40

#### 【 0 2 1 3 】

シール部材 ( 図示せず ) により、基板 1 0 と対向するように基板 1 1 が固定されている。シール部材は基板 1 0 と基板 1 1 の周囲に設けられている。基板 1 1 には、基板 1 0 と同様な基板を用いることができる。基板 1 1 には、カラーフィルタ層 8 1、遮光層 8 2 およびオーバーコート層 8 3 が形成されている。カラーフィルタ層 8 1 は、E L 層 9 3 で発した光 ( 例えは、白色光 ) を、異なる色の光に変換するための光学フィルター層である。基板 1 0 にカラーフィルタ層 8 1 を形成してもよい。

#### 【 0 2 1 4 】

50

また、E L層93の形成を、画素711の表示色（たとえば、赤色、緑色、および青色）毎に異なる層とする、いわゆる塗り分け方式で形成する場合は、カラーフィルタ層81を設けてもよいし、設けなくてもよい。

#### 【0215】

遮光層82は、基板11を通過してO L E D内部に侵入する光を遮光する機能を有する。遮光層82は、単層構造であっても、2層以上の積層構造であってもよい。遮光層82を構成する膜としては、例えば、クロム、チタン、ニッケル、カーボンブラックを分散した高分子等となる膜があげられる。遮光層82は、駆動回路部720および画素711の表示に寄与しない領域を覆うように形成される。

#### 【0216】

オーバーコート層83は、基板11の表面の平坦化と不純物（代表的には水および／または酸素）の拡散を防ぐ機能を有する。オーバーコート層83は、例えば、ポリイミド樹脂、エポキシ樹脂、アクリル樹脂等で形成することができる。

#### 【0217】

また、基板11に、発光素子90の劣化を防止するため乾燥剤を取り付けてもよい。また、同様の理由で、基板10と基板11の間の空間13には、窒素ガスやアルゴンガスなどの不活性気体を充填する、また樹脂材料などの固体物質を充填するとよい。また、空間13に屈折率の高い物質（樹脂等）を充填することで、発光素子90の光の取り出し効率を向上させることができる。

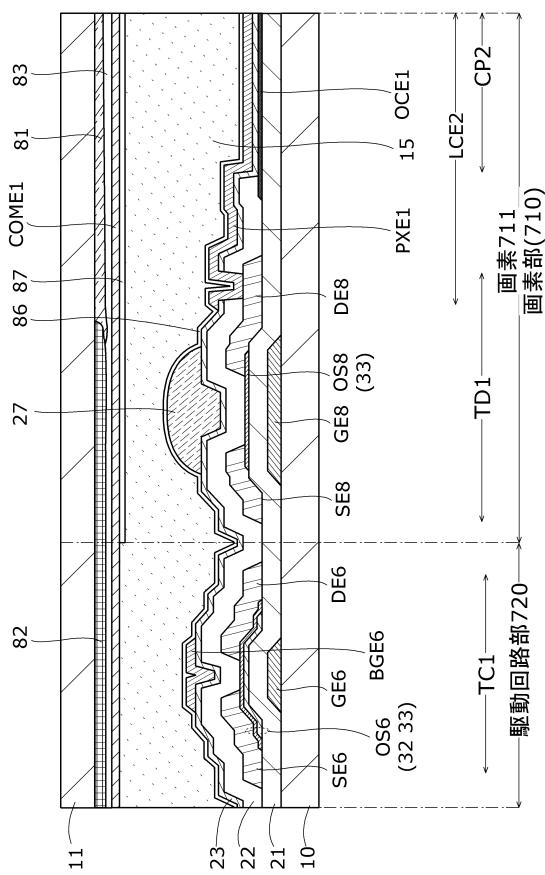

#### 【0218】

##### < L C D の構成例 >

図27に、表示装置700として、L C Dの構成の一例を示す。なお、図26と同様に図27も、L C Dの画素部と駆動回路部のデバイス構造の積層構造を説明するための図であり、L C Dの特定の部位の断面図ではない。

#### 【0219】

ここでは、基板10上に、トランジスタT C 1、トランジスタT D 1、容量素子C P 2が形成されている。トランジスタT C 1は駆動回路部720に含まれるトランジスタである。トランジスタT D 1は画素711に含まれるトランジスタである。また、画素711には容量素子C P 2が形成されている。容量素子C P 2は、一対の電極（P X E 1、O C E 1）を有し、絶縁層21を誘電体とするデバイスである。

#### 【0220】

電極P X E 1は、トランジスタT D 1に接続されている。ここではトランジスタT C 1のバックゲート電極B G E 6は、電極P X E 1と同じ導電膜から、同じ工程で作製される。電極O C E 1は、酸化物半導体膜33から形成される導電膜である。絶縁層23として窒化物絶縁膜を形成する場合、酸化物半導体膜33が絶縁層23に接した状態で加熱することで、その抵抗値がさがり、電極O C E 1が形成される。電極O C E 1を作製する場合は、絶縁層23を形成する前に、絶縁層22の容量素子C P 2が形成される領域に開口を形成する。

#### 【0221】

絶縁層23上に絶縁層27が形成される。絶縁層27は、絶縁層24 - 26と同様に有機樹脂膜で形成することが好ましい。絶縁層27は、画素711に形成されるトランジスタT D 1を覆うように形成される。絶縁層27としては、例えば、ポリイミド、アクリル、ポリアミド、エポキシ等を用いることができる。その厚さが500nm以上10μm以下であることが好ましい。

#### 【0222】

絶縁層27として、500nm以上の厚い有機樹脂膜を形成することで、ゲート電極G E 8に負の電圧が印加されることによって発生する電場が絶縁層27の表面にまで影響せず、絶縁層27の表面に正の電荷が帯電しにくくなる。また、空气中に含まれる正の荷電粒子が、絶縁層27の表面に吸着しても、絶縁層27は、500nm以上と厚さが厚いため、酸化物半導体層O S 8と絶縁層21の界面は、絶縁層27の表面に吸着した正の荷電粒

10

20

30

40

50

子の電場の影響を受けにくい。このような構造のため、層O S 8と絶縁層2 1の界面は実質的に正のバイアスが印加された状態とならないため、トランジスタT D 1のしきい値電圧の変動をおさえることができる。そのため、信頼性の高いL C Dを提供することが可能になる。

#### 【0223】

基板1 1には、カラーフィルタ層8 1、遮光層8 2およびオーバーコート層8 3を覆って対向電極C O M E 1が形成されており、電極C O M E 1を覆って配向層8 7が形成されている。また、基板1 0にも配向層8 6が形成される。配向層8 6、8 7は必要に応じて設ければよい。

#### 【0224】

シール部材(図示せず)により、基板1 0と対向するように基板1 1が固定されている。シール部材は基板1 0と基板1 1の周囲に設けられている。そのため、駆動回路部7 2 0の全てまたは一部がシール部材で覆われる場合もある。基板1 0と基板1 1の隙間には液晶材料1 5が封止されている。液晶材料1 5、電極P X E 1および電極C O M E 1により液晶素子L C E 2が構成される。基板1 0と基板1 1の間隔を維持するためのスペーサとして機能する絶縁層が基板1 0または基板1 1に設けられている。

#### 【0225】

ここでは、表示素子として発光素子、液晶素子を有するO L E D、L C Dについて説明したが、本発明の一形態はこれに限定されない。例えば、本明細書等において、表示素子、表示素子を有する装置である表示装置、発光素子、及び発光素子を有する装置である発光装置は、様々な形態を用いること、又は様々な素子を有することが出来る。表示素子、表示装置、発光素子又は発光装置は、例えば、E L 素子(有機物及び無機物を含むE L 素子、有機E L 素子、無機E L 素子)、L E D(白色L E D、赤色L E D、緑色L E D、青色L E Dなど)、トランジスタ(電流に応じて発光するトランジスタ)、電子放出素子、液晶素子、電子インク、電気泳動素子、グレーティングライトバルブ(G L V)、プラズマディスプレイ(P D P)、M E M S(マイクロ・エレクトロ・メカニカル・システム)を用いた表示素子、デジタルマイクロミラーデバイス(D M D)、D M S(デジタル・マイクロ・シャッター)、M I R A S O L(登録商標)、I M O D(インターフェアレンス・モジュレーション)素子、シャッター方式のM E M S表示素子、光干渉方式のM E M S表示素子、エレクトロウェッティング素子、圧電セラミックディスプレイ、カーボンナノチューブを用いた表示素子などの少なくとも一つを有している。これらの他にも、電気的または磁気的作用により、コントラスト、輝度、反射率、透過率などが変化する表示媒体を有していても良い。

#### 【0226】

E L 素子を用いた表示装置の一例としては、E L 表示装置などがある。電子放出素子を用いた表示装置の一例としては、フィールドエミッションディスプレイ(F E D)又はS E D方式平面型ディスプレイ(S E D: Surface-conduction E lec tron-emitter D isplay)などがある。液晶素子を用いた表示装置の一例としては、液晶表示装置(透過型液晶表示装置、半透過型液晶表示装置、反射型液晶表示装置、直視型液晶表示装置、投射型液晶表示装置)などがある。電子インク又は電気泳動素子を用いた表示装置の一例としては、電子ペーパーなどがある。なお、半透過型液晶表示装置や反射型液晶表示装置を実現する場合には、画素電極の一部、または、全部が、反射電極としての機能を有するようにすればよい。例えば、画素電極の一部、または、全部が、アルミニウム、銀、などを有するようにすればよい。さらに、その場合、反射電極の下に、S R A Mなどの記憶回路を設けることも可能である。これにより、さらに、消費電力を低減することができる。

#### 【0227】

##### (実施の形態3)

実施の形態1で述べたように、半導体装置を一部あるいは全部完成させた後、半導体装置の作製に使用した基板を分離して、他の基板に転載することが可能である。このような作

10

20

30

40

50

製方法を用いることで、トランジスタを耐熱性の劣る基板や可撓性の基板にも転載できる。

【0228】

トランジスタが転載される基板の一例としては、上述したトランジスタを形成することが可能な基板に加え、紙基板、セロファン基板、アラミドフィルム基板、ポリイミドフィルム基板、石材基板、木材基板、布基板（天然纖維（絹、綿、麻）、合成纖維（ナイロン、ポリウレタン、ポリエステル）若しくは再生纖維（アセテート、キュプラ、レーヨン、再生ポリエステル）などを含む）、皮革基板、又はゴム基板などがある。これらの基板を用いることにより、特性のよいトランジスタの形成、消費電力の小さいトランジスタの形成、壊れにくい装置の製造、耐熱性の付与、軽量化、又は薄型化を図ることができる。 10

【0229】

以下、図面を参照して、このような半導体装置の作製方法について説明する。ここでは、半導体装置として表示装置700を作製する例について説明する。

【0230】

<作製方法例1>

本発明の一形態にかかる表示装置700の作製方法について、図28及び図29を用いて説明する。

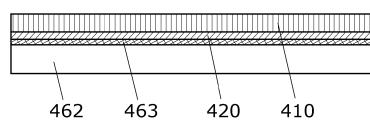

【0231】

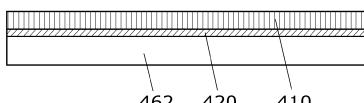

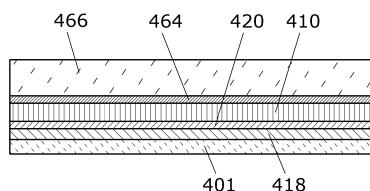

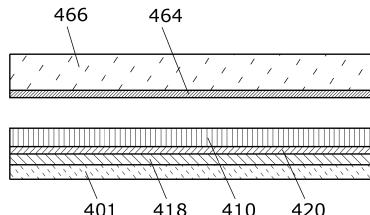

基板462上に絶縁膜420を形成し、絶縁膜420上に素子層410を形成する（図28A）。素子層410には、トランジスタ等の半導体素子が形成されている。或いは、素子層410には、半導体素子に加え、表示素子、または画素電極などの表示素子の一部が形成されていても良い。 20

【0232】

基板462としては、少なくとも、後の熱処理に耐えうる程度の耐熱性を有している必要がある。例えば、ガラス基板、セラミック基板、石英基板、サファイア基板等を、基板462として用いてもよい。

【0233】

基板462にガラス基板を用いる場合、基板462と絶縁膜420との間に、酸化シリコン膜、酸化窒化珪素膜、窒化珪素膜、窒化酸化シリコン膜等の絶縁膜を形成すると、ガラス基板からの汚染を防止でき、好ましい。 30

【0234】

絶縁膜420には、例えば、エポキシ樹脂、アラミド樹脂、アクリル樹脂、ポリイミド樹脂、ポリアミド樹脂、ポリアミドイミド樹脂等の有機樹脂膜を用いることができる。中でもポリイミド樹脂を用いると耐熱性が高いため好ましい。絶縁膜420として、例えば、ポリイミド樹脂を用いる場合、該ポリイミド樹脂の膜厚は、3nm以上20μm以下、好ましくは500nm以上2μm以下である。絶縁膜420として、ポリイミド樹脂を用いる場合、スピンドルコート法、ディップコート法、ドクターブレード法等により形成することができる。例えば、絶縁膜420としてポリイミド樹脂を用いる場合、ドクターブレード法により、当該ポリイミド樹脂を用いた膜の一部を除去することで、所望の厚さを有する絶縁膜420を得ることができる。 40

【0235】

なお、素子層410は、その作製工程における温度が室温以上300℃以下であると好ましい。例えば、素子層410に含まれる、無機材料を用いた絶縁膜または導電膜は、成膜温度が150℃以上300℃以下、さらには200℃以上270℃以下で形成されることが好ましい。また、素子層410に含まれる、有機樹脂材料を用いた絶縁膜等は、成膜温度が室温以上100℃以下で形成されると好ましい。

【0236】

また、素子層410に含まれるトランジスタの酸化物半導体膜には、後述するCAC-O<sub>S</sub>膜を用いることが好ましい。当該トランジスタの酸化物半導体膜にCAC-O<sub>S</sub>膜を用いると、例えば、表示装置700を折り曲げる際に、チャネル形成領域にクラック等

10

20

30

40

50

が入りづらく、曲げに対する耐性を高めることが可能となる。

**【0237】**

また、素子層410に含まれる導電膜として、酸化シリコンを添加したインジウム錫酸化物を用いると、表示装置700を折り曲げる際に、当該導電膜にクラック等が入りづらくなるため、好ましい。

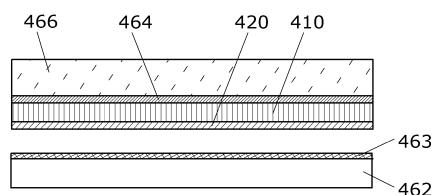

**【0238】**

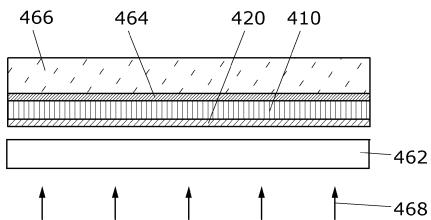

次に、素子層410と、仮支持基板466とを、剥離用接着剤464を用いて接着し、基板462から絶縁膜420と素子層410を剥離する。これにより、絶縁膜420と素子層410は、仮支持基板466側に設けられる（図28B）。

**【0239】**

仮支持基板466としては、ガラス基板、石英基板、サファイア基板、セラミック基板、金属基板などを用いることができる。また、本実施の形態の処理温度に耐えうる耐熱性を有するプラスチック基板を用いてもよいし、フィルムのような可撓性基板を用いてもよい。

**【0240】**

剥離用接着剤464としては、水や溶媒に可溶なものや、紫外線などの照射により可塑化させることができるもののように、必要時に仮支持基板466と素子層410とを化学的もしくは物理的に分離することが可能な接着剤を用いる。

**【0241】**

なお、仮支持基板466への転置工程は、様々な方法を適宜用いることができる。例えば、基板462の絶縁膜420が形成されていない側、すなわち図28Bに示す下方側より絶縁膜420にレーザ光468を照射することで、絶縁膜420を脆弱化させることで基板462と絶縁膜420を剥離することができる。また、上記レーザ光468の照射エネルギー密度を調整することで、基板462と絶縁膜420の密着性が高い領域と、基板462と絶縁膜420の密着性が低い領域を作り分けてから剥離してもよい。

**【0242】**

なお、本実施の形態においては、基板462と絶縁膜420の界面で剥離する方法について例示したが、これに限定されない。例えば、絶縁膜420と素子層410との界面で剥離してもよい。

**【0243】**

また、基板462と絶縁膜420との界面に液体を浸透させて基板462から絶縁膜420を剥離してもよい。または、絶縁膜420と素子層410との界面に液体を浸透させて絶縁膜420から素子層410を剥離してもよい。上記液体としては、例えば、水、極性溶媒等を用いることができる。絶縁膜420を剥離する界面、具体的には基板462と絶縁膜420との界面または絶縁膜420と素子層410との界面に液体を浸透させることによって、素子層410に与えられる剥離に伴い発生する静電気等の影響を抑制することができる。

**【0244】**

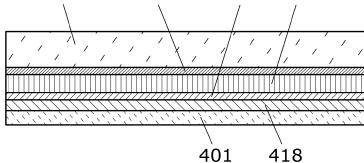

次に、接着層418を用いて、絶縁膜420に基板401を接着させる（図28C）。

**【0245】**

次に、剥離用接着剤464を溶解または可塑化させて、素子層410から剥離用接着剤464及び仮支持基板466を取り外す（図28D）。

**【0246】**

なお、素子層410の表面が露出するように剥離用接着剤464を水や溶媒などで除去すると好ましい。

**【0247】**

以上により、基板401上に素子層410を作製することができる。

**【0248】**

次に、図28に示す工程と同様の工程により、基板405上に、接着層412と、接着層412上の絶縁膜440と、素子層411とを形成する（図29A）。素子層411が有

10

20

30

40

50

する絶縁膜440としては、絶縁膜420と同様の材料、ここでは有機樹脂を用いて形成することができる。

【0249】

次に、素子層410と素子層411の間に、封止層432を充填し、素子層410と素子層411と、を貼り合わせる(図29B)。

【0250】

封止層432により、例えば、固体封止させることができる。ただし、封止層432としては、可撓性を有する構成が好ましい。封止層432としては、例えば、ガラスフリットなどのガラス材料や、二液混合型の樹脂などの常温で硬化する硬化樹脂、光硬化性の樹脂、熱硬化性の樹脂などの樹脂材料を用いることができる。

10

【0251】

以上により、表示装置700を作製することができる。

【0252】

<作製方法例2>

次いで、本発明の一形態にかかる表示装置700の別の作製方法について、図30を用いて説明する。なお、図30では、絶縁膜420及び絶縁膜440として無機絶縁膜を用いる構成について説明する。

【0253】

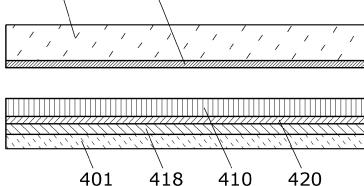

まず、基板462上に剥離層463を形成する。次に、剥離層463上に絶縁膜420を形成し、絶縁膜420上に素子層410を形成する(図30A)。

20

【0254】

剥離層463としては、例えば、タングステン、モリブデン、チタン、タンタル、ニオブ、ニッケル、コバルト、ジルコニウム、亜鉛、ルテニウム、ロジウム、パラジウム、オスミウム、イリジウム、シリコンから選択された元素、該元素を含む合金材料、または該元素を含む化合物材料を含み、単層または積層された構造を用いることができる。また、シリコンを含む層の場合、該シリコンを含む層の結晶構造としては、非晶質、微結晶、多結晶、単結晶のいずれでもよい。

【0255】

剥離層463としては、スパッタリング法、PECVD法、塗布法、印刷法等により形成できる。なお、塗布法は、スピンドルティング法、液滴吐出法、ディスペ ns法を含む。

30

【0256】

剥離層463が単層構造の場合、タングステン、モリブデン、またはタングステンとモリブデンの混合物を含む層を形成することが好ましい。また、タングステンの酸化物もしくは酸化窒化物を含む層、モリブデンの酸化物もしくは酸化窒化物を含む層、またはタングステンとモリブデンの混合物の酸化物もしくは酸化窒化物を含む層を形成してもよい。なお、タングステンとモリブデンの混合物とは、例えば、タングステンとモリブデンの合金に相当する。

【0257】

また、剥離層463として、タングステンを含む層とタングステンの酸化物を含む層の積層構造を形成する場合、タングステンを含む層を形成し、その上層に酸化物で形成される絶縁層を形成することで、タングステン層と絶縁層との界面に、タングステンの酸化物を含む層が形成されることを活用してもよい。また、タングステンを含む層の表面を、熱酸化処理、酸素プラズマ処理、亜酸化窒素( $N_2O$ )プラズマ処理、オゾン水等の酸化力の強い溶液での処理等を行ってタングステンの酸化物を含む層を形成してもよい。またプラズマ処理や加熱処理は、酸素、窒素、亜酸化窒素単独、あるいは該ガスとその他のガスとの混合気体雰囲気下で行ってもよい。上記プラズマ処理や加熱処理により、剥離層463の表面状態を変えることにより、剥離層463と後に形成される絶縁膜420との密着性を制御することが可能である。

40

【0258】

絶縁膜420には、例えば、酸化シリコン膜、窒化珪素膜、酸化窒化珪素膜、窒化酸化シ

50

リコン膜、酸化アルミニウム膜などの透湿性の低い無機絶縁膜を用いることができる。上記無機絶縁膜は、例えば、スパッタリング法、PECVD法等を用いて形成することができる。

#### 【0259】

次に、素子層410と、仮支持基板466とを、剥離用接着剤464を用いて接着し、剥離層463から絶縁膜420と素子層410を剥離する。これにより、絶縁膜420と素子層410は、仮支持基板466側に設けられる(図30B)。

#### 【0260】

なお、仮支持基板466への転置工程は、様々な方法を適宜用いることができる。例えば、剥離層463と絶縁膜420との界面に金属酸化膜を含む層を形成した場合は、該金属酸化膜を結晶化により脆弱化して、剥離層463から絶縁膜420を剥離することができる。また、剥離層463をタンゲステン膜で形成した場合は、アンモニア水と過酸化水素水の混合溶液によりタンゲステン膜をエッチングしながら剥離を行ってもよい。

10

#### 【0261】

また、剥離層463と絶縁膜420との界面に液体を浸透させて剥離層463から絶縁膜420を剥離してもよい。上記液体としては、例えば、水、極性溶媒等を用いることができる。絶縁膜420を剥離する界面、具体的には剥離層463と絶縁膜420との界面に液体を浸透させることによって、素子層410に与えられる剥離に伴い発生する静電気等の影響を抑制することができる。

#### 【0262】

20

次に、絶縁膜420に接着層418を用いて基板401を接着する(図30C)。次に、剥離用接着剤464を溶解または可塑化させて、素子層410から剥離用接着剤464と仮支持基板466を取り除く(図30D)。なお、素子層410の表面が露出するように剥離用接着剤464を水や溶媒などで除去すると好ましい。以上により、基板401上に素子層410を作製することができる。

#### 【0263】

次に、図30に示す工程と同様の形成方法により、基板405と、基板405上の接着層412と、接着層412上の絶縁膜440と、素子層411と、を形成する。その後、素子層410と素子層411の間に、封止層432を充填し、素子層410と素子層411と、を貼り合わせる。

30

#### 【0264】

最後に、素子層410に形成されている接続端子に異方性導電膜によってFPCを電気的に接続する。このFPCにICチップを実装してもよい。

#### 【0265】

以上により、表示装置700を作製することができる。

#### 【0266】

##### (実施の形態4)

本実施の形態では、半導体装置の一例として、表示装置および表示装置を備えた電子機器などについて説明する。

#### 【0267】

40

##### <表示装置の外観>

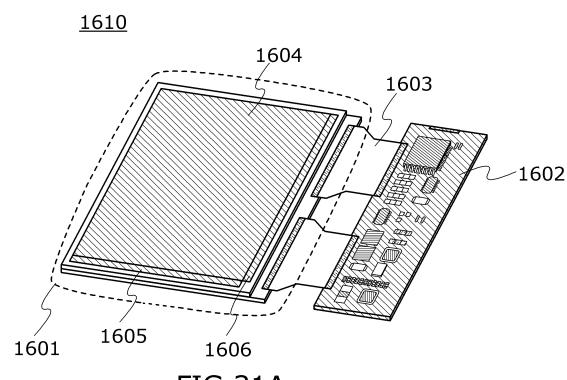

図31Aは、表示装置の外観の一例を示す、斜視図である。図31Aに示すように、表示装置1610は、パネル1601と、コントローラ、電源回路、画像処理回路、画像メモリ、CPUなどが設けられた回路基板1602と、接続部1603とを有している。パネル1601は、画素が複数設けられた画素部1604と、複数の画素を行ごとに選択する駆動回路1605と、選択された行内の画素への画像信号Singの入力を制御する駆動回路1606とを有する。

#### 【0268】

回路基板1602から、接続部1603を介して、各種信号と、電源の電位とが、パネル1601に入力される。接続部1603には、FPC(FlexiblePrinte

50

d Circuit)などを用いることができる。FPCにチップを実装したものをCOFテープと呼び、COFテープを用いると、より小さい面積でより高密度の実装を行うことができる。また、接続部1603にCOFテープを用いる場合、回路基板1602内的一部の回路、或いはパネル1601が有する駆動回路1605や駆動回路1606の一部などを別途用意したチップに形成しておき、COF(Chip On Film)法を用いて当該チップをCOFテープに接続しておいても良い。

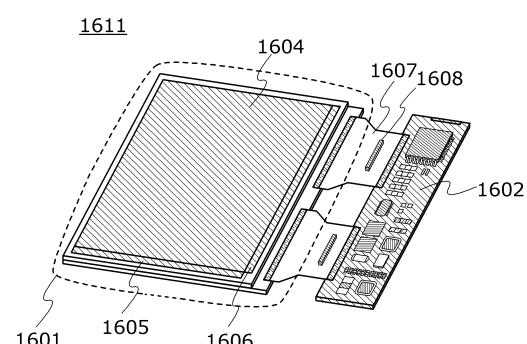

#### 【0269】

また、COFテープ1607を用いた表示装置の外観の一例を示す斜視図を図31Bに示す。図31Bに示すように、表示装置1611において、チップ1608は、バンプなどの端子を表面に有する半導体ペアチップ(IC、LSIなど)である。さらに、COFテープ1607に、CR部品も実装でき、回路基板1602の面積縮小も図れる。フレキシブル基板の配線パターンは、実装するチップの端子に対応して複数形成される。チップ1608は、ポンダー装置などにより、配線パターンを有するフレキシブル基板上に位置決めして配置し、熱圧着することによって実装される。

#### 【0270】

図31Bには、一つのチップ1608を実装した一つのCOFテープ1607の例を示したが特に限定されない。1つのCOFテープ1607の片面または両面に複数列のチップを実装することができるが、コスト削減のためには、実装するチップ数を少なくするため一列とすることが好ましく、さらに好ましくは1個とすることが望ましい。

#### 【0271】

##### <回路基板の構成例>

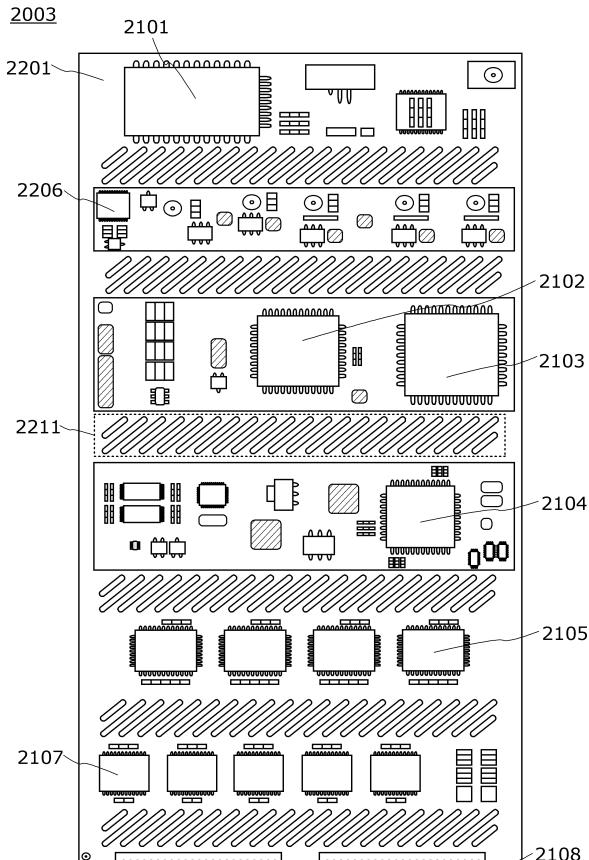

図32に、回路基板2003の外観図を示す。回路基板2003は、スリット2211を有するFPC2201上に、Bluetooth(登録商標。IEEE802.15.1に同じ。)規格の通信装置2101、マイコン2102、記憶装置2103、FPGA2104、DAコンバータ2105、充電制御IC2106、レベルシフタ2107を設けた構成を有する。また、回路基板2003は、入出力コネクタ2108を介して、本発明の一形態に係る表示装置と電気的に接続する。また、FPC2201にスリット2211を設けることにより、FPC2201を用いた回路基板2003の可撓性を高めている。

#### 【0272】

表示装置に可撓性を有する基板を用いることで、回路基板2003と共に表示装置も湾曲させることができる。よって、可撓性を有する基板を用いた表示装置と、回路基板2003とは、装着部位の形状に合わせて繰り返し変形することができるので、腕や足などの身体に装着可能な電子機器に利用するのに適している。

#### 【0273】

##### <情報処理装置の構成例>

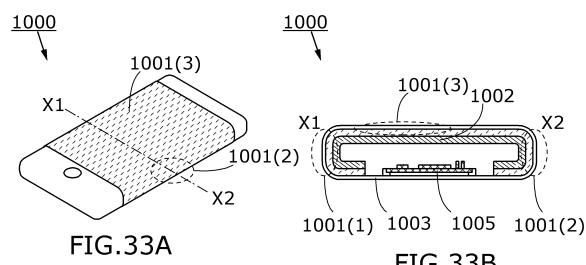

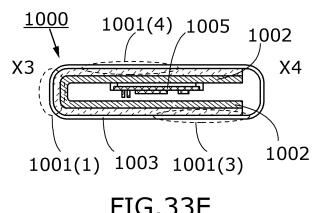

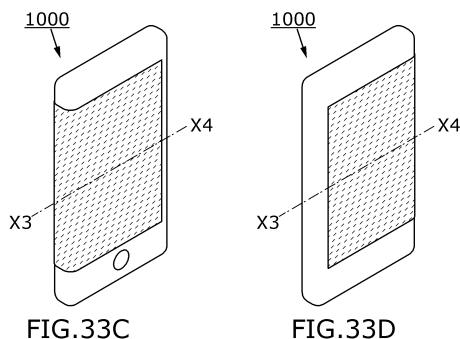

図33Aは情報処理装置1000の外観を説明する模式図であり、図33Bは、図33AのX1-X2線による断面の構造を説明する模式図である。また、図33Cおよび図33Dは、情報処理装置1000の外観を説明する模式図であり、図33Eは、図33Cおよび図33DのX3-X4線による断面の構造を説明する模式図である。図33Cは情報処理装置1000の正面を説明する模式図であり。図33Dは情報処理装置1000の背面を説明する模式図である。

#### 【0274】

図33C、図33Dに示すように、位置入力部1001または表示部1002は、情報処理装置1000の正面だけでなく、側面や背面にも設けられていてよい。また、位置入力部1001または表示部1002は、情報処理装置1000の上面に設けられていてよい。また、位置入力部1001または表示部1002は、情報処理装置1000の底面に設けられていてよい。

#### 【0275】

なお、筐体1003の表面には位置入力部1001のほか、ハードウェアボタンや外部接続端子等を有していてよい。

10

20

30

40

50

**【0276】**

このような構成とすることで、従来の情報処理装置のように筐体1003の正面に平行な面にのみ表示するのではなく、筐体1003の側面にも表示を行うことが可能となる。特に、筐体1003の2以上の側面に沿って表示領域を設けると、表示の多様性がより高まるため好ましい。

**【0277】**

情報処理装置の正面に沿って配置される表示領域と、側面に沿って配置された各表示領域は、それぞれ独立な表示領域として用いて異なる画像等を表示してもよいし、いずれか2つ以上の表示領域にわたって一つの画像等を表示してもよい。例えば、情報処理装置の正面に沿って配置された表示領域に表示する画像を、情報処理装置の側面に沿って設けられる表示領域などに連続して表示してもよい。10

**【0278】**

また、演算装置1005は、筐体1003の内部に設けられている。図33Bでは、演算装置1005が表示部1002と離隔した位置に設けられている。図33Eでは、演算装置1005が表示部1002と重なる位置に設けられている。

**【0279】**

位置入力部1001は、一例としては、第1の領域1001(1)と、第1の領域1001(1)に対向する第2の領域1001(2)と、第1の領域1001(1)および第2の領域1001(2)の間に第3の領域1001(3)と、が形成されるように折り曲げることができる可撓性を有する(図33B参照)。また、他の一例として、第1の領域1001(1)と、第3の領域1001(3)と、第3の領域1001(3)に対向する第4の領域1001(4)と、が形成されるように折り曲げができる可撓性を有する(図33E参照)。20

**【0280】**

また、他の一例として、第3の領域1001(3)と、第5の領域1001(5)と、第3の領域1001(3)に対向する第4の領域1001(4)と、が形成されるように折り曲げができる可撓性を有していても良い。

**【0281】**

なお、第1の領域1001(1)に対向する第2の領域1001(2)の配置は、第1の領域1001(1)に正対する配置に限られず、第1の領域1001(1)に傾きを持って向き合う配置も含むものとする。また、第3の領域1001(3)に対向する第4の領域1001(4)の配置は、第3の領域1001(3)に正対する配置に限られず、第3の領域1001(3)に傾きを持って向き合う配置も含むものとする。30

**【0282】**

表示部1002は、少なくとも第1の領域1001(1)、第2の領域1001(2)、第3の領域1001(3)、または第4の領域1001(4)の一部と重なるように配置される。

**【0283】**

情報処理装置1000は、近接または接触するものを検知する可撓性の位置入力部1001を含んで構成される。そして、位置入力部1001は、例えば、第1の領域1001(1)と、第1の領域に対向する第2の領域1001(2)と、第1の領域1001(1)および第2の領域1001(2)の間に表示部1002と重なる第3の領域1001(3)と、が形成されるように折り曲げができる。これにより、例えば掌もしくは手の指の何れかが、第1の領域1001(1)または第2の領域1001(2)などの何れかに近接したのかを知ることができる。その結果、操作性に優れたヒューマンインターフェイスを提供できる。または、操作性に優れた新規な情報処理装置を提供できる。40

**【0284】**

表示部1002に用いられる基板としては、可撓性を有する程度の厚さの樹脂が適用できる。樹脂としては、例えばポリエステル、ポリオレフィン、ポリアミド、ポリイミド、アラミド、エポキシ、ポリカーボネート若しくはアクリル樹脂等を挙げることができる。50

た、可撓性を有さないような通常の基板としては、ガラス基板、石英基板、半導体基板などを用いることが出来る。

【0285】

<電子機器の構成例>

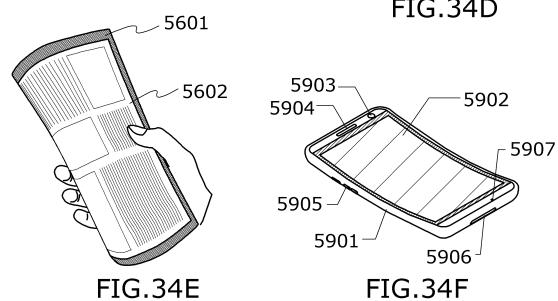

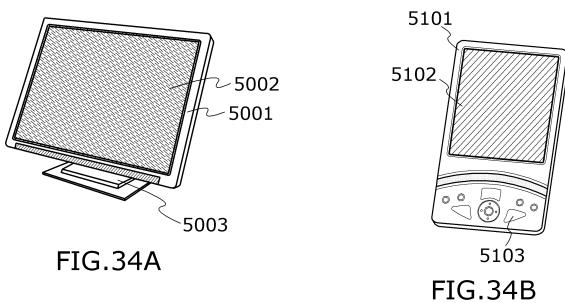

本発明の一態様に係る半導体装置は、表示装置、ノート型パーソナルコンピュータ、記録媒体を備えた画像再生装置（代表的にはDVD：Digital Versatile Disc等の記録媒体を再生し、その画像を表示しうるディスプレイを有する装置）に用いることができる。その他に、本発明の一態様に係る半導体装置を用いることができる電子機器として、携帯電話、携帯型ゲーム機、携帯情報端末、電子書籍、ビデオカメラ、デジタルスチルカメラなどのカメラ、ゴーグル型ディスプレイ（ヘッドマウントディスプレイ）、ナビゲーションシステム、音響再生装置（カーオーディオ、デジタルオーディオプレイヤー等）、複写機、ファクシミリ、プリンター、プリンター複合機、現金自動預け入れ払い機（ATM）、自動販売機などが挙げられる。これら電子機器の具体例を図34に示す。

【0286】

図34Aは表示装置であり、筐体5001、表示部5002、支持台5003等を有する。本発明の一態様に係る半導体装置は、表示部5002に用いることができる。なお、表示装置には、パーソナルコンピュータ用、TV放送受信用、広告表示用などの全ての情報表示用表示装置が含まれる。

【0287】

図34Bは携帯情報端末であり、筐体5101、表示部5102、操作キー5103等を有する。本発明の一態様に係る半導体装置は、表示部5102に用いることができる。

【0288】

図34Cは表示装置であり、曲面を有する筐体5701、表示部5702等を有する。本発明の一態様に係る半導体装置に可撓性を有する基板を用いることで、曲面を有する筐体5701に支持された表示部5702に、当該半導体装置を用いることができ、フレキシブルかつ軽くて使い勝手の良い表示装置を提供することができる。

【0289】

図34Dは携帯型ゲーム機であり、筐体5301、筐体5302、表示部5303、表示部5304、マイクロホン5305、スピーカー5306、操作キー5307、スタイルス5308等を有する。本発明の一態様に係る半導体装置は、表示部5303または表示部5304に用いることができる。表示部5303または表示部5304に本発明の一態様に係る半導体装置を用いることで、ユーザーの使用感に優れ、品質の低下が起こりにくい携帯型ゲーム機を提供することができる。なお、図34Dに示した携帯型ゲーム機は、2つの表示部5303と表示部5304とを有しているが、携帯型ゲーム機が有する表示部の数は、これに限定されない。

【0290】

図34Eは電子書籍であり、筐体5601、表示部5602等を有する。本発明の一態様に係る半導体装置は、表示部5602に用いることができる。そして、可撓性を有する基板を用いることで、半導体装置に可撓性を持たせることができるので、フレキシブルかつ軽くて使い勝手の良い電子書籍を提供することができる。

【0291】

図34Fは携帯電話であり、筐体5901に、表示部5902、マイク5907、スピーカー5904、カメラ5903、外部接続部5906、操作用のボタン5905が設かれている。表示部5902に、本発明の一態様に係る半導体装置を用いることできる。また、本発明の一態様に係る半導体装置を、可撓性を有する基板に形成した場合、図34Fに示すような曲面を有する表示部5902に当該半導体装置を適用することが可能である。

【0292】

（実施の形態5）

10

20

30

40

50

本実施の形態では、O Sトランジスタに用いられる酸化物半導体膜について説明する。

**【0293】**

酸化物半導体膜は、非単結晶酸化物半導体膜と単結晶酸化物半導体膜とに大別される。非単結晶酸化物半導体膜とは、CAAC-O S(C Axis Aligned Crystalline Oxide Semiconductor)膜、多結晶酸化物半導体膜、微結晶酸化物半導体膜、非晶質酸化物半導体膜などをいう。

**【0294】**

酸化物半導体膜は、単結晶構造の酸化物半導体(以下、単結晶酸化物半導体という。)、多結晶構造の酸化物半導体(以下、多結晶酸化物半導体という。)、微結晶構造の酸化物半導体(以下、微結晶酸化物半導体という。)、及び非晶質構造の酸化物半導体(以下、非晶質酸化物半導体という。)の一以上で構成されてもよい。また、酸化物半導体膜は、CAAC-O S膜で構成されていてもよい。また、酸化物半導体膜は、非晶質酸化物半導体及び結晶粒を有する酸化物半導体で構成されていてもよい。以下に、CAAC-O S膜及び微結晶酸化物半導体膜について説明する。

10

**【0295】**

<CAAC-O S>

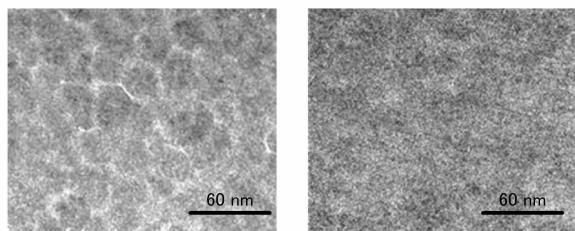

CAAC-O Sは、c軸配向した複数の結晶部を有する酸化物半導体の一つである。CAAC-O Sを、C ANC(C-Axis Aligned nanocrystals)を有する酸化物半導体と呼ぶこともできる。透過型電子顕微鏡(TEM: Transmission Electron Microscope)によってCAAC-O Sの明視野像と回折パターンとの複合解析像(高分解能TEM像ともいう。)を観察すると、複数の結晶部を確認することができる。一方、明確な結晶部同士の境界、即ち結晶粒界(グレインバウンダリーともいう。)を確認することができない。そのため、CAAC-O Sは、結晶粒界に起因する電子移動度の低下が起こりにくいといえる。

20

**【0296】**

試料面と概略平行な方向から観察したCAAC-O Sの断面の高分解能TEM像では、結晶部において、金属原子が層状に配列していることを確認できる。金属原子の各層の配列は、CAAC-O S膜が形成されている面(被形成面ともいう。)または上面の凹凸を反映した形状であり、CAAC-O Sの被形成面または上面と平行となる。

30

**【0297】**

一方、試料面と概略垂直な方向から観察したCAAC-O Sの高分解能TEM像では、結晶部において、金属原子が三角形状または六角形状に配列していることを確認できる。しかしながら、異なる結晶部間で、金属原子の配列に規則性は見られない。

**【0298】**

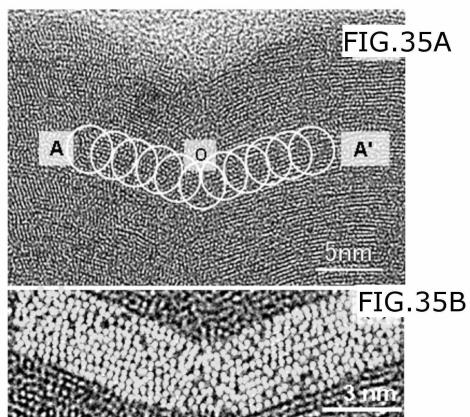

図35Aは、試料面と概略平行な方向から観察したCAAC-O Sの断面の高分解能TEM像である。また、図35Bは、図35Aをさらに拡大した高分解能TEM像であり、理解を容易にするために原子配列を強調表示している。

**【0299】**

図35Cは、図35AのA-O-A'間ににおいて、丸で囲んだ領域(直径約4nm)の局所的なフーリエ変換像である。図35Cより、各領域においてc軸配向性が確認できる。また、A-O間とO-A'間とでは、c軸の向きが異なるため、異なるグレインであることが示唆される。また、A-O間では、c軸の角度が14.3°、16.6°、26.4°のように少しづつ連続的に変化していることがわかる。同様に、O-A'間では、c軸の角度が-18.3°、-17.6°、-15.9°と少しづつ連続的に変化していることがわかる。

40

**【0300】**

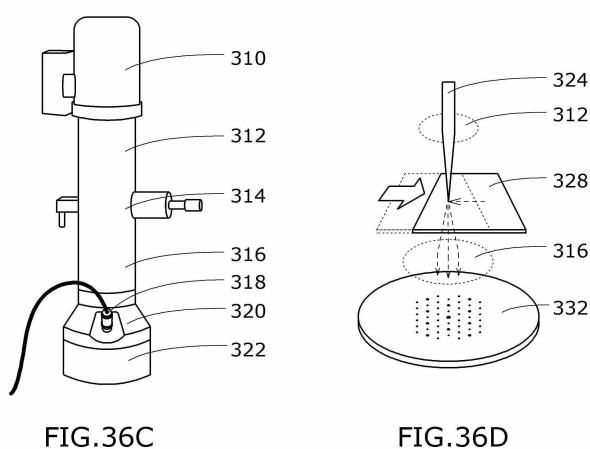

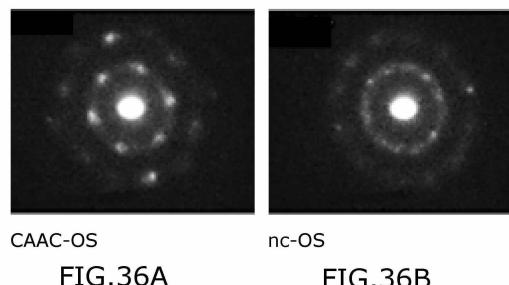

なお、CAAC-O S膜に対し、電子回折を行うと、配向性を示すスポット(輝点)が観測される。例えば、CAAC-O S膜の上面に対し、例えば1nm以上30nm以下の電子線を用いる電子回折(ナノビーム電子回折ともいう。)を行うと、スポットが観測される(図36A参照。)。

50

**【0301】**

高分解能TEM像から、CAC-O<sub>S</sub>膜の結晶部は配向性を有していることがわかる。

**【0302】**

なお、CAC-O<sub>S</sub>に含まれるほとんどの結晶部は、一边が100nm未満の立方体内に収まる大きさである。従って、CAC-O<sub>S</sub>に含まれる結晶部は、一边が10nm未満、5nm未満または3nm未満の立方体内に収まる大きさの場合も含まれる。ただし、CAC-O<sub>S</sub>に含まれる複数の結晶部が連結することで、一つの大きな結晶領域を形成する場合がある。例えば、試料面と概略垂直な方向から観察したCAC-O<sub>S</sub>の高分解能TEM像において、2500nm<sup>2</sup>以上、5μm<sup>2</sup>以上または1000μm<sup>2</sup>以上となる結晶領域が観察される場合がある。10

**【0303】**

CAC-O<sub>S</sub>に対し、X線回折(XRD:X-Ray Diffraction)装置を用いて構造解析を行うと、例えばInGaZnO<sub>4</sub>の結晶を有するCAC-O<sub>S</sub>膜のout-of-plane法による解析では、回折角(2θ)が31°近傍にピークが現れる場合がある。このピークは、InGaZnO<sub>4</sub>の結晶の(009)面に帰属されることから、CAC-O<sub>S</sub>膜の結晶がc軸配向性を有し、c軸が被形成面または上面に概略垂直な方向を向いていることが確認できる。

**【0304】**

一方、CAC-O<sub>S</sub>に対し、c軸に概略垂直な方向からX線を入射させるin-plane法による構造解析を行うと、2θが56°近傍にピークが現れる場合がある。このピークは、InGaZnO<sub>4</sub>の結晶の(110)面に帰属される。InGaZnO<sub>4</sub>の単結晶酸化物半導体膜であれば、2θを56°近傍に固定し、試料面の法線ベクトルを軸(c軸)として試料を回転させながら分析(スキャン)を行うと、(110)面と等価な結晶面に帰属されるピークが6本観察される。これに対し、CAC-O<sub>S</sub>膜の場合は、2θを56°近傍に固定してスキャンした場合でも、明瞭なピークが現れない。20

**【0305】**

以上のことから、CAC-O<sub>S</sub>膜では、異なる結晶部間ではa軸およびb軸の配向は不規則であるが、c軸配向性を有し、かつc軸が被形成面または上面の法線ベクトルに平行な方向を向いていることがわかる。従って、断面の高分解能TEM像で確認された層状に配列した金属原子の各層は、結晶のab面に平行な面である。30

**【0306】**

なお、結晶部は、CAC-O<sub>S</sub>膜を成膜した際、または加熱処理などの結晶化処理を行った際に形成される。上述したように、結晶のc軸は、CAC-O<sub>S</sub>膜の被形成面または上面の法線ベクトルに平行な方向に配向する。従って、例えば、CAC-O<sub>S</sub>膜の形状をエッティングなどによって変化させた場合、結晶のc軸がCAC-O<sub>S</sub>膜の被形成面または上面の法線ベクトルと平行にならないこともある。

**【0307】**

また、CAC-O<sub>S</sub>膜中において、c軸配向した結晶部の分布が均一でなくてもよい。例えば、CAC-O<sub>S</sub>膜の結晶部が、CAC-O<sub>S</sub>膜の上面近傍からの結晶成長によって形成される場合、上面近傍の領域は、被形成面近傍の領域よりもc軸配向した結晶部の割合が高くなることがある。また、不純物の添加されたCAC-O<sub>S</sub>膜は、不純物が添加された領域が変質し、部分的にc軸配向した結晶部の割合の異なる領域が形成されることもある。40

**【0308】**

なお、CAC-O<sub>S</sub>のout-of-plane法による構造解析では、2θが31°近傍のピークの他に、2θが36°近傍にもピークが現れる場合がある。2θが36°近傍のピークは、CAC-O<sub>S</sub>膜中の一部に、c軸配向性を有さない結晶が含まれることを示している。より好ましいCAC-O<sub>S</sub>は、out-of-plane法による構造解析では、2θが31°近傍にピークを示し、2θが36°近傍にピークを示さない。

**【0309】**

10

20

30

40

50

C A A C - O S 膜は、不純物濃度の低い酸化物半導体膜である。不純物は、水素、炭素、シリコン、遷移金属元素などの酸化物半導体膜の主成分以外の元素である。特に、シリコンなどの、酸化物半導体膜を構成する金属元素よりも酸素との結合力の強い元素は、酸化物半導体膜から酸素を奪うことで酸化物半導体膜の原子配列を乱し、結晶性を低下させる要因となる。また、鉄やニッケルなどの重金属、アルゴン、二酸化炭素などは、原子半径（または分子半径）が大きいため、酸化物半導体膜内部に含まれると、酸化物半導体膜の原子配列を乱し、結晶性を低下させる要因となる。なお、酸化物半導体膜に含まれる不純物は、キャリアトラップやキャリア発生源となる場合がある。

#### 【 0 3 1 0 】

また、C A A C - O S 膜は、欠陥準位密度の低い酸化物半導体膜である。例えば、酸化物半導体膜中の酸素欠損は、キャリアトラップとなることや、水素を捕獲することによってキャリア発生源となることがある。

10

#### 【 0 3 1 1 】

不純物濃度が低く、欠陥準位密度が低い（酸素欠損の少ない）ことを、高純度真性または実質的に高純度真性とよぶ。高純度真性または実質的に高純度真性である酸化物半導体膜は、キャリア発生源が少ないとため、キャリア密度を低くすることができる。従って、当該酸化物半導体膜を用いたトランジスタは、しきい値電圧がマイナスとなる電気特性（ノーマリーオンともいう。）になることが少ない。また、高純度真性または実質的に高純度真性である酸化物半導体膜は、キャリアトラップが少ない。そのため、当該酸化物半導体膜を用いたトランジスタは、電気特性の変動が小さく、信頼性の高いトランジスタとなる。なお、酸化物半導体膜のキャリアトラップに捕獲された電荷は、放出するまでに要する時間が長く、あたかも固定電荷のように振る舞うことがある。そのため、不純物濃度が高く、欠陥準位密度が高い酸化物半導体膜を用いたトランジスタは、電気特性が不安定となる場合がある。

20

#### 【 0 3 1 2 】

また、C A A C - O S 膜を用いたトランジスタは、可視光や紫外光の照射による電気特性の変動が小さい。

#### 【 0 3 1 3 】

##### < 微結晶酸化物半導体膜 >

微結晶酸化物半導体は、高分解能TEM像において、結晶部を確認することのできる領域と、明確に結晶部を確認することができない領域とを有する。微結晶酸化物半導体膜に含まれる結晶部は、1 nm以上100 nm以下、または1 nm以上10 nm以下の大きさであることが多い。特に、1 nm以上10 nm以下、または1 nm以上3 nm以下の微結晶であるナノ結晶（n c : n a n o c r y s t a l ）を有する酸化物半導体膜を、n c - O S ( n a n o c r y s t a l l i n e O x i d e S e m i c o n d u c t o r ) 膜とよぶ。n c - O S は、例えば、高分解能TEM像では、結晶粒界を明確に確認できない場合がある。

30

#### 【 0 3 1 4 】