**Erfolgspatent für die Schweiz und Liechtenstein**

Schweizerisch-liechtensteinischer Patentschutzvertrag vom 22. Dezember 1978

**⑪ CH 658 530 A5**

|                                |               |              |

|--------------------------------|---------------|--------------|

| <b>⑯ Int. Cl.<sup>4</sup>:</b> | <b>G 06 F</b> | <b>13/16</b> |

|                                | <b>G 06 F</b> | <b>11/30</b> |

|                                | <b>G 07 F</b> | <b>9/00</b>  |

|                                | <b>G 05 B</b> | <b>23/02</b> |

## **⑫ PATENTSCHRIFT A5**

**⑬ Gesuchsnummer:** 302/83

**⑭ Inhaber:**

Scheidt & Bachmann GmbH, Mönchengladbach 4

(DE)

**⑮ Anmeldungsdatum:** 19.01.1983

**⑯ Erfinder:**

Miller, Gert, Mönchengladbach 1 (DE)

Busch, Erwin, Mönchengladbach 1 (DE)

Wortelkamp, Ulrich, Mönchengladbach 2 (DE)

**⑰ Patent erteilt:** 14.11.1986

**⑲ Vertreter:**

Bovard AG, Bern 25

### **⑳ Verfahren zur Uebertragung und Speicherung von anlagenbezogenen Daten.**

**㉑ Das Verfahren** betrifft die Übertragung und Speicherung von anlagenbezogenen Daten, wie beispielsweise Bilanzdaten und Verkaufsdaten, aus einem Mikrocomputersystem (7), welches zur Steuerung von Anlagen dient, auf einen auf einer Leiterplatte befindlichen externen Basisspeicher (1). Die zu steuernden Anlagen sind beispielsweise Parkhäuser, Tankstellen oder andere Warenverkaufs- und Dienstleistungs-Automaten. Um falsche Dateneingaben bzw. -ausgaben infolge von Störimpulsen zu vermeiden und Manipulationen zu verhindern, wird der Schreib-Lese-Speicher (9) des Basisspeichers vor der Übertragung der Daten über ein I/O-Port (2) des Mikrocomputersystems (7) zum Teil adressiert. Die Restadressierung wird durch ein auf dem Basisspeicher befindliches, ebenfalls über den I/O-Port (2) adressierbares Zeitglied (5) vorgenommen. Die Aktivzeit des Zeitgliedes wird durch Verknüpfung in einer Torschaltung (6) mit der Adressleitung (3) überprüft.

## PATENTANSPRÜCHE

1. Verfahren zur Übertragung und Speicherung von anlagenbezogenen Daten, wie beispielsweise Bilanzdaten, Verkaufsdaten, aus einem Mikrocomputersystem mit einem Mikroprozessor, Festprogrammspeicher und Schreib-Lese-Speicher, welches Mikrocomputersystem zur Steuerung von Anlagen, wie beispielsweise Parkhäusern, Tankstellen, Warenverkaufs- und Dienstleistungs-Automaten, dient, auf einen auf einer Leiterplatte befindlichen externen, als entweder nicht flüchtigen Schreib-Lese-Speicher oder gegen Spannungsausfall durch eine Batterie oder einen Akkumulator geschützten flüchtigen Schreib-Lese-Speicher ausgebildeten Basisspeicher, dadurch gekennzeichnet, dass der Schreib-Lese-Speicher (9) des Basisspeichers (1) vor der Übertragung der Daten über ein I/O-Port (2) des Mikrocomputersystems (7) zum Teil adressiert, die Restadressierung durch ein auf dem Basisspeicher (1) befindliches, ebenfalls über den I/O-Port (2) adressierbares Zeitglied (5) vorgenommen und die Aktivzeit des Zeitgliedes (5) durch Verknüpfung in einer Torschaltung mit der Adressleitung (3) überprüft wird.

2. Verfahren nach Anspruch 1, dadurch gekennzeichnet, dass das Zeitglied (5) retriggerbar ist.

3. Verfahren nach Anspruch 2, dadurch gekennzeichnet, dass das Zeitglied (5) durch eine Batterie bzw. einen Akkumulator (8) gegen Spannungsausfall geschützt ist.

4. Verfahren nach Anspruch 3, dadurch gekennzeichnet, dass eine bestimmte Codenummer bei jeder Datenübertragung zwischen Mikrocomputersystem (7) und Basisspeicher (1) verglichen wird.

Die Erfindung betrifft ein Verfahren zur Übertragung und Speicherung von anlagenbezogenen Daten, wie beispielsweise Bilanzdaten und Verkaufsdaten, aus einem Mikrocomputersystem mit einem Mikroprozessor, Festprogrammspeicher und Schreib-Lese-Speicher, welches Mikrocomputersystem zur Steuerung von Anlagen, wie beispielsweise Parkhäusern, Tankstellen, Warenverkaufs- und Dienstleistungs-Automaten, dient, auf einen auf einer Leiterplatte befindlichen externen, als entweder nicht flüchtigen Schreib-Lese-Speicher oder gegen Spannungsausfall durch eine Batterie oder einen Akkumulator geschützten flüchtigen Schreib-Lese-Speicher ausgebildeten Basisspeicher.

Aus einem Mikroprozessor (CPU), einem Festprogrammspeicher (ROM bzw. PROM bzw. EPROM) sowie einem Arbeitsspeicher (RAM) bestehende Mikrocomputersysteme sind in verschiedenen Ausführungen bekannt. Sie dienen beispielsweise der Steuerung von Anlagen, wie beispielsweise Parkhäusern, Tankstellen, Warenverkaufs- und Dienstleistungs-Automaten, und sind demgemäß mit entsprechenden Peripherie-Geräten versehen. Diese umfassen auch Bedienungspulte, Datensichtgeräte und Drucker, um die Bedienung des Mikrocomputersystems zu vereinfachen und die in den Speichern vorhandenen Werte jederzeit abrufen zu können.

Da die Mikrocomputersysteme in den meisten Fällen mit einem Schreib-Lese-Speicher versehen sind, der wichtige Systemdaten zur Steuerung der jeweiligen Anlage enthält und dem Betriebsdaten der Anlage, insbesondere Summenwerte aufgegeben werden, die auch bei einem Spannungsausfall gespeichert bleiben müssen, sind diese als Basisspeicher ausgebildeten Schreib-Lese-Speicher gegen Spannungsausfall durch eine Batterie oder einen Akkumulator geschützt.

Der Nachteil der bekannten Mikrocomputersysteme der voranstehend beschriebenen Art besteht darin, dass dem Basisspeicher aufgrund von Störimpulsen falsche Informationen aufgegeben werden können. Außerdem besteht bei den bekannten Systemen die Gefahr von Manipulationen.

Der Erfindung liegt demzufolge die Aufgabe zugrunde,

ein Verfahren der eingangs beschriebenen Art gegen falsche Dateneingaben in den Datenspeicher bzw. falsche Datenausgaben aus dem Basisspeicher infolge von Störimpulsen im System zu schützen und Manipulationen zu verhindern.

- 5 Die Lösung dieser Aufgabenstellung durch das erfindungsgemäße Verfahren ist dadurch gekennzeichnet, dass der Schreib-Lese-Speicher des Basisspeichers vor der Übertragung der Daten über ein I/O-Port des Mikrocomputersystems zum Teil adressiert, die Restadressierung durch ein auf

- 10 dem Basisspeicher befindliches, ebenfalls über den I/O-Port adressierbares Zeitglied vorgenommen und die Aktivzeit des Zeitgliedes durch Verknüpfung in einer Torschaltung mit der Adressleitung überprüft wird.

Mit diesem erfindungsgemäßen Vorschlag wird erreicht,

- 15 dass Daten zwischen dem Basisspeicher und dem Mikrocomputersystem nur dann übertragen werden können, wenn das Zeitglied aktiv ist, d.h. innerhalb einer bestimmten Zeitspanne. Die in den Basisspeicher zu überführenden oder aus dem Basisspeicher herauszuholenden Daten werden hierbei

- 20 auf ihre Echtheit überprüft, vorzugsweise durch einen CRC-Check. Das Zeitglied wird nur aktiv, wenn die richtige Adresse in den Adressenleitungen ansteht. Durch das Zeitglied möglicherweise auftretende Fehler (z.B. Aktivierung zur Unzeit) haben dadurch keine Auswirkung, dass zusätzlich

- 25 die richtige Adresse mit dem Zeitglied durch eine Torschaltung verknüpft ist.

Um die Aktivierungszeit des Zeitgliedes vergrößern zu können, kann das Zeitglied gemäß einem weiteren Merkmal der Erfindung retriggerbar sein.

- 30 In an sich bekannter Weise kann das Zeitglied durch eine Batterie bzw. einen Akkumulator gegen Spannungsausfall geschützt sein.

Schliesslich ist es möglich, dass eine bestimmte Codenummer bei jeder Datenübertragung zwischen Mikrocomputersystem und Basisspeicher verglichen wird, wodurch Manipulationen durch Austausch des Basisspeichers und/oder des Mikrocomputersystems ausgeschlossen werden.

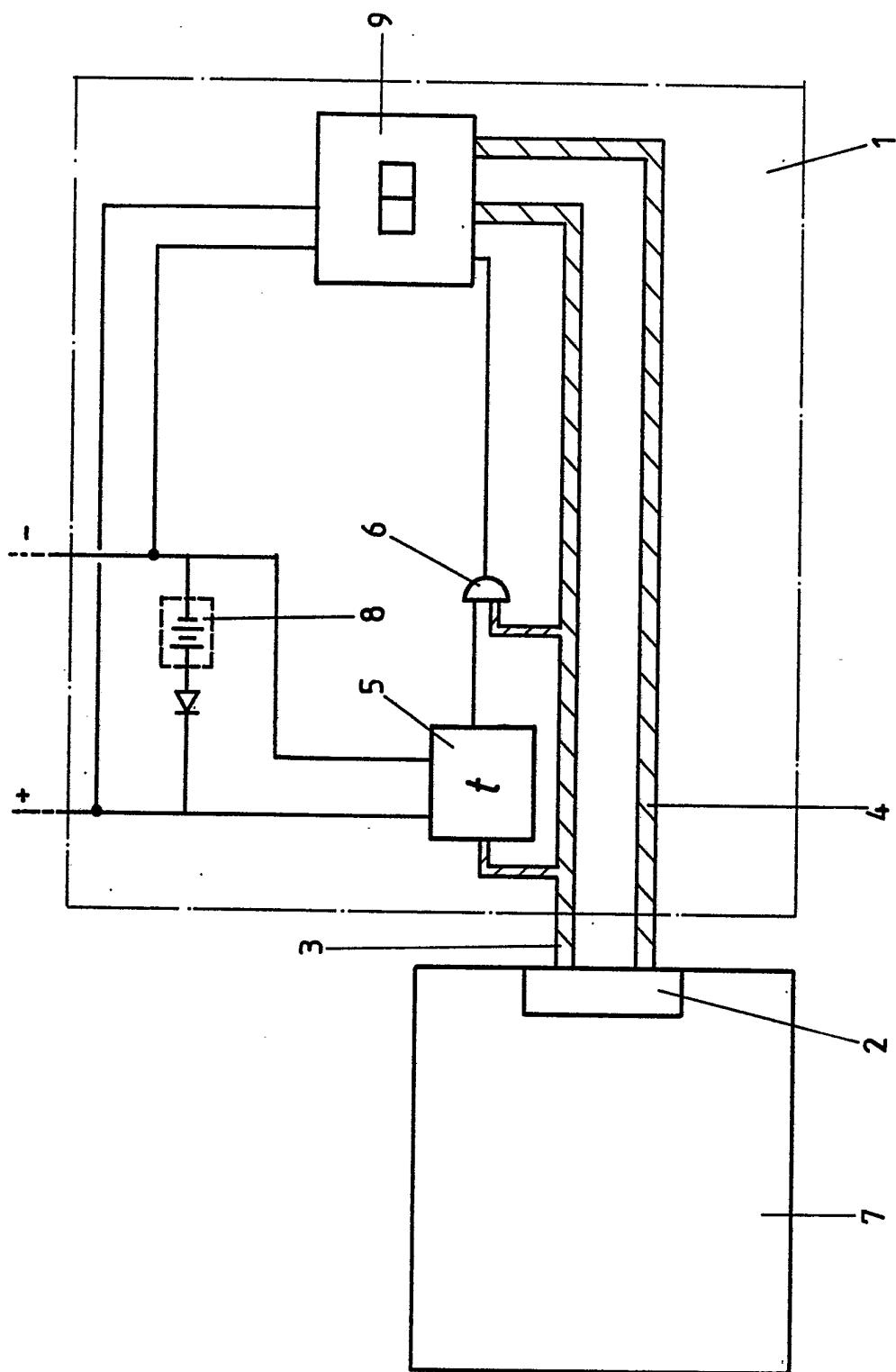

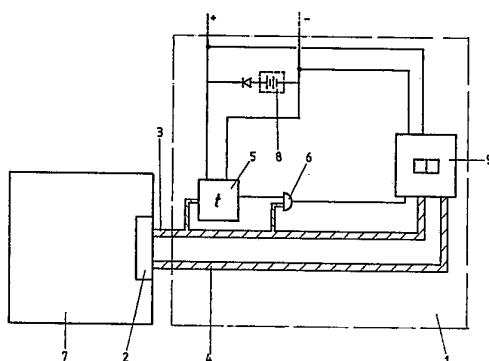

- 35 Auf der Zeichnung ist schematisch ein Ausführungsbeispiel zur Durchführung des erfindungsgemäßen Verfahrens dargestellt.

Zwischen einem Basisspeicher 1 und einem I/O-Port 2 sind Adressleitungen 3 zum Adressieren des Basisspeichers 1 und Datenleitungen 4 zum Datentransfer zwischen dem extern angeordneten Basispeicher 1 und einem Mikrocomputersystem 7 angeordnet. Der Basispeicher 1 besteht in der Hauptsache aus einem Zeitglied 5, einer Torschaltung 6, einem Schreib-Lese-Speicher 9 und einer Batterie bzw. einem Akkumulator 8 zum Schutz der Daten im Schreib-Lese-Speicher 9 bei Spannungsausfall.

- 40 Das Zeitglied 5 ist zwischen dem I/O-Port 2 und dem Schreib-Lese-Speicher 9 in mindestens eine Adressleitung 3 geschaltet. Dies bedeutet, dass das Zeitglied 5 durch Anlegen einer bestimmten Adresse gestartet wird. Der durch das Zeitglied 5 erzeugte Impuls mit einer festgelegten Impulsbreite gibt nach Überprüfung der richtigen Adresse durch die nachgeschaltete Torschaltung 6 und weiteren direkt zum Schreib-Lese-Speicher 9 führenden Adressleitungen 3 diesen zwecks Datenaustausch zwischen Basispeicher 1 und Mikrocomputersystem 7 für die Zeit des Impulses frei. Durch erneutes Anlegen der Adresse ist das Zeitglied 5 retriggerbar, d.h. die Impulsbreite wird erhöht und damit ein längerer Zeitraum für den Datenaustausch erreicht.

Die Batterie bzw. der dargestellte Akkumulator 8 dient bei Verwendung von flüchtigen Schreib-Lese-Speichern 9 (RAM) zur Datensicherung und verhindert gleichzeitig bei Spannungswiederkehr ein mögliches Starten des Zeitgliedes 5 zur Unzeit durch Störimpulse.