(19) 日本国特許庁(JP)

## (12) 公開特許公報(A)

(11) 特許出願公開番号

特開2009-204393

(P2009-204393A)

(43) 公開日 平成21年9月10日(2009.9.10)

(51) Int.Cl.

**G01R 1/073** (2006.01)

**G01R 31/26** (2006.01)

**H01L 21/66** (2006.01)

F 1

G01R 1/073

G01R 31/26

H01L 21/66

E

J

B

テーマコード(参考)

2GO03

2GO11

4M106

審査請求 未請求 請求項の数 23 O L (全 58 頁)

(21) 出願番号

(22) 出願日

特願2008-45809 (P2008-45809)

平成20年2月27日 (2008.2.27)

(71) 出願人 503121103

株式会社ルネサステクノロジ

東京都千代田区大手町二丁目6番2号

(74) 代理人 100080001

弁理士 筒井 大和

(72) 発明者 春日部 進

神奈川県横浜市戸塚区吉田町292番地

株式会社日立製作所生産技術研究所内

(72) 発明者 成塚 康則

神奈川県横浜市戸塚区吉田町292番地

株式会社日立製作所生産技術研究所内

F ターム(参考) 2G003 AA10 AC01 AE03 AG04 AG12

AG20 AH04 AH07

2G011 AA09 AA15 AB01 AB06 AB08

AC14 AC21 AE03 AF07

最終頁に続く

(54) 【発明の名称】プローブカード、プローブカードの製造方法、半導体検査装置および半導体装置の製造方法

## (57) 【要約】

【課題】狭ピッチで電極が配置された半導体素子の電気信号検査を行うための、低荷重で、接触特性が安定し、接触端子先端の位置精度が良好な検査装置を提供する。

【解決手段】シリコン基板を型材とし、そのシリコン基板上にフォトリソグラフィ技術を用いて金属膜およびポリイミド膜等の薄膜を逐次積層することで、片持ち梁構造で先端に角錐形状あるいは角錐台形状の接触端子4を備えたプローブシート5を形成し、さらにそのプローブシート5に固着基板6を固着し、その後、形成したプローブシート5をシリコン基板に逐次積層形成して、基板を固着し、シリコン基板および所定のポリイミド膜をエッチング除去することで、片持ち梁構造の接触端子4群を一括形成する。

【選択図】図2

**【特許請求の範囲】****【請求項 1】**

被検査対象に設けられた電極と接触する複数の接触端子と、

前記複数の接触端子の各々から電気的に引き出された配線と、

前記配線と電気的に接続され、かつ多層配線基板の電極に接続される複数の周辺電極と

を備えたプローブシートを有し、

前記プローブシートにおいて、前記複数の接触端子が形成された第1の面とは反対側の

第2の面にて、前記複数の接触端子が形成された領域に固着基板が固着され、

前記固着基板を傾動可能になるようにした手段が設けられ、

前記複数の接触端子の各々は、前記プローブシートと離間して延在し、前記配線と電気

的に接続された梁の一端に形成され、

前記梁の他端は前記プローブシートに固定されていることを特徴とするプローブカード

。

**【請求項 2】**

被検査対象に設けられた電極と接触する複数の接触端子と、

前記複数の接触端子の各々から電気的に引き出された配線と、

前記配線と電気的に接続され、かつ多層配線基板の電極に接続される複数の周辺電極と

、

前記複数の接触端子が形成された第1の面とは反対側の第2の面にて、前記複数の接触

端子が形成された領域に形成された金属シートとを備えたプローブシートを有し、

前記金属シートに固着基板が固着され、

前記固着基板を傾動可能になるようにした手段が設けられ、

前記複数の接触端子の各々は、前記プローブシートと離間して延在し、前記配線と電気

的に接続された梁の一端に形成され、

前記梁の他端は前記プローブシートに固定されていることを特徴とするプローブカード

。

**【請求項 3】**

請求項1または2記載のプローブカードにおいて、

前記多層配線基板は、前記被検査対象の電気的特性を検査するテスタと電気的に接続さ

れることを特徴とするプローブカード。

**【請求項 4】**

請求項1～3のいずれか1項に記載のプローブカードにおいて、

前記固着基板を傾動可能になるようにした前記手段は、複数のばね性を有したガイドピ

ンであることを特徴とするプローブカード。

**【請求項 5】**

請求項4記載のプローブカードにおいて、

前記固着基板を傾動可能になるようにした前記手段は、さらに複数のばね性のないガイ

ドピンを用いることを特徴とするプローブカード。

**【請求項 6】**

請求項1～5のいずれか1項に記載のプローブカードにおいて、

前記固着基板を傾動可能になるようにした前記手段は、1つ以上の板ばねであることを

特徴とするプローブカード。

**【請求項 7】**

被検査対象に設けられた電極と接触する複数の接触端子と、

前記複数の接触端子の各々から電気的に引き出された配線と、

前記配線と電気的に接続され、かつ多層配線基板の電極に接続される複数の周辺電極と

を備えたプローブシートを有し、

前記プローブシートにおいて、前記複数の接触端子が形成された第1の面とは反対側の

第2の面にて、前記複数の接触端子が形成された領域に固着基板が固着され、さらに前記

プローブシートが前記固着基板を包み込むように前記固着基板に固着されることで形成さ

。

10

20

30

40

50

れた1つ以上のブロックを備え、

前記1つ以上のブロックの各々の前記プローブシートの前記複数の周辺電極と、前記多層配線基板の前記電極とが接触し、

前記複数の接触端子の各々は、前記プローブシートと離間して延在し、前記配線と電気的に接続された梁の一端に形成され、

前記梁の他端は前記プローブシートに固定されていることを特徴とするプローブカード。

#### 【請求項8】

請求項1～7のいずれか1項に記載のプローブカードにおいて、

前記接触端子は、角錐形状または角錐台形状であることを特徴とするプローブカード。 10

#### 【請求項9】

請求項8記載のプローブカードにおいて、

前記接触端子は、結晶性を有する基板に異方性エッチングを施すことで形成した穴を型材としためっきにより形成されたものであることを特徴とするプローブカード。

#### 【請求項10】

請求項9記載のプローブカードにおいて、

前記結晶性を有する基板は、シリコンであることを特徴とするプローブカード。

#### 【請求項11】

被検査対象に設けられた電極と接触する複数の接触端子と、

前記複数の接触端子の各々から電気的に引き出された配線と、 20

前記配線と電気的に接続され、かつ多層配線基板の電極に接続される複数の第1および第2の周辺電極とを備えたプローブシートを有し、

前記プローブシートにおいて、前記複数の接触端子が形成された第1の面とは反対側の第2の面にて、前記複数の接触端子が形成された領域に固着基板が固着され、

前記固着基板を傾動可能になるようにした手段が設けられ、

前記複数の接触端子の各々は、前記プローブシートと離間して延在し、前記配線と電気的に接続された梁の一端に形成され、

前記梁の他端は前記プローブシートに固定され、

前記複数の第1の周辺電極の各々は、前記プローブシートにおいて前記の接触端子と同じ第1の面に形成され、 30

前記複数の第2の周辺電極の各々は、前記プローブシートにおいて前記の接触端子とは反対側の第2の面に形成されていることを特徴とするプローブカード。

#### 【請求項12】

請求項11に記載のプローブカードにおいて、

前記プローブシートにおける前記第1および第2の周辺電極の形成ピッチは、前記複数の接触端子の形成ピッチよりも広いことを特徴とするプローブカード。

#### 【請求項13】

被検査対象に設けられた電極と接触する複数の接触端子と、

前記複数の接触端子の各々から電気的に引き出された配線と、

前記配線と電気的に接続され、かつ多層配線基板の電極に接続される複数の周辺電極とを備えたプローブシートを有し、 40

前記プローブシートにおいて、前記複数の接触端子が形成された第1の面とは反対側の第2の面にて、前記複数の接触端子が形成された領域に固着基板が固着され、

前記固着基板を傾動可能になるようにした手段が設けられ、

前記複数の接触端子の各々は、前記プローブシートと離間して延在し、前記配線と電気的に接続された梁の一端に形成され、

前記梁の他端は前記プローブシートに固定されたプローブカードの製造方法であって、

前記プローブシートを形成する工程は、

(a) 結晶性を有する基板に異方性エッチングを施すことで形成した穴を型材としためっきにより、前記複数の接触端子を形成する工程、 50

- (b) 前記基板上に前記複数の接触端子の各々と電気的に接続する前記梁、前記配線および絶縁層を逐次積層する工程、

(c) 前記複数の接触端子および前記梁と同じ配線層における前記絶縁層を除去することで、前記梁を前記プローブシートから離間させる工程、

を含むことを特徴とするプローブカードの製造方法。

**【請求項 1 4】**

被検査対象を載せる試料台と、

前記被検査対象に設けられた電極と接触する複数の接触端子を有し、かつ前記被検査対象の電気的特性を検査するテスタと電気的に接続されるプローブカードとを有する半導体検査装置であって、

前記プローブカードは、

前記複数の接触端子と、

前記複数の接触端子の各々から電気的に引き出された配線と、

前記配線と電気的に接続され、かつ多層配線基板の電極に接続される複数の周辺電極とを備えたプローブシートを有し、

前記プローブシートにおいて、前記複数の接触端子が形成された第1の面とは反対側の第2の面にて、前記複数の接触端子が形成された領域に固着基板が固着され、

前記固着基板を傾動可能になるようにした手段が設けられ、

前記複数の接触端子の各々は、前記プローブシートと離間して延在し、前記配線と電気的に接続された梁の一端に形成され、

前記梁の他端は前記プローブシートに固定されていることを特徴とする半導体検査装置。

。

**【請求項 1 5】**

被検査対象を載せる試料台と、

前記被検査対象に設けられた電極と接触する複数の接触端子を有し、かつ前記被検査対象の電気的特性を検査するテスタと電気的に接続されるプローブカードとを有する半導体検査装置であって、

前記プローブカードは、

前記複数の接触端子と、

前記複数の接触端子の各々から電気的に引き出された配線と、

前記配線と電気的に接続され、かつ多層配線基板の電極に接続される複数の周辺電極と、

前記複数の接触端子が形成された第1の面とは反対側の第2の面にて、前記複数の接触端子が形成された領域に形成された金属シートとを備えたプローブシートを有し、

前記金属シートに固着基板が固着され、

前記固着基板を傾動可能になるようにした手段が設けられ、

前記複数の接触端子の各々は、前記プローブシートと離間して延在し、前記配線と電気的に接続された梁の一端に形成され、

前記梁の他端は前記プローブシートに固定されていることを特徴とする半導体検査装置。

。

**【請求項 1 6】**

被検査対象を載せる試料台と、

前記被検査対象に設けられた電極と接触する複数の接触端子を有し、かつ前記被検査対象の電気的特性を検査するテスタと電気的に接続されるプローブカードとを有する半導体検査装置であって、

前記プローブカードは、

前記複数の接触端子と、

前記複数の接触端子の各々から電気的に引き出された配線と、

前記配線と電気的に接続され、かつ多層配線基板の電極に接続される複数の周辺電極とを備えたプローブシートを有し、

10

20

30

40

50

前記プローブシートにおいて、前記複数の接触端子が形成された第1の面とは反対側の第2の面にて、前記複数の接触端子が形成された領域に固着基板が固着され、さらに前記プローブシートが前記固着基板を包み込むように前記固着基板に固着されることで形成された1つ以上のブロックを備え、

前記1つ以上のブロックの各々の前記プローブシートの前記複数の周辺電極と、前記多層配線基板の前記電極とが接触し、

前記複数の接触端子の各々は、前記プローブシートと離間して延在し、前記配線と電気的に接続された梁の一端に形成され、

前記梁の他端は前記プローブシートに固定されていることを特徴とする半導体検査装置。

10

#### 【請求項17】

被検査対象を載せる試料台と、

前記被検査対象に設けられた電極と接触する複数の接触端子を有し、かつ前記被検査対象の電気的特性を検査するテスタと電気的に接続されるプローブカードとを有する半導体検査装置であって、

前記プローブカードは、

前記複数の接触端子と、

前記複数の接触端子の各々から電気的に引き出された配線と、

前記配線と電気的に接続され、かつ多層配線基板の電極に接続される複数の第1および第2の周辺電極とを備えたプローブシートを有し、

20

前記プローブシートにおいて、前記複数の接触端子が形成された第1の面とは反対側の第2の面にて、前記複数の接触端子が形成された領域に固着基板が固着され、

前記固着基板を傾動可能になるようにした手段が設けられ、

前記複数の接触端子の各々は、前記プローブシートと離間して延在し、前記配線と電気的に接続された梁の一端に形成され、

前記梁の他端は前記プローブシートに固定され、

前記複数の第1の周辺電極の各々は、前記プローブシートにおいて前記の接触端子と同じ第1の面に形成され、

前記複数の第2の周辺電極の各々は、前記プローブシートにおいて前記の接触端子とは反対側の第2の面に形成されていることを特徴とする半導体検査装置。

30

#### 【請求項18】

請求項14～17のいずれか1項に記載の半導体検査装置において、

前記プローブシートは、

(a) 結晶性を有する基板に異方性エッチングを施すことで形成した穴を型材としためっきにより、前記複数の接触端子を形成する工程、

(b) 前記基板上に前記複数の接触端子の各々と電気的に接続する前記梁、前記配線および絶縁層を逐次積層する工程、

(c) 前記複数の接触端子および前記梁と同じ配線層における前記絶縁層を除去することで、前記梁を前記プローブシートから離間させる工程、

を含む工程により形成されていることを特徴とする半導体検査装置。

40

#### 【請求項19】

半導体ウエハに回路および前記回路と電気的に接続する電極を作り込み、複数の半導体素子を形成する工程と、

前記複数の半導体素子に設けられた前記電極と接触する複数の接触端子を有し、かつ前記複数の半導体素子の各々に形成された前記回路の電気的特性を検査するテスタと電気的に接続されるプローブカードを用いて前記複数の半導体素子の電気的特性を検査する工程と、

前記半導体ウエハをダイシングし、前記複数の半導体素子毎に分離する工程とを有する半導体装置の製造方法であって、

前記プローブカードは、

50

前記複数の接触端子と、

前記複数の接触端子の各々から電気的に引き出された配線と、

前記配線と電気的に接続され、かつ多層配線基板の電極に接続される複数の周辺電極とを備えたプローブシートを有し、

前記プローブシートにおいて、前記複数の接触端子が形成された第1の面とは反対側の第2の面にて、前記複数の接触端子が形成された領域に固着基板が固着され、

前記固着基板を傾動可能になるようにした手段が設けられ、

前記複数の接触端子の各々は、前記プローブシートと離間して延在し、前記配線と電気的に接続された梁の一端に形成され、

前記梁の他端は前記プローブシートに固定されていることを特徴とする半導体装置の製造方法。

#### 【請求項 20】

半導体ウエハに回路および前記回路と電気的に接続する電極を作り込み、複数の半導体素子を形成する工程と、

前記複数の半導体素子に設けられた前記電極と接觸する複数の接触端子を有し、かつ前記複数の半導体素子の各々に形成された前記回路の電気的特性を検査するテスタと電気的に接続されるプローブカードを用いて前記複数の半導体素子の電気的特性を検査する工程と、

前記半導体ウエハをダイシングし、前記複数の半導体素子毎に分離する工程とを有する半導体装置の製造方法であって、

前記プローブカードは、

前記複数の接触端子と、

前記複数の接触端子の各々から電気的に引き出された配線と、

前記配線と電気的に接続され、かつ多層配線基板の電極に接続される複数の周辺電極と、

前記複数の接触端子が形成された第1の面とは反対側の第2の面にて、前記複数の接触端子が形成された領域に形成された金属シートとを備えたプローブシートを有し、

前記金属シートに固着基板が固着され、

前記固着基板を傾動可能になるようにした手段が設けられ、

前記複数の接触端子の各々は、前記プローブシートと離間して延在し、前記配線と電気的に接続された梁の一端に形成され、

前記梁の他端は前記プローブシートに固定されていることを特徴とする半導体装置の製造方法。

#### 【請求項 21】

半導体ウエハに回路および前記回路と電気的に接続する電極を作り込み、複数の半導体素子を形成する工程と、

前記複数の半導体素子に設けられた前記電極と接觸する複数の接触端子を有し、かつ前記複数の半導体素子の各々に形成された前記回路の電気的特性を検査するテスタと電気的に接続されるプローブカードを用いて前記複数の半導体素子の電気的特性を検査する工程と、

前記半導体ウエハをダイシングし、前記複数の半導体素子毎に分離する工程とを有する半導体装置の製造方法であって、

前記プローブカードは、

前記複数の接触端子と、

前記複数の接触端子の各々から電気的に引き出された配線と、

前記配線と電気的に接続され、かつ多層配線基板の電極に接続される複数の周辺電極とを備えたプローブシートを有し、

前記プローブシートにおいて、前記複数の接触端子が形成された第1の面とは反対側の第2の面にて、前記複数の接触端子が形成された領域に固着基板が固着され、さらに前記プローブシートが前記固着基板を包み込むように前記固着基板に固着されることで形成さ

10

20

30

40

50

れた1つ以上のブロックを備え、

前記1つ以上のブロックの各々の前記プローブシートの前記複数の周辺電極と、前記多層配線基板の前記電極とが接触し、

前記複数の接触端子の各々は、前記プローブシートと離間して延在し、前記配線と電気的に接続された梁の一端に形成され、

前記梁の他端は前記プローブシートに固定されていることを特徴とする半導体装置の製造方法。

#### 【請求項22】

半導体ウエハに回路および前記回路と電気的に接続する電極を作り込み、複数の半導体素子を形成する工程と、

前記複数の半導体素子に設けられた前記電極と接触する複数の接触端子を有し、かつ前記複数の半導体素子の各々に形成された前記回路の電気的特性を検査するテストと電気的に接続されるプローブカードを用いて前記複数の半導体素子の電気的特性を検査する工程と、

前記半導体ウエハをダイシングし、前記複数の半導体素子毎に分離する工程とを有する半導体装置の製造方法であって、

前記プローブカードは、

前記複数の接触端子と、

前記複数の接触端子の各々から電気的に引き出された配線と、

前記配線と電気的に接続され、かつ多層配線基板の電極に接続される複数の第1および第2の周辺電極とを備えたプローブシートを有し、

前記プローブシートにおいて、前記複数の接触端子が形成された第1の面とは反対側の第2の面にて、前記複数の接触端子が形成された領域に固着基板が固着され、

前記固着基板を傾動可能になるようにした手段が設けられ、

前記複数の接触端子の各々は、前記プローブシートと離間して延在し、前記配線と電気的に接続された梁の一端に形成され、

前記梁の他端は前記プローブシートに固定され、

前記複数の第1の周辺電極の各々は、前記プローブシートにおいて前記の接触端子と同じ第1の面に形成され、

前記複数の第2の周辺電極の各々は、前記プローブシートにおいて前記の接触端子とは反対側の第2の面に形成されていることを特徴とする半導体装置の製造方法。

#### 【請求項23】

請求項19～22のいずれか1項に記載の半導体装置の製造方法において、

前記プローブシートは、

(a) 結晶性を有する基板に異方性エッチングを施すことで形成した穴を型材としためっきにより、前記複数の接触端子を形成する工程、

(b) 前記基板上に前記複数の接触端子の各々と電気的に接続する前記梁、前記配線および絶縁層を逐次積層する工程、

(c) 前記複数の接触端子および前記梁と同じ配線層における前記絶縁層を除去することで、前記梁を前記プローブシートから離間させる工程、

を含む工程により形成され、

前記複数の接触端子の各々は、角錐形状または角錐台形状であることを特徴とする半導体装置の製造方法。

#### 【発明の詳細な説明】

#### 【技術分野】

#### 【0001】

本発明は、プローブカード、半導体検査装置および半導体装置の製造技術に関し、特に、半導体集積回路の製造に用いる手法と同様の手法で形成するプローブシートを備えたプローブカード、そのプローブカードの製造技術、そのプローブカードを含む半導体検査装置、およびその半導体検査装置による検査工程を含む半導体装置の製造工程に適用して有

効な技術に関するものである。

**【背景技術】**

**【0 0 0 2】**

半導体素子回路を半導体ウエハ（以下、単にウエハと記す）に形成後に行う半導体装置の製造工程のうち、主に検査工程の流れの一例を、代表的な半導体装置の出荷形態であるパッケージ品、ベアチップおよびC S P（Chip Size(Scale) Package）を例にして、図51に示した。

**【0 0 0 3】**

半導体装置の製造工程では、図51に示したように大きく分けて次の3つの検査が行われる。まず、ウエハに半導体素子回路および電極を形成したウエハ状態で行われ、導通状態および半導体素子の電気信号動作状態を把握するウエハ検査、続いて半導体素子を高温や高印加電圧等の状態において不安定な半導体素子を摘出するバーンイン検査、そして半導体装置を出荷する前に製品性能を把握する選別検査である。

10

**【0 0 0 4】**

このような半導体装置の検査に用いられる装置（半導体検査装置）に対し、従来技術では、ウエハは、その面上に多数の半導体装置（半導体チップ（以下、単にチップと記す））が設けられ、個々に切り離して使用に供される。個々に切り離された半導体装置には、その表面に多数の電極が列設されている。こうした半導体装置を工業的に多数生産し、その電気特性を検査するには、プローブカードから斜めに出たタンゲステン針からなるプローブで構成される接続装置が用いられている。この接続装置による検査では、プローブのたわみを利用した接触圧により電極を擦って接触を取り、その電気特性を検査する方法が用いられている。

20

**【0 0 0 5】**

近年、半導体素子の高密度化に伴い、半導体装置製造時の検査工程において検査用のプローブの狭ピッチ多ピン化が進んでいる。そのため、半導体素子の電極と検査回路間で確実に電気信号を伝送し、動作検査を行う工程で、狭ピッチ多ピンの半導体素子の微小な電極に位置精度よくプローピングができる、しかもその半導体素子へ低荷重でプローピングして損傷を防止できる接続装置を使用した半導体素子の検査装置の開発が望まれている。

30

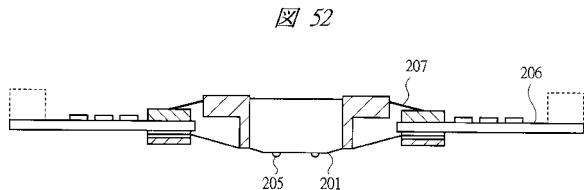

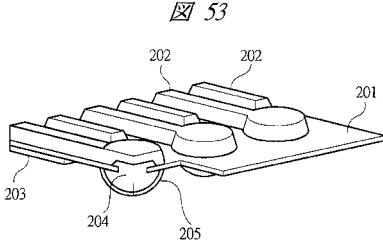

**【0 0 0 6】**

半導体素子の高密度化、狭ピッチ化が進み、高速信号による動作試験が必要になった場合の半導体素子の特性検査を可能とする検査方法および検査装置として、1988年度のITC（インターナショナル テスト コンファレンス）の講演論文集の601頁から607頁（非特許文献1）に記載された技術がある。図52はその非特許文献1に開示された検査装置の構造概略図、図53はその検査装置の要部拡大斜視図である。ここで用いられる半導体検査用のプローブは、フレキシブルな絶縁膜201の上面にフォトリソグラフ技術で配線202を形成し、絶縁膜201の下面にグランド層203を形成し、被検査対象の半導体の電極に対応する位置に設けた絶縁膜201のスルーホール204にめっきによって半球状のバンプ205を形成したものと接触端子として用いるものである。この技術は、絶縁膜201の表面に形成した配線202および配線基板206を通じて検査回路（図示は省略）に接続されているバンプ205を、板ばね207の弾性力によって、検査対象の半導体素子の電極にバンプ205をこすって接触させ、信号の授受を行って検査する方法である。

40

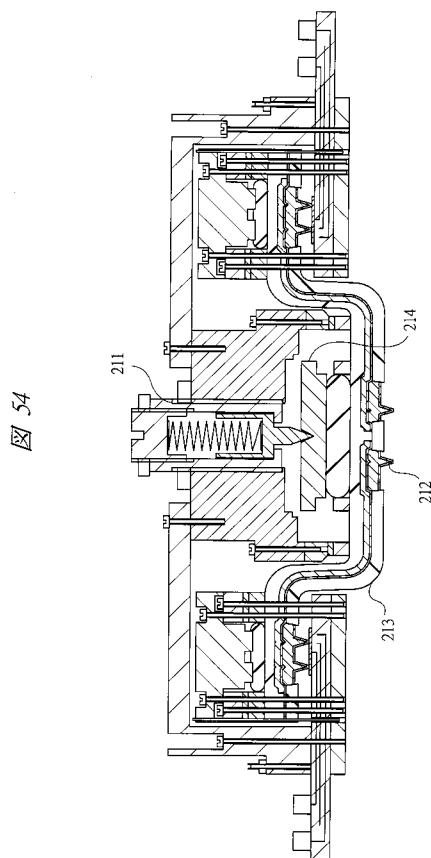

**【0 0 0 7】**

また、特開2005-24377号公報（特許文献1）には、半導体素子の検査装置が開示されており、図54は、その検査用プローブカードの構造の模式図である。これは、プローブシートを4分割して、プローブシートの中央に設置したスプリングプランジャー211により、四角錐状の接触端子212および配線を形成した絶縁膜213を押し駒214および緩衝材を介して押し出すプローブ装置である。

**【0 0 0 8】**

また、特開平7-283280号公報（特許文献2）には、シリコンウエハを選択的に

50

異方性エッティングすることによって形成した穴を型材として接触端子を形成し、この接触端子を柔軟性のある絶縁フィルムに形成した配線に電気的に接続し、この絶縁フィルムにおける接触端子配置面とは反対の裏面側に緩衝層を挟んでプローブシート固定基板を固定し、このプローブシート固定基板と、ウエハ形状の溝に被検査対象である半導体装置が形成されたウエハを固定したウエハ支持基板とを重ね合わせて、接触端子群の先端面をウエハの電極群の面に接触させることにより、電気的接続を取り半導体装置の検査を行う検査システムが開示されている。

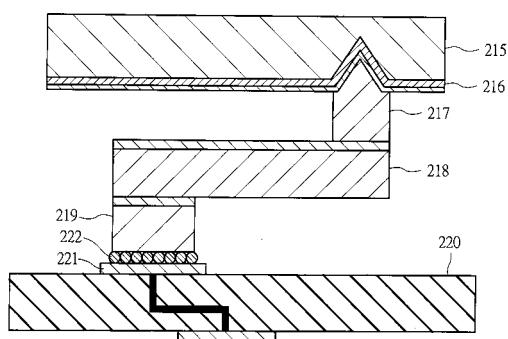

#### 【009】

また、特表2002-531915号公報（特許文献3）には、リソグラフィ技法により形成したばね接触要素が開示されている。図55は、リソグラフィ技法により形成したそのばね接触要素の製造工程の途中段階を示す模式図である。これは、シリコン基板215を異方性エッティングすることによって形成した穴216を型材としてチップ部分（接触端子）217を形成し、さらにこのチップ部分217と接続するビーム部分（梁）218およびポスト部分219をリソグラフィ技法および表面研磨加工（Chemical Mechanical Polishing；CMP）で形成し、ポスト部分219をセラミック多層配線基板220の電極221にはんだ222で接続し、最後にチップ部分217をシリコン基板215から剥離するものである。

【非特許文献1】1988年度ITC（インターナショナル テスト コンファレンス）講演論文集（601頁～607頁）

【特許文献1】特開2005-24377号公報

【特許文献2】特開平7-283280号公報

【特許文献3】特表2002-531915号公報

#### 【発明の開示】

【発明が解決しようとする課題】

#### 【010】

近年、狭ピッチかつ多ピンの半導体素子の電極と検査回路間で電気信号を伝送して動作検査できる接続装置を使用した半導体素子の検査装置の開発が望まれている。また、高速電気信号用の半導体素子は、誘電損失を低減しつつ微細配線化するため、配線層間の絶縁膜として、酸化シリコン（SiO<sub>2</sub>）と比べて誘電率の一段と小さな材料、例えばフッ素が添加された酸化シリコン（FSG）、カーボンが添加された酸化シリコン（SiOC）および有機系材料等の低誘電率膜（Low-k膜）を用いるようになっている。このような誘電率の小さい材料は、耐荷重および機械的強度が比較的弱いため、その低誘電材料に損傷を与えないように、数10mN程度以下の荷重で安定した接触抵抗値が実現できる検査装置が望まれている。

#### 【011】

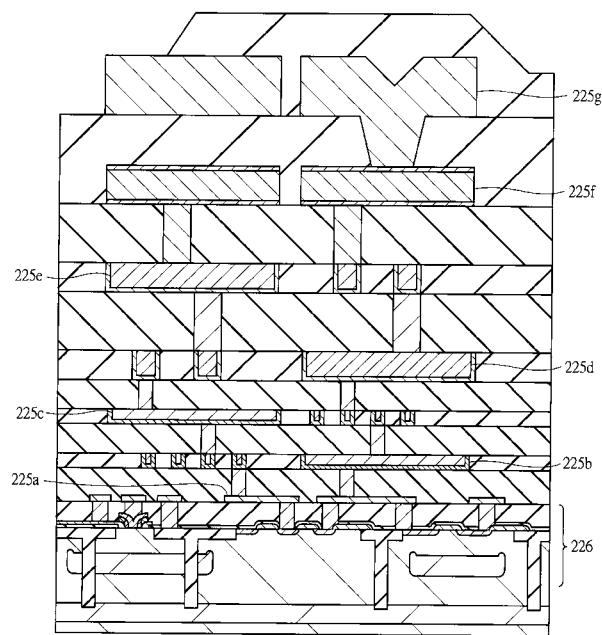

それに加えて、半導体素子の微細化が進行すると、例えば特開2001-53076号に示される上層に多層の配線225a～225gが形成されたCMOS-LSI226のように、半導体素子の検査用の電極部の直下に能動回路素子形成領域（アクティブエリア）や微細な配線が多層に形成されていることが多くなる（図56参照）。そのため、それら能動回路素子や多層な配線にダメージを与えないように、検査時の接触端子の荷重は、良好な接触抵抗値を得られる範囲で可能な限り低荷重とすることが求められている。

#### 【012】

また、狭ピッチの微小な半導体素子の検査用電極パッドに、高位置精度で検査用の接触端子を接触させる必要がある。加えて、その後の工程で、その電極パッドを用いたワイヤボンディングあるいは接続用バンプの形成時に、そのワイヤあるいはバンプの電極パッドへの接続を確実にするために、プロービングによる電極パッド面の荒れを可能な限り防止することが求められている。すなわち、微小なプロービング痕であることが求められている。

#### 【013】

そこで、これらの観点から、上記の技術について検討する。

10

20

30

40

50

## 【0014】

タンゲステン針からなるプローブおよび前記半球状のバンプを形成したプローブは、アルミニウム電極やはんだ電極などの材料表面に酸化物を生成する被接触材料に対しては、接触端子を電極に擦りつけることにより、電極材料表面の酸化物を擦り取り、その下面の金属導体材料と接触させることにより、接触状態を確保している。その結果、電極を接触端子で擦ることで電極材料のクズが生じ、配線間のショートおよび異物発生の原因となる。また、電極にプローブを数百mN程度以上の荷重をかけながら擦りつけて接触状態を確保することにより、低誘電率材料に損傷を与える可能性が指摘されている。

## 【0015】

このように、図52および図53に示したような配線の一部にめっきによって形成したバンプをプローブとする方法は、バンプの先端部が平坦あるいは半球状となるため、アルミニウム電極あるいははんだ電極などの材料表面に酸化物を生成する被接触材料に対しては、酸化物を擦り取り難いために接触抵抗が不安定になり、接触時の荷重を数百mN程度以上にする必要がある。しかし、接触時の荷重を大きくし過ぎることには問題がある。すなわち、半導体素子の高集積化が進み、高密度多ピンかつ狭ピッチの電極を半導体素子表面に形成するため、電極直下に多数の能動素子あるいは微細な配線が形成されていることが多くなり、半導体素子検査時のプローブの電極への接触圧が大き過ぎると、電極およびその直下の能動素子や配線に損傷を与えるおそれがあるため、プロービング時に注意深く動作制御する必要があり、検査のスループットの低下を招くおそれがある。

10

## 【0016】

さらに、バンプの形状等にばらつきが生じることが予想されるため、接触が不十分な突起（バンプ）を完全に接触させるには、全体としてさらに大きな接触荷重が必要となり、部分的には、過大な接触圧となってしまうという問題がある。そのため、接触対象の材料表面の酸化物等を貫通して、安定した接触特性が確保できる接触端子の形状に加えて、プローブシートの押圧時に接触対象の電極と確実に接触させるために、柔軟性のあるプローブシートが必要となっている。

20

## 【0017】

図54に示した四角錐状の接触端子を用いて、半導体素子の検査用電極に垂直にプロービングする検査装置（特許文献1参照）は、接触抵抗値が安定しているが、近年の更なる狭ピッチ化と高速の電気信号検査が求められる場合に、更なる接触端子の先端位置精度の向上が求められている。加えて、高速伝送用回路形成材料には、前述のように低誘電率の比較的耐荷重に弱い材料が用いられる傾向があり、しかも、検査用電極の真下には、能動素子や回路が設けられる傾向があることから、プロービング時の半導体素子への損傷を防止するために更なる低荷重のプローブが求められている。

30

## 【0018】

一方、上記特許文献3に開示された技術では、接触端子が形成された片持ち梁構造にすることにより、接触端子を個別に動作させることができ、梁を構成する材料および形状を適切に選択すれば、ある程度接触端子の加圧荷重を設定することができる。しかしながら、特許文献3が開示している片持ち梁構造の形成方法は、前述したように接触端子の先端の型材となるシリコン基板にチップ部分（接触端子）を形成し、さらにこのチップ部分と接続するビーム部分（梁）およびポスト部分を形成し、ポスト部分をセラミック多層配線基板の電極にはんだで接続し、最後にチップ部分とシリコン基板とをエッティング液で剥離することで形成するものである。そのため、はんだ接続部分の面積確保が必要であり、さらにシリコン基板とセラミック多層配線基板との間にエッティング液の浸透間隙の確保が必要となるため、チップ部分の狭ピッチ化に限界があり、はんだ接続および剥離過程で、チップ部分の位置精度が不安定となり、形成工程および組立工程が複雑となるという課題を残している。

40

## 【0019】

本発明の目的の一つは、被接触対象の電極パッドに低荷重で損傷を与えないでプロービング検査でき、多点かつ高密度（狭ピッチ）で、小さなプロービング痕で接触できる接触

50

端子を有する伝送特性が良好で接触特性が安定した半導体装置検査用のプローブカードを提供することにある。

【0020】

また、本発明の他の目的の一つは、プロービング検査時の接触端子の先端位置精度を高精度に保つことのできるプローブカードを提供することにある。

【0021】

また、本発明の他の目的の一つは、四角錐あるいは四角錐台形状の接触端子を先端部に形成した片持ち梁構造、引き出し配線および固着基板を一括形成し、組立および接続工程が容易で、低荷重でも接触抵抗値が安定しているプローブシートを用いた半導体装置検査用のプローブカードを提供することにある。

10

【課題を解決するための手段】

【0022】

本願において開示される発明のうち、代表的なものの概要を簡単に説明すれば、次のとおりである。

【0023】

(1) 本発明によるプローブカードは、

被検査対象に設けられた電極と接触する複数の接触端子と、

前記複数の接触端子の各々から電気的に引き出された配線と、

前記配線と電気的に接続され、かつ多層配線基板の電極に接続される複数の周辺電極とを備えたプローブシートを有し、

前記プローブシートにおいて、前記複数の接触端子が形成された第1の面とは反対側の第2の面にて、前記複数の接触端子が形成された領域に固着基板が固着され、

前記固着基板を傾動可能になるようにした手段が設けられ、

前記複数の接触端子の各々は、前記プローブシートと離間して延在し、前記配線と電気的に接続された梁の一端に形成され、

前記梁の他端は前記プローブシートに固定されている。

【0024】

(2) 本発明によるプローブカードは、

被検査対象に設けられた電極と接触する複数の接触端子と、

前記複数の接触端子の各々から電気的に引き出された配線と、

前記配線と電気的に接続され、かつ多層配線基板の電極に接続される複数の周辺電極と、

20

前記複数の接触端子が形成された第1の面とは反対側の第2の面にて、前記複数の接触端子が形成された領域に形成された金属シートとを備えたプローブシートを有し、

前記金属シートに固着基板が固着され、

前記固着基板を傾動可能になるようにした手段が設けられ、

前記複数の接触端子の各々は、前記プローブシートと離間して延在し、前記配線と電気的に接続された梁の一端に形成され、

前記梁の他端は前記プローブシートに固定されている。

【0025】

(3) 本発明によるプローブカードは、(1)または(2)記載のプローブカードにおいて、

前記多層配線基板は、前記被検査対象の電気的特性を検査するテスタと電気的に接続される。

【0026】

(4) 本発明によるプローブカードは、(1)～(3)のいずれかに記載のプローブカードにおいて、

前記固着基板を傾動可能になるようにした前記手段は、複数のばね性を有したガイドピンである。

【0027】

40

30

50

(5) 本発明によるプローブカードは、(4)に記載のプローブカードにおいて、前記固着基板を傾動可能になるようにした前記手段は、さらに複数のばね性のないガイドピンを用いる。

【0028】

(6) 本発明によるプローブカードは、(1)～(5)のいずれかに記載のプローブカードにおいて、

前記固着基板を傾動可能になるようにした前記手段は、1つ以上の板ばねである。

【0029】

(7) 本発明によるプローブカードは、

被検査対象に設けられた電極と接触する複数の接触端子と、

前記複数の接触端子の各々から電気的に引き出された配線と、

前記配線と電気的に接続され、かつ多層配線基板の電極に接続される複数の周辺電極とを備えたプローブシートを有し、

前記プローブシートにおいて、前記複数の接触端子が形成された第1の面とは反対側の第2の面にて、前記複数の接触端子が形成された領域に固着基板が固着され、さらに前記プローブシートが前記固着基板を包み込むように前記固着基板に固着されることで形成された1つ以上のプロックを備え、

前記1つ以上のプロックの各々の前記プローブシートの前記複数の周辺電極と、前記多層配線基板の前記電極とが接触し、

前記複数の接触端子の各々は、前記プローブシートと離間して延在し、前記配線と電気的に接続された梁の一端に形成され、

前記梁の他端は前記プローブシートに固定されている。

【0030】

(8) 本発明によるプローブカードは、(1)～(7)のいずれかに記載のプローブカードにおいて、

前記接触端子は、角錐形状または角錐台形状である。

【0031】

(9) 本発明によるプローブカードは、(8)に記載のプローブカードにおいて、

前記接触端子は、結晶性を有する基板に異方性エッティングを施すことで形成した穴を型材としためっきにより形成されたものである。

【0032】

(10) 本発明によるプローブカードは、(9)に記載のプローブカードにおいて、

前記結晶性を有する基板は、シリコンである。

【0033】

(11) 本発明によるプローブカードは、

被検査対象に設けられた電極と接触する複数の接触端子と、

前記複数の接触端子の各々から電気的に引き出された配線と、

前記配線と電気的に接続され、かつ多層配線基板の電極に接続される複数の第1および第2の周辺電極とを備えたプローブシートを有し、

前記プローブシートにおいて、前記複数の接触端子が形成された第1の面とは反対側の第2の面にて、前記複数の接触端子が形成された領域に固着基板が固着され、

前記固着基板を傾動可能になるようにした手段が設けられ、

前記複数の接触端子の各々は、前記プローブシートと離間して延在し、前記配線と電気的に接続された梁の一端に形成され、

前記梁の他端は前記プローブシートに固定され、

前記複数の第1の周辺電極の各々は、前記プローブシートにおいて前記の接触端子と同じ第1の面に形成され、

前記複数の第2の周辺電極の各々は、前記プローブシートにおいて前記の接触端子とは反対側の第2の面に形成されている。

【0034】

10

20

30

40

50

(12) 本発明によるプローブカードは、(11)に記載のプローブカードにおいて、前記プローブシートにおける前記第1および第2の周辺電極の形成ピッチは、前記複数の接触端子の形成ピッチよりも広い。

**【0035】**

(13) 本発明によるプローブカード製造方法は、

被検査対象に設けられた電極と接触する複数の接触端子と、

前記複数の接触端子の各々から電気的に引き出された配線と、

前記配線と電気的に接続され、かつ多層配線基板の電極に接続される複数の周辺電極とを備えたプローブシートを有し、

前記プローブシートにおいて、前記複数の接触端子が形成された第1の面とは反対側の第2の面にて、前記複数の接触端子が形成された領域に固着基板が固着され、

前記固着基板を傾動可能になるようにした手段が設けられ、

前記複数の接触端子の各々は、前記プローブシートと離間して延在し、前記配線と電気的に接続された梁の一端に形成され、

前記梁の他端は前記プローブシートに固定されたプローブカードの製造方法であって、

前記プローブシートを形成する工程は、

(a) 結晶性を有する基板に異方性エッチングを施すことで形成した穴を型材としためっきにより、前記複数の接触端子を形成する工程、

(b) 前記基板上に前記複数の接触端子の各々と電気的に接続する前記梁、前記配線および絶縁層を逐次積層する工程、

(c) 前記複数の接触端子および前記梁と同じ配線層における前記絶縁層を除去することで、前記梁を前記プローブシートから離間させる工程、

を含む。

**【0036】**

(14) 本発明による半導体検査装置は、

被検査対象を載せる試料台と、

前記被検査対象に設けられた電極と接触する複数の接触端子を有し、かつ前記被検査対象の電気的特性を検査するテスタと電気的に接続されるプローブカードとを有する半導体検査装置であって、

前記プローブカードは、

前記複数の接触端子と、

前記複数の接触端子の各々から電気的に引き出された配線と、

前記配線と電気的に接続され、かつ多層配線基板の電極に接続される複数の周辺電極とを備えたプローブシートを有し、

前記プローブシートにおいて、前記複数の接触端子が形成された第1の面とは反対側の第2の面にて、前記複数の接触端子が形成された領域に固着基板が固着され、

前記固着基板を傾動可能になるようにした手段が設けられ、

前記複数の接触端子の各々は、前記プローブシートと離間して延在し、前記配線と電気的に接続された梁の一端に形成され、

前記梁の他端は前記プローブシートに固定されている。

**【0037】**

(15) 本発明による半導体検査装置は、

被検査対象を載せる試料台と、

前記被検査対象に設けられた電極と接触する複数の接触端子を有し、かつ前記被検査対象の電気的特性を検査するテスタと電気的に接続されるプローブカードとを有する半導体検査装置であって、

前記プローブカードは、

前記複数の接触端子と、

前記複数の接触端子の各々から電気的に引き出された配線と、

前記配線と電気的に接続され、かつ多層配線基板の電極に接続される複数の周辺電極と

10

20

30

40

50

、前記複数の接触端子が形成された第1の面とは反対側の第2の面にて、前記複数の接触端子が形成された領域に形成された金属シートとを備えたプローブシートを有し、

前記金属シートに固着基板が固着され、

前記固着基板を傾動可能になるようにした手段が設けられ、

前記複数の接触端子の各々は、前記プローブシートと離間して延在し、前記配線と電気的に接続された梁の一端に形成され、

前記梁の他端は前記プローブシートに固定されている。

#### 【0038】

(16) 本発明による半導体検査装置は、10

被検査対象を載せる試料台と、

前記被検査対象に設けられた電極と接触する複数の接触端子を有し、かつ前記被検査対象の電気的特性を検査するテスタと電気的に接続されるプローブカードとを有する半導体検査装置であって、

前記プローブカードは、

前記複数の接触端子と、

前記複数の接触端子の各々から電気的に引き出された配線と、

前記配線と電気的に接続され、かつ多層配線基板の電極に接続される複数の周辺電極とを備えたプローブシートを有し、

前記プローブシートにおいて、前記複数の接触端子が形成された第1の面とは反対側の第2の面にて、前記複数の接触端子が形成された領域に固着基板が固着され、さらに前記プローブシートが前記固着基板を包み込むように前記固着基板に固着されることで形成された1つ以上のロックを備え、20

前記1つ以上のロックの各々の前記プローブシートの前記複数の周辺電極と、前記多層配線基板の前記電極とが接触し、

前記複数の接触端子の各々は、前記プローブシートと離間して延在し、前記配線と電気的に接続された梁の一端に形成され、

前記梁の他端は前記プローブシートに固定されている。

#### 【0039】

(17) 本発明による半導体検査装置は、30

被検査対象を載せる試料台と、

前記被検査対象に設けられた電極と接触する複数の接触端子を有し、かつ前記被検査対象の電気的特性を検査するテスタと電気的に接続されるプローブカードとを有する半導体検査装置であって、

前記プローブカードは、

前記複数の接触端子と、

前記複数の接触端子の各々から電気的に引き出された配線と、

前記配線と電気的に接続され、かつ多層配線基板の電極に接続される複数の第1および第2の周辺電極とを備えたプローブシートを有し、

前記プローブシートにおいて、前記複数の接触端子が形成された第1の面とは反対側の第2の面にて、前記複数の接触端子が形成された領域に固着基板が固着され、40

前記固着基板を傾動可能になるようにした手段が設けられ、

前記複数の接触端子の各々は、前記プローブシートと離間して延在し、前記配線と電気的に接続された梁の一端に形成され、

前記梁の他端は前記プローブシートに固定され、

前記複数の第1の周辺電極の各々は、前記プローブシートにおいて前記の接触端子と同じ第1の面に形成され、

前記複数の第2の周辺電極の各々は、前記プローブシートにおいて前記の接触端子とは反対側の第2の面に形成されている。

#### 【0040】

(18) 本発明による半導体検査装置は、(14)～(17)のいずれかに記載の半導体検査装置において、

前記プローブシートは、

(a) 結晶性を有する基板に異方性エッチングを施すことで形成した穴を型材としためっきにより、前記複数の接触端子を形成する工程、

(b) 前記基板上に前記複数の接触端子の各々と電気的に接続する前記梁、前記配線および絶縁層を逐次積層する工程、

(c) 前記複数の接触端子および前記梁と同じ配線層における前記絶縁層を除去することで、前記梁を前記プローブシートから離間させる工程、

を含む工程により形成されている。

10

#### 【0041】

(19) 本発明による半導体装置の製造方法は、

半導体ウエハに回路および前記回路と電気的に接続する電極を作り込み、複数の半導体素子を形成する工程と、

前記複数の半導体素子に設けられた前記電極と接触する複数の接触端子を有し、かつ前記複数の半導体素子の各々に形成された前記回路の電気的特性を検査するテスタと電気的に接続されるプローブカードを用いて前記複数の半導体素子の電気的特性を検査する工程と、

前記半導体ウエハをダイシングし、前記複数の半導体素子毎に分離する工程とを有する半導体装置の製造方法であって、

20

前記プローブカードは、

前記複数の接触端子と、

前記複数の接触端子の各々から電気的に引き出された配線と、

前記配線と電気的に接続され、かつ多層配線基板の電極に接続される複数の周辺電極とを備えたプローブシートを有し、

前記プローブシートにおいて、前記複数の接触端子が形成された第1の面とは反対側の第2の面にて、前記複数の接触端子が形成された領域に固着基板が固着され、

前記固着基板を傾動可能になるようにした手段が設けられ、

前記複数の接触端子の各々は、前記プローブシートと離間して延在し、前記配線と電気的に接続された梁の一端に形成され、

30

前記梁の他端は前記プローブシートに固定されている。

#### 【0042】

(20) 本発明による半導体装置の製造方法は、

半導体ウエハに回路および前記回路と電気的に接続する電極を作り込み、複数の半導体素子を形成する工程と、

前記複数の半導体素子に設けられた前記電極と接触する複数の接触端子を有し、かつ前記複数の半導体素子の各々に形成された前記回路の電気的特性を検査するテスタと電気的に接続されるプローブカードを用いて前記複数の半導体素子の電気的特性を検査する工程と、

前記半導体ウエハをダイシングし、前記複数の半導体素子毎に分離する工程とを有する半導体装置の製造方法であって、

40

前記プローブカードは、

前記複数の接触端子と、

前記複数の接触端子の各々から電気的に引き出された配線と、

前記配線と電気的に接続され、かつ多層配線基板の電極に接続される複数の周辺電極と、

前記複数の接触端子が形成された第1の面とは反対側の第2の面にて、前記複数の接触端子が形成された領域に形成された金属シートとを備えたプローブシートを有し、

前記金属シートに固着基板が固着され、

前記固着基板を傾動可能になるようにした手段が設けられ、

50

前記複数の接触端子の各々は、前記プローブシートと離間して延在し、前記配線と電気的に接続された梁の一端に形成され、

前記梁の他端は前記プローブシートに固定されている。

#### 【0043】

(21) 本発明による半導体装置の製造方法は、

半導体ウエハに回路および前記回路と電気的に接続する電極を作り込み、複数の半導体素子を形成する工程と、

前記複数の半導体素子に設けられた前記電極と接触する複数の接触端子を有し、かつ前記複数の半導体素子の各々に形成された前記回路の電気的特性を検査するテスタと電気的に接続されるプローブカードを用いて前記複数の半導体素子の電気的特性を検査する工程と、

前記半導体ウエハをダイシングし、前記複数の半導体素子毎に分離する工程とを有する半導体装置の製造方法であって、

前記プローブカードは、

前記複数の接触端子と、

前記複数の接触端子の各々から電気的に引き出された配線と、

前記配線と電気的に接続され、かつ多層配線基板の電極に接続される複数の周辺電極とを備えたプローブシートを有し、

前記プローブシートにおいて、前記複数の接触端子が形成された第1の面とは反対側の第2の面にて、前記複数の接触端子が形成された領域に固着基板が固着され、さらに前記プローブシートが前記固着基板を包み込むように前記固着基板に固着されることで形成された1つ以上のプロックを備え、

前記1つ以上のプロックの各々の前記プローブシートの前記複数の周辺電極と、前記多層配線基板の前記電極とが接触し、

前記複数の接触端子の各々は、前記プローブシートと離間して延在し、前記配線と電気的に接続された梁の一端に形成され、

前記梁の他端は前記プローブシートに固定されている。

#### 【0044】

(22) 本発明による半導体装置の製造方法は、

半導体ウエハに回路および前記回路と電気的に接続する電極を作り込み、複数の半導体素子を形成する工程と、

前記複数の半導体素子に設けられた前記電極と接触する複数の接触端子を有し、かつ前記複数の半導体素子の各々に形成された前記回路の電気的特性を検査するテスタと電気的に接続されるプローブカードを用いて前記複数の半導体素子の電気的特性を検査する工程と、

前記半導体ウエハをダイシングし、前記複数の半導体素子毎に分離する工程とを有する半導体装置の製造方法であって、

前記プローブカードは、

前記複数の接触端子と、

前記複数の接触端子の各々から電気的に引き出された配線と、

前記配線と電気的に接続され、かつ多層配線基板の電極に接続される複数の第1および第2の周辺電極とを備えたプローブシートを有し、

前記プローブシートにおいて、前記複数の接触端子が形成された第1の面とは反対側の第2の面にて、前記複数の接触端子が形成された領域に固着基板が固着され、

前記固着基板を傾動可能になるようにした手段が設けられ、

前記複数の接触端子の各々は、前記プローブシートと離間して延在し、前記配線と電気的に接続された梁の一端に形成され、

前記梁の他端は前記プローブシートに固定され、

前記複数の第1の周辺電極の各々は、前記プローブシートにおいて前記の接触端子と同じ第1の面に形成され、

10

20

30

40

50

前記複数の第2の周辺電極の各々は、前記プローブシートにおいて前記の接触端子とは反対側の第2の面に形成されている。

#### 【0045】

(23) 本発明による半導体装置の製造方法は、(19)～(22)のいずれかに記載の半導体装置の製造方法において、

前記プローブシートは、

(a) 結晶性を有する基板に異方性エッティングを施すことで形成した穴を型材としためっきにより、前記複数の接触端子を形成する工程、

(b) 前記基板上に前記複数の接触端子の各々と電気的に接続する前記梁、前記配線および絶縁層を逐次積層する工程、

(c) 前記複数の接触端子および前記梁と同じ配線層における前記絶縁層を除去することで、前記梁を前記プローブシートから離間させる工程、

を含む工程により形成され、

前記複数の接触端子の各々は、角錐形状または角錐台形状である。

#### 【発明の効果】

#### 【0046】

本願において開示される発明のうち、代表的なものによって得られる効果を簡単に説明すれば以下のとおりである。

#### 【0047】

角錐形あるいは角錐台形の形状および位置精度の良好な片持ち梁構造の接触端子と、引き出し配線と、周辺電極と、絶縁シートとを一括形成したプローブシートを備え、その接触端子を形成した領域に固着された基板を傾動可能にした本発明のプローブカードおよびその製造方法は、半球状のめっきバンプを形成したメンブレンプローブ、あるいは接触端子形成梁とセラミック多層配線基板とをはんだ接続後、その犠牲基板をエッティング液で剥離して形成する片持ち梁の形成方法と比較して、以下の効果を奏する。

(1) 数 $10\mu m$ 以下の狭ピッチで多ピンの片持ち梁構造の接触端子を形成したプローブシートでも、接触端子群を容易に一括形成することができ、配線の多層化による電気信号特性の設計も容易なため、狭ピッチかつ多ピンの検査用であるばかりでなく、インピーダンス整合した高速伝送用回路を有したプローブカードが実現できる。

(2) 被検査対象と同程度の線膨張率を持つ金属シートおよび固着基板を、接触端子を形成した領域に直接固着した構造により、広い温度範囲で接触端子の先端位置精度が良好なプローブカードが実現できる。

(3) 角錐形状あるいは角錐台形状の接触端子を一括形成したプローブシートを、組立用基材と一緒に一括形成し、片持ち梁構造の接触端子の個別の押圧動作と傾動動作とを両立させることにより、大面積の被検査対象でも低荷重での接触で良好な接触抵抗値の安定性を実現し、接触端子の先端位置精度および組立性の良好なプローブカードが実現できる。

#### 【0048】

また、本発明のプローブカードは、片持ち梁構造の接触端子が形成された領域のプローブシートの反対面に固着された基板を包み込むブロック構造のプローブを複数個組み合わせて半導体検査に使用することにより、多数個チップの同時検査用プローブカード、あるいはフルウエハ検査用のウエハカセットが、簡単な構成で実現できる。

#### 【発明を実施するための最良の形態】

#### 【0049】

以下の実施の形態においては便宜上その必要があるときは、複数のセクションまたは実施の形態に分割して説明するが、特に明示した場合を除き、それらはお互いに無関係なものではなく、一方は他方の一部または全部の変形例、詳細、補足説明等の関係にある。

#### 【0050】

また、以下の実施の形態において、要素の数等（個数、数値、量、範囲等を含む）に言及する場合、特に明示した場合および原理的に明らかに特定の数に限定される場合等を除き、その特定の数に限定されるものではなく、特定の数以上でも以下でも良い。

**【0051】**

さらに、以下の実施の形態において、その構成要素（要素ステップ等も含む）は、特に明示した場合および原理的に明らかに必須であると考えられる場合等を除き、必ずしも必須のものではないことは言うまでもない。また、実施例等において構成要素等について、「Aからなる」、「Aよりなる」と言うときは、特にその要素のみである旨明示した場合等を除き、それ以外の要素を排除するものでないことは言うまでもない。

**【0052】**

同様に、以下の実施の形態において、構成要素等の形状、位置関係等に言及するときは、特に明示した場合および原理的に明らかにそうでないと考えられる場合等を除き、実質的にその形状等に近似または類似するもの等を含むものとする。このことは、上記数値および範囲についても同様である。

10

**【0053】**

また、材料等について言及するときは、特にそうでない旨明記したとき、または、原理的または状況的にそうでないときを除き、特定した材料は主要な材料であって、副次的要素、添加物、付加要素等を排除するものではない。たとえば、シリコン部材は特に明示した場合等を除き、純粋なシリコンの場合だけでなく、添加不純物、シリコンを主要な要素とする2元、3元等の合金（たとえばSiGe）等を含むものとする。

**【0054】**

また、本実施の形態を説明するための全図において同一機能を有するものは原則として同一の符号を付し、その繰り返しの説明は省略する。

20

**【0055】**

また、本実施の形態で用いる図面においては、平面図であっても図面を見易くするために部分的にハッチングを付す場合がある。

**【0056】**

以下の実施の形態および実施例では、主な用語を次のように定義する。

**【0057】**

半導体装置とは、その形態に関わらず、回路が形成されたウエハ状態のものであっても、半導体素子であっても、その後パッケージされたもの（QFP（Quad Flat Package）、BGA（Ball Grid Array）およびCSP（Chip Size Package）等）でも構わない。

30

**【0058】**

プローブシートとは、検査対象と接触する接触端子とそこから引き回された配線が設けられ、その配線に外部接続用の電極が形成された薄膜をいい、厚さ $10\text{ }\mu\text{m} \sim 100\text{ }\mu\text{m}$ 程度のものを対象としている。

**【0059】**

プローブカードとは、検査対象と接触する端子、多層配線基板等を有する構造体（例えば、後述の実施の形態において図2を用いて説明する構造体）を示す。

**【0060】**

半導体検査装置とは、プローブカードと検査対象を載せる試料支持系を有する検査装置を示す。

40

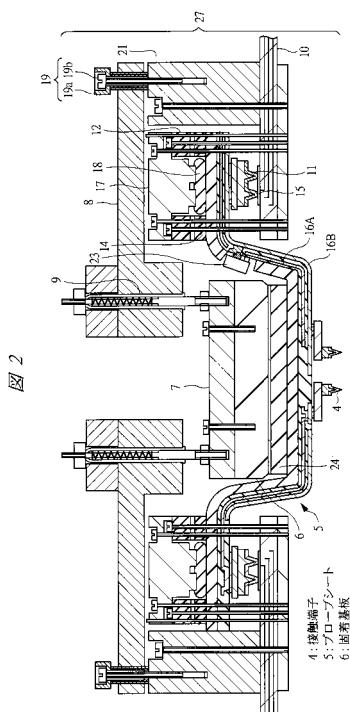

**【0061】**

被検査対象の一例であるLSI用の半導体素子（チップ）2は、図1に示すようにウエハ1に多数個形成され、その後切り離されて使用に供される。図1は、LSI用の半導体素子2が多数並設されたウエハ1を示す斜視図であり、その一部である1個の半導体素子2は拡大して示している。半導体素子2の表面には、周辺に沿って半導体素子2内に形成された回路と電気的に接続する多数の電極3が配列されている。

**【0062】**

ところで、半導体素子2においては、高集積化に伴って上記電極3の配置の高密度化および狭ピッチ化が更に進む状況にある。電極3の配置の狭ピッチ化の傾向は、 $0.1\text{ mm}$ 程度以下となってきており、例えば、 $0.08\text{ mm}$ 、 $0.04\text{ mm}$ 、またはそれ以下となっている。電極3の高密度化の傾向としては、半導体素子2の周辺に沿って、1列か

50

ら 2 列へ、更に全面に配列される傾向となってきた。10

#### 【 0 0 6 3 】

また、半導体素子を高温で動作試験することにより、半導体素子の特性および信頼性をより明確に把握する高温動作試験(85 ~ 150)が実施される傾向となってきた。また、使用環境の拡大とともに、低温動作試験(-55)も実施される傾向になっている。

#### 【 0 0 6 4 】

以下の実施例に係る半導体検査装置は、上記電極3の高密度化および狭ピッチ化に対応でき、なおかつ、高速電気信号(100MHz ~ 20GHz)による検査を可能にするものである。

10

#### 【 0 0 6 5 】

また、半導体検査装置におけるプローブカードの一部の構成材料として、150の耐熱性があり、かつ線膨張率が被検査対象と同程度の材料を用いることにより、雰囲気温度によるプローブ先端部の位置ずれを防止することを可能としている。

#### 【 0 0 6 6 】

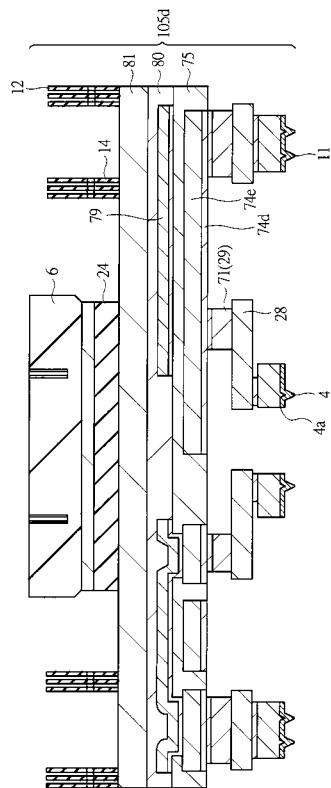

以下、本実施の形態に係る半導体装置検査用プローブカードについて図2から図15を用いて説明する。

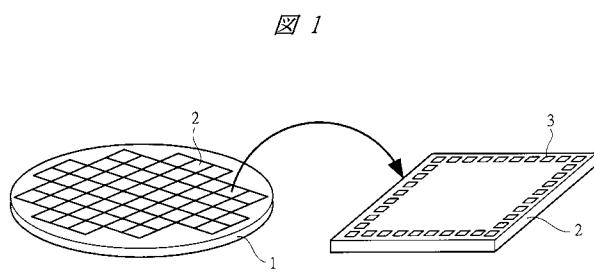

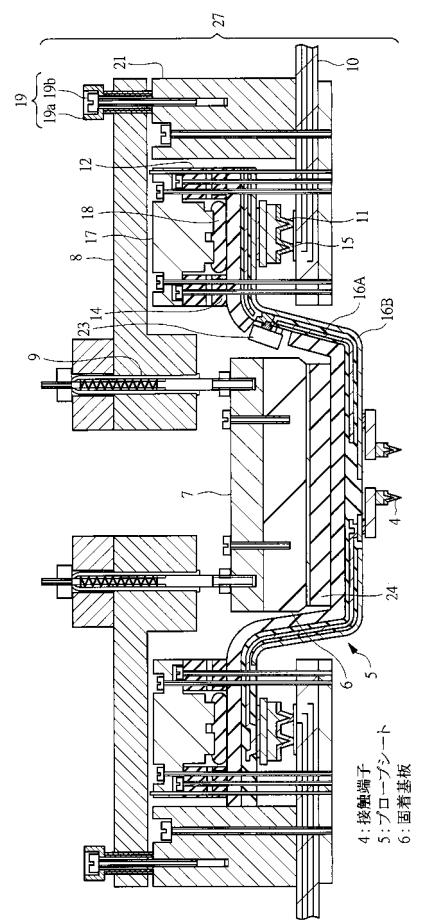

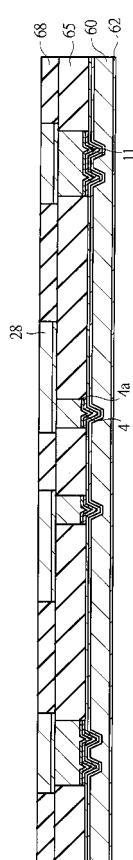

#### 【 0 0 6 7 】

##### ( 実施の形態 1 )

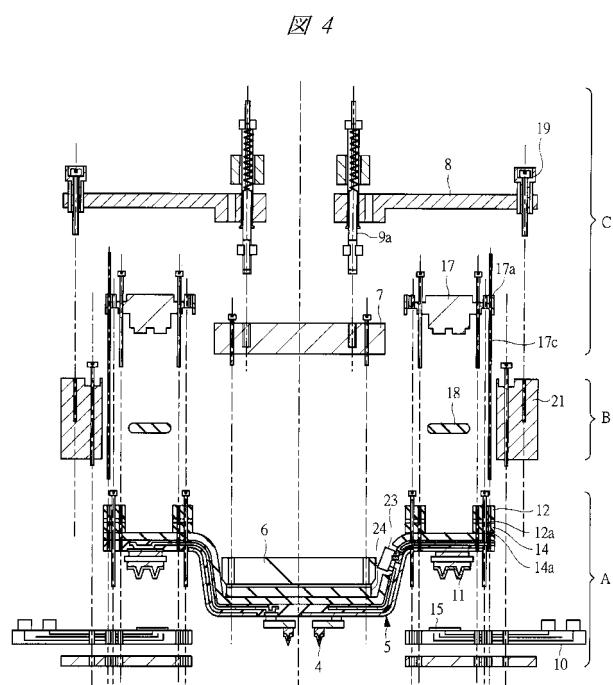

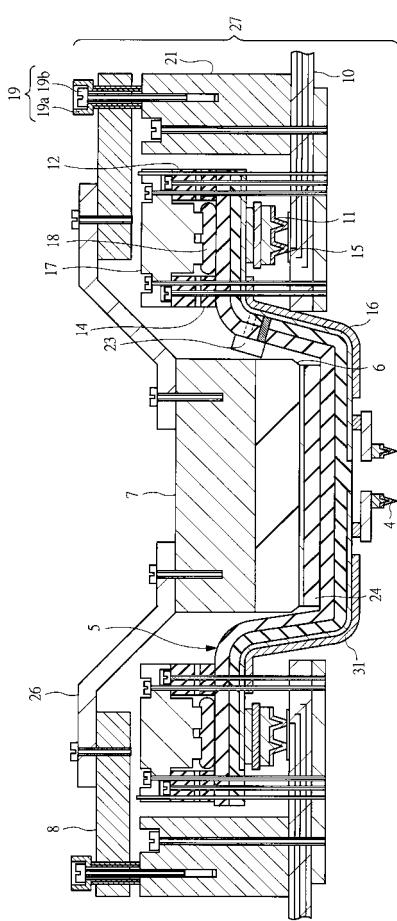

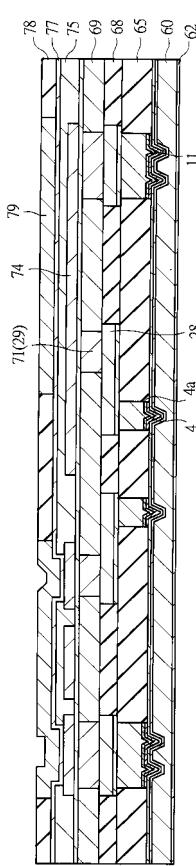

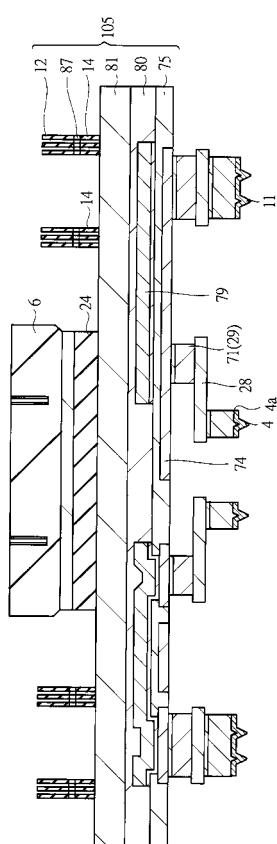

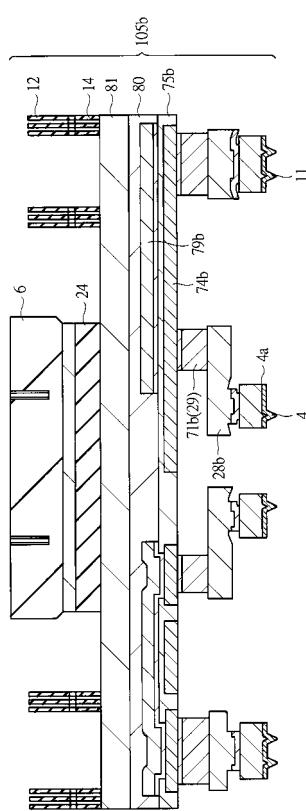

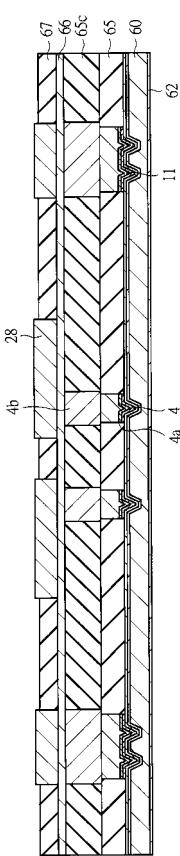

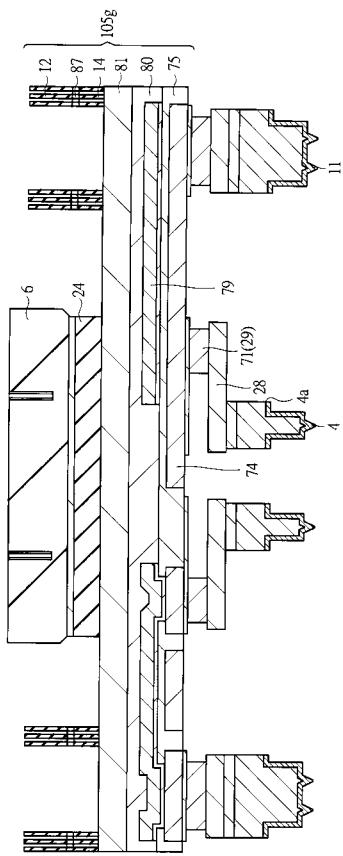

図2は本実施の形態1のプローブカードの要部を示す断面図であり、図3は図2に示した主要部品を分解して図示した斜視図であり、図4は図2に示した主要部品を分解して図示した組み立て断面図である。これらの図を用いて本実施の形態1のプローブカードについて説明する。

20

#### 【 0 0 6 8 】

本実施の形態1のプローブカードは、接触端子4群が形成されたプローブシート5、固着基板6、中間板7、支持部材(上部固定板)8に挿入されて中間板7にねじ止めされたガイドピン9等から構成される。

#### 【 0 0 6 9 】

プローブシート5は、シートのプローピング(正面(第1の面))側の中央領域部に半導体素子2の電極3群と接触するための上記接触端子4群が形成されている。また、プローブシート5の4辺の周辺部には、多層配線基板10との信号授受のための、周辺電極11群が形成され、その周辺電極11群を囲むように周辺電極固定板12に対応した領域に金属膜14が形成されている。詳しくは後述するが、周辺電極11群は、上記接触端子4群と同一工程で形成されるものであり、その先端が多層配線基板10の電極15に接続されている。また、接触端子4群と周辺電極11群との間には、図3に示した多数の引き出し配線16が形成されている。詳細は後述するが、接触端子4群および周辺電極11群を形成する個々の接触端子は、角錐形状あるいは角錐台形状となっている。

30

#### 【 0 0 7 0 】

更に、信号授受のための上記周辺電極11群が形成された部分のプローブシート5の裏面の金属膜14には、上記周辺電極固定板12が接着固定されている。

40

#### 【 0 0 7 1 】

金属膜14には、位置決め用のノックピン用孔14aおよびねじ挿入用孔14bをエッチングでパターン形成しておき、周辺電極固定板12および周辺押さえ板17にも、それぞれ位置決め用のノックピン用孔12a、17aおよびねじ挿入用孔12b、17bを形成しておくことにより、組立性を向上することができる。

#### 【 0 0 7 2 】

周辺電極11群を囲むようにしてプローブシート5に固着した周辺電極固定板12に対し、上記ノックピン用孔17aを用いてノックピン17cにて位置決めしながら緩衝材18を挟んで周辺押さえ板17をねじ止めすることにより、緩衝材18を介して周辺電極11群は多層配線基板10の電極15に接続される。

50

## 【0073】

なお、支持部材8に設けた傾斜微調節用のダブルねじ19、あるいは、後述するスペーサ20(図7参照)を用いて、接触端子4群が形成された領域のプローブシート5の傾きを微調整してもよい。ここで、ダブルねじ19は、外側のねじ19aの中央に別の中ねじ19bが形成されたものであり、外側のねじ19aで、支持部材8と上板21との間隔を調整することにより、両者の傾斜を微調整した後、中ねじ19bでねじ止め固定する構造のものである。

## 【0074】

また、プローブシート5中には、必要に応じて検査用の高速電気信号の乱れを少なくするために、基準電位(接地電位)に電気的に接続するグランド用の引き出し配線16Aと、信号用および電源用の引き出し配線16Bとが形成されている。これら引き出し配線16A、16Bは、前述の引き出し配線16を構成するものである。このような引き出し配線16A、16Bについては、プローブシート5の製造工程中において、フォトリソグラフィ技術を用いてお互いの間の配置状態および形状を設計および製作することで、インピーダンス整合やシールド構造を形成することができる。

10

## 【0075】

また、プローブシート5の裏面には、チップコンデンサ23が取り付けられている。このチップコンデンサ23は、プローブシート5中に形成された配線を介して接触端子4群中の所定の接触端子と電気的に接続されている。このようなチップコンデンサ23は、接触端子4の近くに配置して、信号の乱れを極力防止したい場合に効果を奏する。

20

## 【0076】

固着基板6は、プローブシート5の接触端子4群が形成された領域と平面で重なるようにプローブシート5の裏面(第2の面)に金属膜24を介して接着固定されている。詳細は後述するが、この金属膜24は、前述の金属膜14と同一の材質であり、かつ同一の工程で形成およびパターニングされるものである。さらに固着基板6には、中間板7がねじ止めされている。

## 【0077】

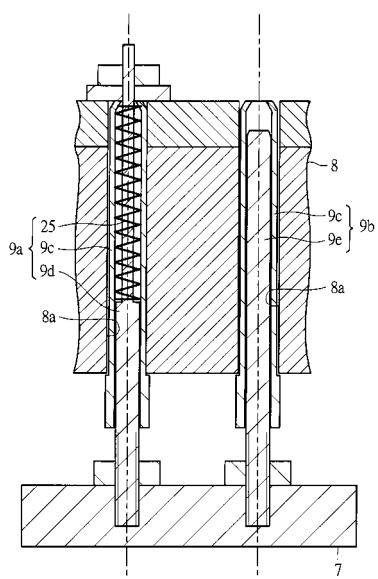

ガイドピン9は、支持部材(上部固定板)8に挿入されて上記中間板7にねじ止めされている。また、ガイドピン9は、プロービング検査時に、接触端子先端の位置ずれを極力防止するためと、接触端子4群が形成された領域を、被検査対象の電極3群の面に合わせるための平行出し機構としての役割とを有している。すなわち、ガイドピン9は、接触端子4群が形成された領域が微傾した状態で動作(微傾動)可能な状態で、後述する片持ち梁構造の撓みによる接触端子4の押し付け力と同程度か、それより小さなほぼ一定の押し付け力(例えば、500ピン程度の場合、押し込み量100μm程度で5~10N程度)を実現するために、図5に示すようなスプリング25を内蔵したスプリング内蔵ガイドピン9aおよび位置決め専用ガイドピン9bが用いられる構成となっている。これら複数のスプリング内蔵ガイドピン(枠に押し付け力を付与する複数の手段)9aおよび複数の位置決め専用ガイドピン9bは、支持部材8に挿入され、中間板7にねじ止め固定されて用いられる。また、スプリング内蔵ガイドピン9aは、金属製のチューブ9c内に上記スプリング25および中軸9dを内蔵し、スプリング25の弾性力によって中軸9dが中間板7を押圧する構造となっており、位置決め専用ガイドピン9bは、金属製のチューブ9c内に中軸9eを内蔵し、中軸9eが中間板7に固定されることによって位置決めを行う構造となっている。ガイドピン9は、少なくとも3本配置するものであり、好ましくは4本以上配置する。また、支持部材8においてガイドピン9が挿入される挿入孔8aは、接触端子先端の位置ずれを防止するために、挿入後のガイドピン9との間での隙間(遊び)が極力ないことが好ましく、本実施の形態1では、挿入孔8aの径はガイドピン9の径より10μm~20μm程度だけ大きくすることを例示できる。

30

## 【0078】

上記のような種々の部材により本実施の形態1のプローブカード27が形成される。

40

## 【0079】

50

上記のような本実施の形態 1 によれば、プローブシート 5 を複数のガイドピン 9（ばね性を有するスプリング内蔵ガイドピン 9 a および位置決め専用ガイドピン 9 b）で位置決めすると同時に、押し付け力を付与する構成とすることにより、押圧荷重を広範囲に制御した狭ピッチで多ピンの半導体検査用プローブカードを実現できる。半導体素子 2 内の高集積化が進むと、高密度多ピンかつ狭ピッチの電極 3 を半導体素子 2 表面に形成するため、電極 3 直下に多数の能動素子あるいは微細な配線が形成されていることが多くなり、半導体素子 2 の検査時の接触端子 4 群の電極 3 群への接触圧が大き過ぎると、電極 3 およびその直下の能動素子や配線に損傷を与えるおそれがあるが、本実施の形態 1 の半導体検査用プローブカードでは押圧荷重を広範囲に制御できるので、そのような能動素子や配線の損傷を防ぐことができる。

10

## 【0080】

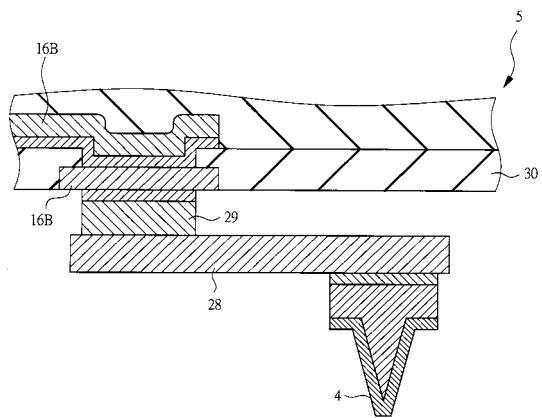

ここで、図 6 は、プローブシート 5 における 1 つの接触端子 4 付近を拡大して示した要部断面図である。本実施の形態 1 における接触端子 4 は、フォトリソグラフィ技術を用いてパターニングされた金属の梁 2 8 の先端付近に接続され、その梁 2 8 の他端付近では、接触端子 4 が接続された面とは反対側の面に金属のポスト 2 9 が接続している。ポスト 2 9 は、ポリイミド膜 3 0 に埋め込まれるように形成された引き出し配線 1 6 B に接続され、梁 2 8 は、ポリイミド膜 3 0 と離間した状態となっている。すなわち、梁 2 8 は、ポスト 2 9 との接続のみによってプローブシート 5 に支持される構造（以降、片持ち梁構造と記す）となっている。このような梁 2 8 の先端付近に配置された接触端子 4 は、梁 2 8 のしなりによって個別に動作させることが可能となる。それにより、接触が不十分な接触端子 4 と電極 3 とを完全に接触させるためにさらに大きな接触荷重が不要となる。

20

## 【0081】

ところで、半導体素子 2 の表面の電極 3 群の面と、プローブシート 5 における接触端子 4 群の面とは、傾きが生じていることも予想される。本実施の形態 1 では、中間板 7、固定基板 6、金属膜 2 4 およびプローブシート 5 が、接触端子 4 群が形成された領域を微傾動可能とした状況下で押圧動作を行うことを可能とし、接触が不十分な接触端子 4 と電極 3 とを完全に接触させるためのさらに大きな接触荷重を不要としている。さらに、前述したように、接触端子 4 を梁 2 8 のしなりによって個別に動作させることによっても、接触が不十分な接触端子 4 と電極 3 とを完全に接触させるための更なる接触荷重を不要としているので、接触端子 4 群と電極 3 群との接触圧が部分的に過大となってしまうことを防止しつつ、接触端子 4 群と接触対象の電極 3 群と確実に接触させることができる。その結果、プローピングによる電極 3 の表面の荒れを可能な限り防止することができるので、低荷重でも安定した接触特性、すなわち安定な接触抵抗値が確保できるようになる。

30

## 【0082】

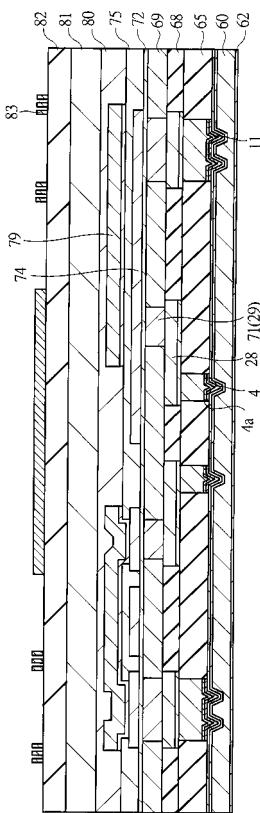

## （実施の形態 2）

図 7 は、本実施の形態 2 のプローブカードの要部を示す断面図である。

## 【0083】

前記実施の形態 1 では、プローブシート 5 の平行出し機構としてガイドピン 9（スプリング内蔵ガイドピン 9 a および位置決め専用ピン 9 b）を用いたが、図 7 に示すように、ガイドピン 9 の代わりに 1 つ以上の板ばね 2 6 を用いて微傾動可能な構造を形成してもよい。また、初期の傾斜微調節用に、ダブルねじ 1 9 の代わりにスペーサ 2 0 を用いてもよい。このスペーサ 2 0 あるいは前記実施の形態 1 で説明したダブルねじ 1 9 は、必要に応じて使用すればよいものであり、省略してもよいことはいうまでもない。

40

## 【0084】

また、図 7 および前記実施の形態 1 における図 2 では、プローブシート 5 において、接触端子 4 群が形成された面とは反対の面に接触端子 4 群および周辺電極 1 1 群が形成された領域と平面で重なるように金属膜 2 4、1 4 を配置した例について示したが、必要な接触端子 4 および周辺電極 1 1 の先端位置精度に応じて、金属膜 2 4 あるいは金属膜 1 4 の一方、もしくは両者を省略してもよい。

## 【0085】

50

上記のような本実施の形態 2 によっても、前記実施の形態 1 と同様の効果を得ることができる。

【0086】

(実施の形態3)

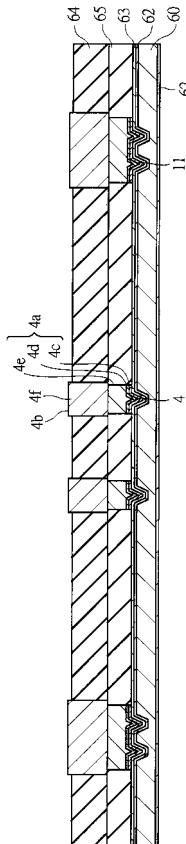

図8は、本実施の形態3のプローブカードの要部を示す断面図である。

【0087】

図8に示すように、本実施の形態3のプローブシート5は、片持ち梁構造の接触端子4からの引き出し配線16を一層で形成し、接触端子4が形成された面をポリイミドの保護膜31で保護した構造となっている。

【0088】

また、図8では、高速電気信号の乱れを少なくするために、信号用、電源用およびグランド用に一層で形成した引き出し配線16のうちの電源用の引き出し配線16とグランド用の引き出し配線16との間に、チップコンデンサ23を配置した例を示したが、必要に応じて省略してもよい。

【0089】

また、図8では、プローブシート5において、接触端子4群が形成された面とは反対の面に接触端子4群および周辺電極11群が形成された領域と平面で重なるように金属膜24、14を配置した例について示したが、必要な接触端子4および周辺電極11の先端位置精度に応じて、金属膜24あるいは金属膜14の一方、もしくは両者を省略してもよい。

10

【0090】

上記のような本実施の形態3によっても、前記実施の形態1、2と同様の効果を得ることができる。

20

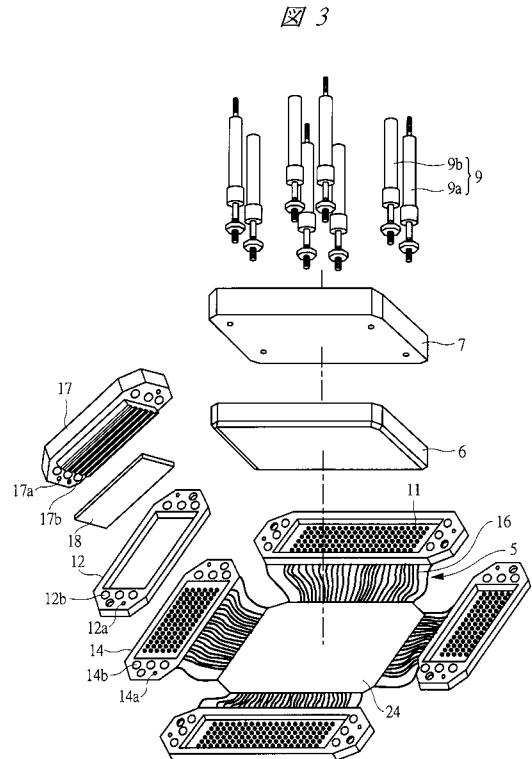

【0091】

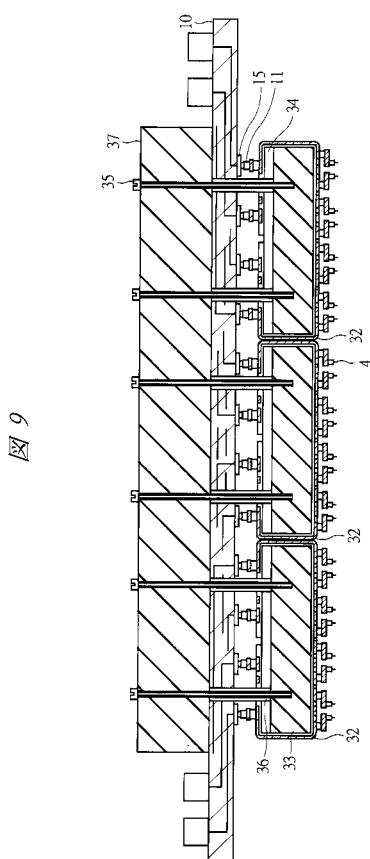

(実施の形態4)

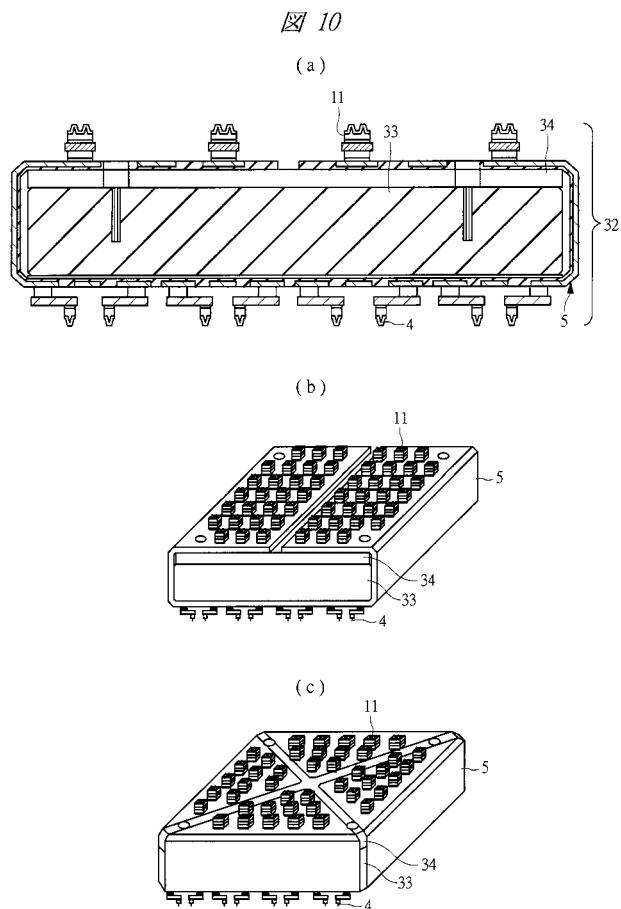

図9は、本実施の形態4のプローブカードの要部を示す断面図である。また、図10(a)は、図9に示した本実施の形態4のプローブカードの構成要素である1個のブロック32を示す断面概略図である。本実施の形態4は、必要な個数のこれらブロック32を多層配線基板10に取り付けて、一体のプローブカードとして用いる例である。

【0092】

図10(a)に示すブロック32を製作するに当たっては、図10(b)に示すように、固着基板33に対し、複数の片持ち梁構造の接触端子4を形成したプローブシート5を、接触端子4群が形成された面とは反対の面を対向させ、固着基板33の上面の対向する2辺から覆うように固着基板33の裏面に回し、緩衝材34を挟んで固着する構成を例示できる。このように固着基板33および緩衝材34に固着されたプローブシート5の裏面の周辺電極11群を多層配線基板10の電極15群に位置決めピン(図示せず)で位置合わせし、多層配線基板10を貫通するスペーサ36を介して、固着基板33と上押さえ板37とを固定ねじ35でねじ止め固定することにより、図9に示した複数のブロック32を用いたプローブカードを構成できる。

30

【0093】

また、図10(a)に示すブロック32を製作するに当たっては、図10(c)に示すように、固着基板33に対し、複数の片持ち梁構造の接触端子4を形成したプローブシート5を、接触端子4群が形成された面とは反対の面を対向させ、固着基板33の上面の4辺から覆うように固着基板33の裏面に回し、緩衝材34を挟んで固着する構成としてもよい。このような構成の場合でも、固着基板33および緩衝材34に固着されたプローブシート5の裏面の周辺電極11群を多層配線基板10の電極15群に位置決めピン(図示せず)で位置合わせし、多層配線基板10を貫通するスペーサ36を介して、固着基板33と上押さえ板37とを固定ねじ35でねじ止め固定することにより、図9に示した複数のブロック32を用いたプローブカードを構成できる。

40

【0094】

50

なお、必要に応じて、プローブシート5の接触端子4群が形成された面とは反対の面において、引き出し配線に必要な電子部品（コンデンサ、抵抗器、ヒューズおよびコネクタ等）を配置および搭載することにより、安定した検査や回路を形成してもよい。

#### 【0095】

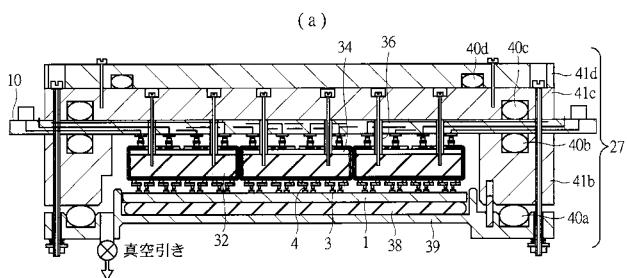

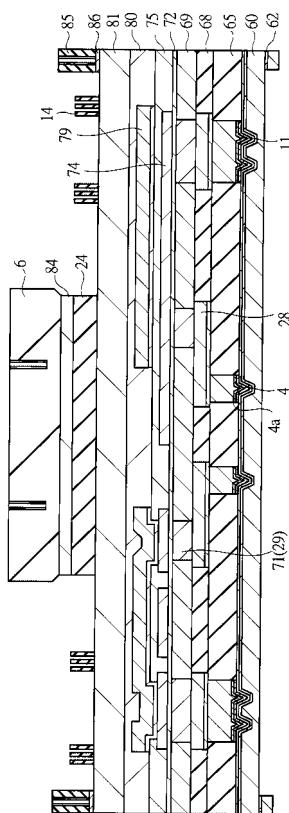

（実施の形態5）

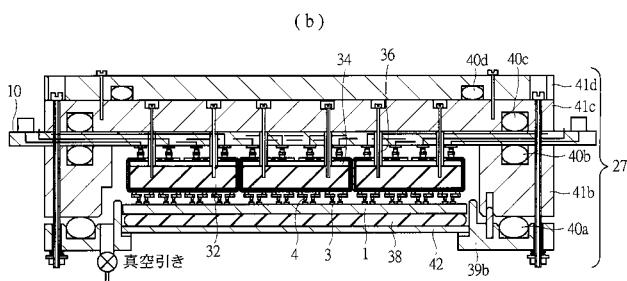

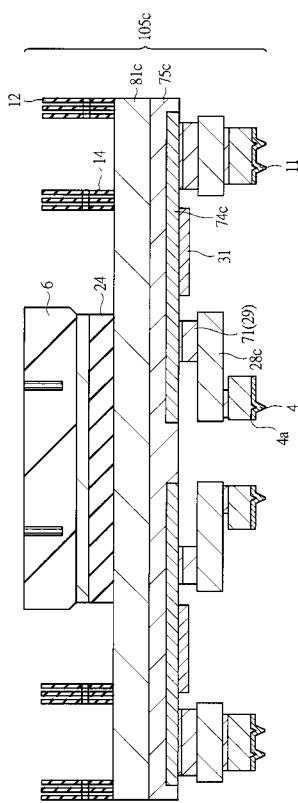

図11は、本実施の形態5のプローブカードの要部を示す断面図である。

#### 【0096】

本実施の形態5では、前記実施の形態4において説明したブロック32（図9および図10参照）を複数取り付けたプローブカード（図9参照）と同等な構成とし、接触端子4群と、緩衝材38を敷いたウエハ搭載台39に搭載したウエハ1の電極3群とを位置合わせして、ウエハ搭載台39に嵌合されたOリング40a、下基板41bに嵌合されたOリング40b、中基板41cに嵌合されたOリング40c、および上基板41dに嵌合されたOリング40dで密閉する。このような状況下で、ウエハ搭載台39と多層配線基板10との間を減圧することにより、適度な大気圧を利用して接触端子4群とウエハ1の電極3群とを大面積でも確実に接触させ、フルウェハ検査用の検査装置をウエハカセットとして構成することが可能となる。

10

#### 【0097】

また、図11（b）に示すように、上記ウエハ搭載台39を用いる代わりに、ウエハ搭載台39bに周囲を固着した柔軟性のあるウエハ搭載膜42（例えば、ポリイミドシート）用いた構成とし、ウエハ搭載膜42上に緩衝材38を介してウエハ1を搭載し、このような状況下で、ウエハ搭載膜42と多層配線基板10との間を減圧することにより、適度な大気圧を利用して接触端子4群とウエハ1の電極3群とを大面積でも確実に接触させ、フルウェハ検査用の検査装置をウエハカセットとして構成することが可能となる。

20

#### 【0098】

なお、フルウェハ検査用の検査装置の構成として、上記密閉構造は任意であり。また、接触端子4群とウエハ1の電極群3とが確実に接触すれば、減圧機構なしのウエハカセット構造でもよいことはいうまでもない。

20

#### 【0099】

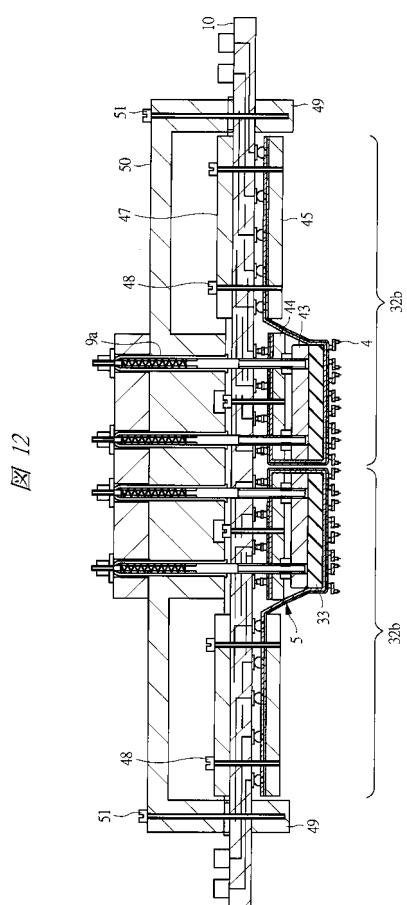

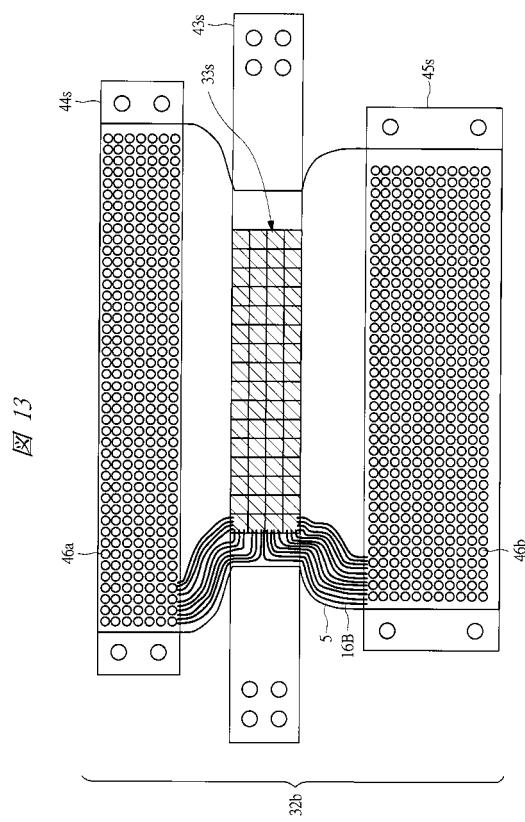

（実施の形態6）

図12は、本実施の形態6のプローブカードの要部を示す断面図である。図13は、本実施の形態6のプローブカードの構成要素である1個のブロック32bに取り付けられるプローブシート5の展開図である。図13には、プローブシート5に対する、固着基板33の固着位置33s（斜線を付した部分）、ブロック吊り板43の固着位置43s、固着基板直上シート押さえ板44の固着位置44s、および基板下面シート押さえ板45の固着位置45sについても図示している。

30

#### 【0100】

固着基板33は、プローブシート5に対して、接触端子4が形成された面とは反対側の面の接触端子形成対応領域に固着される。固着基板直上シート押さえ板44も、固着基板33と同様に、プローブシート5に対して、接触端子4が形成された面とは反対側の面に固着され、その固着位置は、多層配線基板10の基板電極に対応した配線ピッチ拡大パッド（第1の周辺電極）46aが形成された領域である。この配線ピッチ拡大パッド46aは、プローブシート5の形成時に接触端子4と同一の工程で形成される端子であり、プローブシート5において接触端子4と同一面に形成され、接触端子4より形成ピッチが広くなっている。一方、基板下面シート押さえ板45は、プローブシート5に対して、接触端子4が形成された面に固着され、その固着位置は、多層配線基板10の基板電極に対応した配線ピッチ拡大パッド（第2の周辺電極）46bが形成された領域である。この配線ピッチ拡大パッド46bは、プローブシート5において接触端子4とは反対側の面に形成され、接触端子4より形成ピッチが広くなっている。

40

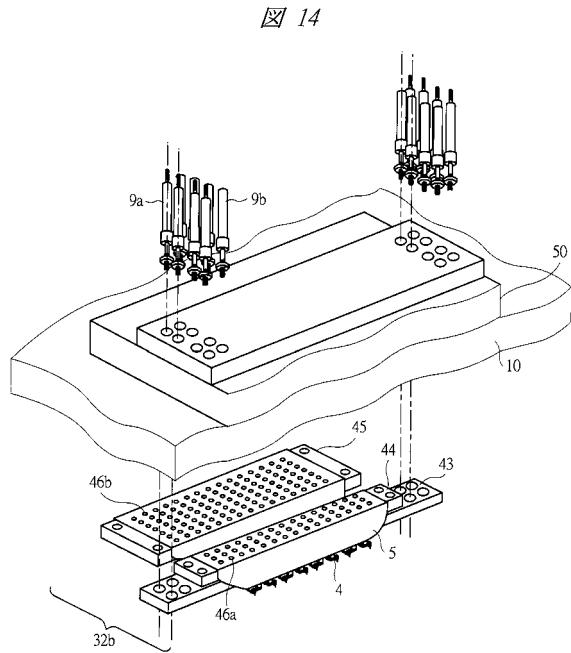

#### 【0101】

図14は、図12および図13に示したブロック32bの多層配線基板10への取り付

50

け例を斜視図で示したものである。

**【0102】**

本実施の形態6では、プローブシート5と固着する各々の基板（固着基板33、固着基板直上シート押さえ板44および基板下面シート押さえ板45）を上記のような構成とし、引き出し配線16Bのピッチは、組立状態を考慮して接触端子4を形成したプローブシート5上で拡大することで、多層配線基板10の通常の基板電極の形成ピッチまでプローブシート5の周辺電極（配線ピッチ拡大パッド46a、46b）のピッチを拡大している。それにより、多数チップ同時検査用プローブカードのように多ピンかつ狭ピッチで配線が形成される場合でも、プローブシート5の周辺電極と多層配線基板10の基板電極間との電極パッドピッチ拡大用の中間基板を省略することができる。すなわち、プローブカードを形成する部品点数を低減できることから、部品間の接触部を減らすことができ、組み立ても容易となる。

10

**【0103】**

なお、図12に示した例は、図14に示したプロック32bを2個用いてプローブカードを構成した例である。

**【0104】**

プロック32bを製作するに当たっては、固着基板33とプロック吊り板43とを一体として加工形成してもよい。また、片持ち梁構造の接触端子4で、検査時の接触端子4部のストロークを確保できる場合は、個々のプロック32bをプロック間固定板で固定して、一体プロックとして用いてもよい。

20

**【0105】**

プローブシート5の周辺電極と対応する多層配線基板10の基板電極とを位置合わせした状態で、プローブシート5および多層配線基板10を基板下面シート押さえ板45と基板上面押さえ板47とで挟み、固定ねじ48でこれらをねじ止め固定することにより、プローブシート5の周辺電極（配線ピッチ拡大パッド46a、46b）と対応する多層配線基板10の基板電極とを電気的に接続する。また、多層配線基板10は、下押さえ板49と上押さえ板50とで挟み、固定ねじ51でねじ止め固定することにより、本実施の形態6のプローブカードを形成することができる。なお、平行出し機構としてのスプリング内蔵ガイドピン9aおよび接触端子4の先端の位置ずれ防止用の位置決め専用ガイドピン9bは、上押さえ板50を貫通し、上押さえ板50の上面で固定される構成となっている。

30

**【0106】**

（実施の形態7）

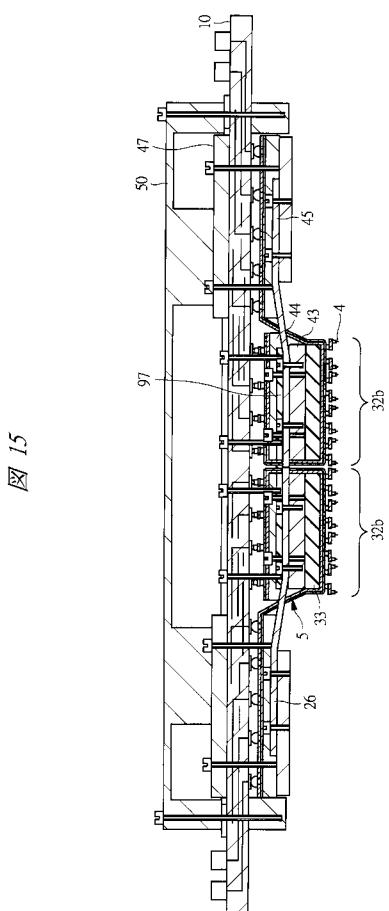

図15は、本実施の形態7のプローブカードの要部を示す断面図である。

**【0107】**

図15に示すように、本実施の形態7では、前記実施の形態6で用いているスプリング内蔵ガイドピン9a（図12参照）の代わりに板ばね26を用い、複数のプロック32bをプロック間固定基板97に取り付けて、一体プロックとしている。

30

**【0108】**

上記のような本実施の形態7によっても、前記実施の形態6と同様の効果を得ることができる。

40

**【0109】**

（実施の形態8）

次に、前記実施の形態1～7で説明したプローブカードにて用いられるプローブシート（プローブシート構造体）の一例について、その製造方法を図16～図28を参照して説明する。なお、以降のプローブシートを形成する各部材は、図2～図15に示した前記実施の形態1～7のプローブカードの要部断面図中にも適宜示されている。

**【0110】**

図16～図28は、前記実施の形態1において図2に示したプローブカードを形成するための製造プロセスのうち、特に、シリコンウエハに異方性エッ칭で形成した角錐台形状の穴を型材として用いて、角錐台形状の接触端子4、梁28（図6参照）および引き

50

出し配線 16 用の配線材料をポリイミド膜(絶縁シート)に一体で形成する工程や、その表面にポリイミド膜および配線材料を形成し、さらに固着基板 6 を固着する工程等の製造プロセスを工程順に示したものである。

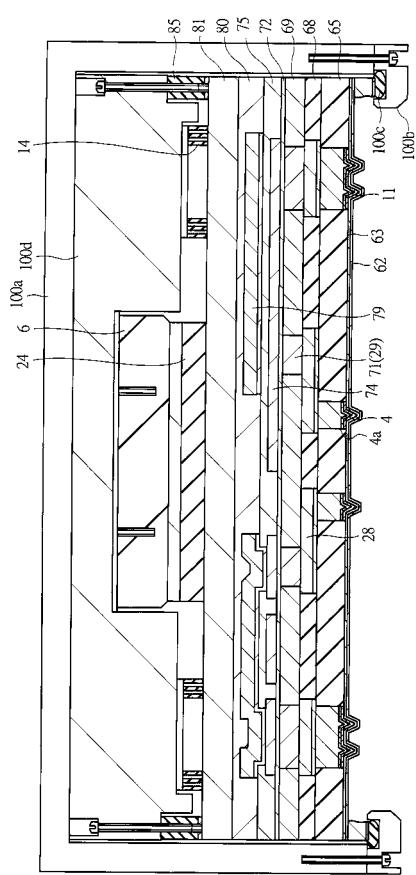

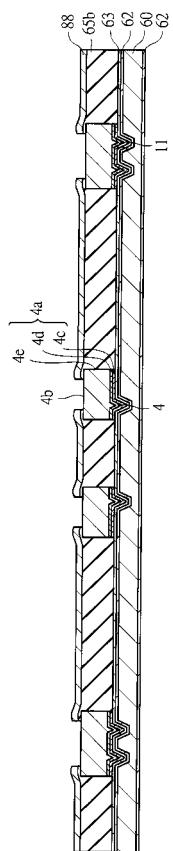

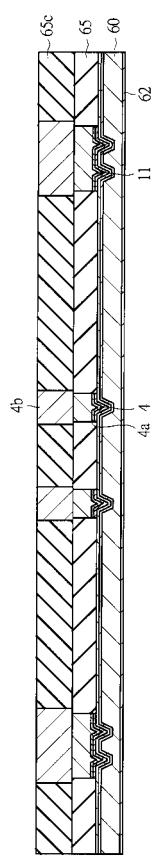

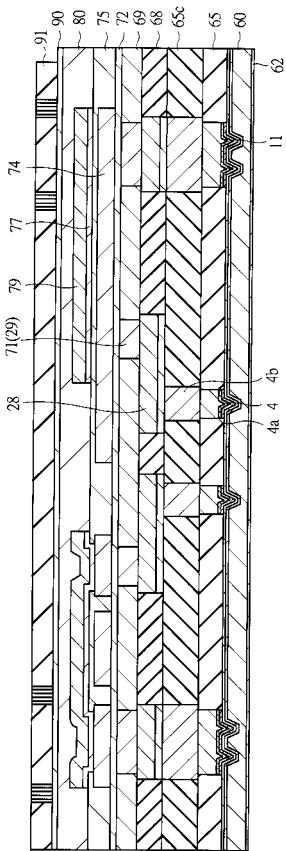

#### 【0111】

まず、図 16 に示す工程が実行される。この工程は、厚さ 0.2 ~ 0.6 mm のシリコンウエハ 60 の(100)面の両面に熱酸化により二酸化シリコン膜 61 を 0.5 μm 程度形成し、フォトレジストを塗布し、フォトリソグラフィ工程により角錐台形状の穴 60a を開ける位置のフォトレジストを除去したパターンを形成する。次いで、そのフォトレジストをマスクとし、二酸化シリコン膜 61 をフッ酸とフッ化アンモニウムの混合液によりエッチング除去して、前記二酸化シリコン膜 61 をマスクとして、シリコンウエハ 60 を強アルカリ液(例えば、水酸化カリウム)により異方性エッチングして、(111)面および(100)面に囲まれた角錐台形状のエッチング穴 60a を形成する。

#### 【0112】

ここで、本実施の形態 8 では、シリコンウエハ 60 を型材としたが、型材としては、結晶性を有するものであればよく、その範囲で種々変更可能であることは言うまでもない。また、本実施の形態 8 では、異方性エッチングによる穴を角錐台形状としたが、その形状は、角錐状でもよく、小さな針圧で安定した接触抵抗を確保できる程度の接触端子 4 を形成できる形状の範囲で、種々変更可能である。また、接触対象とする 1 つの電極に、複数の接触端子 4 で接触するようにしてもよいことはいうまでもない。

#### 【0113】

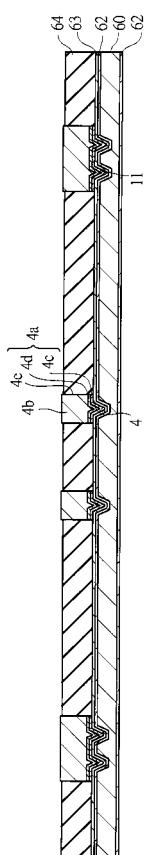

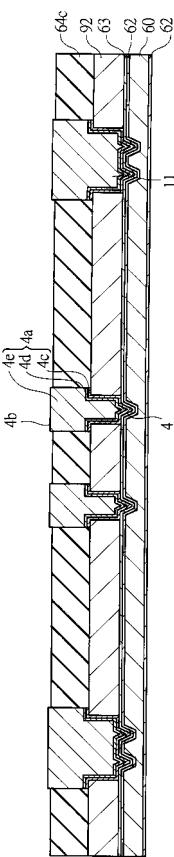

次に、図 17 に示す工程が実行される。この工程では、マスクとして用いた二酸化シリコン膜 61 をフッ酸とフッ化アンモニウムの混合液によりエッチング除去して、再度ウェット酸素中の熱酸化により、シリコンウエハ 60 の全面に二酸化シリコン膜 62 を 0.5 μm 程度形成する。次いで、その二酸化シリコン膜 62 の表面に導電性被覆 63 を形成し、次にその導電性被覆 63 の表面に、接触端子 4 部を開口するようにフォトレジストマスク 64 を形成する。

#### 【0114】

次に、そのフォトレジストマスク 64 をマスクとし、上記導電性被覆 63 を給電層として、硬度の高い材料を主成分として電気めっきして、接触端子 4 および接続電極部 4b を一体として形成する。この時、接触端子 4 と同様の構造の周辺電極 11 が形成される。硬度の高いめっき材料として、例えば、ニッケル 4c、ロジウム 4d およびニッケル 4e を順次めっきして接触端子 4 および接続電極部 4b を一体として接触端子部 4a を形成すればよい。フォトレジストマスク 64 としては、液状レジストでもフィルム状レジスト(ドライフィルム)でもよい。

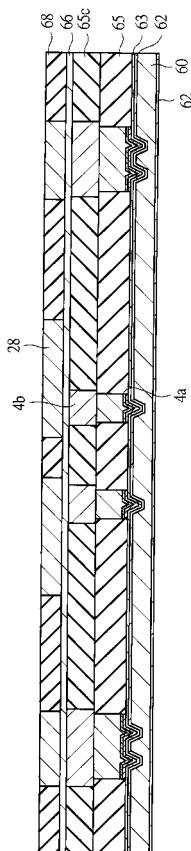

#### 【0115】

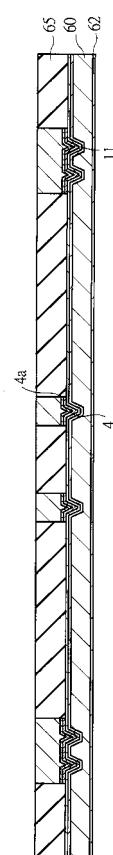

次に、図 18 に示す工程が実行される。この工程は、上記フォトレジストマスク 64 を除去した後、上記接触端子部 4a および導電性被覆 63 を覆うようにポリイミド膜 65 を形成し、上記接触端子部 4a の表面がポリイミド膜 65 より露出するように平坦に研磨するものである。ポリイミド膜 65 の表面および接触端子部 4a の表面の研磨には、例えば CMP (Chemical Mechanical Polishing)、あるいは研磨シートを用いた研磨加工を例示できる。

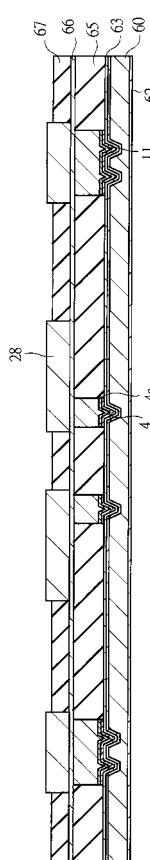

#### 【0116】

次に、図 19 に示す工程が実行される。この工程は、ポリイミド膜 65 に導電性被覆 66 を形成し、フォトレジストマスク 67 を形成した後、梁 28 をめっきするものである。導電性被覆 66 としては、例えば、クロムをスパッタリング法あるいは蒸着法により成膜することにより、厚さ 0.1 μm 程度のクロム膜を形成し、そのクロム膜を形成した表面に銅をスパッタリング法あるいは蒸着法により成膜することにより、厚さ 1 μm 程度の銅膜を形成すればよい。また、梁 28 の材料としては、例えば銅めっきにニッケルめっきを施した材料、あるいはニッケルコバルトめっき等を用いればよい。フォトレジストマスク 67 としては、フォトレジストマスク 64 と同様に液状レジストでもフィルム状レジスト

10

20

30

40

50

(ドライフィルム)でもよい。

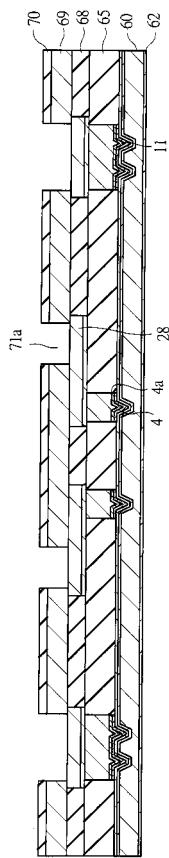

【0117】

次に、図20に示す工程が実行される。この工程は、上記フォトレジストマスク67を除去した後、上記導電性被覆66を梁28のめっき膜をマスクとしてソフトエッチングした後、梁28およびポリイミド膜65を覆うようにポリイミド膜68を形成し、梁28の表面がポリイミド膜68より露出するように平坦に研磨するものである。ポリイミド膜68の表面および梁28の表面を研磨するには、例えばCMP、あるいは研磨シートを用いた研磨加工を例示できる。

【0118】

次に、図21に示す工程が実行される。この工程は、上記梁28およびポリイミド膜68を覆うようにポリイミド膜69を形成した後、表面にアルミニウムマスク70を形成して、引き出し配線接続用穴71aを形成すべき位置にあるポリイミド膜69を梁28の表面に至るまでエッチング除去するものである。

【0119】

上記引き出し配線接続用穴71aを形成するに当たっては、アルミニウムマスク70をエッチングマスクとして、ドライエッチングあるいはレーザーエッチングを用いればよい。また、アルミニウムマスク70の形成を省略して、直接にレーザー穴開け加工して引き出し配線接続用穴71aを形成してもよい。

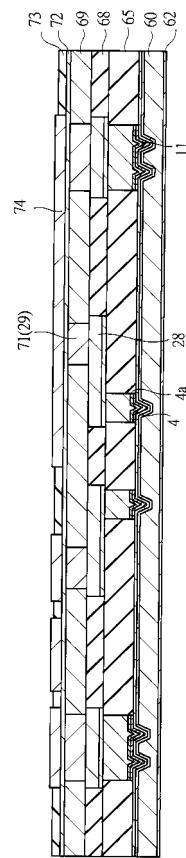

【0120】

次に、図22に示す工程が実行される。この工程は、上記アルミニウムマスク70を除去した後、引き出し配線接続用穴71aをめっき71で充填し、さらに導電性被覆72を形成し、フォトレジストマスク73を形成した後、配線材料74をめっきするものである。

【0121】

上記導電性被覆72としては、例えば、クロムをスパッタリング法あるいは蒸着法によって成膜することにより、厚さ0.1μm程度のクロム膜を形成し、そのクロム膜を形成した表面に銅をスパッタリング法あるいは蒸着法により成膜することにより、厚さ1μm程度の銅膜を形成すればよい。なお、その銅膜に数μm厚の銅をめっきで形成して、穴開け加工の耐性を増してもよい。また、配線材料74としては、銅めっきあるいは銅めっきにニッケルめっきを施した材料を用いればよい。フォトレジストマスク73としては、フォトレジストマスク64、67と同様に液状レジストでもフィルム状レジスト(ドライフィルム)でもよい。

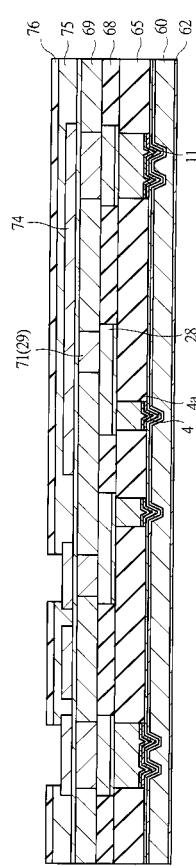

【0122】

次に、図23に示す工程が実行される。この工程は、上記フォトレジストマスク73を除去し、ポリイミド膜75を形成し、アルミニウムマスク76を形成した後、配線材料74と上部の配線材料79(図24を用いて後述)との接続用の穴を形成すべき位置にあるポリイミド膜75を、上記配線材料74の表面に至るまで除去するものである。

【0123】

ポリイミド膜75を配線材料74の表面に至るまで除去するに当たっては、アルミニウムマスク76をエッチングマスクにしたドライエッチングあるいはレーザーエッチングを用いればよい。また、アルミニウムマスク76の形成を省略して、直接レーザー穴開け加工を施してもよい。

【0124】

次に、図24に示す工程が実行される。この工程は、上記アルミニウムマスク76を除去した後、ポリイミド膜75に導電性被覆77を形成し、フォトレジストマスク78を形成した後、配線材料79をめっきするものである。

【0125】

導電性被覆77としては、例えばクロムをスパッタリング法あるいは蒸着法により成膜することによって厚さ0.1μm程度のクロム膜を形成し、そのクロム膜を形成した表面に銅をスパッタリング法あるいは蒸着法により成膜することにより、厚さ1μm程度の銅

10

20

30

40

50

膜を形成すればよい。また、配線材料 7 9 としては、銅めっき、あるいは銅めっきにニッケルめっきを施した材料を用いればよい。フォトレジストマスク 7 8 としては、フォトレジストマスク 6 4、6 7、7 3 と同様に液状レジストでもフィルム状レジスト(ドライフィルム)でもよい。

#### 【0126】

引き出し配線 1 6 となる配線材料 7 4、7 9 を二層構造とするのは、例えば、配線材料 7 4 をグランド用配線(引き出し配線 1 6 A)とし、配線材料 7 9 を信号用および電源用配線(引き出し配線 1 6 B)として、配線材料 7 4、7 9 間でマイクロストリップ構造を形成してインピーダンスを整合し、高速電気信号の乱れを極力防止するためである。また、狭ピッチかつ多ピンに配置された接触端子 4 群からの周辺電極 1 1 群への引き出し配線 1 6 を二層構造とする目的は、引き出し配線 1 6 の形成を容易にし、加えて、微細配線の引き回しを避けて配線幅を広くすることにより、配線抵抗値を低くして電圧降下を少なくするとともに、電流容量を確保するためでもある。

10

#### 【0127】

なお、必要に応じて、配線材料 7 9 の形成を省略して、配線材料 7 4 のみの一層としてもよいことは言うまでもない。

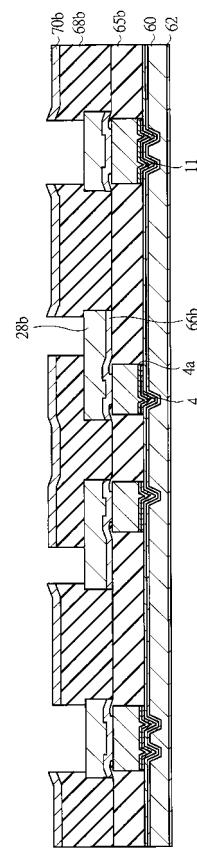

#### 【0128】

次に、図 2 5 に示す工程が実行される。この工程は、上記フォトレジストマスク 7 8 を除去し、配線材料 7 9 をマスクとして導電性被覆 7 7 をソフトエッチング除去した後、ポリイミド膜 8 0 を形成し、そのポリイミド膜 8 0 に接着層 8 1 および金属膜 8 2 を接着し、その金属膜 8 2 に所望のパターンを形成するためのフォトレジストマスク 8 3 を形成するものである。

20

#### 【0129】

ここで、接着層 8 1 としては、例えばポリイミド系接着シート、あるいはエポキシ系接着シートを用いればよい。また、金属膜 8 2 としては、4 2 アロイ(ニッケル 4 2 % および鉄 5 8 % の合金で線膨張率 4 ppm / )あるいはインバー(例えば、ニッケル 3 6 % および鉄 6 4 % の合金で線膨張率 1 . 5 ppm / )の様な線膨張率で、かつシリコンウエハ(シリコン型材) 6 0 の線膨張率に近い金属シートを、接着層 8 1 でポリイミド膜 8 0 に貼り合わせて構成する。それにより、形成されるプローブシート 5 の強度向上および大面積化が図れる他、検査時の温度による位置ずれ防止等、様々な状況下での位置精度確保が可能となる。この主旨において、金属膜 8 2 としては、バーンイン検査時の位置精度確保を狙い、検査対象の半導体素子の線膨張率に近い線膨張率の材料を用いてもよい。

30

#### 【0130】

上記接着工程は、例えば、接触端子部 4 a およびポリイミド膜 8 0 を形成したシリコンウエハと、接着層 8 1 および金属膜 8 2 とを重ね合わせて、1 0 ~ 2 0 0 K gf / cm<sup>2</sup> 程度で加圧しながら接着層 8 1 のガラス転移点温度(Tg)以上の温度を加え、真空中で加熱加圧接着すればよい。なお、金属膜 8 2 に所望のパターンを形成するためのフォトレジストマスク 8 3 としては、フォトレジストマスク 6 4、6 7、7 3、7 8 と同様に液状レジストでもフィルム状レジスト(ドライフィルム)でもよい。

40

#### 【0131】

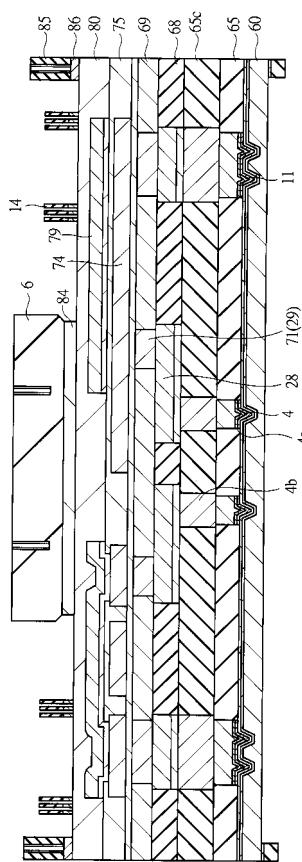

次に、図 2 6 に示す工程が実行される。この工程は、上記フォトレジストマスク 8 3 をマスクとして金属膜 8 2 をエッチングして所望の金属膜 1 4、2 4 のパターンを形成した後、次の工程(図 2 7 参照)の前処理として、金属膜 1 4、2 4 のパターンを形成した接着層 8 1 の面を保護フィルムで覆い、反対側の面においては、シリコンエッチング用保護治具のふた 1 0 0 b(詳しくは図 2 7 を用いて後述)より露出する領域の二酸化シリコン膜 6 2 を、中央を割り抜いた保護フィルムをマスクとしてフッ酸とフッ化アンモニウムの混合液によりエッチング除去する。続いて、その保護フィルムを剥離した後、接触端子 4 群を形成した領域に対応する金属膜 2 4 に接着材 8 4 で接着基板 6 を接着固定し、シリコンエッチング用保持リング 8 5 を前記接着層 8 1 に対して接着材 8 6 で接着するものである。

50

## 【0132】

金属膜82として42アロイシートあるいはインバーシートを用いた場合には、金属膜14、24のパターンを形成するためのエッチングは、塩化第二鉄溶液を用いたスプレー エッティングとすることを例示できる。

## 【0133】

次に、図27に示す工程が実行される。この工程はシリコンエッティング用保護治具を取り付けて、シリコンウエハ60をエッティング除去するものである。例えば、中間固定板100dに、前記シリコンエッティング用保持リング85をねじ止めし、ステンレス製の固定治具100aとステンレス製のふた100bとをOリング100cを介して装着し、型材であるシリコンウエハ60を強アルカリ液（例えば、水酸化カリウム）によりエッティング除去する。10

## 【0134】

次に、図28に示す工程が実行される。この工程では、上記シリコンエッティング用保護治具（固定治具100a、ふた100b、Oリング100cおよび中間固定板100d）を取り外し、シリコンエッティング用保持リング85に対して片面を覆うように保護フィルムを接着し、二酸化シリコン膜62、導電性被覆63（クロムおよび銅）およびニッケル4cをエッティング除去する。続いて、その保護フィルムを除去した後、導電性被覆72をストップバーとしてポリイミド膜65、68、69をエッティング除去し、さらに不要な導電性被覆72を除去する。次いで、金属膜14に周辺電極固定板12を接着材87で接着し、その周辺電極固定板12および接着基板6の外周部に沿って、ポリイミド膜75、80および接着層81を切り出し、プローブシート構造体105を製作するものである。なお、上記の切り出したプローブシート構造体105を、プローブカードに組み立てる工程の説明図は、前記実施の形態1において、図3に斜視図で、図4に断面図で示している。20

## 【0135】

図28に示した工程において、二酸化シリコン膜62はフッ酸およびフッ化アンモニウムの混合液によりエッティング除去することができ、クロム膜は過マンガン酸カリウム液によりエッティング除去することができ、銅膜およびニッケル膜4cはアルカリ性銅エッティング液によりエッティング除去することができる。この一連のエッティング処理によって接触端子4の表面にはロジウム4d露出するが、このようにロジウム4dが接触端子4の表面となることにより、接触端子4には電極3（図1参照）の材料であるはんだやアルミニウム等が付着し難くなる。また、ロジウム4dは、ニッケルより硬度が高く、酸化され難いことから、接触端子4の接触抵抗を安定なものとすることができます。30

## 【0136】

（実施の形態9）

次に、前記実施の形態8で説明したプローブシート構造体105の製造工程とは若干異なる本実施の形態9のプローブシート構造体の製造方法について、図29～図32を参照して説明する。

## 【0137】

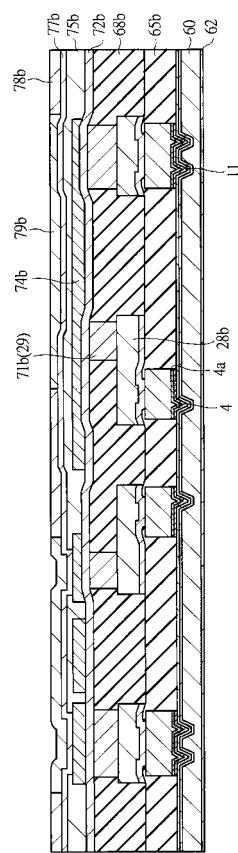

図29～図32は、本実施の形態9のプローブシートを形成する製造プロセスを工程順に示したものである。40

## 【0138】

製造方法の基本は、前記実施の形態8にて図16～図28を用いて説明した製造方法に準じたものであるが、研磨工程を一切省略した製法となっている。なお、必要に応じて、前記実施の形態8にて説明した研磨工程を導入してもよいことは言うまでもない。

## 【0139】

まず、図29に示す工程が実行される。この工程は、前記実施の形態8において図16および図17に示した工程と同様の工程を経て、接触端子部4aを形成した後、フォトレジストあるいはドライフィルム64（図17参照）を除去して、ポリイミド膜65bを形成する。次いで、ポリイミド膜65bの表面にアルミニウムマスク88を形成し、次の工程で形成される梁28bと接触端子部4aとの電気的接続位置となる接触端子部4a上の50

ポリイミド膜 65 b を、接触端子部 4 a の表面に至るまで除去する。

【0140】

ポリイミド膜 65 b を除去するには、例えば、アルミニウムマスク 88 をエッティングマスクとしたドライエッティングあるいはレーザーエッティングを行えばよい。また、アルミニウムマスク 88 の形成を省略して、直接レーザー穴開け加工を施して所望の位置のポリイミド膜 65 b を除去してもよい。

【0141】

次に、図 30 に示す工程が実行される。この工程は、前記実施の形態 8 において図 19 および図 20 に示した工程と同様の工程を経て、ポリイミド膜 65 b 上に導電性被覆 66 b を形成し、フォトレジストマスクを形成した後、梁 28 b をめっきで形成する。その後、フォトレジストマスクを除去した後、梁 28 b のめっき膜をマスクとして導電性被覆 66 b をソフトエッティングした後、梁 28 b およびポリイミド膜 65 b を覆うようにポリイミド膜 68 b を形成する。次いで、ポリイミド膜 68 b の表面にアルミニウムマスク 70 b を形成し、引き出し配線接続用穴（ポスト）を形成すべき位置にあるポリイミド膜 68 b を、梁 28 b の表面に至るまでエッティング除去するものである。

10

【0142】

導電性被覆 66 b としては、例えば、クロムをスパッタリング法あるいは蒸着法により成膜することによって厚さ 0.1 μm 程度のクロム膜を形成し、そのクロム膜の表面に銅をスパッタリング法あるいは蒸着法により成膜することによって厚さ 1 μm 程度の銅膜を形成すればよい。また、梁の材料としては、例えば、銅めっきにニッケルめっきを施した材料、あるいはニッケルコバルトめっき等を用いればよい。引き出し配線接続用穴（ポスト）を形成するに当たっては、アルミニウムマスク 70 b をエッティングマスクとしたドライエッティングあるいはレーザーエッティングを用いればよい。また、アルミニウムマスク 70 b の形成を省略して、直接レーザー穴開け加工を施して引き出し配線接続用穴を形成してもよい。

20

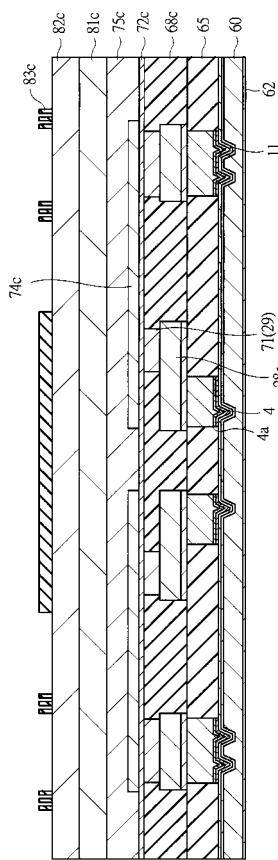

【0143】

次に、図 31 に示す工程が実行される。この工程は、前記実施の形態 8 において図 22 および図 23 に示した工程と同様の工程を経て、アルミニウムマスク 70 b を除去した後、引き出し配線接続用穴をめっき 71 b で充填し、さらに導電性被覆 72 b を形成する。次いで、導電性被覆 72 b 上にフォトレジストマスクを形成し、配線材料 74 b をめっきする。次いで、フォトレジストマスクを除去し、ポリイミド膜 75 b を形成した後に、ポリイミド膜 75 b の表面にアルミニウムマスクを形成し、配線材料 74 b 上に形成される配線材料 79 b と配線材料 74 bとの接続用の穴を形成すべき位置にあるポリイミド膜 75 b を、配線材料 74 b の表面に至るまで除去する。その後、そのアルミニウムマスクを除去した後、ポリイミド膜 75 b の表面に導電性被覆 77 b を形成し、フォトレジストマスク 78 b を形成し、配線材料 79 b をめっきするものである。

30

【0144】

次に、前記実施の形態 8 において図 25 ~ 図 27 に示した工程と同様な工程を経て、図 32 に示す本実施の形態 9 のプローブシート構造体 105 b を製作するものである。

40

【0145】

（実施の形態 10）

次に、本実施の形態 10 のプローブシートの製造方法について、図 33 ~ 図 35 を参照して説明する。図 33 ~ 図 35 は、本実施の形態 10 のプローブシートを形成する製造プロセスを工程順に示したものである。

【0146】

本実施の形態 10 では、片持ち梁構造のポストからの引き出し配線を一層で形成し、ポリイミドの保護膜を片持ち梁構造の接触端子形成面に形成したプローブシート 5 となる。なお、図 33 ~ 図 35 では、研磨工程のない場合を示すが、必要に応じて研磨工程を導入してもよいことは言うまでもない。

【0147】

50

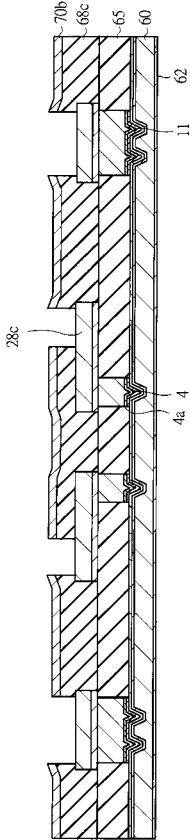

まず、図33に示す工程が実行される。この工程は、前記実施の形態8において図16～図19に示した工程と同様な工程を経て、接触端子部4aを形成した後、フォトレジストマスク67あるいはドライフィルムを除去して、ポリイミド膜68cを形成する。次いで、ポリイミド膜68cの表面にアルミニウムマスク70bを形成し、梁28c上に形成される配線材料と梁28cとを接続する位置にあるポリイミド膜68cを、梁28bの表面に至るまでエッティング除去するものである。

#### 【0148】

次に、図34に示す工程が実行される。この工程は、上記アルミニウムマスク70bを除去した後、引き出し配線接続用穴をめっき71bで充填し、さらに導電性被覆72cを形成する。次いで、フォトレジストマスクを形成した後、配線材料74cをめっきする。その後、フォトレジストマスクを除去し、ポリイミド膜75cを形成し、そのポリイミド膜75cに接着層81cおよび金属膜82cを接着し、その金属膜82c上に所望のパターンを形成するためのフォトレジストマスク83cを形成するものである。

#### 【0149】

次に、前記実施の形態8において図26～図28に示した工程と同様の工程を経た後、図35に示すように、配線間の短絡あるいは配線面の保護のために、必要に応じてポリイミドの保護膜31（前記実施の形態3および図8も参照）を片持ち梁構造の接触端子形成面に形成し、プローブシート構造体105cを組み立て、図8に示したプローブカードを作成する。

#### 【0150】

なお、高速伝送信号の安定化のために、図8に示したように、必要に応じてグランド用の引き出し配線16と電源用の引き出し配線16との間にコンデンサ23を配置および搭載してもよい。

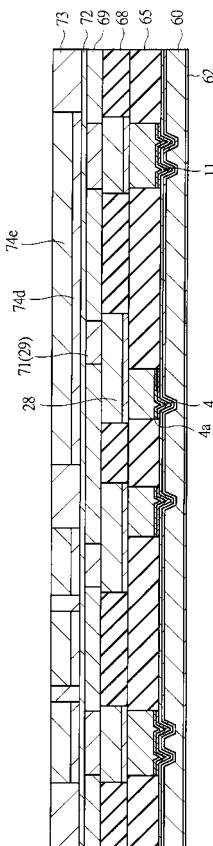

#### 【0151】

##### （実施の形態11）

次に、本実施の形態11のプローブシートの製造方法について、図36および図37を参照して説明する。図36および図37は、本実施の形態11のプローブシートを形成する製造プロセスを工程順に示したものである。

#### 【0152】

本実施の形態11は、ポスト（片持ち梁の土台の嵩上げ部）29と引き出し配線との間に、梁のたわみによる応力が加わることを考慮して、補強のために、ポスト29と接続する配線材料（引き出し配線16）を、例えば、銅とニッケルとの二層構造にして補強した例である。ポスト29と配線材料との接続部の補強は、図36および図37に示すように配線材料全体でもよいし、部分的に補強してもよい。

#### 【0153】

まず、図36に示すように、前記実施の形態8において図16～図21に示した工程と同様な工程を経た後、図22に示した工程の段階で、配線材料74の部分を、銅74dおよびニッケル74eのめっきの二層構造にする。

#### 【0154】

その後、前記実施の形態8において図23～図27に示した工程と同様の工程を経て、図37に示すプローブシート構造体105dを製作する。

#### 【0155】

なお、補強材料としては、ニッケル合金またはパラジウム合金等の合金材料、あるいは、タンゲステンのような金属材料を用いてもよい。

#### 【0156】

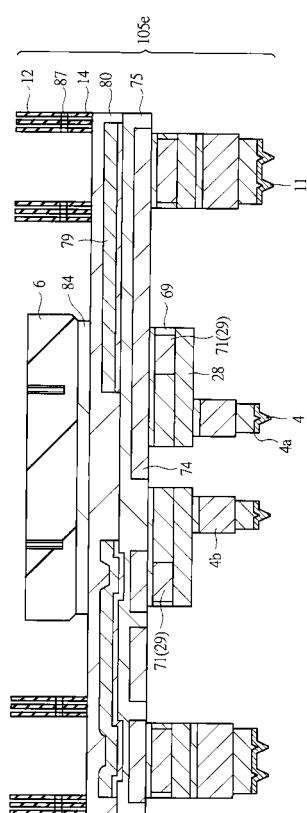

##### （実施の形態12）

次に、前記実施の形態8で説明したプローブシート構造体105の製造工程とは若干異なる本実施の形態12のプローブシート構造体の製造方法について、図38～図43を参照して説明する。

#### 【0157】

10

20

30

40

50

図38～図43は、本実施の形態12のプローブシートを形成する製造プロセスを工程順に示したものである。

#### 【0158】

製造方法の基本は、前記実施の形態8にて図16～図28を用いて説明した製造方法に準じたものであるが、ポリイミド膜65、65cの2層の犠牲層にして、接触端子部4aの高さを増加させ、ポリイミド膜65、65c、68、69をエッチング除去する際に、梁28の金属材料をマスクとして、梁28の裏面のポリイミド膜を残すようにした製法の例である。なお、要求仕様に応じて、ポリイミド膜65cの犠牲層を省略したり、研磨工程を省略したり、梁28の裏面のポリイミド膜69を除去してもよいことは言うまでもない。

10

#### 【0159】

まず、図38に示す工程が実行される。この工程では、前記実施の形態8において図16～図18に示した工程と同様の工程を経て接触端子部4aを形成した後、ポリイミド膜65にフォトレジストマスク64を形成し、導電性被覆63を給電層として、硬度の高い材料を主成分として電気めっきして2層目の金属材料4fを形成することにより、接続電極部4bを接触端子部4aと一緒に形成する工程が実行される。なお、フォトレジストマスク64としては、液状レジストでもフィルム状レジスト（ドライフィルム）でもよい。2層目の金属材料4fとしては、例えばニッケルめっきを用いればよい。

20

#### 【0160】

次に、図39に示す工程が実行される。この工程は、上記フォトレジストマスク64を除去した後、上記接続電極部4bを覆うようにポリイミド膜65cを形成し、接続電極部4bの表面がポリイミド膜65cより露出するように、ポリイミド膜65cを平坦に研磨するものである。ポリイミド膜65cの表面および接続電極部4bの表面を研磨するには、例えば、CMP、あるいは研磨シートを用いた研磨加工を用いればよい。

20

#### 【0161】

次に、図40に示す工程が実行される。この工程は、前記実施の形態8において図19に示した工程と同様にポリイミド膜65c上に導電性被覆66を形成し、さらにフォトレジストマスク67を形成した後、梁28をめっきするものである。

30

#### 【0162】

次に、図41に示す工程が実行される。この工程は、前記実施の形態8において図20～図24に示した工程と同様な工程を経て、フォトレジストマスク78を除去した後、配線材料79をマスクとして導電性被覆77をソフトエッチング除去する。次いで、ポリイミド膜80を形成し、そのポリイミド膜80上に導電性被覆90を形成し、所望の周辺パターンを形成するためのフォトレジストマスク91を形成するものである。フォトレジストマスク91としては、液状レジストでもフィルム状レジスト（ドライフィルム）でもよい。

30

#### 【0163】

次に、図42に示す工程が実行される。この工程は、上記導電性被覆90を給電層として電気めっきして、金属膜14のパターンを形成し、フォトレジストマスク91を除去した後、金属膜14のパターンをマスクとして導電性被覆90をソフトエッチング除去する。その後、次の工程の前処理として、金属膜14のパターンが形成されたポリイミド膜80の面を保護フィルムで覆い、反対側の面においては、シリコンエッチング用保護治具のふた100b（図27参照）より露出する領域の二酸化シリコン膜62を、中央を割り抜いた保護フィルムをマスクとしてフッ酸とフッ化アンモニウムの混合液によりエッチング除去する。続いて、その保護フィルムを剥離した後、接触端子4群を形成した領域に対応するポリイミド膜80に接着材84で接着基板6を接着固定し、シリコンエッチング用保持リング85をポリイミド膜80に接着するものである。

40

#### 【0164】

導電性被覆90としては、例えば、クロムをスパッタリング法あるいは蒸着法により成膜することにより、厚さ0.1μm程度のクロム膜を形成し、そのクロム膜を形成した表

50

面に銅をスパッタリング法あるいは蒸着法により成膜することにより、厚さ 1 μm 程度の銅膜を形成すればよい。また、金属膜 14 としては、例えば、ニッケルめっきあるいは銅めっき等を用いて形成すればよい。

#### 【0165】

次に、前記実施の形態 8 において図 27 および図 28 に示した工程と同様の工程を経て、図 43 に示す本実施の形態 12 のプローブシート構造体 105e を製作するものである。

#### 【0166】

本実施の形態 12 では、梁 28 の金属材料をマスクとして、梁 28 の裏面のポリイミド膜を残すようにポリイミド膜 65、65c、68、69 をエッチング除去した例を示している。これらのポリイミド膜の除去は、例えば、ドライエッチングあるいはレーザー加工を用いればよい。ここで、ポリイミド膜 69 の一部を残すことにより、片持ち梁構造の接触端子の強度および弾性率を確保することができる。なお、ポスト 29 が完全に露出するようにポリイミド膜を除去してもよいことは言うまでもない。

10

#### 【0167】

なお、図 38～図 43 に示した製造工程では、プローブシート周辺の金属膜 14 のパターン材料としてめっき材料を用い、接触端子 4 群を形成した領域に対応するポリイミド膜 80 に接着材 84 で直接固着基板 6 を接着固定した例を示したが、前記実施の形態 1 において図 16～図 28 で示した接着層 81 および金属膜 82 を用いてもよいことは言うまでもない。

20

#### 【0168】

(実施の形態 13)

次に、前記実施の形態 8 で説明したプローブシート構造体 105 の製造工程とは若干異なる本実施の形態 13 のプローブシート構造体の製造方法について、図 44 および図 45 を参照して説明する。

#### 【0169】

図 44 および図 45 は、本実施の形態 13 のプローブシートを形成する製造プロセスを工程順に示したものである。

#### 【0170】

製造方法の基本は、前記実施の形態 8 にて図 16～図 28 を用いて説明した製造方法と前記実施の形態 12 にて図 38～図 43 を用いて説明した製造方法とに準じたものであるが、ポリイミド膜 65、65c のみをエッチング除去して、他のポリイミド膜を残すようにした製法の例である。なお、要求仕様に応じて、ポリイミド膜 65c の犠牲層を省略したり、研磨工程を省略したりしてもよいことは言うまでもない。

30

#### 【0171】

まず、図 44 に示す工程が実行される。この工程は、前記実施の形態 12 において図 38～図 40 に示した工程と同様の工程を経てフォトレジストマスク 67 を除去した後、導電性被覆 66 を残したまま接続電極部 4b を覆うようにポリイミド膜 68 を形成し、接続電極部 4b の表面がポリイミド膜 68 より露出するように平坦に研磨するものである。ポリイミド膜 68 の表面および接続電極部 4b の表面の研磨には、例えば、CMP あるいは研磨シートを用いた研磨加工を用いればよい。

40

#### 【0172】

次に、図 45 に示す工程が実行される。この工程は、前記実施の形態 12 において図 41～図 42 に示した工程と同様の工程を経て、図 45 に示すプローブシート構造体 105f を製作するものである。

#### 【0173】

本実施の形態 13 では、ポリイミド膜 65、65c のみをエッチング除去した例を示している。これらのポリイミド膜の除去には、例えば、ドライエッチング、アルカリ液エッチング、レーザー加工あるいは酸素プラズマエッチング等の手段を用いればよい。ここで、ポリイミド膜 68 および 69 を残すことにより、片持ち梁構造の接触端子の強度および

50

弾性率を確保することができる。

【0174】

(実施の形態14)

次に、前記実施の形態8で説明したプローブシート構造体105の製造工程とは若干異なる本実施の形態14のプローブシート構造体の製造方法について、図45～図49を参照して説明する。

【0175】

図46～図49は、本実施の形態14のプローブシートを形成する製造プロセスを工程順に示したものである。

【0176】

製造方法の基本は、前記実施の形態8にて図16～図28を用いて説明した製造方法に準じたものであるが、図18のポリイミド膜65の下部に更に金属層92を形成することにより、金属層92を犠牲層にして、接触端子部4aの高さを増加させ、金属層92およびポリイミド膜65、68、69を除去した製法の例である。なお、要求される仕様に応じて、研磨工程を省略したり、梁28の金属材料をマスクとして梁28の裏面のポリイミド膜69を残すようにしてもよいことは言うまでもない。

【0177】

まず、図46に示す工程が実行される。この工程では、前記実施の形態8において図16に示した工程と同様の工程を経て穴60aを形成する。

【0178】

次に、マスクとして用いた二酸化シリコン膜61をフッ酸とフッ化アンモニウムの混合液によりエッチング除去して、再度ウェット酸素中の熱酸化により、シリコンウエハ60の全面に二酸化シリコン膜62を0.5μm程度形成する。次いで、その二酸化シリコン膜62の表面に導電性被覆63を形成し、次にその導電性被覆63の表面に、接触端子部4aを形成する部分および周辺電極11を形成する部分にフォトレジストマスク64bを形成する。

【0179】

次に、そのフォトレジストマスク64bをマスクとし、上記導電性被覆63に金属材料を電気めっきして金属層92(犠牲層)を形成する。金属層92(犠牲層)とする金属材料としては、接触端子の材料に対して選択エッチング(エッチング選択比を有する)ができる金属を犠牲層として用いればよい。例えば、後の工程で形成する接触端子部4aにロジウム4dおよびニッケル4eからなる接触端子を形成した場合(図48参照)は、ニッケルおよびロジウムと選択エッチング性がある銅を犠牲層として用いればよい。フォトレジストマスク64bとしては、液状レジストでもフィルム状レジスト(ドライフィルム)でもよい。

【0180】

次に、図47に示す工程が実行される。この工程では、フォトレジストマスク64bを除去した後、フォトレジストを形成し、接触端子部4aを形成する部分および周辺電極11を形成する部分のフォトレジストを除去したフォトレジストマスク64cを形成する。フォトレジストマスク64cとしては、液状レジストでもフィルム状レジスト(ドライフィルム)でもよい。

【0181】

次に、図48に示す工程が実行される。この工程では、前記のフォトレジストマスク64cをマスクとし、上記導電性被覆63を給電層として、硬度の高い材料を主成分として電気めっきして、接触端子4および接続電極部4bを一体として形成する。この時、接触端子4と同様の構造の周辺電極11も形成される。硬度の高いめっき材料として、例えば、ニッケル4c、ロジウム4dおよびニッケル4eを順次めっきして接触端子4および接続電極部4bを一体として接触端子部4aを形成すればよい。

【0182】

次に、図49に示す工程が実行される。この工程は、前記実施の形態8において図18

10

20

30

40

50

～図24および図25～図27に示した工程と同様の工程を経て、図49に示す本実施の形態14のプローブシート構造体105gを製作するものである。

#### 【0183】

なお、図47では、接触端子部4aを形成する部分および周辺電極11を形成する部分のフォトレジストを除去したパターンを形成する例を示したが、フォトレジストマスク64bを残したまま前記のフォトレジストマスク64bおよび金属層92の表面にフォトレジストマスク64cを形成し、例えば、必要によってはアルミニウム膜マスクを形成した上で、ドライエッティングあるいはレーザー加工を用いて、所望の接触端子部4aを形成する部分および周辺電極11を形成する部分のフォトレジストマスク64cおよびフォトレジストマスク64bを除去してもよい。

10

#### 【0184】

また、図47では、フォトレジストマスク64bを除去した後、ポリイミド膜65を形成し、例えば、必要によってはアルミニウム膜マスクを形成した上で、ドライエッティングあるいはレーザー加工を用いて、所望の接触端子部4aを形成する部分および周辺電極11を形成する部分のポリイミド膜65を除去してもよい。

20

#### 【0185】

なお、図46～図49に示した製造工程では、接着層81および金属膜82を用いた例を示したが、本実施の形態14において、接着層81および金属膜82を省略して、プローブシート周辺の金属膜14のパターン材料としてめっき材料を用いてもよいことは言うまでもない。

#### 【0186】

##### (実施の形態15)

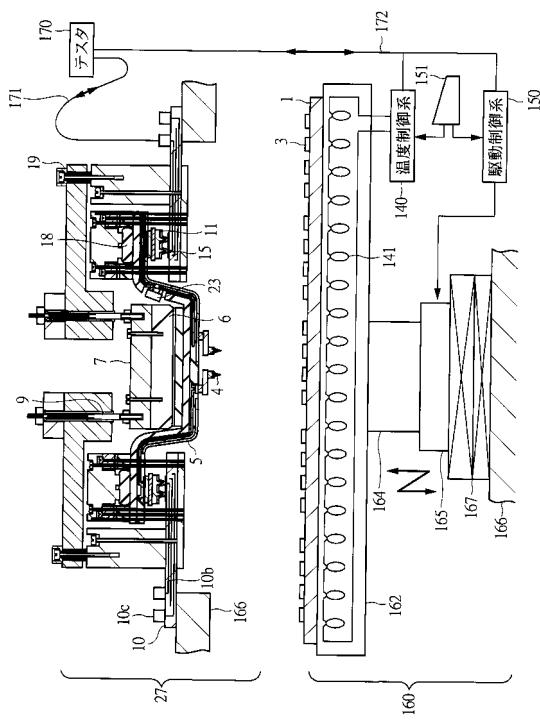

次に、以上説明した実施の形態1～14に係るプローブカード(プローピング装置)を用いた半導体検査装置について図50を用いて説明する。

#### 【0187】

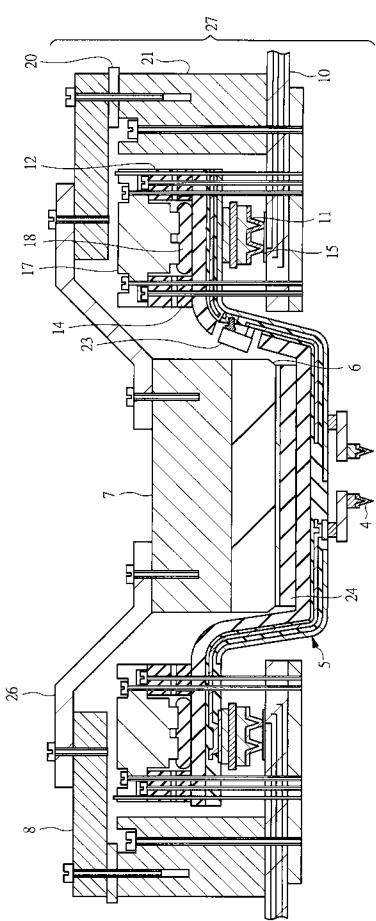

図50は、本実施の形態15に係る半導体検査装置を含む検査システムの全体構成を示す説明図であり、所望の接触荷重を、片持ち梁構造の接触端子4でウエハ1のそれぞれの電極3面に加えて電気特性検査を実施する試験装置を示している。

#### 【0188】

図50に示す状態では、スプリング内蔵ガイドピン9a(板ばね26(図示は省略)で代用してもよい)が、プローブカード27の接触端子4群の先端面とウエハ1の電極3面が倣うまでの荷重、およびその後のオーバードライブによる荷重増加を吸収することにより低荷重に保つ。このような状態で、個々の片持ち梁構造の押圧力(荷重)が片持ち梁構造の先端に形成された接触端子4に加わり、ウエハ1の電極3に接触した接触端子4、引き出し配線16(例えば、配線材料74、79)、周辺電極11、多層配線基板10の電極15、内部配線10bおよび電極10cを通じて半導体素子の電気的特性の検査を行うテスタ170との間で検査用電気信号の送受信が実施される。

30

#### 【0189】

検査システムの全体構成において、プローブカード27はウエハプローバとして構成されている。この検査システムは、被検査対象であるウエハ1を支持する試料支持系160と、被検査対象(ウエハ1)の電極3に接触して電気信号の授受を行うプローブカード27と、試料支持系160の動作を制御する駆動制御系150と、被検査対象の温度制御を行う温度制御系140と、半導体素子(チップ)2の電気的特性の検査を行うテスタ170とで構成される。ウエハ1には、多数の半導体素子(チップ)2が配列され、各半導体素子2の表面には、外部接続電極である複数の電極3が配列されている。試料支持系160は、ウエハ1を着脱自在に載置してほぼ水平に設けられた試料台162と、この試料台162を支持するように垂直に配置される昇降軸164と、この昇降軸164を昇降駆動する昇降駆動部165と、この昇降駆動部165を支持するX-Yステージ167とで構成される。X-Yステージ167は、筐体166の上に固定される。昇降駆動部165は、例えば、ステッピングモータなどから構成される。試料台162の水平および垂直方向

40

50

における位置決め動作は、X-Yステージ167の水平面内における移動動作と、昇降駆動部165による上下動などを組み合わせることにより行われる。また、試料台162には、図示しない回動機構が設けられており、水平面内における試料台162の回動変位を可能とされている。

#### 【0190】

試料台162の上方には、プローブ系（プローブカード27）が配置される。すなわち、前記実施の形態1において図2にも示したプローブカード27および多層配線基板10は、その試料台162に平行に対向する姿勢で設けられる。各々の接触端子4は、プローブカード27のプローブシート5に設けられた引き出し配線16（図2および図3参照）および周辺電極11を介して、多層配線基板10の電極15および内部配線10bを通じて多層配線基板10に設けられた電極10cに電気的に接続され、電極10cに接続されるケーブル171を介してテスタ170と電気的に接続される。

10

#### 【0191】

駆動制御系150は、ケーブル172を介してテスタ170と接続される。また、駆動制御系150は、試料支持系160の各駆動部のアクチュエータに制御信号を送って、その動作を制御する。すなわち、駆動制御系150は、内部にコンピュータを備え、ケーブル172を介して伝達されるテスタ170のテスト動作の進行情報に合わせて、試料支持系160の動作を制御する。また、駆動制御系150は、操作部151を備え、駆動制御に関する各種指示の入力の受付、例えば、手動操作の指示を受け付ける。

20

#### 【0192】

試料台162には、半導体素子2を加熱するためのヒータ141が備えられている。温度制御系140は、試料台162のヒータ141あるいは冷却治具を制御することにより、試料台162に搭載されたウエハ1の温度を制御する。また、温度制御系140は、操作部151を備え、温度制御に関する各種指示の入力の受付、例えば、手動操作の指示を受け付ける。ここで、上記プローブシート5あるいはプローブカード27の一部に設けた温度制御の可能な発熱体と試料台162のヒータ141とを連動させて温度制御してもよい。

20

#### 【0193】

以下、半導体検査装置の動作について説明する。まず、被検査対象であるウエハ1は、試料台162の上に位置決めして載置され、X-Yステージ167および回動機構を駆動制御し、ウエハ1上に配列された複数個の半導体素子2上に形成された電極3群を、プローブカード27に並設された多数の接触端子4群の直下に位置決めする。次いで、駆動制御系150は、昇降駆動部165を作動させて、被接触材である多数の電極3の全体の面が接触端子の先端に接触した時点から $10\sim100\mu m$ 程度押し上げる状態になるまで試料台162を上昇させることによって、プローブシート5において必要に応じてダブルネジ19あるいはシムによる微調整を実施して初期的に平坦度を高精度に確保された片持ち梁構造の先端に形成された個々の接触端子4群における各々の先端を、複数個のスプリング内蔵ガイドピン9aあるいは板ばね26による平行出し機構（押圧機構）により半導体素子2に配列された多数の電極3群（全体）の面に追従するように倣って平行出しだす。その後は、個々の片持ち梁構造のたわみによる荷重によってウエハ1上に配列された各被接触材（電極3）に倣って均一な荷重（1ピン当たり $3\sim150mN$ 程度）に基づく押し込みによる接触が行われ、各接触端子4と各電極3との間は低抵抗（0.01~0.1）で電気的に接続されることになる。

30

#### 【0194】

この場合の初期の押圧時には、スプリング内蔵ガイドピン9a（あるいは、板ばね26）により、接触端子4群が形成された領域の接触端子4側とは反対側の面に固着された固着基板6が傾動し、その固着基板6の反対側の面の接触端子4群の先端面が半導体素子2の電極3の群の面に追随するように倣って平行出しだす、個々の片持ち梁構造のたわみによる接触圧で、接触端子4の押し込みによる接触が行われる。

40

#### 【0195】

50

さらに、ケーブル 171、多層配線基板 10 および接触端子 4 を介して、ウエハ 1 に形成された半導体素子 2 とテスト 170との間で、動作電流や動作検査信号などの授受を行い、該当する半導体素子 2 の動作特性の可否などを判別する。さらに、上記の一連の検査動作が、ウエハ 1 に形成された複数の半導体素子 2 の各々について実施され、動作特性の可否などが判別される。

#### 【0196】

(実施の形態 16)

ここで、前記実施の形態 15 で説明した半導体検査装置を用いた検査工程、または検査方法を含む半導体装置の製造方法の一例について、図 51 を参照して説明する。

#### 【0197】

10

(1) 本実施の形態 16 に係る半導体装置の製造方法は、ウエハ 1 に回路を作り込み、半導体装置を形成する工程(半導体素子回路形成)と、前記実施の形態 15 で説明した半導体検査装置によりウエハレベルで複数の半導体装置の電気的特性を一括して検査する工程(ウエハ検査)と、ウエハ 1 を切断し、半導体素子 2 毎に分離する工程(ダイシング)と、半導体素子 2 を樹脂等で封止する工程(組立および封止)とを有する。その後、バーンイン、選別検査、および外観検査を経て、チップパッケージ品として出荷される。

#### 【0198】

20

(2) 本実施の形態 16 に係る半導体装置の製造方法は、ウエハ 1 に回路を作り込み、半導体素子を形成する工程(半導体素子回路形成)と、前記実施の形態 15 で説明した半導体検査装置によりウエハレベルで複数の半導体素子の電気的特性を一括して検査する工程(ウエハ検査)と、ウエハ 1 を切断し、半導体素子 2 毎に分離する工程(ダイシング)とを有する。その後、チップ検査用ソケット装着、バーンイン、選別検査、ソケットからの取り外し、および外観検査を経て、ペアチップ出荷品として出荷される。

#### 【0199】

30

(3) 本実施の形態 16 に係る半導体装置の製造方法は、ウエハ 1 に回路を作り込み、半導体装置を形成する工程(半導体素子回路形成)と、前記実施の形態 15 で説明した半導体検査装置によりウエハレベルで複数の半導体装置の電気的特性を一括して検査する工程(ウエハ検査)とを有する。その後、バーンイン、選別検査、および外観検査を経て、フルウエハ出荷品として出荷される。このバーンインおよび選別検査においても、前記実施の形態 15 で説明した半導体検査装置により検査が行われる。

#### 【0200】

40

(4) 本実施の形態 16 に係る半導体装置の製造方法は、ウエハ 1 に回路を作り込み、半導体装置を形成する工程(半導体素子回路形成)と、前記実施の形態 15 で説明した半導体検査装置によりウエハレベルで複数の半導体装置の電気的特性を一括して検査する工程(ウエハ検査)とを有する。その後、バーンインおよび外観検査を経て、ウエハ 1 を切断し半導体素子 2 每に分離する工程(ダイシング)と、外観検査とを経て、ペアチップ出荷品として出荷される。このバーンインおよび選別検査においても、前記実施の形態 15 で説明した半導体検査装置により検査が行われる。

#### 【0201】

50

(5) 本実施の形態 16 に係る半導体装置の製造方法は、ウエハ 1 に回路を作り込み、半導体装置を形成する工程(半導体素子回路形成)と、ウエハ 1 を分割する工程(ウエハ分割)と、前記実施の形態 15 で説明した半導体検査装置により分割したウエハレベルで複数の半導体装置の電気的特性を一括して検査する工程(分割ウエハ検査)とを有する。その後、バーンイン、選別検査および外観検査を経て、分割ウエハ出荷品として出荷される。このバーンインおよび選別検査においても、前記実施の形態 15 で説明した半導体検査装置により検査が行われる。

#### 【0202】

(6) 本実施の形態 16 に係る半導体装置の製造方法は、ウエハ 1 に回路を作り込み、半導体装置を形成する工程(半導体素子回路形成)と、ウエハを分割する工程(ウエハ分割)と、前記実施の形態 15 で説明した半導体検査装置により分割したウエハレベルで複

50

数の半導体装置の電気的特性を一括して検査する工程（分割ウエハ検査）とを有する。その後、バーンイン、選別検査、分割したウエハを切断し、半導体素子ごとに分離する工程（ダイシング）と、外観検査とを経て、ベアチップ出荷品として出荷される。このバーンインおよび選別検査においても、前記実施の形態15で説明した半導体検査装置により検査が行われる。

#### 【0203】

(7) 本実施の形態16に係る半導体装置の製造方法は、ウエハ1に回路を作り込み、半導体装置を形成する工程（半導体素子回路形成）と、ウエハ1に樹脂層等を形成する工程（樹脂層形成）と、樹脂層等を形成したウエハ1に形成された複数の半導体素子2の電気的特性を前記実施の形態15で説明した半導体検査装置により一括して検査する工程（ウエハ検査）とを有する。その後、バーンインおよび選別検査を経て、ウエハ1を切断し、半導体素子2毎に分離する工程（ダイシング）と、外観検査とを経て、CSP出荷品として出荷される。このバーンインおよび選別検査においても、前記実施の形態15で説明した半導体検査装置により検査が行われる。

10

#### 【0204】

(8) 本実施の形態16に係る半導体装置の製造方法は、ウエハ1に回路を作り込み、半導体装置を形成する工程（半導体素子回路形成）と、ウエハ1に樹脂層等を形成する工程（樹脂層形成）と、樹脂層等を形成したウエハ1に形成された複数の半導体素子2の電気的特性を前記実施の形態15で説明した半導体検査装置により一括して検査する工程（ウエハ検査）とを有する。その後、バーンイン、選別検査、および外観検査を経て、フルウエハCSP出荷品として出荷される。このバーンインおよび選別検査においても、前記実施の形態15で説明した半導体検査装置により検査が行われる。

20

#### 【0205】

(9) 本実施の形態16に係る半導体装置の製造方法は、ウエハ1に回路を作り込み、半導体装置を形成する工程（半導体素子回路形成）と、ウエハ1に樹脂層等を形成する工程（樹脂層形成）と、樹脂層等を形成したウエハ1を分割する工程（ウエハ分割）と、前記実施の形態15で説明した半導体検査装置により分割したウエハレベルで複数の半導体装置の電気的特性を一括して検査する工程（分割ウエハ検査）とを有する。その後、バーンイン、選別検査、および外観検査を経て、分割ウエハCSP出荷品として出荷される。このバーンインおよび選別検査においても、前記実施の形態15で説明した半導体検査装置により検査が行われる。

30

#### 【0206】

(10) 本実施の形態16に係る半導体装置の製造方法は、ウエハ1に回路を作り込み、半導体装置を形成する工程（半導体素子回路形成）と、ウエハ1に樹脂層等を形成する工程（樹脂層形成）と、樹脂層等を形成したウエハを分割する工程（ウエハ分割）と、前記実施の形態15で説明した半導体検査装置により分割したウエハレベルで複数の半導体装置の電気的特性を一括して検査する工程（分割ウエハ検査）とを有する。その後、バーンイン、選別検査、ウエハを切断して半導体素子ごとに分離する工程（ダイシング）、および外観検査を経て、CSP出荷品として出荷される。このバーンインおよび選別検査においても、前記実施の形態15で説明した半導体検査装置により検査が行われる。

40

#### 【0207】

上記の半導体装置の製造方法における、半導体素子2の電気的特性を検査する工程では、前記実施の形態1～13で説明したプローブシート構造体を用いることにより、低荷重な数10mN以下の押圧力で、接触端子4の先端位置精度が高精度で、安定な接触抵抗値および良好な伝送特性を有した検査を実現できる。

#### 【0208】

すなわち、前記実施の形態で説明したプローブカードは、角錐形あるいは角錐台形の形状で、位置精度の良好な片持ち梁構造の接触端子と、引き出し配線と、周辺電極と、ポリイミド膜（絶縁シート）とをシリコン基板上に一体形成して、型材であるそのシリコン基板および所定のポリイミド膜をそれぞれ順次エッティング除去することで一括形成したプロ

50

ープシートを備え、接触端子が形成された領域に固着された固着基板を傾動可能にしたものである。このようなプローブカードによれば、数  $10 \mu m$  程度以下の狭ピッチかつ多ピンの片持ち梁構造の接触端子が形成されたプローブシートでも、容易に一括形成することができ、フォトリソグラフィ技術を用いて薄膜配線の多層化による電気信号特性の設計および製作も容易にできる。そのため、狭ピッチかつ多ピンの検査用であるばかりでなく、インピーダンス整合した高速伝送用回路を有するプローブカードを容易に実現できる。また、被検査対象と同程度の線膨張率を持つ金属シートおよび固着基板を、接触端子を形成した領域に直接固着した構造により、接触端子の先端位置精度が広い温度範囲で良好なプローブカードを実現できる。

#### 【0209】

また、前記実施の形態で説明したプローブカードは、角錐形状あるいは角錐台形状の接触端子が良好な位置精度で先端に配置された片持ち梁構造が一括形成されたプローブシートを備え、このようなプローブシートをシート裏面の固着基板および組立用基材と一緒に形成し、スプリング内蔵ガイドピンあるいは板ばねで傾動動作を実現し、片持ち梁構造で個々の接触端子の所望の押圧荷重を実現することにより、低荷重で接触抵抗値の安定性が良好で、接触端子群の位置精度と組立性の良好なプローブカードが実現できる。

#### 【0210】

また、前記実施の形態で説明したプローブカードは、片持ち梁構造の接触端子が形成された領域のプローブシートの反対面に固着された固着基板を包み込むブロック構造のプローブを複数個組み合わせて半導体検査に使用することにより、多数個チップの同時検査用プローブカード、あるいはフルウエハ検査用のウエハカセットが、簡単な構成で実現できる。

#### 【0211】

以上、本発明者によってなされた発明を実施の形態に基づき具体的に説明したが、本発明は上記実施の形態に限定されるものではなく、その要旨を逸脱しない範囲で種々変更可能であることは言うまでもない。

#### 【0212】

例えば、前記実施の形態では、図16～図28を用いて説明した工程で製造されたプローブシートを、図2に示した構成を有するプローブシート構造体を組み合わせて用いる例を示したが、図29～図49に示したような種々の製造工程によるプローブシートと、図7～図15に示したような種々のプローブシート構造体を自由に組み合わせて用いてよいことは言うまでもない。

#### 【産業上の利用可能性】

#### 【0213】

本発明は、プローブカード、プローブカードの製造方法、半導体検査装置および半導体装置の製造方法に広く適用することができる。

#### 【図面の簡単な説明】

#### 【0214】

【図1】半導体素子（チップ）が配列された被接触対象であるウエハと、その一部である半導体素子（チップ）とを示す斜視図である。

【図2】本発明の実施の形態1であるプローブカードの要部断面図である。

【図3】図2に示したプローブカードの主要部品を分解して図示した斜視図である。

【図4】図2に示したプローブカードの主要部品を分解して図示した組み立て断面図である。

【図5】図2に示したプローブカードの主要部品であるガイドピンの要部を示す断面図である。

【図6】本発明の実施の形態1であるプローブカードの接触端子群付近を拡大して示す要部断面図である。

【図7】本発明の実施の形態2であるプローブカードの要部断面図である。

【図8】本発明の実施の形態3であるプローブカードの要部断面図である。

10

20

30

40

50

【図9】本発明の実施の形態4であるプローブカードの要部断面図である。

【図10】(a)は本発明の実施の形態4であるプローブカードの構成要素である1個のブロックを示す断面概略図であり、(b)および(c)は(a)に示したブロックの構成を示す斜視図である。

【図11】(a)および(b)は、本発明の実施の形態5であるプローブカードの要部断面図である。

【図12】本発明の実施の形態6であるプローブカードの要部断面図である。

【図13】本発明の実施の形態6であるプローブカードの構成要素である1個のブロックに取り付けられるプローブシートの展開図である。

【図14】本発明の実施の形態6であるプローブカードの構成要素である1個のブロックの多層配線基板への取り付け例を示す要部斜視図である。 10

【図15】本発明の実施の形態7であるプローブカードの要部断面図である。

【図16】本発明の実施の形態8に係るプローブカードにおけるプローブシート(プローブシート構造体)部分を形成する製造プロセスの一部を示した要部断面図である。

【図17】図16に続くプローブシート部分の製造プロセスの一部を示した要部断面図である。 20

【図18】図17に続くプローブシート部分の製造プロセスの一部を示した要部断面図である。

【図19】図18に続くプローブシート部分の製造プロセスの一部を示した要部断面図である。 20

【図20】図19に続くプローブシート部分の製造プロセスの一部を示した要部断面図である。

【図21】図20に続くプローブシート部分の製造プロセスの一部を示した要部断面図である。 20

【図22】図21に続くプローブシート部分の製造プロセスの一部を示した要部断面図である。

【図23】図22に続くプローブシート部分の製造プロセスの一部を示した要部断面図である。

【図24】図23に続くプローブシート部分の製造プロセスの一部を示した要部断面図である。 30

【図25】図24に続くプローブシート部分の製造プロセスの一部を示した要部断面図である。

【図26】図25に続くプローブシート部分の製造プロセスの一部を示した要部断面図である。

【図27】図26に続くプローブシート部分の製造プロセスの一部を示した要部断面図である。 30

【図28】図27に続くプローブシート部分の製造プロセスの一部を示した要部断面図である。

【図29】本発明の実施の形態9に係るプローブカードにおけるプローブシート(プローブシート構造体)部分を形成する製造プロセスの一部を示した要部断面図である。 40

【図30】図29に続くプローブシート部分の製造プロセスの一部を示した要部断面図である。

【図31】図30に続くプローブシート部分の製造プロセスの一部を示した要部断面図である。

【図32】図31に続くプローブシート部分の製造プロセスの一部を示した要部断面図である。

【図33】本発明の実施の形態10に係るプローブカードにおけるプローブシート(プローブシート構造体)部分を形成する製造プロセスの一部を示した要部断面図である。

【図34】図33に続くプローブシート部分の製造プロセスの一部を示した要部断面図である。 50

【図35】図34に続くプローブシート部分の製造プロセスの一部を示した要部断面図である。

【図36】本発明の実施の形態11に係るプローブカードにおけるプローブシート(プローブシート構造体)部分を形成する製造プロセスの一部を示した要部断面図である。

【図37】図36に続くプローブシート部分の製造プロセスの一部を示した要部断面図である。

【図38】本発明の実施の形態12に係るプローブカードにおけるプローブシート(プローブシート構造体)部分を形成する製造プロセスの一部を示した要部断面図である。

【図39】図38に続くプローブシート部分の製造プロセスの一部を示した要部断面図である。

【図40】図39に続くプローブシート部分の製造プロセスの一部を示した要部断面図である。

【図41】図40に続くプローブシート部分の製造プロセスの一部を示した要部断面図である。

【図42】図41に続くプローブシート部分の製造プロセスの一部を示した要部断面図である。

【図43】図42に続くプローブシート部分の製造プロセスの一部を示した要部断面図である。

【図44】本発明の実施の形態13に係るプローブカードにおけるプローブシート(プローブシート構造体)部分を形成する製造プロセスの一部を示した要部断面図である。

【図45】図44に続くプローブシート部分の製造プロセスの一部を示した要部断面図である。

【図46】本発明の実施の形態14に係るプローブカードにおけるプローブシート(プローブシート構造体)部分を形成する製造プロセスの一部を示した要部断面図である。

【図47】図46に続くプローブシート部分の製造プロセスの一部を示した要部断面図である。

【図48】図47に続くプローブシート部分の製造プロセスの一部を示した要部断面図である。

【図49】図48に続くプローブシート部分の製造プロセスの一部を示した要部断面図である。

【図50】本発明の実施の形態15に係る検査システムの一例を示す全体概略構成図である。

【図51】半導体装置の検査工程の一例を示す工程図である。

【図52】従来のめっきによるバンプを用いた半導体素子検査装置の要部断面図である。

【図53】図52のめっきによるバンプ部分を示す斜視図である。

【図54】四角錐接触端子が形成された従来のプローブシートを用いた半導体素子検査装置の要部断面図である。

【図55】リソグラフィ技法により形成したばね接触要素の製造プロセスの途中段階を示す模式断面図である。

【図56】半導体素子の検査用の電極部の直下に能動回路素子や微細な配線が多層に形成されている構造を説明する要部断面図である。

#### 【符号の説明】

##### 【0 2 1 5】

- 1 ウエハ

- 2 半導体素子(チップ)

- 3 電極

- 4 接触端子

- 4 a 接触端子部

- 4 b 接続電極部

- 4 c, 4 e ニッケル

10

20

30

40

50

|                 |              |    |

|-----------------|--------------|----|

| 4 d             | ロジウム         |    |

| 4 f             | 金属材料         |    |

| 5               | プローブシート      |    |

| 6               | 固着基板         |    |

| 7               | 中間板          |    |

| 8               | 支持部材(上部固定板)  |    |

| 8 a             | 挿入孔          |    |

| 9               | ガイドピン        |    |

| 9 a             | スプリング内蔵ガイドピン | 10 |

| 9 b             | 位置決め専用ガイドピン  |    |

| 9 c             | チューブ         |    |

| 9 d、9 e         | 中軸           |    |

| 1 0             | 多層配線基板       |    |

| 1 0 b           | 内部配線         |    |

| 1 0 c           | 電極           |    |

| 1 1             | 周辺電極         |    |

| 1 2             | 周辺電極固定板      |    |

| 1 2 a           | ノックピン用孔      |    |

| 1 2 b           | ねじ挿入用孔       |    |

| 1 4             | 金属膜          | 20 |

| 1 4 a           | ノックピン用孔      |    |

| 1 4 b           | ねじ挿入用孔       |    |

| 1 5             | 電極           |    |

| 1 6             | 引き出し配線       |    |

| 1 6 A、1 6 B     | 引き出し配線       |    |

| 1 7             | 周辺押さえ板       |    |

| 1 7 a           | ノックピン用孔      |    |

| 1 7 b           | ねじ挿入用孔       |    |

| 1 7 c           | ノックピン        |    |

| 1 8             | 緩衝材          | 30 |

| 1 9             | ダブルねじ        |    |

| 1 9 a           | ねじ           |    |

| 1 9 b           | 中ねじ          |    |

| 2 0             | スペーサ         |    |

| 2 1             | 上板           |    |

| 2 3             | チップコンデンサ     |    |

| 2 4             | 金属膜          |    |

| 2 5             | スプリング        |    |

| 2 6             | 板ばね          |    |

| 2 7             | プローブカード      | 40 |

| 2 8、2 8 b、2 8 c | 梁            |    |

| 2 9             | ポスト          |    |

| 3 0             | ポリイミド膜       |    |

| 3 1             | 保護膜          |    |

| 3 2、3 2 b       | ブロック         |    |

| 3 3             | 固着基板         |    |

| 3 3 s           | 固着位置         |    |

| 3 4             | 緩衝材          |    |

| 3 5             | 固定ねじ         |    |

| 3 6             | スペーサ         | 50 |

|                        |                     |    |

|------------------------|---------------------|----|

| 3 7                    | 上押さえ板               |    |

| 3 8                    | 緩衝材                 |    |

| 3 9、 3 9 b             | ウエハ搭載台              |    |

| 4 0 a ~ 4 0 d          | Oリング                |    |

| 4 1 b                  | 下基板                 |    |

| 4 1 c                  | 中基板                 |    |

| 4 1 d                  | 上基板                 |    |

| 4 2                    | ウエハ搭載膜              |    |

| 4 3                    | ブロック吊り板             |    |

| 4 3 s                  | 固着位置                | 10 |

| 4 4                    | 固着基板直上シート押さえ板       |    |

| 4 4 s                  | 固着位置                |    |

| 4 5                    | 基板下面シート押さえ板         |    |

| 4 5 s                  | 固着位置                |    |

| 4 6 a                  | 配線ピッチ拡大パッド（第1の周辺電極） |    |

| 4 6 b                  | 配線ピッチ拡大パッド（第2の周辺電極） |    |

| 4 7                    | 基板上面押さえ板            |    |

| 4 8                    | 固定ねじ                |    |

| 4 9                    | 下押さえ板               |    |

| 5 0                    | 上押さえ板               | 20 |

| 5 1                    | 固定ねじ                |    |

| 6 0                    | シリコンウエハ             |    |

| 6 0 a                  | 穴                   |    |

| 6 1、 6 2               | 二酸化シリコン膜            |    |

| 6 3                    | 導電性被覆               |    |

| 6 4、 6 4 b、 6 4 c      | フォトレジストマスク          |    |

| 6 5、 6 5 b、 6 5 c      | ポリイミド膜              |    |

| 6 6、 6 6 b             | 導電性被覆               |    |

| 6 7                    | フォトレジストマスク          |    |

| 6 8、 6 8 b、 6 8 c、 6 9 | ポリイミド膜              | 30 |

| 7 0、 7 0 b             | アルミニウムマスク           |    |

| 7 1、 7 1 b             | めっき                 |    |

| 7 1 a                  | 引き出し配線接続用穴          |    |

| 7 2、 7 2 b、 7 2 c      | 導電性被覆               |    |

| 7 3                    | フォトレジストマスク          |    |

| 7 4、 7 4 b、 7 4 c      | 配線材料                |    |

| 7 4 d                  | 銅                   |    |

| 7 4 e                  | ニッケル                |    |

| 7 5、 7 5 b、 7 5 c      | ポリイミド膜              |    |

| 7 6                    | アルミニウムマスク           | 40 |

| 7 7、 7 7 b             | 導電性被覆               |    |

| 7 8、 7 8 b             | フォトレジストマスク          |    |

| 7 9、 7 9 b             | 配線材料                |    |

| 8 0                    | ポリイミド膜              |    |

| 8 1、 8 1 c             | 接着層                 |    |

| 8 2、 8 2 c             | 金属膜                 |    |

| 8 3、 8 3 c             | フォトレジストマスク          |    |

| 8 4                    | 接着材                 |    |

| 8 5                    | シリコンエッティング用保持リング    |    |

| 8 6、 8 7               | 接着材                 | 50 |

|                                                                   |                 |    |

|-------------------------------------------------------------------|-----------------|----|

| 8 8                                                               | アルミニウムマスク       |    |

| 9 0                                                               | 導電性被覆           |    |

| 9 1                                                               | フォトレジストマスク      |    |

| 9 2                                                               | 金属層（犠牲層）        |    |

| 9 7                                                               | ブロック間固定基板       |    |

| 1 0 0 a                                                           | 固定治具            |    |

| 1 0 0 b                                                           | ふた              |    |

| 1 0 0 c                                                           | Oリング            |    |

| 1 0 0 d                                                           | 中間固定板           |    |

| 1 0 5 、 1 0 5 b 、 1 0 5 c 、 1 0 5 d 、 1 0 5 e 、 1 0 5 f 、 1 0 5 g | プローブシート構造体      | 10 |

| 1 4 0                                                             | 温度制御系           |    |

| 1 4 1                                                             | ヒータ             |    |

| 1 5 0                                                             | 駆動制御系           |    |

| 1 5 1                                                             | 操作部             |    |

| 1 6 0                                                             | 試料支持系           |    |

| 1 6 2                                                             | 試料台             |    |

| 1 6 4                                                             | 昇降軸             |    |

| 1 6 5                                                             | 昇降駆動部           |    |

| 1 6 6                                                             | 筐体              | 20 |

| 1 6 7                                                             | X - Yステージ       |    |

| 1 7 0                                                             | テスタ             |    |

| 1 7 1 、 1 7 2                                                     | ケーブル            |    |

| 2 0 1                                                             | 絶縁膜             |    |

| 2 0 2                                                             | 配線              |    |

| 2 0 3                                                             | グランド層           |    |

| 2 0 4                                                             | スルーホール          |    |

| 2 0 5                                                             | バンプ             |    |

| 2 0 6                                                             | 配線基板            |    |

| 2 0 7                                                             | 板ばね             | 30 |

| 2 1 1                                                             | スプリングプランジャ      |    |

| 2 1 2                                                             | 接触端子            |    |

| 2 1 3                                                             | 絶縁膜             |    |

| 2 1 4                                                             | 押し駒             |    |

| 2 1 5                                                             | シリコン基板          |    |

| 2 1 6                                                             | 穴               |    |

| 2 1 7                                                             | チップ部分（接触端子）     |    |

| 2 1 8                                                             | ビーム部分（梁）        |    |

| 2 1 9                                                             | ポスト部分           |    |

| 2 2 0                                                             | セラミック多層配線基板     | 40 |

| 2 2 1                                                             | 電極              |    |

| 2 2 2                                                             | はんだ             |    |

| 2 2 5 a ~ 2 2 5 g                                                 | 配線              |    |

| 2 2 6                                                             | C M O S - L S I |    |

【図1】

【図2】

【図3】

【図4】

【図5】

図5

【図6】

図6

【図7】

図7

【図8】

図8

【図 9】

【図 10】

【図 11】

図 11

【図 12】

【図 13】

【図 14】

【図 15】

【図 16】

【図 17】

図 17

【図 18】

図 18

【図 19】

図 19

【図 20】

図 20

【図 2 1】

図 21

【図 2 2】

図 22

【図 2 3】

図 23

【図 2 4】

図 24

【図 25】

図 25

【図 26】

図 26

【図 27】

図 27

【図 28】

図 28

【図 29】

図 29

【図 30】

図 30

【図 31】

図 31

【図 32】

図 32

【図 3 3】

図 33

【図 3 4】

図 34

【図 3 5】

図 35

【図 3 6】

図 36

【図 37】

図 37

【図 38】

図 38

【図 39】

図 39

【図 40】

図 40

【図 4 1】

図 41

【図 4 2】

図 42

【図 4 3】

図 43

【図 4 4】

図 44

【図 4 5】

図 45

【図 4 6】

図 46

【図 4 7】

図 47

【図 4 8】

図 48

【図 49】

図 49

【図 50】

【図 51】

図 51

【図 52】

【図 53】

【図 5 4】

【図 5 5】

図 55

【図 5 6】

図 56

---

フロントページの続き

F ターム(参考) 4M106 AA01 AA02 BA01 CA01 CA31 DD10