(19) 日本国特許庁(JP)

## (12) 公開特許公報(A)

(11) 特許出願公開番号

特開2005-183686

(P2005-183686A)

(43) 公開日 平成17年7月7日(2005.7.7)

(51) Int.Cl.<sup>7</sup>

H01L 21/822

H01L 21/76

H01L 21/762

H01L 21/8234

H01L 27/04

F 1

H01L 27/04

H01L 27/08

H01L 27/08

H01L 29/78

H01L 29/78

テーマコード(参考)

P 5FO32

331A 5FO38

331E 5FO48

621 5F110

613Z

審査請求 未請求 請求項の数 12 O L (全 24 頁) 最終頁に続く

(21) 出願番号

特願2003-422762 (P2003-422762)

(22) 出願日

平成15年12月19日 (2003.12.19)

(71) 出願人

503121103

株式会社ルネサステクノロジ

東京都千代田区丸の内二丁目4番1号

(74) 代理人

100089233

弁理士 吉田 茂明

(74) 代理人

100088672

弁理士 吉竹 英俊

(74) 代理人

100088845

弁理士 有田 貴弘

(72) 発明者

岩松 俊明

東京都千代田区丸の内二丁目4番1号 株式会社ルネサステクノロジ内

(72) 発明者

一法師 隆志

東京都千代田区丸の内二丁目4番1号 株式会社ルネサステクノロジ内

最終頁に続く

(54) 【発明の名称】半導体装置およびその製造方法

## (57) 【要約】

【課題】ディッシングの発生を防止するとともに、抵抗素子の寄生容量を低減して高性能な回路動作を実現したSOIデバイスを提供する。

【解決手段】抵抗領域RRにおいては、スパイラルインダクタSIの配設領域に対応するSOI層3の表面内にトレンチ分離絶縁膜4がSOI層3を間に挟んで複数配設され、各トレンチ分離絶縁膜4上に抵抗素子30がそれぞれ配設されている。トレンチ分離絶縁膜4は、中央部分においてはSOI層3を貫通して埋め込み酸化膜2に達して完全分離構造となり、両端縁部においては、その下部にSOI層3を有して部分分離構造となった併合分離構造を有している。

【選択図】図3

**【特許請求の範囲】****【請求項 1】**

土台となる基板部、該基板部上に配設された埋め込み酸化膜、および該埋め込み酸化膜上に配設されたS O I層を有するS O I基板と、

前記S O I基板の上方に配設されたインダクタンス素子と、

前記インダクタンス素子の下部に相当する第1の領域の前記S O I層の正面内に、間に前記S O I層を挟んで配設された複数の第1の素子分離絶縁膜と、

前記第1の領域の前記複数の第1の素子分離絶縁膜上にそれぞれ配設された、複数の抵抗素子と、を備え、

前記複数の第1の素子分離絶縁膜のそれぞれは、少なくとも一部分が前記S O I層を貫通して前記埋め込み酸化膜に達する完全分離構造をなす、半導体装置。 10

**【請求項 2】**

土台となる基板部、該基板部上に配設された埋め込み酸化膜、および該埋め込み酸化膜上に配設されたS O I層を有するS O I基板と、

前記S O I基板の上方に配設されたインダクタンス素子と、

前記インダクタンス素子の下部に相当する第1の領域の前記S O I層の正面内に、間に前記S O I層を挟んで配設された複数の第1の素子分離絶縁膜と、

前記複数の第1の素子分離絶縁膜の間の前記S O I層上に、それぞれ絶縁膜を介して配設された、複数の抵抗素子と、を備え、

前記複数の第1の素子分離絶縁膜のそれぞれは、少なくとも一部分が前記S O I層を貫通して前記埋め込み酸化膜に達する完全分離構造をなす、半導体装置。 20

**【請求項 3】**

前記複数の第1の素子分離絶縁膜のそれぞれは、その断面形状において、中央部分は前記完全分離構造をなし、両端部分は、その下部に前記S O I層を有する部分分離構造をなす、併合分離構造を有する、請求項1または請求項2記載の半導体装置。

**【請求項 4】**

前記複数の第1の素子分離絶縁膜のそれぞれは、その断面形状において、全体が前記完全分離構造を有する、請求項1または請求項2記載の半導体装置。

**【請求項 5】**

前記第1の領域の前記S O I層は、完全空乏化状態を可能とする濃度に不純物を含む、請求項1または請求項2記載の半導体装置。 30

**【請求項 6】**

複数の半導体素子が配設される第2の領域の前記S O I層の正面内に配設された第2の素子分離絶縁膜を備え、

前記複数の第1の素子分離絶縁膜は、前記第2の素子分離絶縁膜の厚さよりも厚い、請求項5記載の半導体装置。

**【請求項 7】**

前記複数の第1の素子分離絶縁膜のそれぞれの平面視形状は、第1の方向に細長く延在する細長形状を有し、

前記複数の第1の素子分離絶縁膜は、前記第1の方向とは直交する第2の方向に並列して配列され、 40

前記第1の領域の前記S O I層は、前記複数の第1の素子分離絶縁膜の配列間に少なくとも配設される、請求項1または請求項2記載の半導体装置。

**【請求項 8】**

前記第1の領域の前記S O I層は、前記複数の第1の素子分離絶縁膜の前記第1の方向の両端部外側の位置にも配設される、請求項7記載の半導体装置。

**【請求項 9】**

前記第1の領域とは異なる第2の領域に配設されたM O Sトランジスタを備え、

前記M O Sトランジスタは、第2の領域の前記S O I層上に配設されたゲート絶縁膜を有し、 50

前記第1の領域の前記SOI層上の前記絶縁膜の厚さは、前記ゲート絶縁膜よりも厚い、請求項2記載の半導体装置。

#### 【請求項10】

前記複数の抵抗素子はポリシリコンで構成される、請求項1または請求項2記載の半導体装置。

#### 【請求項11】

土台となる基板部、該基板部上に配設された埋め込み酸化膜、および該埋め込み酸化膜上に配設されたSOI層を有するSOI基板の上方に配設されたインダクタンス素子と、前記インダクタンス素子の下部に相当する第1の領域の前記SOI層の主面内に、間に前記SOI層を挟んで配設された複数の素子分離絶縁膜と、前記第1の領域の前記複数の素子分離絶縁膜上または前記複数の素子分離絶縁膜間の前記SOI層上にそれぞれ配設された、複数の抵抗素子と、前記第1の領域とは異なる第2の領域に配設されたMOSトランジスタとを備えた半導体装置の製造方法であって、

(a)前記第1の領域の前記SOI層の主面内に、前記複数の素子分離絶縁膜を形成する工程と、

(b)前記第2の領域の前記SOI層内に、イオン注入により前記MOSトランジスタのしきい値電圧を設定するための不純物を導入する工程と、

(c)前記工程(b)の後に、前記第1および第2の領域に渡るようにポリシリコン層を形成する工程と、

(d)前記第1および第2の領域の前記ポリシリコン層をそれぞれパターニングして、前記複数の抵抗素子および前記MOSトランジスタのゲート電極を形成する工程と、を備え、

前記工程(b)は、前記第1の領域上をマスクで覆い、前記第1の領域への前記不純物の導入を防止する工程を含む、半導体装置の製造方法。

#### 【請求項12】

(e)前記工程(d)の後に、前記第2の領域の前記SOI層内に、イオン注入により前記MOSトランジスタのソース・ドレイン層を形成するためのソース・ドレイン不純物を導入する工程をさらに備え、

前記工程(e)は、前記第1の領域上をマスクで覆い、前記第1の領域への前記ソース・ドレイン不純物の導入を防止する工程を含む、請求項11記載の半導体装置の製造方法。

#### 【発明の詳細な説明】

##### 【技術分野】

##### 【0001】

本発明は半導体装置およびその製造方法に関し、特に、インダクタを有した半導体装置およびその製造方法に関する。

##### 【背景技術】

##### 【0002】

シリコン基板上に埋め込み酸化膜およびSOI(Silicon On Insulator)層が配設されたSOI基板に形成されるSOI構造の半導体装置(以後、SOIデバイスと呼称)は、寄生容量を低減でき、高速で安定な動作および低消費電力という特徴を有し、携帯機器などに使用されている。

##### 【0003】

SOIデバイスの一例としては、SOI層の表面内に埋め込み酸化膜に達するトレンチを設け、該トレンチ内に絶縁物を埋め込むことで形成された完全トレンチ分離絶縁膜により、素子間を電気的に分離する完全トレンチ分離(FTI)構造のSOIデバイスがある。しかし、衝突電離現象によって発生するキャリア(NMOSではホール)がチャネル形成領域に溜まり、これによりキンクが発生したり、動作耐圧が劣化したり、また、チャネル形成領域の電位が安定しないために遅延時間の周波数依存性が発生する等の基板浮遊効果により生ずる種々の問題点があった。

##### 【0004】

10

20

30

40

50

そこで考案されたのが、トレンチの底部と埋め込み酸化膜との間に所定厚さの S O I 層が残るように S O I 層の表面内にトレンチを形成し、該トレンチ内に絶縁物を埋め込むことで形成されたパーシャルトレンチ分離（ P T I ）構造である。

#### 【 0 0 0 5 】

P T I 構造の採用により、トレンチ分離絶縁膜の下部のウエル領域を通じてキャリアの移動が可能であり、キャリアがチャネル形成領域に溜まるということを防止でき、またウエル領域を通じてチャネル形成領域の電位を固定することができるので、基板浮遊効果による種々の問題が発生しない。

#### 【 0 0 0 6 】

ここで、高周波アナログ回路等では、能動素子としてのトランジスタに加え、受動素子としてのインダクタ、キャパシタ、抵抗などが用いられる。 10

#### 【 0 0 0 7 】

例えば、特許文献 1 にはポリシリコン抵抗を L O C O S ( Local Oxide of Silicon ) 酸化膜の上に配設する構成が開示されている。

#### 【 0 0 0 8 】

ここで、P T I 構造を採用する S O I デバイスにおいて、インダクタとしてスパイラルインダクタを備える場合、当該インダクタの下部に対応する S O I 層の領域に完全トレンチ分離絶縁膜を配設するようにしていた。そして当該完全トレンチ分離絶縁膜上に抵抗素子を配設する構成を探っていた。 20

#### 【 0 0 0 9 】

スパイラルインダクタは、その一辺が数  $10 \mu m$  ~ 数  $100 \mu m$  の長さを有する方形形状の外形を有するが、その下部に上述したような完全トレンチ分離絶縁膜を配設する構成を探ると、スパイラルインダクタの配設面積に相当する広い領域に渡って、完全トレンチ分離絶縁膜が存在することとなる。

#### 【 0 0 1 0 】

そして、このような構造を採用する場合、完全トレンチ分離絶縁膜の形成時に C M P ( Chemical Mechanical Polishing ) 処理を行うと、完全トレンチ分離絶縁膜が所望の研磨量よりも過剰に除去され、完全トレンチ分離酸化の厚みが中央部になるほど薄くなる、いわゆるディッシングが発生する。そして、ディッシングが発生した完全トレンチ分離絶縁膜上に抵抗素子を配設すると、完全トレンチ分離絶縁膜の端縁部近傍に配置される抵抗素子は、寸法異常や形状異常などを引き起こす問題があった。 30

#### 【 0 0 1 1 】

また、これらを回避するため、完全トレンチ分離絶縁膜の端縁部近傍には抵抗素子を配設しないこととすると、抵抗を必要個数配設するために完全トレンチ分離絶縁膜の面積を大きくする必要が生じ、装置面積の増大が生じる。

#### 【 0 0 1 2 】

また、C M P 処理で過度のディッシングが発生するような場合には、分離絶縁膜と S O I 層はもとより、その下層の埋め込み酸化膜まで研磨が及ぶことがあり、さらには、埋め込み酸化膜まで研磨され、場合によってはシリコン基板にまで研磨が及ぶことも起こりうる。 40

#### 【 0 0 1 3 】

このようなディッシングの発生を防止するには、従来は、例えば特許文献 2 に開示されるように、スパイラルインダクタの配設領域の下部およびその周辺に、複数のダミー素子領域を分散配置する構成が提案されていた。

#### 【 0 0 1 4 】

【 特許文献 1 】特開平 9 - 289324 号公報(第 5 、第 6 欄、図 2 ( g ))

【 特許文献 2 】特開 2002 - 110908 号公報(第 6 欄、図 3 、 4 )

#### 【 発明の開示 】

#### 【 発明が解決しようとする課題 】

#### 【 0 0 1 5 】

10

20

30

40

50

上記のように、大きな面積を有するトレンチ分離絶縁膜を形成する際には、ディッシングの発生を防止することが課題であるが、そのために特許文献1のようにトレンチ分離絶縁膜の形成領域に複数のダミー素子領域を分散配置すると抵抗素子を配設することができず、高周波アナログ回路等には不向きな構成となってしまう。

#### 【0016】

本発明は上記のような問題点を解消するためになされたもので、ディッシングの発生を防止するとともに、抵抗素子の寄生容量を低減して高性能な回路動作を実現したSOIデバイスを提供することを目的とする。

#### 【課題を解決するための手段】

#### 【0017】

本発明に係る請求項1記載の半導体装置は、土台となる基板部、該基板部上に配設された埋め込み酸化膜、および該埋め込み酸化膜上に配設されたSOI層を有するSOI基板と、前記SOI基板の上方に配設されたインダクタンス素子と、前記インダクタンス素子の下部に相当する第1の領域の前記SOI層の主面内に、間に前記SOI層を挟んで配設された複数の第1の素子分離絶縁膜と、前記第1の領域の前記複数の第1の素子分離絶縁膜上にそれぞれ配設された、複数の抵抗素子とを備え、前記複数の第1の素子分離絶縁膜のそれぞれは、少なくとも一部分が前記SOI層を貫通して前記埋め込み酸化膜に達する完全分離構造をなしている。

#### 【0018】

本発明に係る請求項2記載の半導体装置は、土台となる基板部、該基板部上に配設された埋め込み酸化膜、および該埋め込み酸化膜上に配設されたSOI層を有するSOI基板と、前記SOI基板の上方に配設されたインダクタンス素子と、前記インダクタンス素子の下部に相当する第1の領域の前記SOI層の主面内に、間に前記SOI層を挟んで配設された複数の第1の素子分離絶縁膜と、前記複数の第1の素子分離絶縁膜の間の前記SOI層上に、それぞれ絶縁膜を介して配設された、複数の抵抗素子とを備え、前記複数の第1の素子分離絶縁膜のそれぞれは、少なくとも一部分が前記SOI層を貫通して前記埋め込み酸化膜に達する完全分離構造をなしている。

#### 【0019】

本発明に係る請求項11記載の半導体装置の製造方法は、土台となる基板部、該基板部上に配設された埋め込み酸化膜、および該埋め込み酸化膜上に配設されたSOI層を有するSOI基板の上方に配設されたインダクタンス素子と、前記インダクタンス素子の下部に相当する第1の領域の前記SOI層の主面内に、間に前記SOI層を挟んで配設された複数の素子分離絶縁膜と、前記第1の領域の前記複数の素子分離絶縁膜上または前記複数の素子分離絶縁膜間の前記SOI層上にそれぞれ配設された、複数の抵抗素子と、前記第1の領域とは異なる第2の領域に配設されたMOSトランジスタとを備えた半導体装置の製造方法であって、以下の工程(a)ないし(e)を備えている。すなわち、前記第1の領域の前記SOI層の主面内に、前記複数の素子分離絶縁膜を形成する工程(a)と、前記第2の領域の前記SOI層内に、イオン注入により前記MOSトランジスタのしきい値電圧を設定するための不純物を導入する工程(b)と、前記工程(b)の後に、前記第1および第2の領域に渡るようにポリシリコン層を形成する工程(c)と、前記第1および第2の領域の前記ポリシリコン層をそれぞれパターニングして、前記複数の抵抗素子および前記MOSトランジスタのゲート電極を形成する工程(d)とを備えている。そして前記工程(b)は、前記第1の領域上をマスクで覆い、前記第1の領域への前記不純物の導入を防止する工程を含んでいる。

#### 【発明の効果】

#### 【0020】

本発明に係る請求項1記載の半導体装置によれば、インダクタンス素子の下部に相当する第1の領域のSOI層の主面内に、間にSOI層を挟んで配設された複数の第1の素子分離絶縁膜を備えるので、単一の分離絶縁膜が広い面積に渡って存在する所以で、分離絶縁膜の形成時のCMP処理においてディッシングが発生することを防止できる。

また、第1の領域の複数の第1の素子分離絶縁膜上には、それぞれ複数の抵抗素子が配設されているので、スパイラルインダクタの下方に対応する領域を有効に利用することができ、装置面積が増大することなく、かつ高周波アナログ回路等の形成に有利な構成となる。

#### 【0021】

本発明に係る請求項2記載の半導体装置によれば、インダクタンス素子の下部に相当する第1の領域のSOI層の主面内に、間にSOI層を挟んで配設された複数の第1の素子分離絶縁膜を備えるので、単一の分離絶縁膜が広い面積に渡って存在する事がないので、分離絶縁膜の形成時のCMP処理においてディッシングが発生することを防止できる。また、複数の第1の素子分離絶縁膜の間のSOI層上に、それぞれ絶縁膜を介して抵抗素子が配設されているので、スパイラルインダクタの下方に対応する領域を有効に利用することができ、装置面積が増大することなく、かつ高周波アナログ回路等の形成に有利な構成となる。

#### 【0022】

本発明に係る請求項11記載の半導体装置の製造方法によれば、第1の領域のSOI層内には、半導体素子の形成時に不純物が導入されることが防止されるので、第1の領域のSOI層を高抵抗に保つことができ、また、電圧条件によっては完全空乏化が可能となり、抵抗素子の寄生容量の低容量化が可能となり、高周波動作に有利な半導体装置を得ることができる。

#### 【発明を実施するための最良の形態】

#### 【0023】

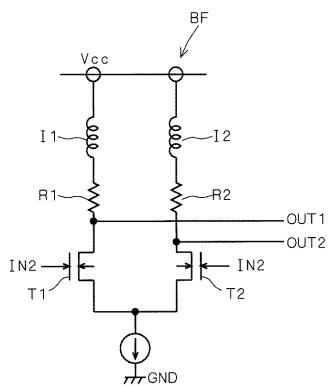

##### <高周波アナログ回路の一例>

図1に高周波アナログ回路の一例として、電流作動型のバッファ回路BFの構成を示す。この駆動電源VCCに並列に接続されたスパイラルインダクタI1およびI2、スパイラルインダクタI1およびI2にそれぞれ接続された抵抗R1およびR2、抵抗R1およびR2に、それぞれのドレインが接続されたNチャネルトランジスタT1およびT2、NチャネルトランジスタT1およびT2のソースが共通に接続される電流源CSとを備えている。

#### 【0024】

このような構成を有するバッファ回路BFは、NチャネルトランジスタT1およびT2のゲートに相補的な信号IN1およびIN2が与えられると、それぞれの出力OUT1およびOUT2からは反転した相補的な信号が出力される。

#### 【0025】

この出力信号の立ち上がりや立ち下がりの変化率は、回路中の抵抗成分および容量成分で決定され、立ち上がりや立ち下がりを急峻なものとするには、抵抗R1およびR2に寄生する容量を低減することが効果的である。また、抵抗R1およびR2はそれぞれ複数の抵抗素子で構成されるので、それらの抵抗素子を設計通りに形成することができ、回路動作を良好なものとする上で重要である。

#### 【0026】

##### <実施の形態>

##### <A. 装置構成>

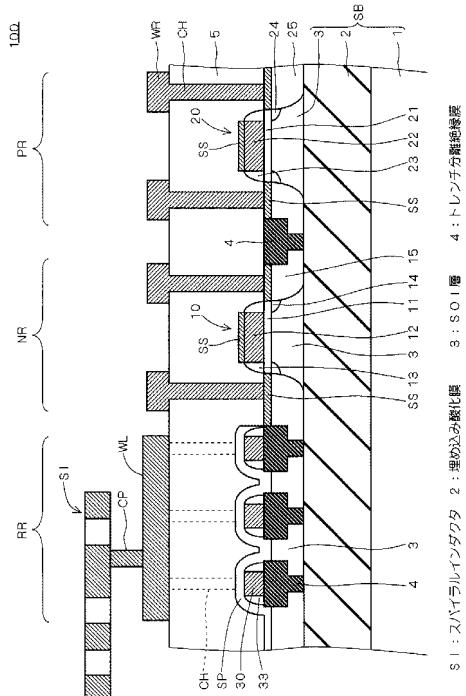

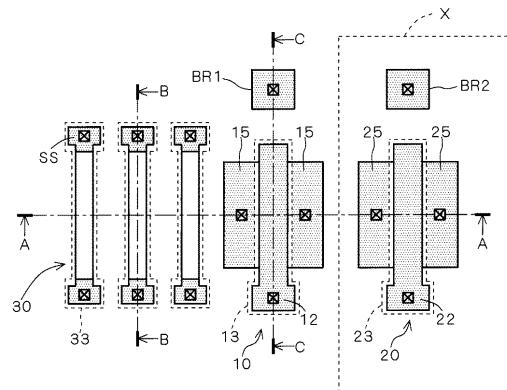

本発明に係る半導体装置の実施の形態として、図2を用いてSOIデバイス100の平面構成を説明する。

#### 【0027】

図2において、Nチャネル型のMOSトランジスタ10と、Pチャネル型のMOSトランジスタ20とが、それぞれのゲート電極12および22がゲート長方向に並列するように隣り合って配設されている。

#### 【0028】

そして、MOSトランジスタ10および20の、それぞれのゲート電極12および22のゲート幅方向の一方の端縁部の先には電位固定のためのボディ固定領域BR1およびB

10

20

30

40

50

R 2 が配設されている

なお、MOSトランジスタ10の配設領域とMOSトランジスタ20の配設領域とは電気的に絶縁されており、その様子を図2においては便宜的に破線Xで示している。

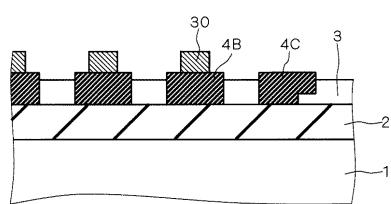

#### 【0029】

そしてMOSトランジスタ10の図に向かって左隣は抵抗素子の配設領域となっており、複数の抵抗素子30が並列に配設されている。なお、抵抗素子30は細長形状を有し、短手方向に並列するように配列されている。

#### 【0030】

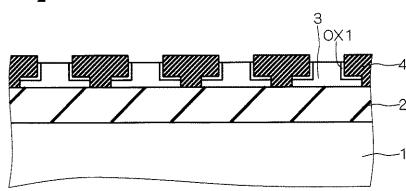

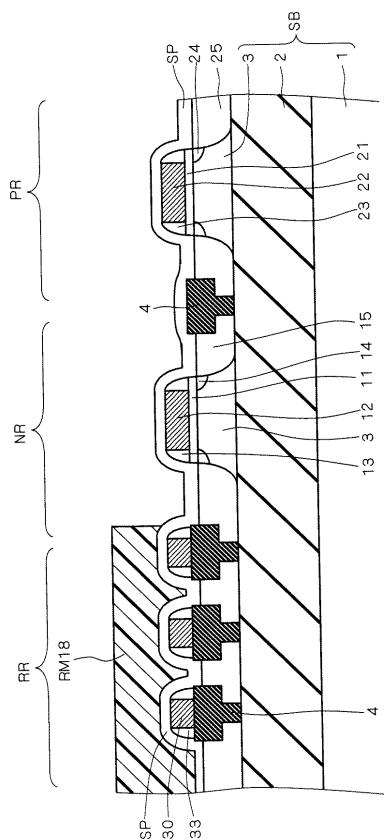

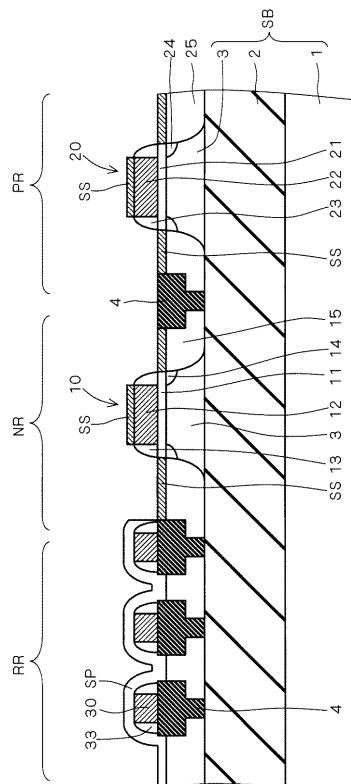

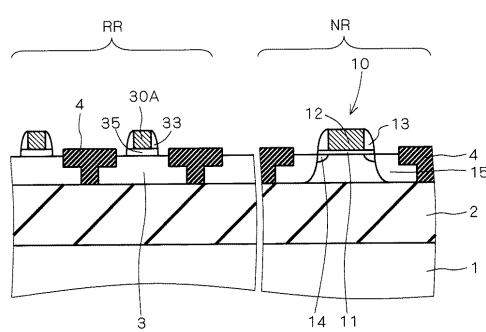

次に、SOIデバイス100の断面構成として、図2に示すA-A線での断面構成を図3に示し、またB-B線での断面構成を図4に、C-C線での断面構成を図5に示す。

10

#### 【0031】

図3に示すようにSOIデバイス100は、シリコン基板1と、当該シリコン基板1上に配設された埋め込み酸化膜2と、埋め込み酸化膜2上に配設されたSOI層3とで構成されるSOI基板SB上に配設されている。

#### 【0032】

SOI基板SB上は、抵抗素子30が配設される抵抗領域RR(第1の領域)と、素子領域(第2の領域)であるNチャネル型のMOSトランジスタ10が配設されるNMOS領域NRと、Pチャネル型のMOSトランジスタ20が配設されるPMOS領域PRとに区分されている。なお、図2および図3においては、MOSトランジスタ10および20は、それぞれ1個ずつ、抵抗素子30は3個しか示していないが、これは便宜的なものであり、何れの構成もこの個数に限定されるものではない。また、抵抗素子30はゲート電極12および22と並列に配設された例を示したがこれに限定されるものではなく、ゲート電極12および22の配列方向と直交する方向に配列しても良い。

20

#### 【0033】

抵抗領域RRにおいては、スパイラルインダクタSIの配設領域に対応するSOI層3の表面内にトレンチ分離絶縁膜4がSOI層3を間に挟んで複数配設され、各トレンチ分離絶縁膜4上に抵抗素子30がそれぞれ配設されている。なお、抵抗素子30の側面を覆うようにサイドウォール酸化膜33が配設されている。

#### 【0034】

ここでトレンチ分離絶縁膜4は、中央部分においてはSOI層3を貫通して埋め込み酸化膜2に達して完全分離構造(フルトレンチ分離構造:FTI)となり、両端縁部においては、その下部にSOI層3を有して部分分離構造(パーシャルトレンチ分離構造:PTI)となって、断面の輪郭形状が略T字形となった併合分離構造(ハイブリッドトレンチ分離構造:HTI)を有している。

30

#### 【0035】

なお、併合分離構造は上述した略T字形の形状に限定されるものではなく、部分分離構造と完全分離構造とを有するものであれば断面形状に関係なく併合分離構造と言うことができる。

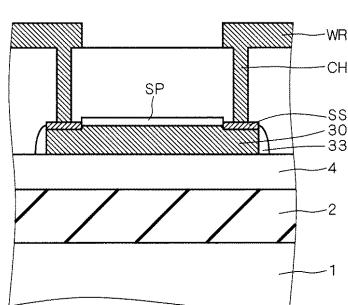

#### 【0036】

また、複数の抵抗素子30の上部および抵抗素子間のSOI層3上を覆うようにシリサイドプロテクション膜SPが配設されている。シリサイドプロテクション膜SPは、シリサイド膜の形成を望まない部分に配設される膜であり、シリコン酸化膜等の絶縁膜で構成される。細長形状の抵抗素子30においては、図4に示すように、長手方向の両端縁部上にはシリサイド膜SSを配設し、中央部はシリサイドプロテクション膜SPで覆っている。なお、図2でハッチングを付している部分はシリサイド膜SSが形成されている部分である。

40

#### 【0037】

MOSトランジスタ10は、SOI層3上に選択的に配設されたゲート絶縁膜11、ゲート絶縁膜11上に配設されたゲート電極12、ゲート電極12上に配設されたシリサイド膜SSおよび、それらの側面を覆うように配設されたサイドウォール絶縁膜13を備え

50

ている。

【0038】

また、MOSトランジスタ10のサイドウォール絶縁膜13の外側のSOI層3の表面内にはソース・ドレイン層15が配設され、ソース・ドレイン層15よりも浅い位置にはエクステンション層14が配設されている。なお、ソース・ドレイン層15上にはシリサイド膜SSが配設されている。

【0039】

MOSトランジスタ20は、SOI層3上に選択的に配設されたゲート絶縁膜21、ゲート絶縁膜21上に配設されたゲート電極22、ゲート電極22上に配設されたシリサイド膜SSおよび、それらの側面を覆うように配設されたサイドウォール絶縁膜23を備えている。

【0040】

また、MOSトランジスタ20のサイドウォール絶縁膜23の外側のSOI層3の表面内にはソース・ドレイン層25が配設され、ソース・ドレイン層25よりも浅い位置にはエクステンション層24が配設されている。なお、ソース・ドレイン層25上にはシリサイド膜SSが配設されている。

【0041】

ここで、エクステンション層14および24は、ソース・ドレイン層よりも浅い接合となるように形成される不純物層であり、ソース・ドレイン層と同一導電型であり、ソース・ドレイン層として機能するのでソース・ドレインエクステンション層と呼称すべきであるが、便宜的にエクステンション層と呼称する。

【0042】

なお、NMOs領域NRとPMOS領域PRとの間は、併合分離構造を有するトレンチ分離絶縁膜4によって電気的に分離されている。

【0043】

そして、SOI基板SB上全域を覆うように、例えばシリコン酸化膜で構成される層間絶縁膜5が配設され、層間絶縁膜5の上方にはスパイラルインダクタSIが配設されている。

【0044】

また、層間絶縁膜5を貫通して、ソース・ドレイン層15および25上のシリサイド膜SSに接続されるように複数のコンタクト部CHが設けられ、各コンタクト部CHは層間絶縁膜5上の配線WRに接続されている。

【0045】

なお、各抵抗素子30もコンタクト部CHを介して絶縁膜5上の配線WLに接続されている。配線WLはコンタクト部CPを介してスパイラルインダクタSIに電気的に接続される配線である。

【0046】

なお、層間絶縁膜5上にはさらに層間絶縁膜が多層に形成されるが、図3においては簡略化のため図示は省略している。

【0047】

また、図5に示すように、MOSトランジスタ10が配設される領域NRのボディ固定領域BR1とMOSトランジスタ10のゲート電極12直下のSOI層3とは、部分分離構造を有するトレンチ分離絶縁膜4Aの下部のSOI層3を介して電気的に接続される構成となっている。なお、この構造は領域PRのボディ固定領域BR2とMOSトランジスタ20のゲート電極22直下のSOI層3との間でも同じである。

【0048】

このようにMOSトランジスタ10は、トレンチ分離絶縁膜4Aの下部のSOI層3を通じてボディ固定領域BR1との間でキャリアの移動が可能であり、キャリアがチャネル形成領域に溜まるということを防止でき、またチャネル形成領域の電位を固定することができるので、基板浮遊効果を抑制できる。

10

20

30

40

50

## 【0049】

また、図2に示したようにN MOS領域NRとPMOS領域PRとの間に配設されるトレンチ分離絶縁膜4は併合分離構造を有し、上記2つの領域を完全に電気的に分離することができるので、ラッチアップの発生を防止することが可能となる。

## 【0050】

また、併合分離構造の形成においては、その過程で部分分離構造を形成する工程を経るので、部分分離構造は、併合分離構造の形成過程で形成することができ、効率的な製造が可能となる。このように、併合分離構造(HTI)は非常に理想的なデバイス構造と言える。

## 【0051】

10

<B. 製造方法>

## &lt;B-1. トレンチ分離絶縁膜の形成&gt;

まず、製造工程を順に示す図6～図13を用いて、トレンチ分離絶縁膜4の製造方法について説明する。なお、図6～図13では抵抗領域のみを例示しており、半導体素子領域は省略している。

## 【0052】

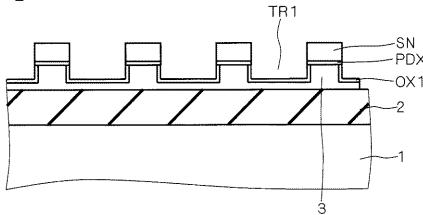

図6に示す工程において、SIMOX法や貼り合わせ法などにより形成した、シリコン基板1、埋め込み酸化膜2およびSOI層3で構成されるSOI基板SBを準備する。通常、SOI層3の膜厚は50～200nm、埋め込み酸化膜2の膜厚は100～400nmである。なお、この状態でのSOI層3の不純物濃度は $1 \times 10^{16} / \text{cm}^3$ 未満である。

20

## 【0053】

なお、シリコン基板1に高比抵抗(1000 $\cdot$ cm以上)の基板を採用することにより、アナログ・デジタル回路間のクロストークを抑制でき、また、スパイラルインダクタなどの受動素子の高性能化(高Q値化)が可能となり、高周波アナログ回路に適した構成となる。

## 【0054】

そして、SOI層3上に、熱酸化により厚さ5～30nmのパッド酸化膜PDXを形成した後、パッド酸化膜PDX上に、CVD法により600～800 $^{\circ}\text{C}$ の形成温度で厚さ100～200nmのシリコン窒化膜SNを堆積する。

30

## 【0055】

その後、シリコン窒化膜SN上にパターニングによりレジストマスクRM1を形成する。レジストマスクRM1は、トレンチを形成するための開口部を有している。

## 【0056】

続いて、図7に示す工程においてレジストマスクRM1をマスクとしてシリコン窒化膜SN、パッド酸化膜PDXおよびSOI層3をエッチングによりパターニングし、SOI層3に部分トレンチTR1を形成する。このエッチングにおいては、SOI層3を完全にエッチングして埋め込み酸化膜2を露出させるのではなく、トレンチTR1の底部に所定厚さのSOI層3が残るようにエッチング条件を調整する。

40

## 【0057】

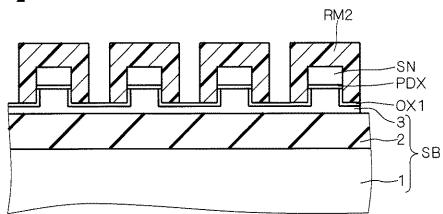

次に、レジストマスクRM1を除去した後、図8に示す工程において、露出したSOI層3を700～1100 $^{\circ}\text{C}$ の温度で熱酸化して、5～30nmの厚さのシリコン酸化膜OX1を形成する。

## 【0058】

次に、図9に示す工程において、SOI基板SB上にパターニングによりレジストマスクRM2を形成する。レジストマスクRM2は、トレンチTR1の所定部分だけが開口部となるようなパターンを有している。より具体的には、後に形成される併合分離構造のトレンチ分離絶縁膜4(図3)のうち、SOI層3を貫通して埋め込み酸化膜2に達する部分に対応する領域のみが開口部となつたパターンを有している。

50

## 【0059】

そして、図10に示す工程においてレジストマスクRM2の開口パターンに合わせてトレンチTR1をエッチングし、埋め込み酸化膜2を露出させるようにエッチングしてトレンチTR2を形成し、レジストマスクRM2を除去する。

#### 【0060】

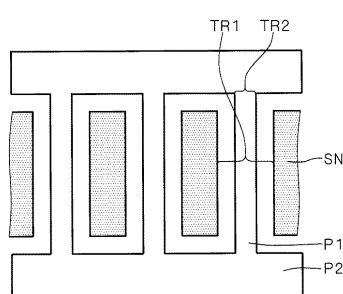

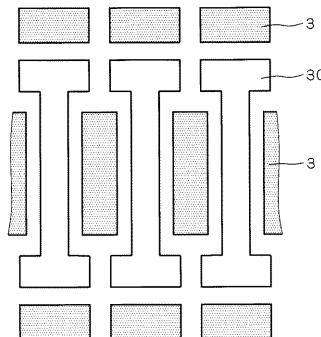

ここで、図14にレジストマスクRM2を除去した状態でのSOI基板SBの上平面の平面図を示す。

#### 【0061】

図14に示すようにトレンチTR2の平面視形状は、細長形状を有する複数の第1の領域P1が間隔を開けて短手方向に並列に形成され、各第1の領域P1の長手方向の両端部には、全端部間に渡るように細長形状の第2の領域P2がそれぞれ形成されている。なお、第1の領域P1および第2の領域P2においてはその底部に埋め込み酸化膜2が露出していることは言うまでもない。

#### 【0062】

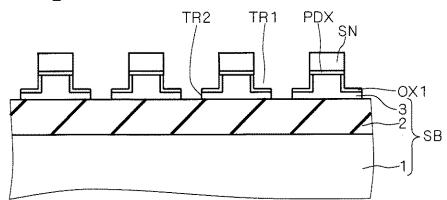

次に、図11に示す工程において、SOI基板全域に渡って厚さ150～600nmのシリコン酸化膜OX2を形成し、シリコン酸化膜OX2によりトレンチTR1およびTR2を完全に埋め込む。

#### 【0063】

シリコン酸化膜OX2は、例えばHDP(High Density Plasma)-CVD法によって形成される。HDP-CVD法は、一般的なプラズマCVDよりも1桁～2桁高い密度のプラズマを使用し、スパッタリングとデポジションを同時にいながら酸化膜を堆積するものであり、膜質の良好なシリコン酸化膜を得ることができる。

#### 【0064】

なお、シリコン酸化膜OX2はトレンチTR1およびTR2内を越えてSOI基板SBの全面を覆うように形成されるので、少なくともシリコン窒化膜SNの表面が露出する程度までCMP処理によりシリコン酸化膜OX2を研磨して平坦化する。このときシリコン窒化膜SNを半分程度の厚さになるまで研磨しても良い。

#### 【0065】

次に、図12に示す工程において、シリコン窒化膜SNおよびパッド酸化膜PDXを、ウェットエッチングまたはドライエッチングにより除去することで、併合分離構造のトレンチ分離絶縁膜4を得る。

#### 【0066】

トレンチ分離絶縁膜4を形成することで、その間に位置するSOI層3を電気的に独立した構成にすることが可能となる。

#### 【0067】

なお、図12においてはトレンチ分離絶縁膜4の部分分離構造に対面するSOI層3の表面にはシリコン酸化膜OX1が存在するように示されているが、図2においては両者は一体化したものとして扱い、記載を省略している。

#### 【0068】

なお、ここまででの工程で、図2に示したNMOSENTRAL領域NRとPMOS領域PRとの間を電気的に分離するトレンチ分離絶縁膜4や、図5に示した部分分離構造を有するトレンチ分離絶縁膜4Aも同時に形成されている。

#### 【0069】

次に、図13に示す工程において、SOI基板SBの全面を覆うようにポリシリコン膜を堆積し、パターニングすることでトレンチ分離絶縁膜4上に所望の形状の抵抗素子30を形成する。なお、抵抗素子30の形成については、以下に説明する半導体素子の製造方法で、より具体的に説明する。

#### 【0070】

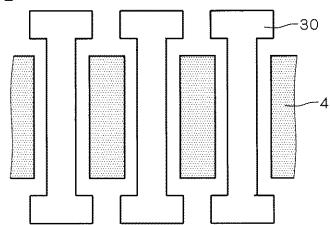

ここで、図15に、抵抗素子30をパターニングした状態でのSOI基板SBの上平面の平面図を示す。

#### 【0071】

10

20

30

40

50

図15に示すように、トレンチTR1の平面視形状はアルファベットのI字形状をなし、細長形状の胴体部が図14に示した第1の領域P1に対応する位置に配置され、長手方向両端の面積が広くなっている部分が図14に示した第2の領域P2に対応する位置に配置され、当該部分が電気的なコンタクト部となる。

#### 【0072】

なお、トレンチTR2の平面視形状を図14に示したような形状とすると、トレンチ分離絶縁膜4で完全に囲まれるSOI層3が存在することとなり、当該SOI層3を電気的に独立した構成にすることが可能となる。

#### 【0073】

なお、上記SOI層3は電気的にフローティング状態となるが、このSOI層3の電位を固定したい場合には、コンタクト部を接続させれば良い。 10

#### 【0074】

また、トレンチTR2の平面視形状を図14に示すような形状とせず、第2の領域P2を分割して、トレンチTR2で完全に囲まれるSOI層3が存在しない構成としても良い。

#### 【0075】

##### < B - 2 . 半導体素子の形成 >

次に、製造工程を順に示す図16～図25を用いて、半導体素子の製造方法について説明する。なお、図16～図25では抵抗領域および半導体素子領域を例示している。

#### 【0076】

まず、図6～図12を用いて説明した工程を経て、SOI層3の所定部分の表面内にトレンチ分離絶縁膜4や、部分分離構造を有するトレンチ分離絶縁膜（図示せず）を配設する。そして、SOI層3上には熱酸化により厚さ5～30nmのパッド酸化膜PDX1を形成する。なお、パッド酸化膜PDX1を新たに配設する代わりに、図6を用いて説明した工程で形成されたパッド酸化膜PDXを除去せずに残しても良い。 20

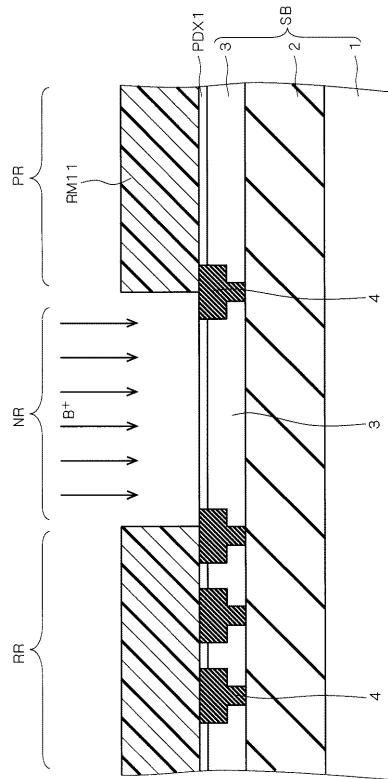

#### 【0077】

その後、図16に示す工程においてSOI基板SB上に、NMOS領域NRが開口部となつたレジストマスクRM11をパターニングし、当該開口部からボロン（B）などのP型不純物をSOI層3内にイオン注入する（チャネル注入）。この注入はトランジスタのしきい値電圧を設定するための注入であり、SOI層3の主面近傍に不純物層が形成されるように注入エネルギーが設定される。 30

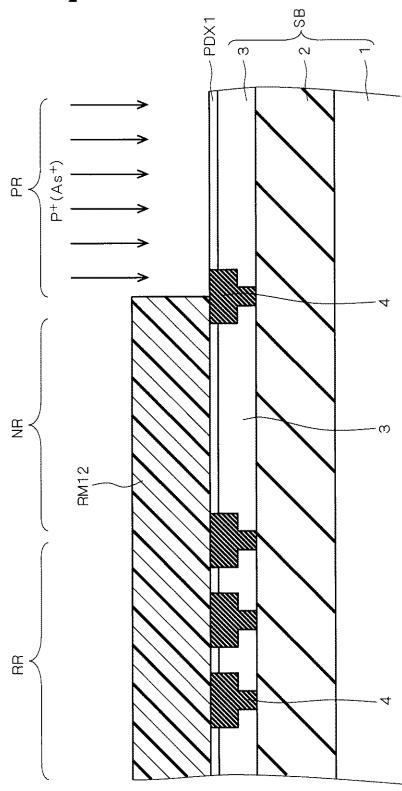

#### 【0078】

次に、レジストマスクRM11を除去した後、図17に示す工程において、PMOS領域PRが開口部となつたレジストマスクRM12をパターニングし、当該開口部からリン（P）、ヒ素（As）などのN型不純物をSOI層3内にイオン注入する（チャネル注入）。

#### 【0079】

以上説明した何れのチャネル注入においても、抵抗領域RRのSOI層3には不純物が注入されないので、抵抗領域RRのSOI層3の不純物濃度が高まることが防止され、SOI層3を高抵抗に保つことができ、また、電圧条件によっては完全空乏状態が可能となり、抵抗素子30の寄生容量の低容量化が可能となる。 40

#### 【0080】

すなわち、トレンチ分離絶縁膜4は、中央部分においては完全分離構造となっているので、この部分の寄生容量は小さいが、両端縁部においては、その下部にSOI層3を有した部分分離構造となっている。従って、この部分では、シリコン酸化膜の厚さが薄いので容量成分が大きくなるが、SOI層3が完全空乏状態であればシリコン酸化膜の厚さが厚くなつたことと実質的に等価となり、この部分での寄生容量を低くできる。

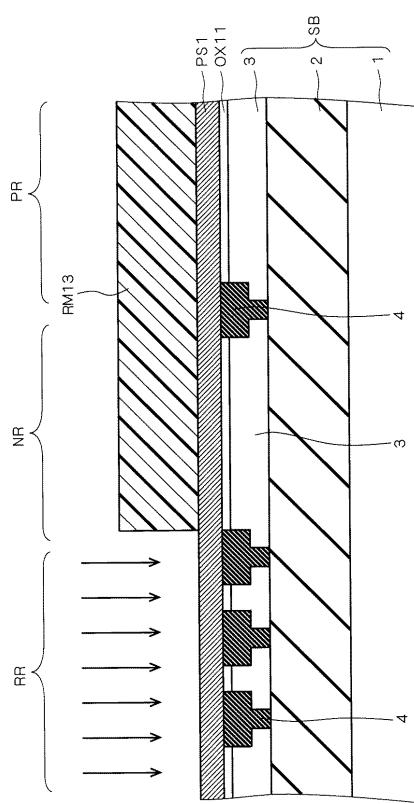

#### 【0081】

次に、レジストマスクRM12を除去した後パッド酸化膜PDX1を全て除去し、図18に示す工程において、露出したSOI層3の表面に、ゲート絶縁膜となるシリコン酸化

10

20

30

40

50

膜OX11を形成する。その後、SOI基板SBの全面に例えればCVD法により、後にゲート電極11、21および抵抗素子30となるポリシリコン層PS1を堆積する。このときの堆積温度は600～800が選択される。また、400～600の温度条件でスパッタリング法により形成しても良い。

#### 【0082】

その後、ポリシリコン層PS1上に、抵抗領域RRが開口部となつたレジストマスクRM13をパターニングし、当該開口部から不純物をポリシリコン層PS1内にイオン注入する。このときの不純物はP型(B)でもN型(P、As)でも良く、ドーズ量は $0.2 \times 10^{15} \sim 5 \times 10^{15} / \text{cm}^2$ とする。この注入で、ポリシリコン層PS1の抵抗値を設定することができる。このように抵抗素子30をポリシリコンで構成することで抵抗値を任意に設定することができる。10

#### 【0083】

なお、ゲート電極として使用されるNMOS領域NRおよびPMOS領域PRのポリシリコン層PS1に不純物を注入して(ゲート注入)、ゲート電極とシリコン層との仕事関数差を小さくし、ゲートの空乏化を抑制してしきい値電圧を下げるなどを企図する場合には、レジストマスクRM13の代わりに、NMOS領域NRあるいはPMOS領域PRの何れか一方と抵抗領域RRとが開口部となつたレジストマスクを形成し、当該開口部から不純物をイオン注入すれば良い。この場合、NMOS領域NRのポリシリコン層PS1と同時に注入するのであればN型の不純物を、PMOS領域PRのポリシリコン層PS1と同時に注入するのであればP型の不純物を注入する。20

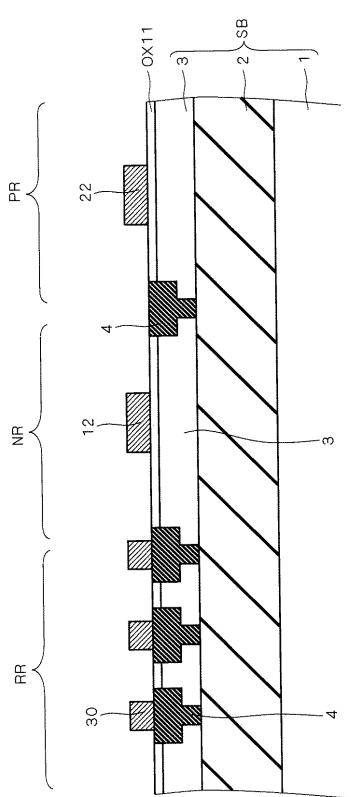

#### 【0084】

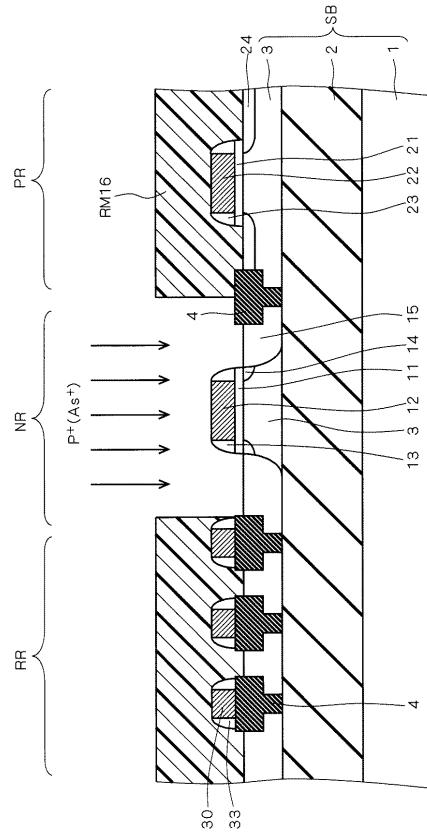

次に、レジストマスクRM13を除去した後、図19に示す工程において、NMOS領域NRおよびPMOS領域PRでは、それぞれシリコン酸化膜OX11上にゲート電極12および22を形成するようにポリシリコン層PS1をパターニングし、抵抗領域RRではトレンチ分離絶縁膜4上に抵抗素子30を形成するようにポリシリコン層PS1をパターニングする。

#### 【0085】

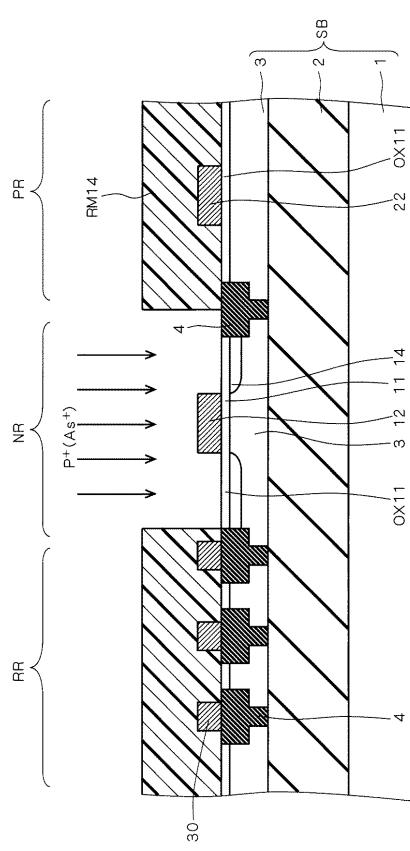

次に、図20に示す工程において、SOI基板SB上に、NMOS領域NRが開口部となつたレジストマスクRM14をパターニングし、当該開口部からN型不純物(例えばPやAs)をSOI層3内にイオン注入してエクステンション層14を形成する(エクステンション注入)。このとき、ゲート電極12が注入マスクとなる。30

#### 【0086】

次に、レジストマスクRM14を除去した後、図21に示す工程において、SOI基板SB上に、PMOS領域PRが開口部となつたレジストマスクRM15をパターニングし、当該開口部からP型不純物(例えばB)をSOI層3内にイオン注入してエクステンション層24を形成する(エクステンション注入)。このとき、ゲート電極22が注入マスクとなる。

#### 【0087】

以上説明した何れのエクステンション注入においても、抵抗領域RRのSOI層3には不純物が注入されないので、抵抗領域RRのSOI層3の不純物濃度が高まることが防止され、SOI層3を高抵抗に保つことができ、また、電圧条件によっては完全空乏状態が可能となり、抵抗素子30の寄生容量の低容量化が可能となる。40

#### 【0088】

次に、レジストマスクRM15を除去した後、ゲート電極12および22の側面に、例えばシリコン酸化膜で、それぞれサイドウォール絶縁膜13および23を、抵抗素子30の側面にサイドウォール絶縁膜33を形成する。このとき、シリコン酸化膜OX11の不要部分が除去され、ゲート電極12および22の下にゲート絶縁膜11および21が形成される。

#### 【0089】

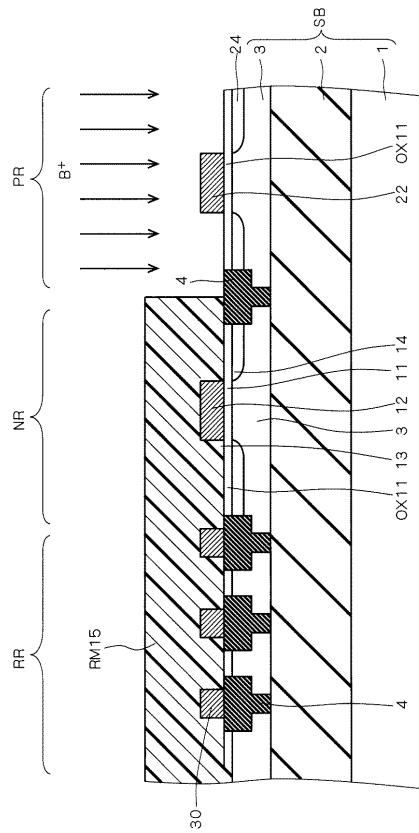

その後、図22に示す工程において、SOI基板SB上に、NMOS領域NRが開口部

10

20

30

40

50

となったレジストマスク R M 1 6 をパターニングし、当該開口部から N 型不純物（例えば P や A s ）を S O I 層 3 内にイオン注入してソース・ドレイン層 1 5 を形成する（ソース・ドレイン注入）。このとき、ゲート電極 1 2 およびサイドウォール絶縁膜 1 3 が注入マスクとなる。

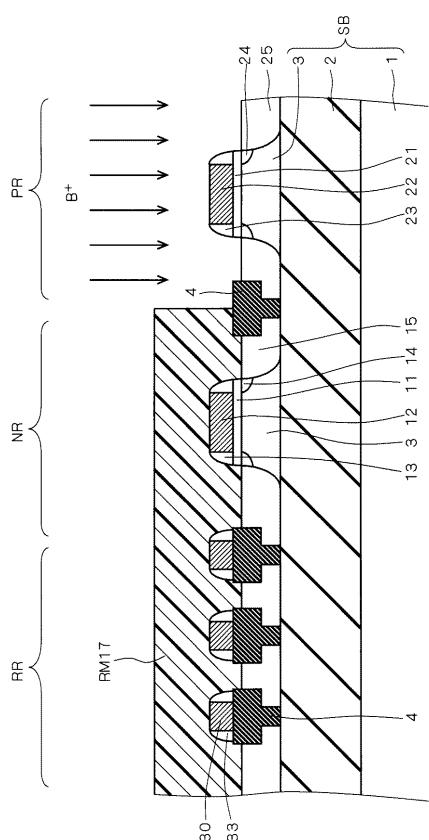

#### 【 0 0 9 0 】

次に、レジストマスク R M 1 6 を除去した後、図 2 3 に示す工程において、S O I 基板 S B 上に、P M O S 領域 P R が開口部となったレジストマスク R M 1 7 をパターニングし、当該開口部から P 型不純物（例えば B ）を S O I 層 3 内にイオン注入してソース・ドレイン層 2 5 を形成する（ソース・ドレイン注入）。このとき、ゲート電極 2 2 およびサイドウォール絶縁膜 2 3 が注入マスクとなる。 10

#### 【 0 0 9 1 】

以上説明した何れのソース・ドレイン注入においても、抵抗領域 R R の S O I 層 3 には不純物が注入されないので、抵抗領域 R R の S O I 層 3 の不純物濃度が高まることが防止され、S O I 層 3 を高抵抗に保つことができ、また、電圧条件によっては完全空乏状態が可能となり、抵抗素子 3 0 の寄生容量の低容量化が可能となる。

#### 【 0 0 9 2 】

なお、エクステンション層の先端からさらに突出するように、イオン注入によりソース・ドレイン層とは反対の導電型の不純物層（ポケット層）を形成する場合があるが、その場合も、抵抗領域 R R の S O I 層 3 には不純物が注入されないようにする。

#### 【 0 0 9 3 】

次に、レジストマスク R M 1 7 を除去した後、図 2 4 に示す工程において、C V D 法により、S O I 基板 S B の正面全面を覆うように、厚さ 1 0 ~ 1 0 0 n m のシリサイドプロテクション膜 S P を形成する。シリサイドプロテクション膜 S P はシリコン酸化膜やシリコン窒化膜などの絶縁膜で構成される。 20

#### 【 0 0 9 4 】

シリサイドプロテクション膜 S P はシリサイド膜の形成を望まない部分を保護するための膜であるので、シリサイド膜の形成を望む部分が開口部となったレジストマスク R M 1 8 を形成して、当該開口部に露出するシリサイドプロテクション膜 S P をエッティングにより除去する。

#### 【 0 0 9 5 】

なお、図 2 4 では抵抗領域 R R はレジストマスク R M 1 8 で覆われるよう示されているが、図 2 および図 4 を用いて説明したように、抵抗素子 3 0 の長手方向の両端部上にはシリサイド膜 S S を形成するので、当該部分はレジストマスク R M 1 8 で覆われていない。 30

#### 【 0 0 9 6 】

次に、レジストマスク R M 1 8 を除去した後、図 2 5 に示す工程において、S O I 基板 S B の全面に渡って C o （コバルト）などの高融点金属層をスパッタリング法で形成し、熱処理によりシリコンとのシリサイド反応を起こさせてシリサイド膜 S S を形成する。なお、シリサイド反応は絶縁膜との間では起きないので、サイドウォール絶縁膜 1 3 および 2 3 上や、シリサイドプロテクション膜 S P 上には未反応の高融点金属層が残り、これを除去することで、ゲート電極 1 2 および 2 2 の上部、ソース・ドレイン層 1 5 および 2 5 の上部に、それぞれシリサイド膜 S S を選択的に形成できる。 40

#### 【 0 0 9 7 】

なお、高融点金属層としては C o に限定されず、チタン（ T i ）、タンゲステン（ W ）、モリブデン（ M o ）や N i （ニッケル）などシリサイド反応を起こす金属であって、コンタクト部との接触抵抗を低減できる金属であれば何でも良い。

#### 【 0 0 9 8 】

その後、S O I 基板 S B の正面全面に渡って層間絶縁膜 5 を形成し、層間絶縁膜 5 を貫通してシリサイド膜 S S に達するコンタクト部 C H を設け、コンタクト部 C H に配線層 W R や W L を接続する。そして、層間絶縁膜 5 の上方にスパイラルインダクタ S I を形成す 50

ることで、図3に示すSOIデバイス100が形成される。

【0099】

< C . 特徴的効果 >

以上説明したSOIデバイス100においては、スパイラルインダクタSIの下方に対応する抵抗領域RRのSOI層3の表面内に、併合分離構造のトレンチ分離絶縁膜4をSOI層3を間に挟むようにして飛び飛びに配置するようにしたので、単一のトレンチ分離絶縁膜が広い面積に渡って存在する事がないので、トレンチ分離絶縁膜4の形成時のCMP処理においてディッキングが発生することを防止できる。

【0100】

そして、抵抗領域RRにはディッキングが発生しないので、スパイラルインダクタSIの下方に対応する領域を有効に利用して抵抗素子30を配設することができ、装置面積が増大する事がない。

【0101】

また、スパイラルインダクタSIの下方に抵抗素子30を配設できるので、高周波アナログ回路等の形成に有利な構成となる。

【0102】

また、抵抗領域RRのSOI層3には、半導体素子の形成時に不純物が導入されることを防止しているので、SOI層3を高抵抗に保つことができ、また、電圧条件によっては完全空乏化が可能となり、トレンチ分離絶縁膜4上に配設される抵抗素子30の寄生容量の低容量化が可能となり、高周波動作に有利となる。

【0103】

また、NMOS領域NRとPMOS領域PRとの間は、トレンチ分離絶縁膜4で電気的に分離するが、図5を用いて説明したように、NMOS領域NRではボディ固定領域BR1とMOSトランジスタ10のゲート電極12直下のSOI層3とは、部分分離構造を有するトレンチ分離絶縁膜4Aの下部のSOI層3を介して電気的に接続される構成となっている（これはPMOS領域PRでも同様）、基板浮遊効果を抑制でき、キャリア（NMOSトランジスタではホール）がチャネル形成領域に溜まり、これによりキックが発生することを防止でき、アナログ回路に適した構成となっている。

【0104】

また、チャネル形成領域の電位が安定しないために遅延時間の周波数依存性が発生するということも防止され、回路設計においてタイミングマージンを多めに設定する必要がなくなるので、高速動作を最大限に活用できることとなり、デジタル回路に適した構成となっている。

【0105】

< D . 変形例1 >

以上説明した実施の形態では、抵抗領域RRのSOI層3には、半導体素子の形成時に不純物が導入されることを防止して、SOI層3を高抵抗に保つこと、あるいは電圧条件によっては完全空乏化が可能となるように構成したが、例えば、ソース・ドレイン注入に際して抵抗素子30にも不純物を注入すると、抵抗素子30の抵抗値を低くできる。このとき、抵抗領域RRにおいては、抵抗領域RR上全域を開口部とするレジストマスクを形成するのではなく、抵抗素子30の上部だけが開口部となつたレジストマスクを形成することで、トレンチ分離絶縁膜4間のSOI層3には不純物が注入されることを防止できる。

【0106】

なお、このような開口部を有するレジストマスクを形成するには、レジストマスクのパターニングマージンを考慮して、抵抗領域RRのトレンチ分離絶縁膜4の幅を広く設定することが望ましい。

【0107】

但し、装置面積の関係上、抵抗領域RRのトレンチ分離絶縁膜4の幅を広げることが許容されず、抵抗素子30の上部だけが開口部となつたレジストマスクを形成できない場合

10

20

30

40

50

もあるが、それでも抵抗素子 30 の抵抗値を低くすることに主眼を置くのであれば、半導体素子の形成時に抵抗領域 R R の S O I 層 3 に不純物が導入されることとなつても構わない。この場合でも、トレンチ分離絶縁膜 4 の中央部分においては完全分離構造となつてゐるので、この部分の寄生容量は小さく、トレンチ分離絶縁膜 4 の端縁部で寄生容量が多少増加しても、その影響は少ないからである。

#### 【 0 1 0 8 】

< E . 变形例 2 >

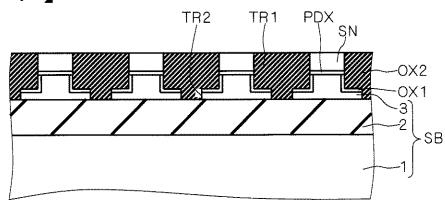

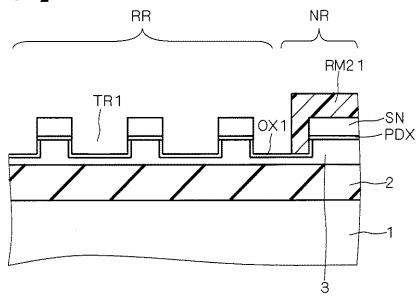

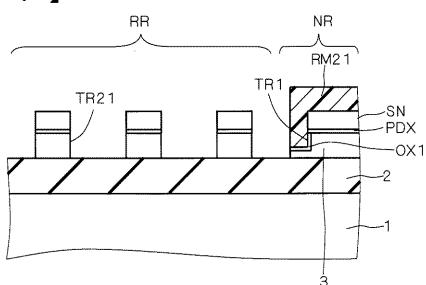

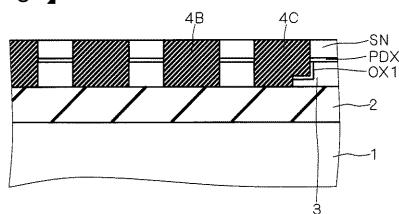

以上説明した実施の形態では、抵抗領域 R R においては併合分離構造のトレンチ分離絶縁膜 4 を S O I 層 3 を間に挟むようにして飛び飛びに配置し、その上に抵抗素子 30 を配設したが、トレンチ分離絶縁膜 4 の代わりに、完全分離構造のトレンチ分離絶縁膜を配設するようにしても良い。以下、当該構成について製造工程を順に示す図 2 6 ~ 図 2 9 を用いて説明する。

#### 【 0 1 0 9 】

図 6 ~ 図 8 を用いて説明した工程を経て、トレンチ T R 1 の内壁にシリコン酸化膜 O X 1 を形成した後、図 2 6 に示す工程において、N M O S 領域 N R との境界部のトレンチ T R 1 の N M O S 領域 N R 側の半分および N M O S 領域 N R の所定部分をレジストマスク R M 2 1 で覆う。このとき、残りの抵抗領域 R R 上にはレジストを配設せず開口部とする。

#### 【 0 1 1 0 】

次に、図 2 7 に示す工程において、シリコン窒化膜 S N をエッチングマスクとしてトレンチ T R 1 をエッチングし、埋め込み酸化膜 2 を露出させる。このエッチングにより、トレンチ T R 1 は全体的にエッチングされて、その底部に埋め込み酸化膜 2 が露出する完全トレンチ T R 2 1 となる。なお、N M O S 領域 N R との境界部のトレンチ T R 1 においては、半分だけが完全トレンチ T R 2 1 となっている。

#### 【 0 1 1 1 】

次に、レジストマスク R M 2 1 を除去した後、図 2 8 に示す工程において、S O I 基板全域に渡って厚さ 15 ~ 600 nm のシリコン酸化膜 O X 2 を形成し、シリコン酸化膜 O X 2 によりトレンチ T R 2 1 および T R 1 を完全に埋め込む。なお、この工程は図 1 1 を用いて説明した工程と同じであるので、重複する説明は省略する。

#### 【 0 1 1 2 】

次に、図 2 9 に示す工程において、シリコン窒化膜 S N およびパッド酸化膜 P D X を、ウェットエッチングまたはドライエッチングにより除去することで、完全分離構造のトレンチ分離絶縁膜 4 B および、半分が部分分離構造で、半分が完全分離構造のトレンチ分離絶縁膜 4 C を得る。その後、トレンチ分離絶縁膜 4 B および 4 C 上に所望の形状の抵抗素子 30 を形成する。

#### 【 0 1 1 3 】

このような構成を採用することで、抵抗素子 30 が形成されるトレンチ分離絶縁膜 4 B は完全分離構造となり、抵抗素子 30 の寄生容量の低容量化をさらに促進できる。

#### 【 0 1 1 4 】

また、抵抗領域 R R では、レジストマスクのパターニングが不要になるため、パターニングマージンを見込む必要がなくなるので、トレンチ T R 1 の幅や、配設間隔を狭くすることができ、結果的に抵抗素子 30 の配設間隔を狭くすることが可能となつてさらなる高集積化が可能となる。

#### 【 0 1 1 5 】

< F . 变形例 3 >

以上説明した実施の形態では、抵抗領域 R R の S O I 層 3 には、半導体素子の形成時に不純物が導入されることを防止しているので、S O I 層 3 を高抵抗に保つこと、あるいは電圧条件によっては完全空乏化が可能となることを説明したが、これは分離絶縁膜にも不純物が導入されないことを意味しており、その結果、素子領域に比べて、分離絶縁膜の膜厚を厚くすることが可能となる。

#### 【 0 1 1 6 】

10

20

30

40

50

すなわち、分離絶縁膜に不純物を注入すると、その後に行われるシリコン酸化膜除去のためのHF(フッ酸)処理でのエッチングレートが増大する。

#### 【0117】

例えば、図16を用いて説明したように、チャネル注入に際してはパッド酸化膜PD<sub>X</sub>1を介してイオン注入を行い、注入後にはパッド酸化膜PD<sub>X</sub>1を除去する。このとき、HF処理を使用すると、NMOS領域NRおよびPMOS領域PRのトレンチ分離絶縁膜4にはチャネル注入の不純物が注入されているので、抵抗領域RRのトレンチ分離絶縁膜4に比べてエッチングの進行が早く、厚さが薄くなる。同様の現象は、ゲート絶縁膜11および21の形成工程においても生じる。

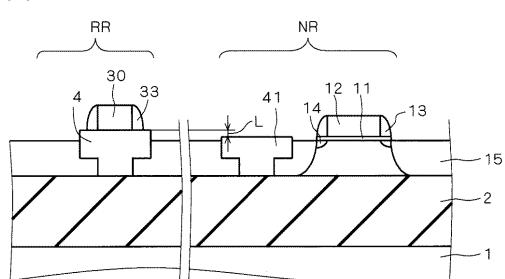

#### 【0118】

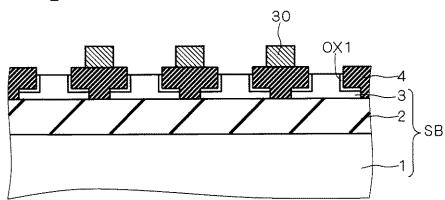

図30には、Nチャネル型のトランジスタ10を形成した段階でのNMOS領域NRおよび抵抗領域RRの断面構成を示す。

#### 【0119】

図30に示すように、抵抗領域RRのトレンチ分離絶縁膜4(第1の素子分離絶縁膜)は、NMOS領域NRのトレンチ分離絶縁膜41(第2の素子分離絶縁膜)よりも厚さLだけ厚くなっている。この構成により抵抗素子30の寄生容量の増大を防止できる。

#### 【0120】

この厚さLは、パッド酸化膜PD<sub>X</sub>1の除去からサイドウォール酸化膜形成までの全ての工程における総エッチング量の差に相当するものである。

#### 【0121】

なお、以上説明した実施の形態以外にも、例えば、3.3Vの入出力(I/O)トランジスタなどのように、ゲート絶縁膜の厚さ異なるデバイスが複数種類存在する場合には、素子領域ではシリコン酸化膜の除去や形成を繰り返すこと(デュアルオキサイドプロセス)があるが、その場合でも抵抗領域RRについてはレジストマスクによりエッチングを受けないように保護することで、分離絶縁膜の膜厚さが減ることを抑制でき、寄生容量の増大を防止できる。

#### 【0122】

##### <G.変形例4>

以上説明した実施の形態では、抵抗領域RRのSOI層3の表面内に、併合分離構造のトレンチ分離絶縁膜4をSOI層3を間に挟むようにして飛び飛びに配置することで、トレンチ分離絶縁膜4の形成時のCMP処理においてディッシングが発生することを防止する構成を示したが、SOI層3の配設はトレンチ分離絶縁膜4の間、すなわち抵抗素子30の間に限定されるものではなく、例えば図31に示すように、抵抗素子30の長手方向の両端部外側の位置に配置しても良い。

#### 【0123】

このような配置とすることで、CMP処理においてトレンチ分離絶縁膜4にディッシングが生じることがさらに抑制され、トレンチ分離絶縁膜4の膜厚均一性がさらに向上する。

#### 【0124】

##### <H.変形例5>

以上説明した実施の形態およびその変形例では、抵抗領域RRのSOI層3の表面内に設けられた併合分離構造のトレンチ分離絶縁膜4あるいは完全分離構造のトレンチ分離絶縁膜4B上に抵抗素子30を配設する構成を示したが、SOI層3上に抵抗素子を配設する構成としても良い。当該構成について図32を用いて説明する。

#### 【0125】

図32には、Nチャネル型のトランジスタ10を形成した段階でのNMOS領域NRおよび抵抗領域RRの断面構成を示している。

#### 【0126】

図32に示すように、抵抗領域RRにおいては、トレンチ分離絶縁膜4で挟まれるSOI層3上に、絶縁膜35を介して抵抗素子30Aが配設されている。そして、絶縁膜35

10

20

30

40

50

および抵抗素子 30A の側面を覆うようにサイドウォール酸化膜 33 が配設されている。

【0127】

このような構成を採ることによっても、スパイラルインダクタ S1 の下方に抵抗素子 30 を配設できる。

【0128】

この場合も、抵抗領域 RR の SOI 層 3 には、素子領域での不純物注入に際して、不純物が注入されないように保護する。

【0129】

なお、絶縁膜 35 は、図 16 に示したパッド酸化膜 PDX1 を、抵抗領域 RR においては除去せずに残し、図 19 を用いて説明したシリコン酸化膜 OX11 の形成に際しては、パッド酸化膜 PDX1 上にシリコン酸化膜 OX11 を形成することで実現できる。これにより、絶縁膜 35 の厚さはパッド酸化膜 PDX1 とシリコン酸化膜 OX11 の厚さの合計の厚さにすることができ、その上に形成される抵抗素子 30 の寄生容量を低減することができる。

10

【0130】

また、例えば、3.3V の入出力 (I/O) ドライバなどのように、ゲート絶縁膜の厚さ異なるデバイスが複数種類存在する場合には、素子領域では厚さの異なるゲート絶縁膜を形成するが、その場合には、シリコン酸化膜の除去や形成を繰り返すこと（デュアルオキサイドプロセス）がある。このとき、素子領域でのシリコン酸化膜の除去に際しては抵抗領域 RR はレジストマスクで覆うなどして、抵抗領域 RR の SOI 層 3 上においては一旦形成したシリコン酸化膜は除去しないこととする。これにより、SOI 層 3 上には分厚いシリコン酸化膜が形成されることになり、その上に抵抗素子 30 を形成すれば抵抗素子 30 の寄生容量を大幅に低減することができる。

20

【0131】

また、以上の説明においては、素子分離絶縁膜はシリコン酸化膜で構成されるものとして説明したが、シリコン窒化膜で構成しても良い。

【図面の簡単な説明】

【0132】

【図 1】バッファ回路の構成を示す図である。

30

【図 2】本発明に係る実施の形態の半導体装置の平面構成を説明する図である。

【図 3】本発明に係る実施の形態の半導体装置の断面構成を説明する図である。

【図 4】本発明に係る実施の形態の半導体装置の断面構成を説明する図である。

【図 5】本発明に係る実施の形態の半導体装置の断面構成を説明する図である。

【図 6】本発明に係る実施の形態の半導体装置の抵抗領域の製造方法を説明する断面図である。

【図 7】本発明に係る実施の形態の半導体装置の抵抗領域の製造方法を説明する断面図である。

【図 8】本発明に係る実施の形態の半導体装置の抵抗領域の製造方法を説明する断面図である。

40

【図 9】本発明に係る実施の形態の半導体装置の抵抗領域の製造方法を説明する断面図である。

【図 10】本発明に係る実施の形態の半導体装置の抵抗領域の製造方法を説明する断面図である。

【図 11】本発明に係る実施の形態の半導体装置の抵抗領域の製造方法を説明する断面図である。

【図 12】本発明に係る実施の形態の半導体装置の抵抗領域の製造方法を説明する断面図である。

【図 13】本発明に係る実施の形態の半導体装置の抵抗領域の製造方法を説明する断面図である。

【図 14】本発明に係る実施の形態の半導体装置の抵抗領域の製造過程における平面構成

50

を説明する図である。

【図15】本発明に係る実施の形態の半導体装置の抵抗素子およびSOI層の配設状態を説明する平面図である。

【図16】本発明に係る実施の形態の半導体装置の抵抗領域および素子領域の製造方法を説明する断面図である。

【図17】本発明に係る実施の形態の半導体装置の抵抗領域および素子領域の製造方法を説明する断面図である。

【図18】本発明に係る実施の形態の半導体装置の抵抗領域および素子領域の製造方法を説明する断面図である。

【図19】本発明に係る実施の形態の半導体装置の抵抗領域および素子領域の製造方法を説明する断面図である。 10

【図20】本発明に係る実施の形態の半導体装置の抵抗領域および素子領域の製造方法を説明する断面図である。

【図21】本発明に係る実施の形態の半導体装置の抵抗領域および素子領域の製造方法を説明する断面図である。

【図22】本発明に係る実施の形態の半導体装置の抵抗領域および素子領域の製造方法を説明する断面図である。

【図23】本発明に係る実施の形態の半導体装置の抵抗領域および素子領域の製造方法を説明する断面図である。

【図24】本発明に係る実施の形態の半導体装置の抵抗領域および素子領域の製造方法を説明する断面図である。 20

【図25】本発明に係る実施の形態の半導体装置の抵抗領域および素子領域の製造方法を説明する断面図である。

【図26】本発明に係る実施の形態の半導体装置の抵抗領域の製造方法の変形例を説明する断面図である。

【図27】本発明に係る実施の形態の半導体装置の抵抗領域の製造方法の変形例を説明する断面図である。

【図28】本発明に係る実施の形態の半導体装置の抵抗領域の製造方法の変形例を説明する断面図である。

【図29】本発明に係る実施の形態の半導体装置の抵抗領域の製造方法の変形例を説明する断面図である。 30

【図30】本発明に係る実施の形態の半導体装置の抵抗領域と素子領域とで異なる素子分離絶縁膜の厚さについて説明する図である。

【図31】本発明に係る実施の形態の半導体装置の抵抗素子およびSOI層の配設状態の変形例を説明する平面図である。

【図32】本発明に係る実施の形態の半導体装置の変形例の構成を説明する断面図である。

【符号の説明】

【0133】

2 埋め込み酸化膜、3 SOI層、4 トレンチ分離絶縁膜、30 抵抗素子、35 絶縁膜、SI スパイラルインダクタ。 40

【図1】

【図2】

【図4】

【図5】

【図3】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【図17】

【図18】

【図19】

【図20】

【 図 2 1 】

【 図 2 2 】

【 図 2 3 】

【図24】

【図25】

【図26】

【図27】

【図28】

【図29】

【図31】

【図30】

【図32】

3.5 : 絶縁膜

## フロントページの続き

| (51)Int.Cl. <sup>7</sup> | F I          | テーマコード(参考) |

|--------------------------|--------------|------------|

| H 01 L 27/06             | H 01 L 29/78 | 6 1 8 F    |

| H 01 L 27/08             | H 01 L 27/04 | L          |

| H 01 L 29/786            | H 01 L 27/06 | 1 0 2 A    |

|                          | H 01 L 21/76 | L          |

|                          | H 01 L 21/76 | D          |

F ターム(参考) 5F032 AA03 AA35 AA44 AA45 AA67 AA70 AA77 BA01 BB03 CA14

CA17 DA23 DA33

5F038 AR09 AR24 AR27 AV06 AZ04 BH19 CA18 CD04 DF12 EZ06

EZ11 EZ14 EZ15 EZ20

5F048 AA04 AC04 AC10 BA16 BB05 BB08 BB12 BC06 BC16 BD04

BE03 BF06 BF11 BF16 BF17 BF18 BG01 BG07 BG13 DA25

5F110 AA02 AA04 AA15 AA26 BB04 CC02 DD05 DD13 DD24 EE05

EE09 EE14 EE31 EE41 EE44 EE45 FF02 GG02 GG12 GG25

GG32 GG34 GG52 GG60 HJ01 HJ13 HK05 HK33 HK40 HM15

NN02 NN23 NN62 NN65 NN71 QQ11 QQ17 QQ19