(19) 대한민국특허청(KR)

(12) 공개특허공보(A)

(11) 공개번호 10-2008-0036844

(43) 공개일자 2008년04월29일

(51) Int. Cl.

G02F 1/133 (2006.01)

(21) 출원번호 10-2006-0103624

(22) 출원일자 2006년10월24일

심사청구일자 없음

(71) 출원인

삼성전자주식회사

경기도 수원시 영통구 매탄동 416

(72) 발명자

김관호

충남 천안시 두정동 세팡2차아파트 203동 1203호

(74) 대리인

정상빈, 특허법인가산

전체 청구항 수 : 총 18 항

(54) 타이밍 컨트롤러 및 이를 포함하는 액정 표시 장치

**(57) 요약**

EMI를 줄일 수 있는 타이밍 컨트롤러 및 이를 포함하는 액정 표시 장치가 제공된다. 타이밍 컨트롤러는 라인 버퍼 메모리와, 제1 데이터 정보과 상기 제2 데이터 정보를 비교하는 비교부 및 비교 결과에 따라 라인 버퍼 메모리를 동일한 메모리 크기의 제1 메모리부와 제2 메모리부로 구분하는 메모리 할당부를 포함한다.

**대표도**

## 특허청구의 범위

### 청구항 1

회로 기판;

상기 회로 기판 상에 실장되는 타이밍 컨트롤러로, 순차적으로 입력되는 제1 내지 제 $n+m$  화소 데이터를, 상기 제1 내지 제 $n$  화소 데이터를 포함하는 제1 영상 데이터 세트와 상기 제 $n+1$  내지 제 $n+m$  화소 데이터를 포함하는 제2 영상 데이터 세트로 구분하여 저장하되, 상기 제1 영상 데이터 세트의 데이터 크기는 상기 제2 영상 데이터 세트의 데이터 크기보다 작고( $m > n$ ), 상기 저장된 제1 영상 데이터 세트 및 상기 제2 영상 데이터 세트로부터 각각 1개씩의 상기 화소 데이터를 동시에 출력하는 타이밍 컨트롤러;

상기 회로 기판과 전기적으로 연결되어 상기 화소 데이터에 대응하는 데이터 전압을 다수의 데이터 라인에 제공하는 데이터 드라이버로서, 제1 내지 제 $n$  화소 데이터에 대응하는 데이터 전압을 제공하는 제1 번째 내지 제 $s$  번째 데이터 드라이브 IC를 포함하는 제1 데이터 드라이브 IC 그룹과, 상기 제 $n+1$  내지 제 $n+m$  화소 데이터에 대응하는 데이터 전압을 제공하는 제 $s+1$  번째 내지 제 $s+t$  번째 데이터 드라이브 IC를 포함하는 제2 데이터 드라이브 IC 그룹을 포함하되, 상기 제1 데이터 드라이브 IC 그룹의 데이터 드라이브 IC 개수는 상기 제2 데이터 드라이브 IC 그룹의 데이터 드라이브 IC 개수보다 작은( $t > s$ ) 데이터 드라이버; 및

상기 다수의 데이터 라인을 통해 인가된 상기 데이터 전압에 따라 영상을 표시하는 액정 패널을 포함하는 액정 표시 장치.

### 청구항 2

제 1항에 있어서,

상기 타이밍 컨트롤러는 상기 제2 영상 데이터 세트를 저장하는 제1 메모리부와, 상기 제2 영상 데이터 세트를 저장하는 제2 메모리부를 포함하는 액정 표시 장치.

### 청구항 3

제 2항에 있어서,

상기 제1 메모리부와 상기 제2 메모리부는 동일한 메모리 크기를 갖는 액정 표시 장치.

### 청구항 4

제 1항에 있어서,

상기 타이밍 컨트롤러는, 제1 메모리부와 제2 메모리부를 포함하고, 상기 제1 메모리부와 상기 제2 메모리부의 메모리 크기를 상기 제2 영상 데이터를 저장할 수 있는 메모리 크기로 할당하고, 상기 제1 메모리부에 상기 제1 영상 데이터 세트를 저장하고, 상기 제2 메모리부에 상기 제2 영상 데이터 세트를 저장하는 액정 표시 장치.

### 청구항 5

제 1항에 있어서, 상기 타이밍 컨트롤러는,

라인 버퍼 메모리와,

상기 제1 영상 데이터 세트의 데이터 크기를 나타내는 제1 데이터 정보와 상기 제2 영상 데이터 세트의 데이터 크기를 나타내는 제2 데이터 정보를 입력받아 상기 제1 영상 데이터 세트의 데이터 크기와 상기 제2 영상 데이터 세트의 데이터 크기를 비교하는 비교부와,

그 비교 결과에 따라 상기 라인 버퍼 메모리를, 상기 제2 영상 데이터 세트를 저장할 수 있는 메모리 크기를 갖는 제1 메모리부와 제2 메모리부로 구분하는 메모리 할당부를 포함하는 액정 표시 장치.

### 청구항 6

제 5항에 있어서,

상기 제1 데이터 정보와 상기 제2 데이터 정보를 상기 비교부에 제공하는 설정 메모리를 더 포함하는 액정 표시 장치.

#### 청구항 7

제 6항에 있어서,

상기 제1 데이터 정보는 상기 다수의 데이터 라인 중에서 상기 제1 데이터 드라이브 IC 그룹과 전기적으로 연결된 데이터 라인의 수이고, 상기 제2 데이터 정보는 상기 다수의 데이터 라인 중에서 상기 제2 데이터 드라이브 IC 그룹과 전기적으로 연결된 데이터 라인의 수인 액정 표시 장치.

#### 청구항 8

제 1항에 있어서,

상기 타이밍 컨트롤러는, 상기 제s 번째 데이터 드라이브 IC 및 상기 제s+1 데이터 드라이브 IC가 상기 회로 기판과 연결되는 부분 사이의 상기 회로 기판 상에 실장되는 액정 표시 장치.

#### 청구항 9

제 1항에 있어서,

상기 회로 기판은 상기 타이밍 컨트롤러로부터 상기 제1 데이터 드라이브 IC 그룹 사이에 연결되고 상기 제1 내지 제n 화소 데이터를 전달하는 제1 신호 전송 라인과, 상기 타이밍 컨트롤러로부터 상기 제2 데이터 드라이브 IC 그룹 사이에 연결되고 상기 제n+1 내지 제n+m 화소 데이터를 전달하는 제2 신호 전송 라인을 포함하고,

상기 제1 및 제2 신호 전송 라인은 각각,

상기 타이밍 컨트롤러로부터 상기 제1 내지 제n+m 화소 데이터 및 상기 제n 내지 제n+m 화소 데이터가 순차적으로 동시에 출력되는 상기 회로 기판의 제1 층의 제1 출력 라인과,

비아를 통해 상기 제1 출력 라인으로부터 상기 제1 내지 제n 화소 데이터 및 상기 제n 내지 제n+m 화소 데이터가 각각 상기 제1 번째 내지 제s 번째 데이터 드라이브 IC 및 상기 제s+1 번째 내지 제s+t 번째 데이터 드라이브 IC에 출력되는 상기 회로 기판의 제2 층의 제2 출력 라인을 포함하는 액정 표시 장치.

#### 청구항 10

제 9항에 있어서,

상기 제1 출력 라인은 다수의 굴곡부를 포함하고, 상기 굴곡부의 내각이 90도 이상인 액정 표시 장치.

#### 청구항 11

순차적으로 입력되는 제1 내지 제n+m 화소 데이터를, 상기 제1 내지 제n 화소 데이터를 포함하는 제1 영상 데이터 세트와 상기 제n+1 내지 제n+m 화소 데이터를 포함하는 제2 영상 데이터 세트로 구분하여 저장하고, 상기 저장된 제1 영상 데이터 세트 및 상기 제2 영상 데이터 세트로부터 각각 1개씩의 상기 화소 데이터를 동시에 출력하는 타이밍 컨트롤러;

상기 제1 내지 제n 화소 데이터를 입력받아 다수의 데이터 라인중 일부에 상기 제1 내지 제n 화소 데이터 각각에 대응하는 데이터 전압을 제공하는 제1 데이터 드라이브 IC 그룹과, 상기 제n+1 내지 제n+m 화소 데이터를 입력받아 상기 다수의 데이터 라인중 나머지에 상기 제n+1 내지 제n+m 화소 데이터 각각에 대응하는 데이터 전압을 제공하는 제2 데이터 드라이브 IC 그룹을 포함하는 데이터 드라이버로서, 상기 제1 데이터 드라이브 IC 그룹은 제1 번째 내지 제s 번째 데이터 드라이브 IC를 포함하고, 제2 데이터 드라이브 IC 그룹은 제s+1 번째 내지 제s+t 번째 데이터 드라이브 IC를 포함하는 데이터 드라이버; 및

상기 타이밍 컨트롤러가 실장되고, 상기 타이밍 컨트롤러로부터 상기 제1 데이터 드라이브 IC 그룹 사이에 연결되고 상기 제1 내지 제n 화소 데이터를 전달하는 제1 신호 전송 라인과, 상기 타이밍 컨트롤러로부터 상기 제2 데이터 드라이브 IC 그룹 사이에 연결되고 상기 제n+1 내지 제n+m 화소 데이터를 전달하는 제2 신호 전송 라인을 포함하는 회로 기판으로서,

상기 제1 및 제2 신호 전송 라인은 각각,

상기 타이밍 컨트롤러로부터 상기 제1 내지 제 $n+m$  화소 데이터 및 상기 제n 내지 제 $n+m$  화소 데이터가 순차적으로 동시에 출력되는 상기 회로기판의 제1 층의 제1 출력 라인과,

비아를 통해 상기 제1 출력 라인으로부터 통해 상기 제1 내지 제 $n+m$  화소 데이터 및 상기 제n 내지 제 $n+m$  화소 데이터가 각각 상기 제1 번째 내지 제s 번째 데이터 드라이브 IC 및 상기 제s+1 번째 내지 제s+t 번째 데이터 드라이브 IC에 출력되는 상기 회로기판의 제2 층의 제2 출력 라인을 포함하고, 상기 제1 출력 라인은 다수의 굴곡부를 포함하고, 상기 굴곡부의 내각이 90도 이상인 회로 기판을 포함하는 액정 표시 장치.

### 청구항 12

제 11항에 있어서,

상기 제1 영상 데이터 세트의 데이터 크기는 상기 제2 영상 데이터 세트의 데이터 크기보다 작고( $m > n$ ), 상기 제1 데이터 드라이브 IC 그룹의 데이터 드라이브 IC 개수는 상기 제2 데이터 드라이브 IC 그룹의 데이터 드라이브 IC 개수보다 작은( $t > s$ ) 액정 표시 장치.

### 청구항 13

제 12항에 있어서,

상기 타이밍 컨트롤러는, 상기 제s 번째 데이터 드라이브 IC 및 상기 제s+1 데이터 드라이브 IC가 상기 회로 기판과 연결되는 연결부 사이의 상기 회로 기판 상에 실장되는 액정 표시 장치.

### 청구항 14

제 11항에 있어서, 상기 타이밍 컨트롤러는,

라인 버퍼 메모리와,

상기 제1 영상 데이터 세트의 데이터 크기와 상기 제2 영상 데이터 세트의 데이터 크기를 비교하는 비교부와, 그 비교 결과에 따라 상기 라인 버퍼 메모리를, 상기 제2 영상 데이터 세트를 저장할 수 있는 메모리 크기를 갖는 제1 메모리부와 제2 메모리부로 구분하는 메모리 할당부를 포함하는 액정 표시 장치.

### 청구항 15

제 14항에 있어서,

상기 제1 데이터 정보와 상기 제2 데이터 정보를 상기 비교부에 제공하는 설정 메모리를 더 포함하는 액정 표시 장치.

### 청구항 16

라인 버퍼 메모리;

제1 데이터 정보과 상기 제2 데이터 정보를 비교하는 비교부; 및

그 비교 결과에 따라 상기 라인 버퍼 메모리를 동일한 메모리 크기의 제1 메모리부와 제2 메모리부로 구분하는 메모리 할당부를 포함하는 타이밍 컨트롤러.

### 청구항 17

제 16항에 있어서,

순차적으로 입력되는 제1 내지 제 $n+m$  화소 데이터를, 상기 제1 내지 제n 화소 데이터를 포함하는 제1 영상 데이터 세트와 상기 제n+1 내지 제 $n+m$  화소 데이터를 포함하는 제2 영상 데이터 세트로 구분하고, 상기 제1 데이터 정보는 상기 제1 영상 데이터 세트의 데이터 크기를 나타내고, 상기 제2 데이터 정보는 제2 영상 데이터 세트의 데이터 크기를 나타낼 때,

상기 메모리 할당부는 상기 라인 버퍼 메모리를 상기 제1 데이터 정보와 상기 제2 데이터 정보 중에서 큰 데이터 크기에 대응하는 메모리 크기를 갖는 상기 제1 메모리부와 상기 제2 메모리부로 구분하는 타이밍 컨트롤러.

## 청구항 18

제 17항에 있어서,

상기 라인 버퍼 메모리는, 상기 제1 영상 데이터 세트를 상기 제1 메모리부에 저장하고, 상기 제2 영상 데이터 세트를 제2 메모리부에 저장하고, 상기 저장된 제1 영상 데이터 세트 및 상기 제2 영상 데이터 세트로부터 각각 1개씩의 상기 화소 데이터를 동시에 출력하는 타이밍 컨트롤러.

## 명세서

### 발명의 상세한 설명

#### 발명의 목적

##### 발명이 속하는 기술 및 그 분야의 종래기술

- <16> 본 발명은 타이밍 컨트롤러 및 이를 포함하는 액정 표시 장치에 관한 것이다.

- <17> 액정 표시 장치는 영상 표시를 위해 다수의 화소 데이터를 제공하는 타이밍 컨트롤러와, 타이밍 컨트롤러로부터 제공된 화소 데이터에 대응하는 전압을 다수의 데이터 라인에 제공하는 데이터 드라이버를 포함한다.

- <18> 1-channel 구동 방식에 의하면, 타이밍 컨트롤러는 순차적으로 입력되는 다수의 화소 데이터를 입력된 순서대로 데이터 드라이버에 화소 데이터를 제공한다. 고해상도 액정 표시 장치의 경우, 데이터 라인의 수가 많아져서, 2-channel 방식으로 구동한다. 즉, 타이밍 컨트롤러는, 다수의 데이터 드라이버 IC를 포함하는 데이터 드라이버를 제1 데이터 드라이버 IC 그룹과 제2 데이터 드라이버 IC 그룹으로 구분하고, 순차적으로 입력되는 다수의 화소 데이터를 저장한 후, 제1 데이터 드라이버 IC 그룹과 제2 데이터 드라이버 IC 그룹에 각각 화소 데이터를 동시에 출력한다. 이를 위해 타이밍 컨트롤러는, 제1 데이터 드라이버 IC 그룹에 제공할 제1 영상 데이터 세트와, 제2 데이터 드라이버 IC 그룹에 제공할 제2 영상 데이터 세트를 각각 제1 메모리부와 제2 메모리부에 저장한다.

- <19> 이러한 타이밍 컨트롤러는, 다수의 화소 데이터를 입력받기 전에 제1 메모리부와 제2 메모리부의 메모리 크기를 할당할 때, 제1 영상 데이터 세트를 저장할 수 있는 메모리 크기로 제1 메모리부와 제2 메모리부의 메모리 크기를 할당한다. 따라서, 제1 영상 데이터의 데이터 크기가 제2 영상 데이터 세트의 데이터 크기보다 크도록, 다수의 데이터 드라이브 IC를 제1 데이터 드라이브 IC 그룹과 제2 데이터 드라이브 IC 그룹으로 구분하여야만 한다. 즉, 제1 데이터 드라이브 IC 그룹이 포함하는 데이터 드라이브 IC의 수는 제2 데이터 드라이브 IC 그룹이 포함하는 데이터 드라이브 IC의 수보다 크게 된다.

- <20> 이러한 경우, 타이밍 컨트롤러가 일정한 형상의 회로 기판에 실장될 때, 제1 데이터 드라이브 IC 그룹과 제2 데이터 드라이브 IC 그룹 사이의 회로 기판 상에 실장되지 못하고, 제1 데이터 드라이브 IC 그룹 쪽으로 치우쳐서 실장된다. 따라서, 제1 데이터 드라이브 IC 그룹에 화소 데이터를 전송하는 신호 전송 라인은 90도 이하의 내각을 갖는 굴곡부를 포함하게 된다. 또한, 타이밍 컨트롤러의 실장 위치가 제한적이 된다. 따라서, 전자기파 간섭 (Electro Magnetic Interference, 이하 'EMI'라 함)이 유발된다.

##### 발명이 이루고자 하는 기술적 과제

- <21> 본 발명이 이루고자 하는 기술적 과제는 EMI를 감소시키는 타이밍 컨트롤러를 제공하는 것이다.

- <22> 본 발명이 이루고자 하는 다른 기술적 과제는 EMI를 감소시키는 액정 표시 장치를 제공하는 것이다.

- <23> 본 발명의 기술적 과제는 이상에서 언급한 기술적 과제들로 제한되지 않으며, 언급되지 않은 또 다른 기술적 과제들은 아래의 기재로부터 당업자에게 명확하게 이해될 수 있을 것이다.

#### 발명의 구성 및 작용

- <24> 상기 기술적 과제를 달성하기 위한 본 발명의 일 태양에 따른 타이밍 컨트롤러는, 라인 버퍼 메모리와, 제1 데이터 정보과 상기 제2 데이터 정보를 비교하는 비교부 및 그 비교 결과에 따라 상기 라인 버퍼 메모리를 동일한 메모리 크기의 제1 메모리부와 제2 메모리부로 구분하는 메모리 할당부를 포함한다.

- <25> 상기 다른 기술적 과제를 달성하기 위한 본 발명의 일 태양에 따른 액정 표시 장치는, 회로 기판과, 상기 회로 기판 상에 실장되는 타이밍 컨트롤러로, 순차적으로 입력되는 제1 내지 제 $n+m$  화소 데이터를, 상기 제1 내지 제

n 화소 데이터를 포함하는 제1 영상 데이터 세트와 상기 제n+1 내지 제n+m 화소 데이터를 포함하는 제2 영상 데이터 세트로 구분하여 저장하되, 상기 제1 영상 데이터 세트의 데이터 크기는 상기 제2 영상 데이터 세트의 데이터 크기보다 작고( $m > n$ ), 상기 저장된 제1 영상 데이터 세트 및 상기 제2 영상 데이터 세트로부터 각각 1개씩의 상기 화소 데이터를 동시에 출력하는 타이밍 컨트롤러와, 상기 회로 기판과 전기적으로 연결되어 상기 화소 데이터에 대응하는 데이터 전압을 다수의 데이터 라인에 제공하는 데이터 드라이버로서, 제1 내지 제n 화소 데이터에 대응하는 데이터 전압을 제공하는 제1 번째 내지 제s 번째 데이터 드라이브 IC를 포함하는 제1 데이터 드라이브 IC 그룹과, 상기 제n+1 내지 제n+m 화소 데이터에 대응하는 데이터 전압을 제공하는 제s+1 번째 내지 제s+t 번째 데이터 드라이브 IC를 포함하는 제2 데이터 드라이브 IC 그룹을 포함하되, 상기 제1 데이터 드라이브 IC 그룹의 데이터 드라이브 IC 개수는 상기 제2 데이터 드라이브 IC 그룹의 데이터 드라이브 IC 개수보다 작은( $t > s$ ) 데이터 드라이버 및 상기 다수의 데이터 라인을 통해 인가된 상기 데이터 전압에 따라 영상을 표시하는 액정 패널을 포함한다.

<26> 상기 다른 기술적 과제를 달성하기 위한 본 발명의 또 다른 태양에 따른 액정 표시 장치는, 순차적으로 입력되는 제1 내지 제n+m 화소 데이터를, 상기 제1 내지 제n 화소 데이터를 포함하는 제1 영상 데이터 세트와 상기 제n+1 내지 제n+m 화소 데이터를 포함하는 제2 영상 데이터 세트로 구분하여 저장하고, 상기 저장된 제1 영상 데이터 세트 및 상기 제2 영상 데이터 세트로부터 각각 1개씩의 상기 화소 데이터를 동시에 출력하는 타이밍 컨트롤러와, 상기 제1 내지 제n 화소 데이터를 입력받아 다수의 데이터 라인 중 일부에 상기 제1 내지 제n 화소 데이터 각각에 대응하는 데이터 전압을 제공하는 제1 데이터 드라이브 IC 그룹과, 상기 제n+1 내지 제n+m 화소 데이터를 입력받아 상기 다수의 데이터 라인 중 나머지에 상기 제n+1 내지 제n+m 화소 데이터 각각에 대응하는 데이터 전압을 제공하는 제2 데이터 드라이브 IC 그룹을 포함하는 데이터 드라이버로서, 상기 제1 데이터 드라이브 IC 그룹은 제1 번째 내지 제s 번째 데이터 드라이브 IC를 포함하고, 제2 데이터 드라이브 IC 그룹은 제s+1 번째 내지 제s+t 번째 데이터 드라이브 IC를 포함하는 데이터 드라이버 및 상기 타이밍 컨트롤러가 실장되고, 상기 타이밍 컨트롤러로부터 상기 제1 데이터 드라이브 IC 그룹 사이에 연결되고 상기 제1 내지 제n 화소 데이터를 전달하는 제1 신호 전송 라인과, 상기 타이밍 컨트롤러로부터 상기 제2 데이터 드라이브 IC 그룹 사이에 연결되고 상기 제n+1 내지 제n+m 화소 데이터를 전달하는 제2 신호 전송 라인을 포함하는 회로 기판으로서, 상기 제1 및 제2 신호 전송 라인은 각각, 상기 타이밍 컨트롤러로부터 상기 제1 내지 제n+m 화소 데이터 및 상기 제n 내지 제n+m 화소 데이터가 순차적으로 동시에 출력되는 상기 회로 기판의 제1 층의 제1 출력 라인과, 비아를 통해 상기 제1 출력 라인으로부터 상기 제1 내지 제n+m 화소 데이터 및 상기 제n 내지 제n+m 화소 데이터가 각각 상기 제1 번째 내지 제s 번째 데이터 드라이브 IC 및 상기 제s+1 번째 내지 제s+t 번째 데이터 드라이브 IC에 출력되는 상기 회로 기판의 제2 층의 제2 출력 라인을 포함하고, 상기 제1 출력 라인은 다수의 굴곡부를 포함하고, 상기 굴곡부의 내각이 90도 이상인 회로 기판을 포함한다.

<27> 기타 본 발명의 구체적인 사항들은 상세한 설명 및 도면들에 포함되어 있다.

<28> 본 발명의 이점 및 특징, 그리고 그것들을 달성하는 방법은 첨부되는 도면과 함께 상세하게 후술되어 있는 실시 예들을 참조하면 명확해질 것이다. 그러나 본 발명은 이하에서 개시되는 실시 예들에 한정되는 것이 아니라 서로 다른 다양한 형태로 구현될 수 있으며, 단지 본 실시 예들은 본 발명의 개시가 완전하도록 하고, 본 발명이 속하는 기술분야에서 통상의 지식을 가진 자에게 발명의 범주를 완전하게 알려주기 위해 제공되는 것이며, 본 발명은 청구항의 범주에 의해 정의될 뿐이다. 명세서 전체에 걸쳐 동일 참조 부호는 동일 구성 요소를 지칭한다.

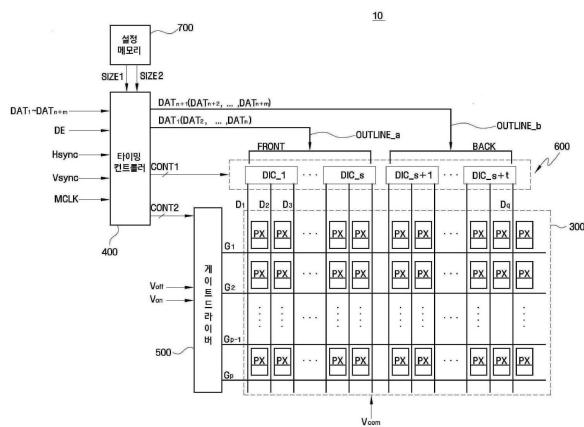

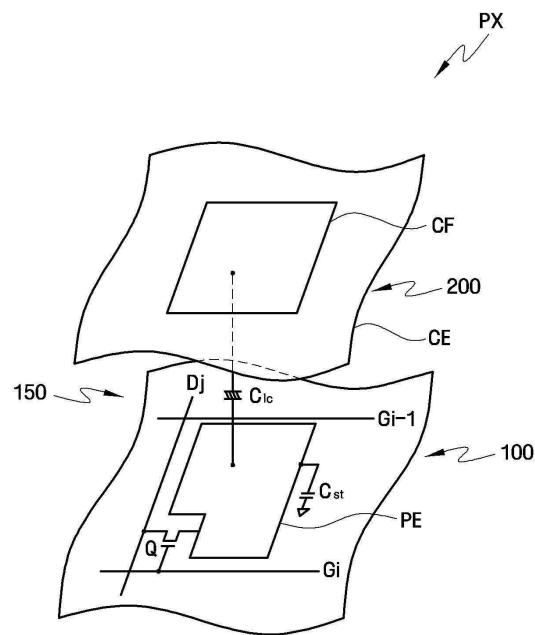

<29> 도 1 내지 도 4를 참조하여, 본 발명의 실시 예들에 따른 타이밍 컨트롤러 및 이를 포함하는 액정 표시 장치에 대해 설명한다. 도 1은 본 발명의 실시 예들에 따른 액정 표시 장치를 설명하기 위한 블록도이고, 도 2는 도 1의 한 화소의 등가 회로도이고, 도 3은 도 1의 타이밍 컨트롤러를 설명하기 위한 블록도이고, 도 4는 도 1의 타이밍 컨트롤러와 데이터 드라이버의 배치 구조를 설명하기 위한 회로 기판의 사시도이다.

<30> 먼저, 도 1을 참고하면, 본 발명의 실시 예들에 따른 액정 표시 장치(10)는 액정 패널(300), 타이밍 컨트롤러(400), 게이트 드라이버(500), 데이터 드라이버(600) 및 설정 메모리(700)를 포함한다.

<31> 액정 패널(300)은 등가 회로로 볼 때 다수의 표시 신호선( $G_1 \sim G_p$ ,  $D_1 \sim D_q$ )과 이에 연결되어 있으며 행렬의 형태로 배열된 다수의 화소(PX)를 포함한다. 표시 신호선( $G_1 \sim G_p$ ,  $D_1 \sim D_q$ )은 게이트 신호를 전달하는 복수의 게이트 라인( $G_1 \sim G_p$ )과 데이터 신호를 전달하는 복수의 데이터 라인( $D_1 \sim D_q$ )을 포함한다.

<32> 도 2에 도 1의 한 화소(PX)에 대한 등가 회로를 나타내었다. 제1 표시판(100)의 화소 전극(PE)과 대향하도록 제2 표시판(200)의 공통 전극(CE)의 일부 영역에 색필터(CF)가 형성될 수 있다. 각 화소(PX), 예를 들면 i번째

( $i=1, 2, \dots, p$ ) 케이트 라인( $G_i$ )과  $j$ 번째( $j=1, 2, \dots, q$ ) 데이터 라인( $D_j$ )에 연결된 화소(PX)는 신호선( $G_i, D_j$ )에 연결된 스위칭 소자(Q)와 이에 연결된 액정 커패시터(liquid crystal capacitor,  $C_{lc}$ ) 및 유지 커패시터(storage capacitor,  $C_{st}$ )를 포함한다. 유지 커패시터( $C_{st}$ )는 필요에 따라 생략될 수 있다.

<33> 한편, 타이밍 컨트롤러(400) 외부의 그래픽 제어기(미도시)로부터 순차적으로 제1 내지 제 $n+m$  화소 데이터( $DAT_1 \sim DAT_{n+m}$ )를 입력받고, 한 쌍씩의 화소 데이터를 순차적으로 출력한다. 즉, 제1 화소 데이터( $DAT_1$ ) 및 제 $n+1$  화소 데이터( $DAT_{n+1}$ )를 동시에 출력하고, 다음으로 제2 화소 데이터( $DAT_2$ ) 및 제 $n+2$  화소 데이터( $DAT_{n+2}$ )를 출력한다. 이러한 방식으로 제1 화소 데이터( $DAT_1$ ) 및 제 $n+1$  화소 데이터( $DAT_{n+1}$ )를 시작으로 순차적으로 한 쌍의 화소 데이터를 동시에 출력한다. 여기서 제1 내지 제 $n+m$  화소 데이터( $DAT_1 \sim DAT_{n+m}$ )는 하나의 케이트 라인( $G_1 \sim G_p$ )과 전기적으로 연결된 화소(PX)에 인가되는 화소 데이터이다.

<34> 좀더 자세히 설명하면, 타이밍 컨트롤러(400)는 먼저, 순차적으로 입력된 제1 내지 제 $n+m$  화소 데이터( $DAT_1 \sim DAT_{n+m}$ )를, 제1 내지 제 $n$  화소 데이터( $DAT_1 \sim DAT_n$ )를 포함하는 제1 영상 데이터 세트와 제 $n+1$  내지 제 $n+m$  화소 데이터( $DAT_{n+1} \sim DAT_{n+m}$ )를 포함하는 제2 영상 데이터 세트로 구분하여 저장한다. 여기서, 제1 영상 데이터 세트의 데이터 크기는 제2 영상 데이터 세트의 크기보다 작을 수 있다( $m > n$ ).

<35> 다음으로 저장된 제1 영상 데이터 세트와 제2 영상 데이터 세트로부터 각각 하나씩의 화소 데이터를 동시에 출력한다. 이를 위해, 타이밍 컨트롤러(400)는, 제1 내지 제 $n+m$  화소 데이터( $DAT_1 \sim DAT_{n+m}$ )를 타이밍 컨트롤러(400) 내부의 라인 버퍼 메모리(미도시)에 저장한다.

<36> 구체적으로, 제1 내지 제 $n$  화소 데이터( $DAT_1 \sim DAT_n$ )를 포함하는 제1 영상 데이터 세트를 라인 버퍼 메모리(미도시)의 제1 메모리부(미도시)에 저장하고, 제 $n$  내지 제 $n+m$  화소 데이터( $DAT_{n+1} \sim DAT_{n+m}$ )를 포함하는 제2 영상 데이터 세트를 라인 버퍼 메모리(미도시)의 제2 메모리부(미도시)에 저장한다. 이때, 제1 메모리부(미도시)와 제2 메모리부(미도시)의 메모리 크기는, 타이밍 컨트롤러(400)가 설정 메모리(700)부로부터 제1 데이터 정보(SIZE1)와 제2 데이터 정보(SIZE2)를 입력받아 각 메모리 크기를 할당한다. 여기서, 제1 데이터 정보(SIZE1)와 제2 데이터 정보(SIZE2)는 각각 제1 영상 데이터 세트의 데이터 크기와 제2 영상 데이터 세트의 데이터 크기를 나타낸다. 이러한 타이밍 컨트롤러(400)의 상세한 동작은 도 3을 참조하여 후술한다.

<37> 또한 타이밍 컨트롤러(400)는 입력 제어 신호를 수신하여 케이트 제어 신호(CONT2)와 데이터 제어 신호(CONT1)를 생성하고, 케이트 제어 신호(CONT2)를 케이트 드라이버(500)에, 데이터 제어 신호(CONT1)를 데이터 드라이버(600)로 보낸다.

<38> 여기서, 입력 제어 신호의 예로는 수직 동기 신호(Vsync)와 수직 동기 신호(Hsync), 메인 클럭(MCLK), 데이터 인에이블 신호(DE) 등이 있다. 케이트 제어 신호(CONT2)는 케이트 드라이버(500)의 동작을 제어하기 위한 신호로써, 케이트 드라이버(500)의 동작을 개시하는 수직 시작 신호, 케이트 온 전압의 출력 시기를 결정하는 케이트 클럭 신호 및 케이트 온 전압의 펄스 폭을 결정하는 출력 인에이블 신호 등을 포함한다. 데이터 제어 신호(CONT1)는 데이터 드라이버의 동작을 제어하는 신호로써, 데이터 드라이버의 동작을 개시하는 수평 개시 신호, 두 개의 데이터 전압의 출력을 지시하는 로드 신호 등을 포함한다.

<39> 데이터 드라이버(600)는 타이밍 컨트롤러(400)로부터 화소 데이터( $DAT_1 \sim DAT_{n+m}$ )를 입력받아, 이에 대응하는 데이터 전압을 다수의 데이터 라인( $D_1 \sim D_q$ )에 제공한다. 이러한 데이터 드라이버(600)는 제1 번째 내지 제 $s$  번째 데이터 드라이브 IC( $DIC_1 \sim DIC_s$ )를 포함하는 제1 데이터 드라이브 IC 그룹(FRONT)과, 제 $s+1$  번째 내지 제 $s+t$  번째 데이터 드라이브 IC( $DIC_{s+1} \sim DIC_{s+t}$ )를 포함하는 제2 데이터 드라이브 IC 그룹(BACK)으로 구분된다.

<40> 여기서 제1 데이터 드라이브 IC 그룹(FRONT)은 타이밍 컨트롤러(400)로부터 제1 영상 데이터 세트의 화소 데이터( $DAT_1 \sim DAT_n$ )를 제1 신호 전송 라인(OUTLINE\_a)을 통해 입력받는다. 제2 데이터 드라이브 IC 그룹(BACK)은 타이밍 컨트롤러(400)로부터 제2 영상 데이터 세트의 화소 데이터( $DAT_{n+1} \sim DAT_{n+m}$ )를 제2 신호 전송 라인(OUTLINE\_b)을 통해 입력받는다.

<41> 즉, 타이밍 컨트롤러(400)가 저장한 제1 영상 데이터 세트의 데이터 크기가 제2 영상 데이터 세트의 데이터 크기보다 작으므로, 제1 데이터 드라이브 IC 그룹(FRONT)의 데이터 드라이브 IC( $DIC_1 \sim DIC_s$ )의 수가 제2 데이터 드라이브 IC 그룹(BACK)의 데이터 드라이브 IC( $DIC_{s+1} \sim DIC_t$ )의 수보다 작을 수 있다( $t > s$ ).

- <42> 한편, 게이트 드라이버(500)는 게이트 라인( $G_1 \sim G_p$ )에 연결되어 게이트 온/오프 전압(Von, Voff) 발생부(미도시)로부터의 게이트 온 전압(Von)과 게이트 오프 전압(Voff)의 조합으로 이루어진 게이트 신호를 게이트 라인( $G_1 \sim G_q$ )에 인가한다. 게이트 드라이버(500)는 타이밍 컨트롤러(400)로부터의 게이트 제어 신호(CONT2)에 따라 게이트 온/오프 전압 발생부(미도시)로부터 게이트 온 전압(Von)을 게이트 라인( $G_1 \sim G_p$ )에 인가하여 이 게이트 라인( $G_1 \sim G_p$ )에 연결된 두 2의 스위칭 소자(Q)를 편온시킨다. 그러면, 데이터 라인( $D_1 \sim D_q$ )에 인가된 데이터 전압이 편온된 스위칭 소자(Q)를 통하여 해당 화소(PX)에 인가된다.

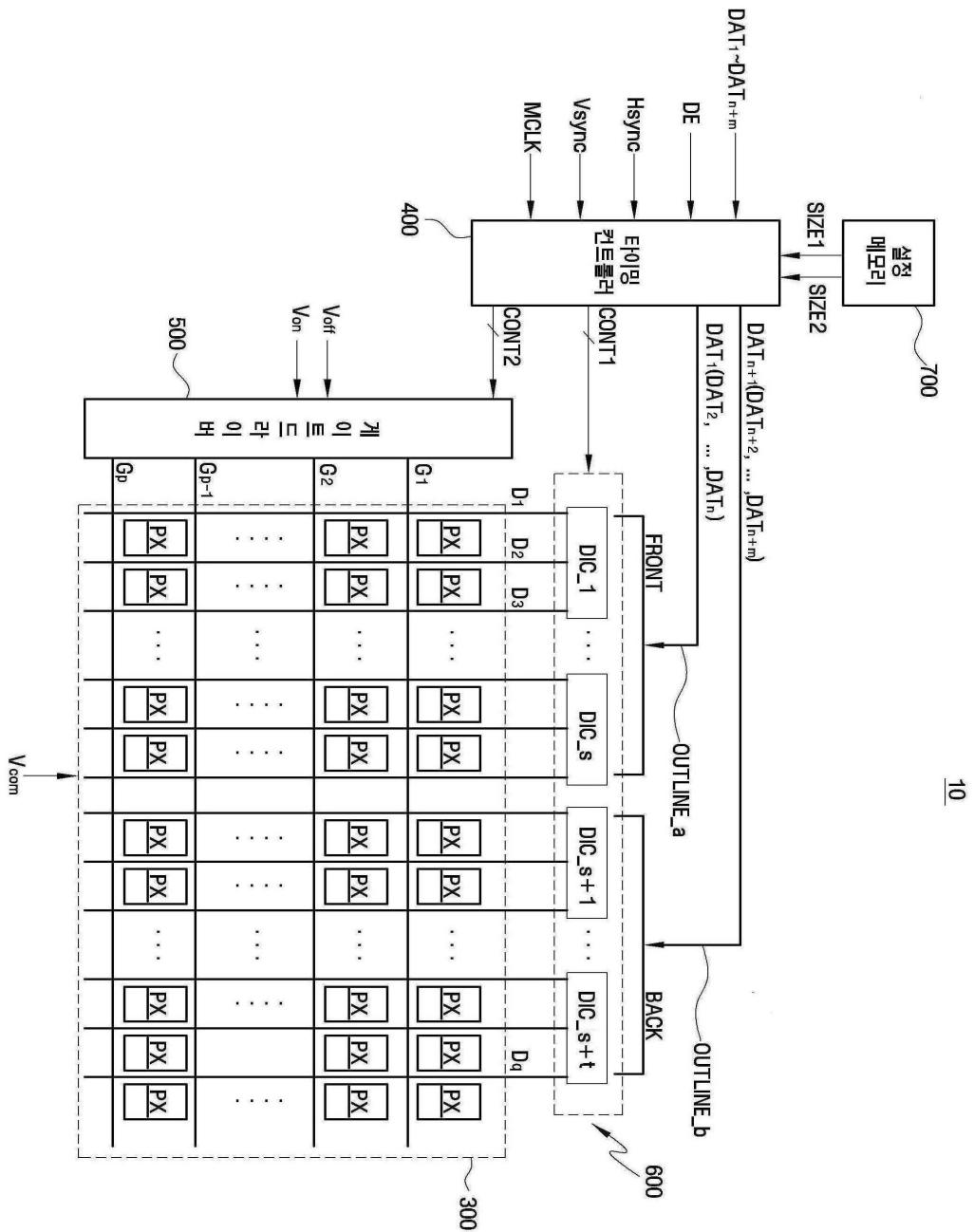

- <43> 도 3을 참조하여 타이밍 컨트롤러(400)가 순차적으로 입력된 제1 내지 제 $n+m$  화소 데이터( $DAT_1 \sim DAT_{n+m}$ )를, 제1 내지 제n 화소 데이터( $DAT_1 \sim DAT_n$ )를 포함하는 제1 영상 데이터 세트와 제 $n+1$  내지 제 $n+m$  화소 데이터( $DAT_{n+1} \sim DAT_{n+m}$ )를 포함하는 제2 영상 데이터 세트로 구분하여 저장하고, 제1 영상 데이터 세트와 제2 영상 데이터 세트로부터 순차적으로 각각 하나씩의 화소 데이터를 동시에 출력하는 동작에 대하여 상세히 설명한다.

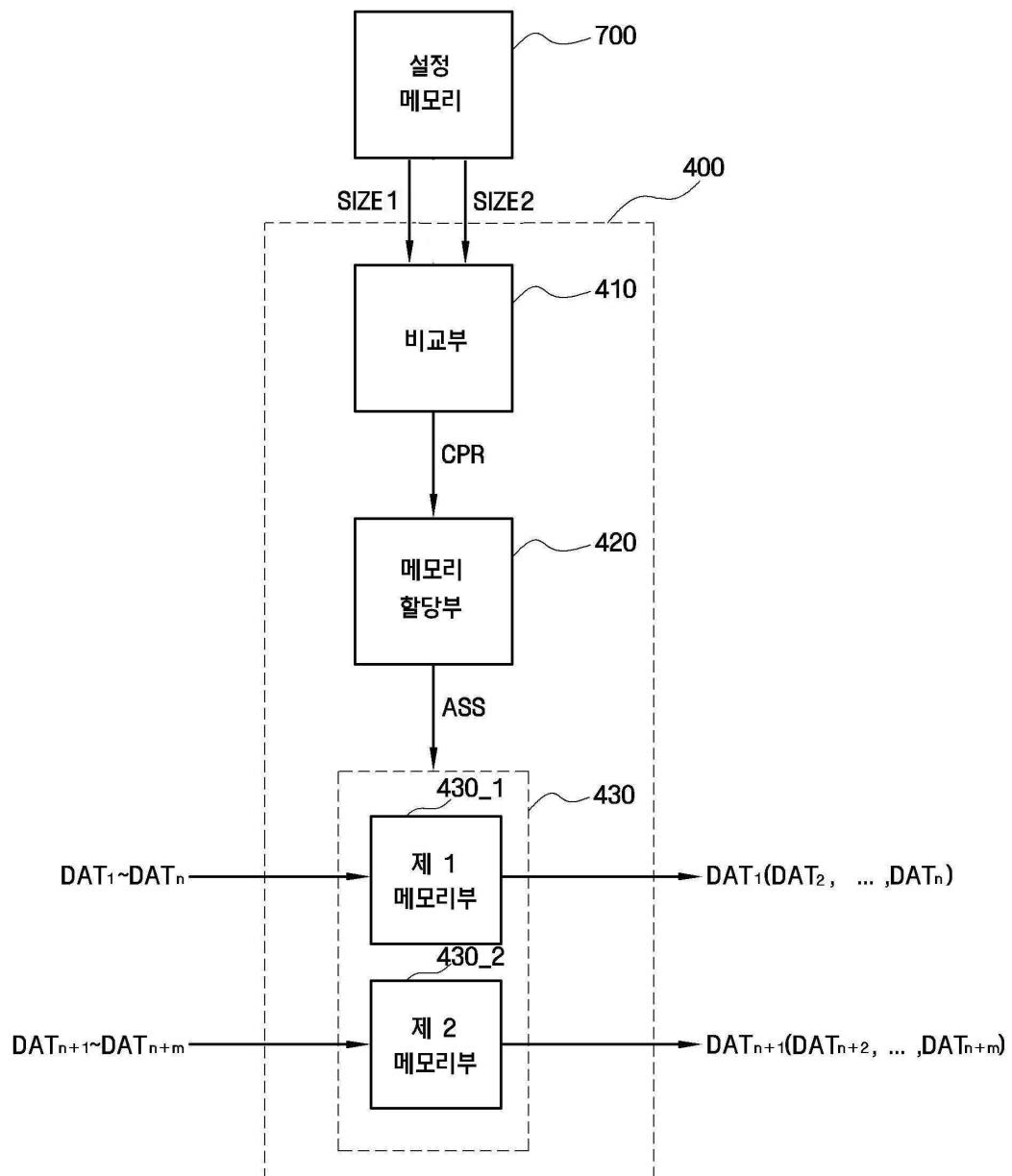

- <44> 도 3을 참조하면, 타이밍 컨트롤러(400)는 비교부(410), 메모리 할당부(420) 및 라인 버퍼 메모리(430)를 포함한다.

- <45> 먼저, 설정 메모리(700)에는 제1 영상 데이터 세트의 데이터 크기를 나타내는 제1 데이터 정보(SIZE1)와 제2 영상 데이터 세트의 데이터 크기를 나타내는 제2 데이터 정보(SIZE2)가 저장되어 있다. 그 밖에도 타이밍 컨트롤러(400)의 동작을 위해 다른 여러 가지의 데이터가 저장되어 있을 수 있다. 예컨데, 데이터 제어 신호(CONT1) 및 게이트 제어 신호(CONT2) 생성을 위한 조건 등이 저장되어 있을 수 있다. 이러한 설정 메모리(700)는 이이피롬(Electrically Erasable and Programmable Read Only Memory, EEPROM)일 수 있다.

- <46> 비교부(410)는 제1 영상 데이터 세트의 데이터 크기를 나타내는 제1 데이터 정보(SIZE1)와 제2 영상 데이터 세트의 데이터 크기를 나타내는 제2 데이터 정보(SIZE2)를 입력받아 데이터 크기를 비교한다. 예컨데, 제1 데이터 정보(SIZE1)는 제1 데이터 드라이브 IC 그룹(FRONT)과 전기적으로 연결된 데이터 라인의 수이고, 제2 데이터 정보(SIZE2)는 제2 데이터 드라이브 IC 그룹(BACK)과 전기적으로 연결된 데이터 라인의 수일 수 있다. 비교부(410)는 비교 결과(CPR)를 메모리 할당부(420)에 알린다. 예컨데, 비교부(410)는 비교한 결과에 따라, 제1 영상 데이터 세트와 제2 영상 데이터 세트 중에서 더 큰 데이터 크기를 메모리 할당부(420)에 알릴 수 있다.

- <47> 메모리 할당부(420)는 비교 결과(CPR)에 따라 라인 버퍼 메모리(430)를 동일한 메모리 크기를 갖는 제1 메모리부(430\_1)와 제2 메모리부(430\_2)로 구분한다. 예컨데, 제1 메모리부(430\_1)와 제2 메모리부(430\_2)는, 데이터 크기가 더 큰 제2 영상 데이터 세트를 저장할 수 있는 메모리 크기를 갖을 수 있다. 여기서 라인 버퍼 메모리(430)는, 하나의 게이트 라인( $G_1 \sim G_p$ )과 전기적으로 연결된 화소(PX)에 인가되는 화소 데이터인 제1 내지 제 $n+m$  화소 데이터( $DAT_1 \sim DAT_{n+m}$ )가 저장되는 메모리이다.

- <48> 제1 메모리부(430\_1)와 제2 메모리부(430\_2)의 메모리 크기가 할당된 후, 외부의 그래픽 컨트롤러(미도시)로부터 순차적으로 제1 내지 제 $n+m$  화소 데이터( $DAT_1 \sim DAT_{n+m}$ )를 입력받는다. 먼저, 순차적으로 입력된 제1 내지 제n 화소 데이터( $DAT_1 \sim DAT_n$ )를 제1 메모리부(430\_1)에 저장한다. 다음으로 순차적으로 입력되는 제 $n+1$  내지 제 $n+m$  화소 데이터( $DAT_{n+1} \sim DAT_{n+m}$ )를 제2 메모리부(430\_2)에 저장한다. 다음으로, 제1 메모리부(430\_1) 및 제2 메모리부(430\_2)에 각각 저장된 제1 영상 데이터 세트 및 제2 영상 데이터 세트로부터 순차적으로 하나씩의 화소 데이터를 동시에 출력한다. 제1 메모리부(430\_1)로부터 출력된 화소 데이터( $DAT_1 \sim DAT_n$ )는 제1 데이터 드라이브 IC 그룹(FRONT)으로 입력되고, 제2 메모리부(430\_2)로부터 출력된 화소 데이터( $DAT_{n+1} \sim DAT_{n+m}$ )는 제2 데이터 드라이브 IC 그룹(BACK)으로 입력된다.

- <49> 다만, 이와 달리, 제1 내지 제n 화소 데이터( $DAT_1 \sim DAT_n$ )를 제1 메모리부(430\_1)에 저장하고, 다음으로 제 $n+1$  내지 제 $n+m$  화소 데이터( $DAT_{n+1} \sim DAT_{n+m}$ )중에서 일부를 제2 메모리부(430\_2)에 저장한 뒤, 제 $n$  내지 제 $n+m$  화소 데이터( $DAT_{n+1} \sim DAT_{n+m}$ )중에서 나머지를 제2 메모리부(430\_2)에 저장하면서 동시에, 제1 메모리부(430\_1)와 제2 메모리부로부터 각각 하나씩의 화소 데이터를 출력할 수 있다.

- <50> 다시 말해서, 타이밍 컨트롤러(400)는 제1 영상 데이터 세트의 데이터 크기와 제2 영상 데이터 세트의 데이터 크기를 비교하여 큰 크기의 제2 영상 데이터 세트를 저장할 수 있도록 제1 메모리부(430\_1)와 제2 메모리부(430\_2)의 메모리 크기를 동일하게 할당하고, 제1 메모리부(430\_1) 및 제2 메모리부(430\_2)에 각각 제1 영상

이터 세트 및 제2 영상 데이터 세트를 저장한 후, 한 쌍의 화소 데이터를 각각 제1 데이터 드라이브 IC 그룹(FRONT)과 제2 데이터 드라이브 IC 그룹(BACK)에 제공한다. 그러므로 제1 데이터 드라이브 IC 그룹(FRONT)이 포함하는 데이터 드라이브 IC의 수가 제2 데이터 드라이브 IC 그룹(BACK)이 포함하는 데이터 드라이브 IC의 수보다 작게 될 수 있다.

<51> 따라서, 타이밍 컨트롤러(400)도 제1 데이터 드라이브 IC 그룹(FRONT)과 제2 데이터 드라이브 IC 그룹(BACK) 사이의 회로 기판 상에 실장될 수 있다.

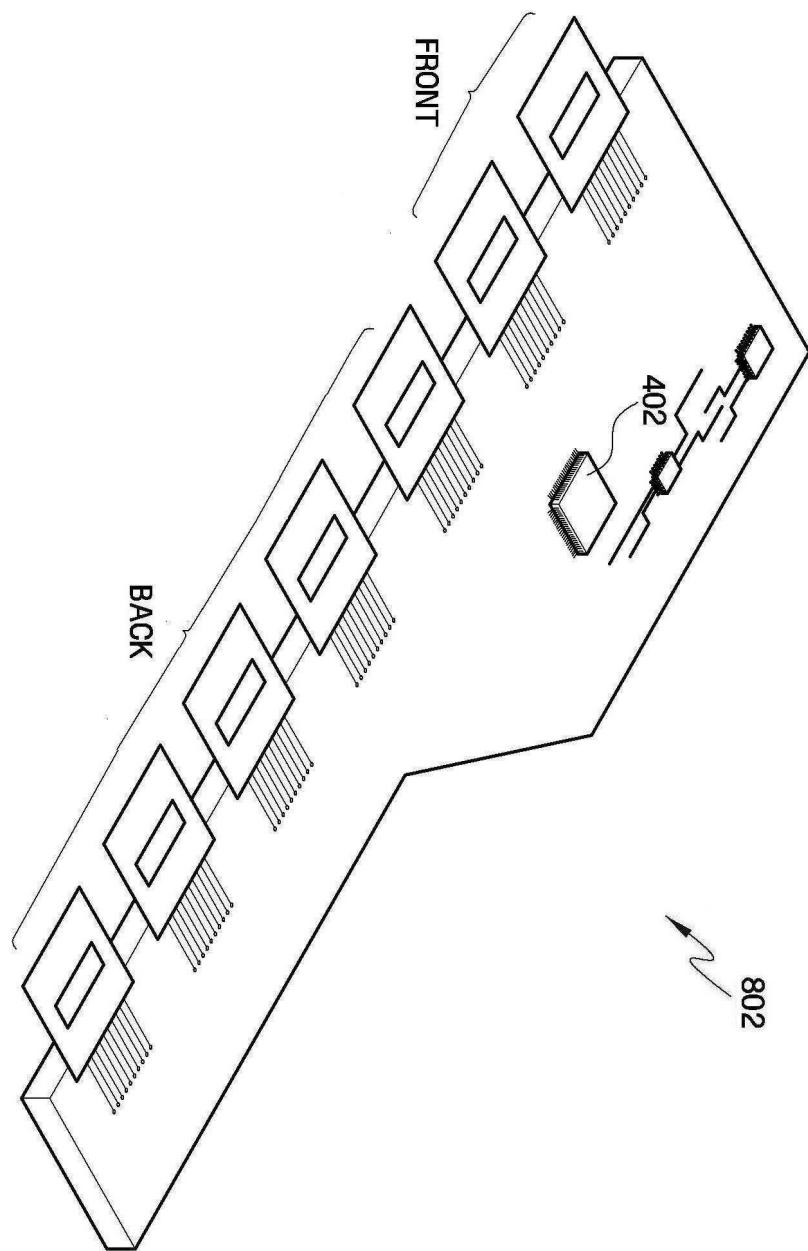

<52> 이에 대하여, 이하에서 도 4를 참조하여 타이밍 컨트롤러(400) 및 데이터 드라이브 IC의 회로 기판에의 배치 구조에 대해 상세히 설명한다.

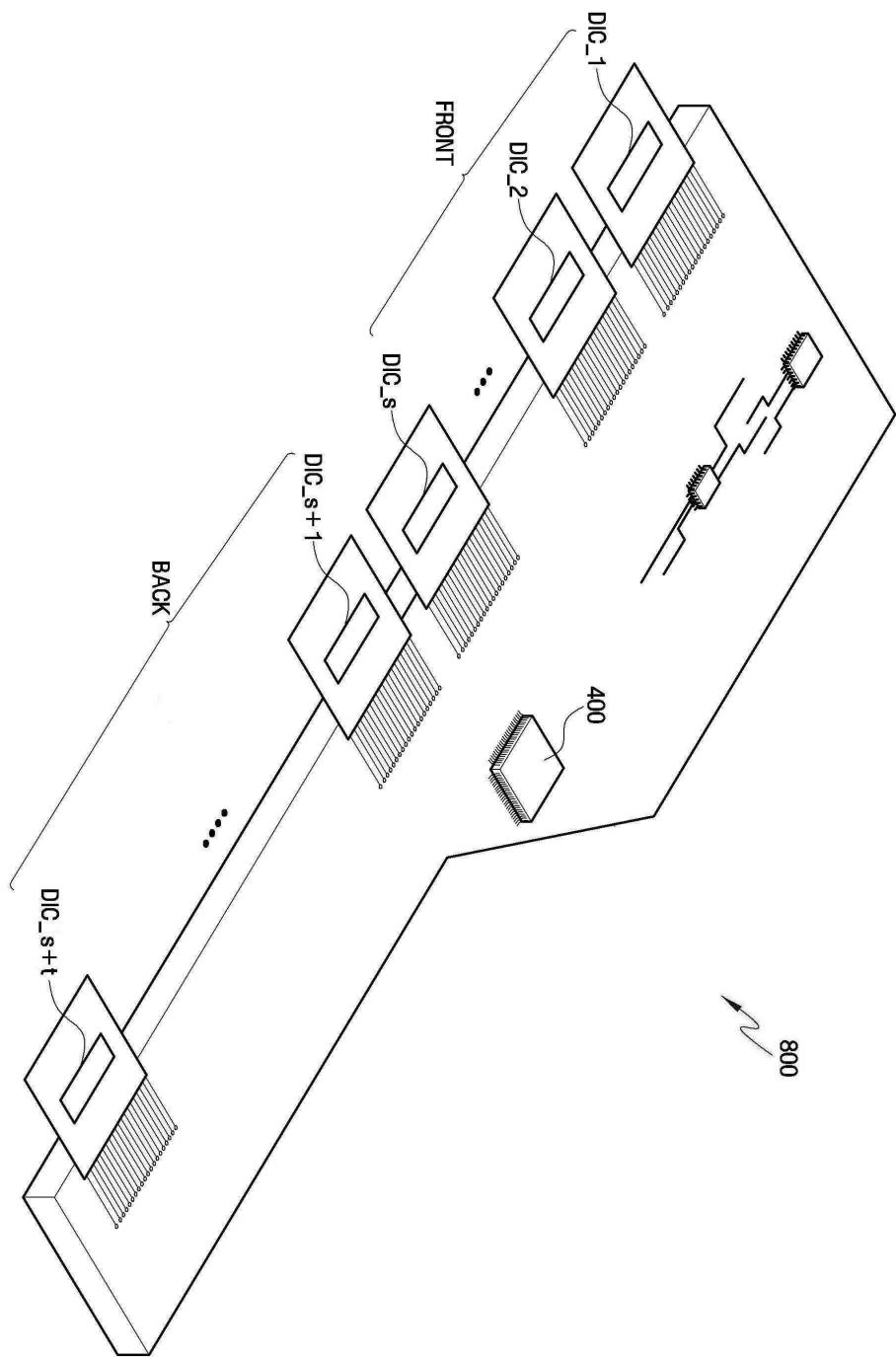

<53> 도 4를 참조하면, 회로 기판(800)에는 제1 내지 제 $n+m$  화소 데이터를 출력하는 타이밍 컨트롤러(400)와 다수의 회로들이 실장되고, 다수의 드라이브 IC들(DIC\_1~DIC\_s+t)과 전기적으로 연결된다. 도 4에 도시하지 않았지만, 다수의 드라이브 IC들(DIC\_1~DIC\_s+t)은 액정 패널(도 1의 300 참조)과 전기적으로 연결되어 다수의 데이터 라인(도 1의 D<sub>1</sub>~D<sub>q</sub> 참조)에 화소 데이터에 대응하는 데이터 전압을 인가한다.

<54> 타이밍 컨트롤러(400)는 제1 데이터 드라이브 IC 그룹(FRONT)과 제2 데이터 드라이브 IC 그룹(BACK) 사이에 배치될 수 있다. 더 자세히 설명하면, 타이밍 컨트롤러(400)는, 제s 번째 데이터 드라이브 IC(DIC\_s)와 제s+1 번째 데이터 드라이브 IC(DIC\_s+1)가 회로 기판(800)과 연결된 부분의 사이에 위치할 수 있다. 여기서 제1 데이터 드라이브 IC 그룹(FRONT)이 포함하는 데이터 드라이브 IC(DIC\_1~DIC\_s)의 수는 제2 데이터 드라이브 IC 그룹(BACK)이 포함하는 데이터 드라이브 IC(DIC\_s+1~DIC\_s+t)의 수보다 적을 수 있다( $t > s$ ).

<55> 이하에서는 타이밍 컨트롤러(400)는 제1 데이터 드라이브 IC 그룹(FRONT)과 제2 데이터 드라이브 IC 그룹(BACK) 사이에 배치되는 경우, EMI가 줄어드는 이유에 대해 구체적인 예를 들어 설명한다.

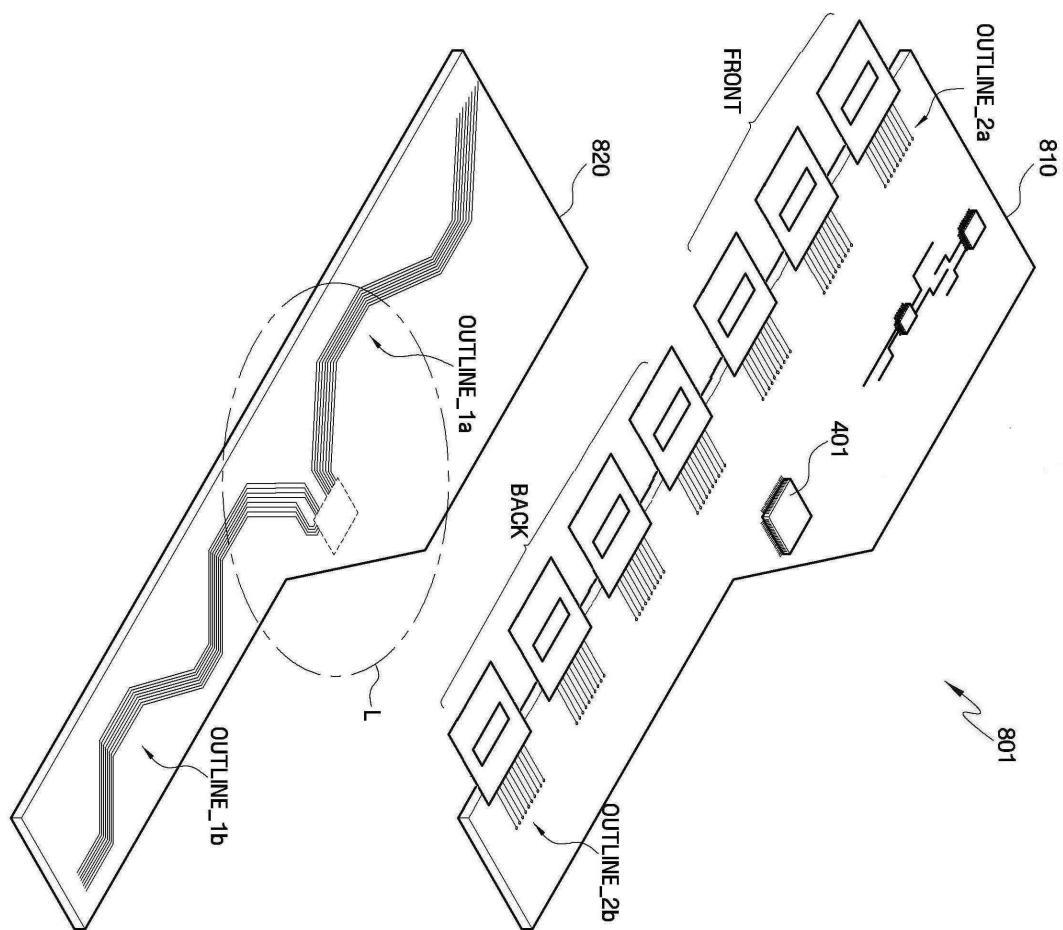

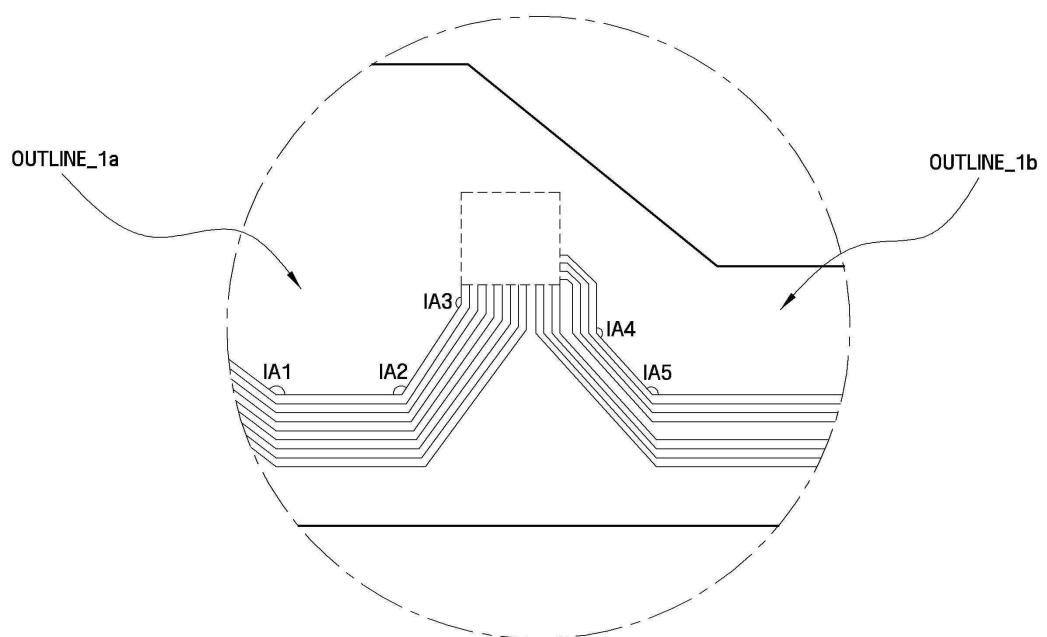

<56> 도 5는 본 발명의 일 실시예에 따른 타이밍 컨트롤러 및 이를 포함하는 액정 표시 장치를 설명하기 위한 사시도이고, 도 6은 도 5의 L 부분을 확대한 확대도이다. 여기서 데이터 드라이브 IC가 7개이고, 회로 기판(801)은 제1 층(810)과 제2 층(820)을 포함하는 경우를 예로 들어 설명한다.

<57> 도 5 및 도 6을 참조하면, 우선 타이밍 컨트롤러(401)는 제1 데이터 드라이브 IC 그룹(FRONT)과 제2 데이터 드라이브 IC 그룹(BACK) 사이에 배치된다.

<58> 회로 기판(801)은 타이밍 컨트롤러(401)로부터 상기 제1 데이터 드라이브 IC 그룹(FRONT) 사이에 연결되고 상기 제1 내지 제n 화소 데이터를 전달하는 제1 신호 전송 라인(OUTLINE\_a)과, 상기 타이밍 컨트롤러로(401)부터 상기 제2 데이터 드라이브 IC 그룹(BACK) 사이에 연결되고 상기 제n+1 내지 제 $n+m$  화소 데이터를 전달하는 제2 신호 전송 라인(OUTLINE\_b)을 포함한다.

<59> 제1 신호 전송 라인(OUTLINE\_a)은, 타이밍 컨트롤러(401)로부터 순차적으로 출력되는 제1 내지 제n 화소 데이터를 전송하는 회로 기판(801)의 제1 층(820)의 제1 출력 라인(OUTLINE\_1a)과, 비아(미도시)를 통해 제1 출력 라인(OUTLINE\_1a)으로부터 제1 내지 제n 화소 데이터를 제1 데이터 드라이브 IC 그룹(FRONT)에 전송하는 회로 기판(801)의 제2 층(810)의 제2 출력 라인(OUTLINE\_2a)을 포함한다.

<60> 제2 신호 전송 라인(OUTLINE\_b)은, 타이밍 컨트롤러(401)로부터 순차적으로 출력되는 제n+1 내지 제 $n+m$  화소 데이터를 전송하는 회로 기판(801)의 제1 층(820)의 제1 출력 라인(OUTLINE\_1a)과, 비아(미도시)를 통해 제1 출력 라인(OUTLINE\_1a)으로부터 제n+1 내지 제 $n+m$  화소 데이터를 제2 데이터 드라이브 IC 그룹(BACK)에 전송하는 회로 기판(801)의 제2 층(810)의 제2 출력 라인(OUTLINE\_2b)을 포함한다.

<61> 따라서, 타이밍 컨트롤러(401)로부터 출력된 제1 영상 데이터 세트의 화소 데이터는, 회로 기판(801)의 제1 층(820)의 제1 출력 라인(OUTLINE\_1a, OUTLINE\_1b)을 통해 전송되고, 비아(미도시)를 거쳐 회고 기판(801)의 제2 층(810)의 제2 출력 라인(OUTLINE\_2a, OUTLINE\_2b)을 통해 제1 데이터 드라이브 IC 그룹(FRONT) 중 하나의 데이터 드라이브 IC에 제공된다. 또한, 타이밍 컨트롤러(401)로부터 출력된 제2 영상 데이터 세트의 화소 데이터는, 회고 기판의 제1 층(810)의 제1 출력 라인(OUTLINE\_1a, OUTLINE\_1b)을 통해 전송되고, 비아(미도시)를 거쳐 회고 기판(801)의 제2 층(820)의 제2 출력 라인(OUTLINE\_2a, OUTLINE\_2b)을 통해 제2 데이터 드라이브 IC 그룹(BACK) 중 하나의 데이터 드라이브 IC에 제공된다.

<62> 여기서, 타이밍 컨트롤러(401)가 제1 데이터 드라이브 IC 그룹(FRONT)과 제2 데이터 드라이브 IC 그룹(BACK) 사이의 회로 기판(800)에 위치하므로, 제1 출력 라인(OUTLINE\_1a, OUTLINE\_1b)의 배치 구조를 EMI를 최소화할 수

있도록 설계할 수 있다. 예컨데, 제1 출력 라인(OUTLINE\_1a, OUTLINE\_1b)은 다수 부분이 굴곡될 수 있는데, 도 6에 도시된 바와 같이 각 굴곡부의 내각(inside angle, IA1, IA2, IA3, IA4, IA5)이 90도 이상이 된다.

<63> 만약, 제1 데이터 드라이브 IC 그룹(FRONT)의 데이터 드라이브 IC의 수가 제2 데이터 드라이브 IC 그룹(BACK)의 데이터 드라이브 IC의 수보다 더 큰 경우, 타이밍 컨트롤러(401)는, 고정된 형상의 회로 기판에서 제1 데이터 드라이브 IC 그룹(FRONT)과 제2 데이터 드라이브 IC 그룹(BACK) 사이에 위치할 수 없게 된다. 이러한 경우에는 제1 출력 라인(OUTLINE\_1a, OUTLINE\_1b)은 내각(IA1, IA2, IA3, IA4, IA5)이 90도 이하의 굴곡부를 포함하게 되고, EMI가 증가하게 된다.

<64> 그러나 본 발명의 경우에는, 제1 데이터 드라이브 IC 그룹(FRONT)이 포함하는 데이터 드라이브 IC의 수는 제2 데이터 드라이브 IC 그룹(BACK)이 포함하는 데이터 드라이브 IC의 수보다 작으므로, 타이밍 컨트롤러(401)가 제1 데이터 드라이브 IC 그룹(FRONT)과 제2 데이터 드라이브 IC 그룹(BACK) 사이의 회로 기판(801)에 위치할 수 있게 되고, 제1 출력 라인(OUTLINE\_1a, OUTLINE\_1b)이 90도 이하의 내각(IA1, IA2, IA3, IA4, IA5)을 형성하는 굴곡부 없이 연장되므로, EMI가 줄어 든다.

<65> 도 7은 본 발명의 다른 실시예에 따른 타이밍 컨트롤러와 이를 포함하는 액정 표시 장치를 설명하기 위한 사시도이다.

<66> 이전 실시예와 달리, 제1 데이터 드라이브 IC 그룹(FRONT)이 포함하는 데이터 드라이브 IC의 개수는 2개이고, 제2 데이터 드라이브 IC 그룹(BACK)이 포함하는 데이터 드라이브 IC의 개수는 5개이다.

<67> 이러한 경우에도 이전 실시예와 마찬가지로, 타이밍 컨트롤러(402)는 제1 데이터 드라이브 IC 그룹(FRONT)과 제2 데이터 드라이브 IC 그룹(BACK) 사이의 회로 기판(802) 상에 설치되어 제1 출력 라인(OUTLINE\_1a, OUTLINE\_1b)은 내각이 90도 이상인 굴곡부를 포함하지 않게 된다. 또한, 타이밍 컨트롤러(402)의 주변에 공간이 확보되므로, 회로 기판(802)의 그라운드 전압이 인가되는 그라운드 영역을 타이밍 컨트롤러(402)의 주변에 형성할 수 있다. 따라서, 타이밍 컨트롤러(402) 및 타이밍 컨트롤러(402)가 설치된 회로 기판(802)으로부터 발생되는 EMI를 줄일 수 있다.

<68> 이상 첨부된 도면을 참조하여 본 발명의 실시예들을 설명하였지만, 본 발명이 속하는 기술분야에서 통상의 지식을 가진 자는 본 발명이 그 기술적 사상이나 필수적인 특징을 변경하지 않고서 다른 구체적인 형태로 실시될 수 있다는 것을 이해할 수 있을 것이다. 그러므로 이상에서 기술한 실시예들은 모든 면에서 예시적인 것이며 한정적이 아닌 것으로 이해해야만 한다.

### 발명의 효과

<69> 상술한 바와 같은 본 발명에 실시예들에 따른 타이밍 컨트롤러 및 이를 포함하는 액정 표시 장치에 의하면 전자기파의 방출을 막아 EMI를 감소시킬 수 있다.

### 도면의 간단한 설명

- <1> 도 1은 본 발명의 실시예들에 따른 액정 표시 장치를 설명하기 위한 블록도이다.

- <2> 도 2는 도 1의 한 화소의 등가 회로도이다.

- <3> 도 3은 도 1의 타이밍 컨트롤러를 설명하기 위한 블록도이다.

- <4> 도 4는 도 1의 타이밍 컨트롤러와 데이터 드라이버의 배치 구조를 설명하기 위한 회로 기판의 사시도이다.

- <5> 도 5는 본 발명의 일 실시예에 따른 타이밍 컨트롤러 및 이를 포함하는 액정 표시 장치를 설명하기 위한 사시도이다.

- <6> 도 6은 도 5의 L 부분을 확대한 확대도이다.

- <7> 도 7은 본 발명의 다른 실시예에 따른 타이밍 컨트롤러와 이를 포함하는 액정 표시 장치를 설명하기 위한 사시도이다.

- <8> (도면의 주요부분에 대한 부호의 설명)

- <9> 10: 액정 표시 장치                    100: 제1 표시판

- <10> 150: 액정층                            200: 제2 표시판

- |      |                |               |

|------|----------------|---------------|

| <11> | 300: 액정 패널     | 400: 타이밍 컨트롤러 |

| <12> | 410: 비교부       | 420: 메모리 할당부  |

| <13> | 430: 라인 버퍼 메모리 | 500: 게이트 드라이버 |

| <14> | 600: 데이터 드라이버  | 700: 설정 메모리   |

| <15> | 800: 회로 기판     |               |

## 도면

도면1

도면2

## 도면3

도면4

도면5

도면6

도면7