(12)

## DEMANDE DE BREVET D'INVENTION

A1

(22) Date de dépôt : 04.07.14.

(30) Priorité :

(43) Date de mise à la disposition du public de la demande : 08.01.16 Bulletin 16/01.

(56) Liste des documents cités dans le rapport de recherche préliminaire : Se reporter à la fin du présent fascicule

(60) Références à d'autres documents nationaux apparentés :

Demande(s) d'extension :

(71) Demandeur(s) : COMMISSARIAT A L'ENERGIE ATOMIQUE ET AUX ENERGIES ALTERNATIVES Etablissement public — FR.

(72) Inventeur(s) : WALTENER GUILLAUME et GONZALEZ JIMENEZ JOSE-LUIS.

(73) Titulaire(s) : COMMISSARIAT A L'ENERGIE ATOMIQUE ET AUX ENERGIES ALTERNATIVES Etablissement public.

(74) Mandataire(s) : CABINET BEAUMONT.

(54) AMPLIFICATEUR HAUTE TENSION.

(57) L'invention concerne un amplificateur haute tension comprenant: des premier et deuxième transistors en cascode (102, 104) adaptés à générer un signal de sortie ( $V_{OUT}$ ) sur la base d'un premier signal de tension ( $V_{SL}$ ) ayant une première plage de tension, et d'un deuxième signal de tension ( $V_{SH}$ ) ayant une plage de tension décalée par rapport à la première plage de tension, le signal de sortie ayant une deuxième plage de tension supérieure à la première plage de tension; et un générateur d'impulsions (128) comprenant un filtre passe-haut passif adapté à générer des impulsions de tension sur la base d'au moins l'un des premier et deuxième signaux de tension et à fournir les impulsions de tension à un noeud de commande d'au moins l'un des premier et deuxième transistors.

**AMPLIFICATEUR HAUTE TENSION**Domaine

La présente description concerne le domaine des amplificateurs à haute tension et des procédés de génération de signaux à haute tension.

5   Exposé de l'art antérieur

Dans certaines applications il peut être nécessaire de générer un signal de tension ayant une plage de tension supérieure à la tension de fonctionnement autorisée de la technologie de transistors utilisée. Par exemple, dans la technologie CMOS 65 nm, la tension appliquée entre les bornes des transistors ne doit pas de façon générale dépasser 1,2 V, alors qu'on peut souhaiter générer un signal de tension ayant une plage de tension supérieure.

Une solution qui a été proposée consiste à utiliser une technique de transistors en cascode. Cependant, bien qu'une telle technique fonctionne bien lorsque la tension d'entrée est statique, des transitions de la tension d'entrée entre les niveaux bas et haut peuvent provoquer des pointes de tension aux bornes de l'un ou des deux transistors en cascode qui correspondent à une surtension, en d'autres termes une tension dépassant les limites de tension autorisées de la technologie de transistors. Bien que cela puisse ne pas provoquer une défail-

lance immédiate des transistors, dans le temps il y aura une dégradation de leurs performances, ce qui conduit à une durée de vie limitée.

Il existe donc un besoin dans la technique d'un amplificateur haute tension qui empêche ou qui au moins réduise partiellement les surtensions, et ayant une faible surface et/ou une relativement faible consommation d'énergie.

#### Résumé

Un objet de modes de réalisation de la présente description est de résoudre au moins partiellement un ou plusieurs besoins de l'art antérieur.

Selon un aspect, on prévoit un amplificateur haute tension comprenant : des premier et deuxième transistors en cascode adaptés à générer un signal de sortie sur la base d'un premier signal de tension ayant une première plage de tension, et d'un deuxième signal de tension ayant une plage de tension décalée par rapport à la première plage de tension, le signal de sortie ayant une deuxième plage de tension supérieure à la première plage de tension ; et un générateur d'impulsions comprenant un filtre passe-haut passif adapté à générer des impulsions de tension sur la base d'au moins l'un des premier et deuxième signaux de tension et à fournir les impulsions de tension à un noeud de commande d'au moins l'un des premier et deuxième transistors.

Selon un mode de réalisation, le filtre passe-haut passif est adapté à générer les impulsions de tension sur la base seulement du premier signal de tension et à fournir les impulsions de tension aux noeuds de commande des premier et deuxième transistors.

Selon un mode de réalisation, l'amplificateur haute tension comprend en outre : un premier tampon adapté à générer le premier signal de tension sur la base d'un signal d'entrée ; un dispositif de décalage de niveau adapté à décaler la plage de tension du signal d'entrée pour générer un signal décalé en

tension ; et un deuxième tampon adapté à générer le deuxième signal de tension sur la base du signal décalé en tension.

Selon un mode de réalisation, l'amplificateur haute tension comprend en outre : un premier inverseur ayant une entrée couplée de façon à recevoir le premier signal de tension et une sortie couplée à un premier noeud de courant principal du premier transistor ; un deuxième inverseur ayant une entrée couplée de façon à recevoir le deuxième signal de tension, et une sortie couplée à un premier noeud de courant principal du deuxième transistor ; et un noeud de sortie couplé à des deuxièmes noeuds de courant principaux des premier et deuxième transistors.

Selon un mode de réalisation, l'amplificateur haute tension comprend en outre au moins un autre inverseur couplé entre une sortie du premier tampon et une entrée du premier inverseur.

Selon un mode de réalisation, le premier transistor est un transistor MOS à canal N, le deuxième transistor est un transistor MOS à canal P, et le filtre passe-haut passif est adapté à : générer des impulsions qui sont positives par rapport à un niveau de tension intermédiaire dans la deuxième plage de tension en réponse à des fronts montants du premier ou du deuxième signal de tension ; et générer des impulsions qui sont négatives par rapport au niveau de tension intermédiaire dans la deuxième plage de tension en réponse à des fronts descendants du premier ou du deuxième signal de tension.

Selon un mode de réalisation, le filtre passe-haut passif est un filtre RC comprenant : un premier condensateur couplé entre une entrée du générateur d'impulsions et le noeud de commande du premier transistor ; et une première résistance couplée entre le noeud de commande du premier transistor et un niveau de tension intermédiaire dans la deuxième plage de tension.

Selon un mode de réalisation, le filtre passe-haut passif comprend en outre : un deuxième condensateur couplé entre

l'entrée du générateur d'impulsions et le noeud de commande du deuxième transistor ; et une deuxième résistance couplée entre le noeud de commande du deuxième transistor et le niveau de tension intermédiaire.

5 Selon un autre aspect, on prévoit un modulateur photonique comprenant l'amplificateur haute tension susmentionné.

Selon un autre aspect, on prévoit un procédé pour générer un signal à haute tension comprenant : générer une tension de sortie par des premier et deuxième transistors en cascode sur la base d'un premier signal de tension ayant une première plage de tension et d'un deuxième signal de tension ayant une plage de tension décalée par rapport à la première plage de tension, le signal de sortie ayant une deuxième plage de tension supérieure à la première plage de tension ; générer, 10 par un filtre passe-haut passif d'un générateur d'impulsions, des impulsions de tension sur la base d'au moins l'un des premier et deuxième signaux de tension ; et fournir les impulsions de tension à un noeud de commande d'au moins l'un des premier et deuxième transistors.

15 20 Brève description des dessins

Les caractéristiques et avantages susmentionnés, et d'autres, apparaîtront clairement à la lecture de la description détaillée suivante de modes de réalisation, donnés à titre d'illustration et non de limitation, en faisant référence aux 25 dessins joints dans lesquels :

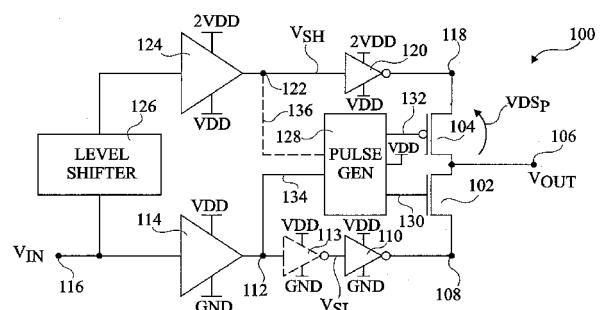

la figure 1 illustre schématiquement un amplificateur haute tension selon un exemple de réalisation de la présente description ;

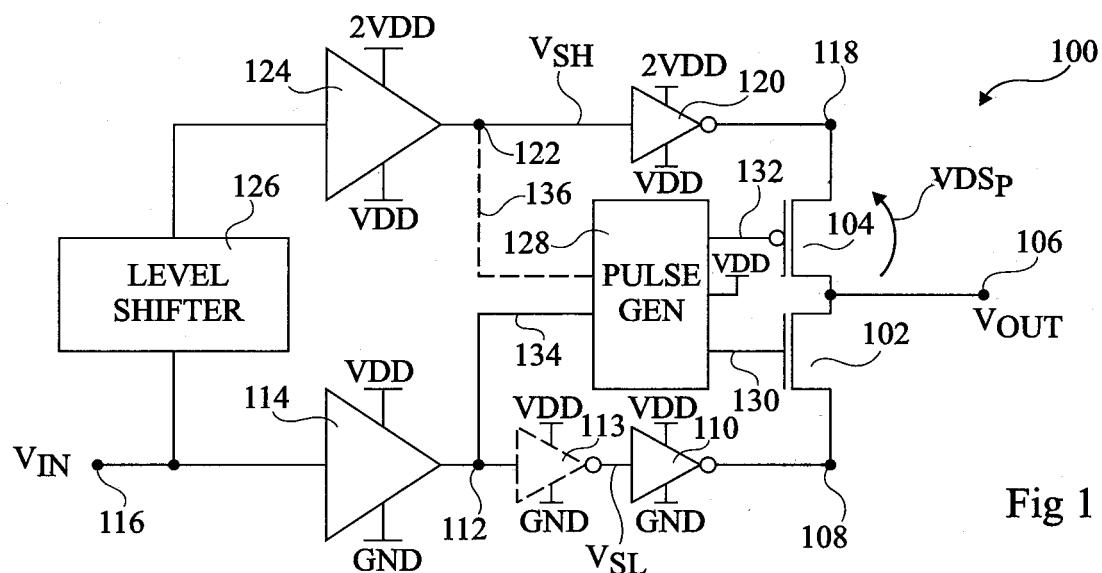

30 la figure 2 est un chronogramme illustrant des signaux dans le circuit de la figure 1 selon un exemple de réalisation ;

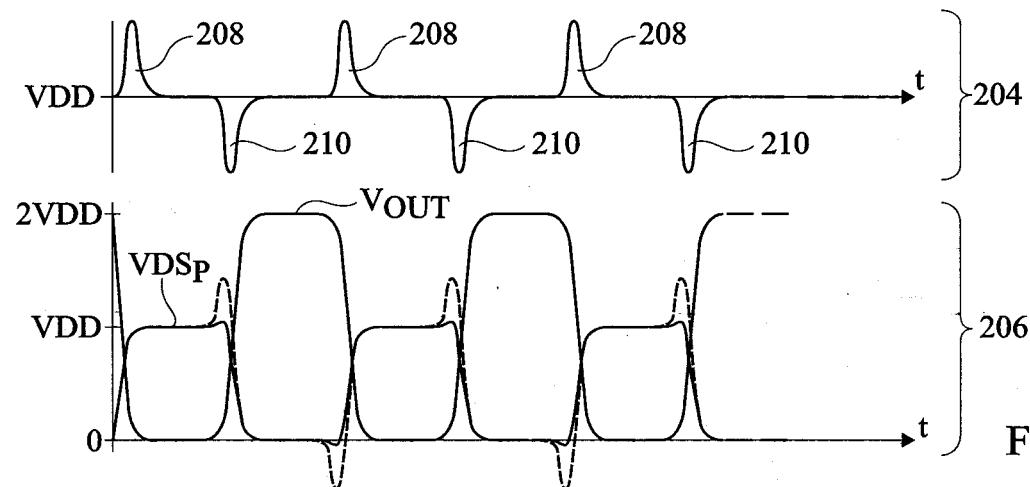

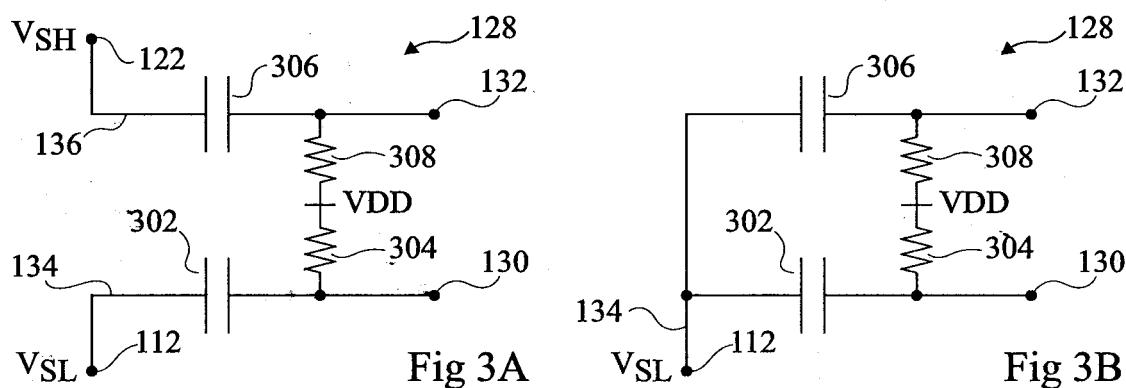

la figure 3A illustre schématiquement un générateur d'impulsions de la figure 1 plus en détail selon un exemple de réalisation ;

la figure 3B illustre schématiquement le générateur d'impulsions de la figure 1 plus en détail selon autre un exemple de réalisation ;

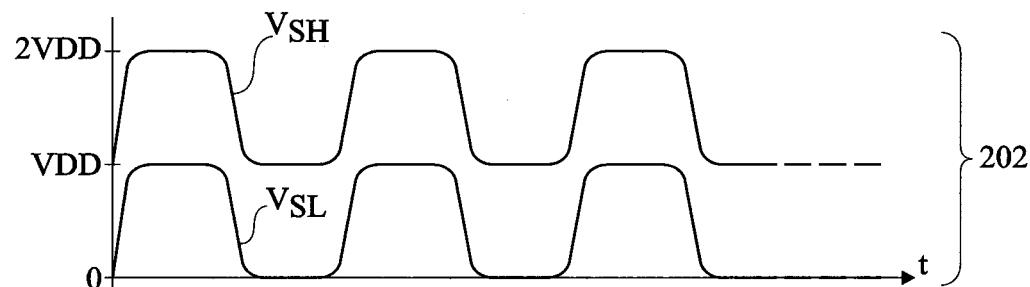

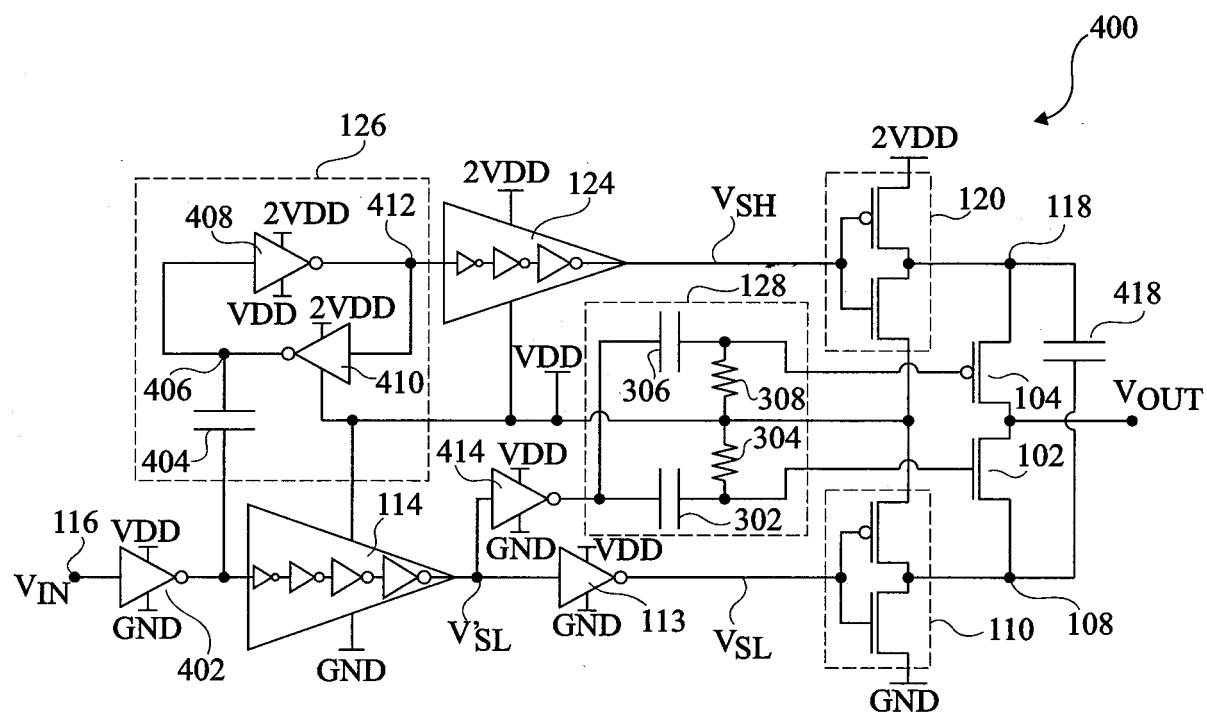

5 la figure 4 illustre schématiquement un amplificateur haute tension selon un autre exemple de réalisation de la présente description ; et

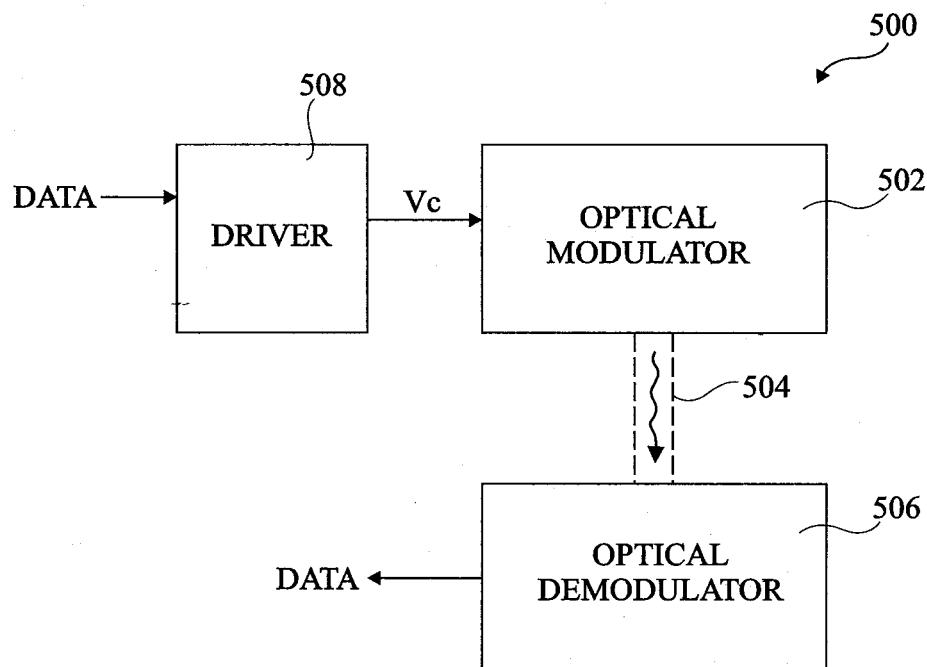

la figure 5 illustre schématiquement un système de transmission optique comprenant un amplificateur haute tension selon un exemple de réalisation de la présente description.

10 Description détaillée

La figure 1 illustre un amplificateur haute tension 100 selon un exemple de réalisation. Un tel amplificateur est par exemple utilisé pour piloter un dispositif (non illustré en figure 1) qui doit être piloté par une tension élevée, en 15 d'autres termes une tension supérieure à la limite de tension normale de la technologie de transistors concernée. Par exemple, dans le cas d'une technologie CMOS à 65 nm, la limite de tension normale est généralement d'environ 1,2 V.

En outre, dans certains modes de réalisation décrits 20 plus en détail ci-après, l'amplificateur haute tension est adapté à fonctionner à des fréquences relativement élevées, par exemple à des fréquences comprises entre 5 et 10 GHz. Par exemple, l'amplificateur haute tension est utilisé pour piloter un dispositif photonique, ou un convertisseur de tension pour des 25 signaux de données d'entrée/sortie d'un circuit intégré.

L'amplificateur 100 comprend deux transistors en cascode 102, 104, couplés en série par leurs noeuds de conduction principaux. Le transistor 102 est par exemple un transistor MOS à canal N, et le transistor 104 est par exemple un 30 transistor MOS à canal P. Les drains des transistors 102, 104 sont couplés à un noeud de sortie 106 de l'amplificateur, et fournissent le signal de sortie  $V_{OUT}$ .

La source du transistor 102 est couplée à un noeud 108 d'un chemin à basse tension. Le signal transmis suivant le 35 chemin à basse tension est par exemple dans la plage de 0 à VDD,

où VDD est une tension d'alimentation comprise par exemple entre 1 et 2 V, et dans un exemple est sensiblement à 1,2 V. Le terme "sensiblement" est utilisé ici pour désigner une tolérance de plus ou moins 5 pourcent.

Le chemin à basse tension comprend un inverseur 110 ayant sa sortie couplée au noeud 108 et son entrée couplée à un noeud 112, dans certains modes de réalisation par l'intermédiaire d'un ou plusieurs autres inverseurs 113, pour recevoir un signal de tension  $V_{SL}$  fourni par un tampon 114. L'entrée du tampon 114 est couplée à un noeud d'entrée 116 de l'amplificateur, qui reçoit un signal de tension d'entrée  $V_{IN}$ . Le tampon 114 comprend par exemple une pluralité d'inverseurs de tailles différentes couplés en série, le plus petit étant couplé au noeud d'entrée 116, et les inverseurs devenant de plus en plus gros en direction de la sortie du tampon 114.

La source du transistor 104 est couplée à un noeud 118 d'un chemin à haute tension. Le signal transmis suivant le chemin à haute tension a un niveau décalé par rapport au chemin à basse tension, et est par exemple dans la plage de VDD à 2VDD. Dans un exemple, la plage de tension du chemin à haute tension est sensiblement comprise entre 1,2 et 2,4 V.

Le chemin à haute tension comprend un inverseur 120 ayant son entrée couplée à un noeud 122 recevant un signal de tension  $V_{SH}$  fourni par un tampon 124. L'entrée du tampon 124 est couplée à la sortie d'un dispositif de décalage de niveau (LEVEL SHIFTER) 126. Le tampon 124 comprend par exemple une pluralité d'inverseurs de différentes tailles couplés en série, le plus petit étant couplé à la sortie du dispositif de décalage de niveau 126, et les inverseurs devenant progressivement de plus en plus gros en direction de la sortie du tampon 124. Le dispositif de décalage de niveau 126 est à son tour couplé au noeud d'entrée 116, et décale la plage de tension du signal d'entrée  $V_{IN}$  vers la plage de tension du chemin à haute tension. Par exemple, le dispositif de décalage de niveau 126 décale le

signal d'entrée  $V_{IN}$  de sensiblement le niveau de la tension d'alimentation VDD.

Les noeuds de commande des transistors 102, 104 sont pilotés par un générateur d'impulsions (PULSE GEN) 128. Par exemple, la grille du transistor 102 est couplée à une ligne de sortie 130 du générateur d'impulsions 128, et la grille du transistor 104 est couplée à une ligne de sortie 132 du générateur d'impulsions 128. Dans des variantes de réalisation, les grilles des transistors 102, 104 pourraient être pilotées par la même ligne de sortie du générateur d'impulsions 128.

Le générateur d'impulsions 128 comprend par exemple un filtre passe-haut passif, en d'autres termes un filtre passe-haut basé seulement sur des composants passifs, comme des résistances, des condensateurs et/ou des inductances. Par exemple, le générateur d'impulsions 128 comprend un filtre RC ou un filtre LC. Le générateur d'impulsions 128 a par exemple une ligne d'entrée 134 couplée au noeud 112, et comme cela est représenté par une ligne en pointillés 136, il peut aussi avoir une autre ligne d'entrée couplée au noeud 122. Le générateur d'impulsions 128 est par exemple en outre couplé à la tension d'alimentation VDD, et génère un signal de tension généralement à VDD, mais avec des impulsions de tension positives sur des fronts montants du signal de tension  $V_{SL}$  et/ou  $V_{SH}$ , et des impulsions négatives sur des fronts descendants du signal de tension  $V_{SL}$  et/ou  $V_{SH}$ .

Le fonctionnement du circuit de la figure 1 va maintenant être décrit plus en détail en référence à la figure 2.

La figure 2 représente des chronogrammes 202, 204 et 206.

Le chronogramme 202 illustre un exemple des signaux de tension  $V_{SL}$  et  $V_{SH}$ , dans le cas où les signaux de tension sont sensiblement des ondes carrées, et le chemin à basse tension est dans la plage de tension de 0 à VDD et le chemin à haute tension est dans la plage de tension de VDD à 2VDD. Comme cela est

illustré, les signaux  $V_{SL}$  et  $V_{SH}$  sont par exemple synchronisés entre eux.

Le chronogramme 204 illustre un exemple du signal d'impulsions correspondant généré par le générateur d'impulsions 128 sur la ligne 130 et/ou 132 sur la base du signal  $V_{SL}$  et/ou  $V_{SH}$ . Ce signal a par exemple un niveau en courant continu de VDD ou d'une tension quelconque permettant au transistor d'être commuté sans être endommagé. Le signal d'impulsions comprend aussi des impulsions hautes 208 survenant sur les fronts montants des signaux  $V_{SL}$ ,  $V_{SH}$ , et des impulsions basses 210 survenant sur les fronts descendants des signaux  $V_{SL}$ ,  $V_{SH}$ . Chaque impulsion a par exemple une amplitude comprise entre 0,1 et 1 V et une durée comprise entre un dixième et la moitié de la période de bit.

Un chronogramme 206 illustre un exemple du signal de sortie correspondant  $V_{OUT}$ , qui a des transitions, sur des fronts montants des signaux  $V_{SL}$  et  $V_{SH}$ , d'un niveau haut situé à 2VDD, ou à proximité, vers un niveau bas situé à 0 V ou à proximité, et sur des fronts descendants des signaux  $V_{SL}$  et  $V_{SH}$ , d'un niveau bas situé à 0 V, ou à proximité, vers un niveau haut situé à 2VDD ou à proximité.

Le chronogramme 206 illustre aussi la tension source-drain  $V_{DSp}$  illustrée en figure 1 du transistor PMOS 104, qui est en général comprise entre 0 V et VDD. Cependant, les portions en pointillés en figure 2 représentent des pointes de tension positives et négatives qui pourraient survenir à chaque front montant ou descendant des signaux  $V_{SL}$  et  $V_{SH}$  si le générateur d'impulsions 128 n'était pas présent. En effet, les pics positifs résultent d'un retard pour amener la tension sur le noeud de sortie 106 au niveau haut de 2VDD, après que le noeud 118 a déjà atteint le niveau de 2VDD, et les pics négatifs résultent d'un retard pour amener la tension sur le noeud de sortie 106 au niveau bas de 0 volt, après que le noeud 118 a déjà été réduit à VDD.

En appliquant des impulsions négatives au noeud de commande du transistor 104 sur les fronts descendants des signaux  $V_{SL}$  et  $V_{SH}$ , la conduction du transistor peut être augmentée, provoquant ainsi une augmentation plus rapide de la tension sur le noeud de sortie 106. Les pointes de tension positives dans la tension  $V_{DSp}$  sont ainsi sensiblement ou complètement supprimées.

En appliquant des impulsions positives sur le noeud de commande du transistor 102 sur les fronts montants des signaux  $V_{SL}$  et  $V_{SH}$ , la conduction du transistor 102 peut être augmentée, entraînant ainsi une diminution plus rapide de la tension sur le noeud de sortie. Les pointes de tension négatives dans la tension  $V_{DSp}$  sont ainsi sensiblement ou complètement supprimées.

Dans certaines modes de réalisation, seules les impulsions négatives 210 pourraient être générées par le générateur d'impulsions 128 et appliquées au noeud de commande du transistor 104.

La figure 3A illustre schématiquement plus en détail le générateur d'impulsions 128 selon un exemple de réalisation dans lequel il est mis en oeuvre par un filtre RC. Le générateur d'impulsions 128 comprend par exemple un condensateur 302 couplé entre la ligne d'entrée 134 et la ligne de sortie 130, et une résistance 304 couplée entre la ligne de sortie 130 et la tension d'alimentation VDD. Le générateur d'impulsions 128 comprend aussi par exemple un autre condensateur 306 couplé entre la ligne d'entrée 136 et la ligne de sortie 132, et une autre résistance 308 couplée entre la ligne de sortie 132 et la tension d'alimentation VDD. Bien que les résistances 304, 308 soient couplées à la tension d'alimentation VDD, dans des variantes de réalisation, elles pourraient être couplées à une tension intermédiaire alternative dans la plage de tension de la tension de sortie  $V_{OUT}$ .

Les condensateurs 302 et 306 ont chacun par exemple une capacité comprise entre 10 et 100 fF, et les résistances ont

chacune par exemple une résistance comprise entre 500 ohm et 2 kilo-ohms.

La figure 3B illustre schématiquement le générateur d'impulsions 128 selon un autre exemple de réalisation similaire à celui de la figure 3A, et les éléments similaires portent les mêmes références et ne seront pas décrits de nouveau en détail. Toutefois, dans le circuit de la figure 3B, il n'y a pas de ligne d'entrée 136, et à la place le condensateur 306 est couplé entre la ligne d'entrée 134 et la ligne de sortie 132.

Dans une variante de réalisation de la figure 3B, le condensateur 306 et la résistance 308 pourraient être omis, et les deux transistors pourraient être couplés à la même ligne de sortie 130 du générateur d'impulsions 128. Un avantage de l'utilisation d'un filtre séparé pour chaque branche est que la capacité de chaque condensateur peut être choisie pour s'adapter au transistor 102, 104 respectif.

La figure 4 illustre schématiquement un amplificateur haute tension 400 selon une variante d'exemple de réalisation. L'amplificateur 400 est très similaire à l'amplificateur 100 de la figure 1, et les éléments similaires portent les mêmes références et ne seront pas décrits de nouveau en détail.

Dans l'exemple de la figure 4, un inverseur 402 est disposé entre le noeud d'entrée 116 et l'entrée du tampon 114. Le dispositif de décalage de niveau 126 est couplé à la sortie de l'inverseur 402.

Un exemple du circuit mettant en oeuvre le dispositif de décalage de niveau 126 est représenté en figure 4, et comprend un condensateur 404 couplé entre la sortie de l'inverseur 402 et un noeud 406. Deux inverseurs 408, 410 sont couplés de façon croisée entre le noeud 406 et un noeud de sortie 412 du dispositif de décalage de niveau. Les tensions d'alimentation des inverseurs 408 et 410 sont par exemple VDD et 2VDD, de sorte que le condensateur 404 et les inverseurs 408, 410 ensemble décalent positivement le niveau continu du signal d'entrée du niveau de VDD.

Dans l'exemple de la figure 4, le générateur d'impulsions 128 est mis en oeuvre par le circuit de la figure 3B, recevant seulement le signal  $V_{SL}'$  à partir d'une sortie du tampon 114. Le signal  $V_{SL}'$  est par exemple fourni à l'entrée du générateur d'impulsions 128 par l'intermédiaire d'un autre inverseur 414.

Les inverseurs 110 et 120 sont aussi illustrés plus en détail en figure 4, et chacun comprend par exemple un transistor PMOS et un transistor NMOS couplés en série entre les tensions d'alimentation respectives.

Le retard introduit par les inverseurs 113 et 110 est par exemple choisi sensiblement égal au retard introduit par l'inverseur 414 et le générateur d'impulsions 128. En outre, le retard introduit par le tampon 114 et les inverseurs 113 et 110 est par exemple choisi sensiblement égal au retard introduit par le dispositif de décalage de niveau 126, le tampon 124 et l'inverseur 120.

La figure 4 illustre aussi un condensateur 418, qui est par exemple couplé entre les noeuds de source 108 et 118 des transistors 102, 104 pour lisser la tension appliquée aux bornes de ces transistors.

La figure 5 illustre schématiquement un système de transmission optique selon un exemple de réalisation. Le système 500 est par exemple intégré sur une puce, et comprend un modulateur optique (OPTICAL MODULATOR) 502 qui transmet un signal optique par l'intermédiaire d'un guide d'onde 504 à un démodulateur optique (OPTICAL DEMODULATOR) 506. Le modulateur optique 502 comprend par exemple un modulateur en anneau (non illustré en figure 5) ayant une fréquence d'oscillation variable par l'intermédiaire du niveau du signal de tension  $V_C$  qu'on lui applique. Le signal de tension  $V_C$  a par exemple une plage de tension d'au moins 2 V, par exemple de 2,2 V ou plus. Le modulateur optique 502 reçoit le signal de tension  $V_C$  par l'intermédiaire d'un pilote de modulateur photonique (DRIVER) 508, qui comprend par exemple le circuit de la figure 1 ou de la

figure 4, et génère la tension  $V_C$  sur la base d'un signal d'entrée DATA. Le signal de données DATA a par exemple un débit binaire compris entre 10 et 20 Gb/s.

Un avantage des modes de réalisation décrits ici est que, en prévoyant un générateur d'impulsions constitué d'un filtre passe-haut passif, on peut réduire ou éviter complètement une surtension aux bornes des transistors d'un amplificateur haute tension, sans augmenter fortement la surface ou la consommation du circuit.

Avec la description ainsi faite d'au moins un mode illustratif, diverses altérations, modifications et améliorations apparaîtront facilement à l'homme de l'art.

Par exemple, bien que l'on ait décrit des circuits amplificateurs comprenant un chemin à haute tension et un chemin à basse tension, il sera clair pour l'homme de l'art que dans des variantes de réalisation un ou plusieurs chemins additionnels pourraient être ajoutés afin de générer des niveaux de tension de sortie encore plus élevés.

En outre, bien que la plage de tension dans chacun des chemins à haute et à basse tension dans les modes de réalisation décrits soient égale à la tension d'alimentation VDD, dans des variantes de réalisation, d'autres plages seraient possibles. En outre, il sera aussi clair pour l'homme de l'art que la tension d'alimentation VDD dans les divers modes de réalisation pourrait être à un niveau quelconque, par exemple entre 1 et 2 V, et plutôt que d'être à 0 V, la tension de masse pourrait être une tension d'alimentation à un niveau de tension différent, comme un niveau négatif.

En outre, bien qu'on ait décrit ici des transistors en technologie MOS, dans des variantes de réalisation on pourrait utiliser d'autres technologies de transistors, comme la technologie bipolaire.

En outre, il sera clair pour l'homme de l'art que les divers éléments décrits en relation avec les divers modes de

13

réalisation pourraient être combinés, dans des variantes de réalisation, selon des combinaisons quelconques.

REVENDICATIONS

1. Amplificateur haute tension comprenant :

des premier et deuxième transistors en cascode (102, 104) adaptés à générer un signal de sortie ( $V_{OUT}$ ) sur la base d'un premier signal de tension ( $V_{SL}, V_{SL}'$ ) ayant une première plage de tension, et d'un deuxième signal de tension ( $V_{SH}, V_{SH}'$ ) ayant une plage de tension décalée par rapport à la première plage de tension, le signal de sortie ayant une deuxième plage de tension supérieure à la première plage de tension ; et

un générateur d'impulsions (128) comprenant un filtre passe-haut passif adapté à générer des impulsions de tension sur la base d'au moins l'un des premier et deuxième signaux de tension et à fournir les impulsions de tension à un noeud de commande d'au moins l'un des premier et deuxième transistors.

2. Amplificateur haute tension selon la revendication 1, dans lequel le filtre passe-haut passif est adapté à générer les impulsions de tension sur la base seulement du premier signal de tension ( $V_{SL}, V_{SL}'$ ) et à fournir les impulsions de tension aux noeuds de commande des premier et deuxième transistors (102, 104).

3. Amplificateur haute tension selon la revendication 1 ou 2, comprenant en outre :

un premier tampon (114) adapté à générer le premier signal de tension ( $V_{SL}, V_{SL}'$ ) sur la base d'un signal d'entrée ( $V_{IN}$ ) ;

un dispositif de décalage de niveau (126) adapté à décaler la plage de tension du signal d'entrée pour générer un signal décalé en tension ; et

un deuxième tampon (124) adapté à générer le deuxième signal de tension ( $V_{SH}$ ) sur la base du signal décalé en tension.

4. Amplificateur haute tension selon la revendication 3, comprenant en outre :

un premier inverseur (110) ayant une entrée couplée de façon à recevoir le premier signal de tension et une sortie

couplée à un premier noeud de courant principal du premier transistor (102) ;

un deuxième inverseur (120) ayant une entrée couplée de façon à recevoir le deuxième signal de tension, et une sortie couplée à un premier noeud de courant principal du deuxième transistor (104) ; et

un noeud de sortie (106) couplé à des deuxièmes noeuds de courant principaux des premier et deuxième transistors.

5 5. Amplificateur haute tension selon la revendication 4, comprenant en outre au moins un autre inverseur (113) couplé entre une sortie du premier tampon et une entrée du premier inverseur (110).

10 6. Amplificateur haute tension selon l'une quelconque des revendications 1 à 5, dans lequel le premier transistor est 15 un transistor MOS à canal N, le deuxième transistor est un transistor MOS à canal P, et le filtre passe-haut passif est adapté à :

20 générer des impulsions qui sont positives par rapport à un niveau de tension intermédiaire (VDD) dans la deuxième plage de tension en réponse à des fronts montants du premier ou du deuxième signal de tension ; et

25 générer des impulsions qui sont négatives par rapport au niveau de tension intermédiaire (VDD) dans la deuxième plage de tension en réponse à des fronts descendants du premier ou du deuxième signal de tension.

7. Amplificateur haute tension selon l'une quelconque des revendications 1 à 6, dans lequel le filtre passe-haut passif est un filtre RC comprenant :

30 un premier condensateur (302) couplé entre une entrée (134, 136) du générateur d'impulsions (128) et le noeud de commande du premier transistor (102) ; et

une première résistance (304) couplée entre le noeud de commande du premier transistor (102) et un niveau de tension intermédiaire (VDD) dans la deuxième plage de tension.

8. Amplificateur haute tension selon la revendication 7, dans lequel le filtre passe-haut passif comprend en outre :

un deuxième condensateur (306) couplé entre l'entrée (134, 136) du générateur d'impulsions (128) et le noeud de commande du deuxième transistor (104) ; et

une deuxième résistance (308) couplée entre le noeud de commande du deuxième transistor (102) et le niveau de tension intermédiaire (VDD).

9. Modulateur photonique comprenant l'amplificateur haute tension de l'une quelconque des revendications 1 à 8.

10. Procédé pour générer un signal à haute tension comprenant :

générer une tension de sortie par des premier et deuxième transistors en cascode (102, 104) sur la base d'un premier signal de tension ( $V_{SL}$ ,  $V_{SL'}$ ) ayant une première plage de tension et d'un deuxième signal de tension ( $V_{SH}$ ,  $V_{SH'}$ ) ayant une plage de tension décalée par rapport à la première plage de tension, le signal de sortie ayant une deuxième plage de tension supérieure à la première plage de tension ;

générer, par un filtre passe-haut passif d'un générateur d'impulsions (128), des impulsions de tension sur la base d'au moins l'un des premier et deuxième signaux de tension ; et

fournir les impulsions de tension à un noeud de commande d'au moins l'un des premier et deuxième transistors.

1/2

Fig 1

Fig 2

Fig 3A

Fig 3B

Fig 4

Fig 5

**RAPPORT DE RECHERCHE

PRÉLIMINAIRE**

établi sur la base des dernières revendications

déposées avant le commencement de la recherche

N° d'enregistrement

nationalFA 799419

FR 1456429

| <b>DOCUMENTS CONSIDÉRÉS COMME PERTINENTS</b>                                                                                                             |                                                                                                                                                                                            | Revendication(s)<br>concernée(s)        | Classement attribué<br>à l'invention par l'INPI |  |  |

|----------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------|-------------------------------------------------|--|--|

| Catégorie                                                                                                                                                | Citation du document avec indication, en cas de besoin,<br>des parties pertinentes                                                                                                         |                                         |                                                 |  |  |

| X                                                                                                                                                        | WO 85/04537 A1 (AMERICAN TELEPHONE &<br>TELEGRAPH [US])<br>10 octobre 1985 (1985-10-10)                                                                                                    | 1-6,9,10                                | H01L27/06                                       |  |  |

| A                                                                                                                                                        | * page 2, ligne 31 - page 8, ligne 15;<br>figures 1-3 *                                                                                                                                    | 7,8                                     |                                                 |  |  |

| X                                                                                                                                                        | -----                                                                                                                                                                                      | 1-6,9,10                                |                                                 |  |  |

| A                                                                                                                                                        | EP 0 542 480 A2 (AMERICAN TELEPHONE &<br>TELEGRAPH [US]) 19 mai 1993 (1993-05-19)<br>* colonne 2, ligne 3 - colonne 5, ligne 3;<br>figures 1-3 *                                           | 7,8                                     |                                                 |  |  |

| X                                                                                                                                                        | -----                                                                                                                                                                                      | 1-3,9,10                                |                                                 |  |  |

| A                                                                                                                                                        | WO 95/20266 A1 (ARITHMOS INC [US];<br>NEUGEBAUER CHARLES F [US]; BRUNETTI JON<br>[US]; STEIN) 27 juillet 1995 (1995-07-27)<br>* page 4, ligne 25 - page 37, ligne 29;<br>figures 2,11-16 * | 4-8                                     |                                                 |  |  |

|                                                                                                                                                          | -----                                                                                                                                                                                      |                                         |                                                 |  |  |

|                                                                                                                                                          |                                                                                                                                                                                            | DOMAINES TECHNIQUES<br>RECHERCHÉS (IPC) |                                                 |  |  |

|                                                                                                                                                          |                                                                                                                                                                                            |                                         | H03K                                            |  |  |

| 2                                                                                                                                                        |                                                                                                                                                                                            |                                         |                                                 |  |  |

| Date d'achèvement de la recherche                                                                                                                        |                                                                                                                                                                                            | Examinateur                             |                                                 |  |  |

| 30 janvier 2015                                                                                                                                          |                                                                                                                                                                                            | Kassner, Holger                         |                                                 |  |  |

| CATÉGORIE DES DOCUMENTS CITÉS                                                                                                                            |                                                                                                                                                                                            |                                         |                                                 |  |  |

| X : particulièrement pertinent à lui seul                                                                                                                |                                                                                                                                                                                            |                                         |                                                 |  |  |

| Y : particulièrement pertinent en combinaison avec un autre document de la même catégorie                                                                |                                                                                                                                                                                            |                                         |                                                 |  |  |

| A : arrière-plan technologique                                                                                                                           |                                                                                                                                                                                            |                                         |                                                 |  |  |

| O : divulcation non-écrite                                                                                                                               |                                                                                                                                                                                            |                                         |                                                 |  |  |

| P : document intercalaire                                                                                                                                |                                                                                                                                                                                            |                                         |                                                 |  |  |

| T : théorie ou principe à la base de l'invention                                                                                                         |                                                                                                                                                                                            |                                         |                                                 |  |  |

| E : document de brevet bénéficiant d'une date antérieure à la date de dépôt et qui n'a été publié qu'à cette date de dépôt ou qu'à une date postérieure. |                                                                                                                                                                                            |                                         |                                                 |  |  |

| D : cité dans la demande                                                                                                                                 |                                                                                                                                                                                            |                                         |                                                 |  |  |

| L : cité pour d'autres raisons                                                                                                                           |                                                                                                                                                                                            |                                         |                                                 |  |  |

| & : membre de la même famille, document correspondant                                                                                                    |                                                                                                                                                                                            |                                         |                                                 |  |  |

**ANNEXE AU RAPPORT DE RECHERCHE PRÉLIMINAIRE

RELATIF A LA DEMANDE DE BREVET FRANÇAIS NO. FR 1456429 FA 799419**

La présente annexe indique les membres de la famille de brevets relatifs aux documents brevets cités dans le rapport de recherche préliminaire visé ci-dessus.

Les dits membres sont contenus au fichier informatique de l'Office européen des brevets à la date du **30-01-2015**

Les renseignements fournis sont donnés à titre indicatif et n'engagent pas la responsabilité de l'Office européen des brevets, ni de l'Administration française

| Document brevet cité<br>au rapport de recherche | Date de<br>publication | Membre(s) de la<br>famille de brevet(s)                                         | Date de<br>publication                                             |

|-------------------------------------------------|------------------------|---------------------------------------------------------------------------------|--------------------------------------------------------------------|

| WO 8504537                                      | A1 10-10-1985          | CA 1229655 A1<br>JP S61501671 A<br>US 4571506 A<br>WO 8504537 A1                | 24-11-1987<br>07-08-1986<br>18-02-1986<br>10-10-1985               |

| EP 0542480                                      | A2 19-05-1993          | EP 0542480 A2<br>JP H0669544 A<br>US 5329210 A                                  | 19-05-1993<br>11-03-1994<br>12-07-1994                             |

| WO 9520266                                      | A1 27-07-1995          | AU 1731295 A<br>JP H09508245 A<br>US 5504444 A<br>US 5696459 A<br>WO 9520266 A1 | 08-08-1995<br>19-08-1997<br>02-04-1996<br>09-12-1997<br>27-07-1995 |