(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第6340193号

(P6340193)

(45) 発行日 平成30年6月6日(2018.6.6)

(24) 登録日 平成30年5月18日(2018.5.18)

(51) Int.Cl.

F 1

G02F 1/1368 (2006.01)

G02F 1/1368

G02F 1/1343 (2006.01)

G02F 1/1343

請求項の数 7 (全 17 頁)

(21) 出願番号

特願2013-254206 (P2013-254206)

(22) 出願日

平成25年12月9日 (2013.12.9)

(65) 公開番号

特開2015-114375 (P2015-114375A)

(43) 公開日

平成27年6月22日 (2015.6.22)

審査請求日

平成28年12月7日 (2016.12.7)

(73) 特許権者 502356528

株式会社ジャパンディスプレイ

東京都港区西新橋三丁目7番1号

(74) 代理人 110000350

ポレール特許業務法人

(72) 発明者 廣田 武徳

東京都港区西新橋三丁目7番1号 株式会

社ジャパンディスプレイ内

審査官 磯崎 忠昭

最終頁に続く

(54) 【発明の名称】 液晶表示装置

## (57) 【特許請求の範囲】

## 【請求項 1】

コモン電極の上に絶縁膜を挟んでスリットを有する画素電極が形成され、TFTを有する画素がマトリクス状に形成された表示領域を有し、表示領域の外側にダミー画素が形成されたTFT基板と、

カラーフィルタが形成された表示領域と表示領域周辺をブラックマトリクスによって覆った対向基板を有し、TFT基板と対向基板との間に液晶層が挟持された液晶表示装置であって、

前記表示領域の最外周の画素に印加される信号電圧と同じ電圧を、前記最外周の画素に隣接する前記ダミー画素に印加し、

前記TFT基板において、前記ダミー画素の外側に第1周辺電極が配置され、前記第1周辺電極には、コモン電圧が印加されることを特徴とする液晶表示装置。

## 【請求項 2】

コモン電極の上に絶縁膜を挟んでスリットを有する画素電極が形成され、TFTを有する画素がマトリクス状に形成された表示領域を有し、表示領域の外側にダミー画素が形成されたTFT基板と、

カラーフィルタが形成された表示領域と表示領域周辺をブラックマトリクスによって覆った対向基板を有し、TFT基板と対向基板との間に液晶層が挟持された液晶表示装置であって、

前記液晶層におけるスレッショルド電圧をV<sub>th</sub>とし、前記表示領域の最外の画素の電

圧を  $V_{active}$  とし、前記最外の画素に隣接するダミー画素に印加する電圧を  $V_{dummy}$ とした場合、

$V_{active}$  が  $V_{com}$   $V_{active} < V_{th}$  を満たす場合、

$V_{dummy} = V_{active}$  とし、

$V_{active}$  が  $V_{th}$   $V_{active}$  を満たす場合、

$V_{dummy} = V_{th}$  とすることを特徴とする液晶表示装置。

#### 【請求項 3】

コモン電極の上に絶縁膜を挟んでスリットを有する画素電極が形成され、TFTを有する画素がマトリクス状に形成された表示領域を有し、表示領域の外側にダミー画素が形成されたTFT基板と、

10

カラーフィルタが形成された表示領域と表示領域周辺をブラックマトリクスによって覆った対向基板を有し、TFT基板と対向基板との間に液晶層が挟持された液晶表示装置であって、

前記表示領域の表示画面の平均輝度に相当する信号電圧を前記表示領域最外の画素に隣接するダミー画素に印加し、

前記TFT基板において、前記ダミー画素の外側に第1周辺電極が配置され、前記第1周辺電極には、コモン電圧が印加されることを特徴とする液晶表示装置。

#### 【請求項 4】

前記TFT基板において、前記ダミー画素の外側に第1周辺電極が配置され、前記第1周辺電極には、コモン電圧が印加されることを特徴とする請求項2に記載の液晶表示装置。

20

#### 【請求項 5】

前記対向基板において、前記表示領域の外側に第2周辺電極が配置され、前記第2周辺電極にはコモン電圧が印加されることを特徴とする請求項1、3、または4のいずれか1項に記載の液晶表示装置。

#### 【請求項 6】

前記対向基板において、前記表示領域の外側に第2周辺電極が配置され、前記第2周辺電極にはコモン電圧が印加されることを特徴とする請求項1乃至3のいずれか1項に記載の液晶表示装置。

#### 【請求項 7】

30

前記対向基板はタッチパネル用電極を含むことを特徴とする請求項1乃至6のいずれか1項に記載の液晶表示装置。

#### 【発明の詳細な説明】

##### 【技術分野】

##### 【0001】

本発明は表示装置に係り、特に視野角特性の優れた横電界方式の液晶表示装置に関する

。

##### 【背景技術】

##### 【0002】

液晶表示装置では画素電極および薄膜トランジスタ(TFT)等を有する画素がマトリクス状に形成されたTFT基板と、TFT基板に対向して、TFT基板の画素電極と対応する場所にカラーフィルタが形成された対向基板が配置され、TFT基板と対向基板の間に液晶が挟持されている。そして液晶分子による光の透過率を画素毎に制御することによって画像を形成している。

40

##### 【0003】

液晶表示装置はフラットで軽量であることから、色々な分野で用途が広がっている。携帯電話やDSC(Digital Still Camera)等には、小型の液晶表示装置が広く使用されている。液晶表示装置では視野角特性が問題である。視野角特性は、画面を正面から見た場合と、斜め方向から見た場合に、輝度が変化したり、色度が変化したりする現象である。視野角特性は、液晶分子を水平方向の電界によって動作させるIPS

50

(In Plane Switching) 方式が優れた特性を有している。

#### 【0004】

液晶表示装置では、画素がマトリクス状に配置した表示領域と周辺領域が存在する。周辺領域には、ダミー画素領域、周辺配線領域、TFT基板と対向基板を接着するシール部などが存在している。表示領域と周辺領域とは信号電圧のかかり方等が急激に変化するため、特に表示領域の最外側の画素部分にイオンや不純物が掃き寄せられて、この部分において、光もれや、表示むらを生ずる場合が多い。

#### 【0005】

特許文献1には、表示領域最外周の画素が信号印加領域と隣接する構成が記載されている。このような構成においては、表示領域最外画素の外側には映像信号線が存在しておらず、信号印加領域におけるゲート配線とコモン配線の電位差によるイオンのトラップが発生し、その結果、この部分における光もれが発生する。10

#### 【0006】

この問題を対策するために、特許文献1では表示領域最外画素を他の画素よりも大きく、画素電極を信号印加領域に形成した構成が記載されている。この構成であれば、画素電極によって、最外の画素にのみ発生する信号印加領域の影響を抑制することが出来る。しかし、この構成は、表示領域最外の画素を他の画素よりも大きくしたことにより、他の画素との面積のバランスがくずれ、表示領域の最外付近における色バランスが崩れる。また、画素を大きくした分、イオン等の影響を抑制できるが、掃き寄せられるイオンや不純物が多くなった場合は、対処が難しくなる。20

#### 【0007】

特許文献2には、表示領域の周辺に異なる電圧を印加する2種類の電極を配置し、この2種類の電極から横電界を発生させることによって、表示領域の周辺に集まつたイオンや不純物を表示領域外に移動させる構成が記載されている。この構成は、表示領域最外画素に隣接して、上記2種類の電極を配置する必要があるが、表示領域における画素構造と上記2種類の電極との形状や厚さが異なるために、境界部における平坦性が悪化し、表示領域周辺における表示品質の劣化を招く恐れがある。

#### 【先行技術文献】

#### 【特許文献】

#### 【0008】

【特許文献1】特開2003-84303号公報

【特許文献2】特開2008-58497号公報

#### 【発明の概要】

#### 【発明が解決しようとする課題】

#### 【0009】

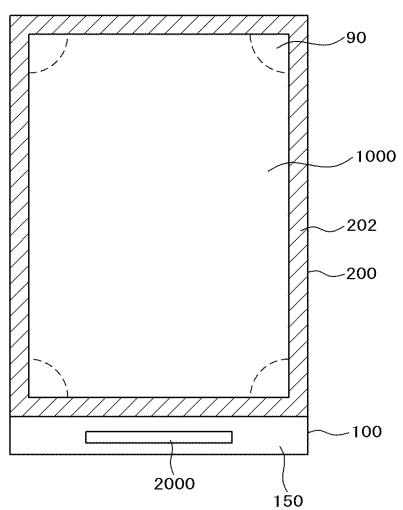

図16は、IPS方式の液晶表示装置において、表示領域1000のコーナー部に不純物、イオン等の影響に起因するむらが発生した場合の様子を示している。図16において、対向基板200にはカラーフィルタが形成された表示領域1000を囲んでブラックマトリクス202が形成されている。一方、TFT基板において、画素が形成された表示領域に隣接する周辺で、対向基板200に形成されたブラックマトリクス202で覆われた部分には、ダミー画素が形成されている。ダミー画素は、表示領域1000の最外画素とその外側において、構造が急激に変化することによる影響を防止するために形成されており、ダミー画素側は表示には寄与しない。40

#### 【0010】

TFT基板100は対向基板200よりも大きく形成されており、TFT基板100が1枚となっている部分は端子部150となっており、この部分にICドライバ2000や、図示しないフレキシブル配線基板が接続されている。

#### 【0011】

図16において、表示領域1000の画素には映像信号が印加されており、ダミー画素にはコモン電圧が印加されている。この場合、表示領域1000の画素とダミー画素との50

間には、常に電圧が発生していることになる。したがって、液晶中のイオンや不純物が表示領域最外画素とダミー画素との間の電界に吸い寄せられて集まつてくる。そうすると、このイオンや不純物によって、表示領域最外画素付近に光もれが発生し、表示むらを発生する。

#### 【0012】

この現象は、特に、画面のコーナー部に強く生ずる。図16に示す表示むら90は、この現象によって現れるものである。表示むら90は、全てのコーナーにおいて生ずるとは限らず、液晶の初期配向の向き、電極の形状等によっても影響を受ける。いずれにしても、表示品質を劣化させることには変わりがない。

#### 【0013】

本発明の課題は、以上述べた、画面コーナー部における表示むら90を抑制することである。

10

#### 【課題を解決するための手段】

#### 【0014】

本発明は上記問題を克服するものであり、具体的な手段は次のとおりである。

#### 【0015】

(1) コモン電極の上に絶縁膜を挟んでスリットを有する画素電極が形成され、TFTを有する画素がマトリクス状に形成された表示領域を有し、表示領域の外側にダミー画素が形成されたTFT基板と、カラーフィルタが形成された表示領域と表示領域周辺をブラックマトリクスによって覆った対向基板を有し、TFT基板と対向基板との間に液晶層が挟持された液晶表示装置であって、前記表示領域の最外周の画素に印加される信号電圧と同じ電圧を、前記最外画素に隣接する前記ダミー画素に印加することを特徴とする液晶表示装置。

20

#### 【0016】

(2) コモン電極の上に絶縁膜を挟んでスリットを有する画素電極が形成され、TFTを有する画素がマトリクス状に形成された表示領域を有し、表示領域の外側にダミー画素が形成されたTFT基板と、カラーフィルタが形成された表示領域と表示領域周辺をブラックマトリクスによって覆った対向基板を有し、TFT基板と対向基板との間に液晶層が挟持された液晶表示装置であって、前記液晶層におけるスレッショルド電圧をVthとし、前記表示領域最外の画素の電圧をVactiveとし、前記最外の画素に隣接するダミー画素に印加する電圧をVdummyとした場合、VactiveがVcom Vactive < Vthを満たす場合、Vdummy = Vactiveとし、VactiveがVth Vactiveを満たす場合、Vdummy = Vthとすることを特徴とする液晶表示装置。

30

#### 【0017】

(3) コモン電極の上に絶縁膜を挟んでスリットを有する画素電極が形成され、TFTを有する画素がマトリクス状に形成された表示領域を有し、表示領域の外側にダミー画素が形成されたTFT基板と、カラーフィルタが形成された表示領域と表示領域周辺をブラックマトリクスによって覆った対向基板を有し、TFT基板と対向基板との間に液晶層が挟持された液晶表示装置であって、前記表示領域の表示画面の平均輝度に相当する信号電圧を前記表示領域最外の画素に隣接するダミー画素に印加することを特徴とする液晶表示装置。

40

#### 【発明の効果】

#### 【0018】

本発明によれば、液晶表示装置中のイオンや不純物を周辺のブラックマトリクスで遮光された部分に移動させてるので、表示領域最外周の画素にイオンや不純物が集められることによる、特に画面コーナーにおける表示むらを防止することが出来る。

#### 【図面の簡単な説明】

#### 【0019】

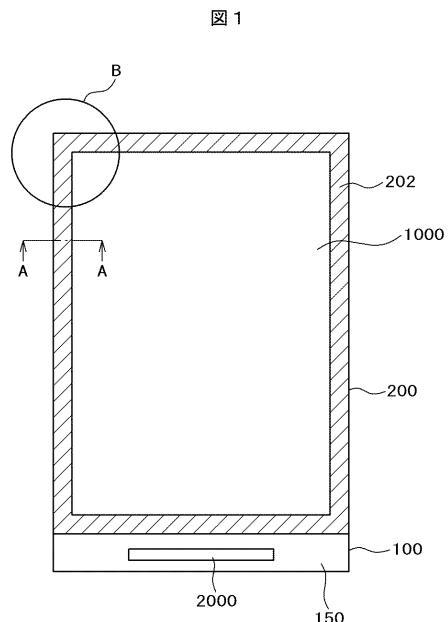

【図1】本発明が適用される液晶表示装置の平面図である。

50

- 【図2】液晶表示装置の画素部の断面図である。

- 【図3】画素電極およびコモン電極の平面図である。

- 【図4】実施例1および2のTFT基板の平面図である。

- 【図5】実施例1および2の対向電極の平面図である。

- 【図6】実施例1および2の断面図である。

- 【図7】液晶層における電圧と透過率の関係を示すグラフである。

- 【図8】液晶表示装置の駆動波形の例である。

- 【図9】実施例3のTFT基板の平面図である。

- 【図10】実施例3の断面図である。

- 【図11】実施例4の対向電極の平面図である。

- 【図12】実施例4の断面図である。

- 【図13】実施例5の断面図である。

- 【図14】第2周辺電極の配置例である。

- 【図15】実施例6の断面図である。

- 【図16】従来例の問題点を示す液晶表示装置の平面図である。

## 【発明を実施するための形態】

## 【0020】

図1は、本発明が適用される製品の例である、携帯電話等に使用される小型の液晶表示装置の平面図である。図1において、TFT基板100の上に対向基板200が配置されている。TFT基板100と対向基板200の間に後述する液晶層が挟持されている。TFT基板100と対向基板200とはブラックマトリクス202によって覆われた額縁部に形成された後述するシール材によって接着している。図1においては、液晶は滴下方式によって封入されるので、封入孔は形成されていない。

## 【0021】

TFT基板100は対向基板200よりも大きく形成されており、TFT基板100が対向基板200よりも大きくなっている部分には、液晶セル1に電源、映像信号、走査信号等を供給するための端子部150が形成されている。

## 【0022】

端子部150には、ICドライバ2000が配置され、図示しないフレキシブル配線基板が接続されることは図16において説明したとおりである。図1の表示領域1000には、多数の画素がマトリクス状に形成されている。また、対向基板がブラックマトリクス202で覆われている周辺領域のTFT基板側には後述するダミー画素、周辺配線、TFT基板と対向基板を接着するシール材等が形成されている。

## 【0023】

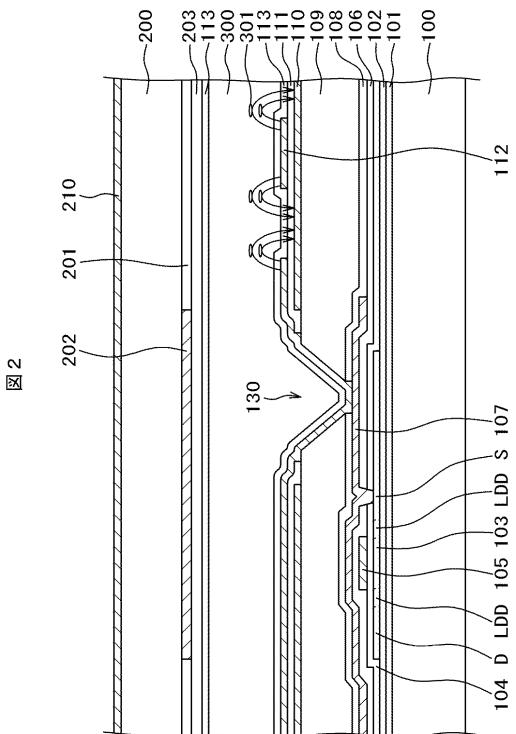

図2は図1に示す表示領域1000の画素部の構造を示す断面図である。図2は、本発明が適用されるIPS方式液晶表示パネルの構造について説明するものである。図2において、ガラス基板100の上にSiNからなる第1下地膜101およびSiO<sub>2</sub>からなる第2下地膜102がCVD(Chemical Vapor Deposition)によって形成される。第1下地膜101および第2下地膜102の役割はガラス基板10からの不純物が半導体層103を汚染することを防止することである。

## 【0024】

第2下地膜102の上には半導体層103が形成される。この半導体層103は第2下地膜102に上にCVDによってa-Si膜を形成し、これをレーザアニールすることによってpoly-Si膜に変換したものである。このpoly-Si膜をフォトリソグラフィによってパターニングする。

## 【0025】

半導体膜103の上にはゲート絶縁膜104が形成される。このゲート絶縁膜104はTEOS(テトラエトキシシラン)によるSiO<sub>2</sub>膜である。この膜もCVDによって形成される。その上にゲート電極105が形成される。ゲート電極105は走査信号線と同層で、同時に形成される。ゲート電極105は例えば、MoW膜によって形成される。ゲ

10

20

30

40

50

ート配線 105 の抵抗を小さくする必要があるときは A1 合金が使用される。

【0026】

ゲート電極 105 はフォトリソグラフィによってパターニングされるが、このパターニングの際に、イオンインプランテーションによって、リンあるいはボロン等の不純物を poly-Si 層にドープして poly-Si 層にソース S あるいはドレイン D を形成する。また、ゲート電極 105 のパターニングの際のフォトレジストを利用して、poly-Si 層のチャネル層と、ソース S あるいはドレイン D との間に LDD (Lightly Doped Drain) 領域を形成する。

【0027】

その後、ゲート電極 105 あるいはゲート配線 105 を覆って層間絶縁膜 106 を SiO<sub>2</sub> によって形成する。層間絶縁膜 106 はゲート配線 105 とソース電極 107 を絶縁するためである。層間絶縁膜 106 の上にソース電極 107 が形成される。ソース電極 107 は、スルーホール 130 を介して画素電極 112 と接続する。図 2においては、ソース電極 107 は広く形成され、TFT を覆う形となっている。一方、TFT のドレイン D は、図示しない部分においてドレイン電極と接続している。

【0028】

ソース電極 107 はドレイン電極及びドレイン電極に接続される映像信号線と同層で、同時に形成される。ソース電極 107 あるいは映像信号線（以後ソース電極 107 で代表させる）は、抵抗を小さくするために、AlSi 合金が使用される。AlSi 合金はヒロックを発生したり、Al が他の層に拡散したりするので、MoW によるバリア層、および SD キャップ層によって AlSi をサンドイッチする構造がとられている。

【0029】

ソース電極 107 と TFT のソース S を接続するために、ゲート絶縁膜 104 と層間絶縁膜 106 にスルーホールが形成され、TFT のソース S とソース電極 107 とが接続される。ソース電極 107 を覆って無機パッシベーション膜（絶縁膜）108 が形成され、TFT 全体を保護する。無機パッシベーション膜 108 は第 1 下地膜 101 と同様に CVD によって形成される。

【0030】

無機パッシベーション膜 108 を覆って有機パッシベーション膜 109 が形成される。有機パッシベーション膜 109 は感光性のアクリル樹脂で形成される。有機パッシベーション膜は、アクリル樹脂の他、シリコーン樹脂、エポキシ樹脂、ポリイミド樹脂等でも形成することが出来る。有機パッシベーション膜 109 は平坦化膜としての役割を持っているので、厚く形成される。有機パッシベーション膜 109 の膜厚は 1 ~ 4 μm であるが、多くの場合は 2 μm 程度である。

【0031】

画素電極 110 とソース電極 107 との導通を取るために、無機パッシベーション膜 108 および有機パッシベーション膜 109 にスルーホール 130 が形成される。有機パッシベーション膜 109 は感光性の樹脂を使用している。感光性の樹脂を塗付し、仮焼成して固化した後、この樹脂を露光すると、光が当たった部分のみが特定の現像液に溶解する。すなわち、感光性樹脂を用いることによって、フォトレジストの形成を省略することが出来る。有機パッシベーション膜 109 にスルーホールを形成したあと、230 度程度で有機パッシベーション膜を焼成することによって有機パッシベーション膜が完成する。

【0032】

有機パッシベーション膜 109 をレジストとしてドライエッチにより無機パッシベーション膜 108 にスルーホールを形成する。こうして、ドレイン電極 130 と画素電極 110 を導通するためのスルーホール 130 が形成される。有機パッシベーション膜 109 は厚いので、スルーホール 130 の上側と下側では、孔の大きさが異なる。

【0033】

このようにして形成された有機パッシベーション膜 109 の上面は平坦となっている。有機パッシベーション膜 109 の上にアモルファスITO (Indium Tin Oxide)

10

20

30

40

50

i d e )をスパッタリングによって被着し、フォトレジストによって、パターニングした後、蔥酸でエッチングし、コモン電極 110 のパターニングを行う。コモン電極 110 はスルーホール 130 を避けて、平面ベタで形成される。その後、230°で焼成して、ITOを多結晶化して、電気抵抗を低下させる。コモン電極 110 は透明電極であるITOによって形成され、厚さは例えば、77 μm である。

#### 【0034】

その後、コモン電極 110 を覆って、層間絶縁膜 111 を CVD によって成膜する。このときの CVD の温度条件は、230°程度であり、これは低温 CVD と呼ばれる。その後、フォトリソグラフィ工程によって、層間絶縁膜 111 のパターニングを行う。図 2においては、有機パッシベーション膜 109 のスルーホール 113 内壁には層間絶縁膜 111 は形成されていない。10

#### 【0035】

ところで、他の膜、例えば、第 1 下地膜 101、無機パッシベーション膜 108 等を CVD で形成する時は、300°以上で行われる。一般に、CVD 膜等は、高温で形成したほうが、下地膜との接着力は強くすることが出来る。しかし、層間絶縁膜 111 の下には有機パッシベーション膜 109 がすでに形成されているので、230°以上の高温にすると、有機パッシベーション膜 109 の特性が変化するので、層間絶縁膜 111 の形成は低温 CVD で行われる。本実施例では、図 2 に示すように、層間絶縁膜 111 をスルーホール 113 の内壁に形成せず、有機パッシベーション膜 109 の平坦部のみに形成している。層間絶縁膜へのストレスを軽減するためである。但し、層間絶縁膜の接着力が問題にならない場合等は、層間絶縁膜がスルーホールの内部にまで形成される場合もある。20

#### 【0036】

層間絶縁膜 111 の上にアモルファスITOをスパッタリングし、フォトリソグラフィ工程によって、櫛歯状の画素電極 112 を形成する。画素電極 112 はスルーホール 113 を介してソース電極 107 と接続する。画素電極 112 には信号電圧が印加され、コモン電極 110 との間に発生する電界によって、液晶分子を回転させ、画素毎に液晶層の光の透過量を制御し、画像を形成する。画素電極 112 は透明導電膜であるITOによって形成され、膜厚は、例えば、40 nm から 70 nm 程度である。

#### 【0037】

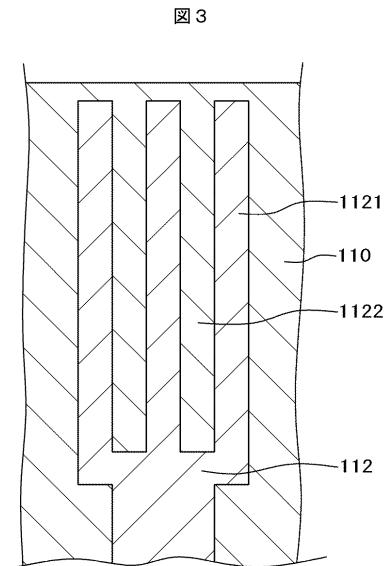

図 3 は、櫛歯状の画素電極 112 と平面ベタで形成されたコモン電極 110 の関係を示す平面図である。図 3において、画素電極 112 は、層間絶縁膜を挟んでコモン電極 110 の上に配置されている。画素電極 112 の櫛歯 1121 と櫛歯 1121 の間のスリット 1122 を通して、画素電極 112 上面からコモン電極 110 に電気力線が伸び、この電気力線によって液晶分子を回転させる。なお、図 3 の画素電極は、スリットの一方が開放された櫛歯状の電極となっているが、外形が略矩形であって、内側に開口端を有さないスリットを有する電極の場合もある。30

#### 【0038】

図 2 に戻り、液晶層 300 を挟んで対向基板 200 が配置されている。対向基板 200 の内側には、カラーフィルタ 201 が形成されている。カラーフィルタ 201 は画素毎に、赤、緑、青のカラーフィルタが形成されており、カラー画像が形成される。カラーフィルタ 201 とカラーフィルタ 201 の間にはブラックマトリクス 202 が形成され、画像のコントラストを向上させている。なお、ブラックマトリクス 202 は TFT の遮光膜としての役割も有し、TFT に光電流が流れることを防止している。40

#### 【0039】

カラーフィルタ 201 およびブラックマトリクス 202 を覆ってオーバーコート膜 203 が形成されている。カラーフィルタ 201 およびブラックマトリクス 202 の表面は凹凸となっているために、オーバーコート膜 203 によって表面を平らにしている。オーバーコート膜の上には、液晶の初期配向を決めるための配向膜 113 が形成されている。なお、図 2 は IPS であるから、対向電極 110 は TFT 基板 100 側に形成されており、対向基板 200 側には形成されていない。本明細書では、対向電極をコモン電極とよぶこ50

ともある。

#### 【0040】

図2に示すように、IPSでは、対向基板200の内側には導電膜が形成されていない。そうすると、対向基板200の電位が不安定になる。また、外部からの電磁ノイズが液晶層300に侵入し、画像に対して影響を与える。このような問題を除去するために、対向基板200の外側に外部導電膜210が形成される。外部導電膜210は、透明導電膜であるITOをスパッタリングすることによって形成される。

#### 【0041】

図2におけるTFTは、トップゲートの場合であるが、TFTがボトムゲートの場合もある。また、半導体層がpoly-Siではなく、a-Siの場合もある。いずれの場合も以下に述べる本発明を適用することが出来る。以上で説明した表示領域の画素構成は、以下で説明する実施例において共通である。なお、上で説明したIPSの構成は、IPS方式の構成の例であって、本発明は他の構成のIPSに対しても適用することが出来る。

10

#### 【0042】

以下に本発明を、実施例を用いて詳細に説明する。以下の実施例における断面図では、対向基板200の外側に形成される外部導電膜210が省略されているが、実際には、外部導電膜210が形成されることが一般的である。本発明は、対向基板200側の外部導電膜210の有無にかかわらず適用することが出来る。

#### 【実施例1】

20

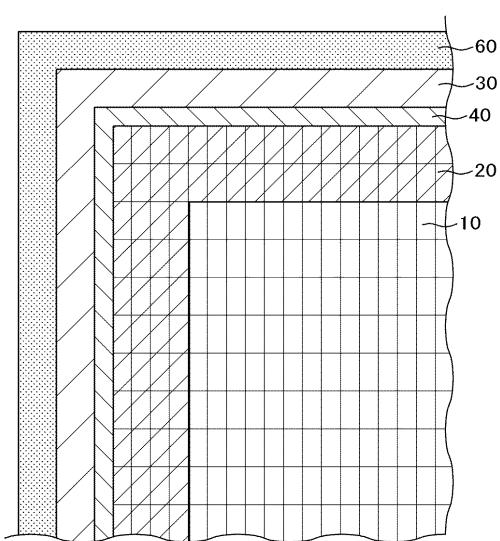

#### 【0043】

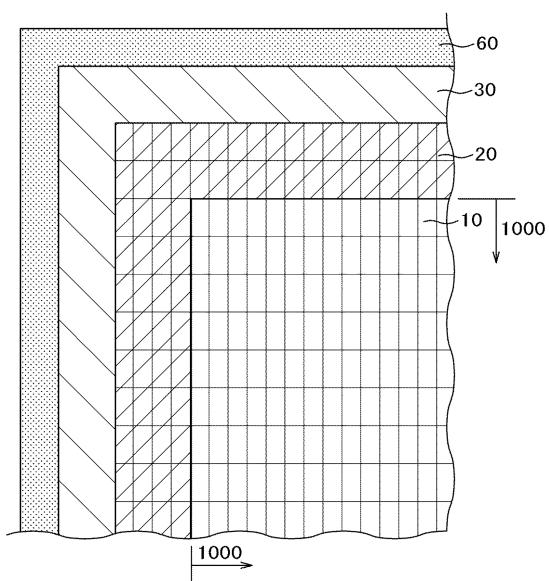

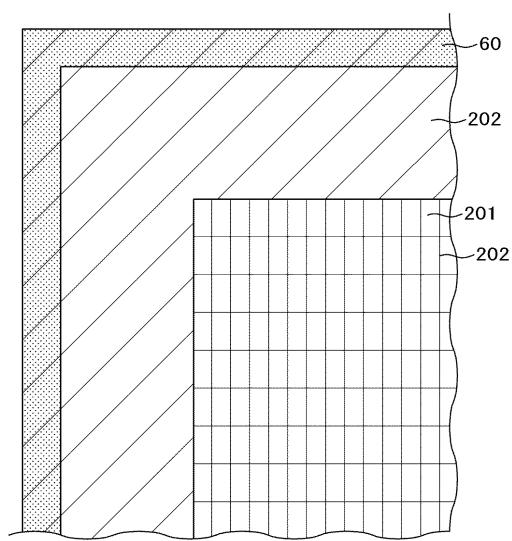

図4は、図1の領域BにおけるTFT基板100の平面図である。図4において多数の画素10が形成された表示領域1000の周辺にダミー画素20が形成されている。ダミー画素20の周辺には、周辺配線30、場合によっては駆動回路が形成されている。周辺配線30等の外側にはTFT基板100と対向基板200を接着するためのシール材60が形成されている。

#### 【0044】

図5は、図1のB領域における対向基板200の平面図である。図5において、TFT基板100の画素10が形成されている部分に対応してカラーフィルタ201が形成されている。カラーフィルタ201とカラーフィルタ201の間にはブラックマトリクス202が形成されているが、図5では単に線で表している。カラーフィルタ201が形成された表示領域1000の周辺にはブラックマトリクス202が形成され、表示領域1000以外を遮光している。対向基板200の周辺には、対向基板200とTFT基板100を接着するためのシール材60が形成されている。

30

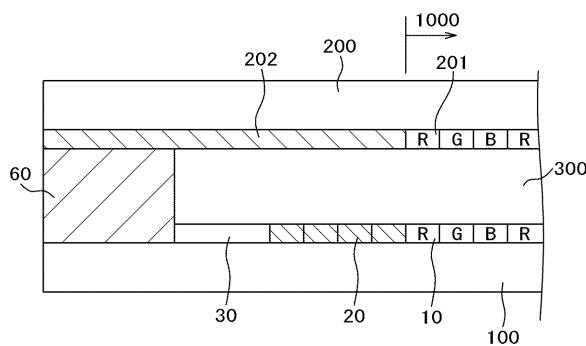

#### 【0045】

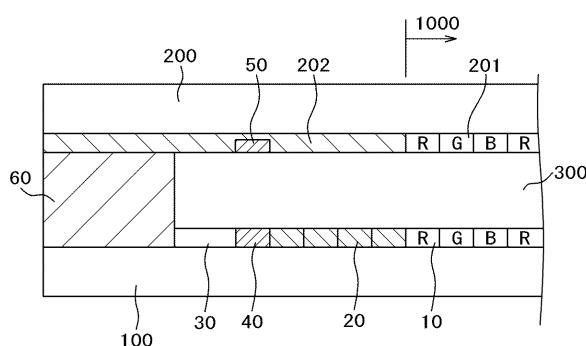

図6は本実施例における図1のA-A断面図である。図6において、TFT基板100において、画素10が形成された表示領域1000の外側にはダミー画素20が形成され、その外側には周辺配線30が形成され、その外側にはシール材60が形成されている。周辺配線30はシール材60とオーバーラップして形成される場合もある。

#### 【0046】

40

図6において、対向基板200側の表示領域1000には、TFT基板100の画素10に対応してカラーフィルタ201が形成され、表示領域1000の外側周辺には、ブラックマトリクス202が形成されている。なお、表示領域1000においてもカラーフィルタ201とカラーフィルタ201の間にはブラックマトリクス202が形成されているが、図6では、単に線で表している。対向基板200とTFT基板100の間には液晶層300が挟持されている。

#### 【0047】

本発明の特徴は、画素10における電圧印加とダミー画素20における電圧印加とを従来とは異なるものである。表示領域1000における画素10には、映像信号が印加される。一方、ダミー画素20には、従来は、コモン電圧が印加されていた。すなわち、

50

コモン電圧は画像形成には寄与しないので、ノーマリブラックでは、常に黒表示としている。

#### 【0048】

この場合、表示領域最外周の画素20とダミー画素20との間には、常に電圧が印加された状態である。そうすると、液晶内のイオンや不純物が表示領域最外の画素10とダミー画素20との間の電界に吸い寄せられて、表示領域最外の画素20にイオンや不純物が蓄積される現象が生ずる。そうすると、表示領域最外画素10において、光もれが生ずる。この現象は、特に、表示領域1000のコーナーにおいて顕著に現れるので、図16に示すようなコーナーにおける表示むら90を引き起こす。

#### 【0049】

本実施例においては、ダミー画素20に印加する電圧をコモン電圧ではなく、表示領域最外周の画素10に印加される映像信号と同じ映像信号を印加する。そうすると、表示領域最外画素10とダミー画素20との電界は生じず、表示領域最外画素10にイオンや不純物が吸い寄せられるという現象を防止することが出来る。すなわち、表示領域最外周の画素に隣接するダミー画素に印加する電圧をVdummyとし、表示領域最外画素に印加する電圧をVactiveとした場合、

$$V_{\text{dummy}} = V_{\text{active}} \dots \dots \dots (1)$$

とすることによってコーナーにおける表示むらを防止することが出来る。

#### 【0050】

表示画面の輝度は、使用環境、表示画像の種類等によって平均輝度が変化する。Vactiveとして、表示領域最外画素10と同じ信号とする代わりに、表示画像の平均輝度を予想しておき、表示画像の平均輝度を与える信号に相当する信号をダミー画素20に印加しても同様な効果を得ることが出来る。すなわち、表示領域1000のコーナーにおける表示むらを抑えることが出来る。

#### 【実施例2】

#### 【0051】

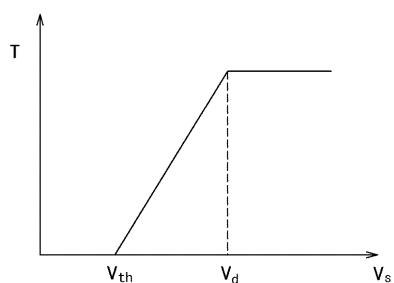

本実施例は、実施例1の構造において、ダミー画素20に印加する電圧を2段階とするものである。すなわち、液晶分子は、印加電圧がゼロの状態からリニアに回転するのではなく、図7に示すように、スレッショルド電圧Vthまでは、液晶分子は殆ど動かない。したがって、Vthまでは、液晶表示装置の透過率はほぼゼロと考えてよい。Vthを超えると、電圧にしたがって、液晶分子の回転が増し、Vdにおいて回転が飽和し、それ以上の電圧を印加しても透過率は殆ど変化しない。したがって、階調表示は、VthとVdとの間でおこなわれる。

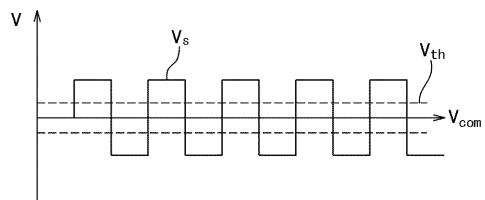

#### 【0052】

また、液晶層には、液晶の電気分解を防止するために、図8に示すように、映像信号線にはパルスの交流電圧が印加される。この交流電圧は、コモン電極に印加されるコモン電圧Vcomを基準に印加される。図8における信号電圧Vsは一定であり、Vsは、Vthよりも大きい。階調の変化は、図8におけるVsの値を変化させることによって行われる。図7において、Vthは例えば2V、Vdは例えば5Vである

本実施例の駆動方法は、次のような構成となっている。

(1) VactiveがVcom Vactive < Vthを満たす場合、

$$V_{\text{dummy}} = V_{\text{active}} \dots \dots \dots (2)$$

とする。

(2) VactiveがVth Vactiveを満たす場合、

$$V_{\text{dummy}} = V_{\text{th}} \dots \dots \dots (3)$$

とする。なお、Vdummyとは表示領域最外周の画素に隣接するダミー画素に印加される電圧をいう。

#### 【0053】

本実施例の有利な点は、ダミー画素20には、Vthよりも高い電圧が印加されないので、ダミー画素20からの光は実質的には発生せず、ダミー画素20からの光もれを防止

することができる。ここで、図7におけるV<sub>t h</sub>は2V、V<sub>d</sub>は5Vであるから、本実施例においては、表示領域最外の画素10とダミー画素20との電界の差は、最大でも3Vであり、従来の駆動方法に対して大きく低減しており、イオンあるいは不純物が表示領域最外画素に吸い寄せられる量は大幅に軽減し、画面コーナーにおける表示むらも抑えることが出来る。

#### 【実施例3】

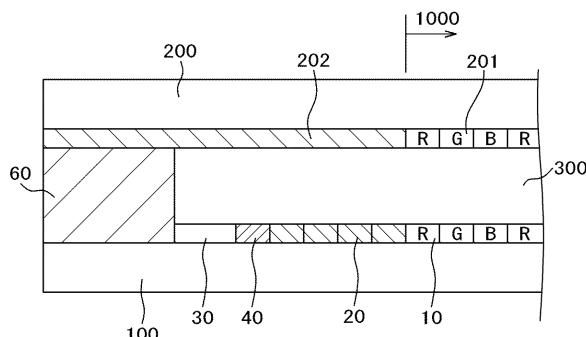

##### 【0054】

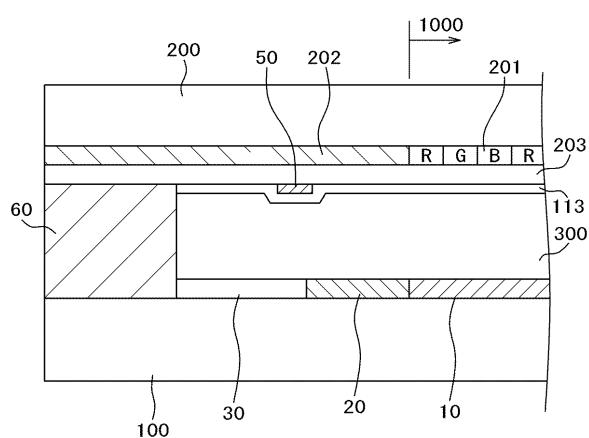

図9は、本発明の第3の実施例におけるTFT基板100側の図1の領域Bに対応する平面図である。なお、対向基板200側の平面図は実施例1の図5と同様である。図9において、多数の画素10がマトリクス状に形成された表示領域1000の外側にダミー画素20が形成されている。図9の特徴は、ダミー画素20の外側に第1周辺電極40が形成されている点である。図9における第1周辺電極40の幅はダミー画素20と同じになっているが、これに限らず、もっと幅が小さくともよい。本実施例においては、第1周辺電極40には同一の電圧V<sub>com</sub>が印加されるので、第1周辺電極40は連続した配線でよい。第1周辺電極40の外側には周辺配線30が形成されている。周辺配線30の外側にはTFT基板100と対向基板200を接着するためのシール材60が形成されている。

##### 【0055】

図10は、図1のA-A断面に相当する本実施例における断面図である。図10のTFT基板100側において、画素10が形成された表示領域1000の外側にダミー画素20が形成され、ダミー画素20の外側に第1周辺電極40が形成され、その外側に周辺配線30が形成されている。周辺配線30の外側にはTFT基板100と対向基板200を接着するシール材60が形成されている。周辺配線30はシール材60の下側にまで形成される場合もある。図10の対向基板200側は図6と同様なので説明を省略する。TFT基板100と対向基板200の間には液晶層300が挟持されている。

##### 【0056】

本実施例における表示領域1000、ダミー画素20、第1周辺電極40に対する電圧印加の方法は次のとおりである。すなわち、表示領域最外周の画素10に印加される信号電圧とダミー画素20に印加する電圧は実施例1または実施例2と同じである。本実施例の特徴は、ダミー画素20の外側に第1周辺電極40を配置し、この第1周辺電極40の電位V<sub>p1</sub>をコモン電圧V<sub>com</sub>に保つことである。

##### 【0057】

このような電圧印加方法であると、第1周辺電極40の電圧は常にダミー画素20の電圧よりも小さい状態となっている。なお、この場合の電圧とは、絶対値を言っている。そうすると、第1周辺電極40とダミー画素20との間につけた電界が存在し、イオンや不純物がこの電界の部分にトラップされる。この部分にトラップされたイオンや不純物の影響は、周辺ブラックマトリクス202によって覆われているので、外部からは視認することは出来ない。この構成によれば、イオンや不純物が表示領域1000には移動してこないので、画面コーナー部における表示むらを安定して防止することができる。

#### 【実施例4】

##### 【0058】

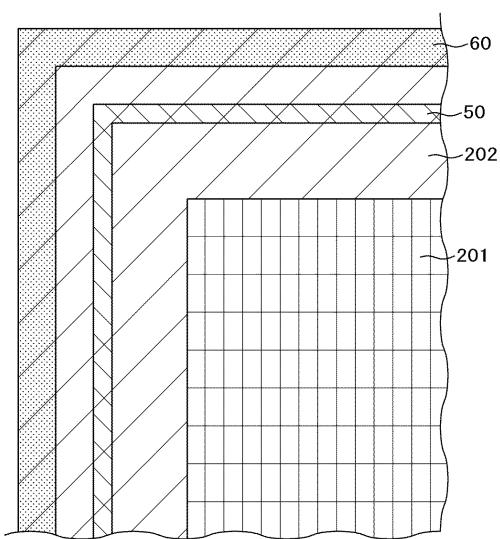

図11は実施例4における対向基板200の図1におけるB領域に対応する平面図である。図11において、カラーフィルタ201が形成されている表示領域1000の外側にブラックマトリクス202が形成されており、周辺にシール材60が形成されていることは図5と同様である。図11が図5と異なる点は、第2周辺電極50が表示領域1000の端部と距離をおいて形成されている点である。この第2周辺電極50は、TFT基板100側のダミー画素20との間の電界によってイオンや不純物をトラップするためのものである。本実施例においては、第2周辺電極50には同一のV<sub>com</sub>が印加されるので、連続した膜でよい。

##### 【0059】

10

20

30

40

50

図12は本実施例における図1のA-A断面に相当する断面図である。図12において、TFT基板100側は実施例1等における図6と同様であるので、説明を省略する。TFT基板100と対向基板200の間には液晶層300が挟持されている。図12における対向基板200側において、カラーフィルタ202が形成された表示領域1000とシール材60との間に第2周辺電極50が形成されている。

#### 【0060】

第2周辺電極50の電位 $V_{p2}$ は $V_{com}$ と同様である。一方、TFT基板100側のダミー画素20には、実施例1あるいは実施例2で説明した電圧が印加されている。この場合、ダミー画素20に印加される電圧は、第2周辺電極50に印加される電圧 $V_{com}$ よりも常に高いので、ダミー画素20と第2周辺電極50との間には常に電界が発生している。なお、この場合の電圧とは絶対値を言っている。10

#### 【0061】

そうすると、ダミー画素20と第2周辺電極50との間の電界によって、イオンや不純物が引き寄せられ、この部分でトラップされる。この部分でトラップされたイオンや不純物は周辺ブラックマトリクス202によって覆われているので、表示に影響を与えることがない。一方、表示領域1000とダミー画素20との境界は、実施例1あるいは実施例2で説明したように、イオンや不純物の蓄積は避けることができるので、画面コーナーにおける表示むらを防止することが出来る。

#### 【実施例5】

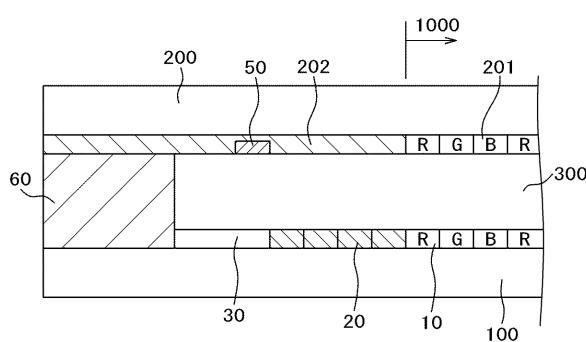

#### 【0062】

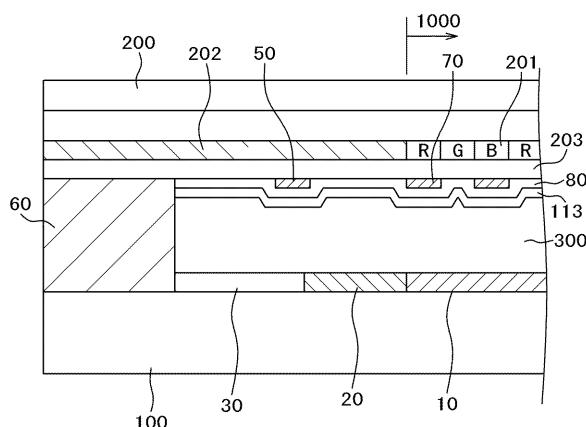

図13は実施例5における図1のA-A断面に相当する断面図である。図13のTFT基板100側の平面図は、実施例3におけるTFT基板100側の平面図である図9と同一であり、図13の対向基板200側の平面図は実施例4における平面図である図11と同様である。TFT基板100と対向基板200の間には液晶層が挟持されている。20

#### 【0063】

図13において、第1周辺電極40の電圧 $V_{p1}$ 、第2周辺電極50の電極 $V_{p2}$ のいずれもコモン電圧 $V_{com}$ と同じである。したがって、第1周辺電極はダミー画素よりも絶対値で常に低い電圧となっており、第2周辺電極50はダミー画素20よりも絶対値で常に低い電圧となっている。つまり、第1周辺電極40とダミー画素20、第2周辺電極50とダミー画素20の間には常に電界が発生しており、この部分にイオンや不純物がトラップされる。30

#### 【0064】

一方、画素10とダミー画素20との間には、実施例1あるいは実施例2で説明したような電圧が印加されているので、表示領域最外画素20にイオンあるいは不純物がトラップされるということは無い。本実施例においては、第1周辺電極40とダミー画素20の間、第2周辺電極50とダミー画素20との間の2箇所において、イオンおよび不純物をトラップするので、画面コーナー部における表示むらを安定して抑制することが出来る。

#### 【0065】

なお、図12および図13における第2周辺電極50の対向基板200における配置位置は、図14のようにすることが出来る。図14の対向基板200側の内側の表示領域1000にはカラーフィルタ201が形成され、その外側にはブラックマトリクス202が形成されている。カラーフィルタ201およびブラックマトリクス202を覆ってオーバーコート膜203が形成されている。第2周辺電極50はオーバーコート膜203の上に形成されている。オーバーコート膜203および第2周辺電極50を覆って配向膜113が形成されている。なお、図14は第2周辺電極50を形成する一例を示したものであり、この他の構成の例としては、第2周辺電極50と配向膜113との間に絶縁膜を形成してもよい。図14におけるTFT基板100側は、図6等で説明したのと同様であるので、説明を省略する。40

#### 【実施例6】

#### 【0066】

10

20

30

40

50

I P S 方式の液晶表示装置では、一般には、対向基板 2 0 0 側には電極が存在していない。これを利用して、I P S 方式では、対向基板 2 0 0 にタッチパネル用電極 7 0 を配置して、対向基板 2 0 0 をタッチパネルとして使用することが出来る。図 1 5 は、I P S 方式において、対向基板 2 0 0 をタッチパネルとして使用した場合の断面図である。図 1 5 において、T F T 基板 1 0 0 側は、図 6 等で説明したのと同様であるので、説明を省略する。T F T 基板 1 0 0 と対向基板 2 0 0 の間には液晶層 3 0 0 が挟持されている。

#### 【 0 0 6 7 】

図 1 5 の対向基板 2 0 0 側の内側の表示領域 1 0 0 0 にはカラーフィルタ 2 0 1 が形成され、その外側にはブラックマトリクス 2 0 2 が形成されている。カラーフィルタ 2 0 1 およびブラックマトリクス 2 0 2 を覆ってオーバーコート膜 2 0 3 が形成されている。オーバーコート膜 2 0 3 の上において、表示領域 1 0 0 0 には、タッチパネル用電極 7 0 が形成されている。一方、表示領域 1 0 0 0 の外側には、第 2 周辺電極 5 0 が形成されている。タッチパネル用電極 7 0 および第 2 周辺電極 5 0 を覆ってタッチパネル用絶縁膜 8 0 が形成され、その上に配向膜 1 1 3 が形成されている。

#### 【 0 0 6 8 】

図 1 5 において、第 2 周辺電極 5 0 の電位 V p 2 はコモン電位 V c o m となっている。また、T F T 基板 1 0 0 側の表示領域 1 0 0 0 の画素 1 0 とダミー画素 2 0 の間には、実施例 1 および実施例 2 で説明したような電圧が印加されている。したがって、第 2 周辺電極 5 0 とダミー画素 2 0 との間にイオンあるいは不純物がトラップされ、表示領域最外周画素 1 0 とダミー画素 2 0 との間にはイオンあるいは不純物が吸い寄せられることを抑制することが出来るので、タッチパネル付液晶表示装置においても、画面コーナー部における表示むらを防止することが出来る。

#### 【 0 0 6 9 】

図 1 5 では、タッチパネル用電極 7 0 は 1 層構成となっているが、絶縁膜を挟んで 2 層配線構造の電極構造とすることも出来る。この場合、第 2 周辺電極 5 0 は、上側すなわち、液晶層側の層に形成することが望ましい。T F T 基板 1 0 0 側のダミー画素 2 0 との間により効果的な電界を発生させることが出来るからである。

#### 【 符号の説明 】

#### 【 0 0 7 0 】

1 0 ... 画素、 2 0 ... ダミー画素、 3 0 ... 周辺配線、 4 0 ... 第 1 周辺電極、 5 0 ... 第 2 周辺電極、 6 0 ... シール材、 7 0 ... タッチパネル用電極、 8 0 ... タッチパネル用絶縁膜、 9 0 ... 表示むら、 1 0 0 ... T F T 基板、 1 0 1 ... 第 1 下地膜、 1 0 2 ... 第 2 下地膜、 1 0 3 ... 半導体層、 1 0 4 ... ゲート絶縁膜、 1 0 5 ... ゲート電極、 1 0 6 ... 層間絶縁膜、 1 0 7 ... ソース電極、 1 0 8 ... 無機パッシベーション膜、 1 0 9 ... 有機パッシベーション膜、 1 1 0 ... コモン電極、 1 1 1 ... 層間絶縁膜、 1 1 2 ... 画素電極、 1 1 3 ... 配向膜、 1 3 0 ... スルーホール、 1 5 0 ... 端子部、 2 0 0 ... 対向基板、 2 0 1 ... カラーフィルタ、 2 0 2 ... ブラックマトリクス、 2 0 3 ... オーバーコート膜、 2 1 0 ... 外部導電膜、 3 0 0 ... 液晶層、 3 0 1 ... 液晶分子、 S ... ソース部、 D ... ドレイン部、 1 1 2 2 ... スリット

10

20

30

【図1】

【図2】

【図3】

【図4】

【図5】

図5

【図6】

図6

【図7】

図7

【図8】

図8

【図9】

図9

【図10】

図10

【図11】

図11

【図12】

図12

【図13】

図13

【図14】

図14

【図15】

図15

## 【図16】

図16

---

フロントページの続き

(56)参考文献 特開2005-003802(JP,A)

特開2010-210734(JP,A)

特開2011-059374(JP,A)

米国特許出願公開第2008/0252807(US,A1)

(58)調査した分野(Int.Cl., DB名)

G 02 F 1 / 1368

G 02 F 1 / 1343