**(19) 대한민국특허청(KR)**

**(12) 특허공보(B1)**

(51) Int. Cl.<sup>5</sup>

G11C 11/40

(45) 공고일자 1990년 11월 26일

(11) 공고번호 특 1990-0008657

|            |                                                           |           |                |

|------------|-----------------------------------------------------------|-----------|----------------|

| (21) 출원번호  | 특 1985-0007625                                            | (65) 공개번호 | 특 1986-0003607 |

| (22) 출원일자  | 1985년 10월 16일                                             | (43) 공개일자 | 1986년 05월 28일  |

| (30) 우선권주장 | 229246 1984년 10월 31일 일본(JP)                               |           |                |

| (71) 출원인   | 가부시끼가이샤 도오시바 사바 쇼오이찌<br>일본국 가나가와엔 가와사끼시 사이와이구 호리가와쵸오 72반지 |           |                |

(72) 발명자

오찌이 기요후미

일본국 가나가와엔 가와사끼시 사이와이구 고무가이도오시바쵸오 1반지

가부시끼가이샤 도오시바 다마까와공장내

야스다 히로시

일본국 가나가와엔 가와사끼시 사이와이구 고무가이도오시바쵸오 1반지

가부시끼가이샤 도오시바 다마까와공장내

마스오까 후지오

일본국 가나가와엔 가와사끼시 사이와이구 고무가이도오시바쵸오 1반지

가부시끼가이샤 도오시바 다마까와공장내

(74) 대리인

김윤배

**심사관 : 연길웅 (책자공보 제2116호)**

**(54) 센스증폭회로**

**요약**

내용 없음.

**대표도**

**도1**

**명세서**

[발명의 명칭]

센스증폭회로

[도면의 간단한 설명]

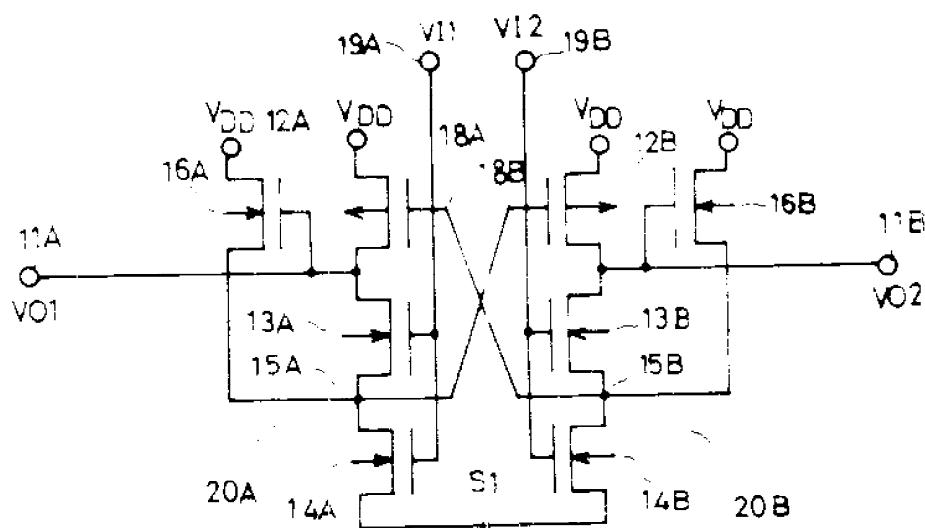

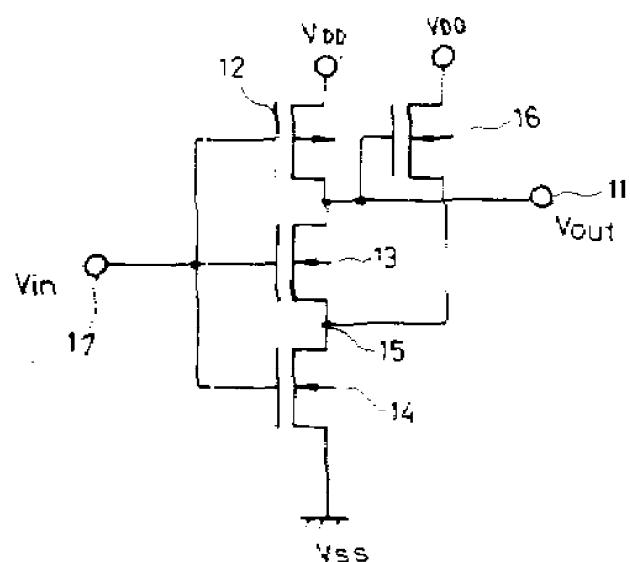

제1도는 본 발명의 1실시예에 따른 센스증폭회로의 회로도.

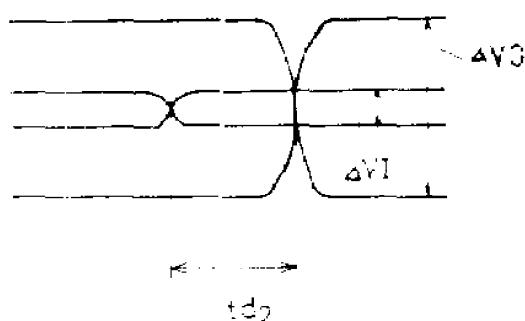

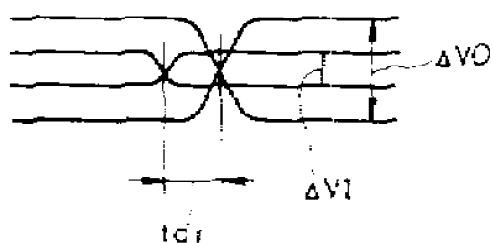

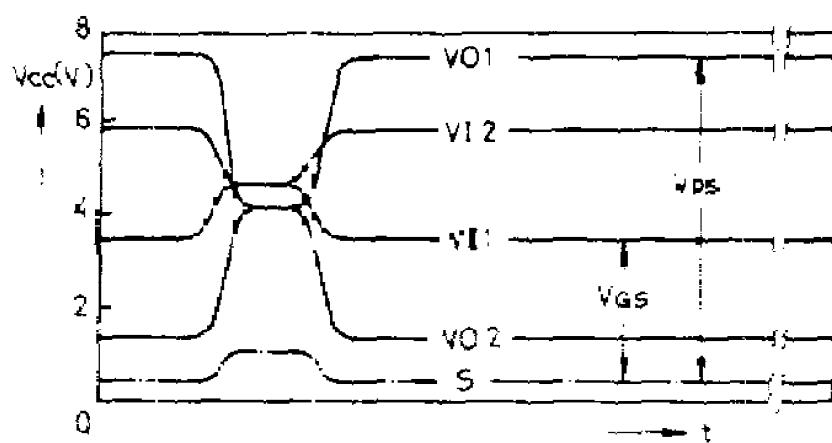

제2도는 상기 실시예의 특성을 나타낸 파형도.

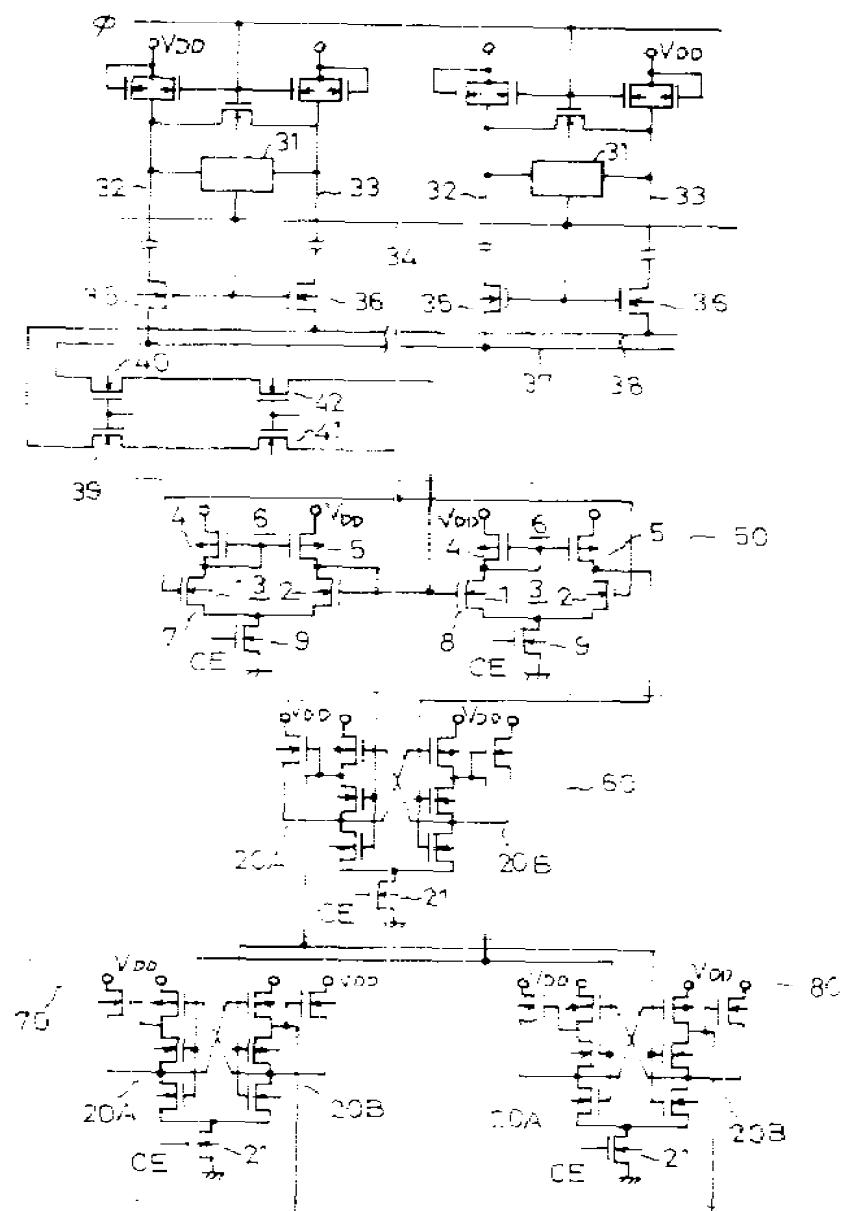

제3도는 본 발명의 다른 실시예에 따른 센스증폭회로의 회로도.

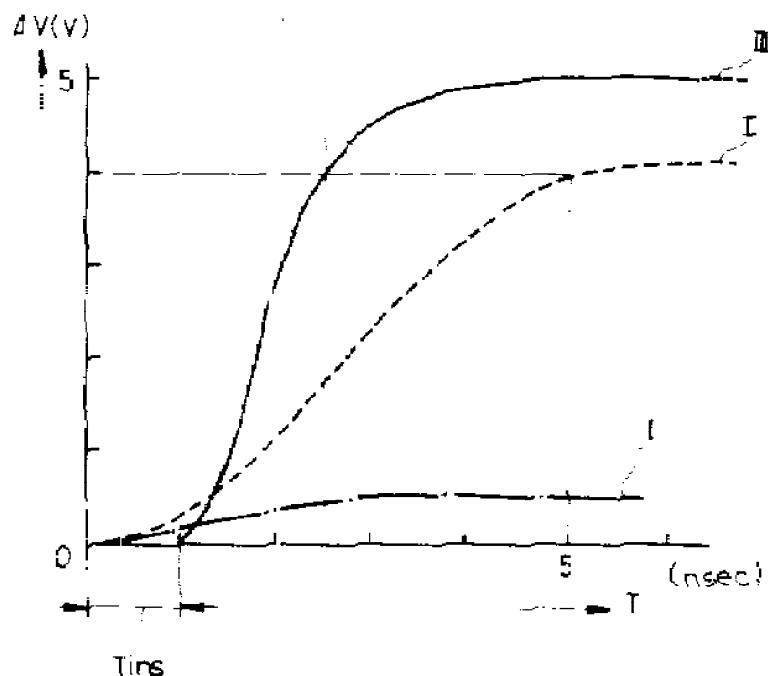

제4도는 제3도에 나타낸 실시예회로 및 종래 회로에 대한 각각의 출력특성을 타낸 특성도.

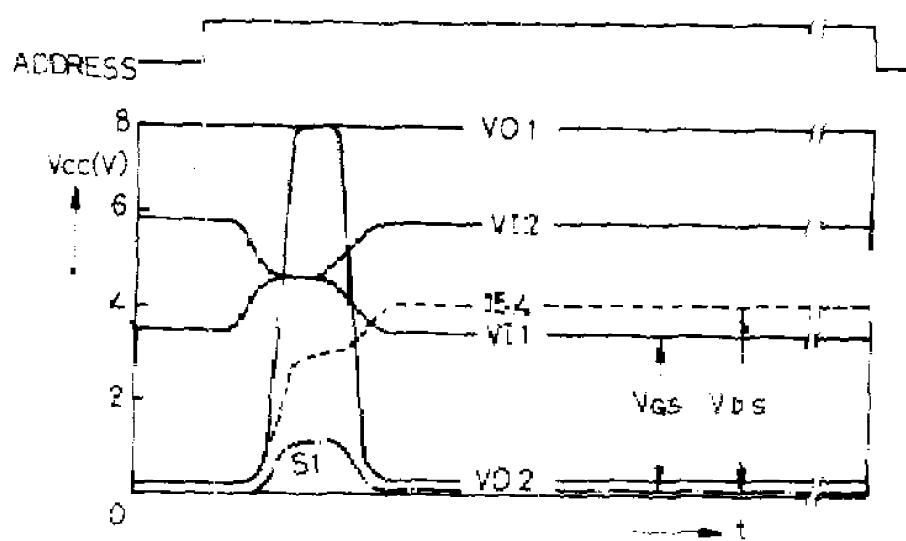

제5도는 제1도에 나타낸 실시예회로의 변형례를 나타낸 파형도.

제6도는 종래의 센스증폭회로의 회로도.

제7도는 종래 회로의 특성을 나타낸 파형도.

제8도는 본 발명의 원리를 설명하기 위해 사용된 슈미트트리거회로의 회로도.

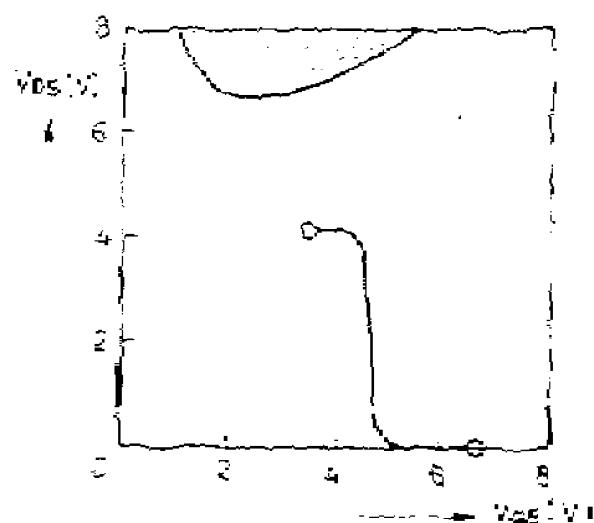

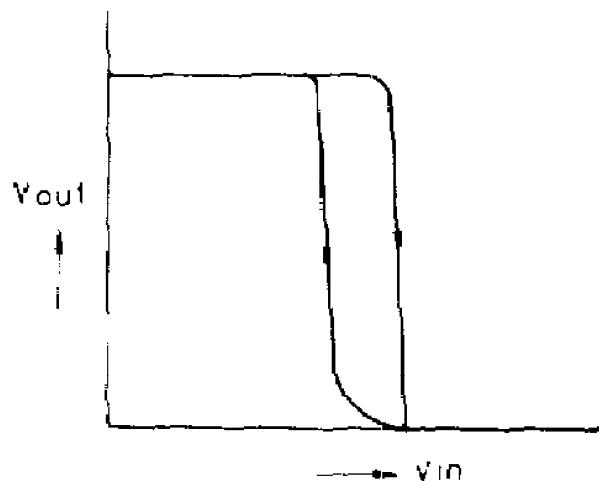

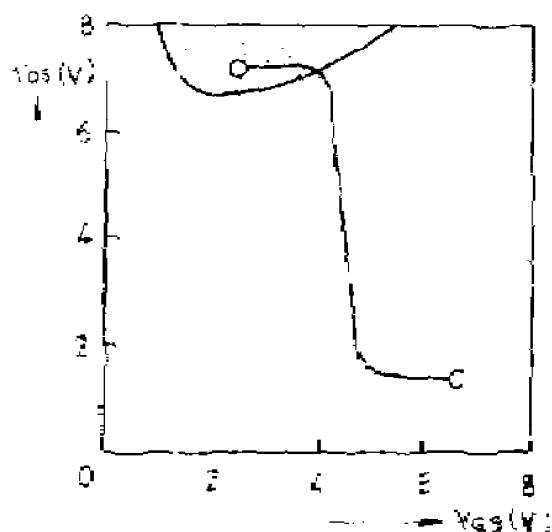

제9도는 상기 슈미트트리거회로의 입력특성도.

제10도 내지 제13도는 본 발명의 효과를 나타낸 도면.

\* 도면의 주요부분에 대한 부호의 설명

1, 2, 13, 14, 16, 13A, 14A, 13B, 14B, 21 : N채널 MOS트랜지스터

3 : 차동증폭회로

4, 5, 12, 12A, 12B : P채널 MOS트랜지스터

6 : 전류미러회로

7, 8, 50 : 미러부하형 차동증폭기

11 : 출력단자

15 : 트랜지스터의 직렬접속점

17 : 입력단자

20A, 20B : 제1, 제2슈미트트리거회로

18A, 18B : MOS트랜지스터의 게이트

19A, 19B : 제1입력단자

31 : 메모리셀

32, 33 : 비트선

34 : 워드선

35, 36, 39~41 : 스위치용 N채널 MOS트랜지스터

37, 38 : 열출력선

60, 70, 80 : 센스증폭회로

[발명의 상세한 설명]

[산업상의 이용분야]

본 발명은 MOS형 반도체기억장치에 사용되는 센스증폭회로에 관한 것이다.

[종래의 기술 및 그 문제점]

MOS형 반도체기억장치(이하, MOS메모리라 칭함)에 있어서, 1쌍의 비트선상으로 독출되는 미소전위차를 고속으로 증폭하는 센스증폭회로로서 차동증폭회로가 좋다고 알려져 있다.

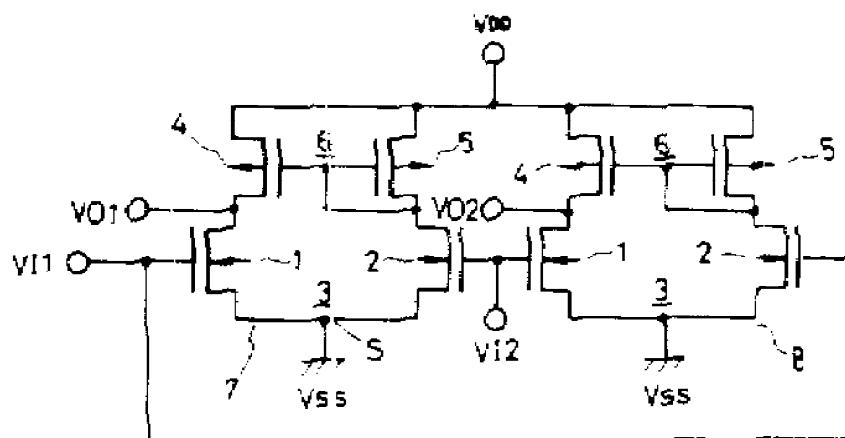

제6도는 이와 같은 종래의 센스증폭회로로서 사용되는 미러부하형 차동증폭회로의 구성을 도시해 놓은 회로인 바, 이 센스증폭회로는 1쌍의 N채널 MOS트랜지스터(1), (2)로 구성되는 차동증폭회로쌍(3)과 1쌍의 P채널 MOS트랜지스터(4), (5)로 구성되면서 상기 차동증폭회로쌍(3)의 부하로 되는 전류미러회로(6)를 각각 구비하고 있는 2개의 미러부하형 차동증폭기(7), (8)등으로 구성되고, 한쪽 미러부하형 차동증폭기(7)의 차동증폭회로쌍(3)에는 제1 및 제2입력전위( $VI_1$ ), ( $VI_2$ )를 공급하면서 다른쪽 미러부하형 차동증폭기(8)의 차동증폭회로쌍(3)에는 상기 입력전위( $VI_1$ ), ( $VI_2$ )를 역으로 공급함으로써, 각각의 미러부하형 차동증폭기(7), (8)로부터 전위차가 확대된 출력전위( $V0_1$ ), ( $V0_2$ )를 얻을 수 있도록 된다.

이상과 같은 미러부하형 차동증폭회로에서는 제7도의 파형도에 도시되어 있는 바와 같이, 메모리셀(도시되지 않았음)에서 데이터가 독출되면, 그에 따라 입력전위차( $\Delta VI$ )가 발생된 후부터 출력전위차( $\Delta V0$ )가 발생되기까지의 시간( $td_1$ )은 충분히 짧아지게 되는 바, 즉 미러부하형 차동증폭회로에서의 전위차증폭속도가 충분히 빨라지게 되도록 되어 있는 것이다.

따라서, 상기한 바와 같이 미러부하형 차동증폭회로에서는 증폭률이 작아지기 때문에 출력증폭이 충분히 확대되지 않게 되어 출력전위차( $\Delta V0$ )의 절대값이 작아지게 되도록 되어 있다. 이 때문에 적정한 증폭률을 얻으면서 출력진폭을 충분하게 하기 위해서 종래에는 미러부하형 차동증폭회로를 단단으로 접속시켜 센스증폭회로를 구성시켰다.

그러나, 이와 같이 하면 증폭률은 충분하게 확득되지만, 이번에는 출력의 지연시간이 누적되어 버려 속도가 느리게 되어 버린다는 문제점이 발생되게 된다.

[발명의 목적]

본 발명은 상기한 점을 감안하여 발명된 것으로, 미소한 전위차를 고속으로 증폭할 수 있을 뿐만 아니라 출력신호의 전위차도 충분하게 확대할 수 있도록 된 센스증폭회로를 제공함에 그 목적이 있다.

[발명의 구성]

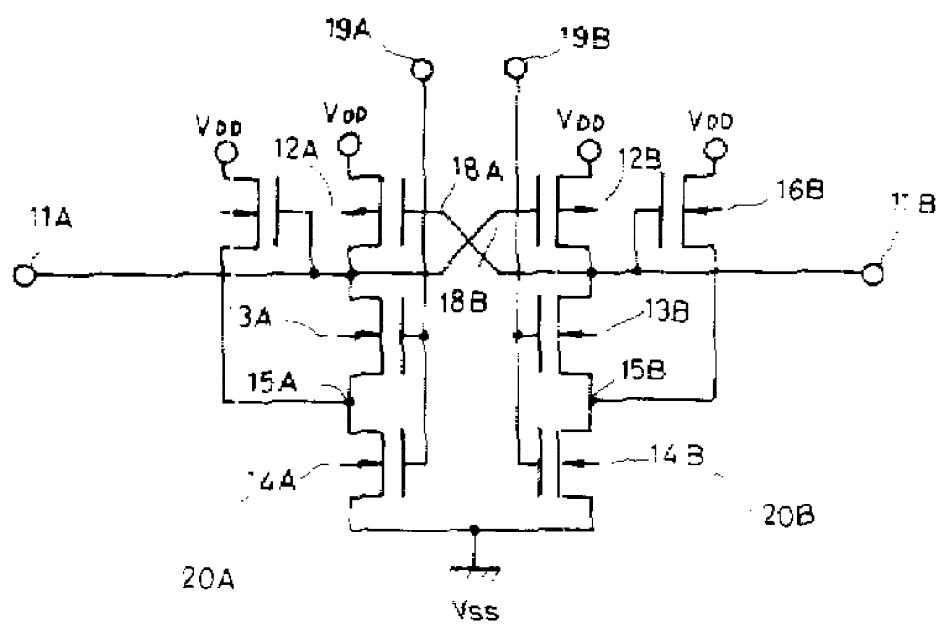

상기 목적을 달성하기 위한 본 발명은, 1쌍의 입력신호를 공급받아 증폭출력하는 센스증폭회로에 있어서, 제1전원전위( $V_{DD}$ )인가점과 출력단자(11A), (11B)사이에 소오스·드레인사이가 삽입된 P채널 MOS트랜지스터(12A), (12B)와, 상기 출력단자(11A), (11B)와 제2전원전위( $V_{SS}$ )인가점사이에 소오스·드레인사이에 직렬로 삽입되면서 게이트가 공통으로 접속되어 상기 공통게이트가 제1입력단자(19A), (19B)로 된 N채널 MOS트랜지스터(13A), (14A), (13B), (14B), 상기 제1전원전위( $V_{DD}$ )인가점과 상기 N채널 MOS트랜지스터(13A), (14A), (13B), (14B)의 직렬접속점(15A), (15B)사이에 소오스·드레인사이가 접속되면서 게이트가 상기 출력단자(11A), (11B)에 접속된 N채널 MOS트랜지스터(16A), (16B)로 각각 이루어진 제1 및 제2슈미트트리거회로(20A), (20B)와, 상기 제1슈미트트리거회로(20A)의 제1입력단자(19A)에다 제1입력전위( $VI_1$ )를 입력하는 제1수단, 상기 제2슈미트트리거회로(20B)의 제1입력단자(11B)에다 제2입력전위( $VI_2$ )를 입력하는 제2수단, 상기 제1슈미트트리거회로(20A)의 P채널 MOS트랜지스터(12A)의 게이트(18A)에다 상기 제2슈미트트리거회로(20B)내의 N채널 MOS트랜지스터(13B), (14B)의 직렬접속점(15B) 전위 또는 제2슈미트트리거회로(20B)의 출력단자(11B) 전위를 입력하는 제

3수단 및, 상기 제2슈미트트리거회로(20B)의 P챈널 MOS트랜지스터(12B)의 게이트(18B)에다 상기 제1슈미트트리거회로(20A)내의 N챈널 MOS트랜지스터(13A), (14A)의 직렬접속점(15A) 전위 또는 제1슈미트트리거회로(20A)의 출력단자(11A)전위를 입력하는 제4수단을 구비하여 구성된 것을 특징으로 한다.

#### [실시예]

이하, 예시도면을 참조해서 본 발명에 따른 1실시예를 상세히 설명한다.

먼저, 본 발명의 센스증폭회로를 설명하기 전에 본 발명에 원리에 대해 설명한다.

제8도는 종래부터 잘 알려진 CMOS트랜지스터(상보형 MOS트랜지스터) 구성인 슈미트트리거회로의 회로도로서, 슈미트트리거회로는 정극성의 전원전위( $V_{DD}$ )인가점과 출력단자(11)사이에다 P챈널 MOS트랜지스터(12)의 소오스·드레인사이를 삽입하고, 상기 출력단자(11)와 기준전위( $V_{SS}$ ; 접지전위)인가점 사이에다 2개의 N챈널 MOS트랜지스터(13), (14)의 소오스·드레인사이를 직렬로 삽입하며, 또 전원전위( $V_{DD}$ )인가점과 상기 트랜지스터(13), (14)의 직렬접속점(15)사이에다 N챈널 MOS트랜지스터(16)의 소오스·드레인사이를 삽입하고, 다음으로 상기 트랜지스터(12), (13), (14)의 게이트를 공통으로 접속해서 상기 게이트 공통접속점에다 입력단자(17)를 설치하여 된 것이다.

상기와 같이 구성된 슈미트트리거회로의 입출력특성은 제9도에 나타낸 바와 같다. 즉 지금 입력전위( $V_{in}$ )가 접지전위측의 저전위로 되어 있는 경우 P챈널 MOS트랜지스터(12)는 온상태로 되고, N챈널 MOS트랜지스터(13), (14)는 각각 오프상태로 되므로 출력전위( $V_{out}$ )가 전원전위( $V_{DD}$ )측의 고전위로 된다. 이때 이미 1개의 N챈널 MOS트랜지스터(16)는 상기 출력전위( $V_{out}$ )에 의해서 온상태로 되어 있으므로, 트랜지스터(13), (14)의 직렬접속점(15)전위는 상기 트랜지스터(16)를 통해 전원전위( $V_{DD}$ )에 가까운 고전위로 된다.

이어서 상기 상태로부터 입력전위( $V_{in}$ )가 전원전위( $V_{DD}$ )쪽으로 순차적으로 높아져 가게 된다. 즉, 입력전위( $V_{in}$ )가 높아지게 됨으로써 N챈널 MOS트랜지스터(13), (14)는 오프상태에서 온상태로 변화하여 임계전압의 주변값으로 되면, 출력단자(11)의 신호전위인 출력전위( $V_{out}$ )는 저전위로 되게 된다. 그런데, 출력전위( $V_{out}$ )는 N챈널 MOS트랜지스터(16)가 온상태로 되는 것으로 충분히 높은 전위로 되고, 상기 트랜지스터(16)를 통한 상기 직렬접속점(15)은 고전위로 된다. 이 때문에 출력전위( $V_{out}$ )가 저전위로 되려고 하는 동작은 트랜지스터(16)에 의해서 저해되게 된다. 다음으로 입력전위( $V_{in}$ )가 높게 되고 N챈널 MOS트랜지스터 임계전압에 도달하게 되면, N챈널 MOS트랜지스터(13), (14) 각각의 소오스·드레인사이의 임피던스가 충분하게 낮은 값으로 되므로 출력전압( $V_{out}$ )은 단숨에 저전압까지 저하되어 버린다.

입력전위( $V_{in}$ )가 전원전위( $V_{DD}$ )측의 고전위로 되는 경우 P챈널 MOS트랜지스터(12)는 오프상태로 되고, 이로부터 N챈널 MOS트랜지스터(13), (14)가 각각 온상태로 되므로 출력전위( $V_{out}$ )는 접지전위( $V_{SS}$ )측의 저전위로 된다.

이때 N챈널 MOS트랜지스터(16)는 상기 출력전위( $V_{out}$ )에 의해 오프상태로 된다.

다음으로 상기 상태로부터 입력전위( $V_{in}$ )는 접지전위( $V_{SS}$ )측으로 향하여 순차적으로 낮게 되어 있는 것으로 한다. 이때 입력전위( $V_{in}$ )가 낮게 되므로 P챈널 MOS트랜지스터(12)는 오프상태에서 온상태로 변화하여 임계전압의 주변값으로 되면, 출력전위( $V_{out}$ )는 통상적으로 CMOS인버터와 마찬가지의 경사로서 고전위로 향해서 높아지게 된다. 그래서 다음으로 입력전위( $V_{in}$ )가 낮아지게 되면, N챈널 MOS트랜지스터(13), (14)가 오프상태로 되므로 출력전위( $V_{out}$ )는 다시 한번 높은 전위로 된다. 그러면, 상기 출력전위( $V_{out}$ )에 의해 트랜지스터(16)가 온상태로 되고, 트랜지스터(13), (14)의 이후 출력전위( $V_{out}$ )는 전원전위( $V_{DD}$ )로 향해 단숨에 높아지게 된다.

상기한 바와 같이 슈미트트리거회로는 출력특성에 히스테리시스가 존재하게 되는데, 트랜지스터(16)작용에 의해 출력전위( $V_{out}$ )로서 CMOS인버터등 보다도 급격한 과도현상(transient)을 갖는 특성을 얻을 수가 있다.

본 발명에 따른 센스증폭회로에서는 상기 슈미트트리거회로가 갖는 급격한 과도현상의 특성을 입력전위차의 검출에 이용함으로써 의해 동작의 고속화를 도모하도록 된 것으로 제1도에 상기 실시예에 따른 회로구성이 도시되어 있다.

본 발명의 실시예 회로에서는 각각 상기 제8도의 경우와 거의 마찬가지 구성으로 되어 있는 제1 및 제2 슈미트트리거회로(20A), (20B)가 설치되어 있고, 상기 제8도의 회로와 대응하는 부분에는 그 부호끝에다 예컨대 제1슈미트트리거회로(20A)에서는 알파벳 A를, 제2슈미트트리거회로(20B)에서는 알파벳 B를 각각 붙여서 설명하고 있다.

실시예회로에서의 제1 및 제2슈미트트리거회로(20A), (20B)가 상기 제8도의 경우와 다르게 되어 있는 부분은 제8도와 같이 P챈널 MOS트랜지스터(12) 및 2개의 N챈널 MOS트랜지스터(13), (14)의 게이트를 공통으로 접속하여 입력단자로 하는 것이 아니고, P챈널 MOS트랜지스터(12A), (12B) 각각의 게이트를 18A와 18B로 하며, 2개의 N챈널 MOS트랜지스터(13A), (14A)의 각 게이트 및 트랜지스터(13B), (14B)의 각 게이트를 각각 공통으로 접속하여 제1입력단자(19A), (19B)로 한다. 그리고 제1 슈미트트리거회로(20A)에 있는 P챈널 MOS트랜지스터의 게이트(18A)는 제2슈미트트리거회로(20B)에 있는 트랜지스터(13B), (14B)의 직렬접속점(15B)에 접속하고, 이와 달리 제2슈미트트리거회로(20B)에 있는 P챈널 MOS트랜지스터의 게이트(18B)는 제1슈미트트리거회로(20A)에 있는 트랜지스터(13A), (14A)의 직렬접속점(15A)에 접속하며, 제1 및 제2슈미트트리거회로(20A), (20B)의 제1입력단자(19A), (19B)에는 제1 및 제2입력전위( $V_{I1}$ ,  $V_{I2}$ )를 각각 입력하도록 되어 있다. 여기서 제1 및 제2 슈미트트리거회로(20A), (20B)에 있는 트랜지스터(13), (14)의 직렬접속점(15)전위는 출력단자(11)

의 전위와 동일방향으로 변화한 것이고, 상기 센스증폭회로는 제1 및 제2슈미트트리거회로(20A), (20B)에 있는 P챈널 MOS트랜지스터의 게이트(18A), (18B)와 출력단자를 교차 접속하여 구성되는 랙치회로로 간주할 수 있다.

상기와 같이 구성된 센스증폭회로의 각 제1입력단자(19A), (19B)에는 제1 및 제2입력전위( $VI_1$ ), ( $VI_2$ )로서 메모리셀(도시되지 않았음)로부터 독출되는 데이터에 따른 전위가 입력된다.

여기서 제2도의 파형도에 도시한 바와 같이 상기 제1 및 제2입력전위( $VI_1$ ), ( $VI_2$ )상이의 전위차인 입력전위차( $\Delta VI$ )가 발생된 후부터 출력전위차( $\Delta VO$ )가 발생되기까지의 시간( $t_{d2}$ )은 입력전위차( $\Delta VI$ )의 값이 작은 경우에 슈미트트리거회로가 갖는 상기한 히스테리시스특성의 영향을 받게 되어 상기 미려부하형 차동 증폭회로의 경우보다도 길어지게 된다. 그러나 입력전위차( $\Delta VI$ )의 값이 단시간인 정도로 크게 되는 경우에는 히스테리시스특성의 영향을 받지 않게 되어 상기한 바와 같은 슈미트트리거회로가 갖는 급격한 과도현상의 특성에 의해 출력전위차( $\Delta VO$ )는 고속으로 확대된다. 더욱이 미려부하형 차동증폭회로와 같이 MOS트랜지스터를 온상태와 오프상태의 경계부근에서 동작시키는 것이 아니고 MOS트랜지스터를 완전하게 온상태 또는 오프상태로 해서 사용하기 때문에 출력전위차( $\Delta VO$ ), 즉 출력진폭 미려부하형 차동증폭회로의 경우보다도 충분하게 크게할 수 있게 된다. 또 MOS트랜지스터를 완전하게 온상태 또는 오프상태로 하여 사용하기 때문에, 전원전위( $V_{DD}$ )와 접지전위( $V_{SS}$ )사이에 전류가 흐르는 기간이 짧아지게 되어 미려부하형 차동증폭회로보다도 소비전력이 적어지는 효과가 발생하게 된다.

제3도는 본 발명의 다른 실시예에 따른 센스증폭회로의 구성을 나타낸 회로로서, 상기 제1도에 도시된 센스증폭회로는 지금 단독으로 사용하는 경우 고속동작을 달성시키기 위해서는 입력전위차가 어느 정도로 크지 않으면 안되는 조건이 있고, 일반적으로 메모리셀에서 출력되는 전위차가 대단히 미소하고 기껏해야 0.5V정도이다. 이 때문에 제1도에 도시한 센스증폭회로에서 직접 상기와 같은 미소전위차를 증폭하는 경우 상기와 같은 고속동작을 달성시키는 것은 비교적 간단하지 않다.

상기 실시예회로에서는 메모리셀에서 출력되는 미소전위차를 증폭하는 프리센스회로로서 제6도에 나타낸 바와 같이 미려부하형 차동증폭회로를 사용하여 전위차를 어느 정도의 값까지 고속으로 증폭하고, 상기 슈미트트리거회로가 갖는 히스테리시스특성의 영향을 받지 않는 정도까지 증폭되는 전위차를 주센스회로로서의 제1도에 도시한 슈미트트리거회로를 사용하여 센스증폭회로에서 증폭함으로써 고속으로 출력진폭을 크게하도록 된 것이다. 즉, 제3도에 있어서 참조부호 31, 31…은 각각 메모리셀이고, 이들 각 메모리셀(31)에는 1쌍의 비트선(32), (33) 및 워드선(34)이 접속되어 있다. 그리고 상기 워드선(34)이 선택적으로 구동되는 것에 의해 그 메모리셀(31)에 미리 기억되어 있는 데이터가 상기 1쌍의 비트선(32), (33)으로 독출되고, 이에 의해 1쌍의 비트선(32), (33) 상호간에 전위차가 발생하게 된다. 이와같은 1쌍의 비트선(32), (33)의 양전위는 열(列)디코더의 출력에 의해 제어되는 각각 1쌍의 스위치용 N챈널 MOS트랜지스터(35), (36)를 통해 1쌍의 열출력선(37), (38)으로 출력된다. 그리고 이와 같은 1상의 열출력선(37), (38)으로 출력된 전위는 구역디코더(section decoder)의 다른 출력에 의해 제어되는 각각 1쌍의 스위치용 N챈널 MOS트랜지스터(39), (40) 및 스위치용 N챈널 MOS트랜지스터(41), (42) 각각을 직렬로 매개해서 프리센스회로로서의 미려부하형 차동증폭회로(50)에 입력된다.

상기 미려부하형 차동증폭회로(50)는 기본적으로 상기 제6도에 도시한 것과 마찬가지로 구성되어 있고, 다른 점은 차동증폭회로쌍(3)이 접지전위( $V_{SS}$ )인가점에 직접 접속되는 것이 아니고, 비선택시에 소비전력을 절감하기 위해, 예컨대 칩이네이블신호(CE)에 의해 스위치제어되는 N챈널 MOS트랜지스터(9)의 소오스·드레인사이가 차동증폭회로쌍(3)과 접지전위( $V_{SS}$ )인가점사이에 삽입되어 있는 것이다.

또 제3도의 미려부하형 차동증폭회로(50)에 있어서 제6도와 대응하는 부분에는 동일부호를 붙인다.

상기 미려부하형 차동증폭회로(50)로부터의 1상의 출력전위는 주센스회로로서 슈미트트리거회로를 사용한 센스증폭회로(60)에 입력된다. 상기 센스증폭회로(60)는 기본적으로 제1도에 도시된 것과 마찬가지로 구성되어 있고, 다른 점은 상기 미려부하형 차동증폭회로(50)와 마찬가지로 칩이네이블신호(CE)에 의해 스위치제어되는 N챈널 MOS트랜지스터(21)가 새롭게 설치되어 있다는 점이다. 도 상기 실시예의 경우에는 데이터를 복수장소로 분배해야 하는 필요로 인해 상기 센스증폭회로(60)와 마찬가지 구성의 센스증폭회로(70), (80)를 센스증폭회로(60)에 대해 직렬로 접속하여 각각가 버퍼로서 사용하고 있는 바, 이는 출력회로등에 포함되는 기생용량에 의한 스피드다운을 개선하기 위한 것이다.

제4도는 상기 제3도에 나타낸 실시예회로와 상기 제6도에 나타낸 종래회로에 대해 각각의 출력특성을 나타낸 특성도로서, 횡축에는 시간( $T$  ; nsec)이, 종축에는 출력전위차( $V$  ; volt)가 각각 플로트(plot)되어 있다. 제4도에 있어서 1점쇄선으로 표시된 곡선(I)은 입력전위차를 나타낸 것이고, 파선으로 표시된 곡선(II)은 종래회로의 출력전위차를 나타낸 것이며, 실선으로 표시된 곡선(III)은 상기 제3도의 실시예회로의 출력전위치를 나타낸 것이다.

제4도에서 알수 있는 바와 같이, 실시예회로의 특성곡선(III)에서는 0에서부터 Insec까지의 기간에서는 출력전위차가 발생하지 않는 입력불감대( $T_{ins}$ )가 발생되는데, 출력전위차( $\Delta V$ )가 4V까지 확대될 때까지의 시간은 약 2.4nsec정도로 되고, 특성곡선(II)에서 표시되는 종래회로의 경우에는 약 5nsec인 2배이상으로 된다.

본 발명은 상기 실시예에 한정되는 것은 아니고, 여러 종류로의 변형이 가능하다.

예컨대, 제1도의 실시예회로에 있어서는 제1 및 제2슈미트트리거회로(20A), (20B) 각각에 있는 P챈널 MOS트랜지스터의 게이트(18A), (18B)를 제1 및 제2슈미트트리거회로(20A), (20B) 각각에 있는 트랜지스터(13), (14)의 직렬접속점(15)에 접속하는 경우에 대해 설명했지만, 이것은 제5도의 변형예회로에 나타낸 바와 같이 다른 슈미트트리거회로 각각의 출력단자(11A), (11B)에 접속하도록 구성해

도 된다.

또, 제3도의 실시예회로에 있어서 프리센스회로로서 종래의 미러부하형 차동증폭회로(50)를 사용하는 경우에 대해 설명했지만, 이것은 슈미트트리거회로를 사용하는 센스증폭회로와 같은 히스테리시스특성 및 입력불감대를 갖지 않고 미러부하형 차동증폭회로와 동등한 정도에서 고속으로 적당한 수준의 증폭율을 갖고 있으면, 어떠한 회로를 사용해도 된다.

또한, 제10도 및 제11도는 각각 제6도 및 제1도에서 나타낸 센스증폭회로의 각부의 변형을 나타낸 도면으로, 각부에 대응하는 파형은 동일번호를 붙이고, 제10도 및 제11도에서 도면부호  $V_{DS}$  와  $V_{GS}$  는 각각 MOS트랜지스터(1)와 MOS트랜지스터(13A)의 드레인 · 소오스사이전압과 게이트 · 소오스사이전압을 나타낸다. 제10도 및 제11도에서 나타낸 바와 같이 제10도에 나타낸 종래예에서는 제12도에 나타난 바와 같이  $V_{DS}$  가 크게 늘어나 핫캐리어(hot carrier)의 스트레스(stress)가 강해지는 위험영역을 궤적대로 통과하며, 핫캐리어가 발생하여 MOS트랜지스터의 임계전압( $V_{TH}$ )을 쉬프트시키므로 신뢰성을 저하시킨다.

그러나, 제11도 및 제13도에 나타난 바와 같이, 종래 기술에 비해 본 발명에서는 센스증폭회로를 구성하는 MOS트랜지스터의 어떤 것도 핫캐리어의 스트레스가 강해지는 위험영역을 궤적대로 통과하는 것이 아니므로 MOS트랜지스터의 임계전압( $V_{TH}$ )변동과 같은 신뢰성 저하를 일으키지 않고 15nm이하의 VLSI의 센스증폭회로로서 가장 적합하게 사용될 수 있게 된다.

#### [발명의 효과]

상기한 바와 같이 본 발명에 의하면, 미소한 전위차를 고속으로 증폭할 수 있고, 출력신호의 전위차를 충분하게 확대할 수 있는 센스증폭회로를 제공할 수 있게 된다.

### (57) 청구의 범위

#### 청구항 1

1쌍의 입력신호를 공급받아 증폭 출력하는 센스증폭회로에 있어서, 제1전원전위( $V_{DD}$ )인가점과 출력단자(11A), (11B)사이에 소오스 · 드레인사이가 삽입된 P챈널 MOS트랜지스터(12A), (12B)와, 상기 출력단자(11A), (11B)와 제2전원전위( $V_{SS}$ )인가점사이에 소오스 · 드레인사이가 직렬로 삽입되면서 게이트가 공통으로 접속되어 상기 공통게이트가 제1입력단자(19A), (19B)로 된 N챈널 MOS트랜지스터(13A), (14A), (13B), (14B), 상기 제1전원전위( $V_{DD}$ )인가점과 상기 N챈널 MOS트랜지스터(13A), (14A), (13B), (14B)의 직렬접속점(15A), (15B)사이에 소오스 · 드레인사이가 접속되면서 게이트가 상기 출력단자(11A), (11B)에 접속된 N챈널 MOS트랜지스터(16A), (16B)로 각각 이루어진 제1 및 제2슈미트트리거회로(20A), (20B)와, 상기 제1슈미트트리거회로(20A)의 제1입력단자(19A)에다 제1입력전위( $VI_1$ )를 입력하는 제1수단, 상기 제2슈미트트리거회로(20B)의 제1입력단자(11B)에다 제2입력전위( $VI_2$ )를 입력하는 제2수단, 상기 제1슈미트트리거회로(20A)의 P챈널 MOS트랜지스터(12A)의 게이트(18A)에다 상기 제2슈미트트리거회로(20B)내의 N챈널 MOS트랜지스터(13B), (14B)의 직렬접속점(15B)전위 또는 제2슈미트트리거회로(20B)의 출력단자(11B)전위를 입력하는 제3수단 및, 상기 제2슈미트트리거회로(20B)의 P챈널 MOS트랜지스터(12B)의 게이트(18B)에다 상기 제1슈미트트리거회로(20A)내의 N챈널 MOS트랜지스터(13A), (14A), (13B), (14B), 상기 제1전원전위( $V_{DD}$ )인가점과 상기 N챈널 MOS트랜지스터(13A), (14A), (13B), (14B)의 직렬접속점(15A)전위 또는 제1슈미트트리거회로(20A)의 출력단자(11A)전위를 입력하는 제4수단을 구비하여 구성된 것을 특징으로 하는 센스증폭회로.

#### 청구항 2

1상의 입력신호를 공급받아 증폭 출력하는 센스증폭회로에 있어서, 히스테리시스특성 및 입력불감대를 갖지 않고서 입력전위차를 증폭하여 제1전위( $VI_1$ ) 및 제2전위( $VI_2$ )를 출력하는 제1센스회로(50)와; 제1전원전위( $V_{DD}$ )인가점과 출력단자(11A), (11B)사이에 소오스 · 드레인사이가 삽입된 P챈널 MOS트랜지스터(12A), (12B)와, 상기 출력단자(11A), (11B)와 제2전원전위( $V_{SS}$ )인가점사이에 소오스 · 드레인사이가 직렬로 삽입되면서 게이트가 공통으로 접속되어 상기 공통게이트가 제1입력단자(19A), (19B)로 된 N챈널 MOS트랜지스터(13A), (14A), (13B), (14B), 상기 제1전원전위( $V_{DD}$ )인가점과 상기 N챈널 MOS트랜지스터(13A), (14A), (13B), (14B)의 직렬접속점(15A), (15B)사이에 소오스 · 드레인사이가 접속되면서 게이트가 상기 출력단자(11A), (11B)에 접속된 N챈널 MOS트랜지스터(16A), (16B)로 각각 이루어진 제1 및 제2슈미트트리거회로(20A), (20B)와, 상기 제1슈미트트리거회로(20A)의 제1입력단자(19A)에다 상기 제1입력전위( $VI_1$ )를 입력하는 제1수단, 상기 제2슈미트트리거회로(20B)의 제1입력단자(19B)에다 제2입력전위( $VI_2$ )를 입력하는 제2수단, 상기 제1슈미트트리거회로(20A)의 P챈널 MOS트랜지스터(12A)의 게이트(18A)에다 상기 제2슈미트트리거회로(20B)내의 N챈널 MOS트랜지스터(13B), (14B)의 직렬접속점(15B)전위 또는 제2슈미트트리거회로(20B)의 출력단자(11B)전위를 입력하는 제3수단 및, 상기 제2슈미트트리거회로(20B)의 P챈널 MOS트랜지스터(12B)의 게이트(18B)에다 상기 제2슈미트트리거회로(20A)내의 N챈널 MOS트랜지스터(13A), (14A)의 직렬접속점(15A)전위 또는 제1슈미트트리거회로(20A)의 출력단자(11A)전위를 입력하는 제4수단으로 이루어진 제2센스회로(50)를 구비하여 구성된 것을 특징으로 하는 센스증폭회로.

#### 청구항 3

제2항에 있어서, 상기 제1센스회로(50)가 미러부하형 차동증폭회로로 구성된 것을 특징으로 하는 센스증폭회로.

도면

도면1

$V_{DD}$

$V_{SS}$

도면2

도면3

도면4

도면5

도면6

도면7

도면8

도면9

도면10

도면11

도면12

도면13