(19) 日本国特許庁(JP)

## (12) 公開特許公報(A)

(11) 特許出願公開番号

特開2005-250650

(P2005-250650A)

(43) 公開日 平成17年9月15日(2005.9.15)

(51) Int.Cl.<sup>7</sup>

G06F 1/10

F 1

G06F 1/04 330Z

テーマコード(参考)

5B079

審査請求 未請求 請求項の数 10 O L (全 11 頁)

(21) 出願番号

特願2004-57598 (P2004-57598)

(22) 出願日

平成16年3月2日 (2004.3.2)

(71) 出願人 302062931

NECエレクトロニクス株式会社

神奈川県川崎市中原区下沼部1753番地

(74) 代理人 100103894

弁理士 家入 健

(72) 発明者 星 幸子

神奈川県川崎市中原区下沼部1753番地

NECエレクトロニクス株式会社内

(72) 発明者 成相 恒一

神奈川県川崎市中原区下沼部1753番地

NECエレクトロニクス株式会社内

F ターム(参考) 5B079 BA12 BB01 DD08

(54) 【発明の名称】マルチレイヤシステム及びクロック制御方法

## (57) 【要約】

## 【課題】

低消費電力のマルチレイヤシステム及びマルチレイヤシステムにおけるクロック制御方法を提供すること。

## 【解決手段】

本発明にかかるマルチレイヤシステムは、クロックジェネレータ4からクロック信号が常時供給されるCPU等の第1のマスタ1によって、他の第2のマスタ1を起動する場合の処理に特徴を有する。まず、第1のマスタ1は、第2のマスタ1と対応付けられたスレーブ3を介して当該第2のマスタ1を起動する起動信号を第2のマスタ1に出力する。第2のマスタ1は、起動信号に応じて起動を開始するとともに、第2のマスタ1へのクロック信号の供給を要求するクロック要求信号をクロックジェネレータ4に対して出力する。クロックジェネレータ4は、クロック要求信号に応じて第2のマスタ1へのクロック信号を供給する。

## 【選択図】 図1

**【特許請求の範囲】****【請求項 1】**

複数のマスタと、複数のスレーブと、前記マスタと前記スレーブ間に設けられ複数のマスタからの命令の同時処理を可能にするマルチレイヤスイッチと、前記マスタ、前記スレーブ及び前記マルチレイヤスイッチに対してクロック信号を供給するクロックジェネレータを備えたマルチレイヤシステムであって、

前記複数のマスタは、前記クロックジェネレータからクロック信号が常時供給される第1のマスタと、クロック信号が必要な時に供給される第2のマスタとを有し、

前記第1のマスタによって第2のマスタを起動する場合は、前記第1のマスタは、前記第2のマスタと対応付けられたスレーブを介して当該第2のマスタを起動する起動信号を第2のマスタに出力し、

前記第2のマスタは、前記起動信号に応じて起動を開始するとともに、第2のマスタへのクロック信号の供給を要求するクロック要求信号を前記クロックジェネレータに対して出力し、

前記クロックジェネレータは、当該クロック要求信号に応じて第2のマスタへのクロック信号を供給するマルチレイヤシステム。

**【請求項 2】**

前記第2のマスタと対応付けられたスレーブは、起動レジスタを備え、

前記第1のマスタは、前記起動レジスタに対して書き込みを行い、

前記スレーブは、前記起動レジスタへの書き込みに応じて第2のマスタを起動する起動信号を第2のマスタに出力することを特徴とする請求項1記載のマルチレイヤシステム。

**【請求項 3】**

前記第2のマスタは、当該第2のマスタに動作が終了した場合に前記クロックジェネレータに対するクロック要求信号をオフ状態とし、

前記クロックジェネレータは、前記クロック要求信号のオフ状態を認識して、前記第2のマスタへのクロック信号の供給を停止することを特徴とする請求項1記載のマルチレイヤシステム。

**【請求項 4】**

前記クロックジェネレータは、前記マスタから前記スレーブに対してアクセスがあった場合に、アクセス先のスレーブへのクロック信号の供給を開始することを特徴とする請求項1記載のマルチレイヤシステム。

**【請求項 5】**

前記マルチレイヤスイッチは、前記マスタに対応したスイッチ内マスタ部と、前記スレーブに対応したスイッチ内スレーブ部とを備え、

前記クロックジェネレータは、前記マスタから前記スレーブに対してアクセスがあった場合に、アクセス先のスレーブに対応するスイッチ内スレーブ部へのクロック信号の供給を開始することを特徴とする請求項1記載のマルチレイヤシステム。

**【請求項 6】**

複数のマスタと、複数のスレーブと、前記マスタと前記スレーブ間に設けられ複数のマスタからの命令の同時処理を可能にするマルチレイヤスイッチと、クロック信号を供給するクロックジェネレータを備えたマルチレイヤシステムにおけるクロック供給方法であって、

前記複数のマスタは、前記クロックジェネレータから常時クロック信号が供給される第1のマスタと、必要な時にクロック信号が供給される第2のマスタとを有し、

前記第1のマスタによって第2のマスタを起動する場合に、前記第1のマスタが、前記第2のマスタと対応付けられたスレーブを介して当該第2のマスタを起動する起動信号を第2のマスタに出力するステップと、

前記第2のマスタが、前記起動信号に応じて起動を開始するとともに、第2のマスタへのクロック信号の供給を要求するクロック要求信号を前記クロックジェネレータに対して出力するステップと、

10

20

30

40

50

前記クロックジェネレータが、当該クロック要求信号に応じて第2のマスタへのクロック信号を供給するステップとを備えたクロック供給方法。

【請求項 7】

前記第2のマスタと対応付けられたスレーブは、起動レジスタを備え、

前記第1のマスタは、前記起動レジスタに対して書き込みを行い、

前記スレーブは、前記起動レジスタへの書き込みに応じて第2のマスタを起動する起動信号を第2のマスタに出力することを特徴とする請求項6記載のクロック供給方法。

【請求項 8】

前記第2のマスタは、当該第2のマスタに動作が終了した場合に前記クロックジェネレータに対するクロック要求信号をオフ状態とし、

前記クロックジェネレータは、前記クロック要求信号のオフ状態を認識して、前記第2のマスタへのクロック信号の供給を停止することを特徴とする請求項6記載のクロック供給方法。

【請求項 9】

前記クロックジェネレータは、前記マスタから前記スレーブに対してアクセスがあった場合に、アクセス先のスレーブへのクロック信号の供給を開始することを特徴とする請求項6記載のクロック供給方法。

【請求項 10】

前記マルチレイヤスイッチは、前記スレーブに対応したスイッチ内スレーブ部とを備え、

前記クロックジェネレータは、前記マスタから前記スレーブに対してアクセスがあった場合に、アクセス先のスレーブに対応するスイッチ内スレーブ部へのクロック信号の供給を開始することを特徴とする請求項6記載のクロック供給方法。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、複数のマスタから出される命令の同時処理を可能にするマルチレイヤスイッチを含むマルチレイヤシステム及びマルチレイヤシステムにおけるクロック制御方法に関する。

【背景技術】

【0002】

近年、携帯電話機においては、本来の電話機能のみならず、インターネット接続機能やカメラ機能も備えており、多機能化が進んでいる。また、携帯電話機においては、小型化、軽量化、低消費電力化の観点から、複数の機能を1チップ上で実現するS o C（システム オン チップ）技術が開発されている。

【0003】

他方、かかる携帯電話機では、高速に各種の処理を同時に実行する必要がある。そのため、複数のスレーブに対して同時にアクセス可能なマルチレイヤスイッチが提案されている。

【0004】

このマルチレイヤスイッチを用いると、例えば、カメラで撮影した画像データを所定のメモリ領域に書き込む処理と、メモリに格納された画像データを読み出してディスプレイに表示する処理とを同時に実行することができる。

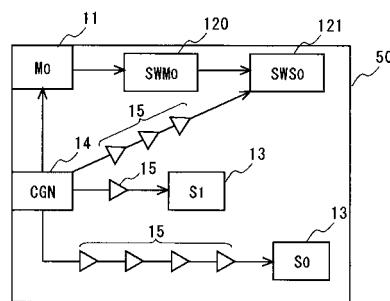

【0005】

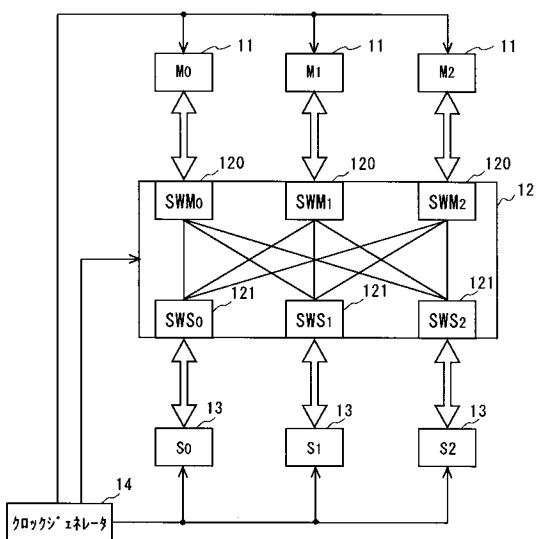

図5に、マルチレイヤスイッチを含むシステムの構成例を示す。マルチレイヤスイッチモジュール（以下、単にマルチレイヤスイッチとする）12には、複数のマスタモジュール（以下、単にマスタとする）11及びスレーブモジュール（以下、単にスレーブとする）13が接続されている。マルチレイヤスイッチ12中には、個々のマスタ11に接続されたスイッチ内マスタ部120と、個々のスレーブ13に接続されたスイッチ内スレーブ部121が設けられている。

【0006】

10

20

30

40

50

これらのマスタ11、マルチレイヤスイッチ12及びスレーブ13に対しては、クロックジェネレータ14よりクロック信号が常時供給されている。

【0007】

図6に1チップ上の各種回路のレイアウト例を示す。例えば、CPU等のマスタ11であるM0が、一角部に設けられているとする。そして、SWM0、SWS0、S0、S1等の他のモジュールは、チップ上に分散して配置されている。これらの各モジュールに対しては、クロックジェネレータ14からクロック信号が常時供給される。

【0008】

各モジュールは、クロック信号が供給され、動作することによって、当然ながら電力を消費する。また、各モジュールとクロックジェネレータ14の間の配線には、信号波形の劣化防止やタイミング制限のために駆動バッファ15が設けられる。特に各モジュールとクロックジェネレータ14までの配線長が長い場合には、図6に示されるように多数の駆動バッファ15が設けれることになる。この駆動バッファ15も各モジュールと同様にトランジスタの出力がハイからローに、またローからハイに遷移する際の貫通電流などに起因して電力を消費する。

【0009】

尚、特許文献1に示されるように、通常のバス構成において、複数のバスのうち一部のバスに対してのみ電源を供給する技術が提案されている。しかしながら、この文献に記載されたバスは、複数のマスタから出される命令の同時処理を可能にするマルチレイヤスイッチの機能を有するものではない。

【特許文献1】特開2003-141061号公報

【発明の開示】

【発明が解決しようとする課題】

【0010】

上述のように、従来のマルチレイヤシステムにおいては、マスタ、スレーブ及びマルチレイヤスイッチの全てに対してクロック信号を供給していたため、消費電力が大きくなるという問題点があった。

【0011】

本発明の目的は、かかる問題を解消し、低消費電力のマルチレイヤシステム及びマルチレイヤシステムにおけるクロック制御方法を提供することである。

【課題を解決するための手段】

【0012】

本発明にかかるマルチレイヤシステムは、複数のマスタと、複数のスレーブと、前記マスタと前記スレーブ間に設けられ複数のマスタからの命令の同時処理を可能にするマルチレイヤスイッチと、前記マスタ、前記スレーブ及び前記マルチレイヤスイッチに対してクロック信号を供給するクロックジェネレータを備えたマルチレイヤシステムであって、前記複数のマスタは、前記クロックジェネレータからクロック信号が常時供給される第1のマスタと、クロック信号が必要な時に供給される第2のマスタとを有し、前記第1のマスタによって第2のマスタを起動する場合は、前記第1のマスタは、前記第2のマスタと対応付けられたスレーブを介して当該第2のマスタを起動する起動信号を第2のマスタに出力し、前記第2のマスタは、前記起動信号に応じて起動を開始するとともに、第2のマスタへのクロック信号の供給を要求するクロック要求信号を前記クロックジェネレータに対して出力し、前記クロックジェネレータは、当該クロック要求信号に応じて第2のマスタへのクロック信号を供給するものである。

【0013】

ここで、前記第2のマスタと対応付けられたスレーブは、起動レジスタを備え、前記第1のマスタは、前記起動レジスタに対して書き込みを行い、前記スレーブは、前記起動レジスタへの書き込みに応じて第2のマスタを起動する起動信号を第2のマスタに出力することが望ましい。

【0014】

10

20

30

40

50

また、前記第2のマスタは、当該第2のマスタに動作が終了した場合に前記クロックジェネレータに対するクロック要求信号をオフ状態とし、前記クロックジェネレータは、前記クロック要求信号のオフ状態を認識して、前記第2のマスタへのクロック信号の供給を停止する。

【0015】

さらに、前記クロックジェネレータは、前記マスタから前記スレーブに対してアクセスがあった場合に、アクセス先のスレーブへのクロック信号の供給を開始することが望ましい。

【0016】

また、前記マルチレイヤスイッチは、前記マスタに対応したスイッチ内マスタ部と、前記スレーブに対応したスイッチ内スレーブ部とを備え、前記クロックジェネレータは、前記マスタから前記スレーブに対してアクセスがあった場合に、アクセス先のスレーブに対応するスイッチ内スレーブ部へのクロック信号の供給を開始するものである。

【0017】

本発明にかかるクロック供給方法は、複数のマスタと、複数のスレーブと、前記マスタと前記スレーブ間に設けられ複数のマスタからの命令の同時処理を可能にするマルチレイヤスイッチと、クロック信号を供給するクロックジェネレータを備えたマルチレイヤシステムにおけるクロック供給方法であって、前記複数のマスタは、前記クロックジェネレータから常時クロック信号が供給される第1のマスタと、必要な時にクロック信号が供給される第2のマスタとを有し、前記第1のマスタによって第2のマスタを起動する場合に、前記第1のマスタが、前記第2のマスタと対応付けられたスレーブを介して当該第2のマスタを起動する起動信号を第2のマスタに出力するステップと、前記第2のマスタが、前記起動信号に応じて起動を開始するとともに、第2のマスタへのクロック信号の供給を要求するクロック要求信号を前記クロックジェネレータに対して出力するステップと、前記クロックジェネレータが、当該クロック要求信号に応じて第2のマスタへのクロック信号を供給するステップとを備えたものである。

【0018】

ここで、前記第2のマスタと対応付けられたスレーブは、起動レジスタを備え、前記第1のマスタは、前記起動レジスタに対して書き込みを行い、前記スレーブは、前記起動レジスタへの書き込みに応じて第2のマスタを起動する起動信号を第2のマスタに出力することが望ましい。

【0019】

また、前記第2のマスタは、当該第2のマスタに動作が終了した場合に前記クロックジェネレータに対するクロック要求信号をオフ状態とし、前記クロックジェネレータは、前記クロック要求信号のオフ状態を認識して、前記第2のマスタへのクロック信号の供給を停止するとよい。

【0020】

さらに、前記クロックジェネレータは、前記マスタから前記スレーブに対してアクセスがあった場合に、アクセス先のスレーブへのクロック信号の供給を開始することが望ましい。

【0021】

また、前記マルチレイヤスイッチは、前記スレーブに対応したスイッチ内スレーブ部とを備え、前記クロックジェネレータは、前記マスタから前記スレーブに対してアクセスがあった場合に、アクセス先のスレーブに対応するスイッチ内スレーブ部へのクロック信号の供給を開始することが好ましい。

【発明の効果】

【0022】

本発明によれば、低消費電力のマルチレイヤシステム及びマルチレイヤシステムにおけるクロック制御方法を提供することができる。

【発明を実施するための最良の形態】

10

20

30

40

50

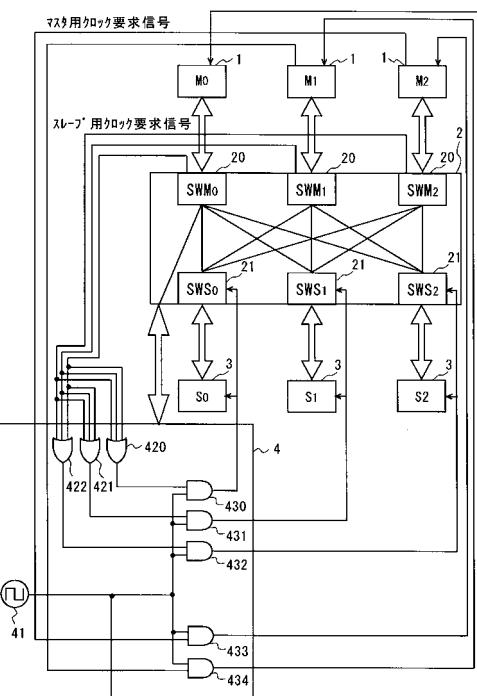

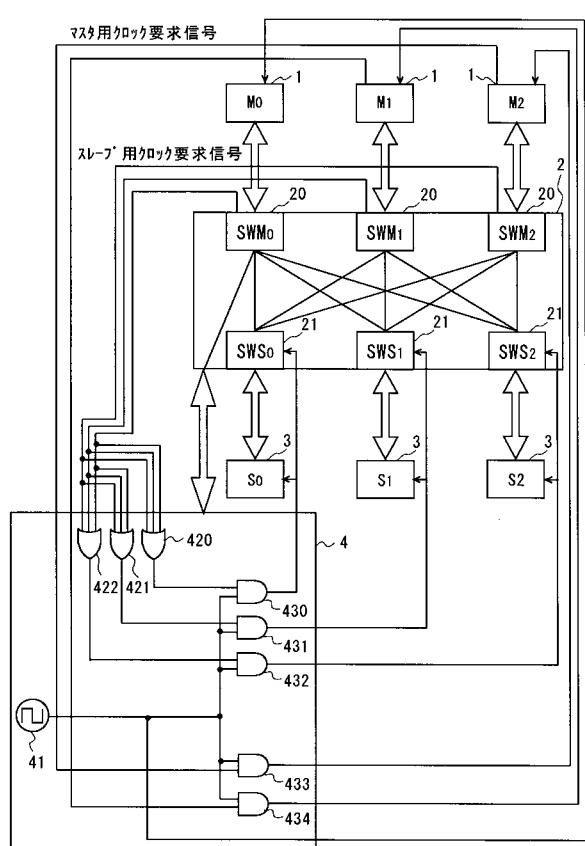

## 【0023】

図1に本発明にかかるマルチレイヤシステムの構成図を示す。当該マルチレイヤシステムは、複数のマスタ1(M0、M1、M2)と、複数のスレーブ3(S0、S1、S2)マスタ1とスレーブ3に設けられたマルチレイヤスイッチ2と、各モジュールに対してクロック信号を供給するクロックジェネレータ4を備えている。

## 【0024】

マスタ1は、システムを制御するモジュールである。例えば、CPU(Central Processor Unit)、DSP(Digital Signal Processor)、画像回転器、カメラ画像処理回路、LCD(Liquid Crystal Display)コントローラ等がある。この例におけるM0は、常時動作しているCPUである。M1、M2は、M0からの指示により必要な時だけ動作するモジュールである。

## 【0025】

マルチレイヤスイッチ2は、複数のマスタから出される命令の同時処理を可能にするものである。マルチレイヤスイッチ2は、システム内の複数のマスター・スレーブ間でパラレル・アクセス・バスの使用を可能にする相互接続バスシステムである。このバスシステムは、より複雑な相互接続マトリックスを使用することによって実現され、システム・アーキテクチャの選択肢や全体のバス帯域幅が広がるといったメリットを提供する。かかるマルチレイヤスイッチ2は、例えば、アーム株式会社よりマルチレイヤAHB(Advanced High-performance Bus)、AHB-Lite(商標)として提供されている。

## 【0026】

スレーブ3は、マスタ1からの制御対象となるモジュールである。例えば、スレーブ3には、メモリ、レジスタ、タイマ、シリアルインターフェース回路等が含まれる。この例では、S1はM1と、S2はM2とそれぞれ対となるモジュールである。例えば、M1がLCDコントローラのメイン回路部分である場合に、S1はLCDコントローラのレジスタ部分である。このレジスタ部分には、パラメータ設定レジスタや起動制御レジスタが含まれる。スレーブ3は互いに独立してクロック制御が行われる。より具体的には、スレーブ3は通常はクロック信号が供給されていない状態にあり、スレーブ3に対してマスタ1からアクセスがあった場合に、アクセス先のスレーブ3に対して初めてクロック信号が供給される。

## 【0027】

マルチレイヤスイッチ2の構成についてさらに詳細に説明する。マルチレイヤスイッチ2は、個々のマスタ1(M0、M1、M2)に接続されたスイッチ内マスター部20(SWM0、SWM1、SWM2)及び個々のスレーブ3に接続されたスイッチ内スレーブ部21(SWS0、SWS1、SWS2)を備えている。

## 【0028】

スイッチ内マスター部20は、マスタ1からのアクセスがどのスレーブ3への接続かを判別し、接続先のスレーブ3に対応するスイッチ内スレーブ部21に対してアクセス要求を出す機能を有する。さらに、当該スイッチ内マスター部20は、クロックジェネレータ4に対して、アクセス先のスレーブ3及びこのスレーブ3に対応するスイッチ内スレーブ部21にクロック信号を供給するためのクロック要求信号を発生する。

## 【0029】

スイッチ内スレーブ部21は、各スイッチ内マスター部20からのアクセス信号の調停を行い、一つのアクセスを選択して、選択したスレーブ3に対して接続することをその主要な機能とする。スイッチ内スレーブ21は互いに独立してクロック制御が行われる。より具体的には、スイッチ内スレーブ21は通常はクロック信号が供給されていない状態にあり、対応するスレーブ3に対してマスタ1からアクセスがあった場合に初めてクロック信号が供給される。

## 【0030】

図1において、クロックジェネレータ4は、各モジュールに対して供給するクロック信号を生成する。当該クロックジェネレータ4は、クロック要求信号に応じて、対応するモ

10

20

30

40

50

ジユールに対してクロック信号の供給及び供給の停止を行なう。

【0031】

クロックジェネレータ4は、クロック信号発振源41、OR回路420、421、422、AND回路430、431、432、433、434を備えている。クロック信号発振源41は、クロック源発振信号を出力する。尚、このクロック信号発振源41は、チップの外部より供給されていてもよい。OR回路420、421、422の入力は、それぞれSWM0、SWM1、SWM2の出力と接続されており、スレーブ用クロック要求信号が、SWM0、SWM1、SWM2からOR回路420、421、422に対して入力される。

【0032】

AND回路430乃至434の一方の入力は、クロック信号発振源41の出力と接続されている。そしてクロック信号発振源41からAND回路430乃至434に対してはクロック源発振信号が出力される。AND回路430の他方の入力には、OR回路420の出力が接続される。AND回路432の他方の入力には、OR回路421の出力が接続される。AND回路433の他方の入力には、OR回路422の出力が接続される。

【0033】

AND回路433の他方の入力には、M1の出力が接続される。AND回路434の他方の入力には、M2の出力が接続される。

【0034】

AND回路430の出力はSWS0及びS0に、AND回路431の出力はSWS1及びS1に、AND回路432の出力はSWS2及びS2にそれぞれ接続されている。AND回路433の出力はM2に、AND回路434の出力はM1に接続されている。また、クロック信号発振源41はM0に接続されている。

【0035】

クロック信号発振源41からは常時、クロック源発振信号がAND回路430乃至432に入力されているため、OR回路420乃至422からオン信号が入力されたAND回路430乃至432のいずれかからは、クロック信号が出力され、接続されたスイッチ内スレーブ部21やスレーブ部3に入力される。同様にM1、M2からオン信号が入力されたAND回路433、434からは、クロック信号が出力され、接続されたM1又はM2に対して入力される。

【0036】

尚、この例では、マスタ1のM0に対してはクロックジェネレータ4から常時クロック信号が供給されている。

【0037】

続いて、本発明の実施の形態にかかるマルチレイヤシステムの動作例について説明する。ここでは、マスタ1であるM0がM1に対して起動をかけ、それに応じてM1が動作を開始する場合について、図1のシステム構成図を参照しながら説明する。

【0038】

クロック信号発振源41からは、常時クロック信号が出力された状態にあり、マスタ1のM0に対して供給されている。しかしながら、クロックジェネレータ4は、スイッチ内マスタ部20からスレーブ用クロック要求信号が入力されていない、即ち、スレーブ用クロック要求信号がオフ状態にあるため、各スレーブ3及びスイッチ内スレーブ部21に対してクロック信号は供給されていない。

【0039】

M0からS1へのアクセスが発生すると、M0は、アクセス先(ここではS1)のアドレス信号や、リード/ライト信号等の制御信号を、マルチレイヤスイッチ2のスイッチ内マスタ部20であるSWM0に対して出力する。この場合の制御信号には、M1の起動信号が含まれている。

【0040】

SWM0は、M0から入力したアドレス信号に基づいて、どのスレーブ3に対してアク

10

20

30

40

50

セスするかを判別する。SWM0は、さらに、アクセス先のスレーブ3であるS1及びS1に対応するSWS1に対してクロック信号を供給することを要求するスレーブ用クロック要求信号を発生し、クロックジェネレータ4に対して出力する。さらに、SWM0は、SWS1に対してアクセス先のアドレス信号及び制御信号を出力する。

【0041】

クロックジェネレータ4は、SWM0から出力されたクロック要求信号を入力する。この例では、当該クロック要求信号は、S1及びSWS1に対するクロック信号の供給を要求するものであるから、OR回路421に対して入力される。OR回路421は、クロック要求信号の入力に応じてオン信号をAND回路431に出力する。AND回路431は、オン信号の入力に応じて、クロック信号発振源41からのクロック信号をS1及びSWS1に出力する。このようにして、S1及びSWS1に対するクロック信号の供給を開始し、S1及びSWS1は動作可能な状態となる。なお、S1、SWS1のいずれか一方には常時クロック信号を供給し、他方のみクロック制御するようにしてもよい。

【0042】

SWS1は、SWM0から入力されたアクセス先のアドレス信号及び制御信号を、アクセス先であるスレーブ3のS1に対して出力する。S1は、当該アドレス信号及び制御信号を入力して、制御信号に含まれるM1の起動信号に応じて、当該起動信号をM1に対して出力する。

【0043】

M1は、S1から起動信号を入力すると、自分自身で、クロックジェネレータ4に対してM1へのクロック信号の供給を要求するマスタ用クロック要求信号を出力する。クロックジェネレータ4は、当該マスタ用クロック要求信号を入力する。入力したクロック要求信号は、AND回路434の他方の入力をオン状態にするから、当該AND回路434の出力にクロック信号が出力され、M1に対して供給される。

【0044】

その後、M1は一連の動作の終了を認識すると、M1へのクロック信号の供給を停止するため、クロック要求信号の出力を停止する。即ち、クロック要求信号をオフ状態とする。クロックジェネレータ4では、クロック要求信号の停止に応じてAND回路434への入力信号がオン信号からオフ信号になり、クロック信号発振源41から発生信号がAND回路434から出力されなくなる。このようにして、M1へのクロック信号の供給が停止する。

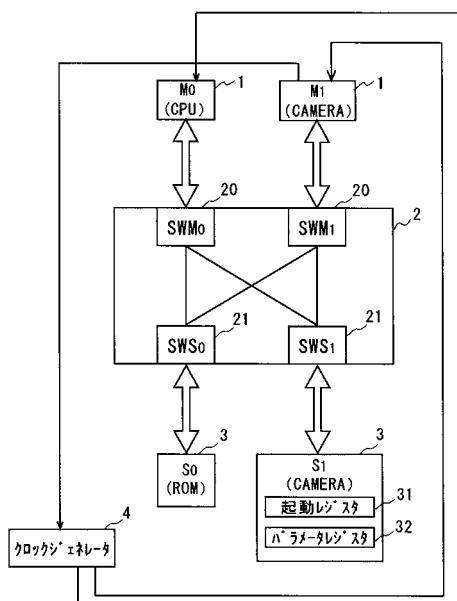

【0045】

次に本発明にかかるマルチレイヤシステムの優位性を具体例を挙げて説明する。この例では、マルチレイヤシステムをカメラ付き携帯電話に適用している。ここでは、カメラのシャッタが切られ、カメラ画像処理回路が起動するまでの動作について説明する。カメラの図2のシステム構成図を示す。この例において、M0はCPU、M1はカメラ画像処理回路である。当該カメラ画像処理回路は、図示しない画像センサよりデータを取り込み、メモリに書き込む処理を行う。S0はROMであり、S1はカメラを起動させるための起動レジスタ31及びパラメータレジスタ32を有する。

【0046】

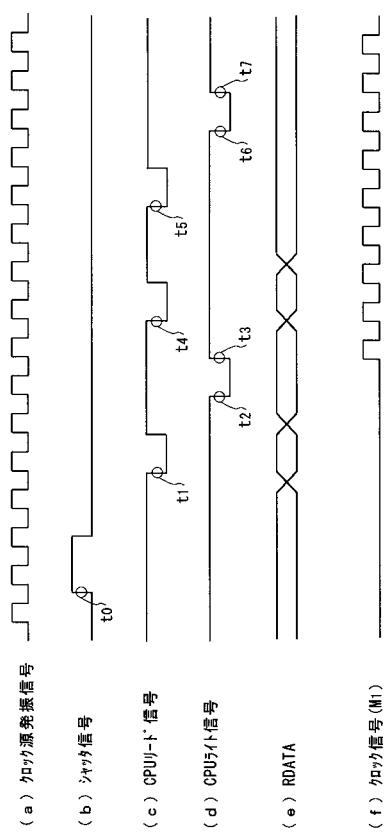

まずは、比較例としてCPUがROMから命令を読み出してカメラ画像処理回路を起動する場合の動作について図3に示すタイミングチャートを用いて説明する。クロックジェネレータ4においてクロック源発振信号は、図3(a)に示されるように常時クロック信号を出力している。このとき、CPUには、クロックジェネレータ4からクロック信号が供給されており、動作可能状態にある。

【0047】

時刻t0において、シャッタが切られ、シャッタ信号がオン状態となったものとする(図3(b)参照)。その後に任意の時刻t1において、CPUは、クロックジェネレータ4から入力されるクロック信号に同期してROMから命令を読み出す(図3(c)(e)参照)。この命令は、カメラ画像処理回路へのクロック信号の供給を要求するクロックジ

10

20

30

40

50

エネレータ4内の所定レジスタ(図示せず)への書き込みを指示するものである。CPUは、当該命令をROMから読み出して、解釈し、次のクロック信号に同期して時刻t2において、クロックジェネレータ4内に設けられたレジスタの予め定められた領域にカメラ画像処理回路へのクロック信号の供給を要求するデータを書き込む(図3(d)参照)。クロックジェネレータ4は、レジスタへの書き込みに応じて、時刻t3からカメラ画像処理回路に対してクロック信号の供給を開始する(図3(f)参照)。

#### 【0048】

次に、時刻t4において、CPUは当該クロック信号に同期してROMから命令を読み出す。この命令は、カメラ画像処理回路を起動させる起動信号である。時刻t5には他の命令を処理する場合がある。

#### 【0049】

時刻t6において、CPUはカメラ画像処理回路への起動信号に基づいて起動レジスタ31の所定領域にデータを書き込む。この書き込み動作に応じて、時刻t7よりカメラ画像処理回路は起動する。

#### 【0050】

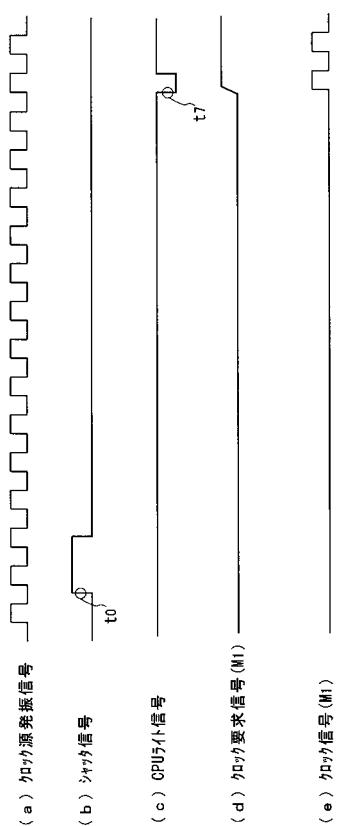

続いて、本発明の実施の形態にかかる動作を図4に示すタイミングチャートを用いて説明する。この場合には、CPUは、図4(c)に示されるように、マルチレイヤスイッチ2を介して起動レジスタ31に直接データの書き込みを行なうと、同じクロックに同期してクロックジェネレータ4に対してカメラ画像処理回路から自身に対するクロック信号の供給を要求するマスタ用クロック要求信号を出力する。クロックジェネレータ4は当該マスタ用クロック要求信号に応じて同じクロックに同期してクロック信号をカメラ画像処理回路に対して供給することができる。そして、カメラ画像処理回路は、起動レジスタ31へのデータの書き込みに応じて起動する。

#### 【0051】

このように本発明の実施の形態においては、カメラ画像処理回路へのクロック信号の供給と、当該カメラ画像処理回路の起動を同じタイミングで行なうことができるので、クロック信号の供給時間を短縮することができる。クロック信号の供給時間の短縮に伴って、回路の省電力化を図ることが可能となる。

#### 【0052】

具体的には、この例の場合には、図3に示す比較例では時刻t3からクロック信号をカメラ画像処理回路に対して供給しているのに対して、図4に示す本発明の実施の形態では、時刻t7からクロック信号を供給することにより同じタイミングでカメラ画像処理回路を起動できるため、時刻t3～t7までの間だけクロック信号の供給時間を短縮できる。

#### 【0053】

尚、上述の例では、マルチレイヤシステムを携帯電話に適用した例について説明したが、これに限らず、他の様々な機器に適用可能である。

#### 【図面の簡単な説明】

#### 【0054】

【図1】本発明によるマルチレイヤシステムの構成図である。

【図2】本発明によるマルチレイヤシステムの具体的な構成例を示す図である。

【図3】比較例のタイミングチャートである。

【図4】本発明の実施の形態のタイミングチャートである。

【図5】従来のマルチレイヤシステムの構成図である。

【図6】従来の課題を説明するための図である。

#### 【符号の説明】

#### 【0055】

1 マスタ

2 マルチレイヤスイッチ

3 スレーブ

4 クロックジェネレータ

10

20

30

40

50

2 0 スイッチ内マスタ部

2 1 スイッチ内スレーブ部

4 1 クロック信号発振源

【 四 1 】

【 図 2 】

【図3】

【図4】

【図5】

【図6】