(19) 日本国特許庁(JP)

## (12) 公表特許公報(A)

(11) 特許出願公表番号

特表2009-510568

(P2009-510568A)

(43) 公表日 平成21年3月12日(2009.3.12)

(51) Int.Cl.

G06F 13/37

(2006.01)

F 1

G 06 F 13/37

Z

テーマコード(参考)

5 B 0 6 1

審査請求 未請求 予備審査請求 未請求 (全 35 頁)

(21) 出願番号 特願2008-532551 (P2008-532551)

(86) (22) 出願日 平成18年9月29日 (2006. 9. 29)

(85) 翻訳文提出日 平成20年5月14日 (2008. 5. 14)

(86) 國際出願番号 PCT/CA2006/001607

(87) 國際公開番号 WO2007/036048

(87) 國際公開日 平成19年4月5日 (2007. 4. 5)

(31) 優先権主張番号 60/722,368

(32) 優先日 平成17年9月30日 (2005. 9. 30)

(33) 優先権主張国 米国(US)

(31) 優先権主張番号 11/324,023

(32) 優先日 平成17年12月30日 (2005. 12. 30)

(33) 優先権主張国 米国(US)

(31) 優先権主張番号 60/787,710

(32) 優先日 平成18年3月28日 (2006. 3. 28)

(33) 優先権主張国 米国(US)

(71) 出願人 508034325

モサイド・テクノロジーズ・インコーポレーテッド

カナダ・オンタリオ・K2K・2X1・カナタ・ハイインズ・ロード・11

(74) 代理人 100064908

弁理士 志賀 正武

(74) 代理人 100089037

弁理士 渡邊 隆

(74) 代理人 100108453

弁理士 村山 靖彦

(74) 代理人 100140534

弁理士 木内 敏二

最終頁に続く

(54) 【発明の名称】デイジーチェーンカスケードデバイス

## (57) 【要約】

デバイスをデイジーチェーンカスケード配列でシリアルに連結する技法である。デバイスはデイジーチェーンカスケード配列で連結されており、第1デバイスの出力部は、データ、アドレスおよびコマンド情報等の情報並びに制御信号を第2デバイスに第1デバイスから転送するのにに対応するよう、デイジーチェーンカスケードの後方にある第2デバイスの入力部に連結されている。デイジーチェーンで連結されたデバイスは、シリアル入力部SIとシリアル出力部SOとを備える。情報がデバイスにSIを通じて入力され、該情報がデバイスからSOを通じて出力される。デイジーチェーンカスケードの前方のデバイスのSOは、デイジーチェーンカスケードの後方のデバイスのSIに連結されている。前方のデバイスにSIを通じて入力された情報は、該デバイスのSOを通じて出力される。該情報は次いで、後方のデバイスのSIに転送される。

**【特許請求の範囲】****【請求項 1】**

デイジーチェーンカスケード配列で構成された複数のデバイスを有する装置であって、

第1のメモリデバイスであって、

(a) メモリと、

(b) 前記メモリ内の記憶場所に関するアドレス情報を受信するための第1の入力部と

、

(c) 前記記憶場所に含まれたデータを第1のメモリデバイスから出力するように構成された第1の出力部と、

を有する第1のメモリデバイスと、

第2のメモリデバイスであって、

(a) 前記第1のデバイスの第1の出力部に連結され、前記第1のメモリデバイスから出力されたデータを受信するように構成された第1の入力部を有する

第2のメモリデバイスと、

を備える装置。

**【請求項 2】**

前記データは、前記第1のメモリデバイスの前記第1の出力部から前記第2のメモリデバイスの前記第1の入力部にシリアルに転送される、請求項1に記載の装置。

**【請求項 3】**

前記データは、クロックサイクルの立ち上がりエッジおよび立ち下がりエッジに基づいて、2倍のデータ転送率でシリアルに転送される、請求項1に記載の装置。

**【請求項 4】**

前記第2のメモリデバイスの前記第1の入力部に転送されるデータは、デバイスアドレス情報を含む、請求項2に記載の装置。

**【請求項 5】**

前記デバイスアドレス情報は、前記第2のメモリデバイスに関する、請求項4に記載の装置。

**【請求項 6】**

前記第2のメモリデバイスの前記第1の入力部に転送されるデータは、コマンドおよびデータ情報をさらに含む、請求項4に記載の装置。

**【請求項 7】**

前記第1のメモリデバイスは、

(a) 前記第1のメモリデバイスの前記第1の入力をイネーブルにして前記アドレス情報を受信するために使用される第1の入力イネーブル信号を受信するための第2の入力部と、

(b) 第2の入力イネーブル信号を出力するための第2の出力部と、をさらに有する、

請求項1に記載の装置。

**【請求項 8】**

前記第1のメモリデバイスは、

前記データを前記第1のメモリデバイスの前記第1の出力部で出力できるようにするために使用される第1の出力イネーブル信号を受信するための第3の入力部と、

第3の出力イネーブル信号を前記第1のメモリデバイスから出力するための第3の出力部と、

を有する、請求項7に記載の装置。

**【請求項 9】**

前記第2の入力イネーブル信号は、遅延した前記第1の入力信号である、請求項7に記載の装置。

**【請求項 10】**

前記第2の入力イネーブル信号は、前記第1の入力信号から誘導される、請求項7に記載の装置。

**【請求項 11】**

10

20

30

40

50

前記第2のメモリデバイスは、前記第1のメモリデバイスの前記第2の出力部に連結された第2の入力部を有し、その第2の入力部は、前記第2の入力イネーブル信号を前記第2のメモリデバイスで受信するためのものである、請求項7に記載の装置。

【請求項 1 2】

前記第1のメモリデバイスは、

第1の出力イネーブル信号を受け取るための第2の入力部であって、その第1の出力イネーブル信号は、前記データを前記第1のメモリデバイスの前記第1の出力部で出力することを可能にするために使用されるものである、第2の入力部と、

第2の出力イネーブル信号を前記第1のメモリデバイスから出力するための第2の出力部と、

を有する、請求項1に記載の装置。

10

【請求項 1 3】

前記第2のメモリデバイスは、前記第1のメモリデバイスの前記第2の出力部に連結された第2の入力部を有し、その第2の入力部は、前記第2の出力イネーブル信号を前記第2のメモリデバイスで受信するためのものである、請求項12に記載の装置。

【請求項 1 4】

前記第1のメモリデバイスおよび第2のメモリデバイスはそれぞれ、クロック信号を受信するための第2の入力部を有し、そのクロック信号は、アクセスしたデータを前記第1のメモリデバイスの前記第1の出力部から前記第2のメモリデバイスの前記第1の入力部に転送することに対応するために、前記第1および第2のメモリデバイスによって使用されるものである、請求項1に記載の装置。

20

【請求項 1 5】

前記第1のメモリデバイスは、前記第2のメモリデバイスの前記第2の入力部に連結された第2の出力部を有し、その第2の出力部は、前記クロック信号を前記第1のメモリデバイスから前記第2のメモリデバイスに転送するためのものである、請求項14に記載の装置。

【請求項 1 6】

前記メモリはフラッシュメモリを含む、請求項1に記載の装置。

【請求項 1 7】

情報をデバイス同士の間で転送するための方法であって、

第1のメモリデバイスの第1の入力部に、前記第1のメモリデバイスに具備されたメモリの記憶場所に関連するアドレス情報を入力する段階と、

30

前記第1のメモリデバイスに具備されたメモリ内のデータに前記記憶場所でアクセスする段階と、

そのアクセスしたデータを前記第1のメモリデバイスから第2のメモリデバイスに転送することが可能となるように、前記第1のメモリデバイスの第1の出力部を前記第2のメモリデバイスの第1の入力部に連結する段階と、

を含む方法。

40

【請求項 1 8】

クロック信号を前記第1のメモリデバイスおよび前記第2のメモリデバイスに連結する段階であって、前記クロック信号は、前記アクセスしたデータを前記第1のメモリデバイスから前記第2のメモリデバイスに転送することに対応するために、前記第1のメモリデバイスおよび第2のメモリデバイスによって使用される、段階をさらに含む、請求項17に記載の方法。

【請求項 1 9】

前記クロック信号は、前記第2のメモリデバイスの第2の入力部に前記第1のメモリデバイスの第2の出力部から連結される、請求項18に記載の方法。

【請求項 2 0】

前記第1のメモリデバイスの第2の入力部に第1の入力イネーブル信号を入力する段階であって、その第1の入力イネーブル信号は、前記アドレス情報を前記第1のメモリデバイスの前記第1の入力部に入力することを可能にするために使用される、段階と、

50

第2の入力イネーブル信号を前記第1のメモリデバイスの第2の出力部から出力する段階と、

前記第2の入力イネーブル信号を前記第1のメモリデバイスから前記第2のメモリデバイスに転送できるように、前記第1のメモリデバイスの前記第2の出力部を前記第2のメモリデバイスの第2の入力部に連結する段階と、

をさらに含む、請求項17に記載の方法。

【請求項 2 1】

前記第2の入力イネーブル信号は、クロックサイクルレイテンシによって遅延した前記第1の入力イネーブル信号である、請求項20に記載の方法。

【請求項 2 2】

前記第2の入力イネーブル信号は、前記第1の入力イネーブル信号から誘導される、請求項20に記載の方法。

【請求項 2 3】

前記第1のメモリデバイスの第2の入力部に第1の出力イネーブル信号を入力する段階であって、その第1の出力イネーブル信号は、前記アクセスしたデータを前記第1のメモリデバイスから出力することを可能にするために使用される、段階と、

第2の出力イネーブル信号を前記第1のメモリデバイスの第2の出力部から出力する段階と、

前記第2の出力イネーブル信号を前記第1のメモリデバイスから前記第2のメモリデバイスに転送できるように、前記第1のメモリデバイスの前記第2の出力部を前記第2のメモリデバイスの第2の入力部に連結する段階と、

をさらに含む請求項17に記載の方法。

【請求項 2 4】

前記第2の出力イネーブル信号は、遅延した前記第1の出力信号である、請求項23に記載の装置。

【請求項 2 5】

前記第2の出力イネーブル信号は、前記第1の出力イネーブル信号から誘導される、請求項23に記載の方法。

【請求項 2 6】

前記アクセスしたデータは、前記第1のメモリデバイスの前記第1の出力部から前記第2のメモリデバイスの前記第1の入力部にシリアルに転送される、請求項17に記載の方法。

【請求項 2 7】

前記第1のメモリデバイスから前記第2のメモリデバイスに転送された前記データは、アドレス情報を含む、請求項26に記載の方法。

【請求項 2 8】

前記第1のメモリデバイスから前記第2のメモリデバイスに転送された前記データは、クロック信号の立ち上がりエッジおよび立ち下がりエッジに基づいて2倍のデータ転送率で発生する、請求項26に記載の方法。

【請求項 2 9】

情報をデバイス同士の間で転送するための装置であって、

第1のメモリデバイスの第1の入力部に、前記第1のメモリデバイスに具備されたメモリの記憶場所に関連するアドレス情報を入力するための手段と、

前記第1のメモリデバイスに具備されたメモリ内のデータに前記記憶場所でアクセスするための手段と、

アクセスした前記データが前記第1のメモリデバイスから第2のメモリデバイスに転送されるように、前記第1のメモリデバイスの第1の出力部を前記第2のメモリデバイスの第1の入力部に連結するための手段と、を備える装置。

【請求項 3 0】

クロック信号を前記第1のメモリデバイスおよび前記第2のメモリデバイスに連結するための手段であって、前記クロック信号は、アクセスした前記データを前記第1のメモリデ

10

20

30

40

50

バイスから前記第2のメモリデバイスに転送することに対応するために、前記第1のメモリデバイスおよび第2のメモリデバイスによって使用される、手段をさらに備える、請求項29に記載の装置。

【請求項31】

前記クロック信号は、前記第2のメモリデバイスの第2の入力部に前記第1のメモリデバイスの第2の出力部から連結される、請求項30に記載の装置。

【請求項32】

前記第1のメモリデバイスの第2の入力部に第1の入力イネーブル信号を入力するための手段であって、その第1の入力イネーブル信号は、前記アドレス情報を前記第1のメモリデバイスの前記第1の入力部に入力することを可能にするために使用される、手段と、

第2の入力イネーブル信号を前記第1のメモリデバイスの第2の出力部から出力するための手段と、

前記第2の入力イネーブル信号が前記第1のメモリデバイスから前記第2のメモリデバイスに転送されるように、前記第1のメモリデバイスの前記第2の出力部を前記第2のメモリデバイスの第2の入力部に連結するための手段と、をさらに備える請求項29に記載の装置。

【請求項33】

前記第1のメモリデバイスの第2の入力部に第1の出力イネーブル信号を入力するための手段であって、その第1の出力イネーブル信号は、アクセスした前記データを前記第1のメモリデバイスから出力することを可能にするために使用される、手段と、

第2の入力イネーブル信号を前記第1のメモリデバイスの第2の出力部から出力するための手段と、

前記第2の出力イネーブル信号が前記第1のメモリデバイスから前記第2のメモリデバイスに転送されるように、前記第1のメモリデバイスの前記第2の出力部を前記第2のメモリデバイスの第2の入力部に連結するための手段と、をさらに備える請求項29に記載の装置。

【請求項34】

アクセスした前記データは、前記第1のメモリデバイスの前記第1の出力部から前記第2のメモリデバイスの前記第1の入力部にシリアルに転送される、請求項29に記載の装置。

【請求項35】

前記データは、クロックサイクルの立ち上がりエッジおよび立ち下がりエッジに基づいて2倍のデータ転送率でシリアル転送される、請求項34に記載の装置。

【請求項36】

メモリと、

シリアル入力データをシリアルデータ入力ポートで受信するように、かつシリアル出力データをシリアル出力ポートに転送するように構成されたシリアルデータリンクインターフェースと、

第1の入力イネーブル信号を受信するための制御入力部であって、その第1の入力イネーブル信号は、メモリデバイスが前記シリアル入力データを処理することを可能にするために使用される、制御入力部と、

第2の入力イネーブル信号を出力するための制御出力部と、

前記第1の入力イネーブル信号に応答する制御回路であって、前記第1の入力イネーブル信号は、前記シリアルデータリンクインターフェースと前記メモリとの間のデータ転送を制御する、制御回路と、

を備える半導体メモリデバイス。

【請求項37】

前記メモリは、複数のメモリバンクを備える、請求項36に記載の半導体メモリデバイス。

【請求項38】

前記第2の入力イネーブル信号は、遅延した前記第1の入力信号である、請求項36に記載

10

20

30

40

50

の半導体メモリデバイス。

【請求項 3 9】

前記第2の入力イネーブル信号は、前記第1の入力信号から誘導される、請求項36に記載の半導体メモリデバイス。

【請求項 4 0】

前記データ転送は、クロック信号の立ち上がりエッジおよび立ち下がりエッジに基づいて2倍のデータ転送率で生じる、請求項36に記載の半導体メモリデバイス。

【請求項 4 1】

前記シリアルデータリンクインターフェースはさらに、シリアル入力データをパラレルデータに変換するように、かつそのデータを前記メモリに転送するように構成される、請求項36に記載の半導体メモリデバイス。

【請求項 4 2】

前記シリアルデータリンクインターフェースはさらに、前記メモリからのパラレルデータをシリアル出力データに変換するように構成される、請求項41に記載の半導体メモリデバイス。

【請求項 4 3】

前記制御回路は、実行命令を前記シリアル入力ポートで受信して、前記メモリとの間のシリアル入力および出力データの転送を制御するように構成される、請求項36に記載の半導体メモリデバイス。

【請求項 4 4】

固有デバイス識別番号をさらに備える、請求項43に記載の半導体メモリデバイス。

【請求項 4 5】

前記制御回路は、ターゲットデバイスアドレスがそのデバイスに関連付けられた前記固有デバイス識別番号に一致したことに応答して、前記メモリのアクセスを制御し、前記ターゲットデバイスアドレスは、前記シリアル入力データのターゲットデバイスアドレスフィールドに含められる、請求項44に記載の半導体メモリデバイス。

【請求項 4 6】

前記制御回路は、前記シリアル入力データのアドレスフィールドにおいて識別された前記メモリ内の場所に前記データを転送するのを制御する、請求項43に記載の半導体メモリデバイス。

【請求項 4 7】

前記メモリ、前記シリアルデータリンクインターフェースおよび前記制御回路は、片面パッドアーキテクチャを有する単一のパッケージ内に配置される、請求項36に記載の半導体メモリデバイス。

【請求項 4 8】

前記メモリは、不揮発性メモリバンクを備える、請求項36に記載の半導体メモリデバイス。

【請求項 4 9】

前記不揮発性メモリバンクは、フラッシュメモリバンクである、請求項48に記載の半導体メモリデバイス。

【請求項 5 0】

前記不揮発性メモリバンクは、NANDフラッシュメモリバンクである、請求項48に記載の半導体メモリデバイス。

【請求項 5 1】

第1の出力イネーブル信号を受信するための第2の制御入力部であって、その第1の入力イネーブル信号は、前記メモリデバイスがシリアル出力データを外部デバイスに送信することを可能にするために使用される、制御入力部と、

第2の出力イネーブル信号を出力するための第2の制御出力部と、

をさらに備える、請求項36に記載の半導体メモリデバイス。

【請求項 5 2】

10

20

30

40

50

半導体メモリデバイスにおけるシリアルデータリンクインターフェースとメモリバンクとの間のデータ転送を制御する方法であって、

シリアル入力データストリームをシリアルデータリンクインターフェースで受信する段階と、

第1の入力イネーブル信号を制御入力部で受信する段階と、

データをメモリバンクに格納したり、データにメモリバンクからアクセスしたりするために、シリアル入力データの処理を前記入力イネーブル信号に基づいて可能にする段階と、

第2の入力イネーブル信号を制御出力部から送信する段階と、

シリアル出力データストリームを前記シリアルデータリンクインターフェースから送信する段階と、

を含む方法。

#### 【請求項 5 3】

デバイスアドレス、コマンド、および前記メモリバンクのメモリバンクアドレスを抽出するために、前記シリアル入力データストリームを解析する段階をさらに含む、請求項52に記載の方法。

#### 【請求項 5 4】

前記コマンドは書込みコマンドであり、処理は、

前記シリアル入力データをパラレルデータに変換するステップと、

前記パラレルデータを前記メモリバンクに転送するステップと、

をさらに含む、請求項52に記載の方法。

#### 【請求項 5 5】

前記コマンドは読み取りコマンドであり、処理は、

パラレルデータを前記メモリバンクと前記シリアルデータリンクインターフェースとの間で転送するステップと、

前記パラレルデータをシリアル出力データに変換するステップと、

をさらに含む、請求項52に記載の方法。

#### 【請求項 5 6】

前記半導体メモリデバイスは、フラッシュメモリデバイスである、請求項52に記載の方法。

#### 【請求項 5 7】

前記フラッシュメモリデバイスは、NANDデバイスである、請求項56に記載の方法。

#### 【請求項 5 8】

複数のシリアル接続されたフラッシュメモリデバイスを有するフラッシュメモリシステムであって、

シリアルデータ入力ポートと、シリアルデータ出力ポートと、制御入力ポートと、制御出力ポートとを有する第1のフラッシュメモリデバイスであって、シリアル入力データおよび入力イネーブル信号を外部ソースデバイスから受信するように、かつシリアル出力データおよび第2の入力イネーブル信号を送信するように構成された第1のフラッシュメモリデバイスと、

シリアルデータ入力ポートと、シリアルデータ出力ポートと、制御入力ポートとを有する第2のフラッシュメモリデバイスであって、シリアル入力データとして前記第1のフラッシュメモリデバイスの前記シリアル出力データを、また、前記制御入力ポートで前記第1のフラッシュメモリデバイスから前記第2の入力イネーブル信号を受信するように構成された第2のフラッシュメモリデバイスと、

を備えるフラッシュメモリシステム。

#### 【請求項 5 9】

前記第2の入力イネーブル信号は、遅延した前記第1の入力信号である、請求項58に記載のフラッシュメモリシステム。

#### 【請求項 6 0】

10

20

30

40

50

前記第2の入力イネーブル信号は、前記第1の入力イネーブル信号から誘導される、請求項58に記載のフラッシュメモリシステム。

【請求項 6 1】

前記外部ソースデバイスは制御器である、請求項58に記載のフラッシュメモリシステム。

【請求項 6 2】

前記外部ソースデバイスはフラッシュメモリデバイスである、請求項58に記載のフラッシュメモリシステム。

【請求項 6 3】

前記第2のフラッシュメモリデバイスは制御出力ポートをさらに備えており、さらにまた、シリアル出力データおよび第3の入力イネーブル信号を外部ターゲットデバイスに送信するように構成されている、請求項58に記載のフラッシュメモリシステム。

10

【請求項 6 4】

前記複数のフラッシュメモリデバイスの各フラッシュメモリデバイスは、固有のデバイス識別番号を有する、請求項63に記載のフラッシュメモリシステム。

【請求項 6 5】

前記複数のフラッシュメモリデバイスの各フラッシュメモリデバイスは、シリアル入力データのターゲットデバイスアドレスフィールドを解析して、そのデバイスがターゲットデバイスであるかどうかを、ターゲットデバイスアドレスをそのデバイスの前記固有のデバイス識別番号と相關させることによって判定するように構成されている、請求項64に記載のフラッシュメモリシステム。

20

【請求項 6 6】

前記複数のフラッシュメモリデバイスの各フラッシュメモリデバイスはさらに、受信したさらなるシリアル入力データを処理する前に前記ターゲットデバイスアドレスフィールドを解析するように構成されている、請求項65に記載のフラッシュメモリシステム。

【請求項 6 7】

前記複数のフラッシュメモリデバイスの各々はさらに、そのメモリデバイスがターゲットデバイスでない場合、前記シリアル入力データを無視するように構成されている、請求項66に記載のフラッシュメモリシステム。

30

【請求項 6 8】

前記第1のフラッシュメモリデバイスはさらに、第2の制御入力ポートと第2の制御出力ポートとを備えており、出力イネーブル信号を外部ソースデバイスから受信するように、かつ第2の出力イネーブル信号を送信するように構成されており、

前記第2のフラッシュメモリデバイスはさらに、第2の制御入力ポートを備えており、前記第2の出力イネーブル信号を前記第1のフラッシュメモリデバイスから受信するように構成されている、請求項58に記載のフラッシュメモリシステム。

【請求項 6 9】

単一のクロック信号が、カスケード接続した信号において、前記複数のシリアル接続されたフラッシュメモリデバイスの各フラッシュメモリデバイスに伝えられる、請求項58に記載のフラッシュメモリシステム。

40

【請求項 7 0】

単一のクロック信号が、前記複数のシリアル接続されたフラッシュメモリデバイスの各々に伝えられ、前記フラッシュメモリシステムの出力は所定のレイテンシだけ遅延される、請求項58に記載のフラッシュメモリシステム。

【請求項 7 1】

前記複数のフラッシュメモリデバイスの各々は、

フラッシュメモリバンクと、

シリアル入力データをシリアル入力データ入力ポートで受信し、そのシリアル入力データを前記フラッシュメモリバンクに転送するように、かつシリアル出力データをシリアルデータ出力ポートに転送するように構成されたシリアルデータリンクインターフェースと、

50

前記シリアルデータリンクインターフェースと前記フラッシュメモリバンクとの間、および前記シリアルデータリンクインターフェースと前記シリアルデータ出力ポートとの間でのデータ転送を制御する制御回路と、

をさらに備える、請求項58に記載のフラッシュメモリシステム。

【請求項 7 2】

前記フラッシュメモリバンクはNANDフラッシュメモリである、請求項71に記載のフラッシュメモリシステム。

【請求項 7 3】

メモリと、

固有のデバイス識別番号と、

シリアル入力データをシリアルデータ入力ポートで受信するように構成されたシリアルデータリンクインターフェースと、

前記シリアル入力データ内のターゲットデバイスアドレスフィールドに応答する制御回路であって、そのターゲットアドレスフィールドは、前記メモリへのアクセスを制御するために、前記固有のデバイス識別番号と相關している、制御回路と、を備える半導体メモリデバイス。

【請求項 7 4】

前記メモリは複数のメモリバンクを備える、請求項73に記載の半導体メモリデバイス。

【請求項 7 5】

前記シリアルデータリンクはさらに、シリアル出力データをシリアルデータ出力ポートに転送するように構成されており、前記シリアル入力データおよびシリアル出力データはターゲットデバイスアドレス情報を含んでおり、

前記制御回路は、前記シリアルデータリンクインターフェースと前記メモリとの間、および前記シリアルデータリンクインターフェースと前記シリアルデータ出力ポートとの間でのデータ転送を制御するように構成されている、

請求項73に記載の半導体メモリデバイス。

【請求項 7 6】

前記データ転送は、クロック信号の立ち上がりエッジおよび立ち下がりエッジに基づいて2倍のデータ転送率で生じる、請求項75に記載の半導体メモリデバイス。

【請求項 7 7】

前記シリアルデータリンクインターフェースはさらに、シリアル入力データをパラレルデータに変換するように、かつそのデータを前記メモリに転送するように構成されている、請求項75に記載の半導体メモリデバイス。

【請求項 7 8】

前記シリアルデータリンクインターフェースはさらに、前記メモリからのパラレルデータをシリアル出力データに変換するように構成されている、請求項77に記載の半導体メモリデバイス。

【請求項 7 9】

前記制御回路は、実行命令を受信して、前記メモリとの間のシリアル入力および出力データの転送を制御するように構成されている、請求項78に記載の半導体メモリデバイス。

【請求項 8 0】

前記制御回路は、シリアル入力データのターゲットアドレスフィールドを解析するように、かつアドレスフィールドにおいて識別された前記メモリ内の場所に前記データを転送するのを制御するように、実行命令でプログラムされている、請求項73に記載の半導体メモリデバイス。

【請求項 8 1】

前記メモリ、前記シリアルデータリンクインターフェースおよび前記制御回路は、片面パッドアーキテクチャを有する単一のパッケージ内に配置されている、請求項73に記載の半導体メモリデバイス。

【請求項 8 2】

10

20

30

40

50

前記メモリは不揮発性メモリバンクを備える、請求項73に記載の半導体メモリデバイス。

。

【請求項 8 3】

前記不揮発性メモリバンクはフラッシュメモリバンクである、請求項82に記載の半導体メモリデバイス。

【請求項 8 4】

前記不揮発性メモリバンクはNANDフラッシュメモリバンクである、請求項82に記載の半導体メモリデバイス。

【請求項 8 5】

半導体メモリデバイスにおけるシリアルデータリンクインターフェースとメモリバンクとの間のデータ転送を制御する方法であって、

シリアル入力データストリームをシリアルデータリンクインターフェースで受信する段階であって、前記シリアル入力データストリームは、ターゲットデバイスアドレスと、コマンドと、メモリバンクアドレス情報を含んでいる、段階と、

ターゲットデバイスアドレスと、コマンドと、前記メモリバンクのメモリバンクアドレスとを抽出するために、前記シリアル入力データストリームを解析する段階と、

前記ターゲットデバイスアドレスが固有のデバイス識別子と関連している場合に、前記シリアル入力データストリームを処理する段階と、

を含む方法。

【請求項 8 6】

シリアル出力データストリームを前記シリアルデータリンクインターフェースから送信する段階をさらに含む、請求項85に記載の方法。

【請求項 8 7】

前記コマンドは書き込みコマンドであり、処理は、

前記シリアル入力データをパラレルデータに変換するステップと、

前記パラレルデータを前記メモリバンクに転送するステップと、

をさらに含む、請求項85に記載の方法。

【請求項 8 8】

前記コマンドは読み取りコマンドであり、処理は、

パラレルデータを前記メモリバンクと前記シリアルデータリンクインターフェースとの間で転送するステップと、

前記パラレルデータをシリアル出力データに変換するステップと、

をさらに含む、請求項85に記載の方法。

【請求項 8 9】

前記半導体メモリデバイスはフラッシュメモリデバイスである、請求項85に記載の方法。

。

【請求項 9 0】

前記半導体メモリデバイスはNANDデバイスである、請求項85に記載の方法。

【請求項 9 1】

複数のシリアル接続されたフラッシュメモリデバイスを有するフラッシュメモリシステムであって、

第1のメモリデバイスであって、

(a) メモリと、

(b) 固有のデバイス識別子と、

(e) シリアルデータ入力ポートと、

(d) シリアルデータ出力ポートと、

を有し、第1のメモリデバイスは、シリアル入力データを前記シリアルデータ入力ポートで外部ソースデバイスから受信するように、かつシリアル出力データを前記シリアルデータ出力ポートから送信するように構成されており、前記シリアル入力データおよびシリアル出力データはターゲットデバイスアドレス情報を含み、第1のメモリデバイスはさら

10

20

30

40

50

に、前記ターゲットデバイスアドレスが固有のデバイス識別子と相関している場合に前記シリアル入力データを処理するように構成されている、第1のメモリデバイスと、

第2のメモリデバイスであって、

(a) メモリと、

(b) 固有のデバイス識別子と、

(c) 前記第1のメモリデバイスの前記シリアルデータ出力ポートと通じたシリアルデータ入力ポートと、

(d) シリアルデータ出力ポートと、

を有し、前記第2のメモリデバイスは、前記第1のメモリデバイスのシリアル出力データを前記第2のメモリデバイスの前記シリアルデータ入力ポートで受信するように、かつ、前記ターゲットデバイスアドレスが固有のデバイス識別子と相関している場合に前記シリアル入力データを処理するように構成されている、第2のメモリデバイスと、

10 を備えるメモリシステム。

#### 【請求項 9 2】

前記外部ソースデバイスは制御器である、請求項91に記載のメモリシステム。

#### 【請求項 9 3】

前記外部ソースデバイスはメモリデバイスである、請求項91に記載のメモリシステム。

#### 【請求項 9 4】

前記第2のメモリデバイスはさらに、シリアル出力データを外部ターゲットデバイスに送信するように構成されている、請求項91に記載のメモリシステム。

#### 【請求項 9 5】

前記複数のメモリデバイスの各メモリデバイスはさらに、前記ターゲットデバイスアドレスが固有デバイス識別子と相関しない場合、前記シリアルデータを処理せずに無視するように構成されている、請求項91に記載のメモリシステム。

#### 【請求項 9 6】

前記メモリはフラッシュメモリである、請求項91に記載のメモリシステム。

#### 【請求項 9 7】

前記メモリはNANDフラッシュメモリである、請求項91に記載のメモリシステム。

#### 【発明の詳細な説明】

##### 【技術分野】

##### 【0 0 0 1】

本発明は、デイジーチェーンカスケード配列で構成された複数のデバイスを有する装置に関する。

##### 【背景技術】

##### 【0 0 0 2】

現在、コンピュータ利用システムは、ほとんど至る所で見出すことができ、携帯電話、ハンドヘルドコンピュータ、自動車、医療装置、パーソナルコンピュータなど、社会で日々使用されている多数の装置に組み込まれてきた。総じて、社会は、小切手帳の帳尻を合わせる等の単純な作業などから天気を予想するなどの比較的複雑な作業まで、日々の作業を処理するためにコンピュータ利用システムに大いに依存してきた。技術が改善されるにつれて、より多くの作業がコンピュータ利用システムへと移行される。これによって、社会は、これらのシステムにますます依存するようになっている。

##### 【0 0 0 3】

典型的なコンピュータ利用システムは、システムボードと、ディスプレイ装置、記憶装置などの任意選択による1台以上の周辺装置とを備えている。システムボードは、1台以上のプロセッサと、メモリサブシステムと、シリアルデバイスインターフェース、ネットワークデバイスコントローラ、ハードディスクコントローラなどの他の論理回路とを具備することができる。

##### 【0 0 0 4】

特定のシステムボード上で用いられるプロセッサの種類は通常、そのシステムで実施さ

10

20

30

40

50

れるタスクの種類に依存する。例えば、自動車のエンジンによって生成される廃棄物の監視、およびエンジンが燃料を完全燃焼させるようにするための混合気の調整など、限られた組みのタスクを実施するシステムは、これらのタスクを実施するのに合わせて製作された簡潔な専用プロセッサを用いていることがある。一方で、多数のユーザを管理し多数の異なるアプリケーションを実行するなど、多数の異なるタスクを実施するシステムは、ユーザの要求をサービスする応答時間を最小にすべく、高速な計算を実施しデータを操作するように構成された、事実上汎用のものである1台以上の複合プロセッサを用いていることがある。

#### 【0005】

メモリサブシステムは、プロセッサが使用する情報(例えば命令、データ値)を保持する記憶装置である。メモリサブシステムは典型的には、コントローラ制御回路と、1台以上のメモリデバイスとを備えている。コントローラ制御回路は典型的には、メモリデバイスをプロセッサとインターフェースさせ、そのメモリデバイスにまたそのメモリデバイスからプロセッサが情報を格納しまた取り出すことができるよう構成されている。メモリデバイスは実情報を保持する。

10

#### 【0006】

プロセッサと同様に、メモリサブシステムにおいて用いられる種類のデバイスは、多くの場合、コンピュータシステムによって実施される種類のタスクによって駆動される。例えば、コンピュータシステムは、ディスクドライブの支援なしに始動し、かつ頻繁には変化しない一組みのソフトウェアルーティンを実施しなければならないというタスクを有していることがある。ここで、メモリサブシステムは、フラッシュメモリデバイスなどの不揮発性デバイスを用いて、そのソフトウェアルーティンを格納してもよい。他のコンピュータシステムは、情報の大部分を保持するために大型で高速なデータストアを必要とする非常に複雑なタスクを実行することができる。ここで、メモリサブシステムは、高速で高密度なダイナミックランダムアクセスメモリ(DRAM)デバイスを用いて、情報の大部分を格納することができる。

20

#### 【0007】

現在、ハードディスクドライブは、20ギガバイトから40ギガバイトのデータを格納しうる高密度を有しているが、比較的かさ高いものとなっている。しかしながら、ソリッドステートドライブとしても知られるフラッシュメモリは、高密度であり、不揮発性であり、かつハードディスクドライブと比較して小型であることから、一般に普及している。フラッシュメモリ技術は、EPROMおよびEEPROM技術に基づいている。「フラッシュ」という用語は、各バイトが個別に消去されるEEPROMとは異なり、多数のメモリセルを一度に消去することができるために選択されたものである。多値セル(MLC)の出現により、フラッシュメモリ密度が二値セルと比較してさらに増加している。フラッシュメモリは、NORフラッシュまたはNANDフラッシュとして構成することができ、NANDフラッシュは、そのメモリアレイ構造がより小型であるがために、所与の面積に対してより高い密度を有することが、当業者には理解されよう。さらなる議論において、フラッシュメモリと述べるものは、NORもしくはNANDまたは他の種類のフラッシュメモリのいずれかであるとして解釈されるべきである。

30

#### 【0008】

メモリサブシステム内のデバイスは多くの場合、パラレル相互接続スキームを使用して相互接続される。このスキームでは、アドレスおよびデータ情報ならびに制御信号がパラレル形式でデバイスに連結されるような方式でデバイスを相互接続することが必要となる。各デバイスは、データおよびアドレス情報ならびに制御信号をデバイスにパラレル転送するに対応するように、複数の入力部/出力部を組み合わせることができる。

40

#### 【特許文献1】米国特許出願第11/324,023号

#### 【発明の開示】

#### 【発明が解決しようとする課題】

#### 【0009】

50

パラレル相互接続をメモリサブシステムで利用することに伴う1つの欠点は、パラレル相互接続では、情報および信号をデバイスにパラレルに転送するために、デバイス間の多数の相互接続が必要となりがちであるということである。これによって、これらのサブシステムを実装する基板の複雑性が増すことになる。さらに、クロストークなど、多数の相互接続に伴う望ましくない影響により、これらのサブシステムの性能が制限されがちである。加えて、これらのサブシステムに組み込まれるデバイスの数が、相互接続によって伝えられる信号の伝播遅延が原因で制限されることがある。

#### 【0010】

本明細書で説明する技法は、パラレル相互接続による実装と比べてより少数でかつより短い接続を用いるシリアルディジーチェーンカスケード配列でデバイスを連結するための技法を提供することによって、上記の欠点を克服している。デバイスをディジーチェーン配列で構成することにより、デバイスは、パラレル相互接続による実装と比較してより高速で動作することが可能となるが、これが可能となるのは、より少数でかつより短い相互接続を利用することで、全体的な実装が、伝播遅延およびクロストークなどの望ましくない影響を受けにくくなるからである。さらに、より少数でかつより短い接続は、実装の複雑性を軽減するのに役立つ。さらにこの複雑性の軽減により、デバイスを具備するサブシステムをより小さな面積で実装することが可能となり、それによってサブシステムが占めるフットプリントはより小さくなる。

10

#### 【課題を解決するための手段】

#### 【0011】

本明細書で説明する技法の態様によれば、デバイスはディジーチェーンカスケード配列で連結され、したがって、ディジーチェーンカスケードにおける前方のデバイスの出力部は、情報(例えばデータ、アドレスおよびコマンド情報)と制御信号(例えばイネーブル信号)を前方のデバイスから後方のデバイスに転送することに対応するように、ディジーチェーンにおける後方の次のデバイスの入力部に連結される。

20

#### 【0012】

この技法の実施形態では、ディジーチェーンカスケードにおける各デバイスは、シリアル入力部(SI)とシリアル出力部(SO)とを備えている。情報は、デバイスにそのSIを通じて入力される。同様に、この情報は、デバイスからそのSOを通じて出力される。ディジーチェーンカスケードにおけるあるデバイスのSOは、ディジーチェーンカスケードにおける次のデバイスのSIに連結される。ディジーチェーンカスケードにおける前方のデバイスにそのSIを通じて入力された情報を、そのデバイスに通し、そのデバイスからそのSOを通じて出力することを可能にするために、回路がデバイスに設けられている。情報は次いで、前方のデバイスのSOと次のデバイスのSIとの接続を通じて、ディジーチェーンカスケードにおける次のデバイスのSIに転送される。転送された情報は次いで、次のデバイスにそのSIを通じて入力される。

30

#### 【0013】

加えて、クロック信号が、ディジーチェーンカスケードにおけるデバイスに連結されている。このクロック信号は、ディジーチェーンカスケードにおいてあるデバイスから次のデバイスに情報を転送することに対応するために、デバイスによって使用される。

40

#### 【0014】

本明細書で説明する技法の他の態様によれば、例えば、データをデバイスにSIを通じて入力し、デバイスからSOを通じて出力することを可能にするためにデバイスによって利用される制御信号(例えばイネーブル信号)は、上述のように、ディジーチェーンカスケードにおけるデバイス間で転送される。ここで、ディジーチェーンカスケードにおける前方のデバイスに入力された制御信号をそのデバイスに伝播させ、そのデバイスから出力部を通じてディジーチェーンカスケードにおける次のデバイスの入力部に転送することを可能にするために、回路が設けられている。転送された制御信号は次いで、次のデバイスに入力部を通じて入力される。

#### 【0015】

50

本発明の原理によれば、フラッシュメモリシステムは、複数のシリアル接続されたフラッシュメモリデバイスを有することができる。このシステムのフラッシュメモリデバイスは、シリアル入力データポートおよびシリアルデータ出力ポートを有するシリアルデータリンクインターフェースと、第1の入力イネーブル信号を受信するための制御入力ポートと、第2の入力イネーブル信号を送信するための制御出力ポートとを備えることができる。入力イネーブル信号は、シリアルデータリンクインターフェースとメモリバンクとの間のデータ転送を制御する回路において使用される。フラッシュメモリデバイスは、シリアル入力データおよび制御信号を外部ソースから受信するように、かつデータおよび制御信号を外部デバイスに与えるように構成されている。外部ソースおよび外部デバイスは、システム内の他のフラッシュメモリデバイスであってもよい。本発明の実施形態において、デバイスがシステム内でシリアルにカスケード接続されている場合、それらのデバイスは、受信したIPEおよびOPE信号を外部デバイスに「こだま」させる出力制御ポートをさらに備えていてもよい。これによって、システムは、ポイントツーポイント接続した信号ポートを有して、(ブロードキャスティング/マルチドロップカスケード方式に対する)デイジーチェーンカスケードスキームを形成することが可能となる。

10

#### 【0016】

これらのシステムは、限られたハードウェアフィジカルデバイス選択ピンを使用するのではなく、固有のデバイス識別およびターゲットデバイス選択のアドレススキームを使用することができ、したがって、システムの全体的な性能を犠牲にすることなく、システム全体を記憶密度に関して可能な限り高く容易に拡張することができる。本発明のいくつかの実施形態において、フラッシュメモリデバイスの各々は、固有のデバイス識別子を備えることができる。デバイスは、そのデバイスがターゲットデバイスであるかどうかを判定するために、シリアル入力データ内のターゲットデバイス情報フィールドを解析して、ターゲットデバイス情報をそのデバイスの固有のデバイス識別番号と相關させるように構成することができる。デバイスは、受信したさらなる入力データを処理する前に、このターゲットデバイス情報フィールドを解析することができる。メモリデバイスがターゲットデバイスでない場合、そのメモリデバイスは、シリアル入力データを無視することができ、それによって余分な処理時間およびリソースが節約される。

20

#### 【0017】

上記のこととは、添付の図面に示すように、本発明の実施形態の例についての以下のより具体的な説明から明らかとなろう。添付の図面において、類似の参照符号は異なる図を通じて同じ部品を示す。図面は必ずしも一定の尺度ではなく、むしろ本発明の実施形態を説明することを重視している。

30

#### 【発明を実施するための最良の形態】

#### 【0018】

本発明の好ましい実施形態の説明を以下に示す。

#### 【0019】

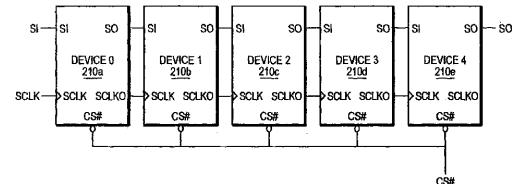

図1は、複数のシングルポートデバイス110a～eを備える例示的なデバイス構成のブロック図であり、これらのシングルポートデバイス110a～eは、シリアルデイジーチェーンカスケード配列で構成されている。デバイス110a～eは、実例として、各々がメモリ(図示せず)を具備するメモリデバイスであり、そのメモリは、ダイナミックランダムアクセスメモリ(DRAM)セル、スタッフィックランダムアクセスメモリ(SRAM)、フラッシュメモリセルなどを備えることができる。各デバイス110は、シリアル入力部(SI)と、シリアル出力部(SO)と、クロック(SCLK)入力部と、チップセレクト(CS#)入力部とを備えている。

40

#### 【0020】

SIは、情報(例えばコマンド、アドレスおよびデータ情報)をデバイス110に転送するために使用される。SOは、情報をデバイス110から転送するために使用される。SCLK入力部は、外部クロック信号をデバイス110に与えるために使用され、CS#入力部は、チップセレクト信号をデバイス110に与えるために使用される。本明細書で説明する技法と共に使用することができるデバイスの一例が、米国特許出願第11/324,023号に記載されているMISL

50

(Multiple Independent Serial Link) メモリデバイスである。

【0021】

SIおよびSOは、デイジーチェーンカスケード配列でデバイス110の間で接続されており、したがって、デイジーチェーンカスケードにおける前方のデバイス110のSOは、デイジーチェーンカスケードにおける次のデバイス110のSIに連結されている。例えば、デバイス110aのSOは、デバイス110bのSIに連結されている。各デバイス110のSCLK入力部は、例えばメモリコントローラ(図示せず)からクロック信号を供給される。クロック信号は、共通のリンクを通じて各デバイス110に分配される。以下でさらに説明するように、SCLKは、とりわけ、デバイス110に入力された情報を、デバイス110に具備された様々なレジスターでラッチするために使用することができる。

10

【0022】

デバイス110に入力された情報は、SCLK入力部に供給されたクロック信号の様々な時間でラッチすることができる。例えば、シングルデータレート(SDR)実装においては、デバイス110にSIで入力された情報は、SCLKクロック信号の立ち上がりエッジまたは立ち下がりエッジのいずれかでラッチすることができる。あるいは、ダブルデータレート(DDR)実装においては、SCLKクロック信号の立ち上がりエッジと立ち下がりエッジの双方を、SIで入力された情報をラッチするために使用することができる。

【0023】

各デバイスのCS#入力部は、デバイスを選択する通常のチップセレクトである。この入力は共通のリンクに連結されており、その共通のリンクによって、チップセレクト信号をデバイス110のすべてに同時にアサートすることが可能となり、したがってデバイス110のすべてが同時に選択される。

20

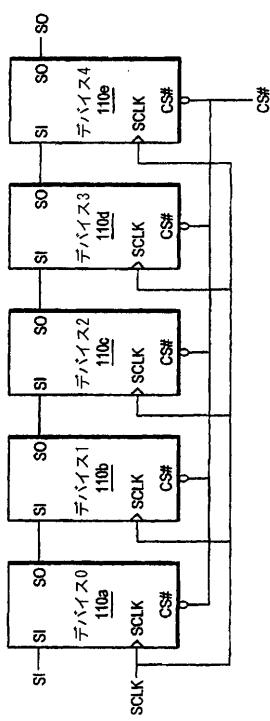

【0024】

図2は、複数のシングルポートデバイス210a～eを備える例示的なデバイス構成のブロック図であり、これらのシングルポートデバイス210a～eは、カスケード接続されたクロックを有するシリアルデイジーチェーンカスケード配列で構成されている。各デバイス210は、上述のように、SI入力部と、SO入力部と、SCLK入力部と、CS#入力部とを備えている。加えて、各デバイス210はクロック出力部(SCLKO)を備えている。SCLKOは、デバイス210に入力されたSCLK信号を出力する出力部である。

30

【0025】

図2を参照すると、デバイス210のSIおよびSOが、上述のようにデイジーチェーンカスケード配列で連結されている。加えて、このデバイスのSCLK入力部およびSCLKOもまたデイジーチェーンカスケード配列で連結されており、したがって、デイジーチェーンカスケードにおける前方のデバイス210のSCLKOが、デイジーチェーンカスケードにおける次のデバイス210のSCLK入力部に連結されている。このように、例えば、デバイス210aのSCLKOはデバイス210bのSCLK入力部に連結されている。

【0026】

クロック信号は、デイジーチェーンカスケードデバイスを通じて伝播するとき、遅延を発生しうることに留意されたい。遅延ロックループ(DLL)などの内部遅延補償回路を用いて、この遅延を回避してもよい。

40

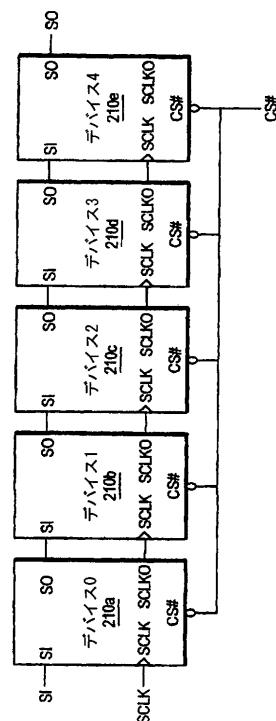

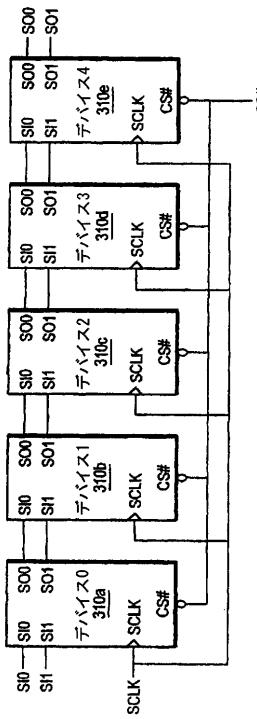

【0027】

図3は、複数のデュアルポートデバイス310a～eを備える例示的なデバイス構成のブロック図であり、これらのデュアルポートデバイス310a～eはシリアルデイジーチェーンカスケード配列で構成されている。各デバイス310は、上述のように、各ポートに対するSIおよびSOと、SCLK入力部と、CS#入力部とを備えている。図3を参照すると、デバイス310の第1のポートに対するSIは「SI0」と記されており、第2のポートに対するSIは「SI1」と記されている。同様に、第1のポートに対するSOは「SO0」、第2のポートに対するSOは「SO1」と記されている。各ポートに対するSIおよびSOは、上述のようにデバイス310の間で接続されている。このように、例えば、デバイス310aのポート0のSOは、デバイス310bのポート0のSIに供給され、以下同様である。同様に、デバイス310aのポート1のSOは、デバイ

50

ス310bのポート1のSIに供給され、以下同様である。

【0028】

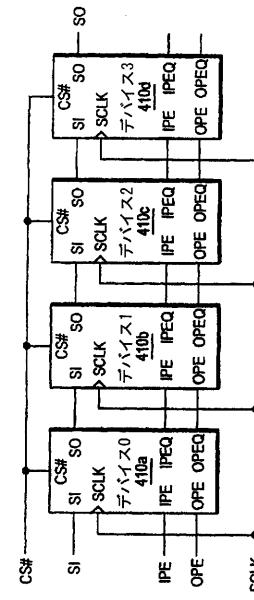

図4は、複数のシングルポートデバイスを備える例示的なデバイス構成のブロック図であり、これらのシングルポートデバイスは、様々なイネーブル信号に対する入力部および出力部を有するシリアルデイジーチェーン配列で構成されている。各デバイス410は、上述のように、SIと、SOと、CS#入力部と、SCLK入力部とを備えている。加えて、各デバイス410は、入力ポートイネーブル(IPE)入力部と、出力ポートイネーブル(OPE)入力部と、入力ポートイネーブル(IPEQ)出力部と、出力ポートイネーブル(OPEQ)出力部とを備えている。IPE入力は、IPE信号をデバイスに入力するために使用される。IPEがアサートされているとき、SIを通じて情報をデバイス410にシリアル入力することができるよう、IPE信号は、SIをイネーブルするためにデバイスによって使用される。同様に、OPE入力部は、OPE信号をデバイスに入力するために使用される。OPEがアサートされているとき、SOを通じて情報をデバイス410にシリアル出力することができるよう、OPE信号は、SOをイネーブルするためにデバイスによって使用される。IPEQおよびOPEQは、それぞれIPEおよびOPE信号をデバイスから出力する出力部である。IPEQ信号は、遅延したIPE信号であっても、IPE信号を微分したものであってもよい。同様に、OPEQ信号は、遅延したOPE信号であっても、OPE信号を微分したものであってもよい。CS#入力部およびSCLK入力部は、上述のように、それぞれCS#およびSCLK信号をデバイス410a～dに分配する別個のリンクに連結されている。

10

【0029】

SIおよびSOは、上述のように、デイジーチェーンカスケード配列において、あるデバイスから次のデバイスへと連結されている。さらに、デイジーチェーンカスケードにおける前方のデバイス410のIPEQおよびOPEQは、デイジーチェーンカスケード配列における次のデバイス410のそれぞれIPE入力およびOPE入力に連結されている。この配列によって、IPEおよびOPE信号は、シリアルデイジーチェーンカスケード方式で、あるデバイス410から次のデバイスに転送される。

20

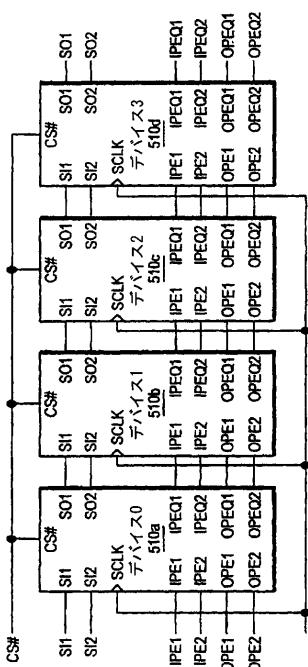

【0030】

図5は、デュアルポートデバイス510a～dを備える例示的なデバイス構成のブロック図であり、これらのデュアルポートデバイス510a～dは、様々なイネーブル信号に対する入力部および出力部を有するシリアルデイジーチェーン配列で構成されている。各デバイス510は、上述のように、CS#入力部と、SCLK入力部と、各ポートに対するSI、SO、IPE、OPE、IPEQおよびOPEQとを備えている。ポート1およびポート2に対するSI、SO、IPE、OPE、IPEQおよびOPEQはそれぞれ、SI1、SO1、IPE1、OPE1、IPEQ1およびOPEQ1、ならびにSI2、SO2、IPE2、OPE2、IPEQ2およびOPEQ2と表されている。

30

【0031】

各デバイス510に対するCS#入力部は、上述のように、すべてのデバイス510を同時に選択するように单一のリンクに連結されている。同様に、各デバイス510に対するSCLKは、上述のように、クロック信号をすべてのデバイス510に同時に分配するように構成された单一のリンクに連結されている。また、上述のように、SI、SO、IPE、OPE、IPEQおよびOPEQは、デイジーチェーンカスケードにおける前方のデバイスのSO、IPEQおよびOPEQが、デイジーチェーンカスケードにおける後方のSI、IPEおよびOPEに連結されるように、デバイス間で連結されている。例えば、デバイス510aのSO1、SO2、IPEQ1、IPEQ2、OPEQ1およびOPEQ2は、デバイス510bのそれぞれSI1、SI2、IPE1、IPE2、OPE1およびOPE2に連結されている。

40

【0032】

デバイス510aのSI、IPEおよびOPE入力部に入力されるSI、IPEおよびOPE信号はそれぞれ、デバイス510aに例えばメモリコントローラ(図示せず)から与えられる。デバイス510dは、デバイス510dのSO、IPEQおよびOPEQ出力部を通じてデータおよび制御信号を再びメモリコントローラに与える。

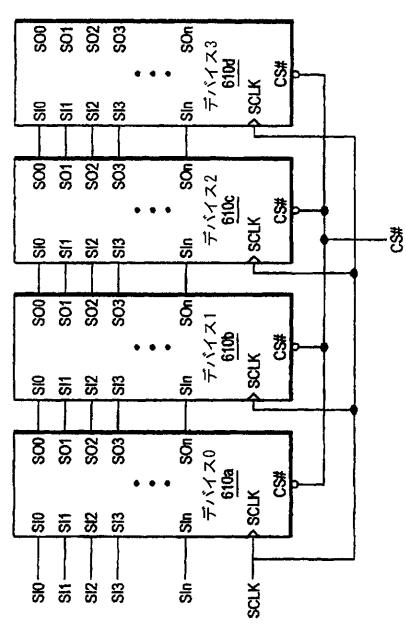

【0033】

50

図6は、多数のシリアル入力部(SI0からSI<sub>n</sub>)および多数のシリアル出力部(SO0からSO<sub>n</sub>)を有する複数のデバイスを備える例示的なデバイス構成のブロック図であり、これらのデバイスはシリアルディジーチェーンカスケード配列で構成されている。加えて、各デバイス610は、上述のようにSCLK入力部とCS#入力部とを有している。

【0034】

各デバイス610に対して用いられているシリアル入力部(SI0からSI<sub>n</sub>)およびシリアル出力部(SO0からSO<sub>n</sub>)により、それぞれシリアル形式で情報をデバイス610に入力し、またデバイス610から出力することが可能となっている。各入力部は、ある種類の情報(例えばアドレス、コマンド、データ)および/または信号(例えばイネーブル信号)をデバイス610に入力するように、特定の役割を与えられていてもよい。同様に、各出力部は、ある種類の情報および信号をデバイス610から出力するように、特定の役割を与えられていてもよい。例えば、1つ以上の入力部が、アドレス情報をデバイス610に入力することができるよう、役割を与えられていてもよい。同様に、例えば、1つ以上の出力部が、アドレス情報をデバイス610から出力するよう、役割を与えられていてもよい。

10

【0035】

各デバイス610に対するシリアル入力部およびシリアル出力部の数は通常、アドレス線の数、コマンドサイズおよびデータ幅サイズなど、特定の要因に依存する。これらの要因は、デバイスが特定のシステムアプリケーションにおいてどのように使用されるかによって影響を受けることがある。例えば、少量の情報を格納するために使用するデータストアを必要とするシステムアプリケーションは、大量の情報に対するデータストアを必要とするシステムアプリケーションと比べて、より少数のアドレスおよびデータ線を、したがつてより少数の入力部/出力部を有するデバイスを用いることができる。

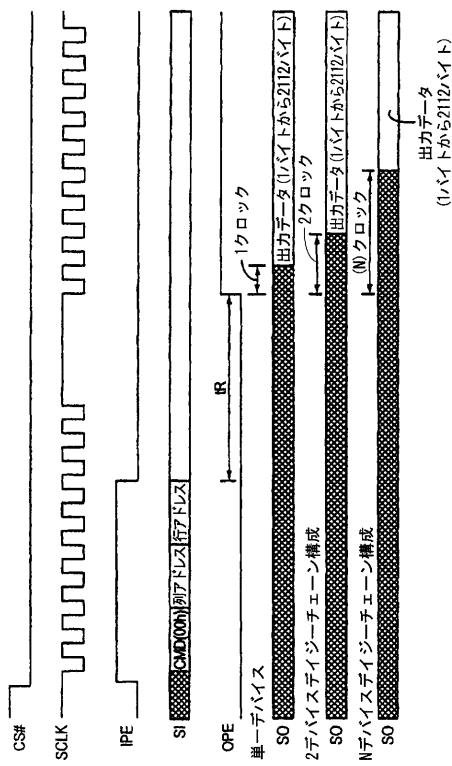

20

【0036】

図7は、読み取り動作に関するタイミングを示すタイミング図であり、この読み取り操作は、単一のデバイスとシリアルディジーチェーンカスケード配列で構成された複数のデバイスとで実施されたものである。図7を参照すると、CS#がアサートされてデバイスのすべてが選択されている。この読み取り動作は、IPEをアサートし、読み取り動作に関連する情報を、SIを通じてデバイスにクロックすることによって開始する。実例として、この情報は、読み取り動作を実施すべきであることを示すコマンド(CMD)と、データが読み取られるメモリ内の開始場所を示す列アドレス(Col. ADD)および行アドレス(Row ADD)とを含んでいる。

30

【0037】

時間「tR」において、要求されたデータがメモリから読み取られ、デバイスに具備された専用の内部データバッファに置かれる。tRの長さは通常、メモリを構成するセルの特性によって決まる。時間tRの後、OPEがアサートされて、内部データバッファからSOを通じてディジーチェーンカスケードにおける次のデバイスへとデータをシリアル転送することが可能となる。データは、SO出力部において、実例としてSCLKの立ち上がりエッジにおいて、内部バッファからシリアル出力される。ディジーチェーンカスケードにおけるデバイスから出力されたデータは、例えば、IPEおよびOPEなどの制御信号を伝播させることに伴うレイテンシを制御するために、1クロックサイクル程度遅延されている。さらに以下で説明するように、レイテンシ制御は、クロック同期したラッチを使用して実施される。

40

【0038】

フラッシュコアアーキテクチャを実現する、カスケード接続されたメモリデバイスの動作の一部の例を以下の表1に示す。表1に、ターゲットデバイスアドレス(TDA)と、使用可能なOP(動作)コードと、列アドレス、行/バンクアドレス、および入力データの対応状態とを示す。

【0039】

【表1】

| 動作                 | ターゲットデバイスアドレス(1バイト) | 動作コード(1バイト) | 列アドレス(2バイト) | 行/列アドレス(3バイト) | 入力データ(1バイトから2112バイト) |

|--------------------|---------------------|-------------|-------------|---------------|----------------------|

| ページリード             | tda                 | 00h         | 有効          | 有効            | -                    |

| ランダムデータリード         | tda                 | 05h         | 有効          | -             | -                    |

| コピー用ページリード         | tda                 | 35h         | -           | 有効            | -                    |

| コピー用ターゲットアドレス入力    | tda                 | 8Fh         | -           | 有効            | -                    |

| シリアルデータ入力          | tda                 | 80h         | 有効          | 有効            | 有効                   |

| ランダムデータ入力          | tda                 | 85h         | 有効          | -             | 有効                   |

| ページプログラム           | tda                 | 10h         | -           | -             | -                    |

| ロック消去              | tda                 | 60h         | -           | 有効            | -                    |

| リードステータス           | tda                 | 70h         | -           | -             | -                    |

| リードID              | tda                 | 90h         | -           | -             | -                    |

| ライトコンフィギュレーションレジスタ | tda                 | A0h         | -           | -             | 有効(1バイト)             |

| ライトDN(デバイス名)エントリ   | 00h                 | B0h         | -           | -             | -                    |

| リセット               | tda                 | FFh         | -           | -             | -                    |

| バンクセレクト            | tda                 | 20h         | -           | 有効(バンク)       | -                    |

表1：コマンドセット

10

20

30

40

50

## 【0040】

本発明のいくつかの実施形態において、図1～6に示すシステムにおける各デバイスは、シリアル入力データ内のターゲットデバイスアドレス(tda)として使用することができる固有のデバイス識別子を有していてもよい。シリアル入力データを受信すると、フラッシュメモリデバイスは、そのシリアル入力データ内のターゲットデバイスアドレスフィールドを解析し、そのデバイスがターゲットデバイスであるかどうかを、ターゲットデバイスアドレスをそのデバイスの固有のデバイス識別番号と相關させることによって判断することができる。

## 【0041】

表2は、図1～6に関連して説明したシステムを含めた本発明の実施形態による入力データストリームの好ましい入力シーケンスを示す。コマンド、アドレス、およびデータが、最上位ビットから開始して各メモリデバイスの内外に順次シフトされる。

## 【0042】

図4を参照する。デバイス410a～dは、入力ポートイネーブル(IPE)がHIGHである間にシリアルクロック(SCLK)の立ち上がりエッジでサンプリングされたシリアル入力信号(SIP)で動作することができる。コマンドシーケンスは、1バイトのターゲットデバイスアドレス(「tda」)および1バイトの動作コードで開始しており、この動作コードはまた、同じ意味でコマンドコード(表1では「cmd」)と呼ばれることもある。最上位ビットにおいて、シリアル入力信号を1バイトのターゲットデバイスアドレスで開始することにより、デバイスは、受信したさらなる入力データを処理する前に、ターゲットデバイスアドレスフィー

ルドを解析することができる。メモリデバイスがターゲットデバイスでない場合、そのメモリデバイスは、処理する前にシリアル入力データを別のデバイスに転送することができ、それによって余分な処理時間およびリソースが節約される。

【0043】

【表2】

| 動作                 | 第1<br>バイ<br>ト | 第2<br>バイ<br>ト | 第3バ<br>イト | 第4バ<br>イト | 第5バ<br>イト | 第6バ<br>イト | 第7バ<br>イト | 第8バ<br>イト | … | 第21<br>バ<br>イト | … | 第21<br>バ<br>イト |

|--------------------|---------------|---------------|-----------|-----------|-----------|-----------|-----------|-----------|---|----------------|---|----------------|

| ページリード             | tda           | cmd           | 列アド<br>レス | 列アド<br>レス | 行アド<br>レス | 行アド<br>レス | 行アド<br>レス | -         | - | -              | - | -              |

| ランダムデータリード         | tda           | cmd           | 列アド<br>レス | 列アド<br>レス | -         | -         | -         | -         | - | -              | - | -              |

| コピー用ページリード         | tda           | cmd           | 行アド<br>レス | 行アド<br>レス | 行アド<br>レス | -         | -         | -         | - | -              | - | -              |

| コピー用ターゲットアドレス入力    | tda           | cmd           | 行アド<br>レス | 行アド<br>レス | 行アド<br>レス | -         | -         | -         | - | -              | - | -              |

| シリアルデータ入力          | tda           | cmd           | 列アド<br>レス | 列アド<br>レス | 行アド<br>レス | 行アド<br>レス | 行アド<br>レス | データ       | … | データ            | … | データ            |

| ランダムデータ入力          | tda           | cmd           | 列アド<br>レス | 列アド<br>レス | データ       | データ       | データ       | データ       | … | データ            | - | -              |

| ページプログラム           | tda           | cmd           | -         | -         | -         | -         | -         | -         | - | -              | - | -              |

| ブロック消去             | tda           | cmd           | 行アド<br>レス | 行アド<br>レス | 行アド<br>レス | -         | -         | -         | - | -              | - | -              |

| リードステータス           | tda           | cmd           | -         | -         | -         | -         | -         | -         | - | -              | - | -              |

| リードID              | tda           | cmd           | -         | -         | -         | -         | -         | -         | - | -              | - | -              |

| ライトコンフィギュレーションレジスタ | tda           | cmd           | データ       | -         | -         | -         | -         | -         | - | -              | - | -              |

| ライトDNエントリ          | tda           | cmd           | -         | -         | -         | -         | -         | -         | - | -              | - | -              |

| リセット               | tda           | cmd           | -         | -         | -         | -         | -         | -         | - | -              | - | -              |

表2：バイトモードにおける入力シーケンス

【0044】

1バイトのTDAは、デバイス内にシフトされ、1バイトのcmdコードが続く。最上位ビット(MSB)はSIPで開始し、各ビットはシリアルクロック(SCLK)の立ち上がりエッジでラッチされる。コマンドに応じて、1バイトのコマンドコードに、列アドレスバイト、行アドレスバイト、バンクアドレスバイト、データバイト、および/もしくは組み合わせが続くか、

10

20

30

40

50

または何も続かないことがある。

【0045】

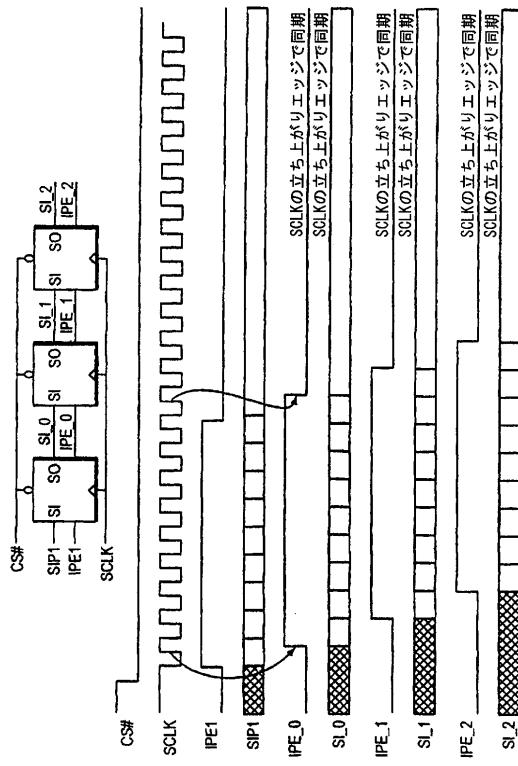

図8は、情報に関するタイミングを示すタイミング図であり、この情報は、シリアルデイジーチェーンカスケード配列で構成されたデバイス間で転送されたものである。上記のように、CS#がアサートされてデバイスが選択される。IPEをアサートし、SCLKの相次ぐ立ち上がりエッジでデータをデバイスにクロックすることによって、デイジーチェーンカスケードにおける第1のデバイスに情報が入力される。IPEは、第1のデバイスを通じて第2のデバイスに1サイクル未満で伝播される。これにより、情報が第1のデバイスにクロックされてから1サイクル後に、第1のデバイスのSOから第2のデバイスのSIに情報をクロックすることが可能となっている。これが、デイジーチェーンカスケードにおける相次ぐデバイスに対して繰り返される。このように、例えば、情報は、シリアルデイジーチェーンカスケードにおける第3のデバイスに、第1のデバイスにおけるデータのラッチ点から3番目のSCLKの立ち上がりエッジで入力される。制御信号IPEおよびOPEは、これらの信号に対する適切なセットアップ時間をデイジーチェーンカスケードにおける次のデバイスで確保するために、SCLKの立ち上がりエッジと同期される。

10

【0046】

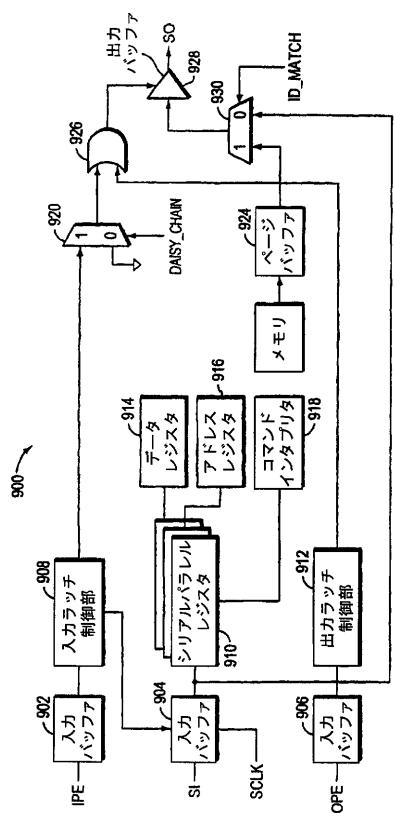

図9は、シングルポートデバイスに対する例示的なシリアル出力制御論理回路900のブロック図である。論理回路900は、IPE用の入力バッファ902と、SI(SIP)用の入力バッファ904と、OPE用の入力バッファ906と、入力ラッチ制御部908と、シリアルパラレルレジスタ910と、出力ラッチ制御部912と、データレジスタ914と、アドレスレジスタ916と、コマンドインタプリタ918と、セレクタ920と、ページバッファ924と、論理和ゲート926と、出力バッファ928と、セレクタ930と、メモリ950とを備えている。

20

【0047】

入力バッファ902は、バッファ902の入力部でデバイスに供給されたIPE信号の状態をバッファリングするように構成された通常のLVTTL(低電圧トランジスタトランジスタ論理回路)バッファである。バッファ902の出力は入力ラッチ制御部908に供給され、この入力ラッチ制御部908は、IPE信号の状態をラッチし、IPE信号のラッチ状態を入力バッファ904およびセレクタ920に与える。入力バッファ904は、SI入力を通じてデバイスに供給された情報をバッファリングするように構成されたLVTTLバッファである。入力バッファ904は、入力ラッチ制御部908の出力によってイネーブルにされる。イネーブルにされると、SI入力部に与えられた情報は、バッファ908によってシリアルパラレルレジスタ910およびセレクタ930の入力に供給される。入力バッファ904は、IPE信号がアサートされていることを、入力ラッチ制御部908から供給されたIPE信号のラッチ状態が示すときイネーブルにされる。シリアルパラレルレジスタ910に供給された情報は、このレジスタ910によってシリアル形式からパラレル形式に変換される。シリアルパラレルレジスタ910の出力は、データレジスタ914、アドレスレジスタ916、およびコマンドインタプリタ918に供給される。

30

【0048】

データレジスタ914およびアドレスレジスタ916は、SIを通じてデバイスに供給されたデータおよびアドレス情報をそれぞれ保持する。コマンドインタプリタ918は、SIを通じてデバイスに入力されたコマンドを解釈するように構成されている。これらのコマンドは、デバイスの動作をさらに制御するために使用される。例えば、「ライトメモリ」コマンドは、デバイスが、データレジスタ914に含まれているデータを、デバイスに具備されたメモリ950に、アドレスレジスタ916によって指定されたアドレスで書き込むようにするために使用することができる。

40

【0049】

入力バッファ906は、デバイスのOPE入力部に供給されたOPE信号をバッファリングするように構成されている。バッファ906の出力は、OPE信号の状態をラッチする出力ラッチ制御部912に転送される。出力ラッチ制御部は、ラッチされたOPE信号状態をORゲート926に出力する。ORゲート926は通常の論理和ゲートであり、この論理和ゲートの出力は、出力バッファ928の出力をイネーブル/ディスエーブルにするために使用されている。

50

## 【0050】

セレクタ920は、2つの入力のうち信号DAISY\_CHAINによって選択された一方を出力する通常の2対1マルチプレクサである。上記のように、これらの入力のうちの一方は、入力ラッチ制御部908からのIPEのラッチ状態である。他方の入力は、論理ローの状態に設定されている。信号DAISY\_CHAINは、デバイスがシリアルディジーチェーンカスケード配列において1つ以上の他のデバイスに連結されているかどうかを示す。実例として、この信号は、デバイスがシリアルディジーチェーンカスケード配列において1つ以上のデバイスに連結されている場合にアサートされる。DAISY\_CHAIN信号をアサートすると、セレクタ920に供給されたIPE信号のラッチ状態がセレクタ920から出力される。DAISY\_CHAINがアサートされていないときは、セレクタ920に入力された論理ローの状態がセレクタ920から出力される。

10

## 【0051】

ページバッファ924は、メモリ950から読み取られた情報を保持するように構成された通常のデータバッファである。セレクタ930は、2つの入力のうち信号ID\_MATCHによって選択された一方を出力する通常の2対1マルチプレクサである。セレクタ930への一方の入力はページバッファ924の出力部から供給され、他方の入力はSI入力バッファ904の出力部から供給される。セレクタ930の出力は、出力バッファ928に供給される。信号ID\_MATCHは、SIを通じてデバイスに送られた特定のコマンドが、そのデバイスを宛先とするものであるかどうかを示す。コマンドがそのデバイスを宛先とするものである場合、ID\_MATCHがアサートされて、ページバッファ924からの出力がセレクタ930から出力される。ID\_MATCHがアサートされていない場合、SIバッファ904からの出力(すなわち、デバイスに入力されたSI信号の状態)がセレクタ930から出力される。

20

## 【0052】

メモリ950は、データを保持するように構成された通常のメモリである。メモリ950は、SIを通じてデバイスに入力されたアドレスを使用してアドレス指定可能な、スタティックRAM(SRAM)、ダイナミックRAM(DRAM)またはフラッシュメモリセルなどのセルを備えるランダムアクセスメモリ(RAM)であってもよい。

## 【0053】

動作中、アサートされたIPE信号は、入力バッファ902によってバッファリングされ、IPEのアサート状態をラッチする入力ラッチ制御部908に転送される。このラッチ状態は、セレクタ920および入力バッファ904に供給されて、このバッファ904をイネーブルにする。入力バッファ904に入力されたコマンド、アドレスおよびデータ情報は次いで、シリアルパラレルレジスタ910に転送され、このシリアルパラレルレジスタ910は、その情報をシリアル形式からパラレル形式に変換し、コマンド、アドレスおよびデータ情報をコマンドインターフェース918、アドレスレジスタ916およびデータレジスタ914にそれぞれ供給する。バッファ904の出力はまた、セレクタ930に供給される。ID\_MATCHがアサートされていない場合は、バッファ904の出力がセレクタ930の出力部に出現し、そのバッファ904の出力が出力バッファ928の入力部に供給される。DAISY\_CHAINがアサートされている場合は、IPEのラッチ状態がセレクタ920の出力部に出現し、ORゲート926の第1の入力部に供給される。ORゲート926は、IPEの状態を出力バッファ928に渡して出力バッファ928をイネーブルにする。これにより、SI入力部に入力された情報を、SOでデバイスから出力させることができる。

30

## 【0054】

ページバッファ924からのデータは、OPEおよびID\_MATCHをアサートすることによってデバイスから出力される。具体的には、OPEのアサート状態が入力バッファ906に供給され、次に、入力バッファ906が、その状態を出力ラッチ制御部912に供給し、出力ラッチ制御部912がその状態をラッチする。ラッチされたアサート状態が、ORゲート926の第2の入力に供給され、ORゲート926が信号を出力して出力バッファ928をイネーブルにする。ID\_MATCHをアサートすると、ページバッファ924の出力をセレクタ930の出力に出現させることができる。セレクタ930の出力は、イネーブルにされた出力バッファ928に供給され、出力バッ

40

50

ファ928は、デバイスのSO出力部でデータをデバイスから出力する。

【0055】

DAISY\_CHAINがアサートされていない場合、出力バッファ928はOPEによってのみイネーブルにされることに留意されたい。これによって、このデバイスは、非デイジーチェーンシリアルカスケード構成で使用することが可能となっている。

【0056】

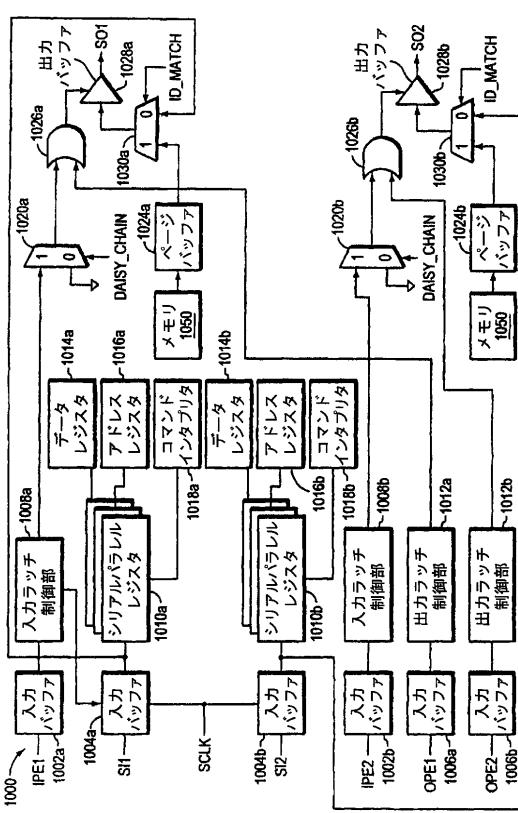

図10は、デュアルポートデバイスに対する例示的なシリアル出力制御論理回路1000のブロック図である。各ポートごとに、入力および制御バス論理回路1000は、IPE入力バッファ1002、SI入力バッファ1004、OPE入力バッファ1006、入力ラッチ制御部1008、シリアルパラレルレジスタ1010、出力ラッチ制御部1012、データレジスタ1014、アドレスレジスタ1016、コマンドインタプリタ1018、セレクタ1020、ページバッファ1024、論理和ゲート1026、出力バッファ1028およびセレクタ1030を備えており、これらはそれぞれ、上述のIPE入力バッファ902、SIP入力バッファ904、OPE入力バッファ906、入力ラッチ制御部908、シリアルパラレルレジスタ910、出力ラッチ制御部912、データレジスタ914、アドレスレジスタ916、コマンドインタプリタ918、セレクタ920、ページバッファ924、論理和ゲート926、出力バッファ928およびセレクタ930と同一である。

10

【0057】

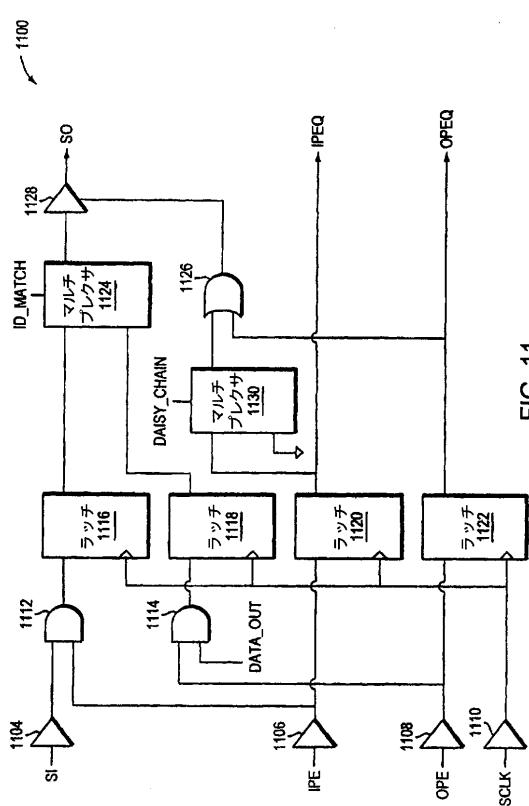

図11は、本明細書で説明する技法と共に使用しされうるシリアル出力制御論理回路1100の別の実施形態の詳細ブロック図である。論理回路1100は、SI入力バッファ1104と、IPE入力バッファ1106と、OPE入力バッファ1108と、SCLK入力バッファ1110と、論理積ゲート1112および1114と、ラッチ1116、1118、1120および1122と、セレクタ1124および1130と、論理和ゲート1126と、SO出力バッファ1128とを備えている。バッファ1104、1106、1108および1110は、デバイスに入力されたSI、IPE、OPEおよびSCLK信号それぞれをバッファリングするように構成された通常のLVTTLバッファである。

20

【0058】

ANDゲート1112は、IPEがアサートされているとき、SIに入力された情報をラッチ1116に出力するように構成されている。ラッチ1116は、クロック信号(SCLK)がバッファ1110によって与えられているとき、情報をラッチするように構成されている。DATA\_OUTは、デバイスに具備されたメモリ(図示せず)から読み取られたデータの状態を表す。ANDゲート1114は、OPEがアサートされているとき、DATA\_OUTの状態を出力するように構成されている。ANDゲート1114の出力はラッチ1118に送り込まれ、このラッチ1118は、クロック信号がバッファ1110によって与えられているとき、DATA\_OUTの状態をラッチするように構成されている。バッファ1106は、デバイスに供給されたIPE信号をバッファリングするように構成されている。バッファ1106の出力は、ラッチ1120によってラッチされる。同様に、バッファ1108は、デバイスに供給されたOPE信号をバッファリングするように構成されている。ラッチ1122は、バッファ1108によって出力されたOPEの状態をラッチするように構成されている。セレクタ1124および1130は、それぞれ2つの入力部を備える通常の2対1マルチブレクサである。セレクタ1124に対する入力は、上述のID\_MATCH信号によって、セレクタ1124からの出力に選択される。一方の入力は、ラッチ1118によって維持されたDATA\_OUTのラッチ状態を供給される。この入力は、ID\_MATCHがアサートされているとき、セレクタ1124からの出力に選択される。他方の入力は、ラッチ1116によって維持されたSIのラッチ状態を供給される。この入力は、ID\_MATCHがアサートされていないとき、セレクタ1124からの出力に選択される。

30

【0059】

セレクタ1130に対する入力は、上述のDAISY\_CHAIN信号によって、セレクタ1130からの出力に選択される。セレクタ1130への一方の入力は、ラッチ1120によって維持されたIPEのラッチ状態を供給され、他方の入力は論理ゼロに結び付けられている。DAISY\_CHAINがアサートされているとき、IPEのラッチ状態が、セレクタ1130からの出力に選択される。同様に、DAISY\_CHAINがアサートされていないとき、論理ゼロが、セレクタ1130からの出力に選択される。

40

50

## 【0060】

ORゲート1126は、イネーブル/ディスエーブル信号を出力バッファ1128に与えるように構成された通常の論理和ゲートである。ORゲート1126は、セレクタ1130の出力と、ラッチ1122によって維持されたOPEのラッチ状態とを供給される。これらの出力のいずれも、イネーブル信号をバッファ1128に与えてバッファの出力をイネーブルにするために使用することができる。バッファ1128は、出力信号SOをバッファリングする通常のバッファである。上記のように、バッファ1128は、ORゲート1126の出力によってイネーブル/ディスエーブルにされる。

## 【0061】

動作中、IPEがアサートされているとき、SIを通じてデバイスに入力された情報はラッチ1116に供給される。ラッチ1116は、実例として、IPEがアサートされた後、SCLKの第1の上昇推移においてこの情報をラッチする。同様に、ラッチ1120は、このSCLKの推移においてIPEの状態をラッチする。ID\_MATCHがアサートされていないと仮定すると、ラッチ1116の出力がセレクタ1124を通じてバッファ1128に供給される。同様に、アサートされたIPEがバッファ1106からラッチ1120に転送され、このラッチ1120において、このIPEはまた、実例として、SCLKの第1の上昇推移によってラッチされる。DAISY\_CHAINがアサートされていると仮定すると、IPEのラッチ状態がセレクタ1130の出力部に与えられ、ORゲート1126に転送されて、イネーブル信号がバッファ1128に与えられる。次いで、SIのラッチ状態が、バッファ1128を通じて出力SOとしてデバイスから転送される。

10

## 【0062】

DAISY\_CHAINがアサートされていないとき、セレクタ1130に入力された論理ゼロが選択され、それによって論理ゼロがセレクタ1130から出力される。これによって、IPEがバッファ1128をイネーブルにすることが不可能になる。

20

## 【0063】

実例として、OPEがアサートされた後のSCLKの次の上昇推移において、OPEのアサート状態がラッチ1122でラッチされ、DATA\_OUTの状態がラッチ1118でラッチされる。ID\_MATCHがアサートされていると仮定すると、DATA\_OUTのラッチ状態がセレクタ1124によって選択され、バッファ1128の入力部に加えられる。同時に、ラッチ1122からのOPEのラッチされたアサート状態が、ORゲート1126を通過してバッファ1128をイネーブルにし、それによって、DATA\_OUTのラッチ状態が、出力SOとしてデバイスから出力される。

30

## 【0064】

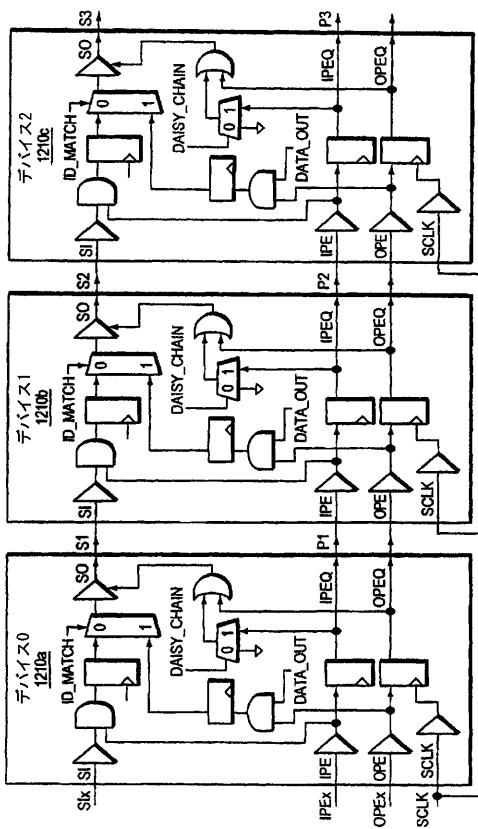

図12は、シリアルディジーチェーンカスケード配列で構成され、例示的なシリアル出力制御論理回路を具備するデバイスの例示的な構成のブロック図である。この配列は3つのデバイス1210を備えており、これらのデバイス1210は、上述のように、ディジーチェーンカスケードにおける前方のデバイスの出力部が、ディジーチェーンカスケードにおける次のデバイスの入力部に連結されるように構成されている。あるデバイスから次のデバイスへの情報およびデータの転送について、図13を参照して以下に説明する。

30

## 【0065】

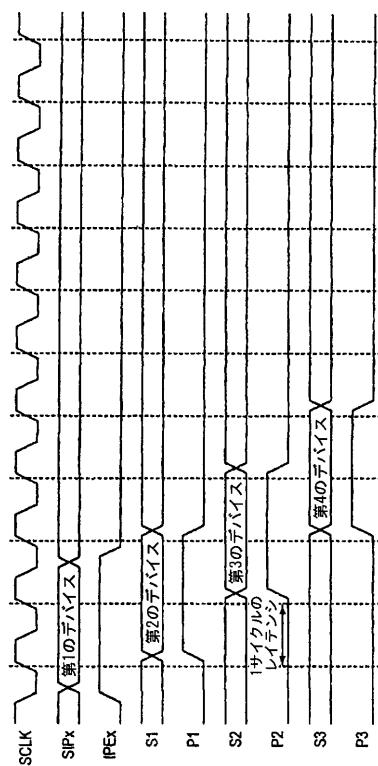

図13は、図12に示すデバイスの入力および出力に関するタイミングを示す例示的なタイミング図である。具体的には、この図は各デバイス内のシリアル出力制御論理回路1100の動作を示しており、この動作は、各デバイス1210のSI入力部で入力された情報をデバイス1210のSO出力部に渡すことに関するものである。

40

## 【0066】

図11、12および13を参照し、DATA\_CHAINがアサートされていると仮定する。IPEがデバイス1210aでアサートされているとき、デバイスのSI入力部における情報が、上述のように、デバイスのシリアル出力制御論理回路1100を通じてデバイス1210aのSO出力部に渡される。具体的には、データが、実例としてIPEがアサートされた後のSCLKの各立ち上がりエッジにおいて、デバイス1210aにクロックされる。情報およびIPEの状態は、上述のように論理回路1100を通じて伝播し、それぞれデバイスのSOおよびIPEQ出力部でデバイス1210aを抜け出す。これらの出力は、図においてそれぞれS1およびP1として表されている。こ

50

これらの出力は、上述のように、デバイス1210bのSIおよびIPE入力部に供給され、デバイス1210bのシリアル出力制御論理回路1100を通過し、1クロックサイクル後に、デバイス1210bからこのデバイスのSOおよびIPEQ出力部で出力される。これらの出力は、図においてそれぞれS2およびP2として表されている。同様に、デバイス1210bのSOおよびIPEQ出力は、デバイス1210cのSIおよびIPE入力部にそれぞれ供給され、デバイス1210cのシリアル出力制御論理回路1100を通過し、1クロックサイクル後にデバイス1210cからデバイスのSOおよびIPEQ出力部でそれぞれ出力される。これらの出力は、図においてそれぞれS3およびP3として表されている。

## 【0067】

上述のデイジーチェーンカスケード配列では、SDR動作用のデイジーチェーンカスケードにおける信号の出力レイテンシは、以下の式を使用して求めることができる。 10

## 【0068】

出力レイテンシ=N\*クロックサイクル時間

## 【0069】

上式において、

「出力レイテンシ」はデータの出力レイテンシであり、

「N」はデイジーチェーンカスケード配列におけるデバイスの数であり、

「クロックサイクル時間」は、クロック(例えばSCLK)が動作するクロックサイクル時間である。

## 【0070】

例えば、図12に示すデイジーチェーンカスケードに対するクロックサイクル時間が10ナノ秒であると仮定する。デバイス1210cのSOでのデータの全出力レイテンシは、 $3 \times 10$ ナノ秒すなわち30ナノ秒である。 20

## 【0071】

DDR動作の場合、出力レイテンシは以下のように求めることができる。

## 【0072】

出力レイテンシ=N\*(クロックサイクル時間/2)

## 【0073】

DDR動作においては、クロックの両エッジが、入力データのラッチ点および出力データの変化点として機能することができる。このように、全レイテンシは、SDR動作に対するレイテンシの半分となる。 30

## 【0074】

上記の説明において、デバイス1210に入力された情報は、SDR動作に対しては1クロックサイクル後、DDR動作に対しては半サイクル後に出力されることに留意されたい。この遅延は、出力バッファ1128を活動化するのに要する時間に対応するために導入されている。

## 【0075】

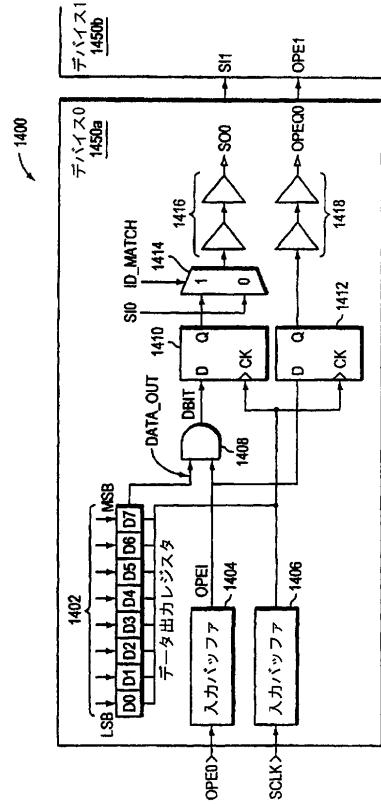

図14は、あるデイジーチェーンカスケードにおける第1のデバイス1450aのメモリに含まれているデータをそのデイジーチェーンカスケードにおける第2のデバイス1450bに転送するために使用する論理回路1400のブロック図である。論理回路1400は、データ出力レジスタ1402と、OPE入力バッファ1404と、SCLK入力バッファ1406と、ANDゲート1408と、データ出力ラッチ1410と、OPE状態ラッチ1412と、セレクタ1414と、SO出力バッファ1416と、OPEQ出力バッファ1418とを備えている。 40

## 【0076】

データ出力レジスタ1402は、デバイス1450に具備されたメモリから読み取られたデータを格納するように構成された通常のレジスタである。レジスタ1402は、実例として、メモリからパラレルにデータをロードし、ゲート1408の入力部にシリアルにデータを転送するパラレルシリアルデータレジスタである。SCLKは、レジスタ1402がデータをゲート1408に転送するために使用するクロックを与える。図示のように、データレジスタ1402は、ビットD0からD7を備える1バイトのデータを保持するように構成されており、ここで、D0はバイトの最下位ビット LSB であり、ビットD7はバイトの最上位ビット MSB である。レジス

10

20

30

40

50

タ1402は、データのバイト値をメモリからパラレルにロードされる。次いでデータが、レジスタからシフトされ、MSBを初めとして1ビットずつゲート1408の入力部にシリアルに供給される。

【0077】

バッファ1404および1406は、入力信号OPEおよびSCLKをそれぞれバッファリングするために使用される通常のLVTTLバッファである。OPE信号は、バッファ1404(OPE1)の出力部からゲート1408に転送される。SCLK信号は、バッファ1406の出力部からデータ出力レジスタ1402とラッチ1410および1412に転送され、これらの構成要素にクロックが与えられる。

【0078】

ゲート1408は、OPEがアサートされているときにデータ出力レジスタ1402(DATA\_OUT)の出力をラッチ1410に転送するように構成された通常の論理積ゲートである。ゲート1408の出力は「DBIT」と表されている。ラッチ1410および1412は、DBITの状態をおよびOPE信号それぞれラッチするように構成された通常のラッチである。セレクタ1414は、信号ID\_MATCHによって制御される通常の2入力の2対1マルチプレクサである。データ入力の一方は、DBITのラッチ状態を供給される。この状態は、ID\_MATCHがアサートされているときにセレクタ1414から出力される。他方の入力は、デバイス1450aにそのSIを通じて入力されたシリアル情報(SIO)を供給される。この情報は、ID\_MATCHがアサートされていないときにセレクタ1414によって出力される。

【0079】

バッファ1416および1418は、セレクタ1414およびラッチ1406の出力をそれぞれバッファリングするように構成された通常のバッファである。バッファ1416の出力は、S0(S00)としてデバイス1450aを抜け出し、バッファ1418の出力はOPEQ(OPEQ0)としてデバイス1450aを抜け出す。

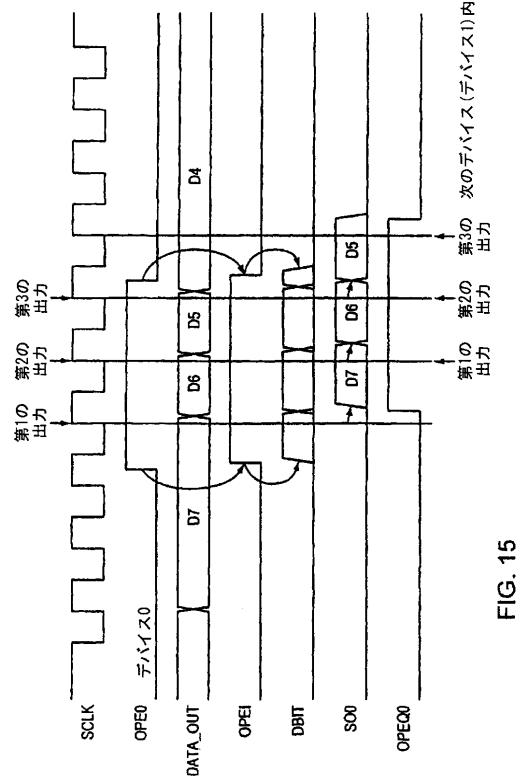

【0080】

図15は、論理回路1400を使用して、デバイス1450aに具備されたメモリからデバイス1450bにデータのバイト値を転送することに関するタイミングを示すタイミング図である。図14および15を参照すると、OPEが入力バッファ1404でデバイス1450aに供給された直後に、OPE1がアサートされている。OPE1がゲート1408に供給されて、データ出力レジスタ1402のD7に出現するデータを、SCLKの次の立ち上がりエッジにおいてラッチ1410でラッチすることが可能となる。加えて、SCLKのこの次の立ち上がりエッジにより、データがデータ出力レジスタ1402において右シフトされ、したがって、D6内のデータがD7にシフトされ、D5内のデータが136にシフトされ、以下同様となる。ラッチ1410の出力はセレクタ1414に出現し、このセレクタ1414は、ID\_MATCHがアサートされていると仮定すると、データのラッチ状態をバッファ1416に出力する。バッファ1416は、このラッチ状態をデバイス1450aからS00として出力し、このS00は、デイジーチェーンカスケードにおける次のデバイス1450bのSI入力部(SI1)に供給される。その間に、OPEがアサートされた後の最初のクロックの立ち上がりエッジにおいて、OPEの状態がまたラッチ1412でラッチされる。ラッチ1412の出力はバッファ1418に転送され、バッファ1418はOPEのラッチ状態をデバイス1450aからOPEQ(OPEQ0)として出力し、OPEQはデイジーチェーンカスケードにおける次のデバイス1450bのOPE入力部(OPE1)に供給される。この手順が、ビットD6からD0に対して繰り返される。

【0081】

本発明について、その好ましい実施形態に関連して具体的に示し説明してきたが、当業者であれば、形式および細部における様々な変更が、添付の特許請求の範囲に包含される本発明の趣旨から逸脱することなく、当技術分野においてなされうることが理解されよう。

【図面の簡単な説明】

【0082】

【図1】複数のシングルポートデバイスを備える例示的なデバイス構成のブロック図であり、これらのシングルポートデバイスはシリアルデイジーチェーンカスケード配列で構成されている。

10

20

30

40

50

【図2】複数のシングルポートデバイスを備える例示的なデバイス構成のブロック図であり、これらのシングルポートデバイスは、カスケード接続されたクロックを有するシリアルディジーチェーンカスケード配列で構成されている。

【図3】複数のデュアルポートデバイスを備える例示的なデバイス構成のブロック図であり、これらのデュアルポートデバイスはシリアルディジーチェーンカスケード配列で構成されている。

【図4】複数のシングルポートデバイスを備える例示的なデバイス構成のブロック図であり、これらのシングルポートデバイスは、様々なイネーブル信号に対する入力部および出力部を有するシリアルディジーチェーン配列で構成されている。

【図5】デュアルポートデバイスを備える例示的なデバイス構成のブロック図であり、これらのデュアルポートデバイスは、様々なイネーブル信号に対する入力部および出力部を有するシリアルディジーチェーン配列で構成されている。

【図6】多数のパラレル入力部および多数のパラレル出力部を有する複数のデバイスを備える例示的なデバイス構成のブロック図であり、これらのデバイスはシリアルディジーチェーンカスケード配列で構成されている。

【図7】読み取り動作に関するタイミングを示すタイミング図であり、この読み取り操作は、単一のデバイスとシリアルディジーチェーンカスケード配列で構成された複数のデバイスとで実施されたものである。

【図8】情報に関するタイミングを示すタイミング図であり、この情報は、シリアルディジーチェーンカスケード配列で構成されたデバイス間で転送されたものである。

【図9】シングルポートデバイスに対する例示的なシリアル出力制御論理回路の高レベルブロック図である。

【図10】デュアルポートデバイスに対する例示的なシリアル出力制御論理回路の高レベルブロック図である。

【図11】デバイスに対する例示的なシリアル出力制御論理回路の詳細なブロック図である。

【図12】デバイスの例示的な構成のブロック図であり、これらのデバイスは、シリアルディジーチェーンカスケード配列で構成されており、例示的なシリアル出力制御論理回路を具備している。

【図13】例示的なシリアル出力制御論理回路を備えるデバイスの入力および出力に関するタイミングを示すタイミング図である。

【図14】例示的なシリアル出力制御論理回路のブロック図であり、このシリアル出力制御論理回路は、あるデイジーチェーンカスケードにおける第1のデバイスに具備されたメモリからそのデイジーチェーンカスケードにおける第2のデバイスにデータを転送するために使用しうるものである。

【図15】例示的なシリアル出力制御論理回路を使用して、あるデイジーチェーンカスケードにおける第1のデバイスのメモリに含まれたデータを、そのデイジーチェーンカスケードにおける第2のデバイスに転送することに関するタイミングを示すタイミング図である。

【符号の説明】

【0083】

- 110 デバイス

- 210 デバイス

- 310 デバイス

- 410 デバイス

- 510 デバイス

- 610 デバイス

- 902 IPE用の入力バッファ

- 904 SI用の入力バッファ

- 906 OPE用の入力バッファ

10

20

30

40

50

908 入力ラッチ制御部

910 シリアルパラレルレジスタ

912 出力ラッチ制御部

914 データレジスタ

916 アドレスレジスタ

918 コマンドインタプリタ

920 セレクタ

924 ページバッファ

926 論理和ゲート

928 出力バッファ

930 セレクタ

10

【図1】

FIG. 1

【図2】

FIG. 2

【 図 3 】

FIG. 3

【 図 4 】

FIG. 4

【 5 】

FIG. 5

【 四 6 】

FIG. 6

【図 7】

FIG. 7

【図 8】

FIG. 8

【図 9】

FIG. 9

【図 10】

FIG. 10

【 図 1 1 】

FIG. 11

【 図 1 2 】

FIG. 12

【 図 1 3 】

FIG. 13

【 図 1 4 】

FIG. 14

【図 15】

FIG. 15

## 【国際調査報告】

| INTERNATIONAL SEARCH REPORT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                     | International application No.<br>PCT/CA2006/001607                                                                                                                                                                                           |                                           |                                                                                    |                                                                                                                                                                                                 |     |                                                                                                                                                     |                                                                                                                                                                          |     |                                                                     |                                                                                                                                                                                                                                              |     |                                                                            |                                                                          |     |                                                                    |                                           |     |  |  |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------|------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|---------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|----------------------------------------------------------------------------|--------------------------------------------------------------------------|-----|--------------------------------------------------------------------|-------------------------------------------|-----|--|--|

| <p><b>A. CLASSIFICATION OF SUBJECT MATTER</b><br/>           IPC: <b>GIIC 7/10</b> (2006.01), <b>GIIC 11/4197</b> (2006.01), <b>GIIC 16/06</b> (2006.01)<br/>           According to International Patent Classification (IPC) or to both national classification and IPC</p>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                     |                                                                                                                                                                                                                                              |                                           |                                                                                    |                                                                                                                                                                                                 |     |                                                                                                                                                     |                                                                                                                                                                          |     |                                                                     |                                                                                                                                                                                                                                              |     |                                                                            |                                                                          |     |                                                                    |                                           |     |  |  |

| <p><b>B. FIELDS SEARCHED</b><br/>           Minimum documentation searched (classification system followed by classification symbols)<br/>           IPC: G11C</p>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                     |                                                                                                                                                                                                                                              |                                           |                                                                                    |                                                                                                                                                                                                 |     |                                                                                                                                                     |                                                                                                                                                                          |     |                                                                     |                                                                                                                                                                                                                                              |     |                                                                            |                                                                          |     |                                                                    |                                           |     |  |  |

| Documentation searched other than minimum documentation to the extent that such documents are included in the fields searched                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                     |                                                                                                                                                                                                                                              |                                           |                                                                                    |                                                                                                                                                                                                 |     |                                                                                                                                                     |                                                                                                                                                                          |     |                                                                     |                                                                                                                                                                                                                                              |     |                                                                            |                                                                          |     |                                                                    |                                           |     |  |  |

| Electronic database(s) consulted during the international search (name of database(s) and, where practicable, search terms used)<br>Canadian Patent Database, Delphion, Espacenet.<br>Searched terms used: memory, flash, cascade, plurality, chain                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                     |                                                                                                                                                                                                                                              |                                           |                                                                                    |                                                                                                                                                                                                 |     |                                                                                                                                                     |                                                                                                                                                                          |     |                                                                     |                                                                                                                                                                                                                                              |     |                                                                            |                                                                          |     |                                                                    |                                           |     |  |  |

| <p><b>C. DOCUMENTS CONSIDERED TO BE RELEVANT</b></p> <table border="1"> <thead> <tr> <th>Category*</th> <th>Citation of document, with indication, where appropriate, of the relevant passages</th> <th>Relevant to claim No.</th> </tr> </thead> <tbody> <tr> <td>X</td> <td>US 4,796,231, 3 January 1989, Pinkham.<br/>           *see figure 1; column 4: lines 59-68; column 5: lines 11-19, and 31-48; column 6: lines 38-48, and 59-67.</td> <td>1-6, 14-19, 26-31, 34, and 35</td> </tr> <tr> <td>A</td> <td>US 6,763,426 B1, 13 July 2004, James et al.<br/>           *see entire document</td> <td>1-35, 58-72, and 91-97</td> </tr> <tr> <td>A</td> <td>US 6,317,350 B1, 13 November 2001, Pereira et al.<br/>           * see entire document</td> <td>1-35, 58-72, and 91-97</td> </tr> <tr> <td>A</td> <td>US 6,091,660, 18 July 2000, Sasaki et al.<br/>           * see entire document</td> <td>1-35, 58-72, and 91-97</td> </tr> </tbody> </table>                                                                                                                                |                                                                                                                                                     |                                                                                                                                                                                                                                              | Category*                                 | Citation of document, with indication, where appropriate, of the relevant passages | Relevant to claim No.                                                                                                                                                                           | X   | US 4,796,231, 3 January 1989, Pinkham.<br>*see figure 1; column 4: lines 59-68; column 5: lines 11-19, and 31-48; column 6: lines 38-48, and 59-67. | 1-6, 14-19, 26-31, 34, and 35                                                                                                                                            | A   | US 6,763,426 B1, 13 July 2004, James et al.<br>*see entire document | 1-35, 58-72, and 91-97                                                                                                                                                                                                                       | A   | US 6,317,350 B1, 13 November 2001, Pereira et al.<br>* see entire document | 1-35, 58-72, and 91-97                                                   | A   | US 6,091,660, 18 July 2000, Sasaki et al.<br>* see entire document | 1-35, 58-72, and 91-97                    |     |  |  |

| Category*                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Citation of document, with indication, where appropriate, of the relevant passages                                                                  | Relevant to claim No.                                                                                                                                                                                                                        |                                           |                                                                                    |                                                                                                                                                                                                 |     |                                                                                                                                                     |                                                                                                                                                                          |     |                                                                     |                                                                                                                                                                                                                                              |     |                                                                            |                                                                          |     |                                                                    |                                           |     |  |  |

| X                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | US 4,796,231, 3 January 1989, Pinkham.<br>*see figure 1; column 4: lines 59-68; column 5: lines 11-19, and 31-48; column 6: lines 38-48, and 59-67. | 1-6, 14-19, 26-31, 34, and 35                                                                                                                                                                                                                |                                           |                                                                                    |                                                                                                                                                                                                 |     |                                                                                                                                                     |                                                                                                                                                                          |     |                                                                     |                                                                                                                                                                                                                                              |     |                                                                            |                                                                          |     |                                                                    |                                           |     |  |  |

| A                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | US 6,763,426 B1, 13 July 2004, James et al.<br>*see entire document                                                                                 | 1-35, 58-72, and 91-97                                                                                                                                                                                                                       |                                           |                                                                                    |                                                                                                                                                                                                 |     |                                                                                                                                                     |                                                                                                                                                                          |     |                                                                     |                                                                                                                                                                                                                                              |     |                                                                            |                                                                          |     |                                                                    |                                           |     |  |  |

| A                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | US 6,317,350 B1, 13 November 2001, Pereira et al.<br>* see entire document                                                                          | 1-35, 58-72, and 91-97                                                                                                                                                                                                                       |                                           |                                                                                    |                                                                                                                                                                                                 |     |                                                                                                                                                     |                                                                                                                                                                          |     |                                                                     |                                                                                                                                                                                                                                              |     |                                                                            |                                                                          |     |                                                                    |                                           |     |  |  |