(10) **DE 10 2014 019 794 B4 2024.10.24**

(12)

## Patentschrift

(21) Aktenzeichen: **10 2014 019 794.8**

(51) Int Cl.: **H01L 27/12 (2006.01)**

(22) Anmelddatag: **12.05.2014**

**H01L 21/84 (2006.01)**

(45) Veröffentlichungstag

der Patenterteilung: **24.10.2024**

**H01L 29/786 (2006.01)**

**H01L 29/24 (2006.01)**

Innerhalb von neun Monaten nach Veröffentlichung der Patenterteilung kann nach § 59 Patentgesetz gegen das Patent Einspruch erhoben werden. Der Einspruch ist schriftlich zu erklären und zu begründen. Innerhalb der Einspruchsfrist ist eine Einspruchsgebühr in Höhe von 200 Euro zu entrichten (§ 6 Patentkostengesetz in Verbindung mit der Anlage zu § 2 Abs. 1 Patentkostengesetz).

(30) Unionspriorität:

**2013-106337 20.05.2013 JP**

(72) Erfinder:

**Yamazaki, Shunpei, Atsugi-shi, Kanagawa-ken, JP; Sakakura, Masayuki, Atsugi-shi, Kanagawa-ken, JP; Suzawa, Hideomi, Atsugi-shi, Kanagawa-ken, JP**

(62) Teilung aus:

**10 2014 208 859.3**

(56) Ermittelter Stand der Technik:

|           |                         |           |

|-----------|-------------------------|-----------|

| <b>US</b> | <b>2010 / 0 102 313</b> | <b>A1</b> |

| <b>US</b> | <b>2012 / 0 319 183</b> | <b>A1</b> |

| <b>US</b> | <b>2013 / 0 009 209</b> | <b>A1</b> |

(62) Teilung in:

**10 2014 020 179.1**

(73) Patentinhaber:

**SEMICONDUCTOR ENERGY LABORATORY CO., LTD., Atsugi-shi, Kanagawa-ken, JP**

(74) Vertreter:

**Grünecker Patent- und Rechtsanwälte PartG mbB,

80802 München, DE**

(54) Bezeichnung: **Halbleitervorrichtung**

(57) Hauptanspruch: Halbleitervorrichtung, die umfasst:

eine erste Oxidhalbleiterschicht (131) über einer isolierenden Schicht (120);

eine zweite Oxidhalbleiterschicht (132) über der ersten Oxidhalbleiterschicht (131); und

eine dritte Oxidhalbleiterschicht (133) über und in Kontakt mit der isolierenden Schicht (120), der ersten Oxidhalbleiterschicht (131) und der zweiten Oxidhalbleiterschicht (132), wobei die dritte Oxidhalbleiterschicht (133) eine erste Schicht (133a) und eine zweite Schicht (133b) über der ersten Schicht (133a) enthält,

wobei eine Kristallinität in der ersten Schicht (133a) geringer ist als eine Kristallinität in der zweiten Schicht (133b),

wobei die zweite Schicht (133b) eine Ausrichtung bezüglich einer c-Achse aufweist und einen ersten kristallinen Bereich und einen zweiten kristallinen Bereich umfasst, und

wobei, bei einer Querschnitts-Beobachtung der zweiten Schicht (133b), Gitter-Randzonen in der zweiten Schicht (133b) verschiedene Richtungen in dem ersten kristallinen Bereich über der zweiten Oxidhalbleiterschicht (132) und in dem zweiten kristallinen Bereich, der derart ausgebildet ist, dass er einer Seitenfläche der ersten Oxidhalbleiterschicht (131) oder der zweiten Oxidhalbleiterschicht (132) zugewandt ist, aufweisen.

**Beschreibung**

## Hintergrund der Erfindung

## 1. Gebiet der Erfindung

**[0001]** Eine Ausführungsform der vorliegenden Erfindung betrifft eine Halbleitervorrichtung, die einen Oxidhalbleiter enthält.

**[0002]** Es sei angemerkt, dass eine Ausführungsform der vorliegenden Erfindung nicht auf das obige technische Gebiet beschränkt ist. Das technische Gebiet einer Ausführungsform der in dieser Beschreibung und dergleichen offenbarten Erfindung betrifft einen Gegenstand, ein Verfahren oder ein Herstellungsverfahren. Eine Ausführungsform der vorliegenden Erfindung betrifft zusätzlich einen Prozess, eine Maschine, Herstellung oder eine Zusammensetzung der Materie. Beispiele für das technische Gebiet einer Ausführungsform der in dieser Beschreibung offenbarten vorliegenden Erfindung umfassen insbesondere eine Halbleitervorrichtung, eine Anzeigevorrichtung, eine Flüssigkristallanzeigevorrichtung, eine lichtemittierende Vorrichtung, eine Beleuchtungsvorrichtung, eine Energiespeichervorrichtung, eine Speichervorrichtung, ein Ansteuerverfahren für eine von ihnen und ein Herstellungsverfahren für eine von ihnen.

**[0003]** In dieser Beschreibung und dergleichen bedeutet eine Halbleitervorrichtung allgemein eine Vorrichtung, die durch Anwenden von Halbleitereigenschaften arbeiten kann. Ein Transistor und eine Halbleiterschaltung sind Ausführungsformen der Halbleitervorrichtungen. Eine Speichervorrichtung, eine Anzeigevorrichtung oder ein elektronisches Gerät beinhaltet in einigen Fällen eine Halbleitervorrichtung.

## 2. Beschreibung des Standes der Technik

**[0004]** Die Aufmerksamkeit konzentriert sich auf eine Technik zum Herstellen eines Transistors unter Verwendung eines Halbleiterdünffilms, der über einem Substrat mit einer isolierenden Oberfläche ausgebildet ist (auch als Dünnschichttransistor (thin film transistor, TFT) bezeichnet). Der Transistor findet Anwendung für eine breite Palette elektronischer Geräte, wie z. B. eine integrierte Schaltung (integrated circuit, IC) und eine Bildanzeigevorrichtung (Anzeigevorrichtung). Als Material für einen Halbleiterdünffilm, der für einen Transistor anwendbar ist, ist ein Halbleitermaterial auf Silizium-Basis weithin bekannt. Als weiteres Beispiel hat ein Oxidhalbleiter Aufmerksamkeit erregt.

**[0005]** Beispielsweise ist ein Transistor, dessen aktive Schicht einen amorphen Oxidhalbleiter aufweist, der Indium (In), Gallium (Ga) und Zink (Zn) ent-

hält, in der japanischen Offenlegungsschrift JP 2006-165528 A offenbart.

**[0006]** US 2012 / 0 319 183 A1, US 2010 / 0 102 313 A1 und US 2013 / 0 009 209 A1 offenbaren Halbleitervorrichtungen und Verfahren zur Herstellung.

## Zusammenfassung der Erfindung

**[0007]** Die Erfindung stellt eine Halbleitervorrichtung gemäß der unabhängigen Ansprüche 1 und 8 bereit. Vorteilhafte Weiterbildungen sind von den abhängigen Ansprüchen umfasst.

**[0008]** Hohe Integration einer integrierten Schaltung erfordert eine Miniaturisierung eines Transistors. Es ist jedoch bekannt, dass die Miniaturisierung eines Transistors eine Verschlechterung oder Schwankungen der elektrischen Eigenschaften des Transistors verursacht. Dies bedeutet, dass die Miniaturisierung eines Transistors wahrscheinlich die Leistung einer integrierten Schaltung verringert.

**[0009]** Daher ist eine Aufgabe einer Ausführungsform der vorliegenden Erfindung, eine Halbleitervorrichtung, bei der eine Verschlechterung der elektrischen Eigenschaften, die mit der Miniaturisierung des Transistors deutlicher wird, unterdrückt werden kann, bereitzustellen. Eine weitere Aufgabe ist, eine Halbleitervorrichtung mit einer Struktur, mit der eine Verringerung der Leistung infolge der Miniaturisierung unterdrückt werden kann, bereitzustellen. Eine weitere Aufgabe ist, eine Halbleitervorrichtung mit einem hohen Grad der Integration bereitzustellen. Eine weitere Aufgabe ist, eine Halbleitervorrichtung, bei der eine Verschlechterung der Durchlassstrom-Eigenschaften (on-state current characteristics) verringert wird, bereitzustellen. Eine weitere Aufgabe ist, eine Halbleitervorrichtung mit niedrigem Leistungsverbrauch bereitzustellen. Eine weitere Aufgabe ist, eine Halbleitervorrichtung mit hoher Zuverlässigkeit bereitzustellen. Eine weitere Aufgabe ist, eine Halbleitervorrichtung, die Daten halten kann, auch wenn die Leistungsversorgung beendet wird, bereitzustellen. Eine weitere Aufgabe ist, eine neuartige Halbleitervorrichtung bereitzustellen.

**[0010]** Es sei angemerkt, dass die Beschreibungen dieser Aufgaben dem Vorhandensein weiterer Aufgaben nicht im Wege stehen. Es sei angemerkt, dass es bei einer Ausführungsform der vorliegenden Erfindung unnötig ist, alle Aufgaben zu erfüllen. Weitere Aufgaben werden ersichtlich aus der Erläuterung der Beschreibung, der Zeichnungen, der Patentansprüche und dergleichen und können davon abgeleitet werden.

**[0011]** Eine Ausführungsform der vorliegenden Erfindung betrifft eine Halbleitervorrichtung mit einem Stapel, der Oxidhalbleiterschichten umfasst.

**[0012]** Eine Ausführungsform der vorliegenden Erfindung ist eine Halbleitervorrichtung, die das Folgende über einer isolierenden Oberfläche beinhaltet: einen Stapel, in dem eine erste Oxidhalbleiterschicht und eine zweite Oxidhalbleiterschicht aufeinander ausgebildet sind; und eine dritte Oxidhalbleiterschicht. Die dritte Oxidhalbleiterschicht bedeckt einen Teil einer ersten Seitenfläche, einen Teil einer nach oben weisenden Oberfläche und einen Teil einer zweiten Seitenfläche, die der ersten Seitenfläche des Staps entgegengesetzt liegt. Die dritte Oxidhalbleiterschicht umfasst eine erste Schicht in Kontakt mit dem Stapel und eine zweite Schicht über der ersten Schicht. Die erste Schicht umfasst eine mikrokristalline Schicht, und die zweite Schicht umfasst eine kristalline Schicht, bei der c-Achsen in einer Richtung senkrecht zu einer Oberfläche der ersten Schicht ausgerichtet sind.

**[0013]** Eine weitere Ausführungsform der vorliegenden Erfindung ist eine Halbleitervorrichtung, die das Folgende über einer isolierenden Oberfläche beinhaltet: einen Stapel, in dem eine erste Oxidhalbleiterschicht und eine zweite Oxidhalbleiterschicht aufeinander ausgebildet sind; eine Source-Elektrodenschicht und eine Drain-Elektrodenschicht, die jeweils teilweise in Kontakt mit dem Stapel stehen; eine dritte Oxidhalbleiterschicht, die teilweise in Kontakt mit der isolierenden Oberfläche, dem Stapel, der Source-Elektrodenschicht und der Drain-Elektrodenschicht steht; einen Gate-Isolierfilm über der dritten Oxidhalbleiterschicht; eine Gate-Elektrodenschicht über dem Gate-Isolierfilm; und eine isolierende Schicht über der Source-Elektrodenschicht, der Drain-Elektrodenschicht und der Gate-Elektrodenschicht. Die dritte Oxidhalbleiterschicht umfasst eine erste Schicht in Kontakt mit dem Stapel und eine zweite Schicht über der ersten Schicht. Die erste Schicht umfasst eine mikrokristalline Schicht, und die zweite Schicht umfasst eine kristalline Schicht, bei der c-Achsen in einer Richtung senkrecht zu einer Oberfläche der ersten Schicht ausgerichtet sind.

**[0014]** Es sei angemerkt, dass Ordnungszahlen, wie z. B. „erstes“ und „zweites“, in dieser Beschreibung und dergleichen verwendet werden, um eine Verwechslung zwischen Komponenten zu vermeiden, und dass sie die Komponenten nicht zahlenmäßig beschränken.

**[0015]** Die erste Oxidhalbleiterschicht umfasst vorzugsweise eine kristalline Schicht, bei der c-Achsen in einer Richtung senkrecht zu der isolierenden Oberfläche ausgerichtet sind. Die zweite Oxidhalbleiterschicht umfasst vorzugsweise eine kristalline

Schicht, bei der c-Achsen in einer Richtung senkrecht zu einer nach oben weisenden Oberfläche der ersten Oxidhalbleiterschicht ausgerichtet sind.

**[0016]** Des Weiteren ist eine Oberfläche der zweiten Oxidhalbleiterschicht vorzugsweise in einem Bereich gekrümmmt, in dem der Stapel in Kontakt mit der dritten Oxidhalbleiterschicht steht.

**[0017]** Des Weiteren liegen ein Minimum des Leitungsbandes der ersten Oxidhalbleiterschicht und ein Minimum des Leitungsbandes der dritten Oxidhalbleiterschicht vorzugsweise um 0,05 eV oder mehr und 2 eV oder weniger näher an einem Vakuumniveau als ein Minimum des Leitungsbandes der zweiten Oxidhalbleiterschicht.

**[0018]** Es ist bevorzugt, dass die ersten bis dritten Oxidhalbleiterschichten jeweils ein In-M-Zn-Oxid (M ist Al, Ti, Ga, Y, Zr, La, Ce, Nd oder Hf) enthalten und dass ein Atomverhältnis von M zu In in jeder der ersten und dritten Oxidhalbleiterschichten höher ist als ein Atomverhältnis von M zu In in der zweiten Oxidhalbleiterschicht.

**[0019]** Einer Ausführungsform der vorliegenden Erfindung entsprechend kann eine der folgenden Wirkungen erzielt werden: eine Halbleitervorrichtung, bei der eine Verschlechterung der elektrischen Eigenschaften, die mit der Miniaturisierung der Halbleitervorrichtung deutlicher wird, unterdrückt werden kann, bereitzustellen; eine Halbleitervorrichtung, die in einem einfachen Prozess miniaturisiert werden kann, bereitzustellen; eine Halbleitervorrichtung mit einer Struktur, mit der eine Verringerung der Leistung infolge der Miniaturisierung unterdrückt werden kann, bereitzustellen; eine Halbleitervorrichtung mit einem hohen Grad der Integration bereitzustellen; eine Halbleitervorrichtung, bei der eine Verschlechterung der Durchlassstrom-Eigenschaften verringert wird, bereitzustellen; eine Halbleitervorrichtung mit niedrigem Leistungsverbrauch bereitzustellen; eine Halbleitervorrichtung mit hoher Zuverlässigkeit bereitzustellen; eine Halbleitervorrichtung, die Daten halten kann, auch wenn die Leistungsversorgung beendet wird, bereitzustellen; und eine neuartige Halbleitervorrichtung bereitzustellen.

**[0020]** Es sei angemerkt, dass die Beschreibungen dieser Wirkungen dem Vorhandensein weiterer Wirkungen nicht im Wege stehen. Es ist bei einer Ausführungsform der vorliegenden Erfindung unnötig, alle Wirkungen zu erzielen. Weitere Wirkungen werden ersichtlich aus der Erläuterung der Beschreibung, der Zeichnungen, der Patentansprüche und dergleichen und können davon abgeleitet werden.

## Kurze Beschreibung der Zeichnungen

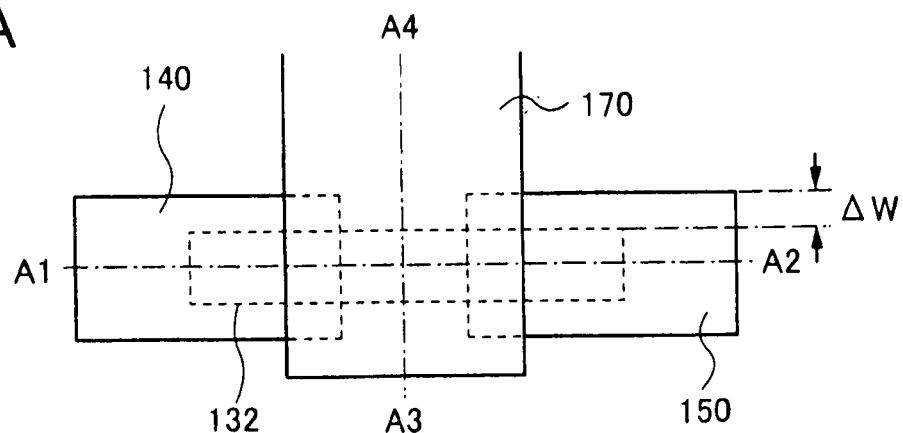

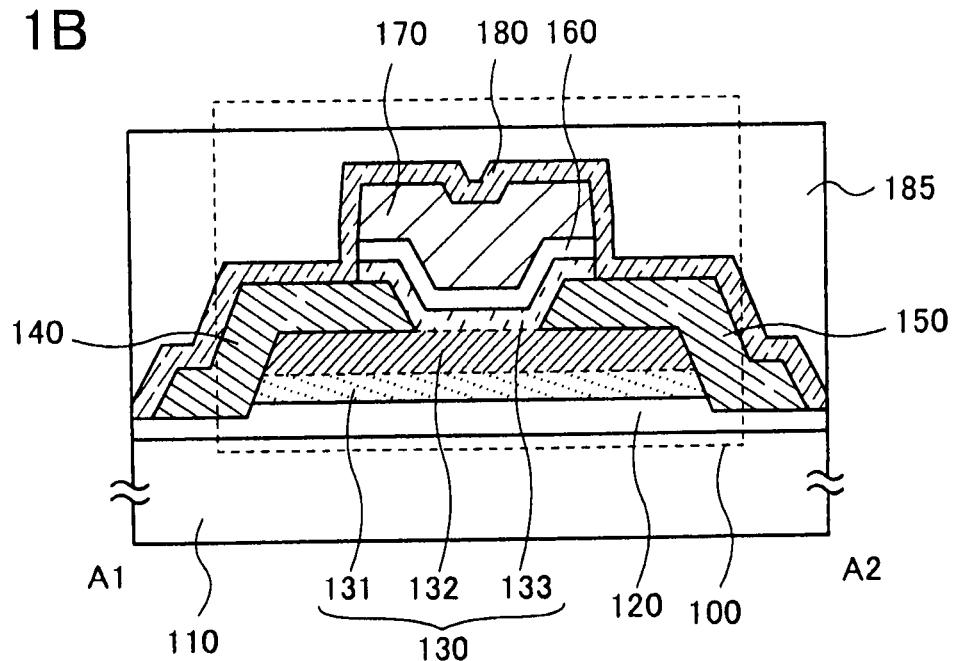

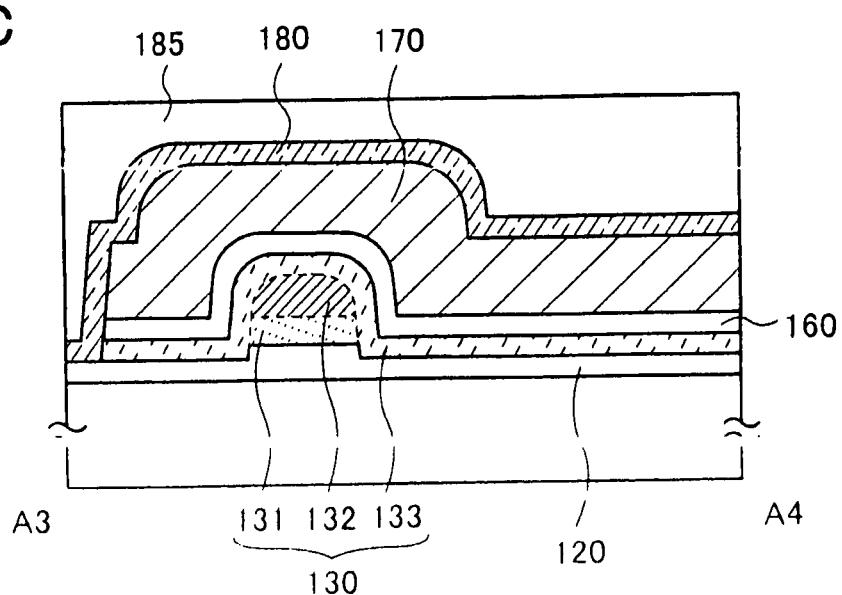

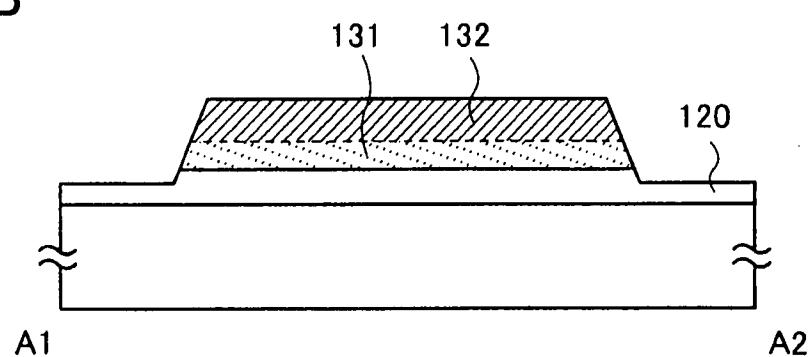

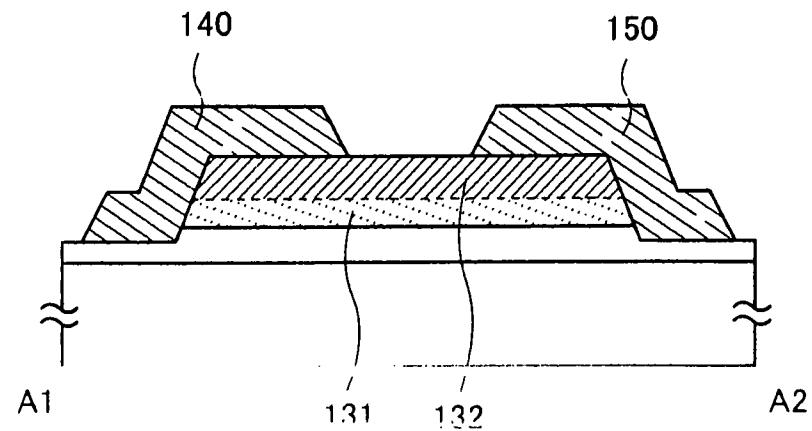

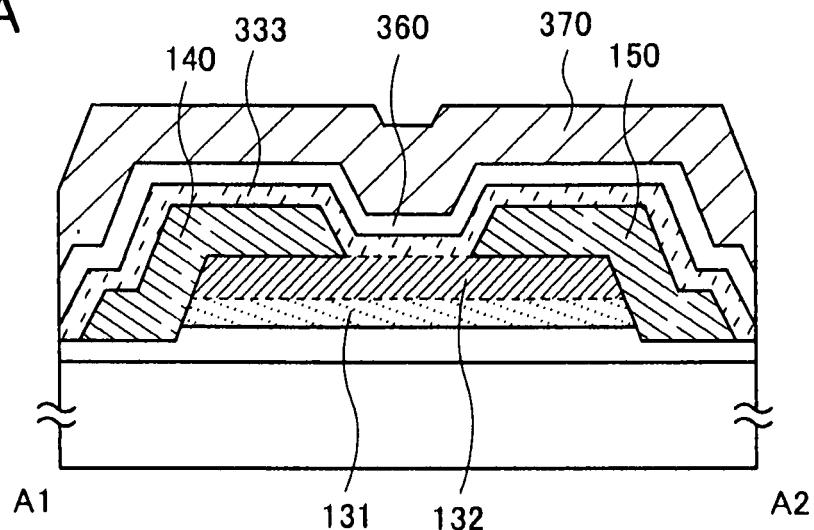

**Fig. 1A bis Fig. 1C** sind eine Draufsicht und Querschnittsansichten eines Transistors.

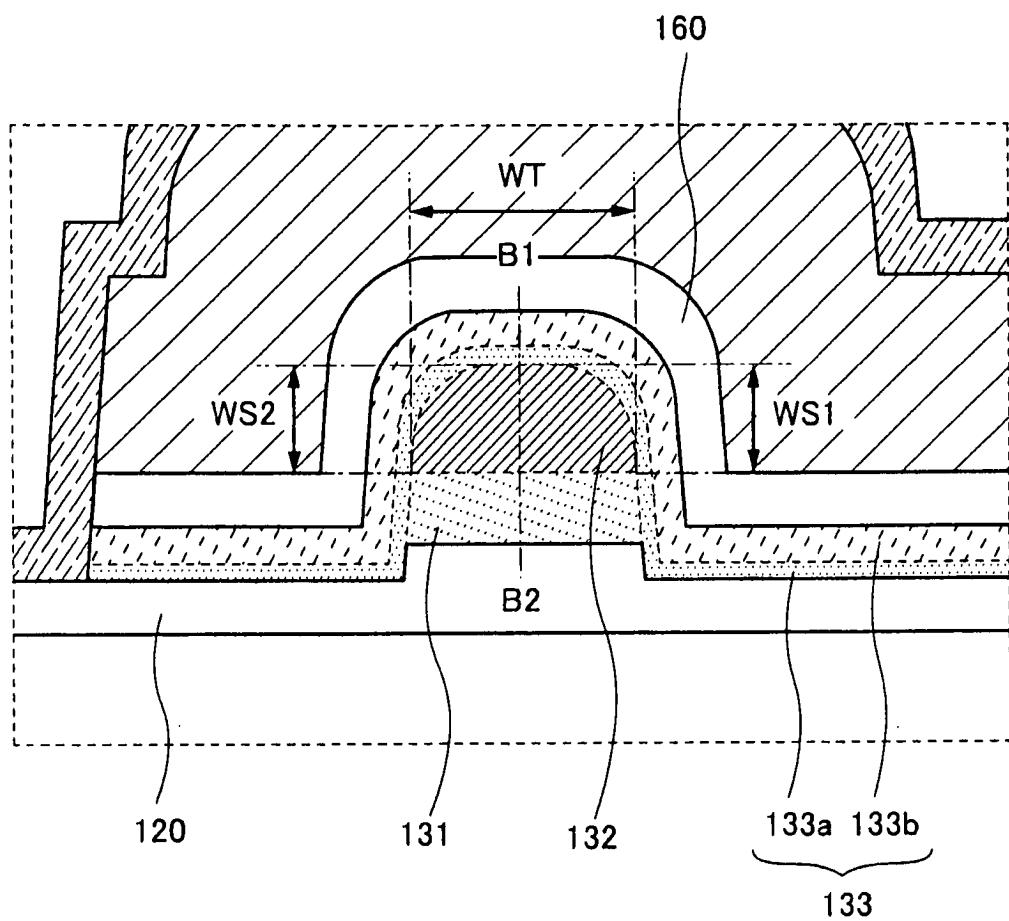

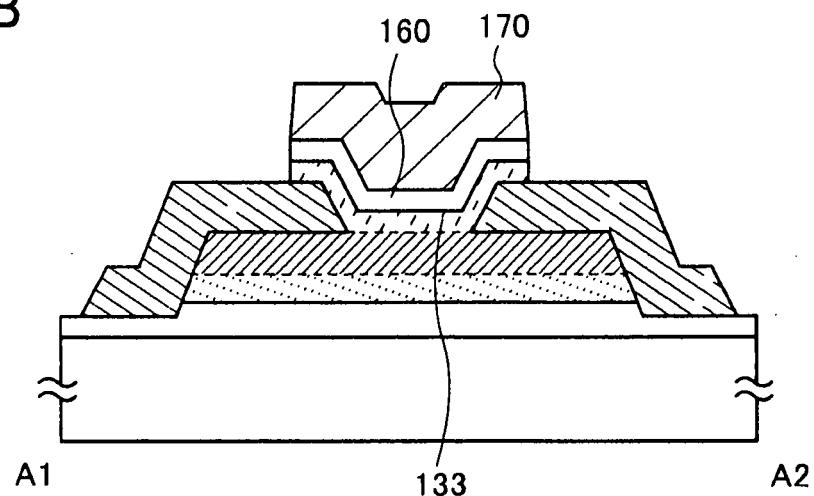

**Fig. 2** ist eine Querschnittsansicht eines Transistors.

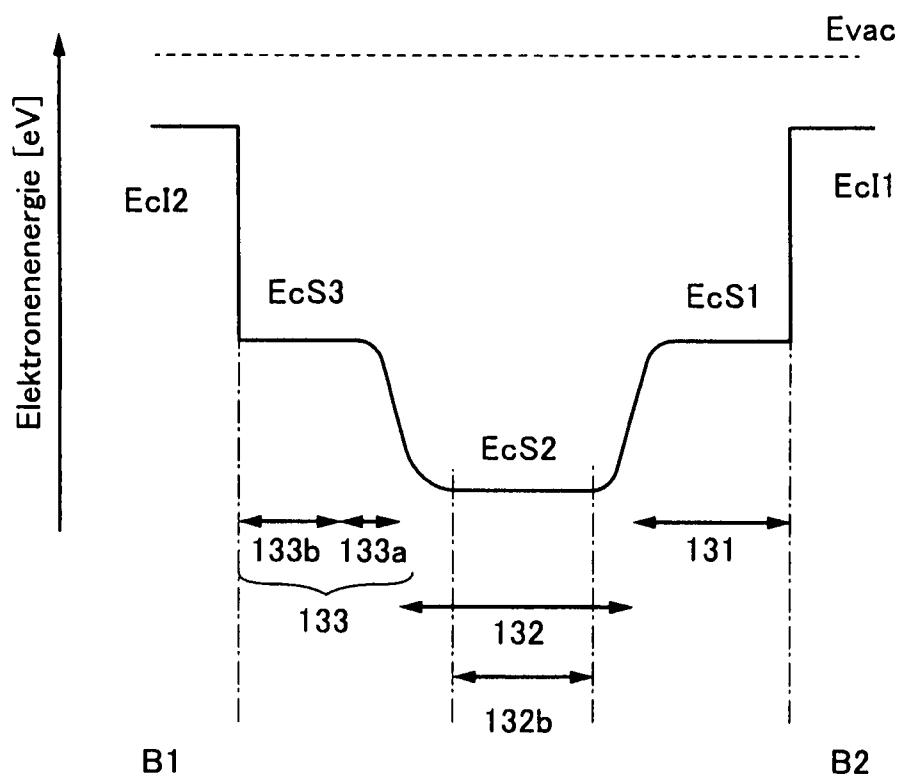

**Fig. 3** zeigt eine Bandstruktur von Oxidhalbleiterschichten.

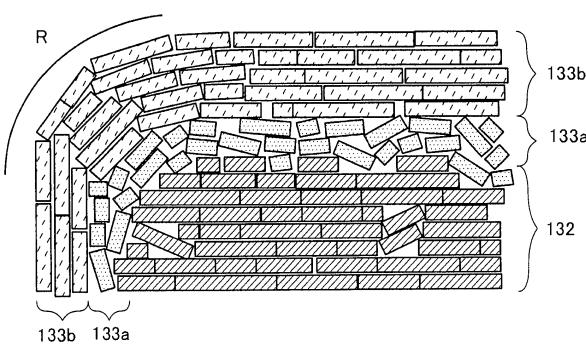

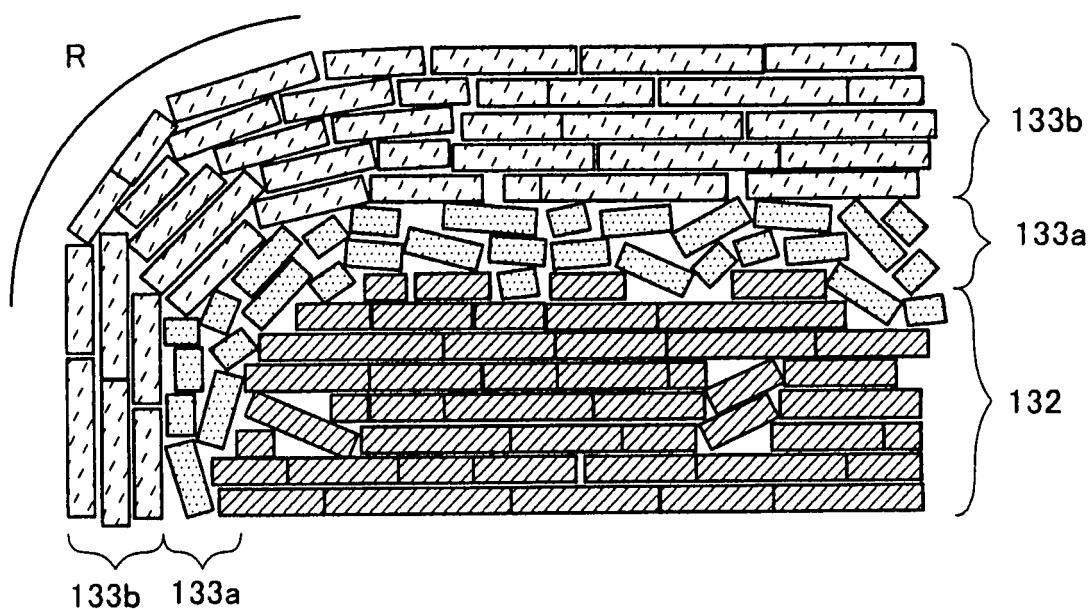

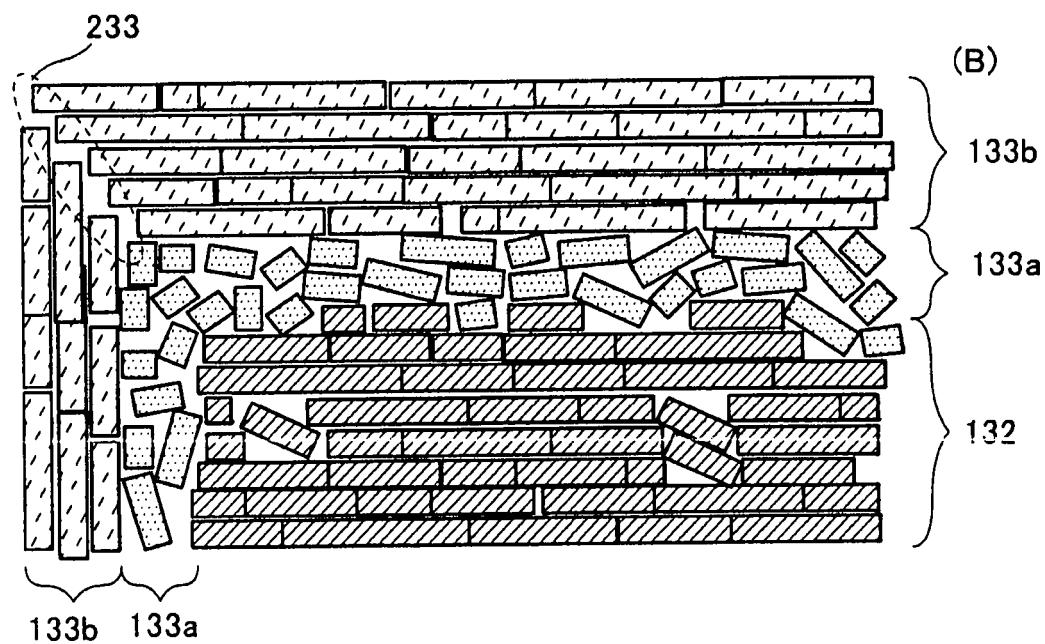

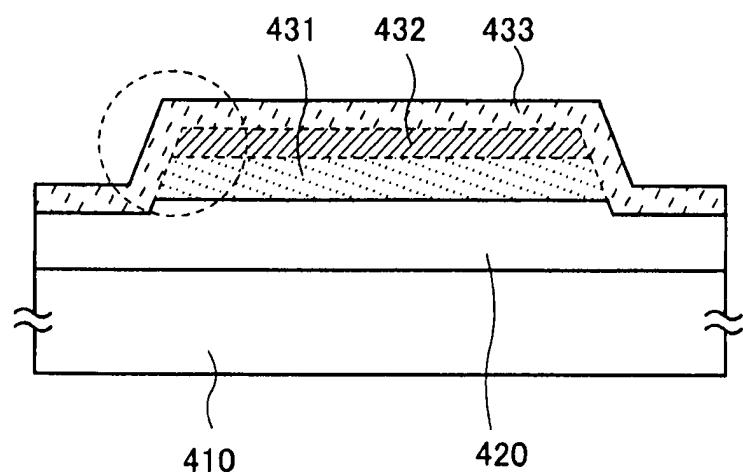

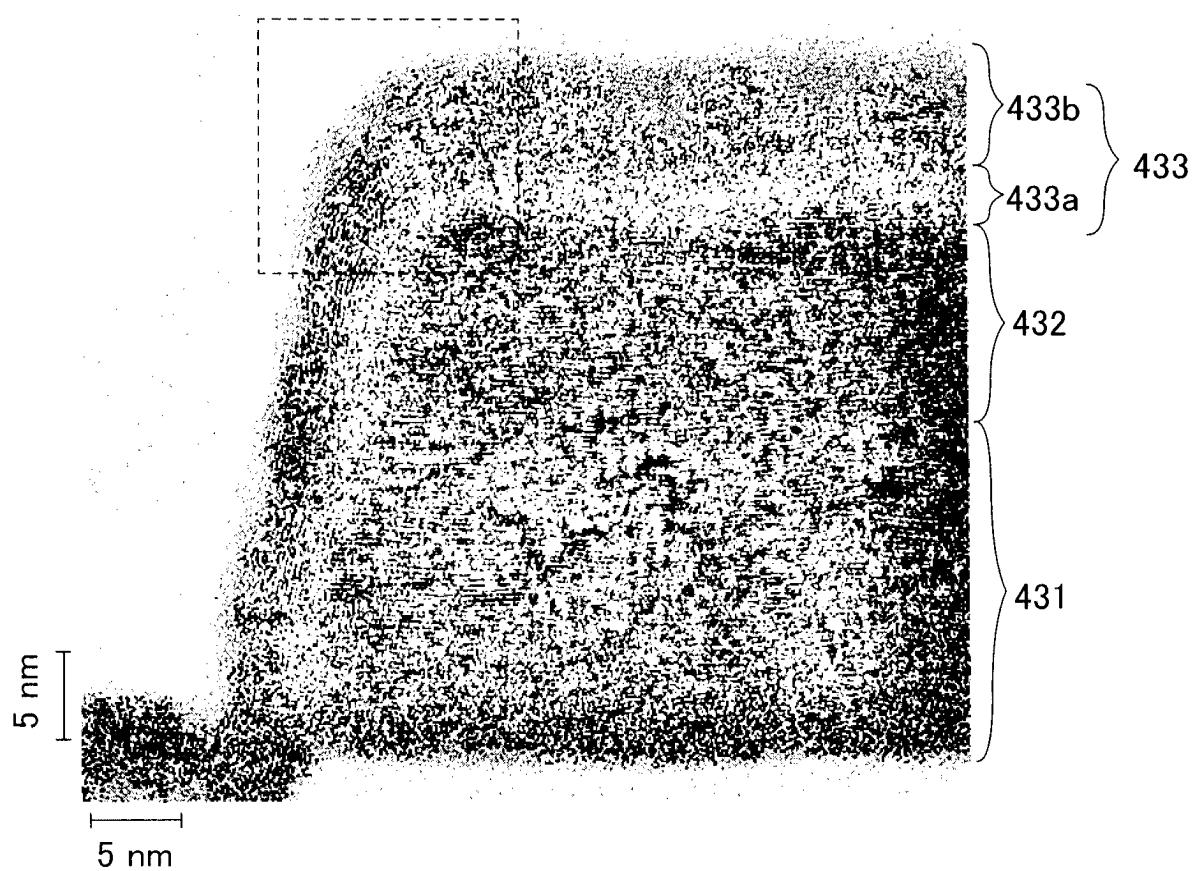

**Fig. 4A** und **Fig. 4B** zeigen jeweils eine Kristallstruktur eines Teils eines Stapels, der Oxidhalbleiterschichten umfasst.

**Fig. 5** ist eine vergrößerte Querschnittsansicht eines Transistors.

**Fig. 6** ist eine Querschnittsansicht eines Transistors.

**Fig. 7A** bis **Fig. 7C** zeigen ein Verfahren zum Herstellen eines Transistors.

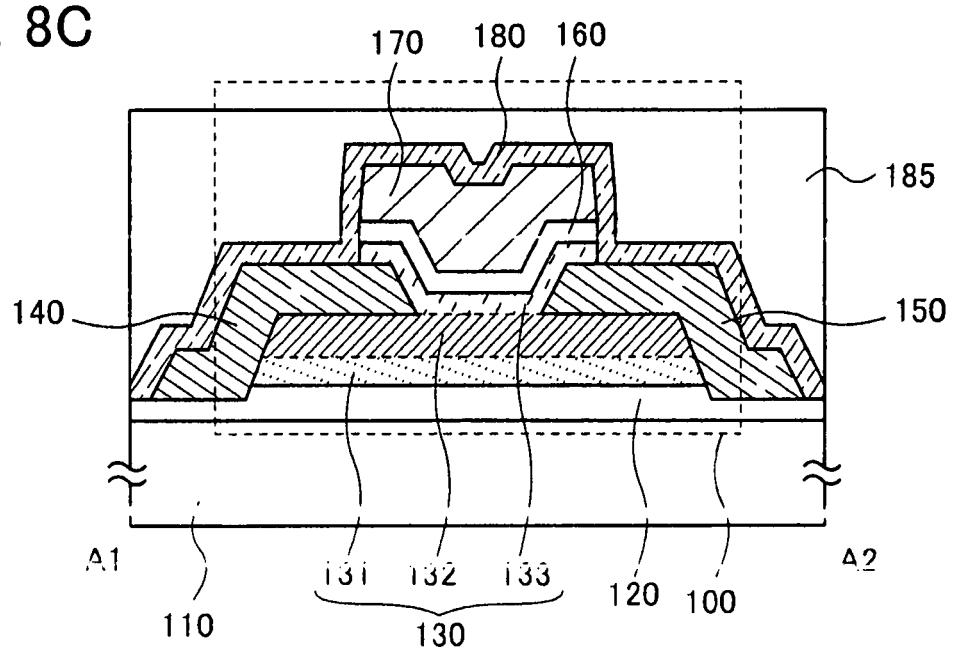

**Fig. 8A** bis **Fig. 8C** zeigen ein Verfahren zum Herstellen eines Transistors.

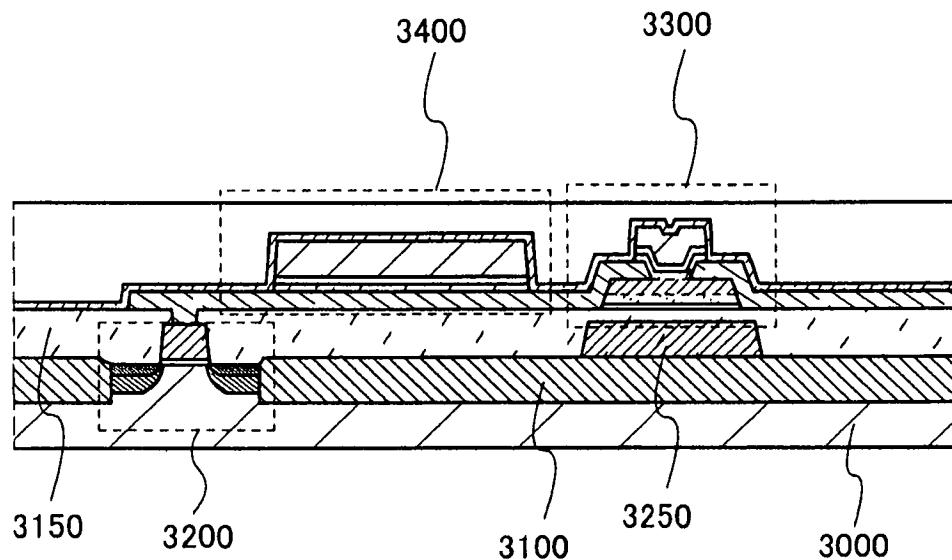

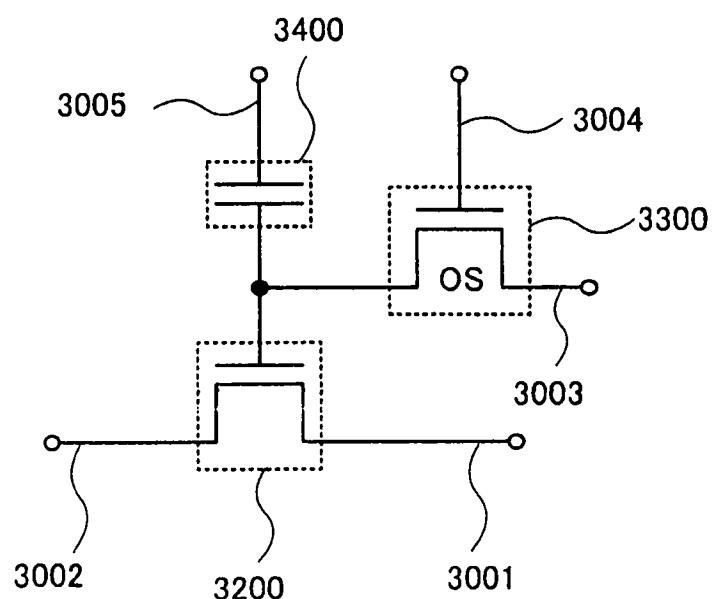

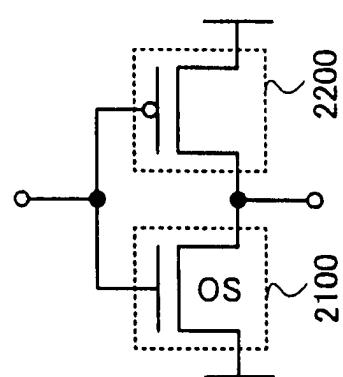

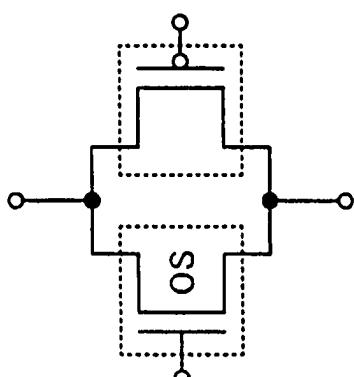

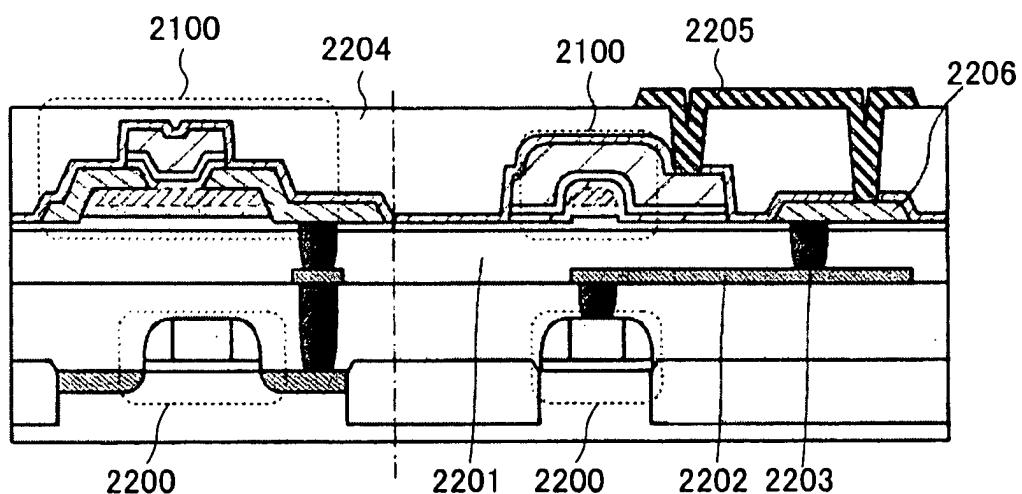

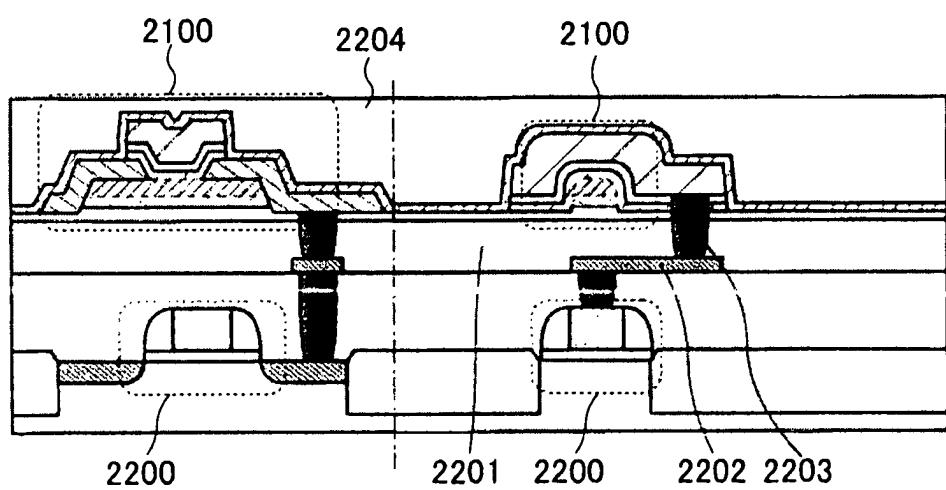

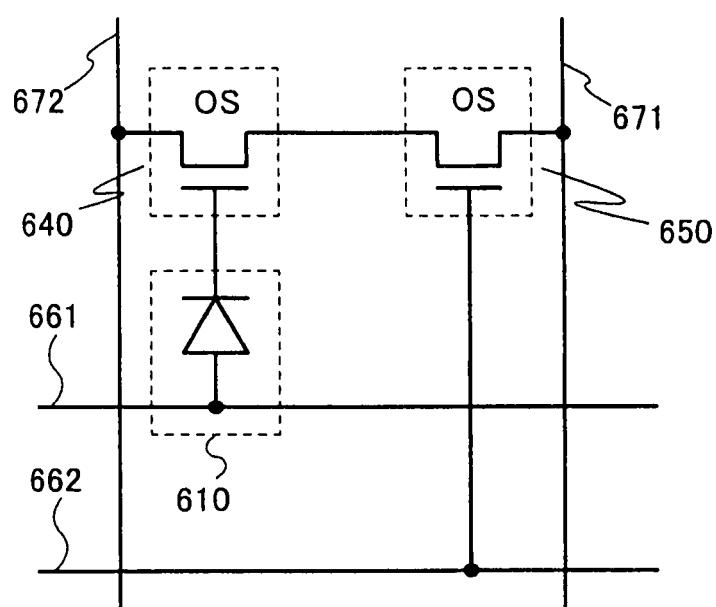

**Fig. 9A** und **Fig. 9B** sind eine Querschnittsansicht und ein Schaltplan einer Halbleitervorrichtung.

**Fig. 10** ist ein Schaltplan einer Halbleitervorrichtung.

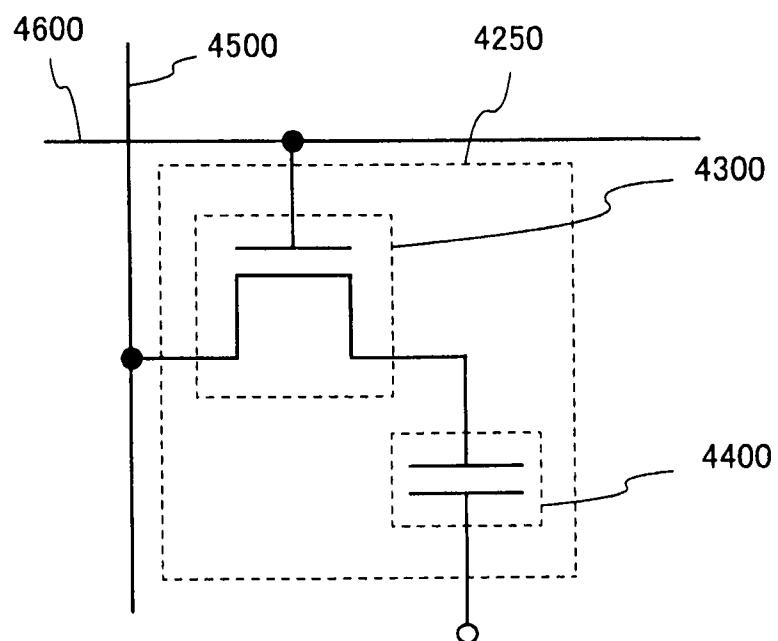

**Fig. 11A** und **Fig. 11B** sind jeweils ein Schaltplan einer Halbleitervorrichtung und **Fig. 11C** und **Fig. 11D** sind jeweils eine Querschnittsansicht einer Halbleitervorrichtung.

**Fig. 12** ist ein Schaltplan einer Halbleitervorrichtung.

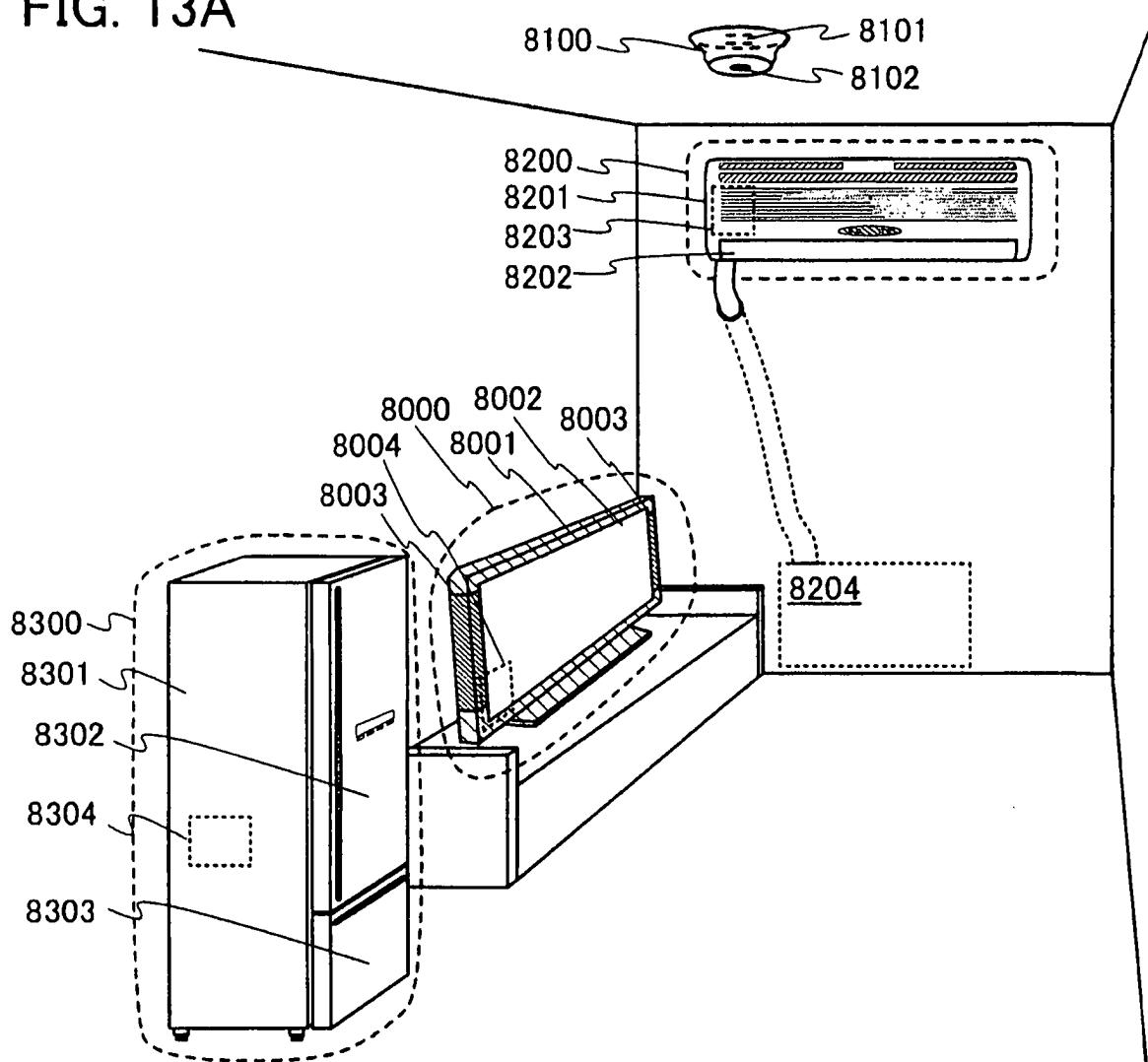

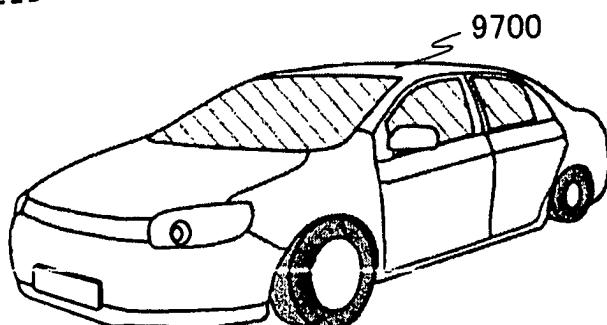

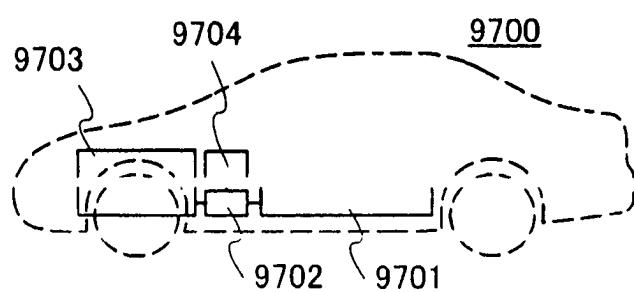

**Fig. 13A** bis **Fig. 13C** zeigen elektronische Geräte, bei denen Halbleitervorrichtungen verwendet werden können.

**Fig. 14** ist eine Querschnittsansicht einer Probe zur Beobachtung einer Stapelstruktur von Oxidhalbleiterschichten.

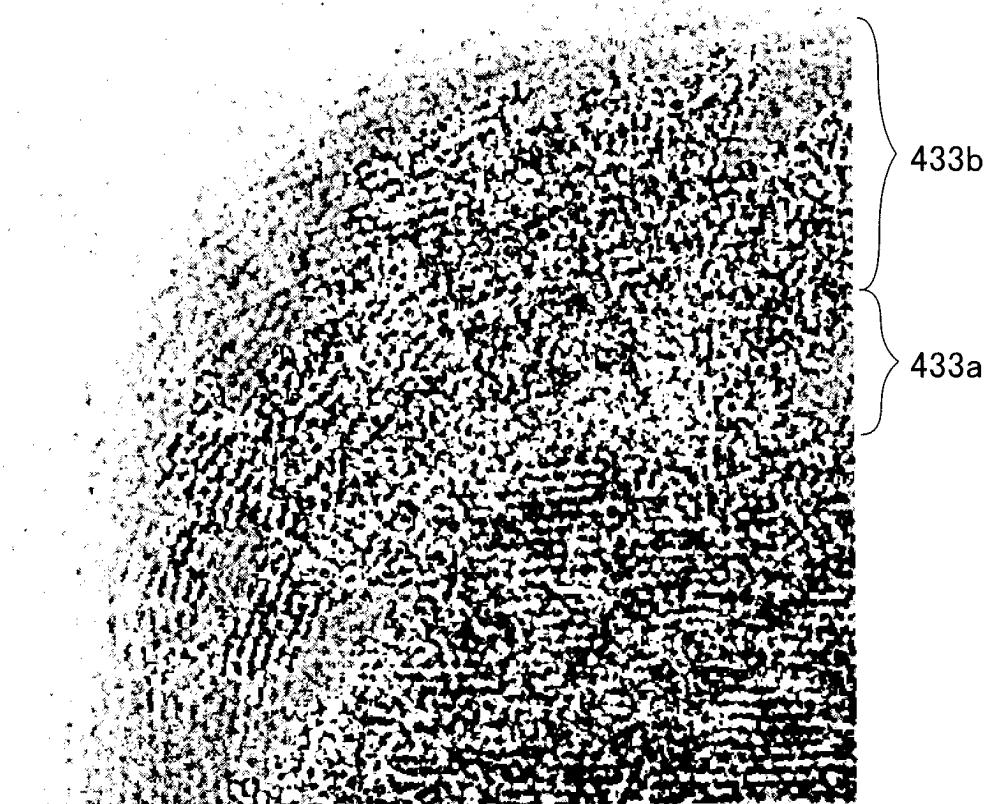

**Fig. 15A** und **Fig. 15B** sind jeweils ein Querschnitts-TEM-Bild (cross-sectional TEM photograph) von Oxidhalbleiterschichten.

## Detaillierte Beschreibung der Erfindung

**[0021]** Ausführungsformen werden unter Bezugnahme auf die Zeichnungen detailliert beschrieben. Es sei angemerkt, dass die vorliegende Erfindung nicht auf die nachfolgende Beschreibung beschränkt ist und dass sich einem Fachmann ohne Weiteres erschließt, dass Modi und Details auf verschiedene Weisen modifiziert werden können, ohne vom Erfindungsgedanken und Schutzbereich der vorliegenden Erfindung abzuweichen. Daher sollte die vorliegende Erfindung nicht auf die Beschreibungen der nachstehenden Ausführungsformen beschränkt sein. Es sei

angemerkt, dass bei Strukturen der im Folgenden beschriebenen vorliegenden Erfindung gleiche Abschnitte oder Abschnitte, die ähnliche Funktionen aufweisen, in verschiedenen Zeichnungen durch gleiche Bezugszeichen gekennzeichnet werden und dass ihre Beschreibung in einigen Fällen weggelassen wird.

**[0022]** Es sei angemerkt, dass dann, wenn in dieser Beschreibung und dergleichen explizit beschrieben wird, dass X und Y verbunden sind, der Fall, in dem X und Y elektrisch verbunden sind, der Fall, in dem X und Y funktional verbunden sind, und der Fall, in dem X und Y direkt verbunden sind, enthalten sind. Hier stellen X und Y jeweils einen Gegenstand (z. B. eine Vorrichtung, ein Bauelement, eine Schaltung, eine Leitung, eine Elektrode, einen Anschluss, einen leitenden Film, eine Schicht oder dergleichen) dar. Folglich ist neben den Verbindungsbeziehungen, die in den Zeichnungen und Texten gezeigt sind, auch eine Verbindungsbeziehung enthalten, ohne auf eine vorbestimmte Verbindungsbeziehung, z. B. eine in den Zeichnungen und Texten gezeigte Verbindungsbeziehung, beschränkt zu sein.

**[0023]** In dem Fall, in dem X und Y elektrisch verbunden sind, können beispielsweise ein oder mehrere Bauelemente (z. B. ein Schalter, ein Transistor, ein Kondensator, eine Spule, ein Widerstand, eine Diode, ein Anzeigeelement, ein lichtemittierendes Element und eine Belastung), die eine elektrische Verbindung zwischen X und Y ermöglichen, zwischen X und Y angeschlossen sein. Es sei angemerkt, dass der Schalter derart gesteuert wird, dass er eingeschaltet oder ausgeschaltet wird. Das heißt, dass der Schalter eine Funktion aufweist, zu bestimmen, ob ein Strom fließt oder nicht, indem er eingeschaltet oder ausgeschaltet wird (indem er in einen Durchlasszustand und einen Sperrzustand versetzt wird). Alternativ weist der Schalter eine Funktion auf, einen Strompfad auszuwählen oder zu ändern.

**[0024]** In dem Fall, in dem X und Y funktional verbunden sind, können beispielsweise eine oder mehrere Schaltungen (z. B. eine logische Schaltung, wie z. B. ein Wechselrichter, eine NAND-Schaltung oder eine NOR-Schaltung; eine Signalwandlerschaltung, wie z. B. eine DA-Wandlerschaltung, eine AD-Wandlerschaltung oder eine Gammakorrekturschaltung; eine Potentialniveau-Wandlerschaltung, wie z. B. eine Leistungsversorgungsschaltung (z. B. eine Aufwärtsschaltung oder eine Abwärtsschaltung) oder eine Niveauverschiebungsschaltung zum Ändern des Potentialniveaus eines Signals; eine Spannungsquelle; eine Stromquelle; ein Schaltkreis; eine Verstärkerschaltung, wie z. B. eine Schaltung, welche die Signalamplitude, die Strommenge oder dergleichen erhöhen kann, ein Operationsverstärker, eine Differentialverstärkerschaltung, eine Source-Folgeschaltung oder eine Pufferschaltung; eine Sig-

nalerzeugungsschaltung; eine Speicherschaltung; und eine Steuerschaltung), die eine funktionale Verbindung zwischen X und Y ermöglichen, zwischen X und Y angeschlossen sein. Es sei angemerkt, dass in dem Fall, in dem beispielsweise ein aus X ausgegebenes Signal auf Y übertragen wird, X und Y funktional verbunden sind, auch wenn eine weitere Schaltung zwischen X und Y liegt.

**[0025]** Es sei angemerkt, dass dann, wenn explizit beschrieben wird, dass X und Y verbunden sind, der Fall, in dem X und Y elektrisch verbunden sind (d. h. der Fall, in dem X und Y verbunden sind, wobei ein weiteres Bauelement oder eine weitere Schaltung dazwischen liegt), der Fall, in dem X und Y funktional verbunden sind (d. h. der Fall, in dem X und Y funktional verbunden sind, wobei eine weitere Schaltung dazwischen liegt), und der Fall, in dem X und Y direkt verbunden sind (d. h. der Fall, in dem X und Y verbunden sind, wobei kein weiteres Bauelement oder keine weitere Schaltung dazwischen liegt), eingeschlossen sind. Das heißt, dass dann, wenn explizit beschrieben wird, dass „X und Y elektrisch verbunden sind“, die Beschreibung gleich dem Fall ist, in dem lediglich explizit beschrieben wird, dass „X und Y verbunden sind“.

**[0026]** Selbst wenn unabhängige Komponenten in einem Schaltplan elektrisch miteinander verbunden sind, weist eine Komponente in einigen Fällen Funktionen einer Vielzahl von Komponenten auf. Wenn zum Beispiel ein Teil einer Leitung auch als Elektrode dient, dient ein leitender Film als Leitung und als Elektrode. Folglich beinhaltet die Kategorie „elektrische Verbindung“ in dieser Beschreibung einen solchen Fall, in dem ein leitender Film Funktionen einer Vielzahl von Komponenten aufweist.

**[0027]** Es sei angemerkt, dass beispielsweise der Fall, in dem ein Source-Anschluss (oder ein erster Anschluss oder dergleichen) eines Transistors über (oder nicht über) Z1 elektrisch mit X verbunden ist und ein Drain-Anschluss (oder ein zweiter Anschluss oder dergleichen) des Transistors über (oder nicht über) Z2 elektrisch mit Y verbunden ist, oder der Fall, in dem ein Source-Anschluss (oder ein erster Anschluss oder dergleichen) eines Transistors direkt mit einem Teil von Z1 verbunden ist und ein anderer Teil von Z1 direkt mit X verbunden ist, während ein Drain-Anschluss (oder ein zweiter Anschluss oder dergleichen) des Transistors direkt mit einem Teil von Z2 verbunden ist und ein anderer Teil von Z2 direkt mit Y verbunden ist, durch einen der folgenden Ausdrücke dargestellt werden kann.

**[0028]** Die Ausdrücke umfassen beispielsweise „X, Y, ein Source-Anschluss (oder ein erster Anschluss oder dergleichen) eines Transistors und ein Drain-Anschluss (oder ein zweiter Anschluss oder dergleichen) des Transistors sind elektrisch miteinander

verbunden, und X, der Source-Anschluss (oder der erste Anschluss oder dergleichen) des Transistors, der Drain-Anschluss (oder der zweite Anschluss oder dergleichen) des Transistors und Y sind in dieser Reihenfolge elektrisch miteinander verbunden“, „ein Source-Anschluss (oder ein erster Anschluss oder dergleichen) eines Transistors ist elektrisch mit X verbunden, ein Drain-Anschluss (oder ein zweiter Anschluss oder dergleichen) des Transistors ist elektrisch mit Y verbunden, und X, der Source-Anschluss (oder der erste Anschluss oder dergleichen) des Transistors, der Drain-Anschluss (oder der zweite Anschluss oder dergleichen) des Transistors und Y sind in dieser Reihenfolge elektrisch miteinander verbunden“ und „X ist über einen Source-Anschluss (oder einen ersten Anschluss oder dergleichen) und einen Drain-Anschluss (oder einen zweiten Anschluss oder dergleichen) eines Transistors elektrisch mit Y verbunden, und X, der Source-Anschluss (oder der erste Anschluss oder dergleichen) des Transistors, der Drain-Anschluss (oder der zweite Anschluss oder dergleichen) des Transistors und Y sind derart angeordnet, dass sie in dieser Reihenfolge verbunden sind“. Wenn die Reihenfolge der Verbindung bei einer Schaltungskonfiguration durch einen Ausdruck, der den obigen Beispielen ähnlich ist, definiert wird, kann man einen Source-Anschluss (oder einen ersten Anschluss oder dergleichen) und einen Drain-Anschluss (oder einen zweiten Anschluss oder dergleichen) eines Transistors voneinander unterscheiden, um den technischen Einflussbereich zu bestimmen. Es sei angemerkt, dass diese Ausdrücke Beispiele sind und dass es keine Beschränkung auf die Ausdrücke gibt. Hier stellen X, Y, Z1 und Z2 jeweils einen Gegenstand (z. B. eine Vorrichtung, ein Bauelement, eine Schaltung, eine Leitung, eine Elektrode, einen Anschluss, einen leitenden Film, eine Schicht oder dergleichen) dar.

**[0029]** Es sei angemerkt, dass in dieser Beschreibung und dergleichen ein Transistor unter Verwendung eines der verschiedenen Substrate hergestellt werden kann. Die Art eines Substrates ist nicht auf eine gewisse Art beschränkt. Beispiele für das Substrat umfassen ein Halbleitersubstrat (z. B. ein einkristallines Substrat oder ein Siliziumsubstrat), ein SOI-Substrat, ein Glassubstrat, ein Quarzsubstrat, ein Kunststoffsubstrat, ein Metallsubstrat, ein Edelstahlsubstrat, ein Substrat, das eine Edelstahlfolie beinhaltet, ein Wolframsubstrat, ein Substrat, das eine Wolframfolie beinhaltet, ein flexibles Substrat, einen Befestigungsfilm, Papier, das ein Fasermaterial enthält, und einen Basismaterial-Film. Beispiele für ein Glassubstrat umfassen ein Bariumborosilikat-glas-Substrat, ein Aluminiumborosilikatglas-Substrat und ein Kalknatronglas-Substrat. Für ein flexibles Substrat kann beispielsweise ein flexibles Kunstharz, wie z. B. Kunststoff, der durch Polyethylenterephthalat (PET), Polyethylenphthalat (PEN) und Poly-

ethersulfon (PES) gekennzeichnet ist, oder Acryl, verwendet werden. Beispiele für einen Befestigungsfilm umfassen Befestigungsfilme, die unter Verwendung von Polypropylen, Polyester, Polyvinylfluorid, Polyvinylchlorid und dergleichen ausgebildet sind. Beispiele für einen Basisfilm umfassen einen Polyester-Basisfilm, einen Polyamid-Basisfilm, einen Polyimid-Basisfilm, einen anorganischenen durch Ablagerung von Dampf gebildeten Film, Papier und dergleichen. Wenn ein Transistor im Besonderen unter Verwendung eines Halbleitersubstrates, eines einkristallinen Substrates, eines SOI-Substrates oder dergleichen hergestellt wird, kann ein Transistor mit geringen Schwankungen der Eigenschaften, der Größe, der Form oder dergleichen, mit großer Stromversorgungsfähigkeit und mit einer geringen Größe hergestellt werden. Durch Ausbilden einer Schaltung unter Verwendung eines derartigen Transistors kann der Leistungsverbrauch der Schaltung verringert werden oder die Schaltung kann hoch integriert werden.

**[0030]** Alternativ kann ein flexibles Substrat als Substrat verwendet werden, und der Transistor kann direkt auf dem flexiblen Substrat angeordnet werden. Als weitere Alternative kann eine Trennschicht zwischen dem Substrat und dem Transistor angeordnet werden. Die Trennschicht kann verwendet werden, wenn ein Teil oder die gesamte Halbleitervorrichtung über der Trennschicht von dem Substrat getrennt und auf ein weiteres Substrat überführt wird. In einem solchen Fall kann der Transistor auch auf ein Substrat mit niedriger Wärmebeständigkeit oder ein flexibles Substrat überführt werden. Für die vorstehende Trennschicht kann beispielsweise ein Stapel, der anorganische Filme, nämlich einen Wolframfilm und einen Siliziumoxidfilm, umfasst, oder ein organischer Harzfilm, der aus Polyimid oder dergleichen über einem Substrat ausgebildet ist, verwendet werden.

**[0031]** Mit anderen Worten: ein Transistor kann unter Verwendung eines Substrates hergestellt und dann auf ein weiteres Substrat überführt werden. Beispiele für ein Substrat, auf das ein Transistor überführt wird, umfassen zusätzlich zu den oben beschriebenen Substraten, über denen Transistoren hergestellt werden können, ein Papiersubstrat, ein Zellglassubstrat, ein Aramidfilm-Substrat, ein Polyimidfilm-Substrat, ein Steinsubstrat, ein Holzsubstrat, ein Stoffsubstrat (darunter eine Naturfaser (z. B. Seide, Baumwolle oder Hanf), eine Kunstfaser (z. B. Nylon, Polyurethan oder Polyester), eine Regeneratfaser (z. B. Acetat, Cupro, Viskose oder regenerierter Polyester) oder dergleichen), ein Ledersubstrat, ein Gummisubstrat und dergleichen. Unter Verwendung eines derartigen Substrates kann ein Transistor mit ausgezeichneten Eigenschaften, ein Transistor mit niedrigem Leistungsverbrauch oder eine Vorrichtung mit hoher Beständigkeit hergestellt werden, hohe

Wärmebeständigkeit kann bereitgestellt werden, oder es kann eine Verringerung des Gewichts oder der Dicke erzielt werden.

(Ausführungsform 1)

**[0032]** Bei dieser Ausführungsform wird eine Halbleitervorrichtung nach einer Ausführungsform der vorliegenden Erfindung unter Bezugnahme auf Zeichnungen beschrieben.

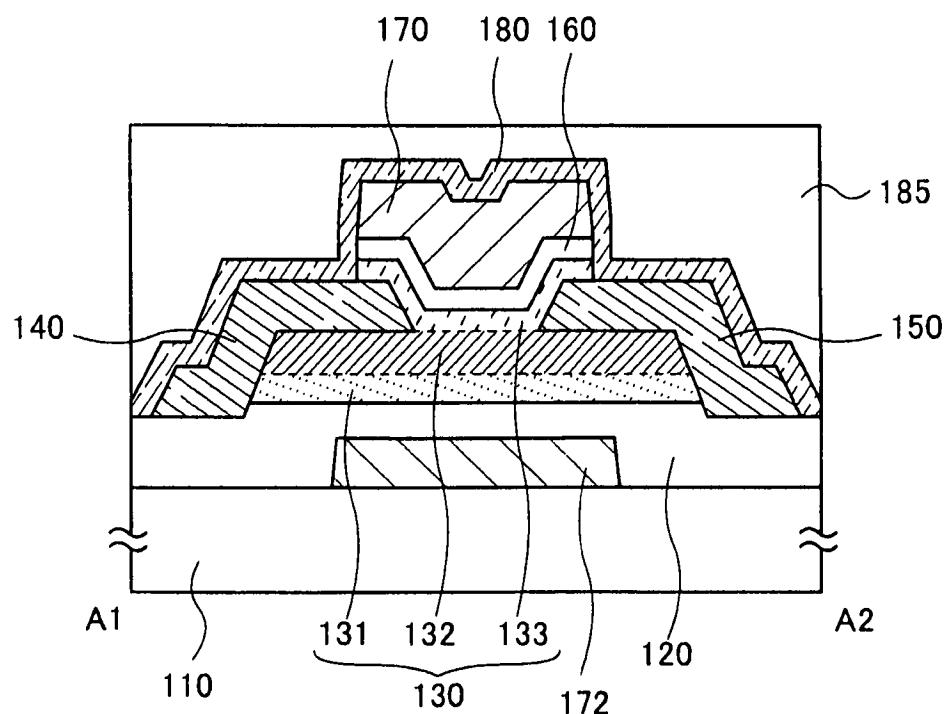

**[0033]** **Fig. 1A** bis **Fig. 1C** sind eine Draufsicht und Querschnittsansichten eines Transistors nach einer Ausführungsform der vorliegenden Erfindung. **Fig. 1A** ist die Draufsicht. **Fig. 1B** stellt einen Querschnitt entlang der Strich-Punkt-Linie A1-A2 in **Fig. 1A** dar. **Fig. 1C** ist eine Querschnittsansicht entlang der Strich-Punkt-Linie A3-A4 in **Fig. 1A**. Es sei angemerkt, dass einige Bestandteile nicht in der Draufsicht in **Fig. 1A** abgebildet sind, um die Zeichnung zu vereinfachen. In einigen Fällen wird die Richtung der Strich-Punkt-Linie A1-A2 als Längsrichtung eines Kanals bezeichnet, und die Richtung der Strich-Punkt-Linie A3-A4 wird als Querrichtung eines Kanals bezeichnet.

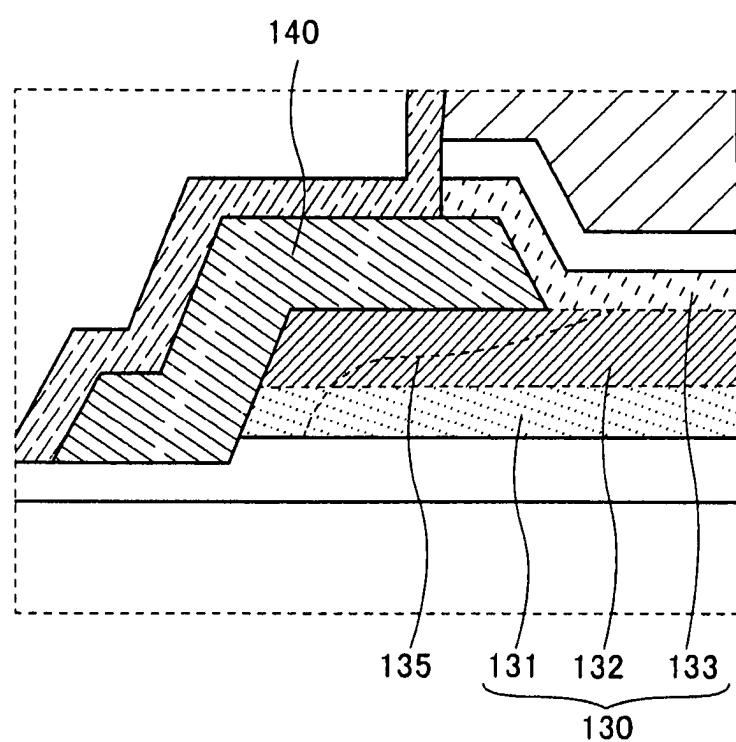

**[0034]** Ein Transistor 100, der in **Fig. 1A** bis **Fig. 1C** und **Fig. 2** gezeigt ist, beinhaltet einen isolierenden Basisfilm 120, der über einem Substrat 110 ausgebildet ist; einen Stapel, in dem eine erste Oxidhalbleiterschicht 131 und ein zweite Oxidhalbleiterschicht 132 in dieser Reihenfolge angeordnet sind und der über dem isolierenden Basisfilm ausgebildet ist; eine Source-Elektrodenschicht 140 und eine Drain-Elektrodenschicht 150, die jeweils in Kontakt mit einem Teil des Stapels stehen; eine dritte Oxidhalbleiterschicht 133, die in Kontakt mit jeweiligen Teilen des isolierenden Basisfilms 120, des Stapels, der Source-Elektrodenschicht 140 und der Drain-Elektrodenschicht 150 steht; einen Gate-Isolierfilm 160, der über der dritten Oxidhalbleiterschicht ausgebildet ist; eine Gate-Elektrodenschicht 170, die über dem Gate-Isolierfilm ausgebildet ist; und eine isolierende Schicht 180, die über der Source-Elektrodenschicht 140, der Drain-Elektrodenschicht 150 und der Gate-Elektrodenschicht 170 ausgebildet ist.

**[0035]** Die erste Oxidhalbleiterschicht 131 umfasst hier vorzugsweise eine kristalline Schicht, bei der c-Achsen in einer Richtung senkrecht zu einer Oberfläche des isolierenden Basisfilms 120 ausgerichtet sind. Die zweite Oxidhalbleiterschicht 132 umfasst vorzugsweise eine kristalline Schicht, bei der c-Achsen in einer Richtung senkrecht zu einer nach oben weisenden Oberfläche der ersten Oxidhalbleiterschicht 131 ausgerichtet sind.

**[0036]** Darüber hinaus ist die dritte Oxidhalbleiterschicht 133 derart ausgebildet, dass sie eine erste Schicht in Kontakt mit dem Stapel und eine zweite

Schicht über der ersten Schicht aufweist. Die erste Schicht umfasst eine mikrokristalline Schicht, und die zweite Schicht umfasst eine kristalline Schicht, bei der c-Achsen in einer Richtung senkrecht zu einer Oberfläche der ersten Schicht ausgerichtet sind.

**[0037]** Ferner kann eine isolierende Schicht 185, die unter Verwendung eines Oxids ausgebildet ist, über der isolierenden Schicht 180 ausgebildet sein. Die isolierende Schicht 185 kann nach Bedarf bereitgestellt sein und eine weitere isolierende Schicht kann darüber angeordnet sein. Die erste Oxidhalbleiterschicht 131, die zweite Oxidhalbleiterschicht 132 und die dritte Oxidhalbleiterschicht 133 werden insgesamt als Oxidhalbleiterschicht 130 bezeichnet.

**[0038]** Es sei angemerkt, dass Funktionen eines „Source-Anschlusses“ und eines „Drain-Anschlusses“ eines Transistors manchmal miteinander ausgetauscht werden, wenn beispielsweise ein Transistor mit der entgegengesetzten Polarität verwendet wird oder wenn die Richtung des Stromflusses beim Betrieb einer Schaltung geändert wird. Deshalb können die Begriffe „Source-Anschluss“ und „Drain-Anschluss“ in dieser Beschreibung verwendet werden, um den Drain-Anschluss bzw. den Source-Anschluss zu bezeichnen.

**[0039]** Zusätzlich ist bei der Source-Elektrodenschicht 140 oder der Drain-Elektrodenschicht 150, welche die Oxidhalbleiterschichten (die erste Oxidhalbleiterschicht 131 und die zweite Oxidhalbleiterschicht 132) des Transistors nach einer Ausführungsform der vorliegenden Erfindung überlappt, der in der Draufsicht in **Fig. 1A** gezeigte Abstand ( $\Delta W$ ) zwischen einem Randbereich der Oxidhalbleiterschicht und einem Randbereich der Source-Elektrodenschicht 140 oder der Drain-Elektrodenschicht 150 auf kürzer als oder gleich 50 nm, bevorzugt kürzer als oder gleich 25 nm eingestellt. Wenn  $\Delta W$  klein eingestellt ist, kann verhindert werden, dass Sauerstoff, der in dem isolierenden Basisfilm 120 enthalten ist, in ein Metallmaterial diffundiert, das der Bestandteil der Source-Elektrodenschicht 140 und der Drain-Elektrodenschicht 150 ist. Demzufolge kann unnötige Abgabe von Sauerstoff, im Besonderen überschüssigem Sauerstoff, der in dem isolierenden Basisfilm 120 enthalten ist, verhindert werden. Als Ergebnis kann Sauerstoff auf effiziente Weise von dem isolierenden Basisfilm 120 zu der Oxidhalbleiterschicht zugeführt werden.

**[0040]** Nun werden die Bestandteile des Transistors 100 nach einer Ausführungsform der vorliegenden Erfindung detailliert beschrieben.

**[0041]** Das Substrat 110 ist nicht auf ein einfaches tragendes Substrat beschränkt und kann ein Substrat sein, bei dem eine weitere Vorrichtung, wie z.

B. ein Transistor, gebildet ist. In diesem Fall kann mindestens eine der Gate-Elektrodenschicht 170, der Source-Elektrodenschicht 140 und der Drain-Elektrodenschicht 150 des Transistors 100 elektrisch mit der obigen Vorrichtung verbunden sein.

**[0042]** Der isolierende Basisfilm 120 kann eine Funktion zum Zuführen von Sauerstoff zu der Oxidhalbleiterschicht 130 sowie eine Funktion zum Verhindern einer Diffusion von Verunreinigungen aus dem Substrat 110 aufweisen. Aus diesem Grund handelt es sich bei dem isolierenden Basisfilm 120 bevorzugt um einen Sauerstoff enthaltenden isolierenden Film. Es ist stärker bevorzugt, dass es sich bei dem isolierenden Basisfilm 120 um einen isolierenden Film handelt, der Sauerstoff enthält und in dem der Sauerstoffgehalt höher ist als derjenige in der stöchiometrischen Zusammensetzung. In dem Fall, in dem, wie oben beschrieben, das Substrat 110 mit einer weiteren Vorrichtung versehen ist, weist der isolierende Basisfilm 120 auch eine Funktion als isolierender Zwischenschichtfilm auf. In diesem Fall wird der isolierende Basisfilm 120 vorzugsweise einer Planarisierungsbehandlung, wie z. B. chemisch-mechanischem Polieren (chemical mechanical polishing, CMP), unterzogen, um eine ebene Oberfläche aufzuweisen.

**[0043]** Des Weiteren hat in einem Bereich, in dem ein Kanal des Transistors 100 gebildet wird, die Oxidhalbleiterschicht 130 eine Struktur, bei der die erste Oxidhalbleiterschicht 131, die zweite Oxidhalbleiterschicht 132 und die dritte Oxidhalbleiterschicht 133 in dieser Reihenfolge von der Seite des Substrates 110 aus gestapelt sind. Wie in der Querschnittsansicht in einer Querrichtung des Kanals in **Fig. 1C** gezeigt ist, ist zusätzlich die dritte Oxidhalbleiterschicht 133 in dem Kanalbildungsbereich derart ausgebildet, dass sie eine Seitenfläche, die nach oben weisende Oberfläche und die entgegengesetzt liegende Seitenfläche des Stapels, der die erste Oxidhalbleiterschicht 131 und die zweite Oxidhalbleiterschicht 132 umfasst, bedeckt. Dies bedeutet, dass in dem Kanalbildungsbereich die zweite Oxidhalbleiterschicht 132 von der ersten Oxidhalbleiterschicht 131 und der dritten Oxidhalbleiterschicht 133 umschlossen ist.

**[0044]** Für die zweite Oxidhalbleiterschicht 132 wird hier beispielsweise ein Oxidhalbleiter verwendet, dessen Elektronenaffinität (ein Energieunterschied zwischen einem Vakuumniveau und dem Minimum des Leitungsbandes) höher ist als diejenige der ersten Oxidhalbleiterschicht 131 und der dritten Oxidhalbleiterschicht 133. Die Elektronenaffinität kann durch Abziehen eines Energieunterschiedes zwischen dem Minimum des Leitungsbandes und dem Maximum des Valenzbandes (der als Energielücke bezeichnet) ausgehend von einem Energieunterschied zwischen dem Vakuumniveau und dem Maxi-

mum des Valenzbandes (der als Ionisierungspotential bezeichnet) ermittelt werden.

**[0045]** Die erste Oxidhalbleiterschicht 131 und die dritte Oxidhalbleiterschicht 133 enthalten jeweils eine oder mehrere Arten von Metallelementen, welche die zweite Oxidhalbleiterschicht 132 bilden. Beispielsweise sind die erste Oxidhalbleiterschicht 131 und die dritte Oxidhalbleiterschicht 133 vorzugsweise unter Verwendung eines Oxidhalbleiters ausgebildet, dessen Minimum des Leitungsbandes näher an einem Vakuumniveau liegt als dasjenige der zweiten Oxidhalbleiterschicht 132. Des Weiteren ist bevorzugt, dass der Energieunterschied des Minimums des Leitungsbandes zwischen der zweiten Oxidhalbleiterschicht 132 und der ersten Oxidhalbleiterschicht 131 und der Energieunterschied des Minimums des Leitungsbandes zwischen der zweiten Oxidhalbleiterschicht 132 und der dritten Oxidhalbleiterschicht 133 jeweils größer als oder gleich 0,05 eV, 0,07 eV, 0,1 eV oder 0,15 eV und kleiner als oder gleich 2 eV, 1 eV, 0,5 eV oder 0,4 eV sind.

**[0046]** Wenn bei einer derartigen Struktur ein elektrisches Feld an die Gate-Elektrodenschicht 170 angelegt wird, wird ein Kanal in der zweiten Oxidhalbleiterschicht 132 gebildet, deren Minimum des Leitungsbandes in der Oxidhalbleiterschicht 130 am tiefsten liegt. Mit anderen Worten: die dritte Oxidhalbleiterschicht 133 ist zwischen der zweiten Oxidhalbleiterschicht 132 und dem Gate-Isolierfilm 160 ausgebildet, wodurch eine Struktur erhalten wird, bei welcher der Kanal des Transistors nicht in Kontakt mit dem Gate-Isolierfilm steht.

**[0047]** Ferner wird, da die erste Oxidhalbleiterschicht 131 ein oder mehrere Metallelemente, die in der zweiten Oxidhalbleiterschicht 132 enthalten sind, enthält, ein Grenzflächenzustand (interface state) an der Grenzfläche der zweiten Oxidhalbleiterschicht 132 zu der ersten Oxidhalbleiterschicht 131 weniger wahrscheinlich gebildet als an der Grenzfläche zu dem isolierenden Basisfilm 120, wenn man davon ausgeht, dass die zweite Oxidhalbleiterschicht 132 in Kontakt mit dem isolierenden Basisfilm 120 steht. Der Grenzflächenzustand bildet manchmal einen Kanal, was zu einer Veränderung der Schwellenspannung des Transistors führt. Mit der ersten Oxidhalbleiterschicht 131 können daher Schwankungen der elektrischen Eigenschaften des Transistors, wie z. B. einer Schwellenspannung, verringert werden. Überdies kann die Zuverlässigkeit des Transistors verbessert werden.

**[0048]** Darüber hinaus tritt, da die dritte Oxidhalbleiterschicht 133 ein oder mehrere Metallelemente, die in der zweiten Oxidhalbleiterschicht 132 enthalten sind, enthält, eine Streuung von Ladungsträgern an der Grenzfläche der zweiten Oxidhalbleiterschicht 132 zu der dritten Oxidhalbleiterschicht 133 weniger

wahrscheinlich auf als an der Grenzfläche zu dem Gate-Isolierfilm 160, wenn man davon ausgeht, dass die zweite Oxidhalbleiterschicht 132 in Kontakt mit dem Gate-Isolierfilm 160 steht. Mit der dritten Oxidhalbleiterschicht 133 kann daher die Feldeffektbeweglichkeit des Transistors erhöht werden.

**[0049]** Wenn die erste Oxidhalbleiterschicht 131, die zweite Oxidhalbleiterschicht 132 und die dritte Oxidhalbleiterschicht 133 jeweils eine In-M-Zn-Oxidschicht, die zumindest Indium, Zink und M (M ist ein Metall, wie z. B. Al, Ti, Ga, Ge, Y, Zr, Sn, La, Ce oder Hf) enthält, sind, ist das Atomverhältnis von M zu In oder Zn in der ersten Oxidhalbleiterschicht 131 und der dritten Oxidhalbleiterschicht 133 vorzugsweise höher als dasjenige in der zweiten Oxidhalbleiterschicht 132. Insbesondere beträgt das Atomverhältnis von M zu In oder Zn in der ersten Oxidhalbleiterschicht 131 und der dritten Oxidhalbleiterschicht 133 1,5-mal oder mehr, bevorzugt zweimal oder mehr, stärker bevorzugt dreimal oder mehr so groß wie dasjenige in der zweiten Oxidhalbleiterschicht 132. Das Metall M ist stärker an Sauerstoff gebunden als In oder Zn und weist daher eine Funktion auf, die Erzeugung einer Sauerstofffehlstelle in einer Oxidhalbleiterschicht zu unterdrücken. Das heißt, dass eine Sauerstofffehlstelle in der ersten Oxidhalbleiterschicht 131 und der dritten Oxidhalbleiterschicht 133 weniger wahrscheinlich erzeugt wird als in der zweiten Oxidhalbleiterschicht 132.

**[0050]** Es sei angemerkt, dass dann, wenn die erste Oxidhalbleiterschicht 131, die zweite Oxidhalbleiterschicht 132 und die dritte Oxidhalbleiterschicht 133 jeweils eine In-M-Zn-Oxidschicht, die zumindest Indium, Zink und M (M ist ein Metall, wie z. B. Al, Ti, Ga, Ge, Y, Zr, Sn, La, Ce oder Hf) enthält, sind und wenn die erste Oxidhalbleiterschicht 131 ein Atomverhältnis von In zu M und Zn von  $x_1:y_1:z_1$  aufweist, die zweite Oxidhalbleiterschicht 132 ein Atomverhältnis von In zu M und Zn von  $x_2:y_2:z_2$  aufweist und die dritte Oxidhalbleiterschicht 133 ein Atomverhältnis von In zu M und Zn von  $x_3:y_3:z_3$  aufweist, vorzugsweise sowohl  $y_1/x_1$  als auch  $y_3/x_3$  größer sind als  $y_2/x_2$ . Sowohl  $y_1/x_1$  als auch  $y_3/x_3$  sind 1,5-mal oder mehr, bevorzugt zweimal oder mehr, stärker bevorzugt dreimal oder mehr so groß wie  $y_2/x_2$ . Dabei kann der Transistor stabile elektrische Eigenschaften aufweisen, wenn in der zweiten Oxidhalbleiterschicht 132  $y_2$  größer als oder gleich  $x_2$  ist. Jedoch wird dann, wenn  $y_2$  dreimal oder mehr so groß wie  $x_2$  ist, die Feldeffektbeweglichkeit des Transistors verringert; folglich ist  $y_2$  bevorzugt kleiner als das Dreifache von  $x_2$ .

**[0051]** Es sei angemerkt, dass in dieser Beschreibung ein Atomverhältnis, das für Beschreibung der Zusammensetzung einer Oxidhalbleiterschicht verwendet wird, ebenfalls als Atomverhältnis eines Basismaterials verwendet werden kann. In dem

Fall, in dem eine Oxidhalbleiterschicht durch ein Sputterverfahren unter Verwendung eines Oxidhalbleitermaterials als Target abgeschieden wird, könnte sich die Zusammensetzung der Oxidhalbleiterschicht in Abhängigkeit von der Art oder dem Verhältnis eines Sputtergases, der Dichte des Targets oder den Abscheidungsbedingungen ausgehend von der Zusammensetzung des Targets unterscheiden, nämlich eines Basismaterials. Deshalb wird in dieser Beschreibung ein Atomverhältnis, das für Beschreibung der Zusammensetzung einer Oxidhalbleiterschicht verwendet wird, ebenfalls als Atomverhältnis eines Basismaterials verwendet. Beispielsweise kann man in dem Fall, in dem ein Sputterverfahren zur Abscheidung verwendet wird, einen In-Ga-Zn-Oxidfilm, dessen Atomverhältnis von In zu Ga und Zn 1:1:1 ist, auch als einen In-Ga-Zn-Oxidfilm verstehen, der unter Verwendung eines In-Ga-Zn-Oxidmaterials, dessen Atomverhältnis von In zu Ga und Zn 1:1:1 ist, als Target ausgebildet wird.

**[0052]** Des Weiteren betragen in dem Fall, in dem Zn und O außer Acht gelassen werden, der Anteil an In und der Anteil an M in der ersten Oxidhalbleiterschicht 131 und in der dritten Oxidhalbleiterschicht 133 jeweils bevorzugt kleiner als 50 Atom-% bzw. größer als oder gleich 50 Atom-% und stärker bevorzugt kleiner als 25 Atom-% bzw. größer als oder gleich 75 Atom-%. Zudem betragen in dem Fall, in dem Zn und O außer Acht gelassen werden, der Anteil an In und der Anteil an M in der zweiten Oxidhalbleiterschicht 132 bevorzugt größer als oder gleich 25 Atom-% bzw. kleiner als 75 Atom-% und stärker bevorzugt größer als oder gleich 34 Atom-% bzw. kleiner als 66 Atom-%.

**[0053]** Die Dicken der ersten Oxidhalbleiterschicht 131 und der dritten Oxidhalbleiterschicht 133 sind jeweils größer als oder gleich 1 nm und kleiner als oder gleich 100 nm, bevorzugt größer als oder gleich 3 nm und kleiner als oder gleich 50 nm. Die Dicke der zweiten Oxidhalbleiterschicht 132 ist größer als oder gleich 1 nm und kleiner als oder gleich 200 nm, bevorzugt größer als oder gleich 3 nm und kleiner als oder gleich 100 nm, stärker bevorzugt größer als oder gleich 3 nm und kleiner als oder gleich 50 nm.

**[0054]** Für die erste Oxidhalbleiterschicht 131, die zweite Oxidhalbleiterschicht 132 und die dritte Oxidhalbleiterschicht 133 kann beispielsweise ein Oxidhalbleiter, der Indium, Zink und Gallium enthält, verwendet werden. Es sei angemerkt, dass die zweite Oxidhalbleiterschicht 132 vorzugsweise Indium enthält, weil die Ladungsträgerbeweglichkeit erhöht werden kann.

**[0055]** Mit der Oxidhalbleiterschicht 130 mit einer Stapschicht-Struktur, welche die erste Oxidhalbleiterschicht 131, die zweite Oxidhalbleiterschicht 132

und die dritte Oxidhalbleiterschicht 133 umfasst, kann daher ein Kanal in der zweiten Oxidhalbleiterschicht 132 gebildet werden. Demzufolge kann der Transistor eine hohe Feldeffektbeweglichkeit und stabile elektrische Eigenschaften aufweisen.

**[0056]** Bei einer Bandstruktur sind die Minima der Leitungsbänder der ersten Oxidhalbleiterschicht 131, der zweiten Oxidhalbleiterschicht 132 und der dritten Oxidhalbleiterschicht 133 stetig miteinander verbunden. Man kann dies auch aus der Tatsache verstehen, dass die Zusammensetzungen der ersten Oxidhalbleiterschicht 131, der zweiten Oxidhalbleiterschicht 132 und der dritten Oxidhalbleiterschicht 133 nahe beieinander liegen und dass Sauerstoff leicht zwischen der ersten Oxidhalbleiterschicht 131, der zweiten Oxidhalbleiterschicht 132 und der dritten Oxidhalbleiterschicht 133 diffundiert. Deshalb weisen die erste Oxidhalbleiterschicht 131, die zweite Oxidhalbleiterschicht 132 und die dritte Oxidhalbleiterschicht 133 eine stetige physikalische Eigenschaft auf, obwohl sie verschiedene Zusammensetzungen haben und einen Stapel bilden. In den Zeichnungen sind Grenzflächen zwischen den Oxidhalbleiterschichten des Stapels durch Punktlinien dargestellt.

**[0057]** Die Oxidhalbleiterschicht 130, in der Schichten mit den gleichen Hauptkomponenten gestapelt sind, ist derart ausgebildet, dass sie nicht nur eine einfache Stapschicht-Struktur der Schichten, sondern auch ein stetiges Energieband aufweist (hier besonders eine U-förmige Wanne-Struktur, bei der die Minima der Leitungsbänder stetig miteinander verbunden sind). Mit anderen Worten: die Stapschicht-Struktur ist derart ausgebildet, dass an jeder Grenzfläche keine Verunreinigung, die ein Defektniveau (defect level) wie z. B. ein Einfangzentrum (trap center) oder ein Rekombinationszentrum (recombination center) bildet, existiert. Wenn Verunreinigungen zwischen den gestapelten Oxidhalbleiterschichten existieren, geht die Stetigkeit des Energiebandes verloren und Ladungsträger verschwinden durch Einfangen oder Rekombination an der Grenzfläche.

**[0058]** Beispielsweise kann ein In-Ga-Zn-Oxid, dessen Atomverhältnis von In zu Ga und Zn 1:3:2, 1:3:3, 1:3:4, 1:3:6, 1:6:4 oder 1:9:6 ist, für die erste Oxidhalbleiterschicht 131 und die dritte Oxidhalbleiterschicht 133 verwendet werden, und ein In-Ga-Zn-Oxid, dessen Atomverhältnis von In zu Ga und Zn 1:1:1, 5:5:6, 3:1:2 oder dergleichen ist, kann für die zweite Oxidhalbleiterschicht 132 verwendet werden.

**[0059]** Die zweite Oxidhalbleiterschicht 132 der Oxidhalbleiterschicht 130 dient als Wanne, so dass ein Kanal in der zweiten Oxidhalbleiterschicht 132 in einem Transistor, der die Oxidhalbleiterschicht 130 beinhaltet, gebildet wird. Es sei angemerkt, dass da die Minima der Leitungsbänder stetig mitei-

nander verbunden sind, die Oxidhalbleiterschicht 130 auch als U-förmige Wanne bezeichnet werden kann. Außerdem kann ein Kanal, der derart ausgebildet ist, dass er eine derartige Struktur hat, auch als eingebetteter Kanal (buried channel) bezeichnet werden.

**[0060]** Es sei angemerkt, dass Einfangniveaus aufgrund von Verunreinigungen oder Defekten in der Nähe der Grenzfläche zwischen einem isolierenden Film, wie z. B. einem Siliziumoxidfilm, und der ersten Oxidhalbleiterschicht 131 bzw. der dritten Oxidhalbleiterschicht 133 gebildet werden könnten. Die zweite Oxidhalbleiterschicht 132 kann von den Einfangniveaus getrennt sein, da die erste Oxidhalbleiterschicht 131 und die dritte Oxidhalbleiterschicht 133 vorhanden sind.

**[0061]** Wenn die Energieunterschiede zwischen dem Minimum des Leitungsbandes der zweiten Oxidhalbleiterschicht 132 und den jeweiligen Minima der Leitungsbänder der ersten Oxidhalbleiterschicht 131 und der dritten Oxidhalbleiterschicht 133 klein sind, könnte jedoch ein Elektron in der zweiten Oxidhalbleiterschicht 132 über die Energieunterschiede hinüber das Einfangniveau erreichen. Wenn das Elektron im Einfangniveau eingefangen wird, wird eine negative feste Ladung an der Grenzfläche zu dem isolierenden Film erzeugt, wodurch die Schwellenspannung des Transistors in positiver Richtung verschoben wird.

**[0062]** Um Schwankungen der Schwellenspannung des Transistors zu verringern, benötigt man deshalb Energieunterschiede von wenigstens einer gewissen Größe zwischen dem Minimum des Leitungsbandes der zweiten Oxidhalbleiterschicht 132 und den jeweiligen Minima der Leitungsbänder der ersten Oxidhalbleiterschicht 131 und der dritten Oxidhalbleiterschicht 133. Jeder der Energieunterschiede beträgt bevorzugt größer als oder gleich 0,1 eV, stärker bevorzugt größer als oder gleich 0,15 eV.

**[0063]** Es sei angemerkt, dass die erste Oxidhalbleiterschicht 131, die zweite Oxidhalbleiterschicht 132 und die dritte Oxidhalbleiterschicht 133 jeweils vorzugsweise eine kristalline Schicht, bei der c-Achsen ausgerichtet sind, umfassen. Ein Film, der die kristalline Schicht umfasst, kann einem Transistor stabile elektrische Eigenschaften liefern.

**[0064]** In dem Fall, in dem ein In-Ga-Zn-Oxid für die Oxidhalbleiterschicht 130 verwendet wird, ist bevorzugt, dass die dritte Oxidhalbleiterschicht 133 weniger In enthält als die zweite Oxidhalbleiterschicht 132, so dass Diffusion von In in den Gate-Isolierfilm verhindert wird.

**[0065]** Der oben beschriebene eingebettete Kanal wird in dem Transistor nach einer Ausführungsform

der vorliegenden Erfindung gebildet. Die dritte Oxidhalbleiterschicht 133 umfasst, wie bei dem in **Fig. 2** gezeigten Transistor, zusätzlich eine mikrokristalline Schicht 133a in Kontakt mit dem isolierenden Basisfilm 120 und dem Stapel, der die erste Oxidhalbleiterschicht 131 und die zweite Oxidhalbleiterschicht 132 umfasst, und eine kristalline Schicht 133b, bei der c-Achsen in einer Richtung senkrecht zu einer Oberfläche der mikrokristallinen Schicht ausgerichtet sind.

**[0066]** **Fig. 3** stellt die Details der Bandstruktur der Oxidhalbleiterschichten (in der B1-B2-Richtung in **Fig. 2**), die eine derartige Struktur aufweisen, dar. Hier stellt Evac die Energie des Vakuumniveaus dar, Ecl1 und Ecl2 stellen jeweils das Minimum des Leitungsbandes des Siliziumoxidfilms dar, EcS1 stellt das Minimum des Leitungsbandes der ersten Oxidhalbleiterschicht 131 dar, EcS2 stellt das Minimum des Leitungsbandes der zweiten Oxidhalbleiterschicht 132 dar, und EcS3 stellt das Minimum des Leitungsbandes der dritten Oxidhalbleiterschicht 133 dar.

**[0067]** Die Energie verändert sich nicht plötzlich zwischen EcS1 und EcS2 und zwischen EcS3 und EcS2, und die Veränderung beginnt und endet allmählich.

**[0068]** Das liegt daran, dass die Bestandteile der Oxidhalbleiterschichten wechselwirkend zwischen der ersten Oxidhalbleiterschicht 131 und der zweiten Oxidhalbleiterschicht 132 und zwischen der dritten Oxidhalbleiterschicht 133 und der zweiten Oxidhalbleiterschicht 132 diffundieren, so dass ein Bereich, der eine mittlere Zusammensetzung zwischen den Zusammensetzungen der ersten Oxidhalbleiterschicht 131 und der zweiten Oxidhalbleiterschicht 132 aufweist, oder ein Bereich, der eine mittlere Zusammensetzung zwischen den Zusammensetzungen der dritten Oxidhalbleiterschicht 133 und der zweiten Oxidhalbleiterschicht 132 aufweist, gebildet wird.

**[0069]** Wie in **Fig. 3** gezeigt ist, wird daher ein in der zweiten Oxidhalbleiterschicht 132 gebildeter Kanal in einem Bereich 132b gebildet, der auf einer weiter innen liegenden Flanke liegt als die Grenzfläche zwischen der dritten Oxidhalbleiterschicht 133 und der zweiten Oxidhalbleiterschicht 132 und die Grenzfläche zwischen der ersten Oxidhalbleiterschicht 131 und der zweiten Oxidhalbleiterschicht 132. Mit einer derartigen Struktur kann verhindert werden, dass ein Ladungsträger eingefangen wird oder rekombiniert, auch wenn ein Defekt oder eine Verunreinigung an einer der Grenzflächen existiert.

**[0070]** In der dritten Oxidhalbleiterschicht 133 umfasst ein Bereich in Kontakt mit einem Stapel, der die erste Oxidhalbleiterschicht 131 und die zweite Oxidhalbleiterschicht 132 umfasst, die mikro-

kristalline Schicht 133a. Die Dichte der mikrokristallinen Schicht ist niedriger als diejenige der kristallinen Schicht 133b, die über der mikrokristallinen Schicht ausgebildet ist; dementsprechend diffundieren die Bestandteile der zweiten Oxidhalbleiterschicht 132 leicht zur Seite der dritten Oxidhalbleiterschicht 133. Als Ergebnis wird der Bereich groß, der eine mittlere Zusammensetzung zwischen den Zusammensetzungen der dritten Oxidhalbleiterschicht 133 und der zweiten Oxidhalbleiterschicht 132 aufweist. Der in der zweiten Oxidhalbleiterschicht 132 gebildete Kanal liegt also noch weiter von der Grenzfläche zwischen der dritten Oxidhalbleiterschicht 133 und der zweiten Oxidhalbleiterschicht 132 entfernt zur Mitte der zweiten Oxidhalbleiterschicht 132 hin, und eine Fehlfunktion, die auftritt, wenn ein Defekt oder eine Verunreinigung an der Grenzfläche existiert, kann auf wirksamere Weise vermieden werden.

**[0071]** In dem Fall, in dem die erste Oxidhalbleiterschicht 131 und die zweite Oxidhalbleiterschicht 132 jeweils eine kristalline Schicht, bei der c-Achsen ausgerichtet sind, umfassen, diffundiert Sauerstoff relativ leicht, da die Dichte der mikrokristallinen Schicht 133a niedriger ist als diejenige der kristallinen Schicht. Folglich kann Sauerstoff unter Benutzung der mikrokristallinen Schicht 133a als Durchgang auf effiziente Weise von dem isolierenden Basisfilm 120 zu der zweiten Oxidhalbleiterschicht 132, die zu einem Kanal wird, zugeführt werden, und eine Sauerstofffehlstelle kann mit Sauerstoff gefüllt werden.

**[0072]** Bei der kristallinen Schicht 133b in der dritten Oxidhalbleiterschicht 133 sind des Weiteren c-Achsen in der Richtung senkrecht zur Oberfläche der mikrokristallinen Schicht 133a ausgerichtet. Deshalb kann dann, wenn die zweite Oxidhalbleiterschicht 132 derart ausgebildet ist, dass sie eine gekrümmte Oberfläche aufweist, ein Kanalbereich in der zweiten Oxidhalbleiterschicht 132 dicht mit Kristallen, deren c-Achsen ausgerichtet sind, bedeckt sein.

**[0073]** **Fig. 4A** ist eine Querschnittsansicht in der Querrichtung des Kanals des Transistors, die einen Teil einer Kristallstruktur eines Stapsels schematisch darstellt. Der Stapel umfasst die zweite Oxidhalbleiterschicht 132, die derart ausgebildet ist, dass sie eine gekrümmte Oberfläche aufweist, die mikrokristalline Schicht 133a, welche die zweite Oxidhalbleiterschicht bedeckt, und die kristalline Schicht 133b, die über der mikrokristallinen Schicht ausgebildet ist. Hier handelt es sich bei der zweiten Oxidhalbleiterschicht 132 um eine kristalline Schicht, bei der c-Achsen in einer Richtung senkrecht zu einer Oberfläche der ersten Oxidhalbleiterschicht 131 (nicht abgebildet) ausgerichtet sind.

**[0074]** Wenn die zweite Oxidhalbleiterschicht 132 derart ausgebildet ist, dass sie eine gekrümmte Oberfläche aufweist, wie in **Fig. 4A** gezeigt, kann

die dritte Oxidhalbleiterschicht 133 derart ausgebildet sein, dass sie die dichte kristalline Schicht 133b, bei der c-Achsen in der Richtung senkrecht zur gekrümmten Oberfläche aufgerichtet sind, aufweist, wobei die mikrokristalline Schicht 133a zwischen der zweiten Oxidhalbleiterschicht 132 und der dichten kristallinen Schicht 133b liegt. Eine derartige Struktur kann einen Effekt, die Abgabe von Sauerstoff aus der zweiten Oxidhalbleiterschicht 132 zu unterdrücken, oder einen Effekt, aus dem isolierenden Basisfilm 120 abgegebenen Sauerstoff in der dritten Oxidhalbleiterschicht 133 einzuschließen, verstärken. Somit kann eine Sauerstofffehlstelle in der zweiten Oxidhalbleiterschicht 132 auf effiziente Weise mit Sauerstoff gefüllt werden.

**[0075]** Es sei angemerkt, dass in dem Fall, in dem die zweite Oxidhalbleiterschicht 132 derart ausgebildet ist, dass sie keine gekrümmte Oberfläche aufweist, wie in **Fig. 4B** gezeigt, ein Bereich 233, der dünn mit Kristallen besiedelt ist, an einer Kreuzung zwischen der kristallinen Schicht 133b, die über der nach oben weisenden Oberfläche der zweiten Oxidhalbleiterschicht 132 ausgebildet ist, und der kristallinen Schicht 133b, die einer Seitenfläche der zweiten Oxidhalbleiterschicht 132 zugewandt ausgebildet ist, in der dritten Oxidhalbleiterschicht 133 ausgebildet ist. Deswegen ist wahrscheinlich, dass Sauerstoff, der in der zweiten Oxidhalbleiterschicht 132 enthalten ist, und Sauerstoff, der von dem isolierenden Basisfilm 120 zu der zweiten Oxidhalbleiterschicht 132 zugeführt wird, durch den Bereich 233 hindurch freigegeben wird, in welchem Falle eine Sauerstofffehlstelle in der zweiten Oxidhalbleiterschicht 132 nicht auf effiziente Weise mit Sauerstoff gefüllt werden kann.

**[0076]** Es sei angemerkt, dass einem Transistor, in dem eine Oxidhalbleiterschicht als Kanal dient, stabile elektrische Eigenschaften effektiv verliehen werden können, indem die Konzentration der Verunreinigungen in der Oxidhalbleiterschicht verringert wird, um die Oxidhalbleiterschicht intrinsisch oder im Wesentlichen intrinsisch zu machen. Der Begriff „im Wesentlichen intrinsisch“ bezeichnet den Zustand, in dem eine Oxidhalbleiterschicht eine Ladungsträgerdichte von niedriger als  $1 \times 10^{17} / \text{cm}^3$ , bevorzugt niedriger als  $1 \times 10^{15} / \text{cm}^3$ , stärker bevorzugt niedriger als  $1 \times 10^{13} / \text{cm}^3$  aufweist.

**[0077]** In der Oxidhalbleiterschicht sind ferner Wasserstoff, Stickstoff, Kohlenstoff, Silizium und ein Metallelement, das verschieden von Hauptkomponenten ist, Verunreinigungen. Wasserstoff und Stickstoff bilden beispielsweise Donatorniveaus, was die Ladungsträgerdichte erhöht, und Silizium bildet Verunreinigungsniveaus in der Oxidhalbleiterschicht. Die Verunreinigungsniveaus dienen als Einfangstellen und könnten die elektrischen Eigenschaften des Transistors verschlechtern. Es ist deshalb bevorzugt,

die Konzentration der Verunreinigungen in der ersten Oxidhalbleiterschicht 131, der zweiten Oxidhalbleiterschicht 132 und der dritten Oxidhalbleiterschicht 133 und diejenige an Grenzflächen zwischen den Schichten zu verringern.

**[0078]** Um die Oxidhalbleiterschicht intrinsisch oder im Wesentlichen intrinsisch zu machen, beträgt beispielsweise bei SIMS (Sekundärionen-Massenpektrometrie) die Siliziumkonzentration in einer gewissen Tiefe der Oxidhalbleiterschicht oder in einem Bereich der Oxidhalbleiterschicht bevorzugt niedriger als  $1 \times 10^{19}$  Atome/cm<sup>3</sup>, stärker bevorzugt niedriger als  $5 \times 10^{18}$  Atome/cm<sup>3</sup>, noch stärker bevorzugt niedriger als oder gleich  $1 \times 10^{18}$  Atome/cm<sup>3</sup>. Ferner beträgt die Wasserstoffkonzentration in einer gewissen Tiefe der Oxidhalbleiterschicht oder in einem Bereich der Oxidhalbleiterschicht bevorzugt niedriger als oder gleich  $2 \times 10^{20}$  Atome/cm<sup>3</sup>, stärker bevorzugt niedriger als oder gleich  $5 \times 10^{19}$  Atome/cm<sup>3</sup>, noch stärker bevorzugt niedriger als oder gleich  $1 \times 10^{19}$  Atome/cm<sup>3</sup>, sogar noch stärker bevorzugt niedriger als oder gleich  $5 \times 10^{18}$  Atome/cm<sup>3</sup>. Ferner beträgt die Stickstoffkonzentration in einer gewissen Tiefe der Oxidhalbleiterschicht oder in einem Bereich der Oxidhalbleiterschicht bevorzugt niedriger als  $5 \times 10^{19}$  Atome/cm<sup>3</sup>, stärker bevorzugt niedriger als oder gleich  $5 \times 10^{18}$  Atome/cm<sup>3</sup>, noch stärker bevorzugt niedriger als oder gleich  $1 \times 10^{18}$  Atome/cm<sup>3</sup>, sogar noch stärker bevorzugt niedriger als oder gleich  $5 \times 10^{17}$  Atome/cm<sup>3</sup>.

**[0079]** In dem Fall, in dem die Oxidhalbleiterschicht Kristalle enthält, könnte eine hohe Silizium- oder Kohlenstoffkonzentration die Kristallinität der Oxidhalbleiterschicht reduzieren. Damit die Kristallinität der Oxidhalbleiterschicht nicht reduziert wird, kann beispielsweise die Siliziumkonzentration in einer gewissen Tiefe der Oxidhalbleiterschicht oder in einem Bereich der Oxidhalbleiterschicht niedriger als  $1 \times 10^{19}$  Atome/cm<sup>3</sup>, bevorzugt niedriger als  $5 \times 10^{18}$  Atome/cm<sup>3</sup>, stärker bevorzugt niedriger als  $1 \times 10^{18}$  Atome/cm<sup>3</sup> betragen. Des Weiteren kann beispielsweise die Kohlenstoffkonzentration in einer gewissen Tiefe der Oxidhalbleiterschicht oder in einem Bereich der Oxidhalbleiterschicht niedriger als  $1 \times 10^{19}$  Atome/cm<sup>3</sup>, bevorzugt niedriger als  $5 \times 10^{18}$  Atome/cm<sup>3</sup>, stärker bevorzugt niedriger als  $1 \times 10^{18}$  Atome/cm<sup>3</sup> betragen.

**[0080]** Ein Transistor, bei dem die oben beschriebene hochreine Oxidhalbleiterschicht für einen Kanalbildungsbereich verwendet wird, weist einen sehr geringen Sperrstrom (off-state current) auf. In dem Fall, in dem die Spannung zwischen einem Source-Anschluss und einem Drain-Anschluss beispielsweise auf zirka 0,1 V, 5 V oder 10 V eingestellt wird, kann der Sperrstrom, der durch die Kanalbreite des Transistors normalisiert ist, so klein wie mehrere

Yoktoampere pro Mikrometer bis mehrere Zeptoampere pro Mikrometer sein.

**[0081]** Es sei angemerkt, dass ein siliziumhaltiger isolierender Film in vielen Fällen als Gate-Isolierfilm des Transistors verwendet wird; es ist also aus dem zuvor beschriebenen Grund bevorzugt, dass, ähnlich wie bei dem Transistor nach einer Ausführungsform der vorliegenden Erfindung, ein als Kanal dienender Bereich der Oxidhalbleiterschicht nicht in Kontakt mit dem Gate-Isolierfilm steht. In dem Fall, in dem ein Kanal an der Grenzfläche zwischen dem Gate-Isolierfilm und der Oxidhalbleiterschicht gebildet wird, tritt eine Streuung von Ladungsträgern an der Grenzfläche auf, wodurch die Feldeffektbeweglichkeit des Transistors in einigen Fällen abnimmt. Im Hinblick darauf ist ebenfalls bevorzugt, dass der als Kanal dienende Bereich der Oxidhalbleiterschicht getrennt von dem Gate-Isolierfilm liegt.

**[0082]** Für die Source-Elektrodenschicht 140 und die Drain-Elektrodenschicht 150 wird vorzugsweise ein leitendes Material, das leicht an Sauerstoff gebunden wird, verwendet. Beispielsweise kann Al, Cr, Cu, Ta, Ti, Mo oder W verwendet werden. Es ist besonders bevorzugt, unter den Materialien Ti, das leicht an Sauerstoff gebunden wird, oder W, das einen hohen Schmelzpunkt aufweist, zu verwenden, so dass der nachfolgende Prozess bei relativ hohen Temperaturen durchgeführt werden kann. Es sei angemerkt, dass die Kategorie „leitendes Material, das leicht an Sauerstoff gebunden wird“ ein Material, in das Sauerstoff leicht diffundiert, umfasst.

**[0083]** Wenn das leitende Material, das leicht an Sauerstoff gebunden wird, in Kontakt mit einer Oxidhalbleiterschicht steht, findet ein Phänomen statt, bei dem Sauerstoff in der Oxidhalbleiterschicht in das leitende Material, das leicht an Sauerstoff gebunden wird, diffundiert. Das Phänomen findet deutlich statt, wenn die Temperatur hoch ist. Da der Herstellungsprozess des Transistors einen Wärmebehandlungsschritt umfasst, verursacht das obige Phänomen eine Erzeugung von Sauerstofffehlstellen in der Nähe eines Bereichs, der sich in der Oxidhalbleiterschicht befindet und in Kontakt mit der Source-Elektrodenschicht oder der Drain-Elektrodenschicht steht. Die Sauerstofffehlstellen binden sich an Wasserstoff, der geringfügig in der Schicht enthalten ist, wodurch sich der Bereich in einen n-Typ-Bereich verändert. Demzufolge kann der n-Typ-Bereich als Source oder Drain des Transistors dienen.

**[0084]** Der n-Typ-Bereich ist in einer vergrößerten Querschnittsansicht des Transistors (die einen Teil eines Querschnitts in der Längsrichtung des Kanals darstellt, welcher nahe an der Source-Elektrodenschicht 140 liegt) in **Fig. 5** gezeigt. Eine Grenze 135, die durch eine Punktlinie in der ersten Oxidhalbleiterschicht 131 und der zweiten Oxidhalbleiter-

schicht 132 dargestellt ist, ist eine Grenze zwischen einem intrinsischen Halbleiterbereich und einem n-Typ-Halbleiterbereich. In der ersten Oxidhalbleiterschicht 131 und der zweiten Oxidhalbleiterschicht 132 wird ein Bereich, der nahe an der Source-Elektrodenschicht 140 liegt, zu einem n-Typ-Bereich. Die Grenze 135 ist hier schematisch abgebildet, aber die reale Grenze ist in einigen Fällen nicht deutlich zu erkennen. **Fig. 5** zeigt, dass sich ein Teil der Grenze 135 in seitliche Richtung in der zweiten Oxidhalbleiterschicht 132 erstreckt; jedoch weist ein Bereich in der ersten Oxidhalbleiterschicht 131 und der zweiten Oxidhalbleiterschicht 132, der zwischen der Source-Elektrodenschicht 140 und dem isolierenden Basisfilm 120 liegt, in einigen Fällen gänzlich in der Dickenrichtung den n-Typ auf.

**[0085]** In dem Fall, in dem ein Transistor mit einer sehr kleinen Kanallänge hergestellt wird, könnte sich ein n-Typ-Bereich, der durch die Erzeugung von Sauerstofffehlstellen gebildet wird, in die Längsrichtung des Kanals des Transistors erstrecken. In diesem Fall verändern sich die elektrischen Eigenschaften des Transistors; beispielsweise wird die Schwellenspannung verschoben, oder Einschalt- und Ausschaltzustände des Transistors können nicht durch die Gate-Spannung gesteuert werden (in welchem Falle der Transistor eingeschaltet wird). Folglich ist dann, wenn ein Transistor mit einer sehr kleinen Kanallänge hergestellt wird, nicht immer bevorzugt, dass ein leitendes Material, das leicht an Sauerstoff gebunden wird, für eine Source-Elektrodenschicht und eine Drain-Elektrodenschicht verwendet wird.

**[0086]** In einem solchen Fall kann ein leitendes Material, das weniger als das vorstehende Material dazu neigt, an Sauerstoff gebunden zu werden, für die Source-Elektrodenschicht 140 und die Drain-Elektrodenschicht 150 verwendet werden. Als das leitende Material, das nicht leicht an Sauerstoff gebunden wird, kann beispielsweise ein Material, das Tantalnitrid, Titanitrid, Gold, Platin, Palladium oder Ruthenium enthält, oder dergleichen verwendet werden. Es sei angemerkt, dass in dem Fall, in dem das leitende Material in Kontakt mit der zweiten Oxidhalbleiterschicht 132 steht, die Source-Elektrodenschicht 140 und die Drain-Elektrodenschicht 150 jeweils eine Struktur haben können, bei der das leitende Material, das nicht leicht an Sauerstoff gebunden wird, und das oben beschriebene leitende Material, das leicht an Sauerstoff gebunden wird, gestapelt sind.

**[0087]** Der Gate-Isolierfilm 160 kann unter Verwendung eines isolierenden Films, der eines oder mehrere von Aluminiumoxid, Magnesiumoxid, Siliziumoxid, Siliziumoxynitrid, Siliziumnitridoxid, Siliziumnitrid, Galliumoxid, Germaniumoxid, Yttriumoxid, Zirconiumoxid, Lanthanoxid, Neodymoxid, Hafniumoxid und Tantaloxid enthält, ausgebildet sein. Der Gate-Isolierfilm 160 kann ein Stapel, der eines der vorstehenden Materialien enthält, sein.

Aluminiumoxid und Tantaloxid enthält, ausgebildet sein. Der Gate-Isolierfilm 160 kann ein Stapel, der eines der vorstehenden Materialien enthält, sein.

**[0088]** Für die Gate-Elektrodenschicht 170 kann ein leitender Film, der unter Verwendung von Al, Ti, Cr, Co, Ni, Cu, Y, Zr, Mo, Ru, Ag, Ta, W oder dergleichen ausgebildet ist, verwendet werden. Die Gate-Elektrodenschicht kann ein Stapel, der eines der vorstehenden Materialien enthält, sein. Alternativ kann ein stickstoffhaltiger leitender Film für die Gate-Elektrodenschicht verwendet werden.

**[0089]** Die isolierende Schicht 180 ist vorzugsweise über dem Gate-Isolierfilm 160 und der Gate-Elektrodenschicht 170 ausgebildet. Die isolierende Schicht ist vorzugsweise unter Verwendung von Aluminiumoxid ausgebildet. Der Aluminiumoxidfilm weist einen hohen Sperreffekt auf, was Durchdringung sowohl von Sauerstoff als auch von Verunreinigungen, wie z. B. Wasserstoff und Feuchtigkeit, verhindert. Deshalb kann während und nach dem Herstellungsprozess des Transistors der Aluminiumoxidfilm vorteilhaft als Schutzfilm dienen, der Effekte aufweist, um zu verhindern, dass Verunreinigungen, wie z. B. Wasserstoff und Feuchtigkeit, die Schwankungen der elektrischen Eigenschaften des Transistors verursachen, in die Oxidhalbleiterschicht 130 eindringen, dass Sauerstoff, der eine Hauptkomponente der Oxidhalbleiterschicht 130 ist, aus der Oxidhalbleiterschicht abgegeben wird und dass Sauerstoff unnötigerweise aus dem isolierenden Basisfilm 120 abgegeben wird. Außerdem kann Sauerstoff, der in dem Aluminiumoxidfilm enthalten ist, in die Oxidhalbleiterschicht diffundieren.

**[0090]** Des Weiteren ist die isolierende Schicht 185 vorzugsweise über der isolierenden Schicht 180 ausgebildet. Die isolierende Schicht 185 kann unter Verwendung eines isolierenden Films, der eines oder mehrere von Magnesiumoxid, Siliziumoxid, Siliziumoxynitrid, Siliziumnitridoxid, Siliziumnitrid, Galliumoxid, Germaniumoxid, Yttriumoxid, Zirconiumoxid, Lanthanoxid, Neodymoxid, Hafniumoxid und Tantaloxid enthält, ausgebildet sein. Die isolierende Schicht 185 kann ein Stapel, der eines der vorstehenden Materialien enthält, sein.

**[0091]** Hierbei enthält die isolierende Schicht 185 vorzugsweise überschüssigen Sauerstoff. Eine isolierende Schicht, die überschüssigen Sauerstoff enthält, bezeichnet eine isolierende Schicht, aus der durch Wärmebehandlung oder dergleichen Sauerstoff abgegeben werden kann. Die isolierende Schicht, die überschüssigen Sauerstoff enthält, ist beispielsweise ein Film, bei dem die Menge an abgegebenem Sauerstoff, umgerechnet in Sauerstoffatome,  $1,0 \times 10^{19}$  Atome/cm<sup>3</sup> oder mehr bei einer Thermodesorptions-Spektroskopie-Analyse beträgt. Bei der Thermodesorptions-Spektroskopie-Analyse

wird eine Wärmebehandlung bei einer Oberflächentemperatur von höher als oder gleich 100 °C und niedriger als oder gleich 700 °C, bevorzugt höher als oder gleich 100 °C und niedriger als oder gleich 500 °C durchgeführt. Der aus der isolierenden Schicht abgegebene Sauerstoff kann durch den Gate-Isolierfilm 160 hindurch in den Kanalbildungsbereich in der Oxidhalbleiterschicht 130 diffundieren, so dass Sauerstofffehlstellen, die in dem Kanalbildungsbereich gebildet werden, mit dem Sauerstoff gefüllt werden können. Auf diese Weise können die elektrischen Eigenschaften des Transistors stabil sein.

**[0092]** Hohe Integration einer Halbleitervorrichtung erfordert eine Miniaturisierung eines Transistors. Es ist jedoch bekannt, dass die Miniaturisierung eines Transistors eine Verschlechterung der elektrischen Eigenschaften des Transistors verursacht. Insbesondere ist eine Verringerung des Durchlassstroms erheblich, welche direkt durch eine Abnahme der Kanalbreite verursacht wird.

**[0093]** In dem Transistor nach einer Ausführungsform der vorliegenden Erfindung ist jedoch, wie oben beschrieben, die dritte Oxidhalbleiterschicht 133 derart ausgebildet, dass sie einen Bereich, der in der zweiten Oxidhalbleiterschicht 132 liegt und in dem ein Kanal gebildet wird, bedeckt, und dass die Kanalbildungsschicht und der Gate-Isolierfilm nicht miteinander in Kontakt stehen. Deshalb kann die Streuung von Ladungsträgern an der Grenzfläche zwischen der Kanalbildungsschicht und dem Gate-Isolierfilm verringert werden, und die Feldeffektbeweglichkeit des Transistors kann erhöht werden.

**[0094]** Zudem können die elektrischen Eigenschaften des Transistors nach einer Ausführungsform der vorliegenden Erfindung im Besonderen mit einer Struktur verbessert werden, die der in der Querschnittsansicht in der Querrichtung des Kanals in **Fig. 2** gezeigten Struktur ähnlich ist, wobei die Länge der nach oben weisenden Oberfläche ( $W_T$ ) der zweiten Oxidhalbleiterschicht 132 in der Querrichtung des Kanals so klein wie ihre Dicke ist.

**[0095]** In dem Fall, in dem  $W_T$  klein ist, wie bei einem Transistor in **Fig. 2**, wird beispielsweise ein elektrisches Feld, das von der Gate-Elektrodenschicht 170 bis zur Seitenfläche der zweiten Oxidhalbleiterschicht 132 erzeugt wird, an die ganze zweite Oxidhalbleiterschicht 132 angelegt. Demzufolge wird ein Kanal gleichmäßig in der Seitenfläche und der nach oben weisenden Oberfläche der zweiten Oxidhalbleiterschicht 132 gebildet.

**[0096]** Im Fall eines Transistors, bei dem  $W_T$  klein ist, kann die Kanalbreite als Summe von  $W_T$  und der Längen der Seitenflächen ( $W_{S1}$  und  $W_{S2}$ ) der zweiten Oxidhalbleiterschicht 132 in der Querrich-

tung des Kanals (d. h.  $W_T + W_{S1} + W_{S2}$ ) definiert werden, und der Kanalbreite entsprechend fließt ein Durchlassstrom in dem Transistor. In dem Fall, in dem  $W_T$  sehr klein ist, fließt ein Strom in der ganzen zweiten Oxidhalbleiterschicht 132.

**[0097]** Das heißt, dass der Transistor nach einer Ausführungsform der vorliegenden Erfindung, bei dem  $W_T$  klein ist, sowohl durch einen Effekt, eine Streuung von Ladungsträgern zu unterdrücken, als auch durch einen Effekt, die Kanalbreite zu vergrößern, einen höheren Durchlassstrom aufweisen kann als der herkömmliche Transistor.

**[0098]** Es sei angemerkt, dass, um den Durchlassstrom des Transistors auf effiziente Weise zu erhöhen, eine Beziehung von  $0,3W_S \leq W_T \leq 3W_S$  ( $W_T$  ist größer als oder gleich  $0,3W_S$  und kleiner als oder gleich  $3W_S$ ) erfüllt wird, wobei  $W_{S1}$  und  $W_{S2}$  durch  $W_S$  ( $W_{S1} = W_{S2} = W_S$ ) dargestellt werden. Des Weiteren ist  $W_T/W_S$  bevorzugt größer als oder gleich 0,5 und kleiner als oder gleich 1,5, stärker bevorzugt größer als oder gleich 0,7 und kleiner als oder gleich 1,3. In dem Fall, in dem  $W_T/W_S > 3$  gilt, könnten der S-Wert (S value) und der Sperrstrom zunehmen.

**[0099]** Wie zuvor beschrieben worden ist, kann mit dem Transistor nach einer Ausführungsform der vorliegenden Erfindung ein ausreichend hoher Durchlassstrom erzielt werden, auch wenn der Transistor miniaturisiert ist.

**[0100]** Bei dem Transistor nach einer Ausführungsform der vorliegenden Erfindung ist die zweite Oxidhalbleiterschicht 132 über der ersten Oxidhalbleiterschicht 131 ausgebildet, so dass weniger wahrscheinlich ist, dass ein Grenzflächenzustand gebildet wird. Zusätzlich dringt keine Verunreinigung von oben und unten in die zweite Oxidhalbleiterschicht 132 ein, da die zweite Oxidhalbleiterschicht 132 eine Zwischenschicht bei einer dreischichtigen Struktur ist. Da die zweite Oxidhalbleiterschicht 132 von der ersten Oxidhalbleiterschicht 131 und der dritten Oxidhalbleiterschicht 133 umschlossen ist, kann nicht nur der Durchlassstrom des Transistors erhöht werden, sondern kann auch die Schwellenspannung stabilisiert werden und der S-Wert kann verringert werden. Folglich kann  $I_{cut}$  (Strom bei einer Gatespannung VG von 0 V) verringert werden und der Leistungsverbrauch der Halbleitervorrichtung kann verringert werden. Da die Schwellenspannung des Transistors stabil wird, kann ferner die langzeitige Zuverlässigkeit der Halbleitervorrichtung verbessert werden.

**[0101]** Der Transistor nach einer Ausführungsform der vorliegenden Erfindung kann einen leitenden Film 172 zwischen der Oxidhalbleiterschicht 130 und dem Substrat 110 beinhalten, wie in **Fig. 6** gezeigt ist. Wenn der leitende Film als zweite Gate-

Elektrode verwendet wird, kann der Durchlassstrom weiter erhöht werden und die Schwellenspannung kann gesteuert werden. Um den Durchlassstrom zu erhöhen, werden beispielsweise die Gate-Elektrodenschicht 170 und der leitende Film 172 derart gesteuert, dass sie das gleiche Potential aufweisen, und der Transistor wird als Doppel-Gate-Transistor (dual-gate transistor) betrieben. Darüber hinaus wird ein festes Potential, das sich von einem Potential der Gate-Elektrodenschicht 170 unterscheidet, dem leitenden Film 172 zugeführt, um die Schwellenspannung zu steuern.

**[0102]** Diese Ausführungsform kann mit einer der anderen Ausführungsformen oder mit einem Beispiel in dieser Beschreibung soweit angemessen kombiniert werden.

(Ausführungsform 2)

**[0103]** Bei dieser Ausführungsform wird ein Verfahren zum Herstellen des Transistors 100, der anhand von **Fig. 1A bis Fig. 1C** bei der Ausführungsform 1 beschrieben worden ist, anhand von **Fig. 7A bis Fig. 7C** und **Fig. 8A bis Fig. 8C** beschrieben.

**[0104]** Für das Substrat 110 kann ein Glassubstrat, ein Keramiksubstrat, ein Quarzsubstrat, ein Saphirsubstrat oder dergleichen verwendet werden. Alternativ kann ein einkristallines Halbleitersubstrat oder ein polykristallines Halbleitersubstrat aus Silizium, Siliziumcarbid oder dergleichen, ein Verbund-Halbleitersubstrat aus Siliziumgermanium oder dergleichen, ein Silizium auf einem Isolator- (silicon on insulator, SOI-) Substrat oder dergleichen verwendet werden. Als weitere Alternative kann eines dieser Substrate, das ferner mit einem Halbleiterbauelement versehen ist, verwendet werden.

**[0105]** Der isolierende Basisfilm 120 kann durch ein Plasma-CVD-Verfahren, ein Sputterverfahren oder dergleichen unter Verwendung eines isolierenden Oxidfilms aus Aluminiumoxid, Magnesiumoxide, Siliziumoxid, Siliziumoxynitrid, Galliumoxid, Germaniumoxid, Yttriumoxid, Zirconiumoxid, Lanthanoxid, Neodymoxid, Hafniumoxid, Tantaloxid oder dergleichen, eines isolierenden Nitridfilms aus Siliziumnitrid, Siliziumnitridoxid, Aluminiumnitrid, Aluminiumnitridoxid oder dergleichen, oder eines Films, in dem einige der obigen Materialien gemischt sind, ausgebildet werden. Alternativ kann ein Stapel, der eines der obigen Materialien enthält, verwendet werden, wobei zumindest eine obere Schicht des isolierenden Basisfilms 120, die in Kontakt mit der Oxidhalbleiterschicht 130 steht, vorzugsweise unter Verwendung eines überschüssigen Sauerstoff enthaltenden Materials, das als Versorgungsquelle von Sauerstoff zu der Oxidhalbleiterschicht 130 dienen könnte, ausgebildet ist.

**[0106]** Sauerstoff kann dem isolierenden Basisfilm 120 durch ein Ionenimplantationsverfahren, ein Ionendotierungsverfahren, ein Plasma-Immersion-Ionenimplantationsverfahren oder dergleichen zugesetzt werden. Der Zusatz von Sauerstoff ermöglicht es dem isolierenden Basisfilm 120, der Oxidhalbleiterschicht 130 Sauerstoff sehr leicht zuzuführen.

**[0107]** In dem Fall, in dem eine Oberfläche des Substrates 110 aus einem Isolator ausgebildet ist und es keinen Einfluss der Verunreinigungsdiffusion in die Oxidhalbleiterschicht 130 gibt, die später ausgebildet wird, wird der isolierende Basisfilm 120 nicht notwendigerweise bereitgestellt.

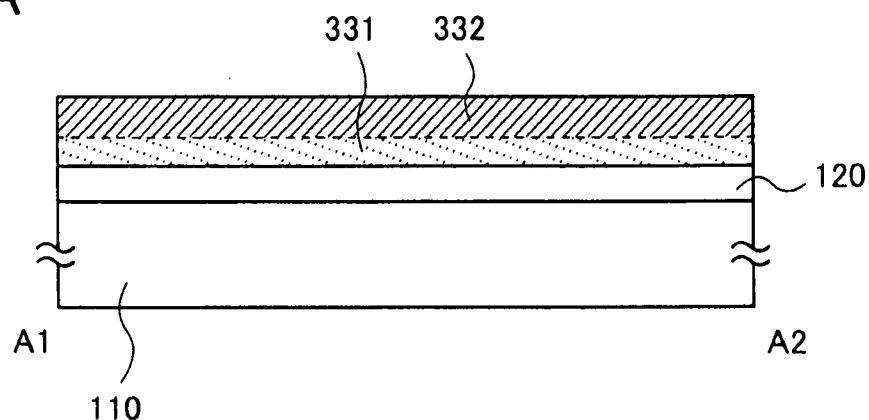

**[0108]** Als nächstes werden ein erster Oxidhalbleiterfilm 331, der zu der ersten Oxidhalbleiterschicht 131 wird, und ein zweiter Oxidhalbleiterfilm 332, der zu der zweiten Oxidhalbleiterschicht 132 wird, durch ein Sputterverfahren, ein CVD-Verfahren, ein MBE-Verfahren, ein ALD-Verfahren oder ein PLD-Verfahren über dem isolierenden Basisfilm 120 abgeschieden (siehe **Fig. 7A**).

**[0109]** Anschließend werden der erste Oxidhalbleiterfilm 331 und der zweite Oxidhalbleiterfilm 332 selektiv geätzt, um die erste Oxidhalbleiterschicht 131 und die zweite Oxidhalbleiterschicht 132 auszubilden (siehe **Fig. 7B**). Zu dieser Zeit kann auch der isolierende Basisfilm 120 geringfügig geätzt werden, wie in **Fig. 7B** gezeigt ist. Der geringfügig geätzte isolierende Basisfilm 120 ermöglicht, dass die zweite Oxidhalbleiterschicht 132 leicht mit der Gate-Elektrode, die später ausgebildet wird, bedeckt wird. Des Weiteren wird die zweite Oxidhalbleiterschicht 132 derart ausgebildet, dass sie im Querschnitt in der Querrichtung eines Kanals des Transistors eine Krümmung von ihrer nach oben weisenden Oberfläche bis zu ihrer Seitenfläche aufweist.

**[0110]** Es sei angemerkt, dass dann, wenn der erste Oxidhalbleiterfilm 331 und der zweite Oxidhalbleiterfilm 332 selektiv geätzt werden, nicht nur ein Fotolack, sondern auch eine Hartmaske, wie z. B. ein Metallfilm, verwendet werden kann. Zusätzlich kann ein organisches Harz über dem Metallfilm ausgebildet werden. Als Metallfilm kann beispielsweise ein Wolframfilm mit einer Dicke von zirka 5 nm verwendet werden.

**[0111]** Zum Ätzen wird vorzugsweise Trockenätzen verwendet, bei dem ein Unterschied zwischen der Ätzgeschwindigkeit des ersten Oxidhalbleiterfilms 331 und derjenigen des zweiten Oxidhalbleiterfilms 332 klein ist.

**[0112]** Um ein stetiges Energieband in einem Stapel, der die erste Oxidhalbleiterschicht 131 und die zweite Oxidhalbleiterschicht 132 umfasst, zu bilden, ist zu bevorzugen, dass die Schichten unter Verwen-