RÉPUBLIQUE FRANÇAISE

INSTITUT NATIONAL

DE LA PROPRIÉTÉ INDUSTRIELLE

PARIS

(11) N° de publication :

(A n'utiliser que pour les

commandes de reproduction).

**2 501 945**

A1

**DEMANDE

DE BREVET D'INVENTION**

(21)

**N° 82 03833**

(54) Circuit servant à déduire un signal de synchronisation de trame d'un signal incident.

(51) Classification internationale (Int. Cl.<sup>3</sup>). H 04 N 5/10.

(22) Date de dépôt..... 8 mars 1982.

(33) (32) (31) Priorité revendiquée : Pays-Bas, 12 mars 1981, n° 81 01202.

(41) Date de la mise à la disposition du

public de la demande..... B.O.P.I. — « Listes » n° 37 du 17-9-1982.

(71) Déposant : N V PHILIPS' GLOEILAMPENFABRIEKEN, société anonyme de droit néerlandais,

résidant aux Pays-Bas.

(72) Invention de : Peter Antoon Duijkers.

(73) Titulaire : *Idem* (71)

(74) Mandataire : Georges Bailleul-Langlais, société civile SPID,

209, rue de l'Université, 75007 Paris.

"CIRCUIT SERVANT A DEDUIRE UN SIGNAL DE SYNCHRONISATION

DE TRAME D'UN SIGNAL INCIDENT"

L'invention concerne un circuit servant à déduire un signal de synchronisation de trame d'un signal incident contenant au moins des impulsions de synchronisation de ligne et de trame dont l'amplitude s'étend entre un niveau de référence et un niveau de crête, circuit muni d'un générateur de signaux pour engendrer un signal toutes les fois que, dans le signal incident, il apparaît une impulsion ayant une valeur se situant entre le niveau de référence et le niveau de crête, le signal du générateur de signaux ayant une valeur qui est une mesure de la durée de ladite impulsion, ainsi que d'un étage comparateur pour comparer le signal obtenu avec une valeur de seuil.

Un circuit de ce genre est connu du brevet des Etats-Unis d'Amérique N° 3.678.199. Les impulsions qui provoquent l'apparition d'un signal par le générateur de signaux peuvent être des impulsions de synchronisation de ligne, de synchronisation de trame, voire des impulsions perturbatrices, le niveau de référence de ces impulsions étant le plus souvent très peu différent du niveau de noir de l'information vidéo. Toutefois, la valeur de seuil a été choisie de façon que seules les impulsions de synchronisation de trame soient d'une durée suffisante pour fournir un signal dépassant la valeur de seuil.

Dans ce circuit connu, la valeur de seuil doit être choisie assez élevée, si l'on veut pouvoir faire une distinction tant soit peu sûre entre une impulsion de synchronisation de trame et une autre impulsion, de plus courte durée. Toutefois, si le signal incident est affecté d'un bruit tel, que la valeur de seuil ne sera pas toujours atteinte, alors que, entre deux impulsions successives,

- le signal du générateur de signaux n'est pas égal à zéro, cela risque d'affecter la synchronisation de trame. De plus, il est possible que, même avec un faible bruit, une tension de ronflement soit superposée au signal de télévision, tension de ronflement provenant par exemple d'un amplificateur à fréquence intermédiaire, ce qui provoque un décalage en continu du signal d'entrée, de sorte que la valeur de seuil risque de ne pas être atteinte à l'instant correct.

- 10 L'invention vise à fournir un circuit servant à engendrer dans toutes les conditions un signal de synchronisation de trame plus fiable et, à cet effet, le circuit conforme à l'invention est remarquable en ce qu'il comporte en outre un circuit de porte pour rendre le générateur de signaux inactif pendant l'apparition des impulsions de synchronisation de ligne avant que la valeur de seuil n'ait été atteinte par le signal du générateur de signaux, ce circuit de porte étant lui-même inactif lorsque la valeur de seuil a été atteinte par ledit signal, alors que le circuit engendre le signal de synchronisation de trame lorsque le signal du générateur de signaux atteint une seconde valeur de seuil qui est une mesure de durée d'impulsion supérieure à la durée correspondante à la valeur de seuil précitée.

- 15 20 25 Etant donné que, conformément à l'invention, dans une grande partie du temps, les impulsions de synchronisation de ligne n'exercent pas d'influence sur le signal du générateur de signaux, on peut choisir une première valeur de seuil peu élevée, c'est-à-dire correspondant à une durée d'impulsion relativement courte, tandis que la seconde valeur de seuil, dont l'obtention provoque l'apparition du signal de synchronisation de trame, est élevée. Cela permet d'obtenir un fonctionnement plus sûr consécutif à une plus grande insensibilité aux perturbations.

- 30 35 Dans un mode de réalisation, le circuit selon l'inven-

tion est remarquable en ce que le circuit de porte comporte une porte pour autoriser le passage, en dehors de l'intervalle de suppression de trame, d'impulsions à fréquence de ligne dont la durée contient à peu près celle des impulsions de synchronisation de ligne et pour bloquer l'apport de ces impulsions à fréquence de ligne lorsque le signal du générateur de signaux a atteint la première valeur de seuil.

Le circuit peut être remarquable en ce qu'il comporte un élément monostable servant, lorsque la seconde valeur de seuil a été atteinte par le signal du générateur de signaux et durant un temps prédéterminé, à maintenir ensuite le circuit de porte dans l'état où la porte bloque l'apport des impulsions à fréquence de ligne.

Le générateur de signaux peut être un générateur qui engendre un signal sensiblement linéaire pendant l'apparition d'une impulsion dans le signal incident, remarquable en ce que la pente du signal sensiblement linéaire est moins rapide après que la première valeur de seuil a été atteinte.

De préférence, le circuit conforme à l'invention est remarquable en ce qu'il comporte un élément bistable qui se trouve dans un premier état si le signal du générateur de signaux est inférieur à la première valeur de seuil et dans un second état lorsque ce signal a atteint la première valeur de seuil, le second état étant maintenu jusqu'au moins la fin du signal de synchronisation de trame, second état dans lequel l'élément bistable maintient le circuit de porte dans l'état où il bloque l'apport des impulsions à fréquence de ligne.

La description qui va suivre en regard du dessin annexé, donné à titre d'exemple non limitatif, permettra de mieux comprendre comment l'invention est réalisée.

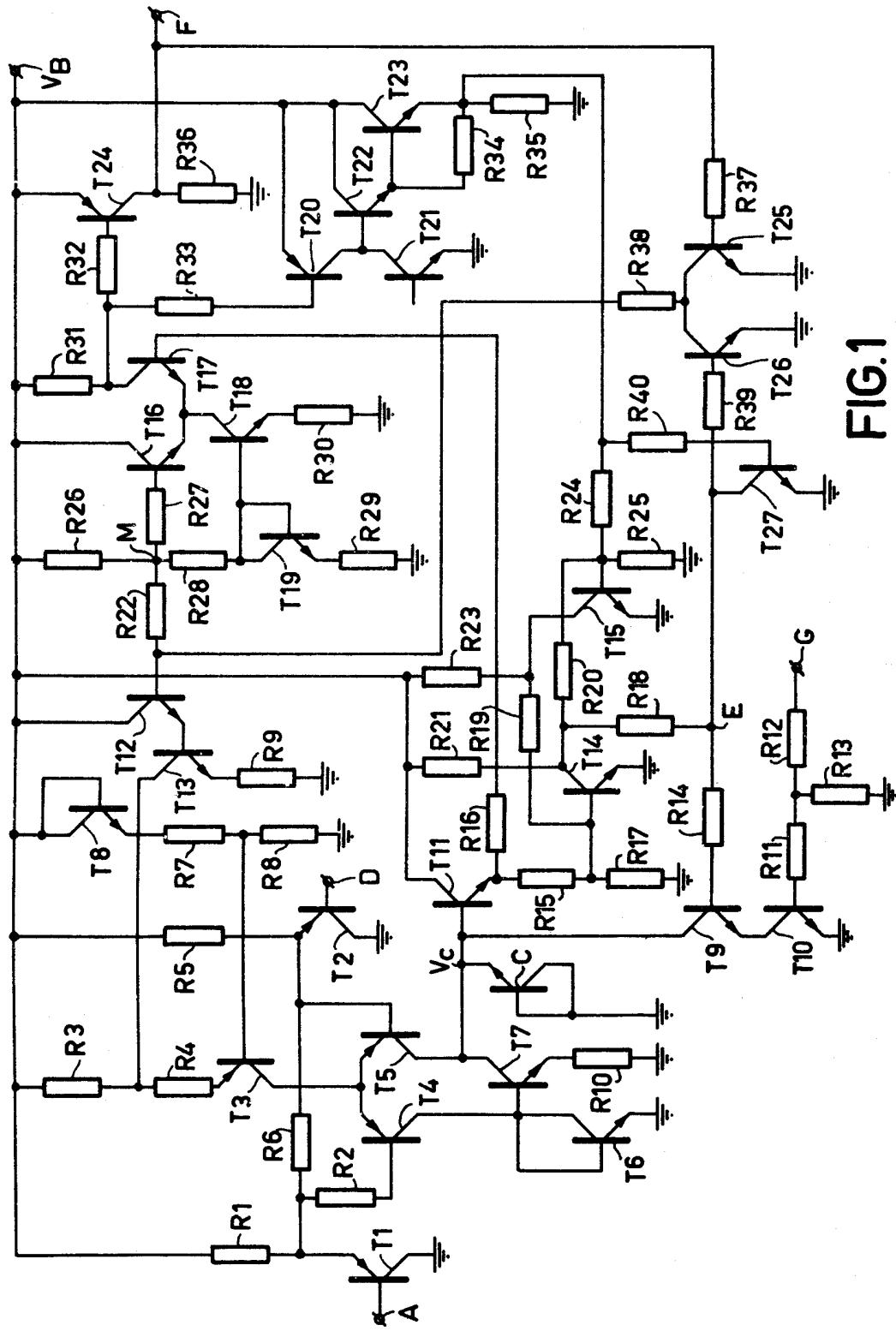

La figure 1 représente un exemple de réalisation du circuit conforme à l'invention, exemple de réalisation qui

convient pour être incorporé dans un circuit intégré pour la génération d'un signal de synchronisation de trame dans un récepteur de télévision.

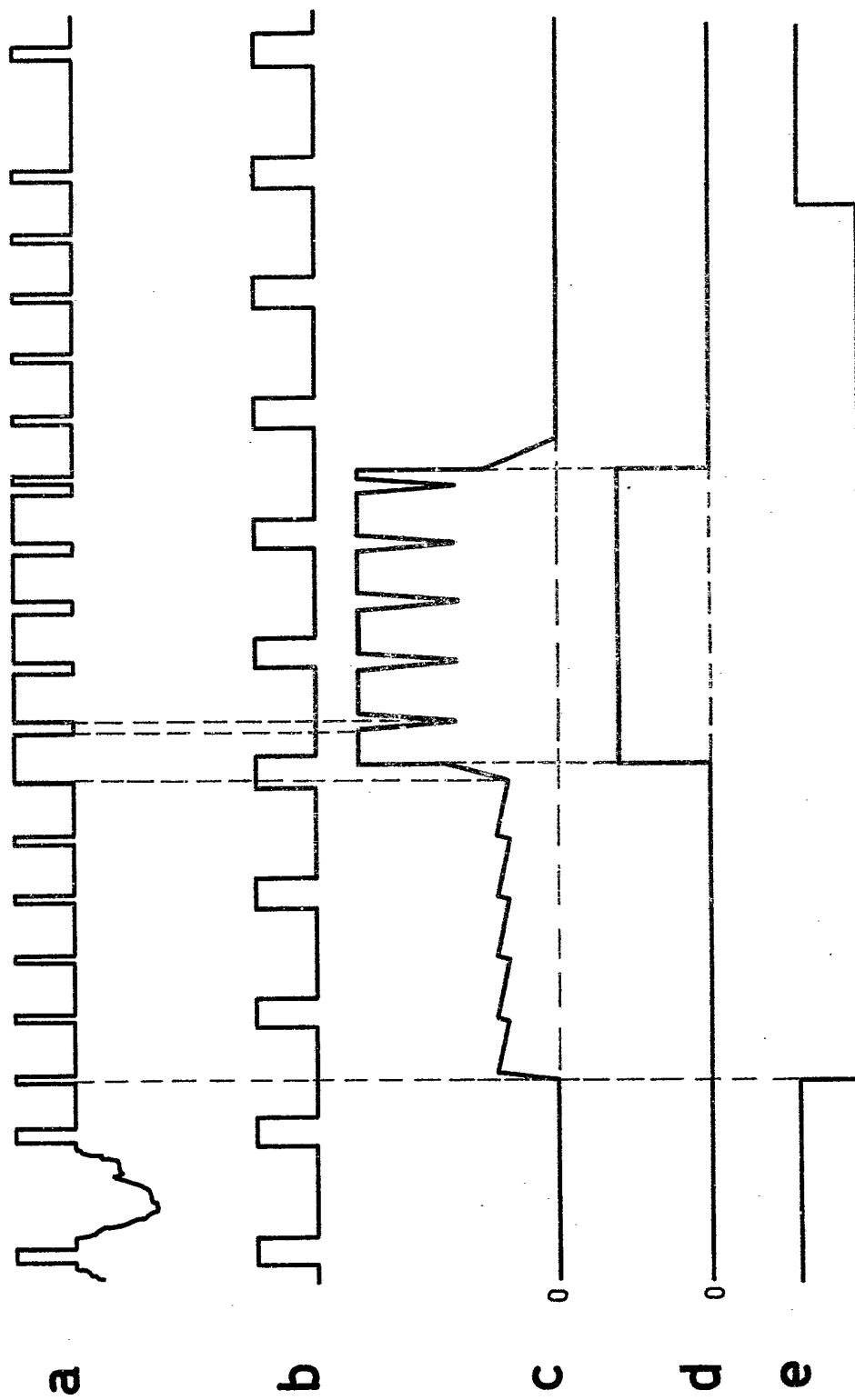

5 La figure 2 représente des formes d'ondes qui, en fonctionnement, sont présentes dans le circuit de la figure 1.

Une borne d'entrée A du circuit de la figure 1 est reliée à la base d'un transistor PNP T1, dont le collecteur est à la masse, alors que l'émetteur est relié au point commun à une résistance R1 de 8,2 k $\Omega$  et à une résistance 10 R2 de 10 k $\Omega$ . De l'autre côté, la résistance R1 est branchée sur la borne positive d'une source de tension d'alimentation V<sub>B</sub> de 12 V, dont la borne négative est mise à la masse. De l'autre côté, la résistance R2 est reliée à la base d'un transistor PNP T<sub>4</sub>, l'autre borne de R<sub>2</sub> étant reliée à une résistance R<sub>6</sub> de 1,5 k $\Omega$ . 15 L'autre borne de la résistance R<sub>6</sub> est reliée à l'émetteur d'un transistor PNP T2 et à la base d'un transistor PNP T5. Le collecteur du transistor T2 est à la masse, alors que la base est raccordée à une borne d'entrée D du circuit et que l'émetteur est branché sur la source V<sub>B</sub> à travers une résistance R5 de 4,3 k $\Omega$ . La borne A est reliée à un circuit vidéo non représenté et la borne D est branchée sur une tension continue de 8 V.

Les émetteurs des transistors T4 et T5 sont interconnectés et reliés au collecteur d'un transistor PNP T3. A travers deux résistances montées en série, R4 de 22 k $\Omega$  et R3 de 1,5 k $\Omega$ , l'émetteur de ce dernier transistor est branché 25 sur la source V<sub>B</sub>, alors que la base est reliée au point commun à une résistance R7 de 1 k $\Omega$  et à une résistance R8 de 15 k $\Omega$ . De l'autre côté, la résistance R7 est reliée à 30 l'émetteur d'un transistor NPN T8, alors que l'autre côté de la résistance R8 est à la masse. Le collecteur et la base du transistor T8 sont branchés l'un et l'autre sur la source V<sub>B</sub>.

Le collecteur du transistor T4 est relié à la base et 35 au collecteur d'un transistor NPN T6 ainsi qu'à la base

d'un transistor NPN T7. L'émetteur du transistor T6 ainsi qu'une résistance d'émetteur R10 de 30 k $\Omega$  du transistor T7 sont à la masse. Les collecteurs des transistors T5 et T7 ainsi que le collecteur d'un transistor NPN T9 et l'émetteur d'un autre transistor PNP sont interconnectés. La base et le collecteur de cet autre transistor sont à la masse. De façon connue, un transistor de ce genre se comporte en fonctionnement comme une faible capacité par rapport à la masse, capacité qui, dans cet exemple, est de 5 l'ordre de 18 pF. Pour cette raison, ce transistor est indiqué par le symbole C sur la figure 1. De plus, l'émetteur du transistor T9 est relié au collecteur d'un transistor NPN T10, dont l'émetteur est à la masse et dont la base est raccordée à une borne d'entrée G à travers deux résistances 10 R11 et R12 montées en série et ayant chacun une valeur de 4,7 k $\Omega$ . Entre le point commun à ces résistances et la masse on a intercalé une résistance R13 de 4,3 k $\Omega$ .

Le point commun aux transistors T5, T7 et T9 et au condensateur C est reliée également à la base d'un transistor NPN T11. Le collecteur du transistor T11 est branché sur la tension V<sub>B</sub>, alors que l'émetteur est relié à une résistance R15 de 6,8 k $\Omega$ . De l'autre côté, la résistance R15 est reliée à une résistance R17 de 6,8 k $\Omega$ , à une résistance R19, également de 6,8 k $\Omega$ , et à la base d'un transistor NPN T14. 15 20 25 30 35 L'autre borne de la résistance R17 ainsi que l'émetteur du transistor T14 sont à la masse. Le collecteur du transistor T14 est relié, d'une part à la base du transistor T9 à travers une résistance R18 de 15 k $\Omega$  et une résistance R14 de 4,7 k $\Omega$  montée en série avec celle-ci, et d'autre part à la base d'un transistor NPN T15 à travers une résistance R20 de 6,8 k $\Omega$ . L'émetteur de ce transistor est à la masse, alors que la base est reliée à l'émetteur d'un transistor NPN T23 à travers une résistance R24 de 4,7 k $\Omega$  et est reliée à la masse à travers une résistance R25 de 6,8 k $\Omega$ . Les résistances de collecteur R21 et R23 des transistors T14 et T15

ont l'une et l'autre une valeur de  $12 \text{ k}\Omega$  et sont branchées l'une et l'autre sur la source  $V_B$ . La borne de la résistance R19 qui n'est pas reliée à la base du transistor T14 est reliée au collecteur du transistor T15. De ce qui précède, il ressort que les transistors T14 et T15 forment avec les résistances correspondantes un élément bistable (flip-flop).

Entre l'émetteur du transistor T11 et la base d'un transistor NPN T17 on a intercalé une résistance R16 de  $1 \text{ k}\Omega$ .

L'émetteur du transistor T17 relié à celui d'un transistor NPN T16 et au collecteur d'un transistor NPN T18 dont l'émetteur est à la masse à travers une résistance R30 de  $200 \Omega$  et dont la base est reliée au collecteur et à la base d'un transistor NPN T19 ainsi qu'à une résistance R28 de  $3,9 \text{ k}\Omega$ . L'émetteur du transistor T19 est à la masse à travers une résistance R29 de  $200 \Omega$ . L'autre extrémité de la résistance R28 est reliée à la base du transistor T16 à travers une résistance R27 de  $1,5 \text{ k}\Omega$ , à la base d'un transistor NPN T12 à travers une résistance R22 de  $3 \text{ k}\Omega$  et à la source  $V_B$  à travers une résistance R26 de  $9,1 \text{ k}\Omega$ . Les collecteurs des transistors T12 et T16 sont l'un et l'autre reliés directement à la source  $V_B$ , alors que celui du transistor T17 est relié à la source  $V_B$  à travers une résistance R31 de  $4,7 \text{ k}\Omega$ . L'émetteur du transistor T12 est relié à la base d'un transistor NPN T13 dont le collecteur est relié au point commun aux résistances R3 et R4 et dont l'émetteur est à la masse à travers une résistance R9 de  $8,2 \text{ k}\Omega$ .

A travers une résistance R32 de  $2 \text{ k}\Omega$ , le collecteur du transistor T17 est relié à la base d'un transistor PNP T24 et à travers une résistance R33 de  $2 \text{ k}\Omega$  à celle d'un transistor PNP T20 dont l'émetteur est raccordé à la tension  $V_B$ . Le collecteur du transistor T24 est à la masse à travers une résistance R36 de  $12 \text{ k}\Omega$  et est relié à la base d'un transistor NPN T25 à travers une résistance R37 de  $11 \text{ k}\Omega$ .

Ledit collecteur est raccordé en outre à la borne de sortie

F du circuit. Le collecteur du transistor T20 est relié à celui d'un transistor NPN T21 et à la base d'un transistor NPN T22. L'émetteur du transistor T22 est relié directement à la base du transistor T23, alors qu'il est relié à travers une résistance R34 de 16 kΩ à l'émetteur de celui-ci. 5 L'émetteur du transistor T21 est mis directement à la masse, alors que celui du transistor T23 est mis à la masse à travers une résistance R35 de 10 kΩ. Les collecteurs des transistors T22 et T23 sont branchés sur la tension  $V_B$ . La 10 base du transistor T21 est "en l'air", de sorte que ce transistor se comporte en fonctionnement comme une faible capacité de 1 à 2 pF.

Entre la base du transistor NPN T26 et le point commun E aux résistances R14 et R18, on a intercalé une résistance R39 de 4,7 kΩ. Au dit point commun, on a relié en outre le collecteur d'un transistor NPN T27. Les collecteurs des transistors T25 et T26 sont directement interconnectés, alors qu'ils sont reliés à la base du transistor T12 à travers une résistance R38 de 2,4 kΩ. Entre la base du transistor T27 et l'émetteur du transistor T23, est intercalée une résistance R40 de 4,7 kΩ. Enfin, les émetteurs des transistors T25, T26 et T27 sont à la masse. 15 20

En fonctionnement, un signal **vidéo négatif** est appliqué sur la borne A. A l'aide du transistor T8, qui fait fonction de diode, et des résistances R7 et R8, la base du transistor T3 est polarisée à une tension quasi constante. Le transistor T3 constitue une source de courant dont le courant traverse, soit le transistor T4, soit le transistor T5. 25 30 Les transistors T4 et T5 constituent un amplificateur différentiel : si la tension sur la borne A est supérieure à celle présente sur la borne D, c'est-à-dire si la tension sur la base du transistor T4 est supérieure à celle présente sur la base du transistor T5, le transistor T5 est conducteur tandis que sont bloqués le transistor T4 ainsi que le transistor T6 faisant fonction de diode, et donc également 35

-8-

le transistor T7, qui forme un miroir de courant avec le transistor T6. Dans ces conditions, le condensateur C est chargé par le courant de collecteur du transistor T5. Le niveau de tension continue sur la borne A a été choisi suffisamment élevé par rapport à celui présent sur la borne D pour que cette charge ne puisse avoir lieu que si le signal d'entrée dépasse le niveau de référence, par exemple lors de l'apparition d'impulsions de synchronisation de ligne.

Les transistors T2 à T7 et le condensateur C forment un générateur de signaux.

Toutefois, à la borne G sont appliquées des impulsions de suppression de retour de ligne issues d'un circuit de déviation de ligne non représenté, et qui sont traitées dans une partie non représentée du circuit intégré dont fait partie le circuit de la figure 1. Pendant chaque période de ligne (de l'ordre de 64  $\mu$ s), ces impulsions présentent une valeur positive durant environ 12  $\mu$ s. Pendant cet intervalle de temps, le temps de retour de ligne, le transistor T10 est rendu conducteur, tandis que durant le reste de la période de ligne, le temps d'aller de ligne, l'amplitude des impulsions est trop faible pour que le transistor T10 soit rendu conducteur.

Si la tension  $V_c$  aux bornes du condensateur C est inférieure à une valeur déterminée, le transistor T11 et, par conséquent, le transistor T14 ne sont pas conducteurs. Le collecteur du transistor T14 est porté à la tension  $V_B$  et la tension au point E est élevée. Toutefois, tant que la tension appliquée à la borne G est basse, les transistors T9 et T10 ne peuvent pas être conducteurs. Durant le temps de retour de ligne, le transistor T5 aussi bien que les transistors T9 et T10 sont conducteurs. La tension sur le collecteur du transistor T9 est maintenue très basse, de sorte que les impulsions de synchronisation de ligne qui, durant le temps de retour de ligne, apparaissent dans le signal de la borne A, ne peuvent pas provoquer de charge sur le condensateur C. Il en est de même pour des impulsions perturbatrices qui, pendant ledit temps, appa-

raissent sur la borne A. Durant le temps d'aller de ligne, la tension vidéo appliquée à la borne A est toujours inférieure à 8 V et le condensateur C est déchargé par le courant de collecteur du transistor T7 qui est conducteur par suite de l'état conducteur du transistor T4. Etant donné la valeur relativement élevée de la résistance R10, ce courant de décharge est assez faible, de sorte que la tension  $V_C$  diminue lentement.

De ce qui précède, il ressort que la tension  $V_C$  est à peu près égale à zéro à la fin du temps d'aller de trame. Dans l'intervalle de suppression de trame qui se produit ensuite, il apparaît d'abord cinq impulsions de pré-égalisation d'une durée de l'ordre de 2,3  $\mu$ s avec un écart de temps d'une demi-période de ligne, soit 32  $\mu$ s environ. Ces impulsions sont suivies de cinq impulsions de synchronisation de trame dont la durée totale est également de 2,5 périodes de ligne et entre lesquelles apparaissent des impulsions de hachage de trame dont la durée est égale à celle des impulsions de synchronisation de ligne, à savoir de l'ordre de 4,7  $\mu$ s. Celles-ci sont suivies de cinq impulsions de post-égalisation. Cela s'applique à la norme de télévision européenne. D'autres normes de télévision, par exemple la norme américaine, diffèrent en quelques détails, ce qui n'a pas d'importance pour l'invention.

La figure 2a représente le signal vidéo présent sur la borne A à savoir pour une partie de l'une des deux trames qui forment une image, en l'espèce la trame se terminant par une ligne entière. De plus, cette figure représente la période de ligne qui vient immédiatement après l'intervalle de post-égalisation. Celle-ci est suivie d'un certain nombre d'autres périodes de ligne jusqu'au commencement d'un nouvel aller de trame. La figure 2b représente le signal appliqué à la borne G. Des figures 2a et 2b, il ressort que la première impulsion de pré-égalisation qui, en effet, ne coïncide pas avec une impulsion de retour de ligne, provoque

-10-

la charge du condensateur C. La tension  $V_C$  (voir figure 2c), qui était pratiquement égale à zéro, augmente alors d'une manière à peu près linéaire.

Le transistor T26 étant conducteur, la tension au point 5 commun M aux résistances R22, R26, R27 et R28 est ajustée à une faible valeur à l'aide des résistances R22, R26, R28, R29 et R38 ainsi qu'à l'aide du transistor T19 faisant fonction de diode. Le transistor T16 est conducteur, tandis que le 10 transistor T17 qui, avec le transistor T16 et le transistor T18 faisant fonction de source de courant, forme un amplificateur différentiel, est bloqué. Comme le transistor T17 est bloqué, le collecteur de ce transistor est porté à la tension  $V_B$ , de sorte que les transistors T20 et T24, et donc également les transistors T22 et T23, sont bloqués, 15 ce qui a pour effet que la tension de sortie sur la borne F (voir figure 2d) ainsi que la tension sur l'émetteur du transistor T23 sont égales à zéro. Les transistors T25 et T27, eux aussi sont bloqués.

Tant que la tension sur la base du transistor T11 est 20 trop basse pour rendre ce transistor conducteur, le transistor T14 reste également bloqué. La tension au point E (voir figure 2e) est élevée, mais, étant donné que la tension appliquée à la borne G est basse, le transistor T9 ne peut pas être conducteur. Le transistor T15, dont la base 25 est branchée sur la tension  $V_B$  à travers la résistance R20, est conducteur. De la même manière, le transistor T26 est conducteur du fait que sa résistance de base R39 est reliée au point E. Le transistor T12, dont la base est reliée au point M à travers la résistance R22 et à la masse à travers 30 la résistance R38, et donc également le transistor T13 sont traversés par un faible courant de collecteur. Le courant d'émetteur du transistor T3 et en conséquence le courant de charge du condensateur C ont une valeur élevée, de sorte que la tension  $V_C$  augmente assez rapidement.

35 Le transistor T11 fait fonction de détecteur de niveau.

Dès que la tension  $V_C$  dépasse la valeur égale au double de la tension de seuil base-émetteur d'un transistor conducteur, soit environ 1,5 V, le transistor T11 et, par conséquent, le transistor T14 deviennent conducteurs. La tension sur le collecteur du transistor T14 et celle du point E (voir figure 2e) deviennent à peu près égales à zéro.

À travers la résistance R18, cette diminution est transmise à la base du transistor T26 et, à travers la résistance R20, elle est transmise à la base du transistor T15, de sorte que ces transistors se bloquent. L'augmentation de tension qui se produit alors sur le collecteur du transistor T15 est transmise à la base du transistor T14 à travers la résistance R19. La mise en conduction du transistor T14 est donc un effet cumulatif, ce qui fait que **la bascule bistable constituée par les transistors T14 et T15 change d'état.**

Comme le transistor T26 est bloqué, la tension au point M prend une valeur élevée, à savoir de l'ordre de 4,2 volts, de sorte qu'il y a augmentation du courant d'émetteur du transistor T12 et par conséquent de celui du transistor T13.

Le courant de collecteur du transistor T13 circule dans la résistance R3 et entre en déduction du courant d'émetteur du transistor T3. Ainsi, le courant de charge du condensateur C prend une valeur plus faible, à savoir environ dix fois, et la tension  $V_C$  augmente moins vite. Tant que la tension sur l'émetteur du transistor T11 est inférieure à 4,2 volts environ, le transistor T17 reste bloqué. L'état des transistors T20, T22, T23, T24, T25 et T27 reste donc inchangé, et le signal de sortie reste égal à zéro.

La seconde valeur du courant de charge est tellement faible et la valeur de l'ordre de 4,2 volts a été choisie tellement grande que la durée de l'impulsion d'égalisation est trop courte pour provoquer l'obtention de cette valeur. À la fin de l'apparition de l'impulsion, la tension appliquée à la borne A diminue, de sorte que les transistors T4 et T6 et, par conséquent, le transistor T7 deviennent

conducteurs, tandis que le transistor T6 est bloqué. De ce fait, le courant de décharge du condensateur C est faible et la tension  $V_C$  diminue lentement. Le transistor T11 reste donc conducteur, mais l'état du reste du circuit et **notamment** 5 **de la bascule bistable** T14,T15 ne change en aucune façon. Comme la tension au point E reste basse, le transistor T9 ne peut pas être conducteur. L'impulsion de retour de ligne apparaissant sur la borne G après la première impulsion de pré-égalisation n'exerce donc pas d'influence sur la tension 10  $V_C$ . Il en est de même pour les impulsions de retour de ligne qui viennent après, alors que les autres impulsions de pré-égalisation provoquent chaque fois une faible augmentation de la tension  $V_C$ , de sorte que la tension  $V_C$  varie peu.

Comme l'impulsion de synchronisation de trame a une 15 plus longue durée que l'impulsion d'égalisation, la tension sur l'émetteur du transistor T11 peut atteindre la valeur de l'ordre de 4,2 volts après l'apparition du flanc avant de cette impulsion de synchronisation de trame. Le circuit, et notamment le courant de charge, sont dimensionnés de 20 façon que ce second niveau soit atteint 15  $\mu s$  environ après le premier, de sorte que le transistor T17 devient conducteur et le transistor T16 non conducteur. Ces transistors font donc fonction de second détecteur de niveau. La tension sur le collecteur du transistor T17 diminue, de sorte que 25 les transistors T20 et T24 deviennent conducteurs. Un flanc positif est maintenant présent sur la borne de sortie F, et sous l'effet de celui-ci, le transistor T25 devient conducteur. L'extrémité inférieure de la résistance R38 est maintenant pratiquement à la masse et la tension au point M prend une plus faible valeur. De ce fait, les transistors 30 T12 et T13 sont moins conducteurs et le courant de charge du condensateur C prend une plus grande valeur. La tension  $V_C$  augmente rapidement jusqu'à atteindre la tension de Zéner, soit environ 7 volts, de la diode semiconductrice dont est 35 constitué le condensateur C, après quoi la tension  $V_C$

n'augmente plus. La valeur élevée du courant de charge fait que la tension  $V_C$  atteigne ce niveau élevé avant l'apparition de la première impulsion de hachage de trame.

Le courant de collecteur du transistor T20 provoque la charge assez rapide du petit condensateur formé par le transistor T21. Les transistors T22 et T23 deviennent conducteurs, de sorte que les transistors T15 et T27, eux aussi, deviennent conducteurs. La tension au point E reste basse et les transistors T9 et T26 restent bloqués. Etant donné que les bases des transistors T14 et T15 sont portées à une tension positive, **la bascule bistable T14, T15 ne peut basculer.**

Lors de l'apparition des impulsions de hachage de trame, la tension appliquée à la borne A reprend la valeur du niveau de référence. De ce fait, le condensateur C est déchargé et la tension  $V_C$  diminue. Comme le transistor T25 est conducteur, l'extrémité de la résistance R38 qui n'est pas reliée à la résistance R22 est mise à la masse, de sorte que la valeur de la seconde tension de seuil au point M est inférieure à 4,2 volts. La tension sur l'émetteur du transistor T11 décroît, elle aussi, mais à cause de la courte durée de l'impulsion de hachage, cette tension ne diminue pas jusqu'au dessous de la valeur de la tension au point M, de sorte que le transistor T17 reste conducteur et que la tension à la borne F reste élevée. Les impulsions de retour de ligne qui sont présentes sur la borne G n'exercent pas d'influence, puisque le transistor T9 est toujours bloqué.

Après la dernière impulsion de synchronisation de trame et la première impulsion de post-égalisation apparaissant peu après celle-ci, le condensateur C est rapidement déchargé. Comme l'intervalle de temps précédent l'impulsion d'égalisation suivante est suffisamment long, la tension sur l'émetteur du transistor T11, diminue cette fois jusqu'au dessous de la nouvelle valeur de la seconde tension de seuil, de sorte que le transistor T17 est bloqué tandis que le transistor T16 devient conducteur. Les transistors T20

-14-

et T24 sont bloqués et la tension de sortie à la borne F devient égale à zéro. Le condensateur formé par le transistor T21 se décharge vers la base du transistor T22. Comme cette base a une résistance apparente élevée, cette décharge prend un certain temps, qui peut être ajusté par la valeur de la résistance R34 et durant lequel les transistors T22 et T23 restent conducteurs. L'état de la bascule bistable T14, T15 ne change pas, de sorte que, durant ledit temps, des impulsions de post-égalisation et des impulsions de courant ne peuvent produire aucun effet.

Par suite du blocage du transistor T14, le transistor T25 est également bloqué, de sorte que la tension sur le point M redevient élevée. Le condensateur C continue à être déchargé lentement. A l'instant où le transistor T11 est bloqué, la base du transistor T14 ne reçoit plus de tension positive. Le basculement de la bascule bistable T14, T15 peut maintenant avoir lieu. Le transistor T15 est alors conducteur tandis que le transistor T14 est bloqué.

Vers la fin de l'intervalle de post-égalisation, le condensateur formé par le transistor T21 est déchargé au point que les transistors T22 et T23 sont bloqués, de sorte que le transistor T27 devient non conducteur. Étant donné que, depuis le basculement de la bascule bistable T14, T15, la tension sur le collecteur du transistor T14 est élevée, la tension sur le point E, elle aussi, devient élevée, ce qui rend les transistors T9 et T26 conducteurs. La tension sur le point M devient basse et le courant des transistors T12 et T13 est de faible valeur, de sorte que le courant d'émetteur du transistor T3 est élevé. Le condensateur C est donc déchargé à coup sûr. Le circuit se trouve maintenant dans le même état qu'à la fin du temps aller de trame.

Si une impulsion perturbatrice de polarité positive apparaît dans le signal sur la borne A, cette impulsion peut provoquer une augmentation de la tension  $V_C$ , voire même, pour une durée d'impulsion suffisante, la conduction du

transistor T11 mais en règle générale, la durée de l'impulsion sera trop courte, c'est-à-dire inférieure à 15  $\mu$ s environ, pour provoquer la conduction du transistor T17 et donc la génération d'un signal de sortie. La prochaine impulsion de retour de ligne, qui est présente sur la borne G et qui rend conducteur le transistor T10, court-circuite la tension  $V_C$  par rapport à la masse. Si, sous l'effet de l'impulsion perturbatrice, le transistor T11 a été rendu conducteur, la bascule bistable T14,T15 a déjà basculé à cet instant, de sorte que la tension sur le point M et, par conséquent, le courant de collecteur du transistor T13 ont pris une valeur élevée. Une impulsion perturbatrice suivante ne provoquera donc qu'un faible courant de charge du condensateur C. La tension  $V_C$  reste basse, et cela jusqu'à l'apparition du train suivant d'impulsions de pré-égalisation. Dans ce cas, la trame se termine par une demi-ligne et la première impulsion de pré-égalisation coïncide avec une impulsion de retour de ligne. Si, le circuit n'a pas été amené sous l'effet d'une impulsion de perturbation dans l'état préparatoire, dans lequel la tension  $V_C$  a atteint la première valeur de seuil, cet état n'est pas provoqué par la première impulsion de pré-égalisation mais par la seconde. Si le signal d'entrée est affecté d'un bruit tel que la première impulsion de pré-égalisation, dans le cas de la trame représentée sur la figure 2, ou la deuxième impulsion de pré-égalisation, dans le cas de la trame suivante, ne provoque pas l'état préparatoire, cet état sera provoqué pour une trame par la troisième ou la cinquième, ou pour la trame suivante par la quatrième impulsion de pré-égalisation. Si ces impulsions sont "manquées", elles aussi, la tension  $V_C$  atteint la première valeur de seuil et ensuite la seconde, sous l'effet de la première impulsion de synchronisation de trame. C'est seulement dans le cas où cela ne se produit pas que le circuit de la figure 1 n'engendre pas de signal de sortie, mais le signal de télévision reçu par le récep-

teur de télévision dont fait partie le circuit est alors affecté d'un tel bruit qu'il est de toute façon impossible d'obtenir une image **observable**.

De ce qui précède, il ressort que le circuit de la figure 1 engendre sur la borne F une **impulsion raisonnablement fiable**, dont le flanc avant apparaît au bout d'un laps de temps constant après le flanc avant de la première impulsion de synchronisation de trame, et dont le flanc arrière apparaît au bout d'un laps de temps constant après le flanc arrière de la dernière impulsion de synchronisation de trame, et qui, par conséquent, convient pour être appliquée comme signal de synchronisation de trame à un circuit de synchronisation de trame raccordé à la borne F. Cela s'applique également dans le cas où le signal d'entrée est un signal non standard, c'est-à-dire un signal qui ne contient pas d'impulsions d'égalisation. Il est à noter à ce sujet qu'un défaut d'interlignage est évité du fait que les impulsions de retour de ligne appliquées à la borne G n'ont aucune influence lors de l'apparition de la première impulsion de synchronisation de trame. S'il en était autrement, la charge du condensateur G ne pourrait commencer qu'après le flanc arrière de l'impulsion de retour de ligne apparaissant à peu près simultanément avec cette impulsion, ce qui impliquerait un décalage du flanc avant de l'impulsion de la figure 2d. Toutefois, lors de la trame suivante, ce décalage ne se produirait pas du fait qu'une impulsion de retour de ligne ne coïncide pas avec la première impulsion de synchronisation de trame, si bien qu'une trame commencerait environ  $12 \mu\text{s}$  en retard alors que l'autre trame commencerait à temps. Il est à remarquer en outre que l'information vidéo contenue dans le signal de la figure 2a n'a aucune influence en ce qui concerne la génération du signal de synchronisation de trame, de sorte que le signal appliqué à la borne A peut être un signal composite de synchronisation de télévision, c'est-à-dire un signal ne comportant pas d'information vidéo.

Dans le circuit de la figure 1, la bascule bistable T14, T15 fait fonction d'élément de mémoire. Ceci fait qu'après l'obtention de la première valeur de seuil, l'application d'impulsions de retour de ligne au circuit n'a pas d'influence, alors que la charge du condensateur C s'effectue lentement. En l'**absence de la bascule bistable**, la tension  $V_C$  diminuerait rapidement après l'apparition de la première impulsion de pré-égalisation de sorte que, en présence de beaucoup de bruit et de peu de perturbations, le premier niveau de seuil risquerait de ne pas être atteint au cours de l'intervalle de pré-égalisation. Cela pourrait donner lieu à un défaut d'interlignage.

Il est clair que des parties du circuit de la figure 1 peuvent être réalisées d'une autre manière. Ainsi, la partie comportant les transistors T20, T21, T22 et T23 peut être remplacée par un élément monostable, puisque ces transistors fonctionnent comme un tel élément, alors que les transistors T25 et T26 constituent une porte OU et les transistors T9 et T10 une porte ET. La commutation du courant de charge ou du courant de décharge du condensateur C peut s'effectuer d'une autre manière connue. Au lieu de cela, il est possible de commuter ledit condensateur sur une autre valeur. La durée des impulsions à fréquence de ligne appliquées à la borne G n'est pas critique : la seule exigence est que ces impulsions comportent à coup sûr les impulsions de synchronisation de ligne du signal appliqué à la borne A, mais il est clair que leur durée doit être inférieure à 32  $\mu$ s.

REVENDICATIONS :

1.- Circuit servant à déduire un signal de synchronisation de trame d'un signal incident contenant au moins des impulsions de synchronisation de ligne et de trame dont l'amplitude s'étend entre un niveau de référence et un niveau de crête, circuit muni d'un générateur de signaux pour engendrer un signal toutes les fois que, dans le signal incident, il apparaît une impulsion ayant une valeur se situant entre le niveau de référence et le niveau de crête, le signal du générateur de signaux ayant une valeur qui est une mesure de la durée de ladite impulsion, ainsi que d'un étage comparateur pour comparer le signal obtenu avec une valeur de seuil, caractérisé en ce que le circuit comporte en outre un circuit de porte (T9,T10) pour rendre le générateur de signaux (T2-T7,C) inactif pendant l'apparition des impulsions de synchronisation de ligne avant que la valeur de seuil n'ait été atteinte par le signal ( $V_C$ ) du générateur de signaux, ce circuit de porte étant lui-même inactif lorsque la valeur de seuil a été atteinte par ledit signal, alors que le circuit engendre le signal de synchronisation de trame (en F) lorsque le signal du générateur de signaux atteint une seconde valeur de seuil qui est une mesure d'une durée d'impulsion supérieure à la durée correspondante à la valeur de seuil précitée.

2.- Circuit selon la revendication 1, caractérisé en ce que le circuit de porte (T9,T10) comporte une porte (T10) pour autoriser le passage, en dehors de l'intervalle de suppression de trame, d'impulsions à fréquence de ligne (en G) dont la durée contient à peu près celle des impulsions de synchronisation de ligne et pour bloquer l'apport de ces impulsions à fréquence de ligne lorsque le signal du générateur de signaux (T2-T7, C) a atteint la première valeur de seuil.

3.- Circuit selon la revendication 2, caractérisé en ce qu'il comporte un élément monostable (T20,T23) servant, lorsque la seconde valeur de seuil a été atteinte par le

signal ( $V_C$ ) du générateur de signaux (T2,T7 C) et durant un temps prédéterminé, à maintenir ensuite le circuit de porte (T9,T10) dans l'état où la porte (T10) bloque l'apport des impulsions à fréquence de ligne (en G).

5 4.- Circuit selon l'une quelconque des revendications 2 et 3, caractérisé en ce que les impulsions à fréquence de ligne (en G) sont des impulsions de suppression de retour de ligne issues d'un circuit de déviation de ligne.

10 5.- Circuit selon la revendication 1, dans lequel le générateur de signaux engendre un signal sensiblement linéaire pendant l'apparition d'une impulsion dans le signal incident (en A), caractérisé en ce que la pente du signal sensiblement linéaire ( $V_C$ ) est moins rapide après que la première valeur de seuil a été atteinte.

15 6.- Circuit selon la revendication 5, caractérisé en ce que la pente du signal sensiblement linéaire ( $V_C$ ) est plus rapide après que la seconde valeur de seuil a été atteinte.

20 7.- Circuit selon les revendications 1 et 2, caractérisé en ce qu'il comporte un élément bistable (T14,T15) qui se trouve dans un premier état si le signal ( $V_C$ ) du générateur de signaux (T2,T7 C) est inférieur à la première valeur de seuil et dans un second état lorsque ce signal a atteint la première valeur de seuil, le second état étant 25 maintenu jusqu'au moins la fin du signal de synchronisation de trame, second état dans lequel l'élément bistable maintient le circuit de porte (T9,T10) dans l'état où la porte bloque l'apport des impulsions à fréquence de ligne (en G).

30 8.- Circuit selon les revendications 3 et 7, caractérisé en ce que l'élément monostable (T20,T23) est couplé à l'élément bistable (T14,T15) pour amener celui-ci dans son premier état.

35 9.- Circuit selon la revendication 3, caractérisé en ce qu'il comporte en outre un second étage comparateur (T16, T18) pour comparer le signal ( $V_C$ ) du générateur de signaux

2501945

-20-

(T2,T7 C) avec la seconde valeur de seuil et pour faire basculer l'élément monostable (T20,T23) lorsque ledit signal a atteint cette seconde valeur.

1/2

FIG.1

2501945

2/2

FIG.2