(19) 日本国特許庁(JP)

## (12) 公開特許公報(A)

(11) 特許出願公開番号

特開2005-293427

(P2005-293427A)

(43) 公開日 平成17年10月20日(2005.10.20)

(51) Int.Cl.<sup>7</sup>

F 1

テーマコード(参考)

G06F 13/28

G06F 13/28

310J

5B061

G06F 13/36

G06F 13/36

310F

5B077

G06F 13/38

G06F 13/38

310C

審査請求 未請求 請求項の数 8 O L (全 17 頁)

(21) 出願番号

特願2004-110465 (P2004-110465)

(22) 出願日

平成16年4月2日 (2004.4.2)

(71) 出願人 000005821

松下電器産業株式会社

大阪府門真市大字門真1006番地

(74) 代理人 100098291

弁理士 小笠原 史朗

(72) 発明者 小谷 敦

大阪府門真市大字門真1006番地 松下

電器産業株式会社内

F ターム(参考) 5B061 BA03 BB01 DD09 FF04 GG01

RR01

5B077 AA17 BA02 BA07 DD09 DD21

MM01

(54) 【発明の名称】データ転送処理装置及びデータ転送処理方法

## (57) 【要約】

【課題】異なるプロトコル又は周波数で動作する複数のシステムバスにおいて、DMAデータ転送の効率及びシステムバスの使用効率を向上できるデータ転送処理装置を提供する。

【解決手段】転送要求処理部10は、要求されているデータの種類を確認し、並列的なデータ転送が必要である場合には、第1のDMAC12に第1のデータバッファ16を、第2のDMAC13に第2のデータバッファ17を、それぞれ割り当て、不必要である場合には、現在起動している第1のDMAC12又は第2のDMAC13に、第1のデータバッファ16及び第2のデータバッファ17の両方を割り当てる転送モードを、転送モード設定部11に設定する。第1のDMAC12及び/又は第2のDMAC13は、転送モードで指示されたデータバッファを用いてデータ転送を実行する。

【選択図】 図1

**【特許請求の範囲】****【請求項 1】**

異なるプロトコル又は周波数で動作する複数のシステムバス間において、ダイレクト・メモリ・アクセス転送方式によるデータ転送を実行するデータ転送処理装置であって、

転送データを一時的に格納する複数のデータバッファと、

前記データバッファの少なくとも1つを用いて、システムバス間のデータ転送を実行する複数のダイレクト・メモリ・アクセス・コントローラと、

データ転送状態に応じて、前記複数のダイレクト・メモリ・アクセス・コントローラが使用する前記データバッファを動的に割り当てるバッファ割り当て部とを備える、データ転送処理装置。

10

**【請求項 2】**

前記バッファ割り当て部は、前記複数のダイレクト・メモリ・アクセス・コントローラのそれぞれについて、データ転送に使用できる前記データバッファが1つであるシングルモード又は複数であるマルチモードを、転送されるデータの種別に基づいて設定する転送モード設定部を含み、

前記複数のダイレクト・メモリ・アクセス・コントローラは、前記転送モード設定部の設定モードに従って、各々のデータ転送に使用可能な前記データバッファを決定することを特徴とする、請求項1に記載のデータ転送処理装置。

20

**【請求項 3】**

前記バッファ割り当て部は、前記複数のダイレクト・メモリ・アクセス・コントローラのそれぞれについて、実際にデータ転送に使用している前記データバッファに関する情報を設定するステータス設定部を含み、

データ転送を実行しようとする前記ダイレクト・メモリ・アクセス・コントローラは、前記ステータス設定部に設定された情報に従って、自己のデータ転送に使用可能な前記データバッファを決定することを特徴とする、請求項1に記載のデータ転送処理装置。

30

**【請求項 4】**

前記バッファ割り当て部は、使用可能な前記データバッファの使用権を調停するデータバッファ調停制御部をさらに含み、

データ転送を実行しようとする前記ダイレクト・メモリ・アクセス・コントローラは、前記ステータス設定部に設定された情報に従って直ちにデータ転送が開始できない場合には、前記データバッファ調停制御部によって与えられる使用権に従って、自己のデータ転送に使用可能な前記データバッファを決定することを特徴とする、請求項3に記載のデータ転送処理装置。

40

**【請求項 5】**

前記複数のダイレクト・メモリ・アクセス・コントローラは、それぞれ、データ転送実行中にデータ転送相手の装置によって転送が中断された回数を記憶する遮断回数保持部を含み、

前記データバッファを2つ以上使用している前記ダイレクト・メモリ・アクセス・コントローラは、前記遮断回数保持部が記憶する回数が所定の回数に達した場合、使用している前記データバッファの数を減少させることを特徴とする、請求項3又は4に記載のデータ転送処理装置。

50

**【請求項 6】**

前記複数のデータバッファは、格納領域を任意に区分して使用するマルチポートのデータバッファで構成され、

前記バッファ割り当て部は、

データ転送を要求する装置毎に、データ転送に必要なデータバッファの段数及び構成に関する情報を予め記憶したバッファ領域対応テーブルと、

前記ダイレクト・メモリ・アクセス・コントローラに割り当てる前記マルチポートのデータバッファの格納領域区分を、前記バッファ領域対応テーブルの記憶情報に基づいて制御するバッファ領域管理部とを含み、

50

データ転送を実行しようとする前記ダイレクト・メモリ・アクセス・コントローラは、前記バッファ領域管理部によって区分されるエリアを、自己のデータ転送に使用可能な前記データバッファとして決定することを特徴とする、請求項1に記載のデータ転送処理装置。

【請求項7】

転送データを一時的に格納する複数のデータバッファと、データバッファの少なくとも1つを用いて、システムバス間のデータ転送を実行する複数のダイレクト・メモリ・アクセス・コントローラとを備えた装置が、異なるプロトコル又は周波数で動作する複数のシステムバス間において、ダイレクト・メモリ・アクセス転送方式によるデータ転送を実行するデータ転送処理方法であって、

10

システムバス上のデータ転送状態を判断するステップと、

前記判断するステップの判断に応じて、前記複数のダイレクト・メモリ・アクセス・コントローラが使用する前記データバッファを動的に割り当てるステップと、

前記割り当てるステップで割り当てられた前記データバッファを使用してデータ転送を実行するステップとを備える、データ転送処理方法。

【請求項8】

異なるプロトコル又は周波数で動作する複数のシステムバス間において、ダイレクト・メモリ・アクセス転送方式によるデータ転送を実行するデータ転送処理装置の集積回路であって、

20

転送データを一時的に格納する複数のデータバッファと、

前記データバッファの少なくとも1つを用いて、システムバス間のデータ転送を実行する複数のダイレクト・メモリ・アクセス・コントローラと、

データ転送状態に応じて、前記複数のダイレクト・メモリ・アクセス・コントローラが使用する前記データバッファを動的に割り当てるバッファ割り当て部とを集積した、集積回路。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、データ転送処理装置及びデータ転送処理方法に関し、異なるプロトコル又は周波数で動作する複数のシステムバス間において、ダイレクト・メモリ・アクセス(DMA)転送方式によるデータ転送を実行するデータ転送処理装置(バスブリッジ等)、及びデータ転送処理方法に関する。

30

【背景技術】

【0002】

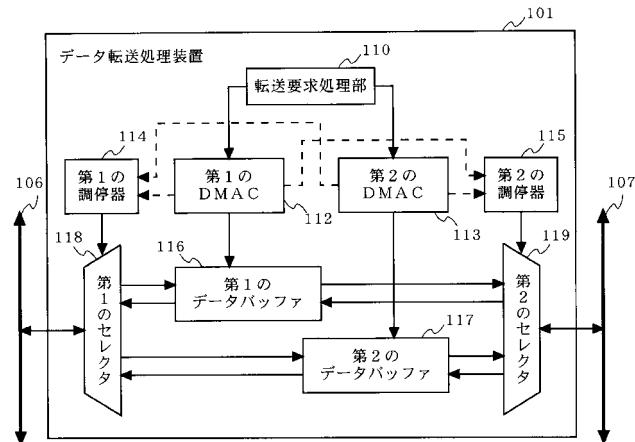

従来のDMA転送方式によるデータ転送処理装置の構成例を、図12に示す。図12において、従来のデータ転送処理装置101は、転送要求処理部110と、第1のダイレクト・メモリ・アクセス・コントローラ(DMAC)112と、第2のDMAC113と、第1の調停器114と、第2の調停器115と、第1のデータバッファ116と、第2のデータバッファ117と、第1のセレクタ118と、第2のセレクタ119とを備える。データ転送処理装置101は、第1のシステムバス106及び第2のシステムバス107に接続され、双方のシステムバス間に発生するデータ転送処理を実行する。

40

【0003】

転送要求処理部110は、内部又は外部からデータ転送の必要が生じると、第1のDMAC112及び/又は第2のDMAC113に対して、DMA転送要求を与える。第1のDMAC112は、DMA転送要求に応じて、第1のデータバッファ116及び第1の調停器114を制御する。第2のDMAC113は、DMA転送要求に応じて、第2のデータバッファ117及び第2の調停器115を制御する。第1の調停器114は、第1のDMAC112及び第2のDMAC113による制御に基づいて、第1のセレクタ118の選択動作を調停する。第2の調停器115は、第1のDMAC112及び第2のDMAC113

50

3による制御に基づいて、第2のセレクタ119の選択動作を調停する。第1のセレクタ118は、第1の調停器114の調停内容に従って、第1のシステムバス106へのアクセス、及び第1のデータバッファ116又は第2のデータバッファ117への選択を実行する。第2のセレクタ119は、第2の調停器115の調停内容に従って、第2のシステムバス107へのアクセス、及び第1のデータバッファ116又は第2のデータバッファ117への選択を実行する。第1のデータバッファ116及び第2のデータバッファ117は、転送されるデータが一時的に書き込まれる記憶領域である。

#### 【0004】

通常、複数のD MACを持つデータ転送処理装置では、図12に示すように、システムバス間の周波数やプロトコルの差を緩衝させるためのデータバッファ116及び117が、D MAC112及び113毎にそれぞれ専用で割り当てられる構成を用いる。この構成によるデータ転送処理装置101において、例えば第1のD MAC112を使用して第1のシステムバス106から第2のシステムバス107へのデータ転送を行う場合を考える。この場合には、次の2つのデータ転送方法が考えられる。

#### 【0005】

第1のデータ転送方法では、第1のD MAC112は、第1のシステムバス106のアクセス権を獲得して、第1のシステムバス106から入力する所定量のデータを第1のデータバッファ116に格納する。そして、データ格納後に、第1のD MAC112は、第2のシステムバス107のアクセス権を獲得して、第1のデータバッファ116に格納されたデータを第2のシステムバス107に出力する。

第2のデータ転送方法では、第1のD MAC112は、第1のシステムバス106のアクセス権を獲得して、第1のシステムバス106から入力する所定量のデータを第1のデータバッファ116に順次格納していく。ここで、第1のD MAC112は、第1のデータバッファ116にデータが格納しながら第2のシステムバス107のアクセス権を獲得して、第1のデータバッファ116に格納済みのデータを順次第2のシステムバス107に出力する。

#### 【0006】

しかし、上記第1のデータ転送方法の場合、第1のデータバッファ116に格納された全てのデータを第2のシステムバス107に出力し終わるまでは、第1のデータバッファ116に新たなデータを格納することができない。このため、システムバスの効率的な利用ができず、大量のデータを転送する場合等には、実用性に欠ける。

また、上記第2のデータ転送方法の場合、第1のシステムバス106及び第2のシステムバス107両方のアクセス権を、1つのD MAC112が長期にわたって獲得し続けるため、実際にはデータ転送が行われない期間にも双方のシステムバスが開放されず、他の処理に影響を与える。この影響を回避するためには、データ転送が行われる期間と行われない期間との境で、その都度アクセス権の獲得又は開放を行う必要があるが、アクセス権を獲得したい時に他の装置が使用していればシステムバスが空くまで待たなければならぬという問題もある（例えば、非特許文献1を参照）。

【非特許文献1】株式会社日立製作所、“日立SuperTM RISC engine SH7751シリーズハードウェアマニュアル”、[online]、[平成15年4月1日検索]、インターネット HYPERLINK "http://www.renesas.com/avs/resource/japan/jpn/pdf/mpumcu/j602215#sh7751.pdf" http://www.renesas.com/avs/resource/japan/jpn/pdf/mpumcu/j602215\_sh7751.pdf

#### 【発明の開示】

##### 【発明が解決しようとする課題】

#### 【0007】

上述したように、従来のDMA転送方式によるデータ転送処理装置では、周波数又はプロトコルが異なるシステムバス間のデータ転送を効率的に行っておらず、また大量のデータを転送する等の場合においてはシステムバスを有効利用できていない。

10

20

30

40

50

**【 0 0 0 8 】**

それ故に、本発明の目的は、DMA転送方式によるデータ転送において、データ転送効率の向上及びシステムバスの使用効率の向上を図った、データ転送処理装置及びデータ転送処理方法を提供することである。

**【課題を解決するための手段】****【 0 0 0 9 】**

本発明は、異なるプロトコル又は周波数で動作する複数のシステムバス間において、ダイレクト・メモリ・アクセス転送方式によるデータ転送を実行するデータ転送処理装置に向けられている。そして、上記目的を達成させるために、本発明のデータ転送処理装置は、複数のデータバッファ、複数のダイレクト・メモリ・アクセス・コントローラ(DMA C)と及びバッファ割り当て部を備える。10

複数のデータバッファは、転送データを一時的に格納する。複数のDMA Cは、データバッファの少なくとも1つを用いて、システムバス間のデータ転送を実行する。バッファ割り当て部は、データ転送状態に応じて、複数のDMA Cが使用するデータバッファを動的に割り当てる。

**【 0 0 1 0 】**

好みいバッファ割り当て部は、複数のDMA Cのそれぞれについて、データ転送に使用できるデータバッファが1つであるシングルモード又は複数であるマルチモードを、転送されるデータの種別に基づいて設定する転送モード設定部を構成に含む。この構成により、複数のDMA Cは、転送モード設定部の設定モードに従って、各々のデータ転送に使用可能なデータバッファを決定することができる。20

また、他の好みいバッファ割り当て部は、複数のDMA Cのそれぞれについて、実際にデータ転送に使用しているデータバッファに関する情報を設定するステータス設定部を構成に含む。この構成により、データ転送を実行しようとするDMA Cは、ステータス設定部に設定された情報に従って、自己のデータ転送に使用可能なデータバッファを決定することが可能となる。

**【 0 0 1 1 】**

このとき、バッファ割り当て部が、使用可能なデータバッファの使用権を調停するデータバッファ調停制御部をさらに構成に含んでもよい。この構成により、データ転送を実行しようとするDMA Cは、ステータス設定部に設定された情報に従って直ちにデータ転送が開始できない場合でも、データバッファ調停制御部によって与えられる使用権に従って、自己のデータ転送に使用可能なデータバッファを決定することができる。30

また、複数のDMA Cに、それぞれ、データ転送実行中にデータ転送相手の装置によって転送が中断された回数を記憶する遮断回数保持部を含ませて、データバッファを2つ以上使用しているDMA Cは、遮断回数保持部が記憶する回数が所定の回数に達した場合、使用しているデータバッファの数を減少させてよい。

**【 0 0 1 2 】**

なお、複数のデータバッファを、格納領域を任意に区分して使用するマルチポートのデータバッファで構成することも可能である。この場合には、バッファ割り当て部は、データ転送を要求する装置毎に、データ転送に必要なデータバッファの段数及び構成に関する情報を予め記憶したバッファ領域対応テーブルと、DMA Cに割り当てるマルチポートのデータバッファの格納領域区分を、バッファ領域対応テーブルの記憶情報に基づいて制御するバッファ領域管理部との構成を含むことが好みい。これらの構成により、データ転送を実行しようとするDMA Cは、バッファ領域管理部によって区分されるエリアを、自己のデータ転送に使用可能なデータバッファとして決定することができる。40

**【 0 0 1 3 】**

また、本発明は、転送データを一時的に格納する複数のデータバッファと、データバッファの少なくとも1つを用いて、システムバス間のデータ転送を実行する複数のDMA Cとを備えた装置が、異なるプロトコル又は周波数で動作する複数のシステムバス間において、DMA転送方式によるデータ転送を実行するデータ転送処理方法に向けられている。50

そして、上記目的を達成させるために、本発明のデータ転送処理方法では、システムバス上のデータ転送状態を判断し、この判断に応じて複数のDMAが使用するデータバッファを動的に割り当て、この割り当てられたデータバッファを使用してデータ転送を実行する。

### 【発明の効果】

#### 【0014】

上記のように、本発明によれば、転送すべきデータの種類に応じて、各DMAがデータ転送に使用するデータバッファの数をシングル又はマルチに切り替えることができる。従って、データ転送効率の向上及びシステムバスの使用効率の向上を図ることができるという効果を発揮する。特に、各DMAの動作状態を表すステータス設定部を用いれば、転送要求処理部の処理負荷を軽減させることができる。また、使用していないデータバッファの使用権を調停するデータバッファ調停制御部を用いることで、データバッファを使用しているDMAのデータ転送の終了を待たなくとも、空きデータバッファによるデータ転送を迅速に開始することが可能となる。また、データ転送相手の装置からの特定の応答（中断応答）を所定の回数以上受信した場合にデータバッファの使用権を制御するので、途中でデータ転送効率が悪くなった場合は、バッファ構成を動的に変更して他のデータ転送を並行して行うことができる。さらに、マルチポートのデータバッファに対しては、転送要求されるデータに応じてエリア区分を変更するので、他のDMA用のデータバッファの使用状態にかかわらず、要求されたデータ転送に最適なデータバッファ構成でデータ転送を行うことが可能となる。

10

20

30

40

50

### 【発明を実施するための最良の形態】

#### 【0015】

本発明のデータ転送処理装置は、異なるプロトコル又は周波数で動作する複数のシステムバス間でデータ転送の実行が可能である。以下の各実施形態では、2つのシステムバス間でデータ転送を実行する場合を一例に挙げて、本発明のデータ転送処理装置を説明する。また、各実施形態では、双方のシステムバスがデータ転送処理装置外に構成される例を説明するが、データ転送処理装置が終端装置である場合には、いずれか一方のシステムバスがデータ転送処理装置内に構成されることになる。

#### 【0016】

##### （第1の実施形態）

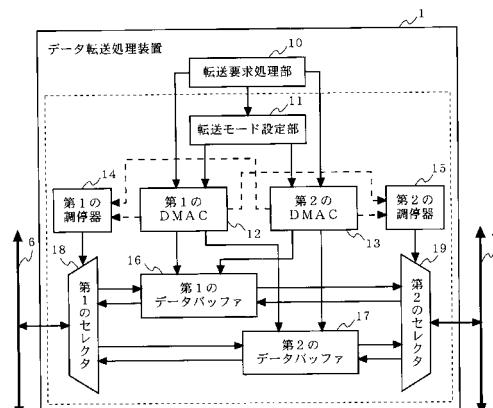

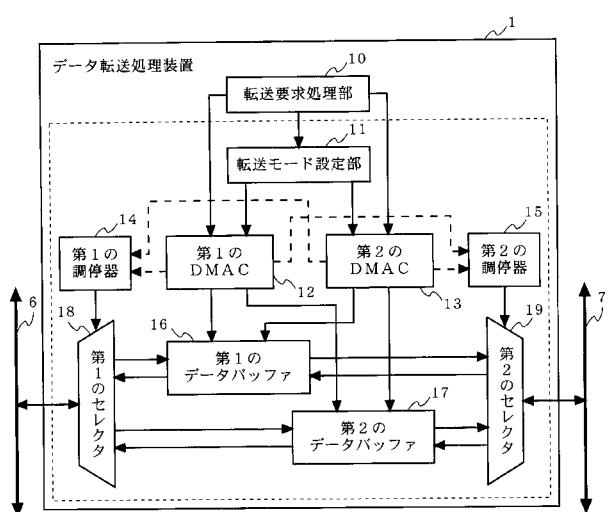

図1は、本発明の第1の実施形態に係るデータ転送処理装置1の構成を示すブロック図である。図1において、第1の実施形態に係るデータ転送処理装置1は、転送要求処理部10と、転送モード設定部11と、第1のDMA12と、第2のDMA13と、第1の調停器14と、第2の調停器15と、第1のデータバッファ16と、第2のデータバッファ17と、第1のセレクタ18と、第2のセレクタ19とを備える。データ転送処理装置1は、第1のシステムバス6及び第2のシステムバス7に接続され、双方のシステムバス間に発生するデータ転送処理を実行する。典型的な転送要求処理部10は、デジタル信号プロセッサ(DSP)、中央演算処理装置(CPU)、及びプログラムメモリ(ROM)等で構成されるが、本発明のデータ転送処理装置（以下の各実施形態において同様）は、この構成に限られるものではない。例えば、CPUだけがデータ転送処理装置外に構成されてもよいし、転送要求処理部10がデータ転送処理装置外に構成されてもよい。

#### 【0017】

まず、データ転送処理装置1の各構成の概要を説明する。

転送要求処理部10は、内部又は外部からデータ転送の必要が生じると、第1のDMA12及び/又は第2のDMA13に対してDMA転送要求を与えると共に、転送モード設定部11への所定の転送モードを設定する。転送モード設定部11は、転送要求処理部10からの指示に従って、第1のデータバッファ16及び第2のデータバッファ17を両方使用するのか、いずれか一方を使用するのか、を与える転送モードを設定する。すなわち、転送モード設定部11は、バッファ割り当て部として機能する。この転送モード設定部11には、レジスタ等が用いられる。第1のDMA12は、DMA転送要求及び転

送モード設定部 11 に設定された転送モードに基づいて、第 1 の調停器 14、第 1 のデータバッファ 16、及び第 2 のデータバッファ 17 を制御する。第 2 の DMA C 13 は、DMA 転送要求及び転送モード設定部 11 に設定された転送モードに基づいて、第 2 の調停器 15、第 1 のデータバッファ 16、及び第 2 のデータバッファ 17 を制御する。第 1 の調停器 14 は、第 1 の DMA C 12 及び第 2 の DMA C 13 による制御に基づいて、第 1 のセレクタ 18 の選択動作を調停する。第 2 の調停器 15 は、第 1 の DMA C 12 及び第 2 の DMA C 13 による制御に基づいて、第 2 のセレクタ 19 の選択動作を調停する。第 1 のセレクタ 18 は、第 1 の調停器 14 の調停内容に従って、システムバス 6 へのアクセス、及び第 1 のデータバッファ 16 又は第 2 のデータバッファ 17 の選択を実行する。第 2 のセレクタ 19 は、第 2 の調停器 15 の調停内容に従って、システムバス 7 へのアクセス、及び第 1 のデータバッファ 16 又は第 2 のデータバッファ 17 への選択を実行する。第 1 のデータバッファ 16 及び第 2 のデータバッファ 17 は、転送されるデータが一時的に書き込まれる記憶領域である。

10

#### 【 0 0 1 8 】

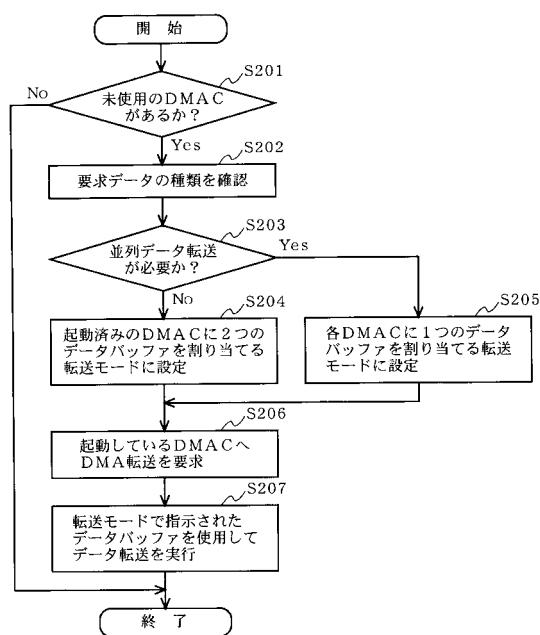

次に、上記構成によるデータ転送処理装置 1 の処理動作を、図 2 及び図 3 をさらに参照して説明する。図 2 は、第 1 の実施形態に係るデータ転送処理装置 1 が実行するデータ転送処理方法の手順を示すフローチャートである。図 2 の処理は、転送要求処理部 10 において新たなデータ転送の必要が生じると開始される。

20

#### 【 0 0 1 9 】

まず、転送要求処理部 10 は、データ転送を行っていない未使用の DMA C、すなわち起動していない DMA C が存在するか否かを判断する（ステップ S 201）。未使用の DMA C が存在する場合、転送要求処理部 10 は、新たに転送が要求されているデータ、またすでにデータ転送が行われている場合にはそのデータの種類を確認する（ステップ S 202）。そして、この確認の結果から、転送要求処理部 10 は、並列的なデータ転送が必要か否かを判断する（ステップ S 203）。例えば、転送すべきデータが、静止画表示用の画面フレームデータと演算処理用データという異なる 2 種類である場合には、並列的なデータ転送が必要であると判断される。また、転送すべきデータが、動画表示用の高速大容量のデータの 1 種類である場合には、並列的なデータ転送が不要であると判断される。

30

#### 【 0 0 2 0 】

並列的なデータ転送が必要であると判断した場合、転送要求処理部 10 は、ステップ S 201 で判断した未使用の DMA C を起動させると共に、第 1 の DMA C 12 に第 1 のデータバッファ 16 を、第 2 の DMA C 13 に第 2 のデータバッファ 17 を、それぞれ割り当てる転送モード（シングルバッファモード）を転送モード設定部 11 に設定する（ステップ S 204）。一方、並列的なデータ転送が不要であると判断した場合、転送要求処理部 10 は、現在起動している第 1 の DMA C 12 又は第 2 の DMA C 13 に、第 1 のデータバッファ 16 及び第 2 のデータバッファ 17 の両方を割り当てる転送モード（マルチバッファモード）を転送モード設定部 11 に設定する（ステップ S 205）。その後、転送要求処理部 10 は、起動している DMA C に対して DMA 転送要求を与える（ステップ S 206）。

40

#### 【 0 0 2 1 】

DMA 転送要求を受けた第 1 の DMA C 12 及び / 又は第 2 の DMA C 13 は、転送モード設定部 11 に設定された転送モードに従って、そこで指示されたデータバッファを用いてデータ転送を実行する（ステップ S 207）。なお、上記ステップ S 201 において未使用の DMA C が存在しない場合には、データ転送要求に応えられないため、この処理を終了させる。

#### 【 0 0 2 2 】

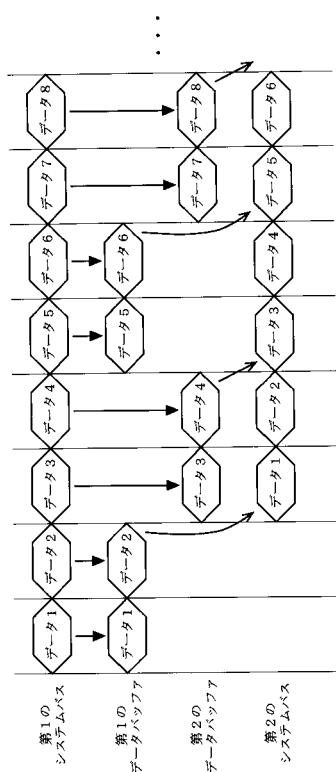

図 3 は、マルチバッファモードによって第 1 の DMA C 12 が実行するデータ転送の一例を説明する図である。図 3 に示すように、このマルチバッファモードでは、第 1 のデータバッファ 16 に格納されたデータの転送が開始されると同時に、第 2 のデータバッファ

50

17を用いて後続するデータを格納することが可能となる。第2のデータバッファ17に格納されたデータの転送は、第1のデータバッファ16に格納されたデータの転送が完了後に開始される。逆に、第2のデータバッファ17に格納されたデータの転送が開始されると同時に、第1のデータバッファ16を用いてさらに後続するデータを格納することが可能となる。以後、転送すべきデータが終了するまで、この処理が繰り返し行われる。このマルチバッファモードでは、シングルバッファモードに比べて、高速にデータ転送を行うことができる。

#### 【0023】

以上のように、本発明の第1の実施形態に係るデータ転送処理装置及び方法によれば、転送すべきデータの種類に応じて、各DMAがデータ転送に使用するデータバッファの数をシングル又はマルチに切り替えることができる。これにより、異なる2種類のデータの並列転送や、大容量データの高速転送といった、システムが要求するデータ転送を適切に行なうことが可能となる。従って、データ転送効率の向上及びシステムバスの使用効率の向上を図ることができる。10

#### 【0024】

##### (第2の実施形態)

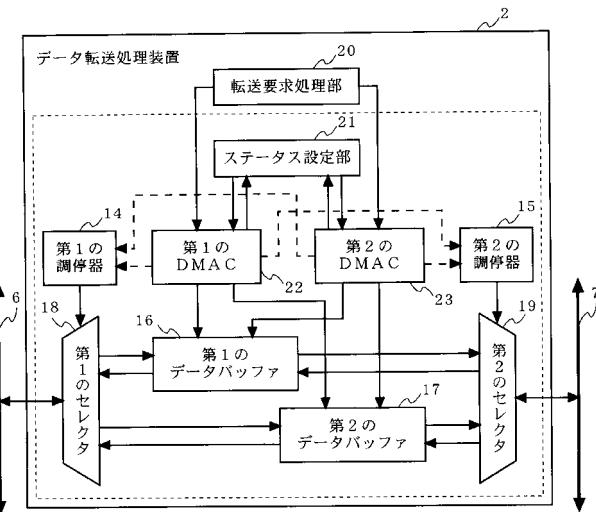

図4は、本発明の第2の実施形態に係るデータ転送処理装置2の構成を示すブロック図である。図4において、第2の実施形態に係るデータ転送処理装置2は、転送要求処理部20と、ステータス設定部21と、第1のDMAC22と、第2のDMAC23と、第1の調停器14と、第2の調停器15と、第1のデータバッファ16と、第2のデータバッファ17と、第1のセレクタ18と、第2のセレクタ19とを備える。図4に示すように、第2の実施形態に係るデータ転送処理装置2の構成は、上記第1の実施形態に係るデータ転送処理装置1の構成に対して、転送要求処理部20、ステータス設定部21、第1のDMAC22及び第2のDMAC23が異なる。以下、この異なる構成部分を中心に、第2の実施形態に係るデータ転送処理装置2を説明する。20

#### 【0025】

転送要求処理部20は、内部又は外部からデータ転送の必要が生じると、第1のDMAC22及び/又は第2のDMAC23に対してDMA転送要求を与える。ステータス設定部21は、第1のDMAC22及び第2のDMAC23について、データ転送を実行しているか否かや、どのデータバッファを使用してデータ転送を行っているか等の動作状態を設定する。すなわち、ステータス設定部21は、バッファ割り当て部として機能する。このステータス設定部21には、レジスタ等が用いられる。第1のDMAC22は、DMA転送要求及びステータス設定部21に設定された動作状態に基づいて、第1の調停器14、第1のデータバッファ16及び第2のデータバッファ17とを制御する。第2のDMAC23は、DMA転送要求及びステータス設定部21に設定された動作状態に基づいて、第2の調停器15、第1のデータバッファ16及び第2のデータバッファ17とを制御する。30

#### 【0026】

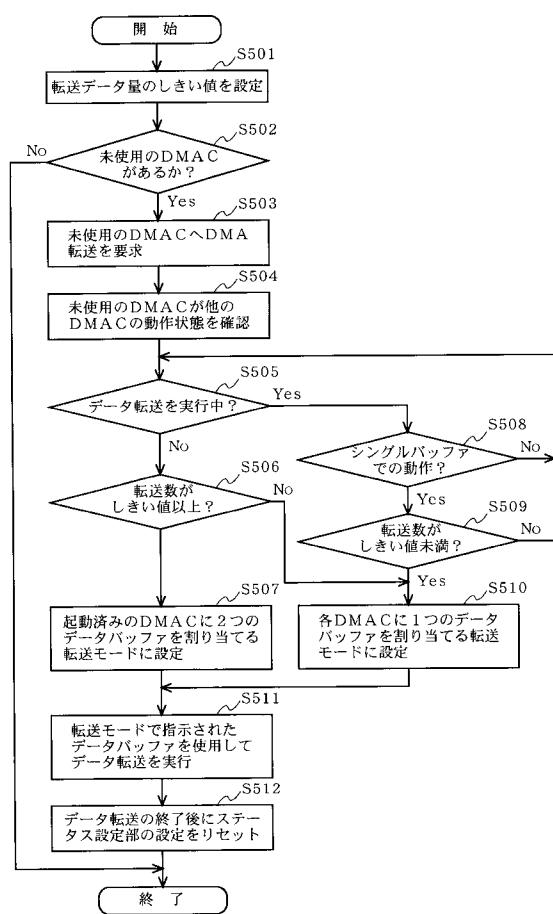

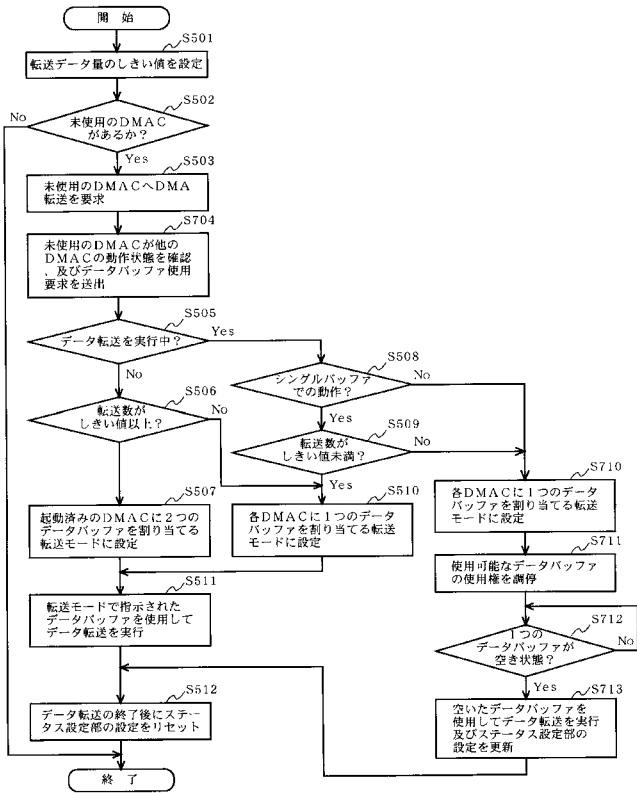

図5は、第2の実施形態に係るデータ転送処理装置2が実行するデータ転送処理方法の手順を示すフローチャートである。図5の処理は、転送要求処理部20において新たなデータ転送の必要が生じると開始される。40

#### 【0027】

まず、転送要求処理部20は、転送するデータ量のしきい値を、第1のDMAC22及び第2のDMAC23に設定する(ステップS501)。このしきい値は、各々のDMAが、2つのデータバッファを用いて(マルチバッファ)並列的にデータ転送を行うのか、1つのデータバッファを用いて(シングルバッファ)通常のデータ転送を行うのかを、判断するために用いられる。その後、転送要求処理部20は、データ転送を行っていない未使用のDMA、すなわち起動していないDMAが存在するか否かを判断する(ステップS502)。未使用のDMAが存在する場合、転送要求処理部10は、未使用のDMAの1つに対してDMA転送要求を与える(ステップS503)。この実施例では、50

未使用のDMAを第1のDMA22として説明する。DMA転送要求を与えられた第1のDMA22は、ステータス設定部21に設定された動作状態を確認し、他方の第2のDMA23がデータ転送を行っているか否かと、マルチバッファ又はシングルバッファのどちらでデータ転送を実行しているかをチェックする(ステップS504)。

#### 【0028】

チェックの結果、第1のDMA22は、第2のDMA23がデータ転送を行っていない場合、DMA転送要求で要求されたデータ転送量が、設定されたしきい値以上であれば第1のデータバッファ16及び第2のデータバッファ17の両方を自分に割り当てる(マルチバッファ)転送モードを、しきい値未満であれば第1のデータバッファ16だけを自分に割り当てる(シングルバッファ)転送モードを、ステータス設定部21に設定する(ステップS505～S507、S510)。これに対し、第1のDMA22は、第2のDMA23がデータ転送を行っている場合、そのデータ転送がシングルバッファで実行されており、かつ、DMA転送要求で要求されたデータ転送量が設定されたしきい値未満であれば、第1のデータバッファ16だけを自分に割り当てる(シングルバッファ)転送モードをステータス設定部21に設定する(ステップS508～S510)。それ以外の場合には、第1のDMA22は、第2のDMA23のデータ転送が終了するまで、すなわち第2のデータバッファ17が空くまで待機することになる。

#### 【0029】

第1のDMA22及び/又は第2のDMA23は、ステータス設定部21に設定された動作状態に従って、指示されたデータバッファを用いてデータ転送を実行する(ステップS511)。そして、データ転送が終了した後、第1のDMA22又は第2のDMA23は、ステータス設定部21に設定している動作状態をリセットする(ステップS512)。なお、上記ステップS502において未使用のDMAが存在しない場合には、データ転送要求に応えられないため、この処理を終了させる。

#### 【0030】

以上のように、本発明の第2の実施形態に係るデータ転送処理装置及び方法によれば、各DMAの動作状態を表すステータス設定部を用いて、一方のDMA自らが他方のDMAの動作状態を判断して、データ転送に使用するデータバッファをシングル又はマルチに切り替えることができる。従って、上述した第1の実施形態の効果に加えて、転送要求処理部の処理負荷を軽減させることができる。

#### 【0031】

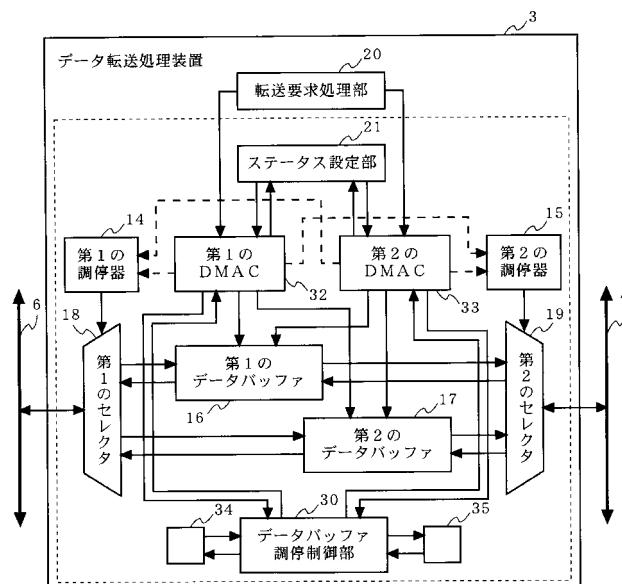

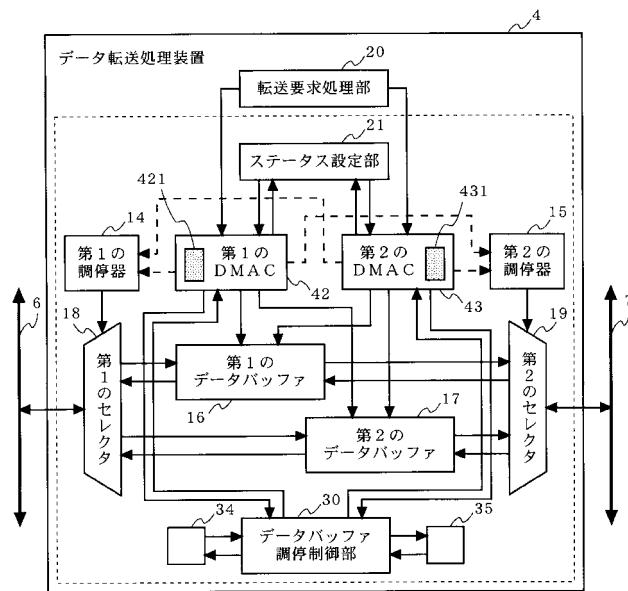

##### (第3の実施形態)

図6は、本発明の第3の実施形態に係るデータ転送処理装置3の構成を示すブロック図である。図6において、第3の実施形態に係るデータ転送処理装置3は、転送要求処理部20と、ステータス設定部21と、第1のDMA32と、第2のDMA33と、第1の調停器14と、第2の調停器15と、第1のデータバッファ16と、第2のデータバッファ17と、第1のセレクタ18と、第2のセレクタ19と、データバッファ調停制御部30と、第1のデータバッファステータスフラグ34と、第2のデータバッファステータスフラグ35とを備える。図6に示すように、第3の実施形態に係るデータ転送処理装置3の構成は、上記第2の実施形態に係るデータ転送処理装置2の構成に対して、第1のDMA32、第2のDMA33、データバッファ調停制御部30、第1のデータバッファステータスフラグ34及び第2のデータバッファステータスフラグ35が異なる。以下、この異なる構成部分を中心に、第3の実施形態に係るデータ転送処理装置3を説明する。

#### 【0032】

第1のDMA32は、DMA転送要求及びステータス設定部21に設定された動作状態に基づいて、第1の調停器14、第1のデータバッファ16及び第2のデータバッファ17を制御する。第2のDMA33は、DMA転送要求及びステータス設定部21に設定された動作状態に基づいて、第2の調停器15、第1のデータバッファ16及び第2のデータバッファ17を制御する。第1のデータバッファステータスフラグ34には、第1

のデータバッファ16が使用中である場合にフラグが設定される。第2のデータバッファステータスフラグ35には、第2のデータバッファ17が使用中である場合にフラグが設定される。データバッファ調停制御部30は、第1のデータバッファステータスフラグ34及び第2のデータバッファステータスフラグ35を用いて、第1のデータバッファ16及び第2のデータバッファ17の使用を調停する。このデータバッファ調停制御部30は、ステータス設定部21と共に、バッファ割り当て部として機能する。

#### 【0033】

図7は、第3の実施形態に係るデータ転送処理装置3が実行するデータ転送処理方法の手順を示すフローチャートである。なお、図7において図5に示す処理と同じ処理を実行するステップについては、同一のステップ番号を付してその説明を省略する。

10

#### 【0034】

未使用のDMACである第1のDMAC32は、転送要求処理部20からDMA転送要求が与えられると、ステータス設定部21に設定された動作状態を確認し、他方の第2のDMAC33がデータ転送を行っているか否かと、マルチバッファ又はシングルバッファのどちらでデータ転送を実行しているかをチェックする(ステップS704)。これと同時に、第1のDMAC32は、データバッファ調停制御部30に対してデータバッファ使用要求を送出する(ステップS704)。

#### 【0035】

データバッファ使用要求を受けたデータバッファ調停制御部30は、第2のDMAC33がデータ転送を行っており、そのデータ転送がマルチバッファで実行されているか、DMA転送要求で要求されたデータ転送量が設定されたしきい値以上であれば、第1のデータバッファ16だけを自分に割り当てる(シングルバッファ)転送モードをステータス設定部21に設定すると共に(ステップS710)、使用可能なデータバッファの使用権を調停する(ステップS711)。具体的には、データバッファ調停制御部30は、第1のデータバッファ16又は第2のデータバッファ17のどちらかのデータ転送が終了する(データバッファが空く)のを判断して(ステップS712)、空いたデータバッファをさらに調停する(ステップS713)。例えば、第1のデータバッファ16が終了した場合には、データバッファ調停制御部30は、第2のDMAC33による第1のデータバッファ16の使用権をクリアする。これにより、第2のDMAC33は、シングルデータバッファ構成で続きのデータ転送を行う。また、データバッファ調停制御部30は、第2のDMAC33から開放された第1のデータバッファ16の使用権を第1のDMAC32に許可する。これにより、第1のDMAC32は、新たなデータ転送の開始が可能となる。なお、この調停処理に応じて、ステータス設定部21の設定が更新される(ステップS713)。

20

30

40

#### 【0036】

以上のように、本発明の第3の実施形態に係るデータ転送処理装置及び方法によれば、使用していないデータバッファの使用権を調停するデータバッファ調停制御部を用いる。これにより、一方のDMACが複数のデータバッファを占有してデータ転送を行っていたとしても、途中に発生するデータバッファ未使用の期間を他方のDMACに一時的に転用させることが可能となる。従って、一方のDMACのデータ転送の終了を待たなくても、空きデータバッファによるデータ転送を迅速に開始することが可能となる。

なお、データバッファの開放を許可させないために、各DMACからデータバッファ調停制御部30へデータバッファ使用要求を出す際に、要求と共にデータ転送の優先度も通知させてもよい。

#### 【0037】

##### (第4の実施形態)

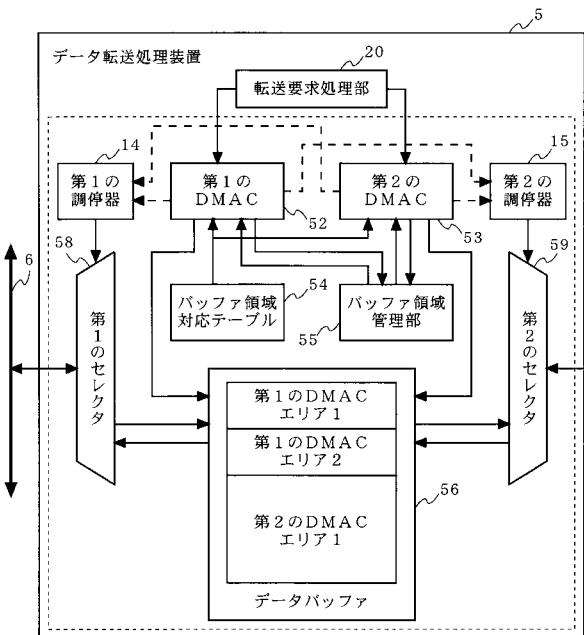

図8は、本発明の第4の実施形態に係るデータ転送処理装置4の構成を示すブロック図である。図8において、第4の実施形態に係るデータ転送処理装置4は、転送要求処理部20と、ステータス設定部21と、第1のDMAC42と、第2のDMAC43と、第1の調停器14と、第2の調停器15と、第1のデータバッファ16と、第2のデータバッ

50

ファ17と、第1のセレクタ18と、第2のセレクタ19と、データバッファ調停制御部30と、第1のデータバッファステータスフラグ34と、第2のデータバッファステータスフラグ35とを備える。図8に示すように、第4の実施形態に係るデータ転送処理装置4の構成は、上記第3の実施形態に係るデータ転送処理装置3の構成に対して、第1のDMA C42及び第2のDMA C43が異なる。以下、この異なる構成部分を中心に、第4の実施形態に係るデータ転送処理装置4を説明する。

#### 【0038】

第1のDMA C42は、上述した第1のDMA C32内に遮断回数保持部421を有する構成である。第2のDMA C43は、上述した第2のDMA C33内に遮断回数保持部431を有する構成である。この遮断回数保持部421及び431は、第1のDMA C42及び第2のDMA C43が、システムバス6又は7にデータ転送を行おうとした際に、データ転送相手の装置によって何度中断されたかをデータバッファ単位でカウントして保持する。この遮断回数保持部421及び431は、レジスタ等が用いられる。

#### 【0039】

転送要求処理部20が、必要に応じて第1のDMA C42及び第2のDMA C43にDMA転送を要求し、要求された第1のDMA C42及び第2のDMA C43が、データ転送を開始する。今、第1のDMA C42が、システムバス6からシステムバス7へ、第1のデータバッファ16及び第2のデータバッファ17の両方を占有したデータ転送を開始した場合で説明する。ここで、システムバス6が、PCIバスのような連続転送と転送遮断が発生するバスであった場合、システムバス6からデータを第1のデータバッファ16へ格納中に、データ転送相手の装置から転送の一時中断を受ける場合がある。これは、データ転送相手の装置側の先読み出しデータバッファ（プリフェッチFIFO等）の段数や、内部処理の状態に依存する。第1のDMA C42は、転送中断回数を遮断回数保持部421へカウントして保持し、予め定めた回数と比較する。予め定めた回数を超える転送中断が発生したときに、第1のデータバッファ16及び第2のデータバッファ17を並列的に使用している場合、第1のDMA C42は、どちらか一方のデータバッファを開放する。このとき、第2のDMA C43に新たなデータ転送が要求が発生している場合には、直ちに開放したデータバッファを用いてデータ転送を開始する。

#### 【0040】

以上のように、本発明の第4の実施形態に係るデータ転送処理装置及び方法によれば、遮断回数保持部を用いて、データ転送相手の装置からの特定の応答を所定の回数以上受信した場合に、データバッファの使用権を制御する。これにより、優先度の高いデータ転送であっても、途中でデータ転送効率が悪くなった場合は、バッファ構成を動的に変更して、他のデータ転送を並行して行うことができる。よって、システム全体のデータ転送効率を高めることが可能となる。

#### 【0041】

##### （第5の実施形態）

図9は、本発明の第5の実施形態に係るデータ転送処理装置5の構成を示すブロック図である。図9において、第5の実施形態に係るデータ転送処理装置5は、転送要求処理部20と、第1のDMA C52と、第2のDMA C53と、バッファ領域対応テーブル54と、バッファ領域管理部55と、第1の調停器14と、第2の調停器15と、データバッファ56と、第1のセレクタ58と、第2のセレクタ59とを備える。図9に示すように、第5の実施形態に係るデータ転送処理装置5の構成は、上記第2の実施形態に係るデータ転送処理装置2の構成に対して、第1のDMA C52、第2のDMA C53、バッファ領域対応テーブル54、バッファ領域管理部55、データバッファ56、第1のセレクタ58及び第2のセレクタ59が異なる。以下、この異なる構成部分を中心に、第5の実施形態に係るデータ転送処理装置2を説明する。

#### 【0042】

第1のDMA C52は、バッファ領域対応テーブル54を参照して、第1の調停器14及びデータバッファ56を制御する。第2のDMA C53は、バッファ領域対応テーブル

10

20

30

40

50

54を参照して、第2の調停器15及びデータバッファ56を制御する。バッファ領域対応テーブル54は、データの転送を要求したデータ転送元の装置に関する情報、例えばベースアドレスと、そのデータ転送元の装置に最適なデータバッファ構成とを保持する。バッファ領域管理部55は、データバッファ56のアドレス制御を行って、第1のDMA52及び第2のDMA53が使用するバッファ領域を管理する。すなわち、バッファ領域対応テーブル54及びバッファ領域管理部55は、バッファ割り当て部として機能する。第1のセレクタ58は、第1の調停器14の調停内容に従って、システムバス6へのアクセス、及びデータバッファ56の第1のDMA52用ポート又は第2のDMA53用ポートの選択を実行する。第2のセレクタ59は、第2の調停器15の調停内容に従って、システムバス6へのアクセス、及びデータバッファ56の第1のDMA52用ポート又は第2のDMA53用ポートの選択を実行する。データバッファ56は、格納領域を任意に区切って使用するマルチポートのデータバッファである。

10

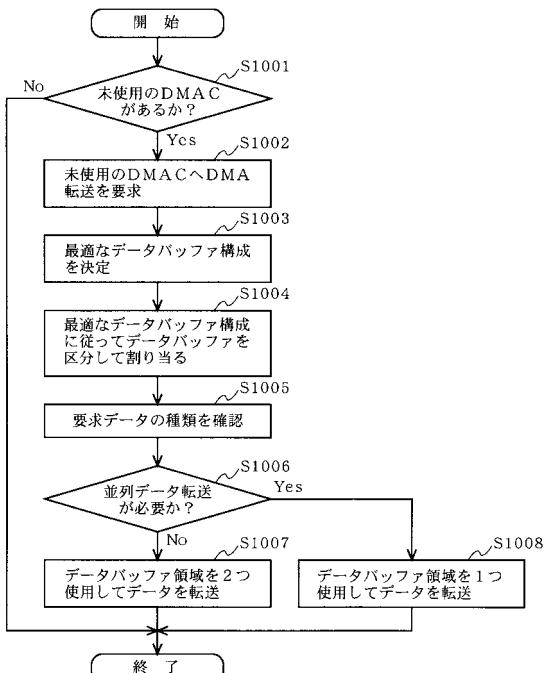

## 【0043】

図10は、第5の実施形態に係るデータ転送処理装置5が実行するデータ転送処理方法の手順を示すフローチャートである。図10の処理は、転送要求処理部20において新たなデータ転送の必要が生じると開始される。

## 【0044】

まず、転送要求処理部20は、データ転送を行っていない未使用のDMA5、すなわち起動していないDMA5が存在するか否かを判断する(ステップS1001)。未使用のDMA5が存在する場合、転送要求処理部20は、未使用のDMA5を起動させて、DMA転送要求を与える(ステップS1002)。この実施例では、未使用のDMA5を第1のDMA52として説明する。DMA転送要求を受けた第1のDMA52は、バッファ領域対応テーブル54を参照して、データバッファ56における最適なデータバッファ構成を決定し、バッファ領域管理部55に通知する(ステップS1003)。最適なデータバッファ構成は、データ転送元の装置のベースアドレスに基づいて決定される。バッファ領域管理部55は、第1のDMA52からの通知を受けて、データバッファ56の未使用領域を通知内容に応じて第1のDMA52用に割り当て、割り当てた旨を第1のDMA52に応答する(ステップS1004)。

20

## 【0045】

図11に、バッファ領域対応テーブル54の情報及びデータバッファ56の割り当て例を示す。図11のように、データバッファ56の格納領域がバッファ[0]～[15]で構成される場合、バッファ領域対応テーブル54には、バッファ[0]～[15]のそれぞれについて割り当てるDMA5及びエリアが記述される。データバッファ56は、このバッファ領域対応テーブル54の記述内容に従って、エリアが区分されることになる。

30

## 【0046】

転送要求処理部20は、転送が要求されているデータの種類を確認する(ステップS1005)。そして、この確認の結果から、転送要求処理部20は、並列的なデータ転送が必要か否かを判断する(ステップS1006)。この判断に従って、第1のDMA52は、データバッファ領域を2つ使用して並列転送又は1つ使用した通常転送を実行する(ステップS1007、S1008)。

40

## 【0047】

以上のように、本発明の第5の実施形態に係るデータ転送処理装置及び方法によれば、任意のエリアで格納領域を区分できる1つの大きなマルチポートのデータバッファを用い、転送要求されるデータ量に応じてエリア区分を変更する。これにより、例えば連続転送可能データ量が長い場合には、それに併せてデータバッファ内に大きなエリアを確保し、短い場合には、小さいエリアで済む。従って、他のDMA5用のデータバッファの使用状態にかかわらず、要求されたデータ転送に最適なデータバッファ構成でデータ転送を行うことが可能となる。

## 【0048】

なお、本発明のデータ転送処理装置を構成する転送モード設定部、ステータス設定部、

50

D M A C、調停器、データバッファ、データバッファ調停制御部、セレクタ、プリフェッチ語数設定部、アドレス検索部、語数設定テーブル、データバッファステータスフラグ、遮断回数保持レジスタ、バッファ領域対応テーブル、及びバッファ領域管理部の各機能ブロックは、典型的には集積回路である L S I (集積度の違いにより、I C、システム L S I、スーパー L S I、又はウルトラ L S I 等と称される)として実現される。これらは、個別に 1 チップ化されてもよいし、一部又は全部を含むように 1 チップ化されてもよい。

また、集積回路化の手法は、L S I に限るものではなく、専用回路又は汎用プロセッサで実現してもよい。また、L S I 製造後にプログラムすることが可能な F P G A (F i e l d P r o g r a m m a b l e G a t e A r r a y) や、L S I 内部の回路セルの接続や設定を再構成可能なリコンフィギュラブル・プロセッサを利用してよい。

さらには、半導体技術の進歩又は派生する別の技術により、L S I に置き換わる集積回路化の技術が登場すれば、当然その技術を用いて機能ブロックの集積化を行ってもよい。バイオ技術の適応等が可能性としてあり得る。

#### 【産業上の利用可能性】

#### 【0049】

本発明のデータ転送処理装置及びデータ転送処理方法は、異なるプロトコル又は周波数で動作する複数のシステムバス間ににおいて、D M A 転送方式によるデータ転送を実行する場合等に利用可能であり、特にデータ転送効率の向上及びシステムバスの使用効率の向上を図る場合に適している。

#### 【図面の簡単な説明】

#### 【0050】

【図 1】本発明の第 1 の実施形態に係るデータ転送処理装置の構成を示すブロック図

【図 2】本発明の第 1 の実施形態に係るデータ転送処理方法の手順を示すフローチャート

【図 3】マルチバッファモードによって D M A C が実行するデータ転送の一例を説明する図

【図 4】本発明の第 2 の実施形態に係るデータ転送処理装置の構成を示すブロック図

【図 5】本発明の第 2 の実施形態に係るデータ転送処理方法の手順を示すフローチャート

【図 6】本発明の第 3 の実施形態に係るデータ転送処理装置の構成を示すブロック図

【図 7】本発明の第 3 の実施形態に係るデータ転送処理方法の手順を示すフローチャート

【図 8】本発明の第 4 の実施形態に係るデータ転送処理装置の構成を示すブロック図

【図 9】本発明の第 5 の実施形態に係るデータ転送処理装置の構成を示すブロック図

【図 10】本発明の第 5 の実施形態に係るデータ転送処理方法の手順を示すフローチャート

【図 11】バッファ領域対応テーブルの情報及びデータバッファの割り当ての一例を示す図

【図 12】従来のデータ転送処理装置の構成を示すブロック図

#### 【符号の説明】

#### 【0051】

1、2、3、4、5、101 データ転送処理装置

6、7、106、107 システムバス

10、20、110 転送要求処理部

11 転送モード設定部

12、13、22、23、32、33、42、43、52、53、112、113 D M A C (ダイレクトメモリアクセスコントローラ)

14、15、114、115 調停器

16、17、56、116、117 データバッファ

18、19、58、59、118、119 セレクタ

21 ステータス設定部

30 データバッファ調停制御部

34、35 データバッファステータスフラグ

10

20

30

40

50

- 4 2 1、4 3 1 遮断回数保持部

5 4 バッファ領域対応テーブル

5 5 バッファ領域管理部

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

&lt;バッファ領域対応テーブル&gt;

| バッファ番号 | 割り当て |     |

|--------|------|-----|

|        | DMAC | エリア |

| 0      | 1    | 1   |

| 1      | 1    | 1   |

| 2      | 1    | 1   |

| 3      | 1    | 1   |

| 4      | 1    | 2   |

| 5      | 1    | 2   |

| 6      | 1    | 2   |

| 7      | 1    | 2   |

| 8      | 2    | 1   |

| 9      | 2    | 1   |

| 10     | 2    | 1   |

| 11     | 2    | 1   |

| 12     | 2    | 1   |

| 13     | 2    | 1   |

| 14     | 2    | 1   |

| 15     | 2    | 1   |

&lt;データバッファ&gt;

|           |

|-----------|

| バッファ [0]  |

| バッファ [1]  |

| バッファ [2]  |

| バッファ [3]  |

| バッファ [4]  |

| バッファ [5]  |

| バッファ [6]  |

| バッファ [7]  |

| バッファ [8]  |

| バッファ [9]  |

| バッファ [10] |

| バッファ [11] |

| バッファ [12] |

| バッファ [13] |

| バッファ [14] |

| バッファ [15] |

【図12】