(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第5788346号

(P5788346)

(45) 発行日 平成27年9月30日(2015.9.30)

(24) 登録日 平成27年8月7日(2015.8.7)

(51) Int.Cl.

F 1

|              |           |      |       |       |

|--------------|-----------|------|-------|-------|

| HO1L 21/8247 | (2006.01) | HO1L | 27/10 | 4 3 4 |

| HO1L 27/115  | (2006.01) | HO1L | 29/78 | 3 7 1 |

| HO1L 21/336  | (2006.01) | HO1L | 29/58 | G     |

| HO1L 29/788  | (2006.01) | HO1L | 29/44 | S     |

| HO1L 29/792  | (2006.01) | HO1L | 21/28 | E     |

請求項の数 11 外国語出願 (全 20 頁) 最終頁に続く

(21) 出願番号

特願2012-46149(P2012-46149)

(22) 出願日

平成24年3月2日(2012.3.2)

(65) 公開番号

特開2012-186474(P2012-186474A)

(43) 公開日

平成24年9月27日(2012.9.27)

審査請求日

平成27年2月2日(2015.2.2)

(31) 優先権主張番号

61/448,828

(32) 優先日

平成23年3月3日(2011.3.3)

(33) 優先権主張国

米国(US)

(31) 優先権主張番号

11075160.9

(32) 優先日

平成23年7月6日(2011.7.6)

(33) 優先権主張国

欧洲特許庁(EP)

早期審査対象出願

(73) 特許権者 591060898

アイメック

I M E C

ペルギー、ペー－3001ルーヴアン、カ

ペルドリーフ75番

(74) 代理人 100101454

弁理士 山田 阜二

(74) 代理人 100081422

弁理士 田中 光雄

(74) 代理人 100100479

弁理士 竹内 三喜夫

(74) 代理人 100112911

弁理士 中野 晴夫

最終頁に続く

(54) 【発明の名称】フローティングゲート半導体メモリデバイスおよびそのようなデバイスの製造方法

## (57) 【特許請求の範囲】

## 【請求項 1】

半導体 - オン - 絶縁体基板を提供する工程であって、この半導体 - オン - 絶縁体基板は、

半導体ベース層と、

半導体ベース層の上でこれと接触する誘電体層と、

誘電体層の上でこれと接触する単結晶半導体上部層と、

を含む工程と、

半導体 - オン - 絶縁体基板の中に少なくとも 2 つのトレンチを形成する工程であって、少なくとも 2 つのトレンチは上部層、誘電体層を通って延び、更に部分的にベース層を通って延びる工程と、

少なくとも 2 つのトレンチを形成する工程の結果として、

ベース層の一部を含むベース部分と、

誘電体層の一部を含み、ベース部分の上でこれと接触する誘電体部分と、

上部層の一部を含み、誘電体部分の上でこれと接触する上部部分と、

を含む少なくとも 1 つの高層構造を形成する工程と、

少なくとも 2 つのトレンチの底部に分離領域を形成する工程であって、少なくとも 2 つのトレンチを部分的に埋める工程を含む工程と、

少なくとも上部部分の露出した側壁面を熱酸化することにより、少なくとも露出した側壁面の上にゲート誘電体層を形成する工程と、

10

20

少なくとも 1 つの高層構造と、ゲート誘電体層と、分離領域との上に導電性層を形成し、少なくとも 1 つのフローティングゲート半導体メモリデバイスを形成する工程と、を含み、

誘電体部分は、トンネル誘電体層を含み、上部部分は、フローティングゲートを含み、導電性層は、コントロールゲートを含む方法。

【請求項 2】

少なくとも 2 つのトレンチを部分的に埋める工程は、

少なくとも 2 つのトレンチを絶縁性材料で埋める工程と、

少なくとも 2 つのトレンチから絶縁性材料を部分的に除去して、少なくとも 2 つのトレンチの底部に絶縁性材料を残し、これにより分離領域を形成する工程と、を含む請求項 1 に記載の方法。 10

【請求項 3】

誘電体層は、約 6 nm から約 10 nm の等価酸化膜厚を有する請求項 1 に記載の方法。

【請求項 4】

更に、少なくとも 1 つの高層構造の上面を熱酸化して、これにより少なくとも 1 つの高層構造の上面の上にゲート誘電体を形成する工程を含む請求項 1 に記載の方法。 20

【請求項 5】

分離領域は、少なくとも 1 つの高層構造のベース部分と誘電体部分と、ゲート誘電体層の一部に接触し、

分離領域は、誘電体部分の上に延びる請求項 1 に記載の方法。 20

【請求項 6】

少なくとも 2 つのトレンチを形成する工程は、

半導体 - オン - 絶縁体基板の上にパターニングされたハードマスク層を形成する工程と、

、

パターニングされたハードマスク層でパターニングされていない半導体 - オン - 絶縁体基板の領域中に少なくとも 2 つのトレンチをエッティングする工程と、を含む請求項 1 に記載の方法。 20

【請求項 7】

少なくとも 2 つのトレンチが形成された後に、少なくとも 1 つの高層構造の上面の上にパターニングされたハードマスク層が残り、 30

少なくとも 1 つの高層構造の上に導電性層を形成する工程は、少なくとも 1 つの高層構造の上面の上に残ったパターニングされたハードマスク層の上に導電性層を形成する工程を含む請求項 6 に記載の方法。

【請求項 8】

更に、少なくとも 2 つのトレンチを形成した後に、パターニングされたハードマスク層を除去する工程と、

パターニングされたハードマスク層を除去する工程の後で、上部部分の露出した側壁面を熱酸化する前に、少なくとも 1 つの高層構造の上の角を丸くする工程を含む請求項 6 に記載の方法。 30

【請求項 9】

少なくとも 2 つのトレンチを形成する工程は、

第 1 のエッティングで、上部層を通るエッティングにより誘電体層を露出させ、これにより少なくとも 2 つの部分的なトレンチを形成する工程と、

第 2 のエッティングで、誘電体層を通り、ベース層を部分的に通ってエッティングし、これにより、少なくとも 2 つの部分的なトレンチを、少なくとも 2 つのトレンチに換える工程と、を含む請求項 1 に記載の方法。 40

【請求項 10】

更に、第 1 エッティングの後で、第 2 エッティングの前に、少なくとも 2 つの部分的なトレンチの中に、ドーパント元素を注入する工程を含む請求項 9 に記載の方法。

【請求項 11】

10

20

30

40

50

ゲート誘電体層は、約 6 nm から約 8 nm の膜厚を有する請求項 1 に記載の方法。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、フローティングゲート半導体デバイスに関し、特に単結晶フローティングゲート半導体デバイスに関する。

【0002】

本発明は、また、フローティングゲート半導体デバイスの製造方法に関し、特に単結晶フローティングゲート半導体デバイスの製造に関する。

【背景技術】

10

【0003】

NAND フラッシュメモリデバイスのために、電気的な小型化と共に物理的な小型化がそれぞれのテクニカルノードで挑戦になってきた。

【0004】

先端技術のNAND フラッシュメモリデバイスでは、より一般にはゲート誘電体と呼ばれるONO (酸化物 - 窒化物 - 酸化物) インターポリ誘電体 (IPD) が、フローティングゲートの側壁に沿って延在し、フローティングゲートとコントロールゲートとの間に大きなキャパシタンスと、それゆえに大きな連結比 (coupling ratio) を与える。IPD 層はフローティングデバイス中で、ピッチにより規定された 1 つの幅で 2 度存在するため、IPD 層の膜厚の小型化は、20 nm と 29 nm の間に含まれるメモリセルハーフピッチに対応する 2X 世代のテクノロジーノード以下で、フラッシュの小型化の制限要素となる。良好なデータ保持を達成するために、IPD 層の物理的な膜厚が、先端材料を用いて約 12 nm から約 15 nm に制限される。フローティングゲートとコントロールゲートの膜厚を加える必要があるため、これはすでに、少なくとも 24 nm から 30 nm のピッチサイズを意味する。

20

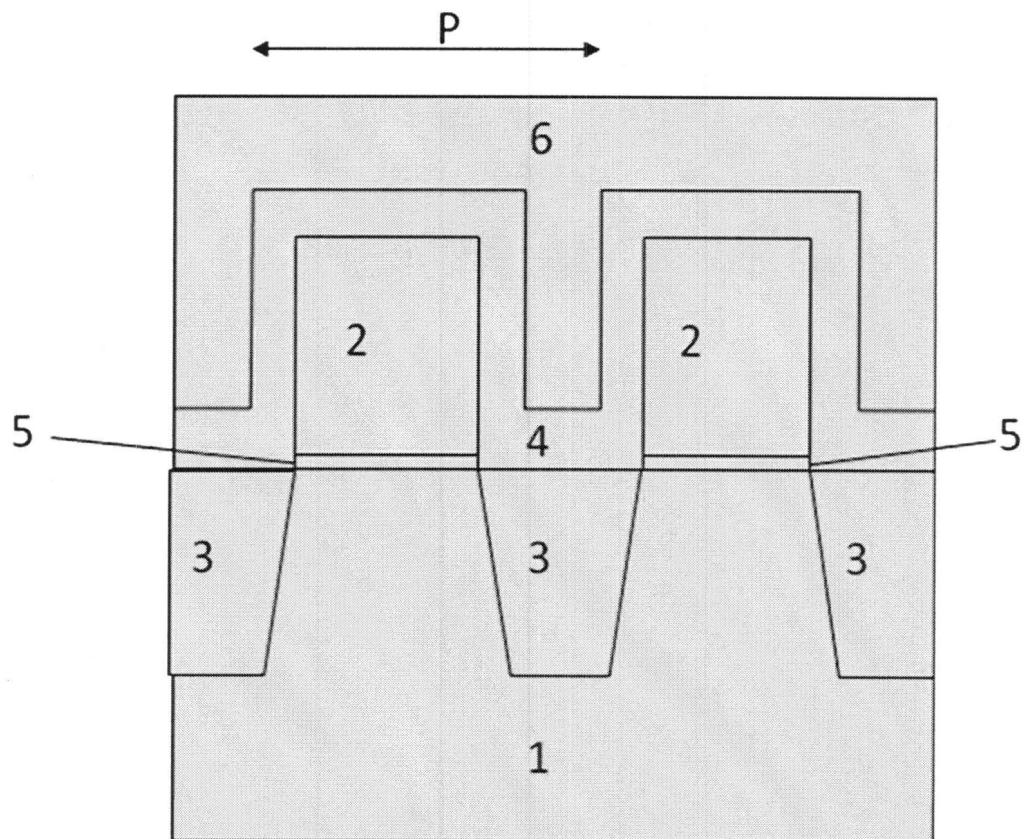

【0005】

図 1 は、フローティングゲート構造 2、分離領域 3、フローティングゲート構造 2 の周囲を包むインターポリ誘電体層 4、トンネル酸化物層 5、およびコントロールゲート 6 を含む、基板 1 の上の従来のフローティングゲートメモリデバイスの模式図を示す。ピッチ P の内側に、フローティングゲート (FG) 2、インターポリ誘電体 (IPD) 層 4、コントロールゲート (CG) 6、および再びインターポリ誘電体 (IPD) 層 4 のための空間を有する必要があるため、フローティングゲートメモリデバイスのピッチ P の小型化は非常に挑戦になる。IPD 層に現在使用される材料、例えば ONO や AlO 系誘電体スタックでは、IPD 層の膜厚はメモリデバイスのために良好なデータ保持 (即ち、約 10 年のデータ保持) を達成するために、約 12 nm から 15 nm に限定される。より薄い膜厚に小型化した場合、IPD 層に使用される材料の電気的特性はもはや十分ではない。なぜなら、より小さな膜厚は、リークを増やし、デバイスの悪い性能を招くからである。

30

【0006】

3X 世代テクノロジーノード以下に小型化可能で、2X 世代テクノロジーノード以下にさえも小型化可能な、良好なデータ保持と電気的特性を備えたフローティングゲートデバイスが必要となる。

40

【発明の概要】

【0007】

本発明は、添付された請求項に記載された方法およびデバイスに関する。本発明は、このように、フローティングゲート半導体メモリデバイスの製造方法に関し、この方法は、半導体 - オン - 絶縁体基板を提供する工程であって、この半導体 - オン - 絶縁体基板は

、

半導体ベース層と、

ベース層の上で接触する誘電体層と、

誘電体層の上で接触する単結晶半導体上部層と、

50

を含む工程と、

半導体 - オン - 絶縁体基板の中に少なくとも 2 つのトレンチを形成する工程であって、トレンチは半導体上部層、誘電体層、および部分的に半導体ベース層を通って延び、これにより少なくとも 1 つの高層構造 (elevated structure) を形成し、この高層構造は、

ベース基板の一部であるベース部分と、

ベース部分の上で接触する、誘電体層の一部である誘電体部分と、

誘電体部分の上で接触する、半導体上部層の一部である単結晶半導体上部部分と、

を含む工程と、

それぞれのトレンチの底に分離領域を形成する工程と、

高層構造の上部部分の側壁面の熱酸化により、少なくとも高層構造の側壁面にゲート誘電体層を形成する工程と、10

高層構造とゲート誘電体層との上に導電性層を形成し、これにより少なくとも 1 つのフローティングゲート半導体メモリデバイスを形成する工程であって、誘電体部分はトンネル誘電体層として働き、半導体上部部分はフローティングゲートとして働き、導電性層はコントロールゲートとして働く工程と、を含む。

#### 【 0 0 0 8 】

ある具体例では、分離領域を形成する工程は、トレンチを絶縁性材料で埋める工程と、それぞれのトレンチ中の絶縁性材料を部分的に除去して、それぞれのトレンチの底に絶縁性材料の一部を残し、それぞれのトレンチ中に絶縁性領域を形成する工程とを含む。

#### 【 0 0 0 9 】

誘電体層の等価酸化膜厚は、好適には 6 nm と 10 nm の間である。20

#### 【 0 0 1 0 】

ある具体例によれば、側壁表面のほかに、高層構造の上部表面も酸化される。

#### 【 0 0 1 1 】

好適な具体例では、それぞれのトレンチの底の分離領域は、半導体ベース部分、誘電体部分、およびトレンチのいずれかの側の高層構造のゲート誘電体層の一部に接触し、分離領域は誘電体部分の上に延びる。好適には、誘電体部分の上に延びる分離領域の部分は、5 nm から 20 nm の範囲の高さを有する。

#### 【 0 0 1 2 】

トレンチは、半導体 - オン - 絶縁体基板の上にパターニングしたハードマスク層を形成し、ハードマスク層で覆われない領域をエッチングすることにより形成しても良い。30

#### 【 0 0 1 3 】

ある具体例では、パターニングされたハードマスク層は、高層構造の上に残り、導電性層はハードマスク層の上に形成される。

#### 【 0 0 1 4 】

他の具体例では、ハードマスク層は、トレンチを形成する工程の後で、ゲート誘電体層を形成する工程の前に除去され、この方法は更に、ハードマスク層の除去後でゲート誘電体層の形成工程の前に、高層構造の上の角を丸くする工程を含む。

#### 【 0 0 1 5 】

本発明の方法の具体例では、少なくとも 2 つのトレンチを形成する工程は、以下のサブ工程：40

上部半導体層を通るエッチングにより第 1 トレンチを形成し、これにより誘電体層を露出させる工程、

更に誘電体層を通り、ベース層を部分的に通ってエッチングする工程、

を含んでも良い。

#### 【 0 0 1 6 】

後者の具体例では、この方法は更に、第 1 トレンチの形成工程後で更に誘電体層を通るエッティング工程の前に行われる、第 1 トレンチの間に形成された空間にドーパント元素を注入する工程を含んでも良い。

#### 【 0 0 1 7 】

10

20

30

40

50

ゲート誘電体層の膜厚は、2X世代テクノロジーノード以下では、好適には6nmと8nmの間である。1X世代テクノロジーノードでは、より小さい膜厚が好ましく、即ち8nmより小さく、更には6nmより小さい膜厚が好ましい。

#### 【0018】

本発明は、同様に、フローティングゲート半導体メモリデバイスに関し、このデバイスは、

ベース半導体基板と、少なくとも1つの高層構造と、高層構造のいずれかの側にトレンチを備え、この高層構造は、

ベース基板の一部である、ベース半導体部分と、

ベース部分の上で接触し、トンネル誘電体として働く誘電体部分と、

10

誘電体部分の上で接触し、フローティングゲートとして働く単結晶半導体上部部分と、を含み、更に、

それぞれのトレンチの底の分離領域と、

少なくともフローティングゲートの側壁上のゲート誘電体と、

コントロールゲートとを含み、

それぞれのトレンチの底の分離領域は、半導体ベース部分、誘電体部分、およびトレンチのいずれかの側の高層構造のゲート誘電体層の一部に接触し、分離領域は誘電体部分の上に延びる。好適には、誘電体部分の上に延びる分離領域の部分は、5nmから20nmの範囲の高さを有する。ある具体例では、高層構造はハードマスク層で覆われる。

#### 【0019】

20

トンネル酸化物領域は、好適には、6nmから10nmの範囲の等価酸化物膜厚を有する。高層構造の上部の角は丸くても良く、少なくとも2nmの半径を有する。ゲート誘電体層の膜厚は、好適には6nmと8nmの間である。

#### 【0020】

半導体メモリデバイスの小型化が、1X世代テクノロジーノードまで可能であることが、本発明にかかる方法およびデバイスの特徴である。

#### 【0021】

更に、特にフローティングゲート半導体メモリデバイスに対して、ゲート誘電体層が12nmより小型にできることができることが、本発明にかかる方法およびデバイスの長所である。

#### 【0022】

30

更に、積極的に小型化されたゲート誘電体層は、メモリセルに対して10年のデータ保持を得ることができることができることが、本発明にかかる方法およびデバイスの長所である。

#### 【0023】

更に、フローティングゲート半導体メモリデバイスが、単純なプロセスフローを用いて製造できることができることが、本発明にかかる方法およびデバイスの長所である。これにより、フローティングゲート半導体メモリデバイスを製造するための製造コストを低減できる。

#### 【図面の簡単な説明】

#### 【0024】

【図1】従来技術にかかる不揮発性半導体メモリデバイス、特にフローティングゲート半導体メモリデバイスの概略図を示す。

40

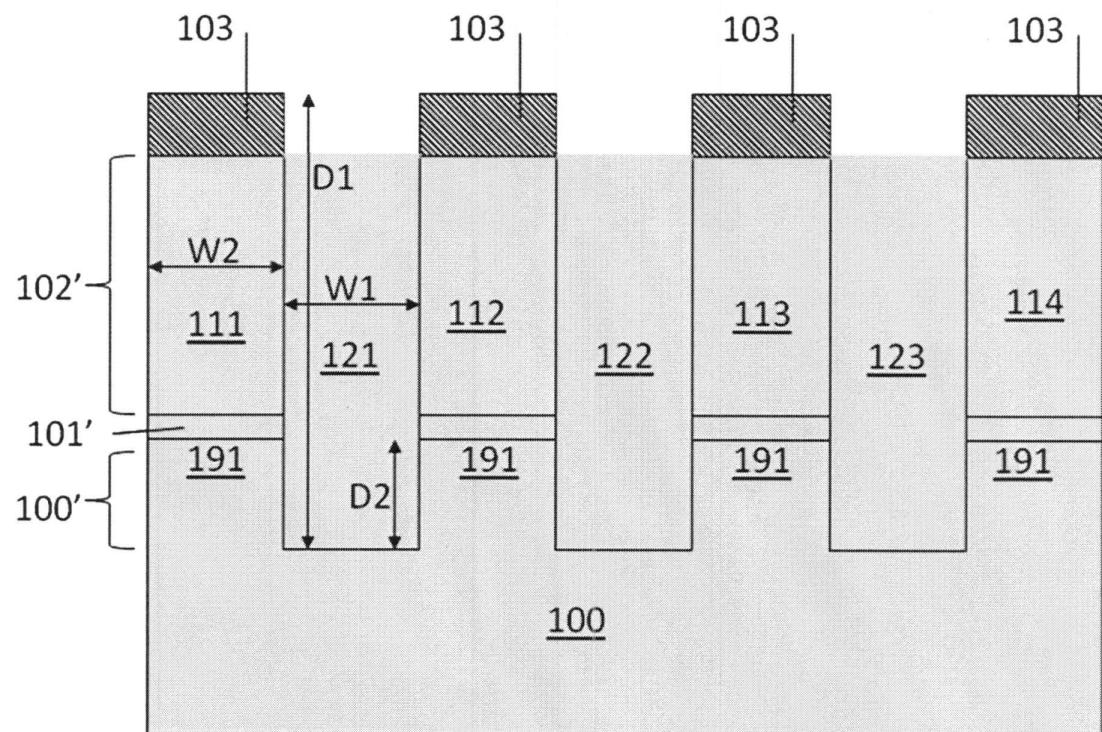

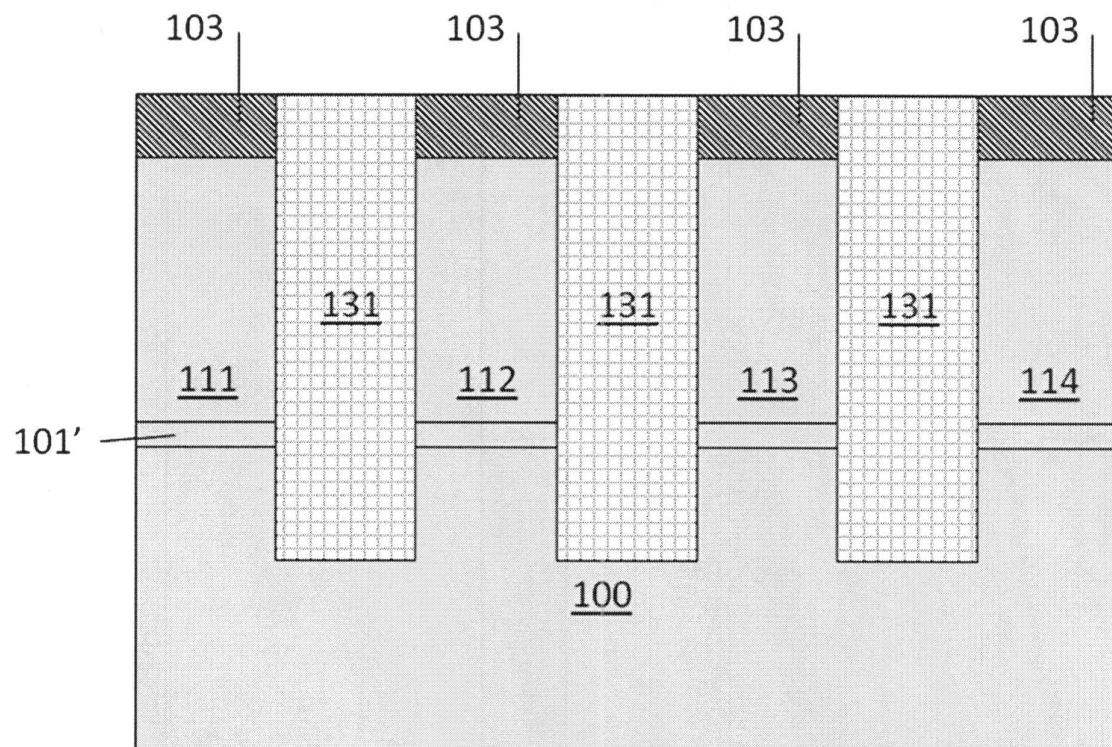

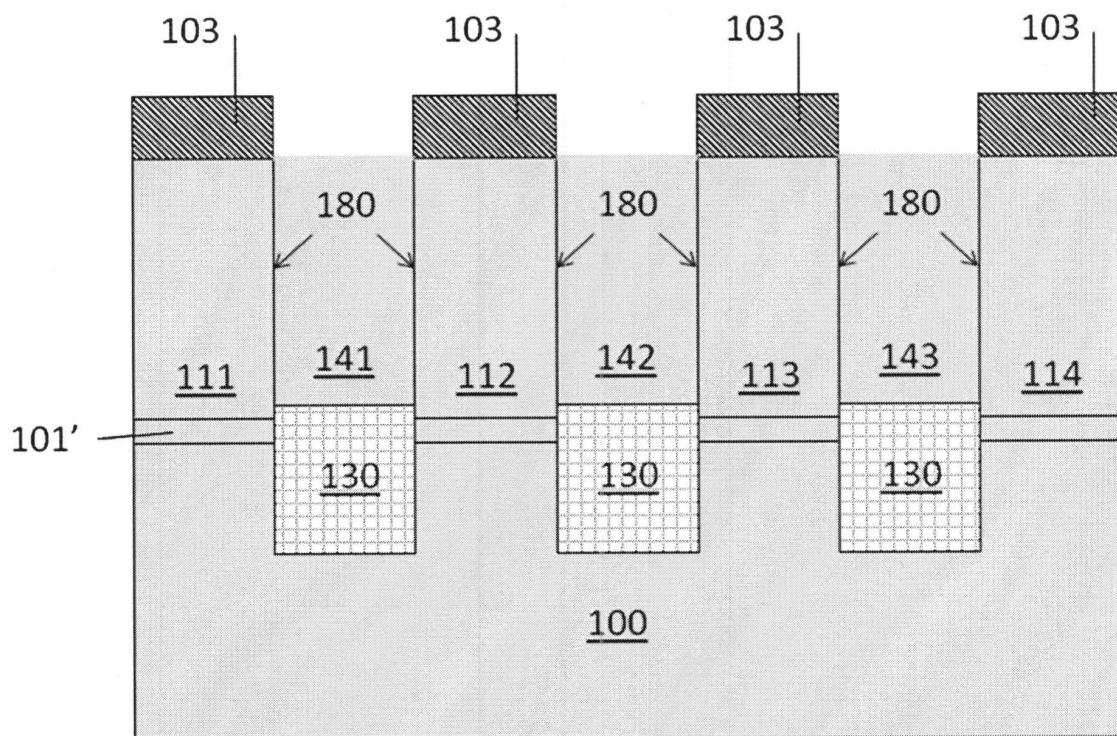

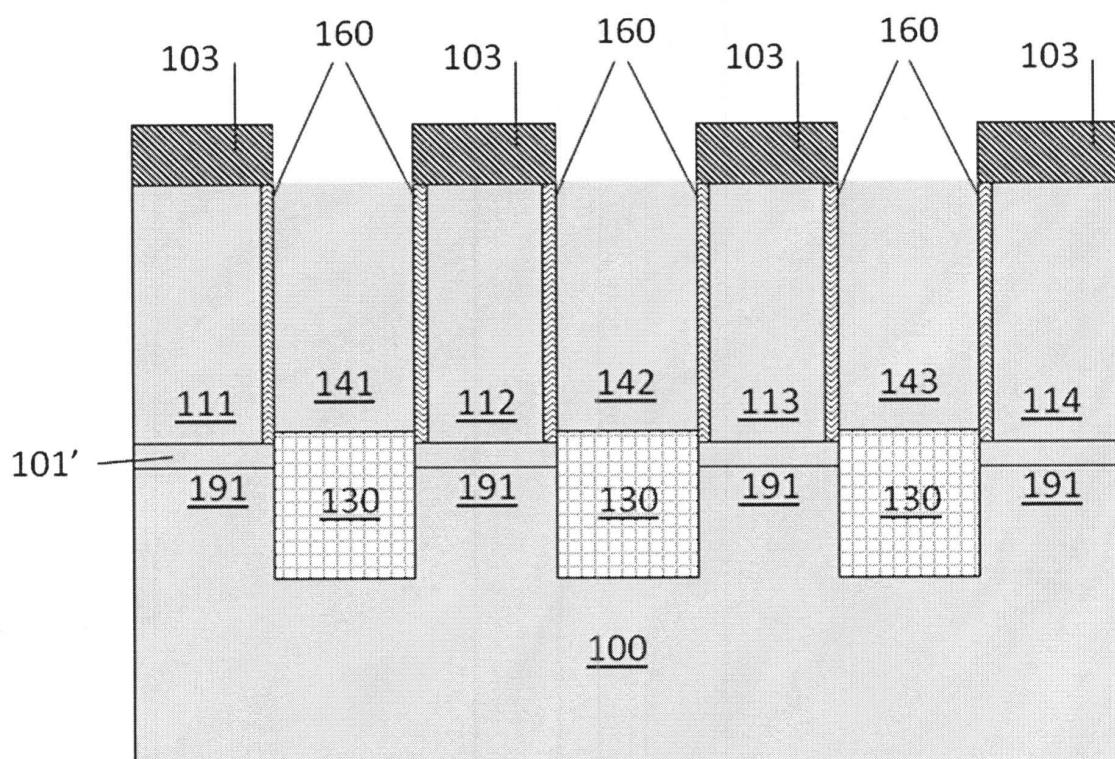

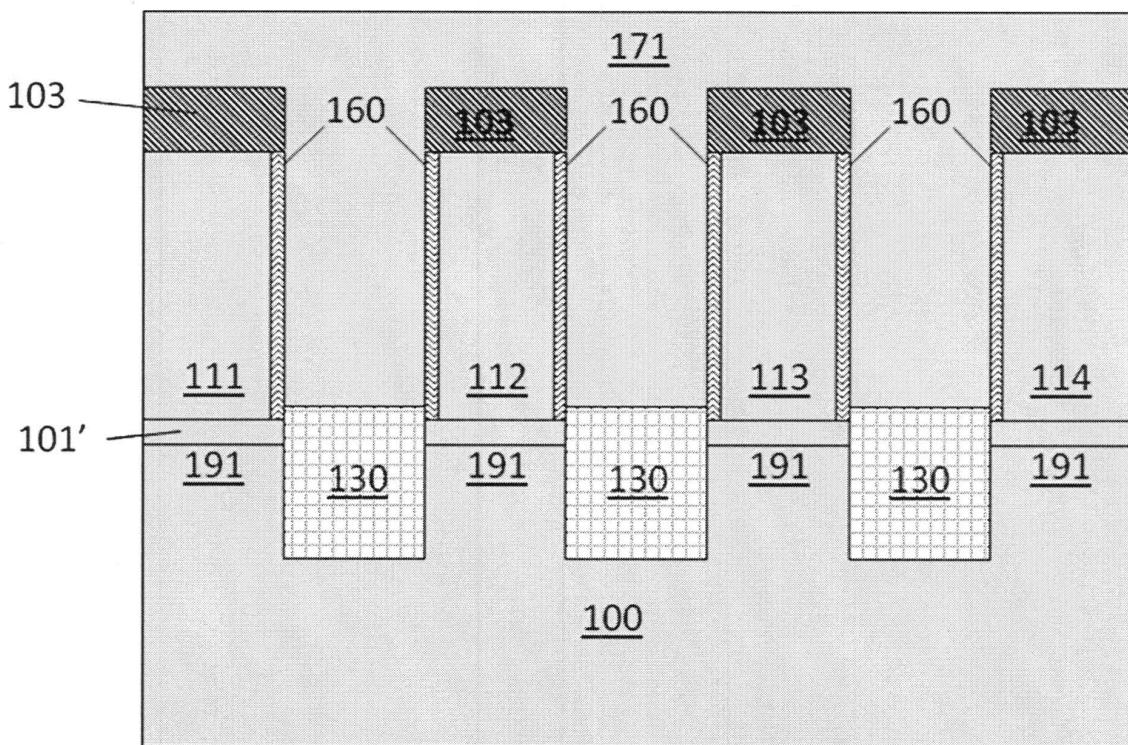

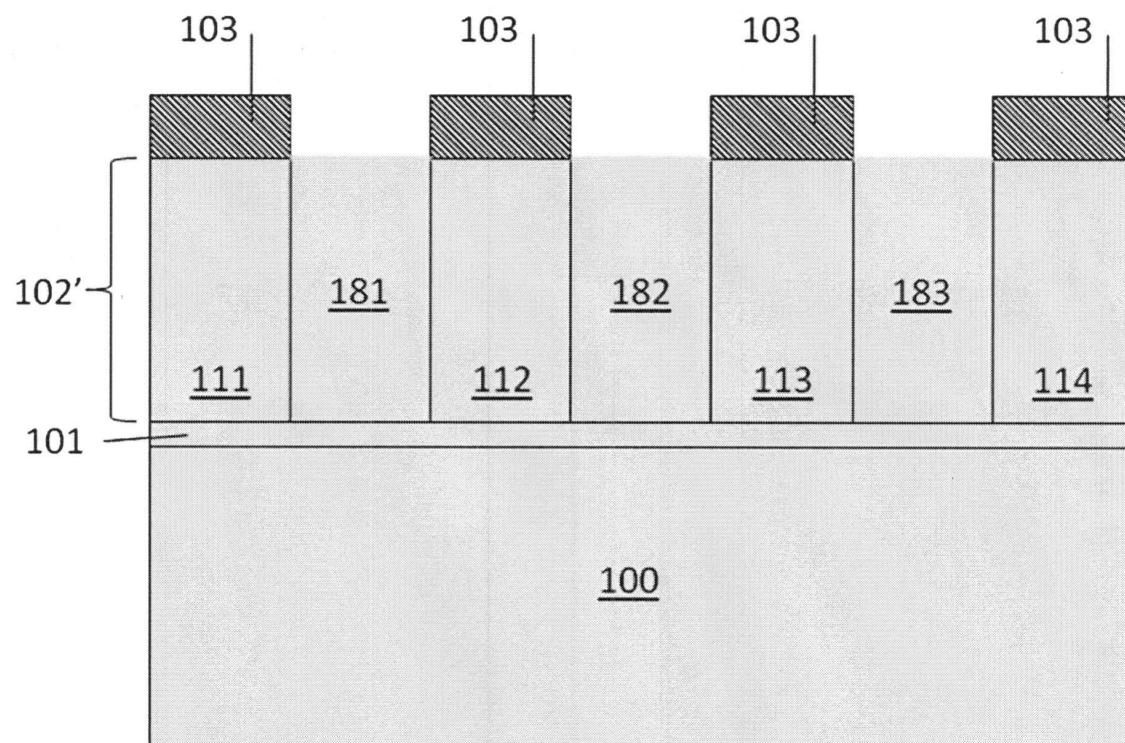

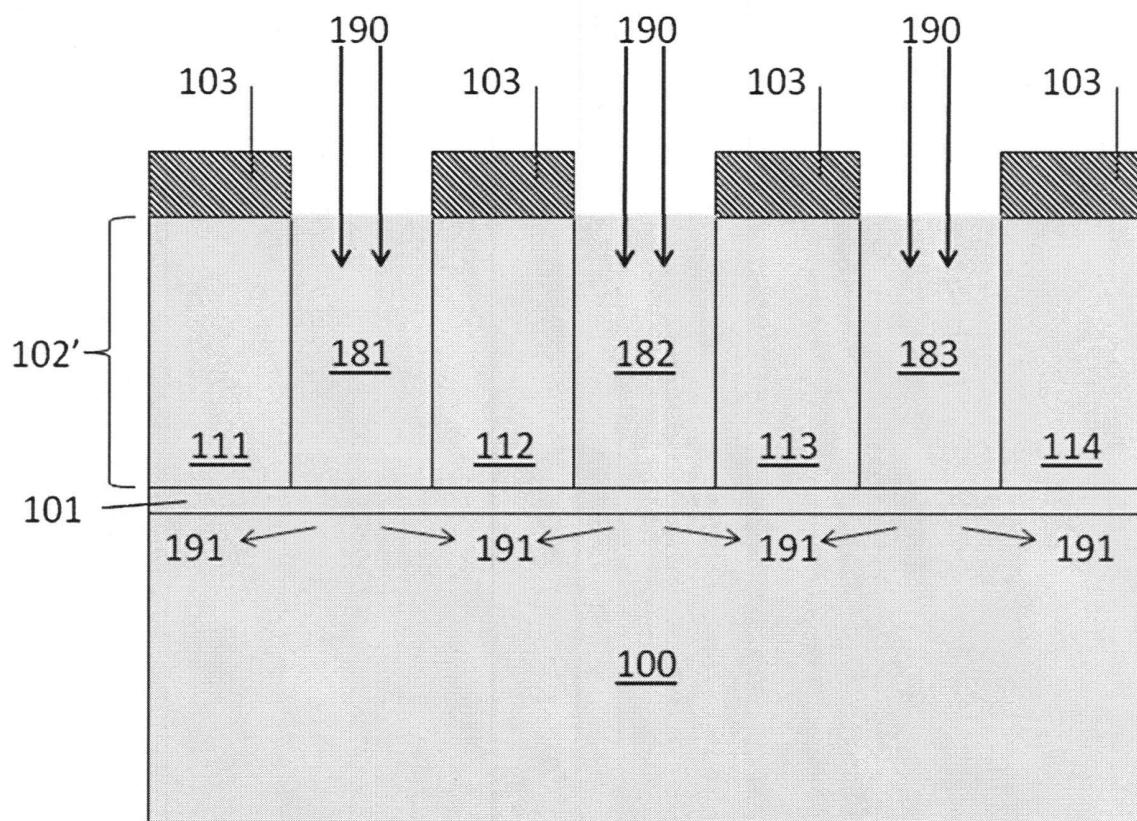

【図2】本発明の具体例にかかるフローティングゲート半導体デバイスの製造方法の異なる具体例を示す。

【図3】本発明の具体例にかかるフローティングゲート半導体デバイスの製造方法の異なる具体例を示す。

【図4】本発明の具体例にかかるフローティングゲート半導体デバイスの製造方法の異なる具体例を示す。

【図5】本発明の具体例にかかるフローティングゲート半導体デバイスの製造方法の異なる具体例を示す。

【図6】本発明の具体例にかかるフローティングゲート半導体デバイスの製造方法の異なる具体例を示す。

50

【図7】本発明の具体例にかかるフローティングゲート半導体デバイスの製造方法の異なる具体例を示す。

【図8】本発明の具体例にかかるフローティングゲート半導体デバイスの製造方法の異なる具体例を示す。

【図9】本発明の具体例にかかるフローティングゲート半導体デバイスの製造方法の異なる具体例を示す。

【図10】本発明の具体例にかかるフローティングゲート半導体デバイスの製造方法の異なる具体例を示す。

【図11】本発明の具体例にかかるフローティングゲート半導体デバイスの製造方法の異なる具体例を示す。 10

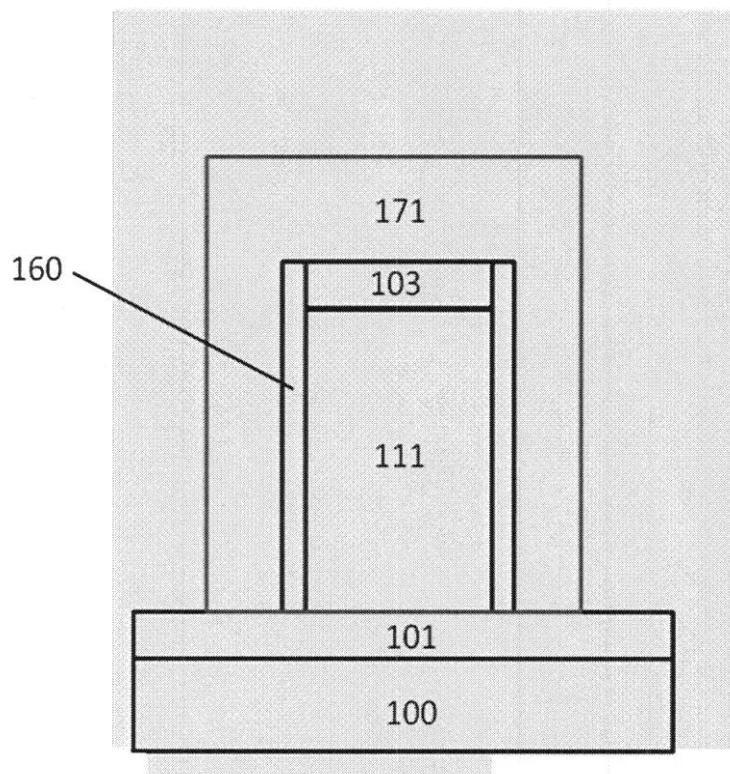

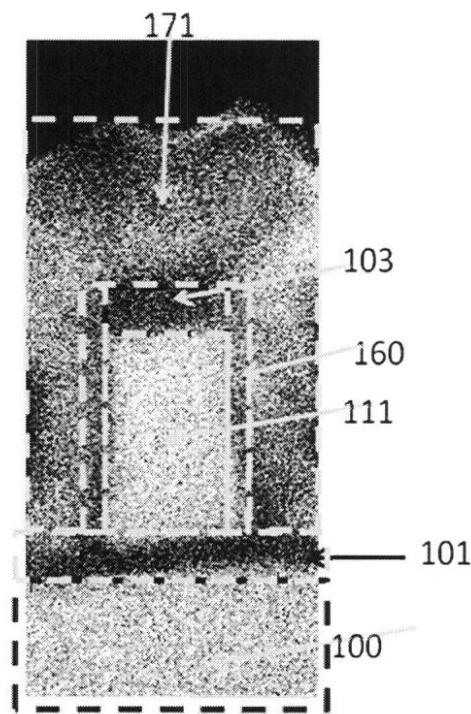

【図12A】本発明の具体例にかかるフローティングゲート半導体デバイスの例を示す。概略図を示す。

【図12B】本発明の具体例にかかるフローティングゲート半導体デバイスの例を示す。顕微鏡写真を示す。

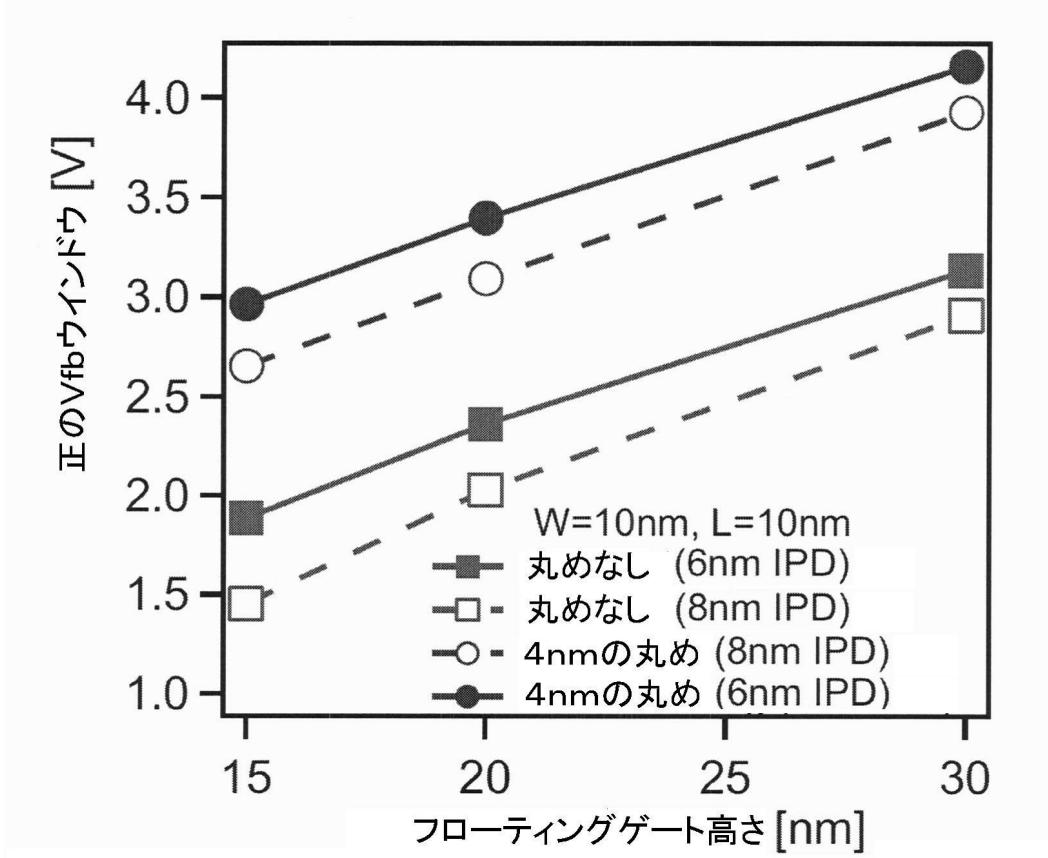

【図13】本発明の具体例により製造されたフローティングゲート領域の角を丸めた場合および角を丸めない場合の正の  $V_{FB}$  シフトのシミュレーション結果を示す。

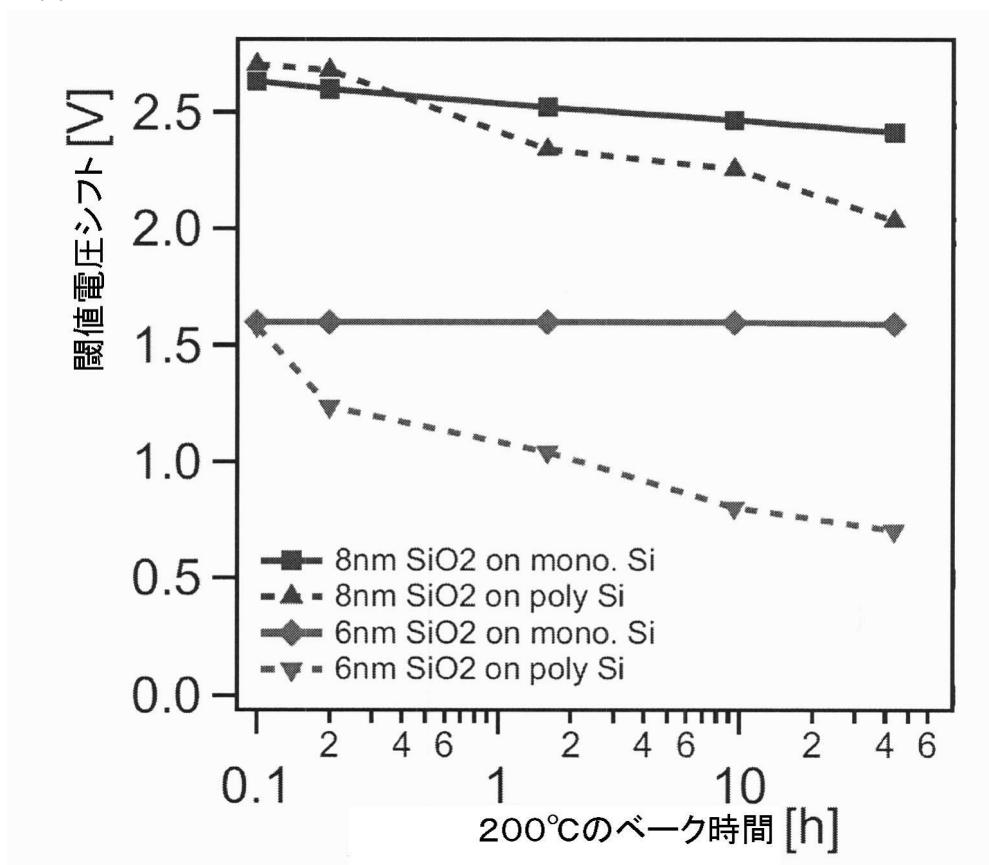

【図14】本発明の具体例にかかるフローティングゲート半導体デバイスについての、10年後の高温データ保持の実験結果を示す。

#### 【0025】

請求項中のいずれの参照符号も、範囲を制限するものと解釈されるべきではない。 20

#### 【0026】

異なる図面において、同一の参照符号は、同一または類似の要素を示す。

#### 【発明を実施するための形態】

#### 【0027】

1またはそれ以上の具体例が、添付の図面を参照して詳細に述べられるが、本発明はこれに限定されるものではない。記載された図面は、単に概略であり、限定するものではない。図面において、図示目的で、いくつかの要素の大きさは拡張され、縮尺通りに記載されていない。当業者は、本発明の範囲に含まれる本発明の多くの変形や修正を認識するであろう。このように、所定の発明の具体例の以下の記載は、本発明の範囲を制限するものと考えるべきではない。 30

#### 【0028】

請求の範囲で使用される「含む (comprising)」の用語は、それ以後に示される要素に限定して解釈すべきではなく、他の要素や工程を排除しない。このように、「手段AおよびBを含むデバイス」の表現の範囲は、構成要素AとBのみを含むデバイスに限定されるべきではない。本発明では、単にデバイスに関連した構成要素がAとBであることを意味する。

#### 【0029】

この明細書を通じて参照される「一の具体例 (one embodiment)」または「ある具体例 (an embodiment)」は、この具体例に関する記載された特定の長所、構造、または特徴は、本発明の少なくとも1つの具体例に含まれることを意味する。このように、この明細書を通して多くの場所の「一の具体例 (one embodiment)」または「ある具体例 (an embodiment)」の語句の表現は、同じ具体例を表す必要はなく、表しても構わない。更に、特定の長所、構造、または特徴は、この記載から当業者に明らかのように、1またはそれ以上の具体例中で適当な方法で組み合わせることができる。 40

#### 【0030】

同様に、例示的な具体例の記載では、能率的に記載し、多くの特徴の1またはそれ以上の理解を助ける目的で、本発明の多くの長所は、時には1つの具体例、図面、またはその記載中にまとめられることを評価すべきである。しかしながら、この開示の方法は、請求される発明がそれぞれの請求項に記載されたものより多くの特徴を必要とする意図して表されていると解釈すべきではない。むしろ、以下の請求項が表すように、発明の態 50

様は、1つの記載された具体例の全ての長所より少なくなる。このように詳細な説明に続く請求の範囲は、これにより詳細な説明中に明確に含まれ、それぞれの請求項は、この発明の別々の具体例としてそれ自身で成立する。

#### 【0031】

更に、ここで記載された幾つかの具体例は幾つかの特徴で、他の具体例に含まれる以外の特徴を含み、異なった具体例の長所の組み合わせは、本発明の範囲に入ることを意味し、当業者に理解されるように異なった具体例を形成する。例えば、以下の請求の範囲では、請求された具体例のいくつかは、他の組み合わせにおいても使用することができる。

#### 【0032】

ここで与えられる記載において、多くの特別な細部が示される。しかしながら、本発明の具体例はそれらの特別な細部無しに実施できることを理解すべきである。他の例では、公知の方法、構造、および技術は、この記載の理解をわかりにくくしないために、詳細には示されていない。10

#### 【0033】

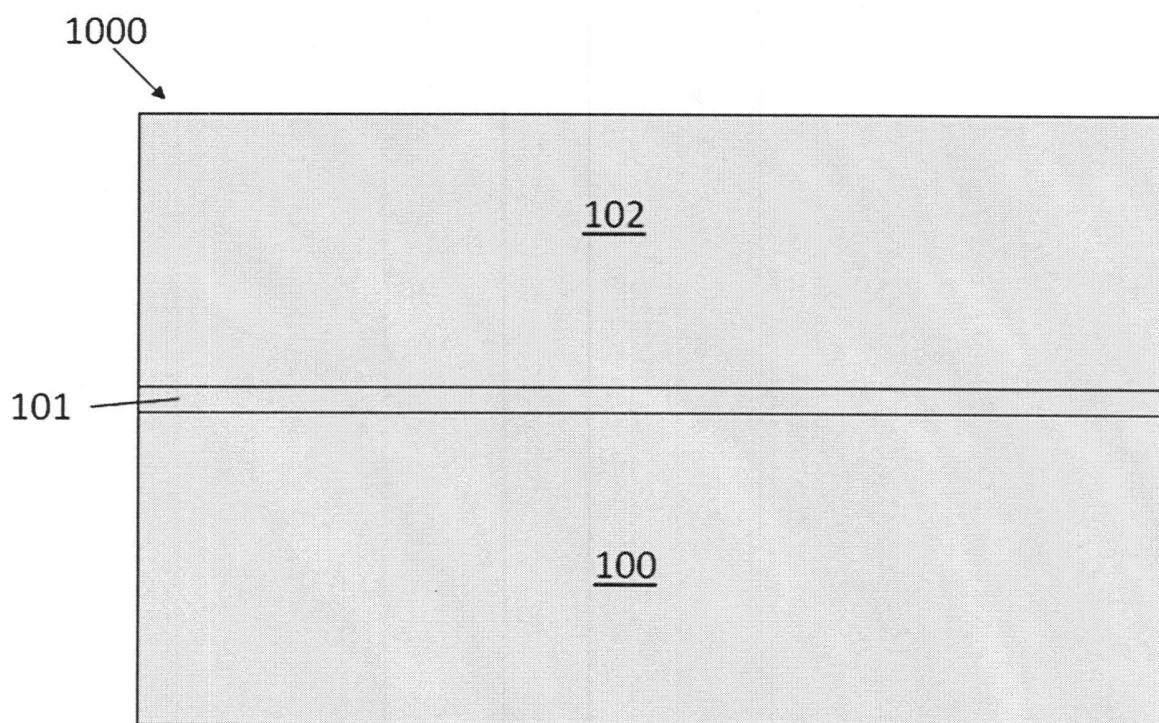

本発明にかかるフローティングゲート半導体メモリデバイスの製造方法の具体例は、図2～図11を参照してより詳細に述べられる。

#### 【0034】

本発明の方法の出発材料は、半導体-オン-絶縁体基板1000である(図2)。半導体-オン-絶縁体基板は、絶縁体層101を含み、これは半導体ベース層100と半導体上部層102との間に挟まれる。半導体上部層102は、単結晶半導体材料を含み、またはからなる。例えば、半導体-オン-絶縁体基板1000は、SOI基板でも良く、即ち、単結晶シリコン(Si)上部層102は埋め込みシリコン酸化層101(box層として知られる)の上に接触し、埋め込みシリコン酸化層101はシリコンベース層100の上に接触する。20

#### 【0035】

誘電体層101は、好適には非常に薄い層であり、これは、誘電体層101の等価酸化膜厚は好適には10nmより小さく、更に好適には6nmと10nmの間であることを意味する。

#### 【0036】

1つの具体例では、少なくとも2つのトレンチ121、122、123が半導体-オン-絶縁体基板1000の中に形成され(図5)、トレンチ121、122、123は半導体ベース層100中に延びて、これにより少なくとも1つの高層構造111、112、113、114を形成し、それぞれの高層構造は、半導体上部部分102'(半導体上部層102の一部、)が誘電体部分101'(誘電体層101の一部)の上に接触し、誘電体部分101'は、半導体ベース部分100'(半導体ベース層100の一部)の上に接触する。高層構造の半導体上部部分102'は、半導体メモリデバイスのフローティングゲートとなる。高層構造の誘電体部分101'は、半導体メモリデバイスのトンネル誘電体層として機能する。30

#### 【0037】

少なくとも2つのトレンチ121-123(およびこれによる高層構造111-114)は、当業者に知られた従来技術を用いて行われ。例えば更に説明するようなリソグラフィ技術を用いて行われる。40

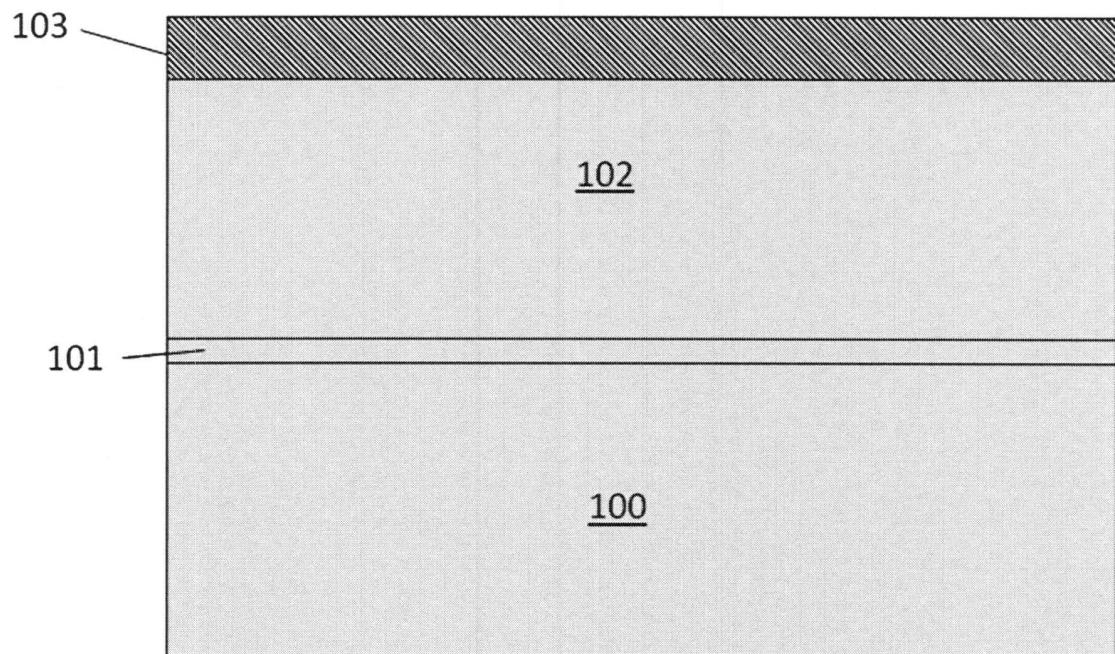

#### 【0038】

示された具体例では、ハードマスク層103は半導体構造1000の上に形成される(図3)。ハードマスク層103は、例えば窒化物層、酸化物層、またはそれらの組み合わせでも良い。

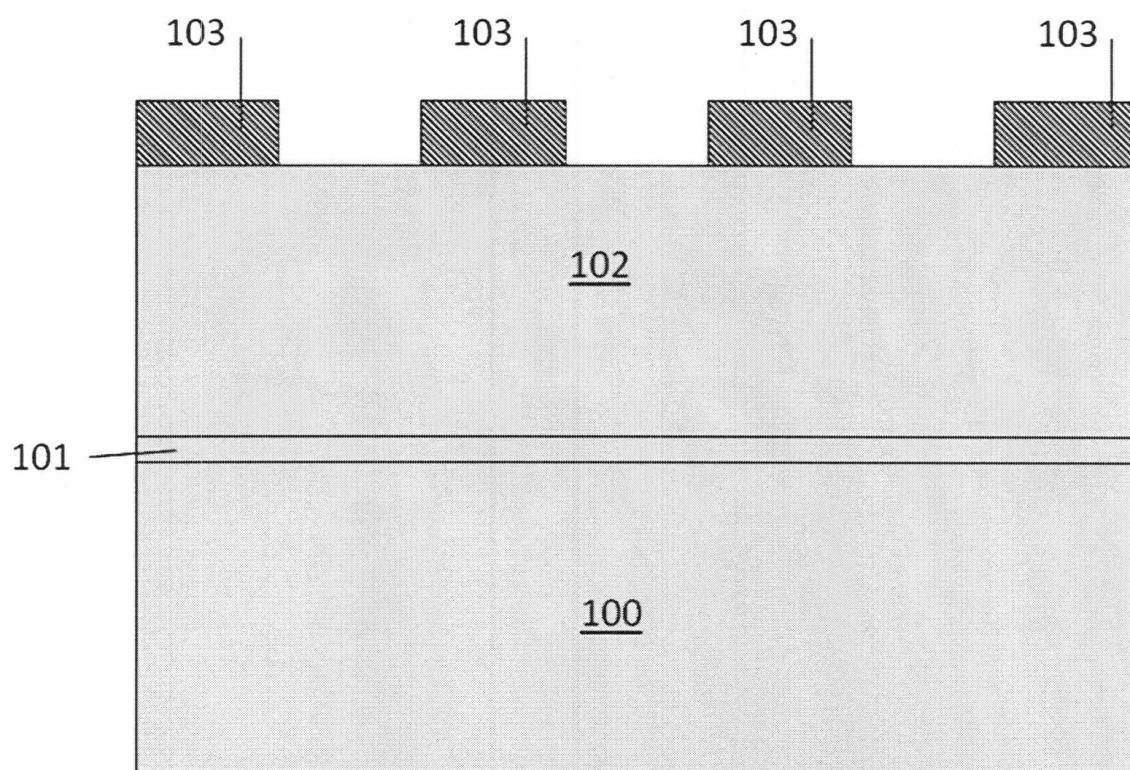

#### 【0039】

次に、ハードマスク層103がパターニングされる(図4)。リソグラフィ技術を用いて、フォトレジスト材料(図示せず)がハードマスク層103の上に提供され、露光され、現像され、およびエッティングされる。次に、下にあるハードマスク層103が、パター50

ニングされたフォトレジスト材料をマスクとして用いてエッティングされても良い。結果としてハードマスク層 103 がパターニングされ、即ちハードマスク層の中に開口部がエッティングされ、これにより下の半導体基板 1000 が露出する。

#### 【0040】

パターニングされたハードマスク層 103 をマスクに用いて、下の半導体基板 1000 がエッティングされて（図 5）、これにより半導体基板 1000 中に一連の開口部（トレンチ）121、122、123 を形成する。換言すれば、半導体基板中に一連の高層構造 111、112、113、114 を形成する。高層構造 111 - 114 は、フィンまたはピローと呼ばれても良い。

#### 【0041】

代わりの具体例では、少なくとも 2 つのトレンチを形成する工程は 2 つの工程で行われ、第 1 エッティング工程では第 1 トレンチ 181、182、183 がエッティングされて、これにより誘電体層 101 が露出し（図 10）、第 2 エッティング工程では、既に形成された高層構造の間の誘電体層 101 の一部をエッティングし、更に半導体層 100 の一部をエッティングすることにより、最終トレンチ 121、122、123 が形成される（図 5）。第 1 と第 2 のエッティング工程の間に、ドーパント原子 190 が基板 100 に注入され、高層構造 111、112、113、114 の下に拡散させても良い（図 11）。この方法で、構造中のチャネル領域 191 が高層構造の下に、細部は本質的に当業者に知られている例えば熱アニールにより形成される。

#### 【0042】

ドーピング方法が基板表面に対して垂直（言い換えれば、高層構造の上面に対して垂直）な場合で、高層構造の上面がハードマスク層 103 で覆われる場合、高層構造は、このドーピング工程中ドープされず、または非常に少量の（無視できるような）ドーパントを受けるだけである。基板中のチャネル領域をドーピングする他の方法は、当業者が予想できるであろう。図 5 に示すように、トレンチ 121 - 123 が 1 つのエッティング工程中に形成される場合、この方法は、高層構造 111 - 114 の側壁を通じて元素を注入することによりドーパント元素を注入し、誘電体部分 101 の下にチャネル領域を形成する工程を含んでも良い。そのような側壁ドーピングは、当業者に等しく知られている。

#### 【0043】

高層構造 111 - 114 は、当業者に知られた、例えばスペーサ規定パターニング（spacer-defined patterning）を用いて形成しても良い。

#### 【0044】

結果の半導体デバイスが用いられる応用やテクノロジーノードに依存して、高層構造の寸法は異なる。好適には、フローティングゲートメモリデバイスの応用では、トレンチの幅 W1（図 5 参照）は、14 nm から 25 nm の範囲であり、高層構造の幅 W2 は 3 nm から 30 nm の範囲であり、トレンチの深さ D1 は 230 nm から 370 nm の範囲であり、これにより誘電体層 101 の下のトレンチの部分の深さ D2 は、200 nm から 300 nm の範囲である。

#### 【0045】

次の工程では、高層構造 111、112、113、114 は、高層構造 111 - 114 の間にシャロートレンチ分離（STI）領域 130 を形成することにより、即ち、トレンチ 121、122、123 を絶縁性材料で部分的に充填することにより、互いに電気的に分離される。これは、最初に、絶縁性材料 131 でトレンチ 121、122、123 を完全に充填した（図 6）後、化学機械研磨（CMP）工程でハードマスク層の上の過剰な絶縁性材料を除去して行われても良い。次に、トレンチ中の絶縁性材料 131 の一部がエッティングされて、高層構造 111、112、113、114 の間に開口部 141、142、143 を残す（図 7）。絶縁性材料 131 のエッティングは、例えばドライエッティング技術またはウエットエッティング技術を用いて行われても良い。絶縁性材料 131 は、シリコン酸化物または STI 領域を形成する当業者に知られたいずれかの材料を含み、またはからなっても良い。フィンの間の良好な電気的分離を確実にするために、シャロートレンチ分

10

20

30

40

50

離領域 130 は、好適には十分深く、即ち、例えば約 300 nm である。シャロートレンチ分離領域 130 は、フローティングゲートチャネル層 191 からのリークを避けるために、コントロールゲート層 171 中に僅かに延びるべきであり、即ち、好適には、トンネル誘電体部分 101' の上に 5 nm から 20 nm の範囲で延びるべきである（図 9）。後者の具体例では、それぞれの分離領域 130 は、このように、ベース部分 100' の側壁、および誘電体部分 101' の側壁、およびその中に分離領域 130 が配置されるトレンチのいずれかの側の上の高層構造のゲート誘電体層 160（の一部）、と横方向に接触する。

#### 【0046】

高層構造 111、112、113、114 は、単結晶半導体材料から形成され、好適には単結晶 Si から形成される。 10

#### 【0047】

全体のハードマスク層、またはその一部 103 のいずれかは、フローティングゲート半導体デバイスの全体の製造フロー中に、存在することが好ましい。ハードマスク層 103 の存在は、セル（高層構造）の角における過大なリークを避ける。代わりに、トレンチ、およびこれにより高層構造の形成工程後に、ハードマスク層が除去されても良い。

#### 【0048】

シャロートレンチ分離領域 130 の形成後に、ゲート誘電体層 160 が高層構造 111、112、113、114 の全ての側壁表面 180 の上に形成されても良い（図 7、図 8 参照）。もしハードマスクが存在しない場合、またはトレンチ 121 - 123 がハードマスクを含まない技術で形成された場合、ゲート誘電体層 160 は、高層構造 111、112、113、114 の上面に形成されても良い。 20

#### 【0049】

本発明では、側壁の表面 180 と、任意的に高層構造 111、112、113、114 の上面に、ゲート誘電体層 160 が、高層構造 111、112、113、114 の半導体材料の熱酸化で形成される。熱酸化は、例えばその場水蒸気発生（ISSG）酸化工程で行われる。

#### 【0050】

高層構造（即ち、フローティングゲート）の上部部分 102' のために、単結晶半導体材料（例えば、単結晶シリコン）を用いることにより、単結晶フローティングゲート上に成長した熱酸化物を使用する機会を与えるように、ゲート誘電体層 160 の品質と拡張性が十分に改良できる。 30

#### 【0051】

そのような熱成長酸化物層は、多結晶フローティングゲート上に従来方法で堆積させた ONO スタックより薄くなる。本発明の方法は、単結晶層 102 に適用可能であり、これにより薄い横方向の分離層（「横方向」は、フィンの側壁を意味する）、好適には 6 nm と 8 nm の間の膜厚を有する分離層を形成できるという長所を提供する。本発明の方法は、それゆえに、メモリデバイスを 1X 世代ノードまで小型化できる。

#### 【0052】

図 8 に示すように、熱酸化は、ゲート誘電体層 160 が分離領域 130 とオーバーラップするような方法で、ゲート誘電体層 160 を形成する。示された具体例では、このオーバーラップは、誘電体部分 101' の上面まで延びる。しかしながら、このオーバーラップはより小さな距離で延びて、ゲート誘電体層 160 は誘電体部分 101' の上面まで延びないで、この上面と、分離領域 130 の上面との間の高さまで延びても良い。 40

#### 【0053】

フローティングゲート領域 102' の上は任意的に丸くても良く、これにより例えば半径が約 2 nm、より好適には 4 nm のような、所定の半径を有する丸い角を形成しても良い。フローティングゲート領域の角の丸みは、過大な電流リークを避ける。ゲート誘電体 160 を形成するための熱酸化は、それ自身が、約 2 nm までの半径のような、角の丸みを、ハードマスク 103 が未だにフィンの上に存在するか否かによらず、フィンの上部の 50

角に形成する。2 nmより大きい半径を有する丸い角を得るために、例えばEP2073 256に記載されたように、ゲート誘電体160を形成する前に好適なプロセスが適用されるのが好ましい。

#### 【0054】

ゲート誘電体160の形成後に、導電性層171が、高層構造111、112、113、114と誘電体層160の上方／上に形成される（図9）。高層構造111、112、113、114の間の空洞141、142、143は、導電性材料171により埋められる。導電性材料171は、また、フィンの上にも形成される。例えばソースとドレイン（s/d）の形成や、フィンの注入やドーピングのような更なる工程が、当業者に知られたように行なわれても良い。

10

#### 【0055】

誘電体層101の一部がトンネル誘電体層として働き、半導体層111、112、113、114の一部がフローティングゲートとして働き、ゲート誘電体層160が従来技術のデバイスのインターポリ誘電体層として働き、そして導電性層がコントロールゲート171として働く、そのようなフローティングゲート半導体デバイスが形成される。

#### 【0056】

##### 例 - 実験結果

具体例にかかる単結晶フローティングゲートデバイスの例と、その電気的な特徴がここで述べられる。

#### 【0057】

例として、単結晶フローティングゲートと、6 nmから8 nmの熱成長SiO<sub>2</sub>ゲート誘電体を有するセル構造が提供される。この薄いゲート誘電体は、ONOの膜厚制限により引き起こされる物理的な小型化の障壁を回避する。シミュレーションでは、12 nmノードまで小さくした場合、そのようなセルは、過大なゲート誘電体リーク無しにプログラム可能であることを示す。モデリングと実験データの組み合わせは、8 nm SiO<sub>2</sub>ゲート誘電体を有する12 nmメモリセルが10年のデータ保持を達成することを示す。シミュレーションは、更に、10 nmノードで、6 nmゲート誘電体に向かう小型化の可能性を予想する。

20

#### 【0058】

提案されたセル構造の断面が、図12Aと図12Bに示される。図12Aは、半導体フローティングゲートデバイスの模式図であり、一方、図12Bは、半導体フローティングゲートデバイスの顕微鏡写真を示す。Si（半導体ベース）層100を有し、その上に約10 nmの膜厚を有するトンネル酸化物層101（SOI埋め込み酸化物層）を有するSOI基板（100-101-111）が示される。半導体層では、フローティングゲート領域111が形成される。フローティングゲート領域は、約75 nmの膜厚／高さと約55 nmの幅を有する単結晶フローティングゲート領域である。フローティングゲート領域111の上には、（フローティングゲート領域のパターニング後に）SiO<sub>2</sub>ハードマスク103が形成される。SiO<sub>2</sub>ハードマスク103は、フローティングゲート111の上のリークを避ける。フローティングゲートの上部の角は、リークを避けるために、例えば4 nmの半径を有するように丸くても良い。単結晶フローティングゲート領域111の側壁は、約6 nmから8 nmの幅を有するSiO<sub>2</sub>ゲート誘電体層を形成するために、熱酸化工程（特に、その場水蒸気発生（ISSG）酸化工程）が行われる。その後に、約25 nmの膜厚を有するポリシリコンのコントロールゲート171が、フローティングゲート／ゲート誘電体構造の上に（堆積工程とパターニング工程で）形成される。

30

#### 【0059】

プログラミング特性と、セルとセルとの干渉を見積もるために、高密度アレイ中に接続されたセルのシミュレーションが、ラファエルRC3（Raphael RC3）を用いて行った。プログラミングとゲート誘電体リークが、RC3から得られる連結比と組み合わせたシングルメモリセルについて、センタウラスデバイス（Sentaurus device）中の非局所トンネリングモデル（nonlocal tunneling model）を用いて得られる。プログラミング飽和は、

40

50

ゲート誘電体リークがフローティングゲート電圧  $V_{FG} = 8.5\text{ V}$  を有するトンネル酸化物電流と等しくなるような、閾値電圧 ( $V_{th}$ ) のシフトとして定義される。データ保持は、パーコレーションモデルと、ささげられたフローティングゲートテスト構造の測定との双方により調査される。

#### 【0060】

フローティングゲート領域の高さと角の丸さの双方が、シングルセルのプログラミング飽和に強い影響を与えることが、図13に示される。上述のように、ゲート誘電体を形成するための熱酸化は、通常、制限された角の丸さを与え、角の丸さの無い場合は、主に理論的な場合に関する。図13は、6 nmまたは8 nmのゲート誘電体層について、角の丸さの有る場合と無い場合の、フローティングゲートの高さを関数とした、正のフラットバンド電圧  $V_{FB}$  ウィンドウの（図12に示すような）フローティングゲートデバイスについてのシミュレーション結果を示す。約1.5 Vの違いが、角の丸さの有る場合と無い場合の間で見られ、これは、角の丸いフローティングゲート領域を有する場合の利点を証明する。しかしながら、ゲート誘電体膜厚は、6 nmから8 nmの研究範囲内では、プログラミング性能に重大ではない。

10

#### 【0061】

また、高温データ保持は、細長いフローティングゲートテスト構造である、多数の単結晶フローティングゲートストライプを含む（図12Bに示すような）ささげられたテスト構造で測定された。フローティングゲート上に成長させた薄いSiO<sub>2</sub>ハードマスク（キャッピング）層の品質が非常に良い場合、200 °Cの温度で40時間より長くベークした後に、小さな閾値電圧 ( $V_{th}$ ) となることが、図14で明らかに見られる。実線は単結晶フローティングゲートの結果であり、一方、点線は多結晶フローティングゲートの結果を示す。6 nmゲート誘電体と、8 nmゲート誘電体の結果が示される。

20

#### 【0062】

究極のフローティングゲートNANDセルの小型化のための、大きく小型化された熱SiO<sub>2</sub>ゲート誘電体を有する単結晶フローティングゲート構造が提供できることが、所定の発明の形態の具体例の利点である。この構造を用いると、NANDフラッシュが、主な障害（幾何学的小型化、寄生干渉、フローティングゲート電荷）無しに、少なくとも12 nmまで小型化できる。テスト構造のシミュレーション結果および実験結果は、これに必要な大きく小型化されたゲート誘電体は、エラーチェッキングと修正アルゴリズム（ECC）により修正可能な、ほんのわずかの壊れたセルを考慮しても、10年のデータ保持が可能であることを示す。

30

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12A】

【図12B】

【図13】

【図14】

---

フロントページの続き

|               |           |              |   |

|---------------|-----------|--------------|---|

| (51)Int.Cl.   | F I       |              |   |

| H 01 L 29/423 | (2006.01) | H 01 L 21/28 | A |

| H 01 L 29/49  | (2006.01) |              |   |

| H 01 L 29/41  | (2006.01) |              |   |

| H 01 L 21/28  | (2006.01) |              |   |

(72)発明者 ピーテル・ブロンメ

ベルギー 3 0 0 1 ルーヴァン、カペルドリーフ 75 番 アイメック内

(72)発明者 アントニーノ・カチアート

ベルギー 3 0 0 1 ルーヴァン、カペルドリーフ 75 番 アイメック内

(72)発明者 ゴウリ・サンカール・カー

ベルギー 3 0 0 1 ルーヴァン、カペルドリーフ 75 番 アイメック内

審査官 加藤 俊哉

(56)参考文献 特開平 11 - 103033 (JP, A)

特開 2009 - 141277 (JP, A)

米国特許出願公開第 2006 / 0043456 (US, A1)

米国特許出願公開第 2010 / 0248435 (US, A1)

欧州特許出願公開第 02073256 (EP, A1)

(58)調査した分野(Int.Cl., DB名)

H 01 L 21 / 8247

H 01 L 21 / 28

H 01 L 21 / 336

H 01 L 27 / 115

H 01 L 29 / 41

H 01 L 29 / 423

H 01 L 29 / 49

H 01 L 29 / 788

H 01 L 29 / 792