(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第3541625号

(P3541625)

(45) 発行日 平成16年7月14日(2004.7.14)

(24) 登録日 平成16年4月9日(2004.4.9)

(51) Int.C1.<sup>7</sup>

F 1

G09F 9/30

G09F 9/30

D

G09G 3/30

G09G 3/30

Z

H05B 33/26

H05B 33/26

請求項の数 11 (全 16 頁)

(21) 出願番号

特願平9-177454

(22) 出願日

平成9年7月2日(1997.7.2)

(65) 公開番号

特開平11-24604

(43) 公開日

平成11年1月29日(1999.1.29)

審査請求日

平成15年11月10日(2003.11.10)

早期審査対象出願

(73) 特許権者 000002369

セイコーエプソン株式会社

東京都新宿区西新宿2丁目4番1号

(74) 代理人 100095728

弁理士 上柳 雅善

(74) 代理人 100107261

弁理士 須澤 修

(72) 発明者 小澤 德郎

長野県諏訪市大和3丁目3番5号 セイコーエプソン株式会社内

審査官 佐竹 政彦

(56) 参考文献 特開平05-258861 (JP, A)

特開平10-333601 (JP, A)

最終頁に続く

(54) 【発明の名称】表示装置及びアクティブマトリクス基板

## (57) 【特許請求の範囲】

## 【請求項1】

複数の走査線と、

前記複数の走査線と交差する方向に設けられた複数のデータ線と、

複数の共通給電線と、

前記複数のデータ線と前記複数の走査線とによりマトリクス状に形成された複数の画素と、を有し、

前記複数の画素の各々は、

層間絶縁膜上に形成された画素電極と前記画素電極に対向する対向電極との間に流れる駆動電流によって発光する発光素子を備え、

前記発光素子は有機半導体膜を含み、

前記有機半導体膜は、前記有機半導体膜より厚く形成されたバンク層により囲まれた領域内に形成されており、

前記バンク層は、絶縁膜からなるとともに前記有機半導体膜の上面より高く形成されており、

前記複数のデータ線は、前記層間絶縁膜により覆われており、

前記複数のデータ線のうち、前記複数の画素の各々に対応するデータ線の少なくとも一部は前記バンク層により覆われていること、

を特徴とする表示装置。

## 【請求項2】

10

20

請求項 1 に記載の表示装置において、

さらに前記複数のデータ線に対して画像信号を出力する第 1 の駆動回路と、

前記複数の走査線に対して走査信号を出力する第 2 の駆動回路と、を備え、

前記第 1 の駆動回路及び前記第 2 の駆動回路のうち少なくともいずれかは、前記バンク層

によって覆われていること、

を特徴とする表示装置。

【請求項 3】

請求項 1 または 2 に記載の表示装置において、

前記複数の画素の各々は、

ゲート電極を備え、前記複数の走査線のうち対応する走査線を介して走査信号が前記ゲー

ト電極に供給される第 1 のトランジスタと、

前記複数のデータ線のうち対応するデータ線及び前記第 1 のトランジスタを介して供給さ

れる画像信号に応じて、前記複数の共通給電線のうち対応する共通給電線と前記画素電極

との電気的な接続の制御を行う第 2 のトランジスタと、を備えていること、

を特徴とする表示装置。

【請求項 4】

請求項 3 に記載の表示装置において、

前記第 2 のトランジスタの一部と前記画素電極とは重なっていること、

を特徴とする表示装置。

【請求項 5】

請求項 3 または 4 に記載の表示装置において、

前記第 1 のトランジスタは前記バンク層により覆われていること、

を特徴とする表示装置。

【請求項 6】

請求項 3 乃至 5 のいずれかに記載の表示装置において、

前記第 2 のトランジスタと前記画素電極とは中継電極を介して接続されており、

前記中継電極は前記バンク層により覆われていること、

を特徴とする表示装置。

【請求項 7】

請求項 1 乃至 6 のいずれかに記載の表示装置において、

前記有機半導体膜は、インクジェット法により形成された膜であり、

前記バンク層は、撥水性を有する膜であること、

を特徴とする表示装置。

【請求項 8】

請求項 1 乃至 7 のいずれかに記載の表示装置において、

前記バンク層は、膜厚が  $1 \mu m$  以上であること、

を特徴とする表示装置。

【請求項 9】

請求項 1 乃至 8 のいずれかに記載の表示装置において、

前記バンク層は黒色のレジスト膜から構成されていること、

を特徴とする表示装置。

【請求項 10】

請求項 1 乃至 9 のいずれかに記載の表示装置において、

前記複数の共通給電線の各々の単位長さ当たりの抵抗値は、前記複数のデータ線の対応す

るデータ線の単位長さ当たりの抵抗値よりも小さいこと、

を特徴とする表示装置。

【請求項 11】

請求項 1 乃至 10 のいずれかに記載の表示装置において、

前記複数の共通給電線の各々の線幅は、前記複数のデータ線の対応するデータ線の線幅よ

りも大であること、

10

20

30

40

50

を特徴とする表示装置。

【発明の詳細な説明】

【0001】

【発明の属する技術分野】

本発明は、有機半導体膜に駆動電流が流れることによって発光するE L (エレクトロルミネッセンス) 素子またはL E D (発光ダイオード) 素子などの発光素子を薄膜トランジスタ(以下、T F T という。)で駆動制御するアクティブマトリクス型の表示装置に関するものである。さらに詳しくは、その表示特性を向上するためのレイアウトの最適化技術に関するものである。

【0002】

10

【従来の技術】

E L 素子またはL E D 素子などの電流制御型発光素子を用いたアクティブマトリクス型の表示装置が提案されている。このタイプの表示装置に用いられる発光素子はいずれも自己発光するため、液晶表示装置と違ってバックライトを必要とせず、また、視野角依存性が少ないなどの利点もある。

【0003】

図13は、このような表示装置の一例として、電荷注入型の有機薄膜E L 素子を用いたアクティブマトリクス型表示装置のブロック図を示してある。この図に示す表示装置1 Aでは、透明基板上に、複数の走査線g a t eと、該走査線g a t eの延設方向に対して交差する方向に延設された複数のデータ線s i gと、該データ線s i gに並列する複数の共通給電線c o mと、データ線s i gと走査線g a t eとの交差点に対応する画素領域7とが構成されている。データ線s i gに対しては、シフトレジスタ、レベルシフタ、ビデオライン、アナログスイッチを備えるデータ側駆動回路3が構成されている。走査線に対しては、シフトレジスタおよびレベルシフタを備える走査側駆動回路4が構成されている。また、画素領域7の各々には、走査線を介して走査信号がゲート電極に供給される第1のT F T 2 0と、この第1のT F T 2 0を介してデータ線s i gから供給される画像信号を保持する保持容量c a pと、該保持容量c a pによって保持された画像信号がゲート電極に供給される第2のT F T 3 0と、第2のT F T 3 0を介して共通給電線c o mに電気的に接続したときに共通給電線c o mから駆動電流が流れ込む発光素子4 0とが構成されている。

20

【0004】

30

すなわち、図14(A)、(B)に示すように、いずれの画素領域においても、島状の2つの半導体膜を利用して第1のT F T 2 0および第2のT F T 3 0が形成され、第2のT F T 3 0のソース・ドレイン領域の一方には、第1層間絶縁膜5 1のコンタクトホールを介して中継電極3 5が電気的に接続し、該中継電極3 5には画素電極4 1が電気的に接続している。この画素電極4 1の上層側には、正孔注入層4 2、有機半導体膜4 3、対向電極o pが積層されている。ここで、対向電極o pは、データ線s i gなどを跨いで複数の画素領域7にわたって形成されている。

【0005】

40

第2のT F T 3 0のソース・ドレイン領域のもう一方には、コンタクトホールを介して共通給電線c o mが電気的に接続している。これに対して、第1のT F T 2 0では、そのソース・ドレイン領域の一方に電気的に接続する電位保持電極s tは、ゲート電極3 1の延設部分3 1 0に電気的に接続している。この延設部分3 1 0に対しては、その下層側においてゲート絶縁膜5 0を介して半導体膜4 0 0が対向し、この半導体膜4 0 0は、それに導入された不純物によって導電化されているので、延設部分3 1 0およびゲート絶縁膜5 0とともに保持容量c a pを構成している。ここで、半導体膜4 0 0に対しては第1の層間絶縁膜5 1のコンタクトホールを介して共通給電線c o mが電気的に接続している。従って、保持容量c a pは、第1のT F T 2 0を介してデータ線s i gから供給される画像信号を保持するので、第1のT F T 2 0がオフになっても、第2のT F T 3 0のゲート電極3 1は画像信号に相当する電位に保持される。それ故、発光素子4 0には共通給電線c

50

o m から駆動電流が流れ続けるので、発光素子 4 0 は発光し続けることになる。

【 0 0 0 6 】

【発明が解決しようとする課題】

しかしながら、前記の表示装置において、画素電極 4 1 に対向する対向電極 o p は、液晶表示装置と相違して、同じ透明基板 1 0 上において、その表面全体、あるいは複数の画素領域 7 にわたって形成されるため、対向電極 o p はデータ線 s i g との間に第 2 の層間絶縁膜 5 2 のみを有することになる。このため、データ線 s i g には大きな容量が寄生することになって、従来の表示装置のままでは、データ線 s i g の負荷が大きい。同様な問題点は、データ側駆動回路 3 や走査側駆動回路 4 の表面側に重なるように対向電極 o p が形成されることに起因して、駆動回路に形成される配線層と対向電極との間に寄生する容量が大きく、データ側駆動回路 3 の負荷が大きいという問題点を引き起こす。

10

【 0 0 0 7 】

ここに、本発明者は、インクジェットヘッドから吐出した液状の材料から有機半導体膜を所定の領域に形成することを検討するとともに、この方法で有機半導体膜を形成する際に有機半導体膜が側方にはみ出すことを防止するために有機半導体膜の形成領域をレジストなどで構成したバンク層で囲うことを検討してきた。このような構成などをを利用して、本願発明者は上記の問題点を解消することを提案する。

【 0 0 0 8 】

すなわち、本発明の課題は、基板上に有機半導体膜の形成領域を規定するためのバンク層を利用して、データ線や駆動回路に容量が寄生することを防止することのできる表示装置

20 を提供することにある。

【 0 0 0 9 】

【課題を解決するための手段】

本発明の表示装置は、複数の走査線と、前記複数の走査線と交差する方向に設けられた複数のデータ線と、複数の共通給電線と、前記複数のデータ線と前記複数の走査線とによりマトリクス状に形成された複数の画素と、を有し、前記複数の画素の各々は、層間絶縁膜上に形成された画素電極と前記画素電極に対向する対向電極との間に流れる駆動電流によって発光する発光素子を備え、前記発光素子は有機半導体膜を含み、前記有機半導体膜は、前記有機半導体膜より厚く形成されたバンク層により囲まれた領域内に形成されており

前記バンク層は、絶縁膜からなるとともに前記有機半導体膜の上面より高く形成されており

前記複数のデータ線は、前記層間絶縁膜により覆われてあり、前記複数のデータ線のうち、前記複数の画素の各々に対応するデータ線の少なくとも一部は前記バンク層により覆われていること、を特徴とする。

30

【 0 0 1 0 】

上記の表示装置において、さらに前記複数のデータ線に対して画像信号を出力する第 1 の駆動回路と、前記複数の走査線に対して走査信号を出力する第 2 の駆動回路と、を備え、前記第 1 の駆動回路及び前記第 2 の駆動回路のうち少なくともいずれかは、前記バンク層によって覆われていてもよい。

【 0 0 1 1 】

上記の表示装置において、前記複数の画素の各々は、ゲート電極を備え、前記複数の走査線のうち対応する走査線を介して走査信号が前記ゲート電極に供給される第 1 のトランジスタと、前記複数のデータ線のうち対応するデータ線及び前記第 1 のトランジスタを介して供給される画像信号に応じて、前記複数の共通給電線のうち対応する共通給電線と前記画素電極との電気的な接続の制御を行う第 2 のトランジスタと、を備えていることが好ましい。

40

【 0 0 1 2 】

上記の表示装置において、前記第 2 のトランジスタの一部と前記画素電極とは重なっていることが好ましい。

【 0 0 1 3 】

上記の表示装置において、前記第 1 のトランジスタは前記バンク層により覆われているこ

50

とが好ましい。

**【0014】**

上記の表示装置において、前記第2のトランジスタと前記画素電極とは中継電極を介して接続されており、前記中継電極は前記バンク層により覆われていることが好ましい。

**【0015】**

上記の表示装置において、前記有機半導体膜は、インクジェット法により形成された膜であり、前記バンク層は、撥水性を有する膜であることが好ましい。

**【0016】**

上記の表示装置において、前記バンク層は、膜厚が $1\text{ }\mu\text{m}$ 以上であることが好ましい。

**【0017】**

上記の表示装置において、前記バンク層は黒色のレジスト膜から構成されていることが好ましい。

上記の表示装置において、前記複数の共通給電線の各々の単位長さ当たりの抵抗値は、前記複数のデータ線の対応するデータ線の単位長さ当たりの抵抗値よりも小さいことが好ましい。

上記の表示装置において、前記複数の共通給電線の各々の線幅は、前記複数のデータ線の対応するデータ線の線幅よりも大であることが好ましい。

**【0019】**

**【発明の実施の形態】**

図面を参照して、本発明の実施の形態を説明する。

**【0020】**

(アクティブマトリクス基板の全体構成)

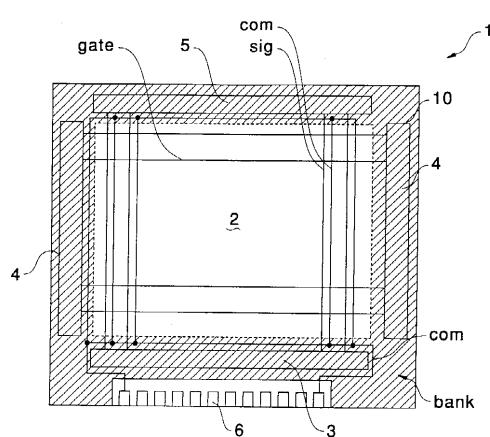

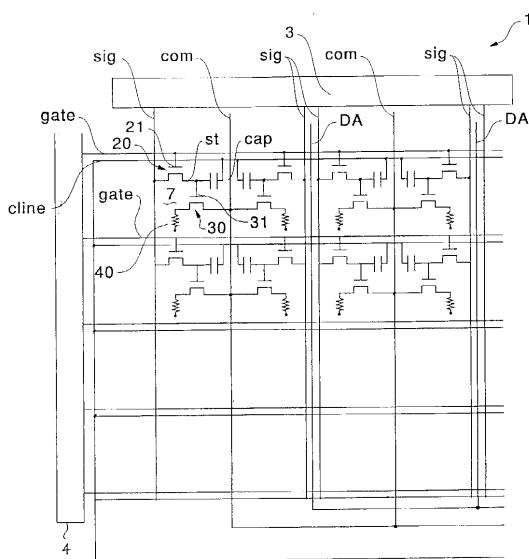

図1は、表示装置の全体のレイアウトを模式的に示すブロック図である。

**【0021】**

この図に示すように、本形態の表示装置1では、その基体たる透明基板10の中央部分が表示部2とされている。透明基板10の外周部分のうち、データ線sigの両端側には画像信号を出力するデータ側駆動回路3(第1の駆動回路)、および検査回路5が構成され、走査線gateの両端側には走査信号を出力する走査側駆動回路4(第2の駆動回路)が構成されている。これらの駆動回路3、4では、N型のTFTとP型のTFTとによって相補型TFTが構成され、この相補型TFTは、シフトレジスタ、レベルシフタ、アナログスイッチなどを構成している。なお、透明基板10上において、データ側駆動回路3よりも外周領域には、画像信号や各種の電位、パルス信号を入力するための端子群とされる実装用パッド6が形成されている。

**【0022】**

このよう構成した表示装置1では、液晶表示装置のアクティブマトリクス基板と同様、透明基板10上に、複数の走査線gateと、該走査線gateの延設方向に対して交差する方向に延設された複数のデータ線sigとが構成され、これらのデータ線sigと走査線gateとによりマトリクス状に形成された複数の画素領域7が構成されている。

**【0023】**

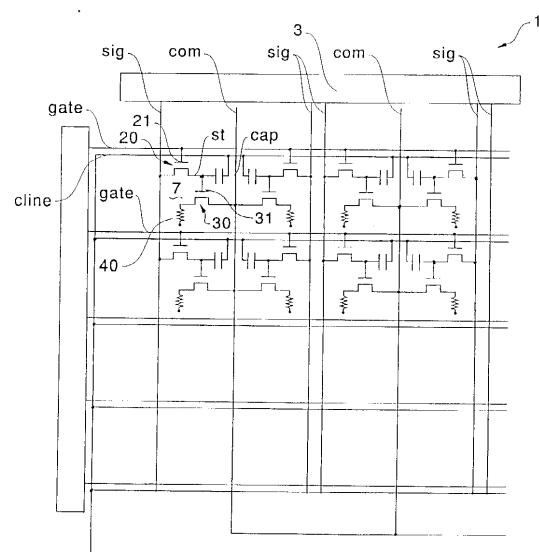

これらの画素領域7のいずれにも、図2に示すように、走査線gateを介して走査信号がゲート電極21(第1のゲート電極)に供給される第1のTFT20が構成されている。このTFT20のソース・ドレイン領域の一方は、データ線sigに電気的に接続され、他方は電位保持電極stに電気的に接続されている。走査線gateに対しては容量線cilineが並列配置され、この容量線cilineと電位保持電極stとの間には保持容量capが形成されている。従って、走査信号によって選択されて第1のTFT20がオン状態になると、データ線sigから画像信号が第1のTFT20を介して保持容量capに書き込まれる。

**【0024】**

電位保持電極stには第2のTFT30のゲート電極31(第2のゲート電極)が電気的に接続されている。第2のTFT30のソース・ドレイン領域の一方は、共通給電線co

10

20

30

40

50

mに電気的に接続されている一方、他方は発光素子40の一方の電極（後述する画素電極）に電気的に接続されている。共通給電線comは、定電位に保持されている。従って、第2のTFT30がオン状態になったときに、第2のTFT30を介して共通給電線comの電流が発光素子40に流れ、発光素子40を発光させる。

#### 【0025】

但し、本形態では、共通給電線comの両側には、該共通給電線comとの間で駆動電流の供給が行われる発光素子40を有する画素領域7が配置され、これらの画素領域7に対して共通給電線comとは反対側を2本のデータ線sigが通っている。すなわち、データ線sig、それに接続する画素群、1本の共通給電線com、それに接続する画素群、および該画素群に画素信号を供給するデータ線sigを1つの単位としてそれを走査線gatetの延設方向に繰り返してあり、共通給電線comは、1本で2列分の画素に対して駆動電流を供給する。従って、1列の画素群ごとに共通給電線comを形成する場合と比較して、共通給電線comの形成領域が狭くて済み、発光面積を増やすことができるので、輝度、コントラスト比などの表示性能を向上させることができる。なお、このように1本の共通給電線comに2列分の画素が接続される構成としたため、データ線sigは2本ずつ並列する状態にあって、それぞれの列の画素群に対して画像信号を供給することになる。

#### 【0026】

##### （画素領域の構成）

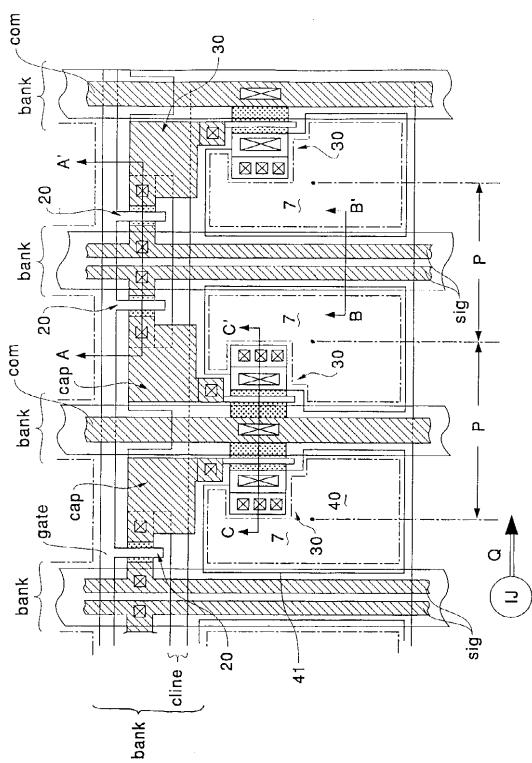

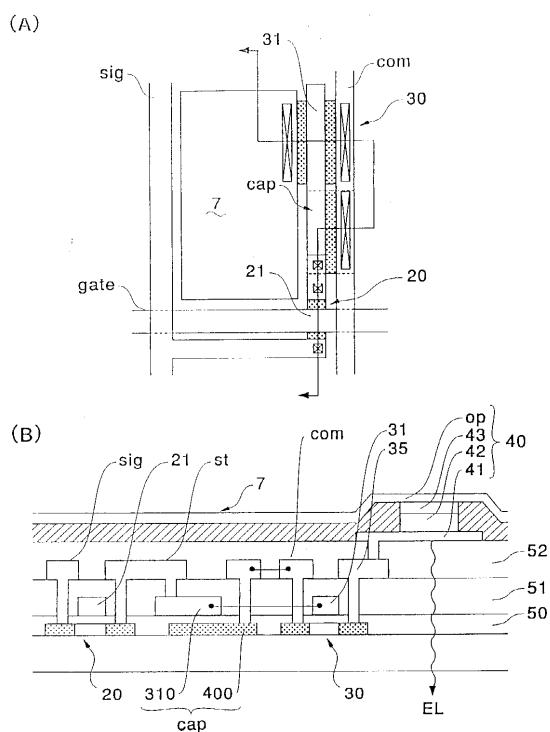

このように構成した表示装置1の各画素領域7の構造を図3ないし図6(A)を参照して詳述する。

#### 【0027】

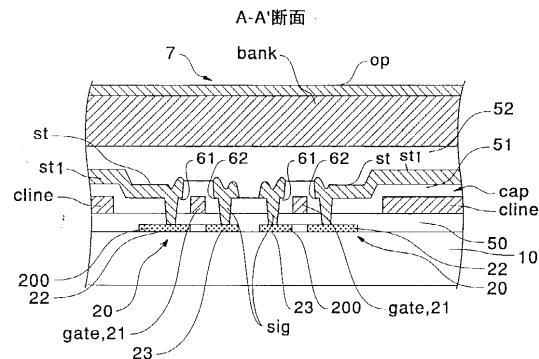

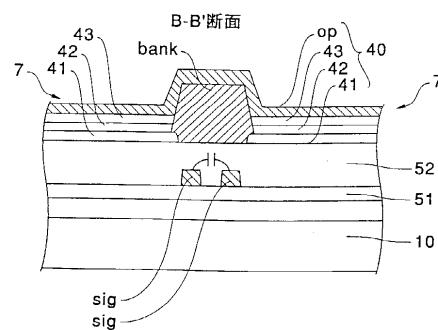

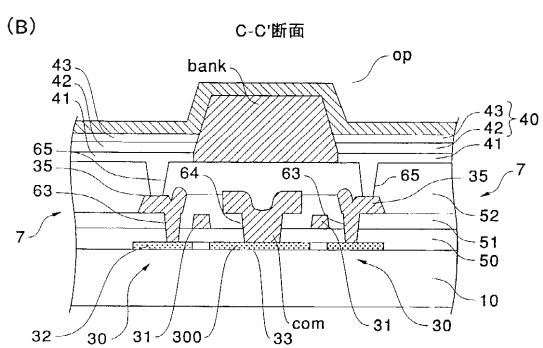

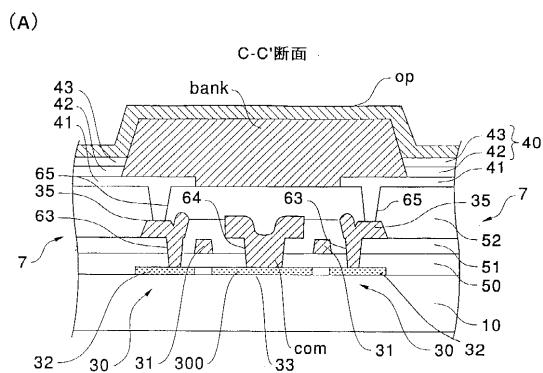

図3は、本形態の表示装置1に形成されている複数の画素領域7のうちの3つの画素領域7を拡大して示す平面図、図4、図5、および図6(A)はそれぞれ、そのA-A線における断面図、B-B線における断面図、およびC-C線における断面図である。

#### 【0028】

まず、図3におけるA-A線に相当する位置では、図4に示すように、透明基板10上には各画素領域7の各々に第1のTFT20を形成するための島状のシリコン膜200が形成され、その表面にはゲート絶縁膜50が形成されている。また、ゲート絶縁膜50の表面にはゲート電極21が形成され、該ゲート電極21に対して自己整合的に高濃度の不純物が導入されたソース・ドレイン領域22、23が形成されている。ゲート絶縁膜50の表面側には第1の層間絶縁膜51が形成され、この層間絶縁膜に形成されたコンタクトホール61、62を介して、ソース・ドレイン領域22、23にはデータ線sig、および電位保持電極stがそれぞれ電気的に接続されている。

#### 【0029】

各画素領域7には走査線gatetと並列するように、走査線gatetやゲート電極21と同一の層間（ゲート絶縁膜50と第1の層間絶縁膜51との間）には容量線cilineが形成されており、この容量線cilineに対しては、第1の層間絶縁膜51を介して電位保持電極stの延設部分st1が重なっている。このため、容量線cilineと電位保持電極stの延設部分st1とは、第1の層間絶縁膜51を誘電体膜とする保持容量capを構成している。なお、電位保持電極stおよびデータ線sigの表面側には第2の層間絶縁膜52が形成されている。

#### 【0030】

図3におけるB-B線に相当する位置では、図5に示すように、透明基板10上に形成された第1の層間絶縁膜51および第2の層間絶縁膜52の表面に各画素領域7に対応するデータ線sigが2本、並列している状態にある。

#### 【0031】

図3におけるC-C線に相当する位置では、図6(A)に示すように、透明基板10上には共通給電線comを挟む2つの画素領域7に跨るように、第2のTFT30を形成するための島状のシリコン膜300が形成され、その表面にはゲート絶縁膜50が形成さ

10

20

30

40

50

れている。また、ゲート絶縁膜 50 の表面には、共通給電線 c o m を挟むように、各画素領域 7 の各々にゲート電極 31 がそれぞれ形成され、このゲート電極 31 に対して自己整合的に高濃度の不純物が導入されたソース・ドレイン領域 32、33 が形成されている。ゲート絶縁膜 50 の表面側には第 1 の層間絶縁膜 51 が形成され、この層間絶縁膜に形成されたコンタクトホール 63 を介して、ソース・ドレイン領域 62 に中継電極 35 が電気的に接続されている。一方、シリコン膜 300 の中央の 2 つの画素領域 7 において共通のソース・ドレイン領域 33 となる部分に対しては、第 1 の層間絶縁膜 51 のコンタクトホール 64 を介して、共通給電線 c o m が電気的に接続されている。これらの共通給電線 c o m、および中継電極 35 の表面には第 2 の層間絶縁膜 52 が形成されている。第 2 の層間絶縁膜 52 の表面には I T O 膜からなる画素電極 41 が形成されている。この画素電極 41 は、第 2 の層間絶縁膜 52 に形成されたコンタクトホール 65 を介して中継電極 35 に電気的に接続され、また中継電極 35 を介して第 2 の T F T 30 のソース・ドレイン領域 32 に電気的に接続されている。

## 【 0 0 3 2 】

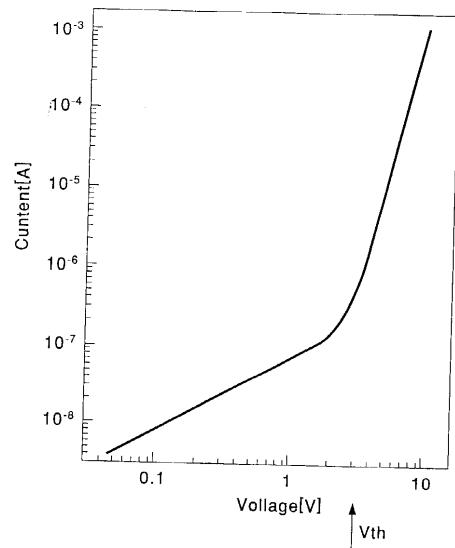

ここで、画素電極 41 は発光素子 40 の一方の電極を構成している。すなわち、画素電極 41 の表面には正孔注入層 42 および有機半導体膜 43 が積層され、さらに有機半導体膜 43 の表面には、リチウム含有アルミニウム、カルシウムなどの金属膜からなる対向電極 o p が形成されている。この対向電極 o p は、少なくとも画素領域 41 の全面、あるいはストライプ状に形成された共通の電極であって、一定の電位に保持されている。

## 【 0 0 3 3 】

このように構成された発光素子 40 では、対向電極 o p および画素電極 41 をそれぞれ正極および負極として電圧が印加され、図 7 に示すように、印加電圧がしきい値電圧を越えた領域で有機半導体膜 43 に流れる電流（駆動電流）が急激に増大する。その結果、発光素子 40 は、エレクトロルミネッセンス素子あるいは L E D 素子として発光し、発光素子 40 の光は、対向電極 o p に反射されて透明な画素電極 41 および透明基板 10 を透過して出射される。

## 【 0 0 3 4 】

このような発光を行うための駆動電流は、対向電極 o p 、有機半導体膜 43 、正孔注入層 42 、画素電極 41 、第 2 の T F T 30 、および共通給電線 c o m から構成される電流経路を流れるため、第 2 の T F T 30 がオフ状態になると、流れなくなる。但し、本形態の表示装置 1 では、走査信号によって選択されて第 1 の T F T 20 がオン状態になると、データ線 s i g から画像信号が第 1 の T F T 20 を介して保持容量 c a p に書き込まれる。従って、第 2 の T F T 30 のゲート電極は、第 1 の T F T 20 がオフ状態になつても、保持容量 c a p によって画像信号に相当する電位に保持されるので、第 2 の T F T 30 はオン状態のままである。それ故、発光素子 40 には駆動電流が流れ続け、この画素は点灯状態のままである。この状態は、新たな画像データが保持容量 c a p に書き込まれて、第 2 の T F T 30 がオフ状態になるまで維持される。

## 【 0 0 3 5 】

## (表示装置の製造方法)

このように構成した表示装置 1 の製造方法では、透明基板 10 上に第 1 の T F T 20 および第 2 の T F T 30 を製造するまでの工程は、液晶表示装置 1 のアクティブマトリクス基板を製造する工程と略同様であるため、図 8 を参照してその概要を説明する。

## 【 0 0 3 6 】

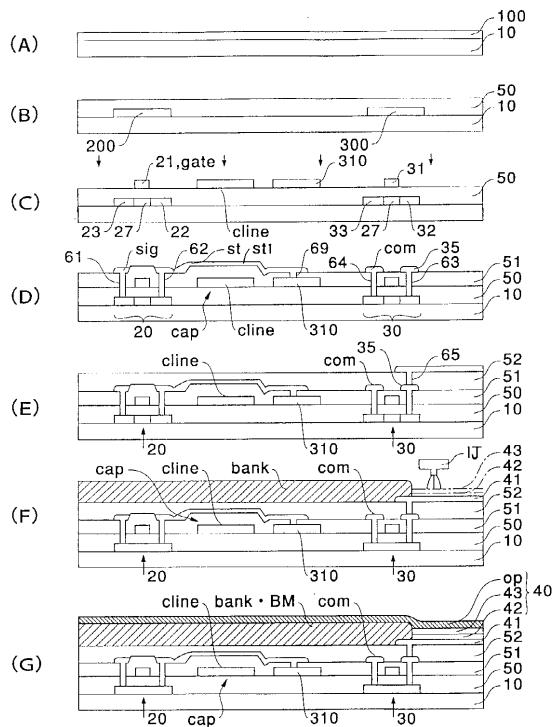

図 8 は、表示装置 1 の各構成部分を形成していく過程を模式的に示す工程断面図である。

## 【 0 0 3 7 】

すなわち、図 8 ( A ) に示すように、透明基板 10 に対して、必要に応じて、T E O S ( テトラエトキシシラン ) や酸素ガスなどを原料ガスとしてプラズマ C V D 法により厚さが約 2 0 0 0 ~ 5 0 0 0 オングストロームのシリコン酸化膜からなる下地保護膜 ( 図示せず。 ) を形成する。次に基板の温度を約 3 5 0 ℃ に設定して、下地保護膜の表面にプラズマ C V D 法により厚さが約 3 0 0 ~ 7 0 0 オングストロームのアモルファスのシリコン膜か

10

20

30

40

50

らなる半導体膜 100 を形成する。次にアモルファスのシリコン膜からなる半導体膜 100 に対して、レーザアニールまたは固相成長法などの結晶化工程を行い、半導体膜 100 をポリシリコン膜に結晶化する。レーザアニール法では、たとえば、エキシマレーザでビームの長寸が 400 mm のラインビームを用い、その出力強度はたとえば 200 mJ / cm<sup>2</sup> である。ラインビームについてはその短寸方向におけるレーザ強度のピーク値の 90 % に相当する部分が各領域毎に重なるようにラインビームを走査していく。

#### 【 0038 】

次に、図 8 (B) に示すように、半導体膜 100 をパターニングして島状の半導体膜 200 、 300 とし、その表面に対して、TEOS ( テトラエトキシシラン ) や酸素ガスなどを原料ガスとしてプラズマ CVD 法により厚さが約 600 ~ 1500 オングストロームのシリコン酸化膜または窒化膜からなるゲート絶縁膜 50 を形成する。

10

#### 【 0039 】

次に、図 8 (C) に示すように、アルミニウム、タンタル、モリブデン、チタン、タンゲステンなどの金属膜からなる導電膜をスパッタ法により形成した後、パターニングし、ゲート電極 21 、 31 を形成する ( ゲート電極形成工程 ) 。この工程では、走査線 gate および容量線 cline も形成する。なお、図中、 310 は、ゲート電極 31 の延設部分である。

#### 【 0040 】

この状態で、高濃度のリンイオンを打ち込んで、シリコン薄膜 200 、 300 にはゲート電極 21 、 31 に対して自己整合的にソース・ドレイン領域 22 、 23 、 32 、 33 を形成する。なお、不純物が導入されなかった部分がチャネル領域 27 、 37 となる。

20

#### 【 0041 】

次に、図 8 (D) に示すように、第 1 の層間絶縁膜 51 を形成した後、コンタクトホール 61 、 62 、 63 、 64 、 69 を形成し、データ線 sig 、容量線 cline およびゲート電極 31 の延設部分 310 に重なる延設部分 st1 を備える電位保持電極 st 、共通給電線 com 、および中継電極 35 を形成する。その結果、電位保持電極 st はコンタクトホール 69 および延設部分 310 を介してゲート電極 31 に電気的に接続する。このようにして第 1 の TFT20 および第 2 の TFT30 を形成する。また、容量線 cline と電位保持電極 st の延設部分 st1 とによって保持容量 cap が形成される。

#### 【 0042 】

30

次に、図 8 (E) に示すように、第 2 の層間絶縁膜 52 を形成し、この層間絶縁膜には、中継電極 35 に相当する部分にコンタクトホール 65 を形成する。次に、第 2 の層間絶縁膜 52 の表面全体に ITO 膜を形成した後、パターニングし、コンタクトホール 65 を介して第 2 の TFT30 のソース・ドレイン領域 32 に電気的に接続する画素電極 41 を形成する。

#### 【 0043 】

次に、図 8 (F) に示すように、第 2 の層間絶縁膜 52 の表面側に黒色のレジスト層を形成した後、このレジストを発光素子 40 の正孔注入層 42 および有機半導体膜 43 を形成して発光領域とすべき領域を囲むように残し、バンク層 bank を形成する。ここで、有機半導体膜 43 は、各画素毎に独立して、たとえば箱状に形成される場合、データ線 sig に沿ってストライプ状に形成される場合などのいずれの場合であっても、それに対応する形状にバンク層 bank を形成するだけで、本形態に係る製造方法を適用できる。

40

#### 【 0044 】

次に、バンク層 bank の内側領域に対してインクジェットヘッド IJ から、正孔注入層 42 を構成するための液状の材料 ( 前駆体 ) を吐出し、バンク層 bank の内側領域に正孔注入層 42 を形成する。同様に、バンク層 bank の内側領域に対してインクジェットヘッド IJ から、有機半導体膜 43 を構成するための液状の材料 ( 前駆体 ) を吐出し、バンク層 bank の内側領域に有機半導体膜 43 を形成する。ここで、バンク層 bank はレジストから構成されているため、撥水性である。これに対して、有機半導体膜 43 の前駆体は親水性の溶媒を用いているため、有機半導体膜 43 の塗布領域はバンク層 bank

50

によって確実に規定され、隣接する画素にはみ出ることがない。それ故、有機半導体膜43などを所定領域内だけに形成できる。但し、予めバンク層bankからなる隔壁が1μmほどの高さであれば、バンク層bankが撥水性でなくても、バンク層bankは隔壁として十分に機能する。なお、バンク層bankを形成しておけば、インクジェット法に代えて、塗布法で正孔注入層42や有機半導体膜43を形成する場合でもその形成領域を規定できる。

#### 【0045】

このように、有機半導体膜43や正孔注入層42をインクジェット法により形成する場合には、その作業効率を高めるために、本形態では、図3に示すように、走査線gateの延設方向に沿って隣接するいずれの画素領域7間でも、前記有機半導体膜43の形成領域の中心のピッチPを等しくしてある。従って、矢印Qで示すように、走査線gateの延設方向に沿って等間隔の位置にインクジェットヘッドIJから有機半導体膜43の材料などを吐出すればよいので、作業効率がよいという利点がある。また、インクジェットヘッドIJが等ピッチの移動で良いということにより、インクジェットヘッドIJの移動機構が簡易になり、かつ、インクジェットヘッドIJの打ち込み精度を高めるのも容易になる。

10

#### 【0046】

かかる後には、図8(G)に示すように、透明基板10の表面全体に対して、あるいはストライプ状に対向電極opを形成する。なお、バンク層bankについては、それが黒色のレジストから構成されているので、そのまま残し、以下に説明するように、ブラックマトリクスBM、および寄生容量を低減するための絶縁層として利用する。

20

#### 【0047】

なお、図1に示すデータ側駆動回路3や走査側駆動回路4にもTFTが形成されるが、これらのTFTは前記の画素領域7にTFTを形成していく工程の全部あるいは一部を援用して行われる。それ故、駆動回路を構成するTFTも、画素領域7のTFTと同一の層間に形成されることになる。

#### 【0048】

また、前記第1のTFT20、および第2のTFT30については、双方がN型、双方がP型、一方がN型で他方がP型のいずれでもよいが、このようないずれの組合せであっても周知の方法でTFTを形成していくので、その説明を省略する。

30

#### 【0049】

なお、発光素子40としては、発光効率(正孔注入率)がやや低下するものの、正孔注入層42を省くこともある。また、正孔注入層42に代えて電子注入層を有機半導体膜43に対して正孔注入層42とは反対側に形成する場合、正孔注入層42および電子注入層の双方を形成する場合がある。

#### 【0050】

##### (バンク層の形成領域)

本形態では、図1に示す透明基板10の周辺領域の総てに対して、前記のバンク層bank(形成領域に斜線を付してある。)を形成する。従って、データ側駆動回路3および走査側駆動回路4はいずれも、バンク層bankによって覆われている。このため、これらの駆動回路の形成領域に対して対向電極opが重なる状態にあっても、駆動回路の配線層と対向電極opとの間にバンク層bankが介在することになる。それ故、駆動回路3、4に容量が寄生することを防止できるため、駆動回路3、4の負荷を低減でき、低消費電力化あるいは表示動作の高速化を図ることができる。

40

#### 【0051】

また、本形態では、図3ないし図5に示すように、データ線sigに重なるようにバンク層bankを形成してある。従って、データ線sigと対向電極opとの間にバンク層bankが介在することになるので、データ線sigに容量が寄生することを防止できる。その結果、データ側駆動回路3の負荷を低減できるので、低消費電力化あるいは表示動作の高速化を図ることができる。

50

## 【0052】

さらに、本形態では、図3、図4、および図6(A)に示すように、画素電極41の形成領域のうち、中継電極35と重なる領域にもバンク層bankが形成されている。図6(B)に示すように、例えば、中継電極35と重なる領域にバンク層bankがないと、対向電極opとの間に駆動電流が流れ、有機半導体膜43が発光しても、この光は中継電極35と対向電極opとの間に挟まれて外に出射されず、表示に寄与しない。かかる表示に寄与しない部分で流れる駆動電流は、表示という面からみて無効電流といえる。しかるに本形態では、従来ならこのような無効電流が流れるはずの部分にバンク層bankを形成し、そこに駆動電流が流れることを防止するので、共通給電線comに無駄な電流が流れることが防止できる。それ故、共通給電線comの幅はその分、狭くてよい。

10

## 【0053】

たとえば、本形態では、共通給電線comには、データ線sigと違って、発光素子40を駆動するための大きな電流が流れ、しかも、2列分の画素に対して駆動電流を供給する。それ故、共通給電線comについては、データ線sigと同一の材料から構成されているが、その線幅をデータ線sigの線幅よりも広く設定してあるため、共通給電線comの単位長さ当たりの抵抗値は、データ線sigの単位長さ当たりの抵抗値よりも小さい。それでも、本形態では、共通給電線comに前記の無効電流が流れることを抑えることによって、共通給電線comの線幅については必要最小限の線幅としてあるので、画素領域7の発光面積を増すことができ、輝度、コントラスト比などの表示性能を向上させることができる。

20

## 【0054】

また、前記のようにバンク層bankを形成しておくと、バンク層bankはブラックマトリクスとして機能し、コントラスト比などの表示の品位が向上する。すなわち、本形態に係る表示装置1では、対向電極opが透明基板10の表面側において画素領域7の全面、あるいは広い領域にわたってストライプ状に形成されるため、対向電極opでの反射光がコントラスト比を低下させる。しかるに本形態では、寄生容量を防止するための機能も担うバンク層bankを黒色のレジストで構成したため、バンク層bankはブラックマトリクスとしても機能し、対向電極opからの反射光を遮るので、コントラスト比が向上する。

## 【0055】

30

## [上記形態の改良例]

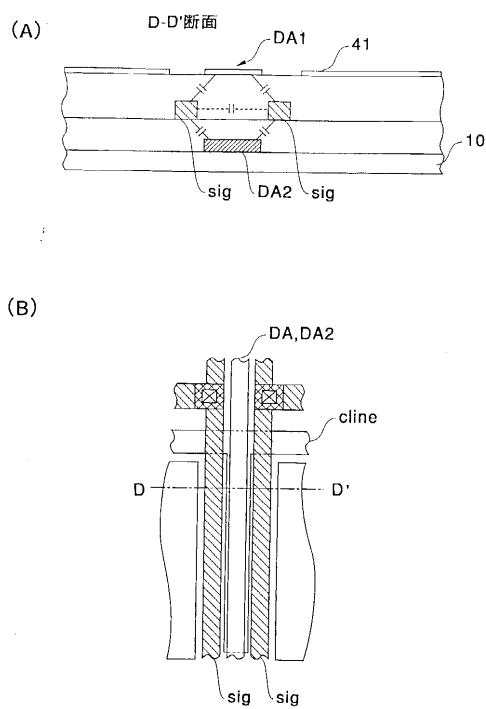

上記形態では、共通給電線comの両側のそれぞれに、該共通給電線comとの間で駆動電流が流れる画素領域7が配置され、該画素領域7に対して前記共通給電線comとは反対側を2本のデータ線sigが並列して通っている。従って、2本のデータ線sigの間でクロストークが発生するおそれがある。そこで、本形態では、図9、図10(A)、(B)に示すように、2本のデータ線sigの間に相当する位置には、ダミーの配線層DAを形成してある。このダミーの配線層DAとしては、たとえば、画素電極41と同時形成されたITO膜DA1を利用することができる。また、ダミーの配線層DAとしては、2本のデータ線sigの間に容量線cilineからの延設部分DA2を構成してもよい。これらの双方をダミーの配線層DAとして用いてもよい。

40

## 【0056】

このように構成すると、並列する2本のデータ線sigの間にはそれらとは別の配線層DAが通っているので、このような配線層DA(DA1、DA2)を少なくとも画像の1水平走査期間内で固定電位としておくだけで、上記のクロストークを防止できる。すなわち、第1の層間絶縁膜51および第2の層間絶縁膜52は、膜厚が凡そ $1.0\mu m$ であるのに対して、2本のデータ線sig2本の間隔は約 $2\mu m$ 以上であるため、各データ線sigとダミーの配線層DA(DA1、DA2)との間に構成される容量に比して、2本のデータ線sigの間に構成される容量は十分に無視できる。それ故、データ線sigから漏れた高周波数の信号はダミーの配線層DAで吸収されるので、2本のデータ線sigの間でのクロストークを防止できる。

50

**【0057】****[その他の形態]**

なお、上記形態では、保持容量 c a p を構成するのに容量線 c l i n e (容量電極)を形成したが、従来技術で説明したように、TFTを構成するためのポリシリコン膜を利用して保持容量 c a p を構成してもよい。

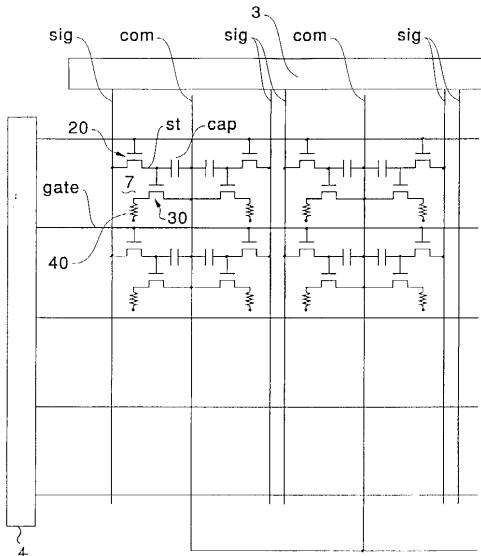

**【0058】**

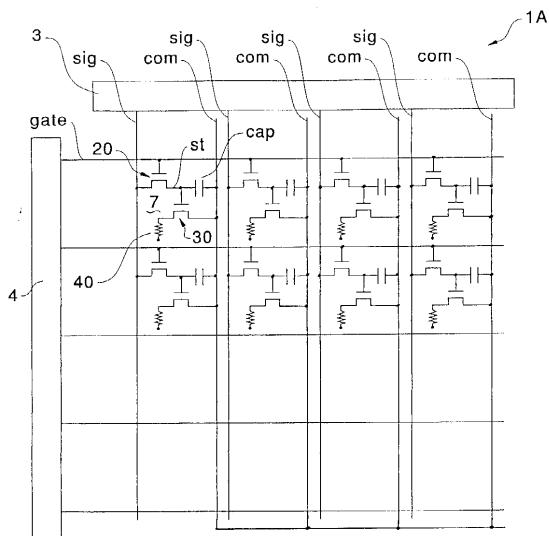

また、図11に示すように、共通給電線 c o m と電位保持電極 s t との間に保持容量 c a p を構成してもよい。この場合には、図12(A)、(B)に示すように、電位保持電極 s t とゲート電極 31 とを電気的に接続させるためのゲート電極 31 の延設部分 310 を共通給電線 c o m の下層側にまで拡張し、この延設部分 310 と共に共通給電線 c o m との間の位置する第1の層間絶縁膜 51 を誘電体膜とする保持容量 c a p を構成すればよい。

10

**【0059】****【発明の効果】**

以上説明したように、本発明に係る表示装置では、発光素子を構成する有機半導体膜の形成領域を規定する絶縁性のバンク層をデータ線と対向電極との間、または駆動回路と対向電極との間に介在させることに特徴を有する。従って、データ線や駆動回路に重なるように対向電極を形成しても、データ線や駆動回路の配線層に容量が寄生することを防止できる。それ故、駆動回路の負荷を低減できるとともに、画像信号の高周波数化を図ることができる。

**【図面の簡単な説明】**

20

**【図1】**本発明を適用した表示装置、およびそれに形成したバンク層の形成領域を模式的に示す説明図である。

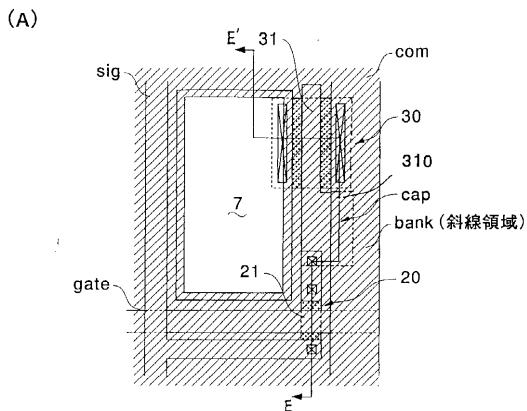

**【図2】**本発明を適用した表示装置のブロック図である。

**【図3】**本発明を適用した表示装置の画素領域を拡大して示す平面図である。

**【図4】**図3のA-A 線における断面図である。

**【図5】**図3のB-B 線における断面図である。

**【図6】**(A)は図3のC-C 線における断面図、(B)はバンク層の形成領域を中継電極を覆うまで拡張しない構造の断面図である。

**【図7】**図1に示す表示装置に用いた発光素子のI-V特性を示すグラフである。

**【図8】**本発明を適用した表示装置の製造方法を示す工程断面図である。

30

**【図9】**図1に示す表示装置の改良例を示すブロック図である。

**【図10】**(A)は、図9に示す表示装置に形成したダミーの配線層を示す断面図、(B)はその平面図である。

**【図11】**図1に示す表示装置の変形例を示すブロック図である。

**【図12】**(A)は、図11に示す表示装置に形成した画素領域を拡大して示す平面図、(B)はその断面図である。

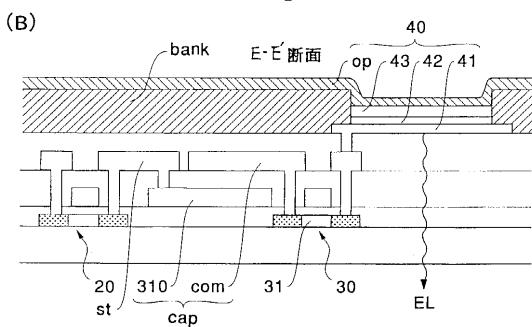

**【図13】**従来の表示装置のブロック図である。

**【図14】**(A)は、図13に示す表示装置に形成した画素領域を拡大して示す平面図、(B)はその断面図である。

**【符号の説明】**

40

- |    |                   |

|----|-------------------|

| 1  | 表示装置              |

| 2  | 表示部               |

| 3  | データ側駆動回路(第1の駆動回路) |

| 4  | 走査側駆動回路(第2の駆動回路)  |

| 5  | 検査回路              |

| 6  | 実装用パッド            |

| 7  | 画素領域              |

| 10 | 透明基板              |

| 20 | 第1のTFT            |

| 21 | 第1のTFTのゲート電極      |

50

|           |                   |    |

|-----------|-------------------|----|

| 3 0       | 第 2 の TFT         |    |

| 3 1       | 第 2 の TFT の ゲート電極 |    |

| 4 0       | 発光素子              |    |

| 4 1       | 膜画素電極             |    |

| 4 2       | 正孔注入層             |    |

| 4 3       | 有機半導体膜            |    |

| 5 0       | ゲート絶縁膜            |    |

| 5 1       | 第 1 の層間絶縁膜        |    |

| 5 2       | 第 2 の層間絶縁膜        |    |

| D A       | ダミーの配線層           | 10 |

| b a n k   | バンク層              |    |

| c a p     | 保持容量              |    |

| c l i n e | 容量線               |    |

| c o m     | 共通給電線             |    |

| g a t e   | 走査線               |    |

| o p       | 対向電極              |    |

| s i g     | データ線              |    |

| s t       | 電位保持電極            |    |

【図 1】

【図 2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

---

フロントページの続き

(58)調査した分野(Int.Cl.<sup>7</sup>, DB名)

G09F 9/30

H05B 33/26