(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第4554900号

(P4554900)

(45) 発行日 平成22年9月29日(2010.9.29)

(24) 登録日 平成22年7月23日(2010.7.23)

|              |                                     |

|--------------|-------------------------------------|

| (51) Int.Cl. | F 1                                 |

| G06F 12/06   | (2006.01)      G06F 12/06      520F |

| G06F 12/00   | (2006.01)      G06F 12/00      597U |

| G06F 13/16   | (2006.01)      G06F 13/16      520C |

| G06F 12/16   | (2006.01)      G06F 12/16      320F |

| G06F 11/10   | (2006.01)      G06F 11/10      320F |

請求項の数 18 (全 18 頁)

|              |                              |

|--------------|------------------------------|

| (21) 出願番号    | 特願2003-281302 (P2003-281302) |

| (22) 出願日     | 平成15年7月28日 (2003.7.28)       |

| (65) 公開番号    | 特開2004-62913 (P2004-62913A)  |

| (43) 公開日     | 平成16年2月26日 (2004.2.26)       |

| 審査請求日        | 平成18年7月14日 (2006.7.14)       |

| (31) 優先権主張番号 | 2002-044638                  |

| (32) 優先日     | 平成14年7月29日 (2002.7.29)       |

| (33) 優先権主張国  | 韓国 (KR)                      |

|           |                                                                                                                                                               |

|-----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------|

| (73) 特許権者 | 390019839<br>三星電子株式会社<br>SAMSUNG ELECTRONICS<br>CO., LTD.<br>大韓民国京畿道水原市靈通区梅灘洞 416<br>416, Maetan-dong, Yeongtong-gu, Suwon-si,<br>Gyeonggi-do 442-742<br>(KR) |

| (74) 代理人  | 100086368<br>弁理士 萩原 誠                                                                                                                                         |

| (72) 発明者  | 季 錫 慎<br>大韓民国京畿道水原市八達区梅灘洞 梅灘<br>住公アパート 516-206                                                                                                                |

最終頁に続く

(54) 【発明の名称】 N A N D フラッシュメモリをシステム駆動用及びデータ貯蔵用として使用する装置

## (57) 【特許請求の範囲】

## 【請求項 1】

コンピュータシステムにおいて、

中央処理装置とメモリバスコントローラとを含み、第1インターフェース方式で動作する

システムコントローラと、

システムバスを通じて前記システムコントローラと連結されたシステムメモリと、

前記コンピュータシステムのためのシステム駆動コード及びオペレーティングシステム

プログラムと使用者データを貯蔵するN A N D フラッシュメモリと、

前記システムコントローラとは前記システムバスを通じて前記第1インターフェース方式

で通信し、前記N A N D フラッシュメモリとは第2インターフェース方式で通信し、所定の

命令情報に応答して内部で発生したクロック信号に同期して動作するインターフェース装置

とを具備することを特徴とするコンピュータシステム。

## 【請求項 2】

前記インターフェース装置は、

前記システムバスを通じて前記システムコントローラと前記第1インターフェース方式で

通信するホストインターフェースユニットと、

前記コンピュータシステム及び前記N A N D フラッシュメモリに関する編成情報と前記

N A N D フラッシュメモリに関する前記命令情報を貯蔵するレジスタユニットと、

前記N A N D フラッシュメモリのデータを貯蔵するバッファユニットと、

前記命令情報に応答して前記クロック信号を発生するオシレータと、

10

20

前記クロック信号に同期して、前記命令情報に応答して前記インターフェース装置の内部動作を制御する状態制御ユニットと、

前記クロック信号に同期して、前記状態制御ユニットにより前記NANDフラッシュメモリと前記第2インターフェース方式で通信するNANDフラッシュインターフェースユニットとを具備することを特徴とする請求項1に記載のコンピュータシステム。

**【請求項3】**

前記インターフェース装置は、電源が印加された時に、電源感知信号を前記状態制御ユニットに印加するパワーアップ感知回路をさらに具備することを特徴とする請求項2に記載のコンピュータシステム。

**【請求項4】**

前記インターフェース装置は、前記クロック信号に同期して前記NANDフラッシュメモリのデータに対するエラー検査及び訂正を行うエラー訂正回路をさらに具備することを特徴とする請求項2または3に記載のコンピュータシステム。

**【請求項5】**

前記状態制御ユニットは、

前記バッファユニットに貯蔵されたデータと予め決められたエラー訂正パリティビットを前記NANDフラッシュメモリにプログラムする動作を制御する第1ブロックと、

前記NANDフラッシュメモリから読み出されたデータを前記バッファユニットに貯蔵する動作を制御する第2ブロックと、

前記NANDフラッシュメモリに貯蔵された前記システム駆動コードを利用して前記コンピュータシステムを駆動する動作を制御する第3ブロックと、

前記NANDフラッシュメモリの前記プログラム動作中に前記エラー訂正パリティビットを発生する動作を制御し、前記NANDフラッシュメモリの読み出し動作中に前記NANDフラッシュメモリに貯蔵された前記パリティビットと新しいパリティビットを比べてエラー訂正する動作を制御する第4ブロックとを具備することを特徴とする請求項4に記載のコンピュータシステム。

**【請求項6】**

前記状態制御ユニットは、

前記NANDフラッシュメモリに貯蔵されたデータを消去する動作を制御する第5ブロックと、

前記NANDフラッシュメモリに印加されるリセット命令と前記インターフェース装置内のレジスタのリセットを制御する第6ブロックとをさらに具備することを特徴とする請求項5に記載のコンピュータシステム。

**【請求項7】**

前記インターフェース装置は、

前記システムバスを通じて前記システムコントローラと前記第1インターフェース方式で通信する第1インターフェースユニットと、

前記クロック信号に同期して前記NANDフラッシュメモリと前記第2インターフェース方式で通信する第2インターフェースユニットと、

前記第1及び第2インターフェースユニット間に交換される情報及びデータを貯蔵する貯蔵ユニットと、

前記クロック信号に同期して前記第1及び第2インターフェースユニット間の前記情報及びデータの伝送を統制する制御ユニットとを具備することを特徴とする請求項1に記載のコンピュータシステム。

**【請求項8】**

前記貯蔵ユニットは、

前記コンピュータシステム及び前記NANDフラッシュメモリに関する編成情報と前記NANDフラッシュメモリに関する前記命令情報を貯蔵するレジスタユニットと、

前記NANDフラッシュメモリのデータを貯蔵するバッファユニットとを具備することを特徴とする請求項7に記載のコンピュータシステム。

10

20

30

40

50

**【請求項 9】**

前記インターフェース装置は電源が印加された時に、電源感知信号を前記状態制御ユニットに印加するパワーアップ感知回路をさらに具備することを特徴とする請求項 7 に記載のコンピュータシステム。

**【請求項 10】**

前記インターフェース装置は前記クロック信号に同期して前記NANDフラッシュメモリのデータに対するエラー検査及び訂正を行うエラー訂正回路をさらに具備することを特徴とする請求項 7 または 9 に記載のコンピュータシステム。

**【請求項 11】**

前記制御ユニットは、

10

前記バッファユニットに貯蔵されたデータと予め決められたエラー訂正パリティビットを前記NANDフラッシュメモリにプログラムする動作を制御する第1ブロックと、

前記NANDフラッシュメモリから読み出されたデータを前記バッファユニットに貯蔵する動作を制御する第2ブロックと、

前記NANDフラッシュメモリに貯蔵された前記システム駆動コードを利用して前記コンピュータシステムを駆動する動作を制御する第3ブロックと、

前記NANDフラッシュメモリの前記プログラム動作中に前記エラー訂正パリティビットを発生する動作を制御し、前記NANDフラッシュメモリの読み出し動作中に前記NANDフラッシュメモリに貯蔵された前記パリティビットと新しいパリティビットを比べてエラー訂正する動作を制御する第4ブロックとを具備することを特徴とする請求項 7 に記載のコンピュータシステム。

20

**【請求項 12】**

前記制御ユニットは、

前記NANDフラッシュメモリに貯蔵されたデータを消去する動作を制御する第5ブロックと、

前記NANDフラッシュメモリに印加されるリセット命令と前記インターフェース装置内のレジスタのリセットを制御する第6ブロックとをさらに具備することを特徴とする請求項 11 に記載のコンピュータシステム。

**【請求項 13】**

中央処理装置とメモリバスコントローラとを含み、第1インターフェース方式で動作するシステムコントローラと、システムバスを通じて前記システムコントローラと連結されたシステムメモリと、システム駆動コード及びオペレーティングシステムプログラムと使用者データを貯蔵するNANDフラッシュメモリと、前記システムコントローラとは前記システムバスを通じて前記第1インターフェース方式で通信し、前記NANDフラッシュメモリとは第2インターフェース方式で通信し、所定の命令情報に応答して内部で発生したクロック信号に同期して動作するインターフェース装置とを備えたコンピュータシステムを駆動する方法において、

30

電源印加感知状態に応答して前記NANDフラッシュメモリから前記システム駆動コードを前記インターフェース装置内の所定のバッファにコピーする第1段階と、

前記バッファに貯蔵された前記システム駆動コードに従って、前記コンピュータシステムを初期化し、前記NANDフラッシュメモリから前記オペレーティングシステムプログラムを前記システムメモリにコピーする第2段階と、

40

前記オペレーティングシステムプログラムを実行する第3段階とを具備することを特徴とする方法。

**【請求項 14】**

中央処理装置とメモリバスコントローラとを含み、第1インターフェース方式で動作するシステムコントローラと、システムバスを通じて前記システムコントローラと連結されたシステムメモリと、システム駆動コード及びオペレーティングシステムプログラムと使用者データを貯蔵するNANDフラッシュメモリと、前記システムコントローラとは前記システムバスを通じて前記第1インターフェース方式で通信し、前記NANDフラッシュメモリとは第2インターフェース方式で通信し、所定の命令情報に応答して内部で発生したクロック信号に同期して動作するインターフェース装置とを備えたコンピュータシステムを駆動する方法において、

50

リとは第2インターフェース方式で通信し、所定の命令情報に応答して内部で発生したクロック信号に同期して動作するインターフェース装置とを備えたコンピュータシステムで前記NANDフラッシュメモリからデータを読み出す方法において、

前記NANDフラッシュメモリに対する命令及びアドレスと読み出されるページを設定する第1段階と、

前記ページのうち一番目のページのデータを前記インターフェース装置内の所定のバッファにコピーする第2段階と、

前記一番目のページのデータを前記バッファから前記システムコントローラに伝送する間に、前記ページのうち二番目のページのデータを前記NANDフラッシュメモリから前記バッファにコピーする第3段階とを具備することを特徴とする方法。 10

#### 【請求項15】

前記設定されたページに対するデータコピーが全部完了するまでn-1番目のページのデータを伝送する間、n番目のページのデータを前記バッファから前記NANDフラッシュメモリにコピーする段階をさらに含むことを特徴とする請求項14に記載の方法。

#### 【請求項16】

前記システムコントローラに前記設定されたページのデータが連続して送信されることを特徴とする請求項14に記載の方法。

#### 【請求項17】

中央処理装置とメモリバスコントローラとを含み、第1インターフェース方式で動作するシステムコントローラと、システムバスを通じて前記システムコントローラと連結されたシステムメモリと、システム駆動コード及びオペレーティングシステムプログラムと使用者データを貯蔵するNANDフラッシュメモリと、前記システムコントローラとは前記システムバスを通じて前記第1インターフェース方式で通信し、前記NANDフラッシュメモリとは第2インターフェース方式で通信し、所定の命令情報に応答して内部で発生したクロック信号に同期して動作するインターフェース装置とを備えたコンピュータシステムで、 20

前記NANDフラッシュメモリにデータをプログラムする方法において、

前記NANDフラッシュメモリに対する命令及びアドレスとプログラムされるページを設定する第1段階と、

前記システムコントローラから前記インターフェース装置内の所定のバッファに前記プログラムされるページに必要なデータを連続してローディングする第2段階と、 30

前記バッファにローディングされたデータを利用して前記ページに対するプログラムを順次に実行する第3段階とを具備することを特徴とする方法。

#### 【請求項18】

前記ページのうち一ページに対するデータが前記バッファにローディングされる間に、他の一つのページに対するプログラムが実行されることを特徴とする請求項17に記載の方法。

#### 【発明の詳細な説明】

##### 【技術分野】

##### 【0001】

本発明はNANDフラッシュメモリをシステム駆動用及びデータ貯蔵用として使用するシステムに関するものである。 40

##### 【背景技術】

##### 【0002】

##### 【特許文献1】米国特許登録番号5,535,357

##### 【0003】

通常の個人情報端末機(PDA)、移動電話機(mobile phone)または衛星チャンネル装置(set top box)などのシステムでは、システム駆動用メモリとしてROMまたはNORフラッシュメモリを主に使用し、データ貯蔵メモリとしてNORフラッシュメモリを多く使用してきた。フラッシュメモリは電気的にデータの書き込みと除去が可能であり、再充電が不要な不揮発性を有するので、データ貯蔵用として適し 50

、特に、NORフラッシュメモリは高速インターフェースではないシステムで駆動及び貯蔵用として多く使用されている。

#### 【0004】

しかし、最近はシステム市場の成長と共にシステムでのサービスの多様化、高機能化、大容量化によって高速アクセスと大容量の支援は勿論、比較的安価なメモリが要求されているが、NORフラッシュメモリでは、そのような要求を満足させるのに限界がある。現在、そのような要求を満足させることができるものとしては、RAMがあるが、DRAMは揮発性メモリで、データ貯蔵用には適しない。

#### 【0005】

一方、NANDフラッシュメモリはメモリ構造上、大容量の実現が容易であり、NORフラッシュメモリに比べて安価に製造することができるので、大容量メモリとして、多く使用されている。また、NANDフラッシュメモリはNORフラッシュメモリに比べて製作が容易であり、集積度が高いので、システムの駆動メモリとして使用が提案されたことがある。特許文献1には、システム駆動用として用いられるフラッシュメモリの一例が開示されている。10

#### 【0006】

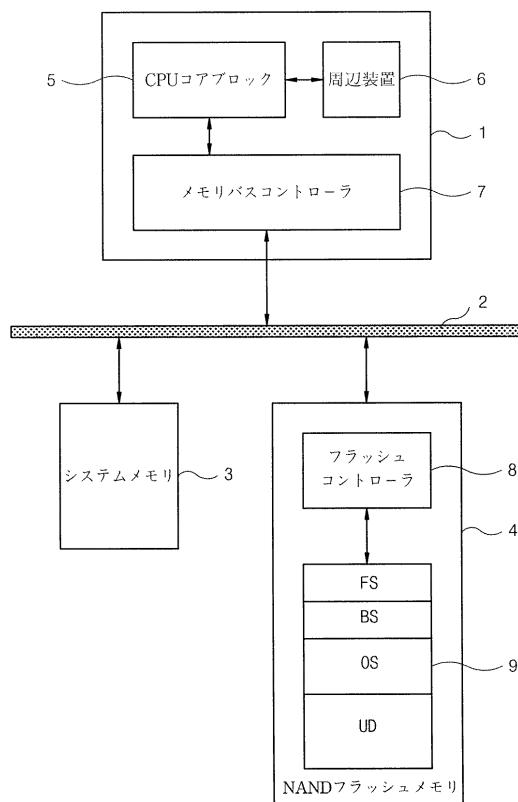

図1は従来のコンピュータシステムの構成を示すブロック図である。この図1を参照すれば、NANDフラッシュメモリをシステム駆動用として使用するために、フラッシュコントローラ8がNANDフラッシュメモリ9とシステムバス2との間のインターフェースを実行する。ここで、NANDフラッシュメモリ9は別途のエミュレーション(emulation)手段を貯蔵しなければならない。エミュレーション手段とは、NANDフラッシュメモリの一部領域をハードディスクとして使用するための手段を言う。フラッシュコントローラ8はバイオス(BIOS)駆動プロセスをインタセットし、システムメモリ3にエミュレーション手段を設置する。20

#### 【0007】

図1の構成でシステム駆動は次の通りである。先ず、NANDフラッシュメモリ4のファイルシステム領域FS(ブロック0に位置する)にバイオス領域BS(ブロック1に位置する)のためのジャンプアドレス(jump address)を貯蔵する。フラッシュコントローラ8内にあるメモリマッピング(mapping)用回路(またはウィンドウ回路)を利用してバイオス領域BSへのメモリマッピングを実行し、これを通じてオペレーティングシステム(operationing system)領域OSをシステムメモリ3に移すことによってシステム駆動を行う。30

#### 【発明の開示】

##### 【発明が解決しようとする課題】

#### 【0008】

しかし、このような従来の方式でNANDフラッシュメモリをシステム駆動用メモリとして使用するためには、図1に示したように、NANDフラッシュメモリ4をファイルシステム領域FS、バイオス領域BS、オペレーティングシステム領域OS及び使用者データ領域UDに区分しなければならない。また、NANDフラッシュメモリ4は、該NANDフラッシュメモリ4をハードディスクとして認識できるようにするエミュレーション手段を持っていなければならない。これと同時に、フラッシュコントローラ8は、バイオス駆動プロセスをインタセプトするための機能とバイオス領域BSにアドレスマッピングをする手段を有しなければならない。40

#### 【0009】

したがって、従来の方式では、NANDフラッシュメモリ及びフラッシュコントローラに対する準備とそれによる動作段階が複雑なので、一般的なコンピュータシステムに適用しづらい短所がある。

#### 【0010】

したがって、本発明の目的は、一般的なコンピュータシステムでNANDフラッシュメモリをシステム駆動用及びデータ貯蔵用としてより容易に使用できる装置を提供すること50

にある。

【0011】

また、本発明の目的は、NANDフラッシュメモリをシステム駆動用及びデータ貯蔵用として使用するコンピュータシステムでより容易に、効率的にインターフェース機能を実行することができる装置を提供することにある。

【0012】

また、本発明の目的は、NANDフラッシュメモリをシステム駆動用及びデータ貯蔵用として使用するコンピュータシステムでNANDフラッシュメモリに対する読み出し及びプログラム動作を実行するインターフェース装置を提供することにある。

【課題を解決するための手段】

10

【0013】

本発明によるコンピュータシステムは、中央処理装置とメモリバスコントローラを含み、第1インターフェース方式で動作するシステムコントローラと、システムバスを通じて前記システムコントローラと連結されたシステムメモリと、前記コンピュータシステムのためのシステム駆動コード及びオペレーティングシステムプログラムと使用者データを貯蔵するNANDフラッシュメモリと、前記システムコントローラとは前記システムバスを通じて前記第1インターフェース方式で通信し、前記NANDフラッシュメモリとは第2インターフェース方式で通信し、所定の命令情報に応答して内部で発生したクロック信号に同期して動作するインターフェース装置とを具備する。

【0014】

20

前記インターフェース装置は、前記システムバスを通じて前記システムコントローラと前記第1インターフェース方式で通信するホストインターフェースユニットと、前記コンピュータシステム及び前記NANDフラッシュメモリに関する編成情報と前記NANDフラッシュメモリに関する前記命令情報を貯蔵するレジスタユニットと、前記NANDフラッシュメモリのデータを貯蔵するバッファユニットと、前記命令情報に応答して前記クロック信号を発生するオシレータと、前記クロック信号に同期し、前記命令情報に応答して前記インターフェース装置の内部動作を制御する状態制御ユニットと、前記クロック信号に同期し、前記状態制御ユニットによって前記NANDフラッシュメモリと前記第2インターフェース方式で通信するNANDフラッシュインターフェースユニットとを有する。

【0015】

30

前記インターフェース装置には電源が印加された時に、電源感知信号を前記状態制御ユニットに印加するパワーアップ感知回路と、前記クロック信号に同期して前記NANDフラッシュメモリのデータに対するエラー検査及び訂正を行うエラー訂正回路とが前記インターフェース装置の内部または外部にさらに具備される。

【0016】

前記状態制御ユニットは、前記バッファユニットに貯蔵されたデータと予め決められたエラー訂正パリティビットを前記NANDフラッシュメモリにプログラムする動作を制御する第1ブロックと、前記NANDフラッシュメモリから読み出されたデータを前記バッファユニットに貯蔵する動作を制御する第2ブロックと、前記NANDフラッシュメモリに貯蔵された前記システム駆動コードを利用して前記コンピュータシステムを駆動する動作を制御する第3ブロックと、前記NANDフラッシュメモリの前記プログラム動作中に、前記エラー訂正パリティビットを発生する動作を制御し、前記NANDフラッシュメモリの読み出し動作中に、前記NANDフラッシュメモリに貯蔵された前記パリティビットと新しいパリティビットを比べて、エラー訂正する動作を制御する第4ブロックと、前記NANDフラッシュメモリに貯蔵されたデータを消去する動作を制御する第5ブロックと、前記NANDフラッシュメモリに印加されるリセット命令と前記インターフェース装置内のレジスタのリセットを制御する第6ブロックからなる。

40

【0017】

本発明の他の側面によると、前記インターフェース装置は、前記システムバスを通じて前記システムコントローラと前記第1インターフェース方式で通信する第1インターフェースユ

50

ニットと、前記クロック信号に同期して前記NANDフラッシュメモリと前記第2インターフェース方式で通信する第2インターフェースユニットと、前記第1及び第2インターフェースユニット間に交換される情報及びデータを貯蔵する貯蔵ユニットと、前記クロック信号に同期して前記第1及び第2インターフェースユニット間の前記情報及びデータの伝送を統制する制御ユニットとを具備する。前記貯蔵ユニットは、前記コンピュータシステム及び前記NANDフラッシュメモリに関する編成情報と前記NANDフラッシュメモリに関する前記命令情報を貯蔵するレジスタユニットと、前記NANDフラッシュメモリのデータを貯蔵するバッファユニットとに区分される。

#### 【0018】

一方、NANDフラッシュメモリを有するコンピュータシステムを駆動する方法においては、電源印加感知状態に応答して前記NANDフラッシュメモリからシステム駆動コードを所定のバッファにコピーする第1段階と、前記バッファに貯蔵された前記システム駆動コードによって、前記コンピュータシステムを初期化し、前記NANDフラッシュメモリからオペレーティングシステムコードを所定のプログラマブルメモリにコピーする第2段階と、前記オペレーティングシステムコードを実行する第3段階とを具備する。

#### 【0019】

また、本発明のシステムではコントローラがNANDフラッシュメモリからデータを読み出し、またはNANDフラッシュメモリにデータをプログラムする時に、NANDフラッシュメモリを高性能で読み出し、またはプログラムする装置及び方法が提示される。

#### 【0020】

システムコントローラ及びバッファとNANDフラッシュメモリを有するコンピュータシステムで前記NANDフラッシュメモリからデータを読み出す方法においては、前記NANDフラッシュメモリに対する命令及びアドレスと読み出されるページを設定する第1段階と、前記ページのうち一番目のページのデータを前記バッファにコピーする第2段階と、前記一番目のページのデータを前記バッファから前記システムコントローラに伝送する間に、前記ページのうち二番目のページのデータを前記NANDフラッシュメモリから前記バッファにコピーする第3段階とを具備する。前記設定されたページに対するデータコピーが全部完了するまで前記第3段階が繰り返される。前記システムコントローラに前記設定されたページのデータが連続して伝送される。

#### 【0021】

システムコントローラ及びバッファとNANDフラッシュメモリを有するコンピュータシステムで前記NANDフラッシュメモリにデータをプログラムする方法においては、前記NANDフラッシュメモリに対する命令及びアドレスと、プログラムされるページを設定する第1段階と、前記システムコントローラから前記バッファに前記プログラムされるページに必要なデータを連続してローディングする第2段階と、前記バッファにローディングされたデータを利用して前記ページに対するプログラムを順次に実行する第3段階とを具備する。前記ページのうち一ページに対するデータが前記バッファにローディングされる間に、他の一つのページに対するプログラムが実行される。

#### 【発明の効果】

#### 【0022】

上述によると、本発明はコンピュータシステムでNANDフラッシュメモリをシステム駆動用として使用可能になることによって、より簡単で効率的な方式を提供できる。特に、本発明によるインターフェース装置を利用することによって、NANDフラッシュメモリに対する読み出し動作において、レイテンシ時間を減らす一方、プログラム動作において、全体的なプログラムデータローディング時間を短縮する利点がある。また、NORフラッシュインターフェース方式を有するシステムコントローラに対しても、NANDフラッシュメモリをシステム駆動用及びデータ貯蔵用として利用できるようになる。結果的に、本発明はNANDフラッシュメモリをシステム駆動及びデータ貯蔵用として使用することにおいて、より容易であり、効率的な方式を提案することによって、システム構成に必要な費用を減らす效果がある。

10

20

30

40

50

**【発明を実施するための最良の形態】****【0023】**

以下、本発明によるコンピュータシステムに関して添付した図面を参照して詳細に説明する。本発明による図面で上述の図1の構成要素と実質的に同一の構成要素に対しては同一の参照符号を使用する。

**【0024】**

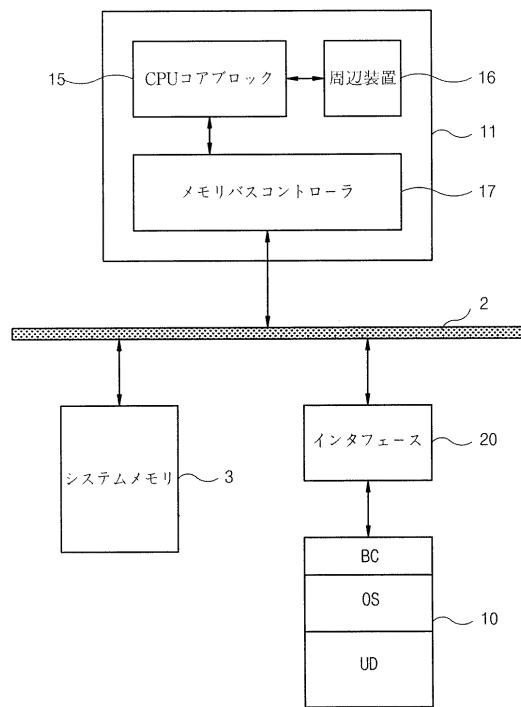

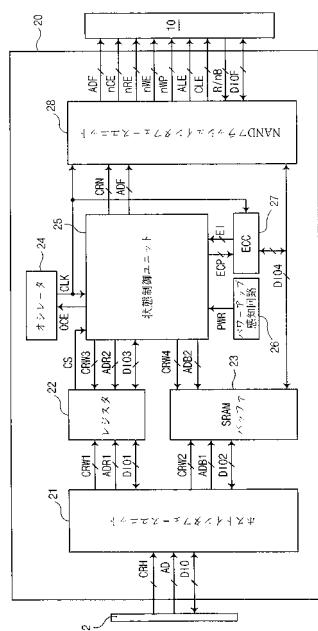

図2は本発明によるコンピュータシステムの構成を示すブロック図である。この図2を参考すると、本発明によるコンピュータシステムは中央処理装置CPUなどのシステムコントローラ11と、システムバス2と、DRAMなどのシステムメモリ3と、本発明に従って領域が区分されたNANDフラッシュメモリ10と、システムバス2とNANDフラッシュメモリ10との間でデータまたは信号の交換を実行するインターフェース装置20からなる。10

**【0025】**

システムバス2はシステムコントローラ11とシステムメモリ3及びインターフェース装置20を互いに連結する。NANDフラッシュメモリ10はデータ貯蔵用だけでなく、システム駆動用としても使用され、その内部のデータ領域はシステム駆動コードを貯蔵する領域BCと、オペレーティングシステム(operating system)に関する情報を貯蔵する領域OSと、通常の使用者データを貯蔵する領域UDとに分けられる。NANDフラッシュメモリ10の貯蔵領域BC、OS及びUDは貯蔵されるデータの種類に従って区分されることとして、各貯蔵領域は複数個のページで構成される。インターフェース装置20は従来のNANDフラッシュコントロール(図1の8)を支援しないシステムコントローラ11のために提供される。システムコントローラ11はコアブロック15と周辺装置16及びメモリバスコントローラ17で構成される。メモリバスコントローラ17はNANDフラッシュメモリのためのインターフェース方式を支援せず、プログラムメモリコントローラとNORフラッシュメモリコントローラを支援する。20

**【0026】**

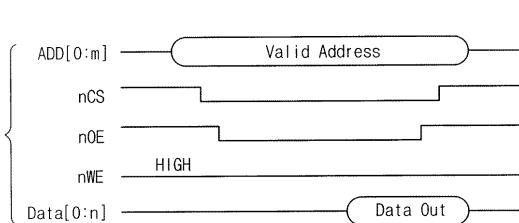

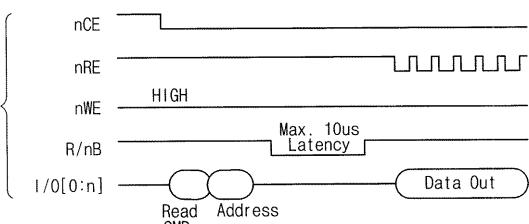

インターフェース装置20はシステムバス2を通じてメモリバスコントローラ17とはNORフラッシュインターフェース方式で動作し、NANDフラッシュメモリ10とはNANDフラッシュインターフェース方式で動作する。図3及び図4はNORフラッシュインターフェース方式とNANDフラッシュインターフェース方式での読み出し動作を各々示す。NORフラッシュメモリはラングムアクセス読み出しが可能であり、NANDフラッシュメモリはラングムアクセス読み出しそれはページ単位で読み出し動作を実行し、最大10μs程度のレイタンシ時間をする。このように、NORフラッシュインターフェース方式とNANDフラッシュインターフェース方式間の差によって、NANDフラッシュインターフェース方式を支援しないシステムコントローラを使用するコンピュータシステムでNANDフラッシュメモリを使用するためには、図2のようなインターフェース装置20が必要である。30

**【0027】**

インターフェース装置20は、図5に示したように、ホストインターフェースユニット21と、レジスタユニット22と、バッファユニット23と、オシレータ24と、状態制御ユニット25と、パワーアップ感知回路26と、エラー訂正回路27と、NANDフラッシュインターフェースユニット28とからなる。40

**【0028】**

ホストインターフェースユニット21は、インターフェース装置20とシステムコントローラ11との間でNORフラッシュインターフェース機能を実行するために、システムコントローラ11に連結されたシステムバス2とアドレス信号AD、データ入出力信号DIO及び制御信号CRHを交換する。アドレス信号ADにはSRAMで構成されたレジスタユニット22及びバッファユニット23とNANDフラッシュメモリ10にデータを貯蔵するためのアドレス信号が含まれる。データ入出力信号DIOとしてはNANDフラッシュメモリ10にプログラムされるか、NANDフラッシュメモリ10から読み出されるデータ50

が伝送される。制御信号 C R H はインターフェース装置 2 0 を動作させるための制御信号を含む。レジスタユニット 2 2 はホストインターフェースユニット 2 1 を通じて提供される制御信号 C R W 1 及びアドレス信号 A D R 1 に応答して図 2 に示したコンピュータシステムの編成(configuration)と命令(command)に関する情報を貯蔵する。ホストインターフェースユニット 2 1 とレジスタユニット 2 2との間で交換されるデータ信号 D I O 1 はそのようなシステム編成と命令に関する情報である。バッファユニット 2 3 はホストインターフェースユニット 2 1 を通じて提供される制御信号 C R W 2 及びアドレス信号 A D B 1 に応答して N A N D フラッシュメモリ 1 0 から読み出されたか、N A N D フラッシュメモリ 1 0 にプログラムされるデータを一時的に貯蔵する。ホストインターフェースユニット 2 1 とバッファユニット 2 3との間で交換されるデータ信号 D I O 2 は N A N D フラッシュメモリ 1 0 から読み出されてシステムコントローラ 1 1 に伝送されるデータ信号やシステムコントローラ 1 1 から提供されて N A N D フラッシュメモリ 1 0 にプログラムされるデータ信号である。

10

#### 【 0 0 2 9 】

レジスタユニット 2 2 とバッファユニット 2 3 は S R A M で構成される。レジスタユニット 2 2 は編成レジスタと命令レジスタとを含んでいる。例えば、編成レジスタにはインターフェース装置 2 0 が制御している N A N D フラッシュメモリ 1 0 の特性、すなわち入出力拡張度( I O \_ d e p t h : × 8 または × 1 6 )、ページのサイズ、記録密度及びエラー訂正の可否などの情報が貯蔵される。命令レジスタでは、例えば該当するアドレスに書き込み命令が入力されれば、書き込み命令が実行され、命令レジスタから命令開始信号 C S が状態制御ユニット 2 5 に印加される。レジスタユニット 2 2 はインターフェース装置 2 0 の内部動作のために、状態制御ユニット 2 5 から印加される制御信号 C R W 3 及びアドレス信号 A D R 2 に応答して状態制御ユニット 2 5 とシステム編成と命令に関するデータ信号を交換する。バッファユニット 2 3 は状態制御ユニット 2 5 から提供される制御信号 C R W 4 及びアドレス信号 A D B 2 に応答して N A N D フラッシュインターフェースユニット 2 8 を通じて N A N D フラッシュメモリ 1 0 とデータ信号(システム駆動コード、読み出しデータまたはプログラムデータ) D I O 4 を交換する。

20

#### 【 0 0 3 0 】

オシレータ 2 4 は状態制御ユニット 2 5 から提供される活性化信号 O C E に応答してインターフェース装置 2 0 の内部動作を同期化させるクロック信号 C L K を発生する。クロック信号 C L K はエラー訂正回路 2 7 と N A N D フラッシュインターフェースユニット 2 8 に供給される。クロック信号をインターフェース装置 2 0 の外部(例えば、図 2 のシステムコントローラ 1 1 など)で発生させた後に、ホストインターフェースユニット 2 1 を通じて供給させることもできるが、インターフェース装置 2 0 の内部で発生させることは電流消耗を減らすためである。すなわち、クロック信号が常にインターフェース装置 2 0 の外部からインターフェース装置 2 0 に印加される方法でないとすると、インターフェース装置 2 0 の外部から印加される命令がレジスタユニット 2 2 内の命令レジスタに設定されれば、オシレータ 2 4 が動作し、それによって状態制御ユニット 2 5 が決められた動作を実行し、すべての動作が完了すれば、オシレータ 2 4 は停止する。

30

#### 【 0 0 3 1 】

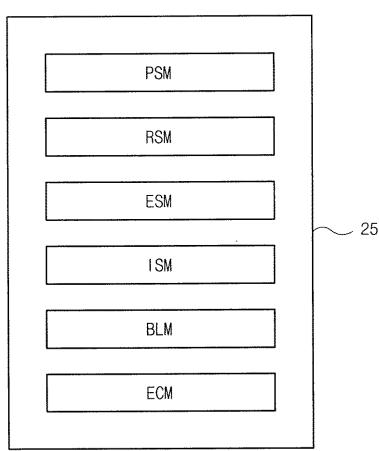

状態制御ユニット 2 5 はインターフェース装置 2 0 の動作を管理して制御する中央処理装置としての機能を実行する。状態制御ユニット 2 5 は、図 6 に示すように、機能別でプログラム制御ブロック P S M 、読み出し制御ブロック R S M 、消去制御ブロック E S M 、遮断制御ブロック I S M 、システム駆動制御ブロック B L M 及びエラー訂正制御ブロック E C M に区分されている。

40

#### 【 0 0 3 2 】

プログラム制御ブロック P S M はバッファユニット 2 3 に貯蔵されたデータを N A N D フラッシュメモリ 1 0 の予め指定されたアドレスにプログラムする動作を制御し、エラー訂正制御ブロック E C M によって発生したパリティビットを N A N D フラッシュメモリ 1 0 の予め指定されたスペーサアドレスに貯蔵する動作を制御する。読み出し制御ブロック R S M 50

ク R S M は N A N D フラッシュメモリ 1 0 から読み出したデータを予め指定されたバッファユニット 2 3 のアドレス位置に貯蔵する動作を制御する。消去制御ブロック E S M は N A N D フラッシュメモリ 1 0 の指定されたアドレスのデータを消去する動作を制御する。遮断制御ブロック I S M は N A N D フラッシュメモリ 1 0 に対するリセット動作とインターフェース装置 2 0 内のレジスタに対するリセット動作を制御する。システム駆動制御ブロック B L M は、システム駆動回路を含んでおり、パワーアップ感知回路 2 6 の出力である電源感知信号 P W R に応答して N A N D フラッシュメモリ 1 0 に貯蔵されたシステム駆動コードをバッファユニット 2 3 に伝送する動作を制御し、読み出し制御ブロック R S M と共同して使用される。システム駆動制御ブロック B L M は通常の読み出し動作と同一であり、予め決められたシステム駆動コードに従ってページ読み出し動作を連続して実行する。

10 例えれば、N A N D フラッシュメモリ 1 0 のシステム駆動コード領域 B C が 8 個のページに割り当てられており、インターフェース装置 2 0 のバッファユニット 2 3 のサイズが 8 個のページと同一またはより大きいと仮定すれば、8 個のページ分のデータが N A N D フラッシュメモリ 1 0 の領域 B S からバッファユニット 2 3 に連続して読み出されて伝送される。エラー訂正制御ブロック E C M は N A N D フラッシュメモリ 1 0 のプログラム動作中にパリティビットを発生する動作を制御し、読み出し動作中に貯蔵されたパリティビットと新しいパリティビットとを比べて、該当するアドレスのデータを補正する動作を実行する。

#### 【 0 0 3 3 】

パワーアップ感知回路 2 6 は図 2 のコンピュータシステムに電源が印加された時に、電源感知信号 P W R を発生して内部のレジスタを初期化し、状態制御ユニット 2 5 のシステム駆動制御ブロック B L M を活性化させる。エラー訂正回路 2 7 は、状態制御ユニット 2 5 から提供されるエラー検査信号 E C P に応答して N A N D フラッシュメモリ 1 0 に対するデータ読み出し及びプログラムの間に生成したパリティビットを利用してデータエラー感知及び補正を行う。エラー訂正回路 2 7 は N A N D フラッシュインターフェースユニット 2 8 とバッファユニット 2 3 との間で伝送されるデータを同時に受け入れた後に、エラー訂正コードを生成し、単一ビットエラーがある場合に、これを補正し、それによるエラー情報信号 E I を状態制御ユニット 2 5 に提供する。N A N D フラッシュインターフェースユニット 2 8 は状態制御ユニット 2 5 から提供される N A N D フラッシュメモリ用の命令及び制御信号 C R N とアドレス信号 A D F を N A N D フラッシュメモリ 1 0 に N A N D フラッシュインターフェース方式で伝送し、N A N D フラッシュメモリ 1 0 とインターフェース装置 2 0 との間のデータ交換を中継する。これによって、N A N D フラッシュメモリ 1 0 は N A N D フラッシュインターフェースユニット 2 8 を通じて動作に必要な制御信号、すなわちチップイネーブル信号 n C E 、読み出しイネーブル信号 n R E 、書き込みイネーブル信号 n W E 、書き込み防止信号 n W P 、アドレスラッチャイネーブル信号 A L E 及び命令ラッチャイネーブル信号 C L E とアドレス信号 A D F を受け入れ、レディ/ビジー信号 R / n B を提供し、データ信号(システム駆動コード、読み出しましたはプログラムデータ) D I O F を N A N D フラッシュインターフェースユニット 2 0 と交換する。

30

#### 【 0 0 3 4 】

図 5 のインターフェース装置 2 0 内に構成されたパワーアップ感知回路 2 6 とエラー訂正回路 2 7 はインターフェース装置 2 0 の外部に設置することができる。例えば、パワーアップ感知回路 2 6 から出力される電源感知信号 P W R を使用せず、インターフェース装置 2 0 の外部から印加されるシステムリセット信号などを利用してシステム駆動を始めることができる。

40

#### 【 0 0 3 5 】

以下、上述のインターフェース装置 2 0 を利用するコンピュータシステムで、N A N D フラッシュメモリ 1 0 をシステム駆動用及びデータ貯蔵用として使用する場合について、動作を詳細に説明する。動作は N A N D フラッシュメモリ 1 0 を利用したシステム駆動と、N A N D フラッシュメモリ 1 0 に対する読み出し、及びプログラムに区分して説明する。それ以外の N A N D フラッシュメモリの動作、例えば消去、または消去/プログラム検証

50

などに関しては一般的なことなので、それらに関する説明は省略する。

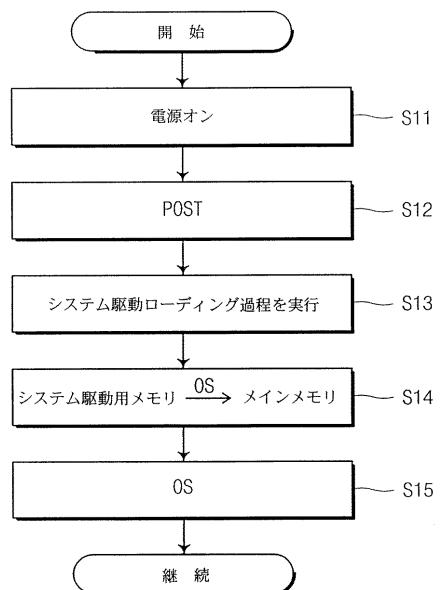

#### 【0036】

図7は図2のコンピュータシステムで全体的なシステム駆動のための基本過程を示す。図7を参照すると、電源が供給されれば(段階S11)、バイオスの処理手順(BIOS routine)に従ってシステムコントローラ11が周辺装置16、例えばメモリ装置またはハードディスクなどが正常に動作するか否かを把握するために、各ハードウェア装置を初期化し、検査するポスト(POST: power-on self test)過程を実行する(段階S12)。<sup>10</sup> POST過程でシステムに連結されたハードウェア装置の動作に異常がなければ、システム駆動用メモリ(すなわち、NANDフラッシュメモリ10)からのシステム駆動ローディング過程を実行する(段階S13)。その次に、NANDフラッシュメモリ10に貯蔵されたオペレーティングシステム(OS)プログラムをメインメモリ(すなわち、システムメモリ3)にロードする(段階S14)。オペレーティングシステムプログラムはコンピュータシステムのハードウェア及びソフトウェアに対して設定された情報を検索してコンピュータシステムが正常に動作するように実行される(段階S15)。

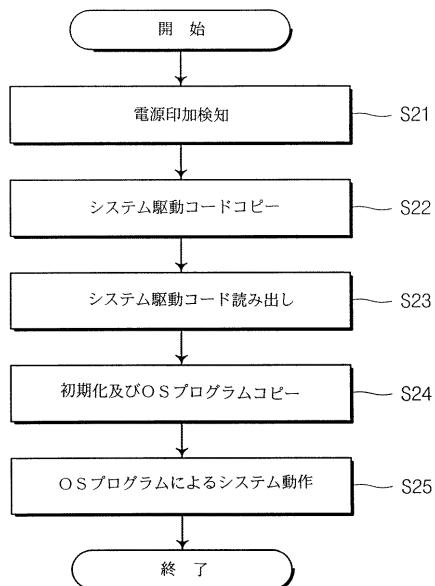

#### 【0037】

NANDフラッシュメモリ10をシステム駆動用として使用して図2のコンピュータシステムを駆動する過程に関してより具体的に説明する。図8を参照すると、先ず、システムに電源が印加されれば(段階S21)、パワーアップ感知回路26が電源感知信号PWRを発生し、状態制御ユニット25のシステム駆動制御ブロックBLMにこれを知らせる。<sup>20</sup>ここで、パワーアップ感知回路26を利用して電源印加状態を感知する方法を使用せず、システムリセット信号に応答してシステム駆動制御ブロックBLMに電源が印加されたことを知らせる方法を採用することもできる。

#### 【0038】

電源印加状態が確認されれば、段階S22で、システム駆動制御ブロックBLMはNANDフラッシュメモリ10に貯蔵されたシステム駆動コードをバッファユニット23にコピーする。システムコントローラ11はバッファユニット23から貯蔵されたシステム駆動コードを読み出す(段階S23)。また、システムコントローラ11は、段階S24で、システムのハードウェア装置を初期化し、NANDフラッシュメモリ10に貯蔵されたオペレーティングシステムプログラムをシステムメモリ3にコピーする(図7の段階S14に相当する)。その後に、段階S25で、システムコントローラ11はシステムメモリ3に貯蔵されたオペレーティングシステムプログラムによってシステムを動作させる(図7の段階S15に相当する)。<sup>30</sup>

#### 【0039】

本発明で利用されるシステム駆動コードは、システムのハードウェア装置を初期化し、オペレーティングシステムプログラムをシステムメモリ3にロードするためのものとして、システムハードウェア装置を初期化させるコードと、オペレーティングシステムプログラムをコピーするためのコードで構成される。また、システム駆動コードは必要な場合、システムに遮断命令が印加される時に実行されるベクタなどを含むことができる。

#### 【0040】

NANDフラッシュメモリ10は、上述のように、システム駆動用だけでなく、固有の動作すなわち、消去、プログラム及び読み出し機能を有するので、システムコントローラ11がNANDフラッシュインターフェース機能を支援しない場合(既存の大部分のシステムコントローラはNORフラッシュインターフェース機能を支援して来た)に、インターフェース装置20がシステムコントローラ11とNANDフラッシュメモリ10との間のインターフェース環境を支援することができるようになる。すなわち、図2または図3、図4に示したように、インターフェース装置20はシステムコントローラ11とはホストインターフェースユニット21を通じてNORフラッシュインターフェースを実行し、NANDフラッシュメモリ10とはNANDフラッシュインターフェースユニット28を通じてNANDフラッシュインターフェースを実行する。NANDフラッシュメモリ10をデータ貯蔵用と<sup>40</sup>

して運用するためにインターフェース装置20は二つの処理方式、すなわちインタリーブ読み出し(int erleave r ead)とインタリーブプログラムを実行する。

#### 【0041】

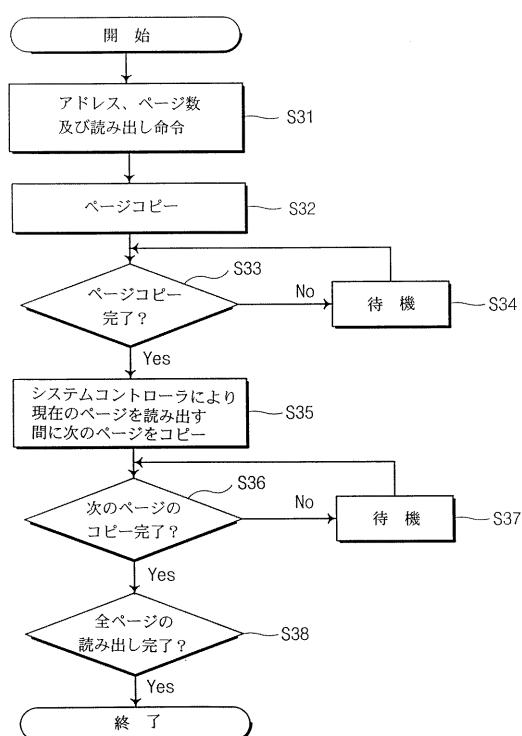

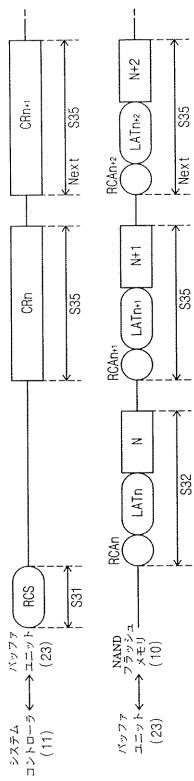

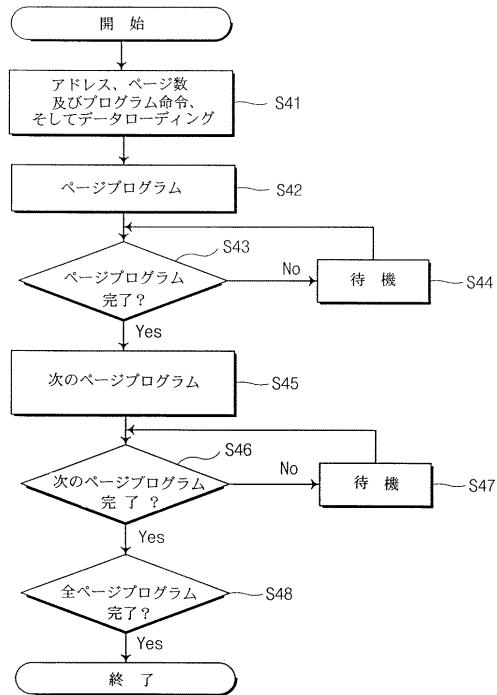

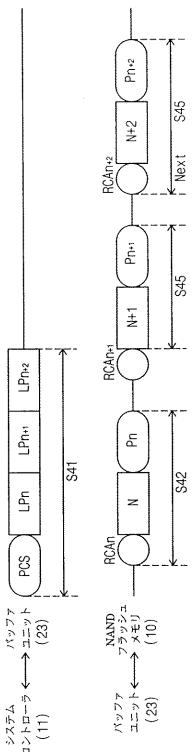

図9及び図10はインタリーブ読み出しに関する過程を示し、図11及び図12はインタリーブプログラムに関する過程を示す。

#### 【0042】

最初に、図9及び図10を参照してインタリーブ読み出しに関する動作過程を説明する。先の図3及び図4と関連して言及したように、NORフラッシュメモリはワードまたはバイト単位でランダムアクセスが可能である一方、NANDフラッシュメモリはページ単位でアクセスするので、データが読み出されるまで(システムコントローラ11がNANDフラッシュメモリ10から読み出されたデータを受け付けるまで)基本的に最大 $10\mu s$ 程度のレイタンシ時間の間待たなければならない。本発明によるインタリーブ読み出し動作では、そのようなレイタンシ時間を減らして動作性能を向上させる。10

#### 【0043】

システムコントローラ11がインターフェース装置20にNANDフラッシュメモリ10に対するアドレス及び読み出しページ数に関する情報とともにNANDフラッシュメモリ10からのデータ読み出し命令を出力すれば(段階S31)、インターフェース装置20はNANDフラッシュメモリ10からバッファユニット23に指定されたアドレスに該当するページのデータをコピーする(段階S32)。段階S31では、図10に示したように、読み出し動作が初期化し、読み出されるページに対するアドレスとデータ量を設定するための区間RCSが含まれる。現在の指定されたページに対するデータコピーが完了すれば(段階S33)、システムコントローラ11は現在ページのデータをバッファユニット23から読み出す一方、インターフェース装置20は次のページのデータをバッファユニット23にコピーする(段階S35)。次のページに対するデータコピーが完了すれば(段階S36)、システムコントローラ11がインターフェース装置20に設定したページ数だけ読み出し及びコピーが完了したか否か検査する(段階S38)。段階S38で指定されたすべてのページに対するデータコピーが完了しなければ、段階S35に戻って、次のページに対するデータ読み出し及びコピー動作を繰り返す。NANDフラッシュメモリ10から各ページ(例えば、ページN)に対するデータを読み出す過程は、各ページに対する読み出し命令とアドレスを導入する区間RCAnと、読み出しに必要なレイタンシ時間が所要される区間LATnと、該当のページに対するデータの読み出し/コピーが進行される区間Rnからなる。20

#### 【0044】

特に、図10を参照すると、一番目のページN(N:任意のページ番号)に対するデータがNANDフラッシュメモリ10からバッファユニット23にコピーされた後(区間Rn)、二番目のページN+1のデータがNANDフラッシュメモリ10からバッファユニット23にコピーされている間に(段階S35の区間Rn+1)、一番目のページNのデータがバッファユニット23からシステムコントローラ11に伝送されている(区間CRn)が見られる。すなわち、最初のページデータがバッファユニット23にコピーされた後(段階S32)からはシステムコントローラ11への伝送とページ読み出し/コピーが同時に進行される(段階S35)。同様に、二番目のページN+1のデータがバッファユニット23からシステムコントローラ11に伝送される間(区間CRN+1)、三番目のページN+2のデータがNANDフラッシュメモリ10からバッファユニット23にコピー(区間Rn+2)される。決められたページ(例えば、N、N+1、N+2)だけ、このような過程が図9に示した手順によって繰り返される。30

#### 【0045】

各々のページがNANDフラッシュメモリ10からバッファユニット23にコピーされる時には、各ページ読み出しに所要されるレイタンシ時間LATn、LATn+1及びLATn+2が所要されるが、システムコントローラ11の立場では、NANDフラッシュメモリ10からの読み出しデータを上述のレイタンシ時間(約 $10\mu s$ :すなわち、LA40

$T_n$ 、 $LAT_{n+1}$ または $LAT_{n+2}$ )を経ずに、ページ単位で連続して受け入れることができる。

#### 【0046】

次に、図11及び図12を参照して、インタリーププログラムに関する動作過程を説明する。 $NAND$ フラッシュメモリ10をプログラムするためには、プログラムするデータを $NAND$ フラッシュメモリ10のページバッファにローディングする動作が必要である。本発明によるインタリーププログラムでは、そのようなデータローディング時間を減らす。

#### 【0047】

最初に、段階S41で、システムコントローラ11がインタフェース装置20に $NAND$ フラッシュメモリ10に対するアドレス及びプログラムするページ数に関する情報とともに $NAND$ フラッシュメモリ10に対するプログラム命令を出力すれば、プログラムされるページに該当するデータがバッファユニット23にローディングされる。すなわち、段階S41では、プログラム編成情報がインタフェース装置20のレジスタユニット22に提供され(PCS)、プログラムされるページに該当するデータがバッファユニット23に順次にローディングされる( $LP_n$ 、 $LP_{n+1}$ 及び $LP_{n+2}$ )。そうすると、段階S42で、バッファユニット23にローディングされた手順に従って、優先的に一番目のページNに対してプログラム命令及びアドレスが提供され(PCAn)、バッファユニット23からの該当するデータがローディングされた後( $Ln$ )に、指定されたページに対するプログラムが実行される(Pn)。ここで、図10のタイミング状態から分かるように、現在の一ページ(例えば、N)に対するプログラムが実行される間に、次のページ(例えば、N+1)のデータがバッファユニット23にローディングされていることに注目しなければならない。現在の指定されたページに対するプログラムが完了したことが確認されれば(段階S43)、段階S45で、インタフェース装置20は既にバッファユニット23に貯蔵された次のページN+1に対するプログラムを上述の一番目のページに対して実行したことと同様にプログラム動作を実行する(PCAn+1 > Ln+1 > Pn+1)。次のページ(すなわち、二番目のページ)に対するプログラムが完了したことが確認されれば(段階S46)、システムコントローラ11がインタフェース装置20に設定したページ数(例えば、三つのページN～N+2)だけプログラムが完了したか否かを検査する(段階S48)。段階S48で指定されたすべてのページに対するプログラムが完了していないことが確認されれば、段階S45に戻って次のページに対するプログラム動作を繰り返す。

#### 【0048】

このように、本発明によるコンピュータシステムでの $NAND$ フラッシュメモリに対するプログラムでは、プログラムされるページに該当するデータを予めバッファユニット23にローディングした後に、各ページに対するプログラムを実行するので、一つのページに対するデータローディングが実行される間に(例えば、 $LP_{n+1}$ )、他のページに対するプログラム(例えば、Pn)を実施することができる。結果的に、 $NAND$ フラッシュメモリに対する全体的なプログラムデータローディング時間が減ることによって、全体的なプログラム時間を短縮することができる。

#### 【0049】

なお、上述の実施の形態で示した本発明の手段と方法に基づいて本発明の技術分野で通常の知識を持つ者は本発明の範囲内で本発明の変形及び応用が可能である。

#### 【産業上の利用可能性】

#### 【0050】

本発明は、コンピュータシステムなどで $NAND$ フラッシュメモリをシステム駆動用及びデータの貯蔵用として同時に使用する場合に適用が可能である。

#### 【図面の簡単な説明】

#### 【0051】

【図1】従来のコンピュータシステムの構成を示すブロック図。

10

20

30

40

50

【図2】本発明によるコンピュータシステムの構成を示すブロック図。

【図3】NORフラッシュメモリに対する読み出し動作を示すタイミング図。

【図4】NANDフラッシュメモリに対する読み出し動作を示すタイミング図。

【図5】図2のインターフェース装置の内部構成を示すブロック図。

【図6】図5の状態制御ユニットの機能別構成を示すブロック図。

【図7】図2のコンピュータシステムが駆動される過程を示すブロック図。

【図8】NANDフラッシュメモリをシステム駆動用として使用する場合に、図2のコンピュータシステムが駆動される過程を示す順序図。

【図9】図5のインターフェース装置を利用してNANDフラッシュメモリからデータを読み出す過程を示す順序図。

10

【図10】図5のインターフェース装置を利用してNANDフラッシュメモリからデータを読み出す過程を示すタイミング図。

【図11】図5のインターフェース装置を利用してNANDフラッシュメモリにデータをプログラムする過程を示す順序図。

【図12】図5のインターフェース装置を利用してNANDフラッシュメモリにデータをプログラムする過程を示すタイミング図。

【符号の説明】

【0052】

- |    |              |

|----|--------------|

| 2  | システムバス       |

| 3  | システムメモリ      |

| 10 | NANDフラッシュメモリ |

| 11 | システムコントローラ   |

| 15 | CPUコアブロック    |

| 16 | 周辺装置         |

| 17 | メモリバスコントローラ  |

| 20 | インターフェース装置   |

20

【 図 1 】

【 四 2 】

【 図 3 】

【図4】

【 四 5 】

【図6】

【図7】

【図8】

【図9】

【図 1 0】

【図 1 1】

【図 1 2】

---

フロントページの続き

(72)発明者 崔 永 準

大韓民国京畿道城南市盆唐区金谷洞142番地 チュンソルタウン814-1802

審査官 堀江 義隆

(56)参考文献 特開2002-109490 (JP, A)

特開平10-260912 (JP, A)

特開2001-266580 (JP, A)

米国特許第05535357 (US, A)

特開2002-207715 (JP, A)

(58)調査した分野(Int.Cl., DB名)

G 06 F 12 / 00 - 12 / 06

G 06 F 13 / 16 - 13 / 18

G 06 F 11 / 10

G 06 F 12 / 16

G 06 F 9 / 445