(19) **日本国特許庁(JP)**

# (12) 特 許 公 報(B2)

(11) 特許番号

特許第4755655号 (P4755655)

(45) 発行日 平成23年8月24日(2011.8.24)

(24) 登録日 平成23年6月3日(2011.6.3)

(51) Int .Cl .

GO3F 1/08 (2006.01)

GO3F 1/08

FL

A

請求項の数 18 (全 14 頁)

(21) 出願番号 特願2007-552287 (P2007-552287)

(86) (22) 出願日 平成18年1月20日 (2006.1.20)

(65) 公表番号 特表2008-529066 (P2008-529066A)

(43) 公表日 平成20年7月31日 (2008. 7. 31)

(86) 国際出願番号 PCT/US2006/002046 (87) 国際公開番号 W02006/078908

(87) 国際公開日 平成18年7月27日 (2006. 7. 27) 審査請求日 平成20年10月8日 (2008. 10.8)

(31) 優先権主張番号 10/905,822

(32) 優先日 平成17年1月21日 (2005.1.21)

(33) 優先権主張国 米国(US)

(73) 特許権者 390009531

インターナショナル・ビジネス・マシーン

ズ・コーポレーション

INTERNATIONAL BUSIN ESS MASCHINES CORPO

RATION

アメリカ合衆国10504 ニューヨーク

州 アーモンク ニュー オーチャード

ロード

||(74)代理人 100108501

弁理士 上野 剛史

|(74)代理人 100112690

弁理士 太佐 種一

|(74)代理人 100091568

弁理士 市位 嘉宏

最終頁に続く

(54) 【発明の名称】差分交互位相シフト・マスクの最適化

#### (57)【特許請求の範囲】

### 【請求項1】

リソグラフィ工程において集積回路設計の画像を投影するためのマスクを設計する方法であって、

複数の限界幅セグメントを有する集積回路レイアウトの設計を準備するステップと、

限界幅セグメントの投影を補助するために用いられるマスク構造体を、前記集積回路設計の前記限界幅セグメントに位置合わせすることにより、所定の製造可能設計ルールを満足する第 1 のマスク設計を作成するステップと、

限界幅セグメントの投影を補助するために用いられるマスク構造体を、前記集積回路設計の前記限界幅セグメントに位置合わせすることにより、所定のリソグラフィ設計ルールを、前記限界幅セグメントの近傍の領域において満足する第2のマスク設計を作成するステップと、

前記所定の製造可能設計ルールに違反する前記第2のマスク設計の設計構造体を識別するステップと、

前記第2のマスク設計から導かれる第3のマスク設計であって、前記所定の製造可能設計ルールに違反する前記第2のマスク設計の前記マスク構造体は、前記第3のマスク設計が前記所定の製造可能設計ルールを満足するように、前記第1のマスク設計からの設計構造体によって選択的に置き替えられる、第3のマスク設計を作成するステップとを含む方法。

【請求項2】

20

前記第2のマスク設計は、前記第1のマスク設計のサブセットを含む、請求項1に記載の方法。

#### 【請求項3】

前記第3のマスク設計を用いて、前記集積回路設計の画像を基板に転写するステップを さらに含む、請求項1に記載の方法。

### 【請求項4】

限界幅セグメントの投影を補助するために用いられる前記マスク構造体は、交互位相シフト領域を含む、請求項1に記載の方法。

#### 【請求項5】

前記所定の製造可能設計ルールは、最小の位相幅及び最小の位相・位相間隔を含む、請求項4に記載の方法。

#### 【請求項6】

限界幅セグメントの投影を補助するために用いられる前記マスク構造体は、サブ解像度アシスト構造体(SRAF)を含む、請求項1に記載の方法。

### 【請求項7】

前記所定の製造可能設計ルールは、SRAFサイズ及び間隔を含む、請求項6に記載の方法。

#### 【請求項8】

集積回路設計の画像を投影するための交互位相シフト・マスクを設計する方法であって .

複数の限界幅セグメントを有する集積回路レイアウトの設計を準備するステップと、

交互位相シフト領域を前記限界幅セグメントに位置合わせし、前記交互位相シフト領域をそれらが位置合わせされる前記限界幅セグメントの少なくとも幾つかの端部を越えて延長させることによって、所定の製造可能設計ルールを満足する交互位相シフト・マスクの第1のマスク設計を作成するステップと、

交互位相シフト領域を前記限界幅セグメントに位置合わせし、前記交互位相シフト領域の対をそれらが位置合わせされる前記限界幅セグメントの端部を実質的に越えて延長させずに、交互位相シフト・マスクの第2のマスク設計を作成するステップと、

前記所定の製造可能設計ルールに違反する前記第2のマスク設計の設計構造体を識別するステップと、

前記第2のマスク設計から導かれる第3のマスク設計であって、前記所定の製造可能設計ルールに違反する前記第2のマスク設計の前記設計構造体は、前記第3のマスク設計が前記所定の製造可能設計ルールを満足するように、前記第1のマスク設計からの設計構造体によって選択的に置き替えられる、第3のマスク設計を作成するステップとを含む方法。

#### 【請求項9】

前記所定の製造可能設計ルールは、最小の位相幅及び最小の位相・位相間隔を含む、請求項8に記載の方法。

### 【請求項10】

前記交互位相シフト・マスクの前記第2のマスク設計は、最小の位相幅及び最小の位相 - 位相間隔を含む製造設計ルールの少なくとも1つに違反する、請求項8に記載の方法。

前記第3のマスク設計を用いて、集積回路設計の画像を基板に転写するステップをさらに含む、請求項8に記載の方法。

#### 【請求項12】

集積回路設計の画像を投影するためのフォトマスクを設計する方法であって、

複数の限界幅セグメントを有する集積回路レイアウトの設計を準備するステップと、

サブ解像度アシスト構造体(SRAF)を前記限界幅セグメントに位置合わせすることにより、所定の製造可能設計ルールを満足するフォトマスクの第1のマスク設計を作成するステップと、

20

10

\_\_

30

40

サブ解像度アシスト構造体を前記限界幅セグメントに位置合わせすることにより、所定のリソグラフィ設計ルールを前記限界幅セグメントの近傍の領域において満足するフォトマスクの第2のマスク設計を作成するステップと、

前記所定の製造可能設計ルールに違反する前記第2のマスク設計の設計構造体を識別するステップと、

前記第2のマスク設計から導かれる第3のマスク設計であって、前記所定の製造可能設計ルールに違反する前記第2のマスク設計の前記設計構造体は、前記第3のマスク設計が前記所定の製造可能設計ルールを満足するように、前記第1のマスク設計からの設計構造体によって選択的に置き替えられる、第3のマスク設計を作成するステップとを含む方法。

【請求項13】

前記所定の製造可能設計ルールは、SRAFサイズ及び間隔を含む、請求項12に記載の方法。

### 【請求項14】

前記第2のマスク設計は、SRAFサイズ及び間隔を含む所定の製造設計ルールの少なくとも1つに違反する、請求項12に記載の方法。

#### 【請求項15】

前記第3のマスク設計を用いて、前記集積回路設計の画像を基板に転写するステップを さらに含む、請求項12に記載の方法。

### 【請求項16】

マシンにより可読なプログラム記憶装置であって、集積回路設計の画像を投影するためのマスクを設計する方法ステップを実行するための、前記マシンにより実行可能な命令のプログラムを記憶し、前記集積回路設計のレイアウトは複数の限界幅セグメントを有し、前記方法ステップは、

限界幅セグメントの投影を補助するために用いられるマスク構造体を、前記集積回路設計の前記限界幅セグメントに位置合わせすることにより、所定の製造可能設計ルールを満足する、マスクの第1のマスク設計を作成するステップと、

限界幅セグメントの投影を補助するために用いられるマスク構造体を、前記集積回路設計の前記限界幅セグメントに位置合わせすることにより、所定のリソグラフィ設計ルールを前記限界幅セグメントの近傍の領域において満足する、マスクの第2のマスク設計を作成するステップと、

前記所定の製造可能設計ルールに違反する前記第2のマスク設計の設計構造体を識別するステップと、

前記第2のマスク設計から導かれる第3のマスク設計であって、前記所定の製造可能設計ルールに違反する前記第2のマスク設計の前記マスク構造体は、前記第3のマスク設計が前記所定の製造可能設計ルールを満足するように、前記第1のマスク設計からのマスク構造体によって選択的に置き替えられる、第3のマスク設計を作成するステップとを含む、プログラム記憶装置。

### 【請求項17】

限界幅セグメントの投影を補助するために用いられる前記マスク構造体は交互位相シフト領域、またはサブ解像度アシスト構造体(SRAF)を含む、請求項16に記載のプログラム記憶装置。

### 【請求項18】

前記所定の製造可能設計ルールは、最小の位相幅及び最小の位相・位相間隔、またはSRAFサイズ及び間隔を含む、請求項17に記載のプログラム記憶装置。

### 【発明の詳細な説明】

## 【技術分野】

#### [0001]

本発明は集積回路のリソグラフィによる製造に用いられるマスクの製作に向けられ、特に、解像度向上技術(RET)により改良されたマスクの製作、より具体的には、RET

10

20

30

40

マスク設計に対するICレイアウトの自動化され最適化された変換に向けられる。

#### 【背景技術】

### [0002]

集積回路のリソグラフィによる製造に用いられるクロム・オン・ガラス(COG)マス クの代替として、投影される限界アクティブ領域パターンの解像度を向上させるために、 交互位相シフト・マスク(altPSM)が用いられている。そのような向上された解像 度は、レジスト上のより細いライン幅及びより密なピッチを露光してウェハ基板をエッチ ングする又はウェハ基板上に堆積することを可能にする。システムの限界寸法(CD)は リソグラフィ・システムが標準的技法によるレジスト層の適切な寸法制御によって作成 することのできる最小の寸法であり、そしてaltPSMはサブ限界寸法(CD)幅を露 光してウェハ上に作成することを可能にする。このことは、リソグラフィエ程で用いられ る可視又は紫外光などのエネルギー・ビームの電界ベクトル又は位相を操作することによ って行われる。この位相変化は、PSM内で、光ビームがマスク材料内を進む距離を変え ることによって達成される。マスクを適切な深さまで窪ませることにより、マスクのより 薄い部分を横切る光とマスクのより厚い部分を横切る光とは位相が180。ずれることに なる、即ち、それらの電界ベクトルは振幅は等しく、しかし正確に反対方向を向くことに なり、その結果、これらの光ビーム間の如何なる相互作用も完全に解消される。非常に厳 しい寸法制御で狭いラインを画像形成するためにaltPSMを用いることの利点は広く 論文に記載されている。

### [0003]

altPSMレイアウトを生成する上での主要な課題は、不適当なレイアウトの矛盾を生じずに、そして光学近接障害を生じずに、作成可能でリソグラフィの実施が可能な位相形状を作成することである。最近、特許文献1は、altPSMレイアウトの設計に対するグローバル指向の(globally oriented)方法を開示している。この方法においては、位相がルールに適合し作成可能なレイアウトが、レイアウト・パタタンの全バックグラウンドを基本的に位相形状で満たすことによって達成され、その結果を引きれた位相形状は、回路及びCD構造体の最初のレイアウトを遥かに越えて広がる。のかれた位相形状は、回路及びCD構造体の最初のレイアウトを遥かに越えて広がる。はれたでは相形状は、面路及びCD構造体の最初のレイアウトを遥かに越えて広がる。カースに対するこれらのグローバル法は、費用が高く間違いの起り易い反復的な位相のループに対するこれらのグローバル法は、費用が高く間違いの起り易い反復的な心を回避するが、光学近接効果補正(OPC)に関する最善のaltPSM設計を常に与えるとは限らない。グローバルPSM設計に用いられる付加の位相形状はOPCに複雑さを加え、最初のレイアウト形状のパターン付けに直接影響する限界位相端との不都合な矛盾を生じる可能性がある。

#### [0004]

グローバルPSM設計法において生成される位相形状の多くを除去し、ローカルPSM 法に焦点を合わせることは、一般にOPC性能を改善する一方で、レイアウトをローカル altPSM設計法にゆだねることは、グローバルPSM設計により初めは回避されてい た位相適合性の課題の全てを元に戻してしまう。

#### [0005]

【特許文献1】米国特許出願第10/707,962号

#### 【発明の開示】

【発明が解決しようとする課題】

### [0006]

従来技術の問題と欠陥を考慮して、本発明の目的は、集積回路のリソグラフィによる製造のための位相シフト・マスク、特にaltPSMを設計するための改善された方法を提供することである。

特に、本発明の目的は、グローバル設計法の効率性及び正確さの利点と、ローカルaltPSMの改善されたOPC性能との間の最適なバランスに達するaltPSMの設計法を提供することである。

10

20

30

40

本発明の別の目的は、グローバル及びローカル設計法の最適化の利点を、サブ解像度アシスト構造体(SRAF)などの限界幅構造体の解像度を向上させるために用いられる他のリソグラフィのマスク構造体に拡張することである。

本発明のさらに他の目的及び利点は、本明細書から部分的に自明となり、部分的に明白となる。

#### 【課題を解決するための手段】

#### [0007]

前述及び他の目的は、当業者には明白となるが、リソグラフィエ程において、複数の限界幅セグメントを有する集積回路設計の画像を投影するためのマスクを設計する方法に向けられる本発明において達成される。本方法は、第1のマスク設計を、限界幅セグメントの投影を補助するために用いるマスク構造体を集積回路設計の限界幅セグメントに位することによって、この第1のマスク設計が所定の製造可能設計ルールを満足するように、作成するステップを含む。本方法はまた、第2のマスク設計を、限界幅セグメントの投影を補助するために用いるマスク構造体を集積回路設計の限界幅セグメントに位いたの投影を補助するために用いるマスク機計が限界幅セグメントの近傍の領域においたのでで、この第2のマスク設計が限界幅セグメントの近傍の領域においた、所定の製造可能設計ルールに違反する、第2のマスク設計の設計構造体を識別テップと、次いで、第2のマスク設計から導かれる第3のマスク設計を作成するスプを含むが、その際、所定の製造可能ルールに違反する第2のマスク設計のマスク構造体が所定の製造可能設計ルールを満足するように、第1のマスク設計からのマスク構造体により選択的に置き替えられる。

#### [0008]

実施例として、限界幅セグメントの投影の補助に用いるマスク構造体は、交互位相シフト領域又はサブ解像度アシスト構造体を含むことができる。第2のマスク設計は第1のマスク設計のサブセットを含むことが好ましい。次に第3のマスク設計は集積回路設計の画像を基板に転写するために用いることができる。

#### [0009]

交互位相シフト領域がマスク構造体として用いられるところでは、所定の製造可能設計ルールは、最小の位相幅及び最小の位相 - 位相間隔を含むことができ、所定のリソグラフィ設計ルールはプロセス・ウィンドウの考慮を含むことができる。

#### [0010]

マスク構造体がサブ解像度アシスト構造体であるところでは、所定の製造可能設計ルールは、SRAFサイズ及び間隔を含むことができ、所定のリソグラフィ設計ルールはプロセス・ウィンドウの考慮を含むことができる。

#### [0011]

別の態様においては、本発明は複数の限界幅セグメントを有する集積回路設計の画像を投影するための交互位相シフト・マスクを設計する方法に向けられ、この方法は、交互位相シフト・マスクの第1のマスク設計を、交互位相シフト領域を限界幅セグメントに置合わせすることによって作成するステップと、交互位相シフト領域を、それらが位置わせされる限界幅領域の少なくとも幾つかの端部を超えて、所定の製造可能設計ルールを満足するステップとを含む。本方法はまた、交互位相シフト・マスクの第2のマスク設計を、交互位相シフト領域を、それらが位置合わせされる限界幅セグメンに第2のマスク設計をでは、での支互位相シフト領域を延長せずに、限界幅セグメンにの当時であることによって、作成するステップを含む。次に、本方法は、所定の製造可化のでででは、所定の製造では、第2のマスク設計の設計構造体を識別するステップと、第2のマスク設計から導かれる第3のマスク設計を作成するステップとを含む。第3のマスク設計の対しにより、第1のマスク設計がある第3のマスク設計を作成するステップとを含む。第3のマスク設計の対しては、所定の製造可能ルールに違反する第2のマスク設計の設計構造体が、第1の製造可能設計ルールを満足するようになる。

### [0012]

50

10

20

30

所定の製造可能設計ルールは、最小の位相幅及び最小の位相・位相間隔を含むことができ、所定のリソグラフィ設計ルールはプロセス・ウィンドウの考慮を含むことができる。 交互位相シフト・マスク第2のマスク設計は、典型的には、最小位相幅及び最小位相・位相間隔を含む製造設計ルールの少なくとも1つに違反する。次に第3のマスク設計は、集積回路設計の画像を基板に転写するために用いられる。

#### [0013]

本発明のさらに別の態様は、複数の限界幅セグメントを有する集積回路設計レイアウトの画像を投影するためのフォトマスクを設計する方法に向けられ、この方法は、フォトマスクの第1のマスク設計を、サブ解像度アシスト構造体(SRAF)を限界幅セグメントに位置合わせすることによって、第1のマスク設計が所定の製造可能設計ルールを満足するように、作成するステップと、フォトマスクの第2のマスク設計を、サブ解像度アスト構造体を限界幅セグメントに位置合わせすることによって、第2のマスク設計が限界の領域において所定のリソグラフィ設計ルールを満足するように、作成マスク設計の設計構造体を識別するステップと、第2のマスク設計から導かれる第3のマスク設計の設計構造体が、第1のマスク設計からの設計構造体によって選択的に置き替えられて第3のマスク設計が所定の製造可能設計ルールを満足するようになる。

#### [0014]

所定の製造可能設計ルールは、SRAFのサイズ及び間隔を含むことができ、所定のリソグラフィ設計ルールはプロセス・ウィンドウの考慮を含むことができる。典型的には、第2のマスク設計は、SRAFのサイズ及び間隔を含む所定の製造設計ルールの少なくとも1つに違反する。次に第3のマスク設計は、集積回路設計の画像を基板に転写するために用いられる。

#### [0015]

本発明のさらに別の態様は、機械可読のプログラム記憶装置に向けられ、その装置は、 複数の限界幅セグメントを有する集積回路設計の画像を投影するためのマスクを設計する ための、前述のあらゆる方法ステップを実行するためのマシン実行可能な命令のプログラ ムを記憶する。

## 【発明を実施するための最良の形態】

#### [0016]

本発明の構造体は新規なものと考えられ、本発明の特徴的な要素は、詳細に添付の特許請求の範囲において記述される。図面は図解のためだけであって、一定の尺度で描かれてはいない。しかし、本発明自体は、操作の編成及び方法の両方について、以下で添付の図面に関連してなされる詳細な説明を参照することにより、最も良く理解することができる

本発明の好ましい実施形態を説明するにあたり、ここで図面の図1-図12を参照することになるが、図中、類似の数表示は本発明の類似の構造体を示す。

#### [0017]

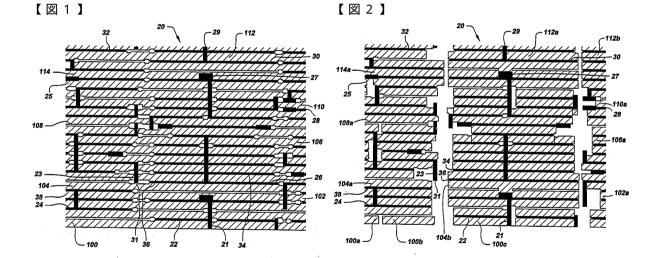

本発明の1つの好ましい実施形態においては、前述の特許文献1の教示に基づいて、初めにグローバルaltPSM設計が設計される。図1に示されるように、集積回路レイアウト20の限界幅セグメント、例えば偶数番号付けされたセグメント22-38として識別されるセグメントは、水平方向を向く本質的に平行な複数のセグメントを有する。ここで用いられる、限界セグメントという用語は、限界寸法、即ち、リソグラフィ・システムがレジスト層の適切な寸法制御によって作成することができる最小寸法より小さな寸法、を有するセグメント又はその部分を表す。図1にはまた、集積回路レイアウトの非限界セグメント、例えば奇数番号付けされたセグメント21-31として示されるセグメントがあり、これらは限界セグメントより広い幅を有する。限界セグメントの垂直方向における中心線間隔は、回路レイアウトの最小ピッチの整数倍であることが好ましい。最初の限界幅セグメントは、PSM設計のためだけであるが、集積回路レイアウトの周囲のあらゆる

10

20

30

40

10

20

30

40

50

境界(図示せず)を超えて延びることが好ましい。その後、交互位相シフト領域、例えば偶数番号付けされた領域100-114として識別される領域が、延長された限界幅セグメントの間に作成される。従って、交互位相シフト領域は、それらが位置合わせされる最初の限界幅セグメントの少なくとも幾つか、又はできれば全ての端部を越えて延びる。

### [0018]

本発明はまた、図1のグローバルaltPSM設計に加えて、概略のローカルaltPSM設計を作成することが好ましい。図2は、図1に示される集積回路レイアウトの同じ限界幅セグメントに関するローカルaltPSMのソリューションを示す。この方法においては、交互位相シフト領域は、最初の限界幅セグメントの両側、即ち、上下に作成される。この概略のローカルaltPSM設計は、所定のリソグラフィ設計ルール、例えば、ドーズ量及び焦点パラメータの許容範囲を与えるaltPSM形状に関するプロセス・ウィンドウのリソグラフィ要件、或いは、位相形状による限界レイアウト端部の連続的なカバレッジ、内側の位相端部から外側の限界端部までの最小距離(名目の位相幅)、又はバン端部を通り越す位相形状の最小延長などのリソグラフィ解像度要件、を満足する。しかし、これらの概略のローカルaltPSMの形状は、全ての製造可能制約、又は、最小の位相・位相間隔若しくは最小位相幅などの交互位相シフト設計パラメータに基づく交互位相シフト設計ルールに、必ずしも従うとは限らない。

#### [0019]

本発明の好ましい方法における次のステップは、一般に製造上の問題はないがOPC( 光学近接効果補正)最適化はされていないと考えられる図1のグローバルaltPSM設計と、OPC最適化はされているが、製造不可能である可能性があると考えられる図2のローカルaltPSM設計との間の差を計算又は識別することである。グローバル及びローカルなaltPSMレイアウトの間の差は、一般に減算と呼ばれる、論理「not」命令によって容易に引き出すことができる。図3に示されるように、クロス・ハッチングされた領域又は形状、例えば300・314として識別される偶数番号付けされた形状は、グローバル及びローカルなaltPSMソリューションの間の差を示す。

### [0020]

本発明によれば、OPC最適化とaltPSM製造可能性の間の最適のバランスに達す る課題は、図3のどの差形状を保存し、どれを除去するかを選択することに還元される。 具体的には、この実施例においては、目標は最終的にローカルaltPSM設計によく似 たレイアウトを生成することであるが、最適化の仕事は、製造可能違反、即ち、前述の又 は他の交互位相シフト設計パラメータに基づく交互位相シフト設計ルールの違反、を導入 することなしには、製造可能なグローバル・レイアウトから除去することができない差形 状を識別することに還元される。最小以下の位相幅又は位相間隔のような単純な1次の製 造可能違反は、ローカル位相シフト設計内で容易に識別することができる。それら基本的 な製造可能違反の近傍における差形状は、除去不能と標識又は明示される。これらの基本 的な製造可能性問題に加えて、以下で詳述するように作成された位相形状から製造ルール に適合するブロック・マスクを誘導できないというような2次的な問題が、差形状を除去 不能と標識するステップにおいて発生する可能性がある。最終的に、全ての製造可能性問 題は、製造可能性を確実にするために最終のレイアウトに保持されるべき差形状のサブセ ットをもたらす。これらは、図4の囲まれた領域350及び360の内部に示され、そこ ではローカル位相シフト設計における製造可能性問題に関連する差形状308及び310 が示されている。

## [0021]

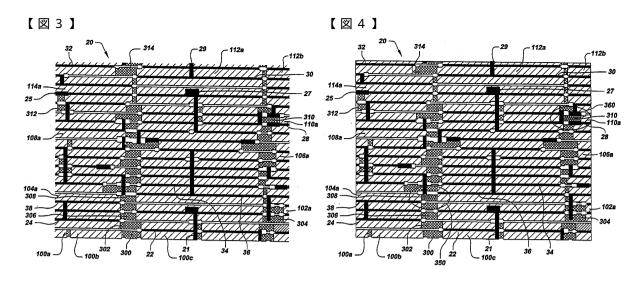

本明細書で説明される簡単化されたaltPSMレイアウト最適化法は、基本的な解像度向上技法(RET)の設計、この場合には位相形状、ばかりでなく、誘導されるRET形状、この場合にはブロック・パターン、に関する製造可能性問題を回避することを可能にする。概略のローカル位相形状から粗いブロック・マスク設計を導くことにより(本実施例においては、組み合わされた位相及び複数レイアウトを単に収縮させて最初の複数レイアウトを加えることにより)、最小間隔違反などの製造可能性問題を識別して違反の近

傍の差形状を除去不能と標識することによって回避することができる。図5は、差形状308の近傍における最終的なブロック・マスク設計の近似を描く。この導かれた近似は、差形状308の左上隅にある矢印400で示される間隔違反のような製造可能性問題を控えめに識別するのに十分に正確である。

#### [0022]

次に本方法による最適化された a 1 t P S M レイアウトが、除去不能と標識されていない(図 4)全ての差形状を最初のグローバル a 1 t P S M 設計(図 1)から除去することにより生成される。図 6 は、着色(カラーリング)前、即ち、位相割当ての前の、そして除去不能な差形状 3 0 8 及び 3 1 0 を含む、最終の a 1 t P S M レイアウトを示す。図 7 は、交互位相割当てを有する最終の a 1 t P S M レイアウトを示す。

#### [0023]

本発明の方法をRET準拠のレイアウト(即ち、ルールに適合するRETソリューションが存在することが分かっているレイアウト)に対して実施する場合、完全に製造可能である(即ち、製造可能ルール違反がなにもない)ことが分かっている1つのRETソリューションが生成され、プロセス・ウィンドウ又はOPC達成機能(即ち、RETレイアウト形状と特定のOPC機能性との好都合な位置合わせによるOPC後の良好な画像忠実度される。その後、二つのソリューションの間の差が、好ましくは小さな細片などの無意味な差を除去する何かのフィルタリングによって確定され、製造可能性問題に関連するそれな差を除去する何かのフィルタリングによって確定され、製造可能性問題に関連するそれの差形状は第2のソリューションにおいて識別される。次に最終の最適化されたRETレイアウトが、第2の、リソグラフィのために最適化されたRETレイアウトを、設計から除去される場合にRETレイアウトを製造不可能にすることになる差形状と組み合せることによって生成される。

#### [0024]

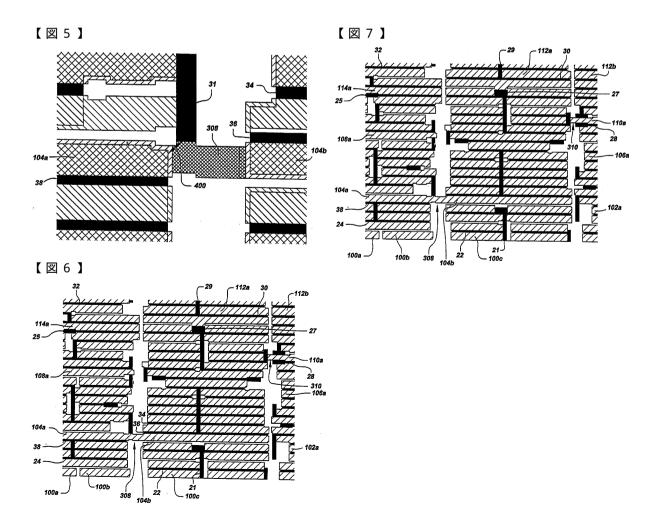

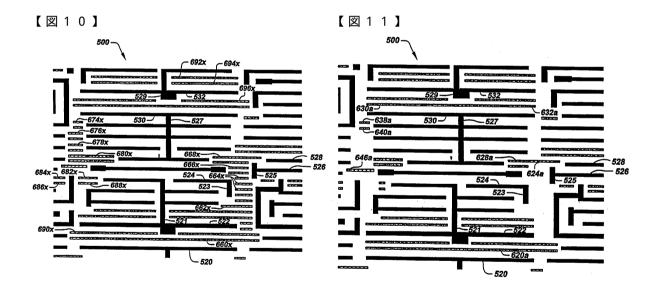

図1.図7に関連して説明された交互位相シフト領域は、限界幅セグメントのリソグラ フィ投影を補助するためにマスクに対して用いられる1つの型の構造体を表す。特に交互 位相シフト・マスク・リソグラフィに関して本明細書で説明されたRET最適化法は、様 々なレイアウト操作型RETに広く適用することができる。そのようなRETの1つの実 施例は、当技術分野においてスキャッタリング・バーとしても既知の、サブ解像度アシス ト構造体(SRAF)の使用であり、それをフォトマスク上で軸外(off-axis) 照射と組み合せて使用するときには、交互位相シフト・マスク・リソグラフィと同様の解 像度向上を達成することができる。図8-図11に示されるように、2つのSRAF設計 ソリューションが、実線で示される例示的なポリシリコン導電体レイアウト500に対し て導かれる。示される集積回路設計の導電体は限界セグメント、例えば偶数番号付けされ たセグメント520-532、及び非限界セグメント、例えば奇数番号付けされたセグメ ント521-529を含む。図2のローカルaltPSM設計に関連して論じられたのと 類似の方法を用いて、導電体レイアウトのセグメント、例えば偶数番号付けされたSRA F620-656、と共にフォトマスク上に作成されるべきローカルSRAFソリューシ ョンのセグメントが、レイアウトの一部分に、即ち、限界設計要素のすぐ近傍だけに生成 される。これらのSRAFは粗い又はありのままの最小のRET設計を示す。ローカルな ソリューションは、プロセス・ウィンドウの考慮などの所定のリソグラフィ設計基準を満 足するように、即ち、リソグラフィエ程のためのドーズ量及び焦点パラメータのより大き な許容範囲をもたらすように、ローカルに最適化され、その結果、許容範囲がより厳しく 寸法がより小さな限界構造体の解像度が向上される。描写された本実施例において、SR AFは全体の形状数及びデータ量の観点から最適化される。しかし、このローカルなSR AFソリューションは、小さ過ぎるSRAF又は間隔が狭過ぎるSRAFなどの製造可能 性問題に直面することが多い。図8に示されるように、所定の製造可能ルールによれば、 丸く囲まれた範囲702内のSRAF624は小さ過ぎ、丸く囲まれた範囲704内では SRAF630と632は接近し過ぎている。これら及び他の製造可能ルールは、従来の 光リソグラフィ製造基準によって決定することができる。これに反して、図9に示される 10

20

30

40

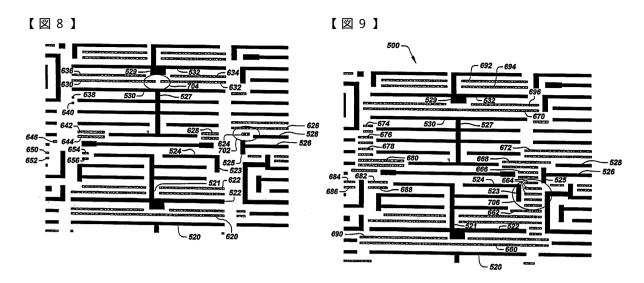

ように、グローバルSRAFのソリューションは、所定の製造可能ルールを満足するまさしく製造可能なソリューション、例えば偶数番号付けされたSRAF660-696、を生成する。しかし、図9の例証されたグローバル・ソリューションは、丸く囲まれた範囲706で示されるSRAF664のような過剰な数の付加的なマスク・パターンをマスク設計に負わせる。ローカル及びグローバルなソリューションの間の差を、図10中、斜め線でハッチングされたSRAF,例えば、添え字「x」で指示されるSRAF部分で示されるように識別すること、及び、簡単な製造可能性に基づく選択基準を適用することによって、有効なローカルSRAFソリューションと製造可能なグローバル・ソリューションとの間の最適の折衷結果を、ローカル及びグローバル・ソリューションの間の差をマスク設計のローカル・ソリューションに選択的に加えることによって見出すことができる。これは、図11において、例えば、添え字「a」で指示されたSRAFとして示されている

10

### [0025]

リソグラフィ投影に用いられるマスクを設計するための本発明の方法は、図12に示されるように、前述のプロセス・ステップ及び命令を組み入れたコンピュータ・プログラム又はソフトウェアにより、さもなければ従来のプログラム・コード内に実装することができ、電子設計自動化(EDA)ツール又はさもなければ従来のコンピュータ・システム900にストアすることができる。プログラム・コード、及び必要なあらゆる入力情報は、EDAツール内、又はコンピュータ上のプログラム記憶装置902内、例えば、半導体チップ、読み取り専用メモリ、ディスケット若しくはコンピュータ・ハード・ドライブなどの磁気媒体、又は、CD若しくはDVD ROMなどの光学媒体にストアすることができる。EDAツール又はコンピュータ・システムは、上述のようにデバイス内にストアされているプログラム・コードを読み取り実行するためのマイクロプロセッサ904を有する

20

#### [0026]

本発明は、特定の好ましい実施形態に関連して詳しく説明されたが、前述の説明を考慮すれば、多くの代替物、変更及び改変が当業者には明らかとなることは明白である。従って、添付の特許請求の範囲は、全てのそのような代替物、変更及び改変を本発明の真の範囲と精神の内に入るものとして包含することが意図されている。

[0027]

30

#### 産業上の利用可能性

本発明は、集積回路のリソグラフィによる製造に用いられるマスクの設計及び作成において、より具体的には、解像度向上技法(RET)により改良されたマスクの設計及び作成において有用である。

【図面の簡単な説明】

[0028]

【図1】グローバルaltPSM設計による、限界幅セグメントを有する集積回路レイアウトの平面図であり、交互位相シフト領域はそれらが位置合わせされる限界幅セグメントの端部を超えて延びている。

40

- 【図2】ローカルaltPSM設計による、図1の集積回路レイアウトの平面図であり、 交互位相シフト領域はそれらが位置合わせされる限界幅セグメントの端部を実質的に超え て延びていない。

- 【図3】図1と図2の交互位相シフト領域の間の差形状を示す、図1の集積回路レイアウトの平面図である。

- 【図4】製造可能性問題を示す、図3の差形状を示す平面図である。

- 【図5】間隔違反を示す図4の差形状の1つの拡大図である。

- 【図 6 】最終的な位相識別の割当て前の、除去不能と指示された全ての差形状と図 1 の交互位相シフト領域との組合せの平面図である。

- 【図7】最終的な位相識別の割当て後の、除去不能と指示された全ての差形状と図1の交 互位相シフト領域との組合せの平面図である。

10

【図8】ローカルな設計問題を満足する、限界幅セグメント及びサブ解像度アシスト構造体を有する集積回路レイアウトのためのフォトマスク設計の上面図である。

【図9】グローバルな製造可能設計ルールを満足する、限界幅セグメント及びサブ解像度アシスト構造体を有する図8の集積回路レイアウトのためのフォトマスク設計の上面図である。

【図10】図8のローカル・ソリューションと図9のグローバル・ソリューションとの間のサブ解像度アシスト構造体における差を示す平面図である。

【図11】図8のローカル・ソリューションのマスク設計に対する、ローカル及びグローバル・ソリューションの間のサブ解像度アシスト構造体の差の選択的な追加を示す平面図である。

【図12】本発明の電子設計自動化ツール、又は本発明の方法を実行するコードをストアするためのプログラム記憶装置の略図である。

【図12】

### フロントページの続き

(74)代理人 100086243

弁理士 坂口 博

(72)発明者 リーバーマン、ラーズ、ダブリュー

アメリカ合衆国 12570 ニューヨーク州 ポクァグ コーンウェル・ストリート 5

(72)発明者 ボーム、ザカリー

アメリカ合衆国 12525 ニューヨーク州 ガーディナー サウス・マウンテン・ロード 5

0 7

### 審査官 佐野 浩樹

(56)参考文献 特表2003-526110(JP,A)

特開2002-131882(JP,A)

米国特許第6832364(US,B2)

特表2007-536581(JP,A)

特表2004-520622(JP,A)

米国特許第6569583(US,B2)

特開昭63-102266(JP,A)

(58)調査した分野(Int.CI., DB名)

G03F 1/00- 1/16