### (19) **日本国特許庁(JP)**

# (12) 特 許 公 報(B2)

HO1L 27/04

(11)特許番号

特許第5301108号 (P5301108)

(45) 発行日 平成25年9月25日(2013.9.25)

(24) 登録日 平成25年6月28日 (2013.6.28)

(51) Int.Cl. F L

HO1 L 21/822 (2006.01) HO1 L 27/04 (2006.01)

HO1L 23/12 5O1P

HO1L 23/12 (2006.01)

請求項の数 4 (全 11 頁)

(21) 出願番号 特願2007-112336 (P2007-112336)

(22) 出願日 平成19年4月20日 (2007.4.20) (65) 公開番号 特開2008-270573 (P2008-270573A)

(43) 公開日 平成20年11月6日 (2008.11.6) 審査請求日 平成22年1月27日 (2010.1.27)

(73) 特許権者 300057230

C

セミコンダクター・コンポーネンツ・イン ダストリーズ・リミテッド・ライアビリテ

ィ・カンパニー

アメリカ合衆国 アリゾナ州 85008 フェニックス イースト・マクドウェル

ロード5005

|(74)代理人 100107906

弁理士 須藤 克彦

(72) 発明者 堀越 勝

群馬県邑楽郡大泉町坂田一丁目1番1号

三洋半導体株式会社内

|(72)発明者 内山 久嘉

群馬県邑楽郡大泉町坂田一丁目1番1号

三洋半導体株式会社内

最終頁に続く

(54) 【発明の名称】半導体装置

## (57)【特許請求の範囲】

## 【請求項1】

半導体基板と、

前記半導体基板の表面に形成された半導体集積回路と、

前記半導体集積回路と接続されたパッド電極と、

前記半導体基板の裏面に形成された容量電極と、

前記半導体基板の側面上及び前記容量電極上に形成された絶縁膜と、

前記容量電極と重畳して前記絶縁膜上に形成され、且つ前記パッド電極と接続された配線層とを備え、

前記容量電極,前記絶縁膜,前記配線層で容量が形成されており、

前記容量電極は、前記半導体基板の裏面上から前記半導体基板の側面上に延在し、

前記絶縁膜は、前記半導体基板の側面上の前記容量電極上に形成され、

前記配線層は、前記半導体基板の側面上の前記絶縁膜上に形成されていることを特徴とする半導体装置。

## 【請求項2】

前記半導体基板は、前記半導体基板を貫通するビアホールを有し、

前記半導体基板の側面は、前記ビアホールの内壁面を含むことを特徴とする請求項 1 に記載の半導体装置。

### 【請求項3】

前記半導体基板の裏面上に、前記パッド電極と前記配線層を介して電気的に接続された第

20

20

30

40

50

1の導電端子と、前記容量電極と接触した第2の導電端子とを備えることを特徴とする請求項1又は2に記載の半導体装置。

#### 【請求項4】

前記半導体基板上に支持体が貼り合わされていることを特徴とする請求項1乃至請求項<u>3</u>のいずれかに記載の半導体装置。

#### 【発明の詳細な説明】

#### 【技術分野】

## [0001]

本発明は、容量素子を備えた半導体装置に関するものである。

#### 【背景技術】

[00002]

電磁ノイズによって電圧レベルが変動する影響を低減し、半導体チップの誤動作を防止する観点から、当該半導体チップの端子(電源端子や接地端子)にバイパスコンデンサと呼ばれる容量素子を設けることが従来から行われている。

#### [0003]

例えば、以下の特許文献1では、半導体チップと、チップコンデンサと呼ばれる外付けの容量素子とを同一の基板上に実装して全体として一つのチップ状にパッケージされた半 導体装置が開示されている。

## [0004]

また、以下の特許文献 2 では、半導体基板上の多層配線層とその間の層間絶縁膜を利用して、バイパスコンデンサとして機能する容量素子を形成した半導体装置が開示されている。

### [0005]

本発明に関連した技術は、例えば以下の特許文献に記載されている。

【特許文献1】特開平05-021698号公報

【特許文献2】特開2000-349238号公報

【発明の開示】

【発明が解決しようとする課題】

## [0006]

しかしながら、上記特許文献1のように、外付けの容量素子を用いる構成では、大きな静電容量を有する容量素子が得られる一方で、当該容量素子を実装するためのスペースが基板上に必要になる。そのため、装置全体としての小型化を図ることが困難になる問題があった。

## [0007]

また、近年の半導体チップの動作は高速化しているため、トランジスタの高速なスイッチング動作によって高周波数(数百MHz以上の周波数)の電磁ノイズが増加し、動作特性が劣化する傾向にある。そのため、当該電磁ノイズを効果的に除去できる技術が要望されている。

### [0008]

電磁ノイズの影響の低減を図る方法の一つとして、半導体チップと容量素子とを出来る限り近接させ、両者を接続する配線(電源配線や接地配線)の低インピーダンス化,低インダクタンス化を図ることが挙げられる。しかしながら、これらの配線はレイアウト設計上長く引き回されることもあるため、半導体チップと容量素子とがそれぞれ別個の部品であると、両者の近接にも限界がある。

## [0009]

以上説明したように、外付けの容量素子を備えた構成では、半導体装置の小型化と電磁 ノイズの影響の更なる低減化の両者を同時に実現することが困難であるという問題があっ た。

## [0010]

一方、上記特許文献2のように、同一半導体装置内に容量素子が形成された従来の構成

では、外付けの容量素子を用いた場合に比べて配線の,低インピーダンス化,低インダクタンス化を図ることは可能であるが、高周波の電磁ノイズを効果的に除去できる程度の充分な静電容量を得るには大面積が必要になってしまう。

#### [0011]

そのため、同一半導体基板上に容量素子以外の他の機能素子(例えばトランジスタ等で構成されたドライバ回路やロジック回路や、それらと接続された配線等)を形成する関係から、半導体装置の小型化が図れないという問題があった。

## [0012]

そこで本発明は、同一半導体装置内に容量素子を備えて装置全体の小型化を図るとともに、従来に比べて大きな静電容量の容量素子を備える半導体装置を提供することを主たる目的とし、更には電磁ノイズの影響を低減できる半導体装置を提供することを目的とする

# 10

#### 【課題を解決するための手段】

## [0013]

本発明は上記課題に鑑みてなされたものであり、その主な特徴は以下のとおりである。すなわち、本発明の半導体装置は、半導体基板と、前記半導体基板の表面に形成された半導体集積回路と、前記半導体基板の裏面に形成された容量電極と、前記半導体基板の側面上及び前記容量電極上に形成された絶縁膜と、前記容量電極と重畳して前記絶縁膜上に形成され、且つ前記パッド電極と接続された配線層とを備え、前記容量電極,前記絶縁膜,前記配線層で容量が形成されており、前記容量電極は、前記半導体基板の裏面上から前記半導体基板の側面上に延在し、前記絶縁膜は、前記半導体基板の側面上の前記絶縁膜上に形成され、前記配線層は、前記半導体基板の側面上の前記絶縁膜上に形成されていることを特徴とする。

#### 20

## 【発明の効果】

#### [0014]

本発明では、半導体基板の一方の面上に半導体集積回路を形成し、他方の面上に容量を形成しているため、従来よりも大きな静電容量の容量を備え、なお且つ小型の半導体装置を実現することができる。

## 【発明を実施するための最良の形態】

## [0015]

30

次に、本発明の第1の実施形態について図面を参照しながら説明する。図1乃至図9は、それぞれ製造工程順に示した断面図または平面図である。なお、以下に説明する製造工程は、ウェハ状の半導体基板を用いて行われるものであり、所定のダイシングラインを境界として多数の半導体装置がマトリクス状に形成されることになるが、便宜上その一つの半導体装置が形成される工程を説明する。

#### [0016]

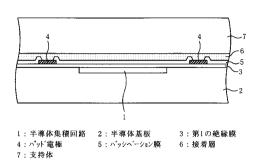

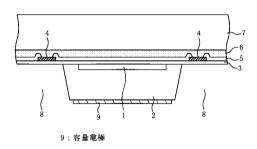

まず、図1に示すように、その表面に半導体集積回路1(例えば、CCDセンサー,CMOSセンサー,照度センサー等の受光素子や発光素子、トランジスタ等の半導体素子が集積されて構成されたドライバ回路やロジック回路、それらと接続された配線等)が形成されたシリコン(Si)等から成る半導体基板2を準備する。半導体基板2は、例えば300μm~700μm程度の厚さになっている。そして、半導体基板2の表面に第1の絶縁膜3(例えば、熱酸化法やCVD法等によって形成されたシリコン酸化膜)を例えば2μmの膜厚に形成する。

# 40

## [0017]

次に、スパッタリング法やメッキ法、その他の成膜方法によりアルミニウム(A1)やアルミニウム合金や銅(Cu)等の金属層を形成し、その後不図示のレジスト層をマスクとして当該金属層をエッチングし、第1の絶縁膜3上にパッド電極4を例えば1µmの膜厚に形成する。パッド電極4は、半導体集積回路1やその周辺素子と不図示の配線を介して電気的に接続された外部接続用の電極である。そして、後述する導電端子13a、13b,13cからパッド電極4を介して電源電圧や接地電圧あるいは種々の信号が半導体集

20

30

40

50

積回路 1 や半導体基板 2 等に供給される。なお、図 1 では半導体集積回路 1 の両側にパッド電極 4 が配置されているが、その位置に限定はなく、半導体集積回路 1 上に配置することもできる。

#### [0018]

次に、半導体基板 2 の表面にパッド電極 4 の一部上あるいは全部を被覆するパッシベーション膜 5 (例えば、CVD法により形成されたシリコン窒化膜)を形成する。図 1 では、パッド電極 4 の一部上を被覆するようにしてパッシベーション膜 5 が形成されている。

## [0019]

次に、パッド電極 4 を含む半導体基板 2 の表面上に、エポキシ樹脂,ポリイミド(例えば感光性ポリイミド),レジスト,アクリル等の接着層 6 を介して支持体 7 を貼り合せる。なお、半導体集積回路 1 が受光素子や発光素子を含む場合、接着層 6 は半導体集積回路 1 から放射される光、あるいは半導体集積回路 1 に入射される光の通り道になるため、透明であって光を透過させる性状の良好な材料から成ることが好ましい。

## [0020]

支持体 7 は、例えばフィルム状の保護テープでもよいし、ガラスや石英,セラミック,金属等の剛性の基板であってもよいし、樹脂から成るものでもよい。支持体 7 は、半導体基板 2 を支持すると共にその素子表面を保護する機能を有するものである。なお、半導体集積回路 1 が受光素子や発光素子を含む場合には、支持体 7 は透明もしくは半透明の材料から成り、光を透過させる性状を有するものである。

### [0021]

次に、半導体基板2の裏面に対して裏面研削装置(グラインダー)を用いてバックグラインドを行い、半導体基板2の厚さを所定の厚さ(例えば100μm程度)に薄くする。なお、当該研削工程はエッチング処理でもよいし、グラインダーとエッチング処理の併用でもよい。なお、最終製品の用途や仕様,準備した半導体基板2の当初の厚みによっては、当該研削工程を行う必要がない場合もある。

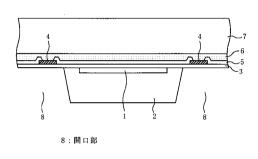

### [0022]

次に、図2に示すように、半導体基板2のうちパッド電極4に対応する所定の領域のみを、半導体基板2の裏面側から選択的にエッチングし、第1の絶縁膜3を一部露出させる。以下、この露出部分を開口部8とする。

## [0023]

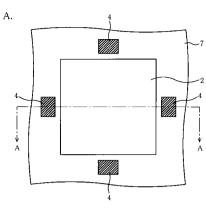

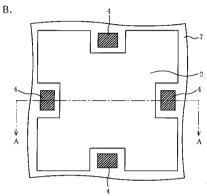

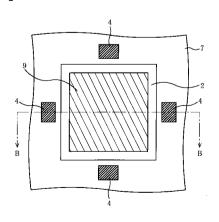

当該半導体基板2の選択的なエッチングについて、図3A,Bを参照して説明する。図3A,Bは、半導体基板2側から見た概略平面図であり、図2は図3A,BのA-A線に沿った断面図に対応するものである。

#### [0024]

図3 Aに示すように、半導体基板2を支持体7の幅よりも狭い、略長方形の形状にエッチングすることもできる。また、図3 Bに示すように、パッド電極4 が形成された領域のみをエッチングすることで、半導体基板2の外周が凹凸状になるように構成することもできる。後者の方が、半導体基板2と支持体7の重畳する面積が大きく、支持体7の外周近くまで半導体基板2が残る。そのため、半導体基板2に対する支持体7の支持強度を向上させる観点からは、後者の構成が好ましい。また、後者の構成によれば、半導体基板2と支持体7の熱膨張率の差異による支持体7の反りが防止できるため、半導体装置のクラックや剥離が防止できる。なお、図3 A , B で示した平面形状とは別の形状に半導体基板2をデザインすることも可能である。なお、以後は半導体基板2を図3 A で示したようにエッチングした場合の製造工程を説明する。

#### [0025]

また、本実施形態では半導体基板2の横幅が表面側に行くほど広がるように、半導体基板2の側壁が斜めにエッチングされているが、半導体基板2の幅が一定であり、その側壁が支持体7の主面に対して垂直となるようにエッチングすることもできる。

#### [0026]

次に、CVD法、スパッタリング法、その他の成膜方法により、半導体基板2の裏面上

20

30

40

50

に、図4及び図5に示すように例えばアルミニウムや金,銀等の金属材料から成る容量電極9を例えば約1~2μmの膜厚で形成する。なお、前記半導体基板2のバックグラインド後に容量電極9を形成し、その後容量電極9と半導体基板2の両者を選択的にエッチングすることで開口部8を形成してもよい。容量電極9は、後述するように容量16の一方の電極を構成し、実際の使用時においては半導体基板2と同じ電位(通常は接地電位)に固定される。なお、可能な限り大きな静電容量の容量素子を得るべく、容量電極9の面積は広いことが好ましい。なお、図5は図4の半導体基板2側から見た平面図の概略であり、図4は図5のB-B線に沿った断面図である。

### [0027]

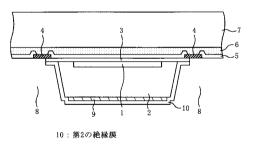

次に、開口部8内及び容量電極9を含む半導体基板2の側面及び裏面上に第2の絶縁膜10を形成する。この第2の絶縁膜10は、例えばプラズマCVD法によって形成されたシリコン酸化膜やシリコン窒化膜である。

## [0028]

次に、不図示のホトレジスト層をマスクとして、図6に示すように、第1の絶縁膜3及び第2の絶縁膜10の選択的なエッチングを行う。このエッチングにより、パッド電極4の一部上からダイシングラインに至る領域にかけて形成された第1の絶縁膜3及び第2の絶縁膜10が選択的に除去され、開口部8の底部においてパッド電極4の少なくとも一部が露出される。

#### [0029]

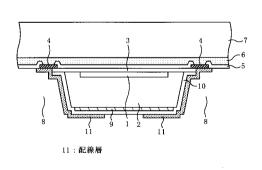

次に、スパッタリング法やメッキ法、その他の成膜方法により、配線層11となるアルミニウム(A1)や銅(Cu)等の金属層を形成する。その後、不図示のホトレジスト層をマスクとして当該金属層をエッチングし、図7及び図9に示すように、パッド電極4の一部上及び第2の絶縁膜10上に配線層11を例えば1μmの膜厚で形成する。配線層11は、パッド電極4及び第2の絶縁膜10を被覆して半導体基板2の側面及び裏面に沿って形成されており、半導体基板2の主面の垂直方向から見た場合には、図9に示すように容量電極9と重畳している。

#### [0030]

なお、容量電極 9 及び配線層 1 1 は同一材料 (例えばアルミニウム)及び同一の方法 (例えばスパッタリング法)によって形成することが好ましい。製造工程が単純化され、製造コストを低く抑えることができるという利点があるからである。

#### [0031]

次に、配線層11を被覆する不図示の電極接続層(例えば、ニッケル層と金層の積層)を形成する。電極接続層を形成するのは、アルミニウム等から成る配線層11と、ハンダ等から成る導電端子13a,13b,13cは接合しにくいという理由や、導電端子13a,13b,13cの材料が配線層11側に流入してくることを防止するという理由による。なお、保護層12の形成後に当該電極接続層を形成することも可能である。次に、図8に示すように、半導体基板2の側面及び裏面上にソルダーレジストのようなレジスト材料から成る保護層12を形成する。

## [0032]

次に、保護層12の所定領域(導電端子形成予定領域)を開口させ、当該開口内で露出させた電極接続層上に導電材料(例えばハンダ)をスクリーン印刷し、この導電材料を熱処理でリフローさせることで、図8及び図9に示すように、ボール状の導電端子13a,13b,13cを形成する。導電端子13aは電源電圧供給用の端子であり、導電端子13bは接地電圧供給用の端子であり、導電端子13cは種々の入出力信号に関わる端子である。なお、導電端子13a,13b,13cの形成方法は上記に限定されることはなく、電解メッキ法や、ディスペンサを用いてハンダ等を所定領域に塗布するいわゆるディスペンス法(塗布法)等で形成することもできる。このようにして、パッド電極4は配線層11を介して導電端子13a,13b,13cと電気的に接続される。

### [0033]

次に、多数の半導体装置の境界であるダイシングラインDLに沿って保護層12や支持

体 7 等を切断し、個々の半導体装置 1 5 に分割する。個々の半導体装置に分割する方法としては、ダイシング法,エッチング法,レーザーカット法等がある。なお、支持体 7 は、半導体基板 2 と貼り合わせたままでもよく、あるいは個々の半導体装置 1 5 に分割する前後で剥離させてもよい。

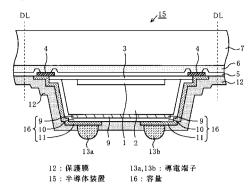

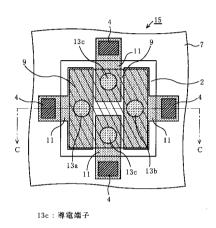

## [0034]

以上の工程により、チップサイズパッケージ型の半導体装置 1 5 が完成する。半導体装置 1 5 は、導電端子 1 3 a , 1 3 b , 1 3 c を介してプリント基板等に実装される。なお、図 9 は、半導体装置 1 5 を半導体基板 2 側から見た平面図の概略であり、図 8 は図 9 の C - C 線に沿った断面図に相当する。

## [0035]

第1の実施形態に係る半導体装置15では、半導体基板2の裏面上に容量電極9、第2の絶縁膜10、配線層11がこの順に積層しているため、これらで容量16が形成されることになる。従って例えば、導電端子13aを電源電圧VDDの供給端子と接続し、導電端子13bを接地電圧GNDの供給端子と接続すると、導電端子13a,13b,13cから内部に浸入する電磁ノイズや,トランジスタのスイッチング動作等によって半導体集積回路1の内部から生じる電磁ノイズは容量16の充放電作用によって除去され、半導体集積回路1の誤動作が防止される。

#### [0036]

この容量 1 6 の静電容量は、容量電極 9 と配線層 1 1 の重畳する面積及び第 2 の絶縁膜 1 0 (誘電体)の誘電率に比例し、第 2 の絶縁膜 1 0 の厚さに反比例するため、各パラメータを変える事によって所望の静電容量を得ることが可能である。

#### [ 0 0 3 7 ]

また、容量16は半導体基板2の裏面上に形成されているため、当該容量16を設けたとしても半導体基板2の表面上のレイアウトを一切変更する必要はなく、半導体装置が大型化することもない。また、半導体装置15の裏面のほぼ全面を容量16として用いることが可能であるため、静電容量を大きくすることが容易である。そのため、本実施形態の構成によれば、半導体装置の小型化と容量素子の大容量化を同時に実現することができる

## [0038]

また、容量16と半導体集積回路1とは同一半導体チップ内に形成されており、容量16と半導体集積回路1との間の配線は外付けの容量素子を用いた場合に比べて短く、低インピーダンス化,低インダクタンス化が図られているため、電磁ノイズの除去に優れた効果を有している。具体的には例えば、0.01μFの静電容量を持つ外付けの容量素子を実装させたものと同程度の電磁ノイズの除去の効果を、100pF~500pF程度の静電容量を持つ容量16を備えることで実現できた。このように、外付けされる一般的な容量素子と比較すると容量16の静電容量は小さいが、同一半導体チップ内であって半導体集積回路1に極めて近く容量16が配置されるため、電磁ノイズの除去の効果を向上させることができた。従って、容量16を備える構成によれば、トランジスタの高速なスイッチング動作が必要とされる装置等であって、高周波数(数百MHz以上の周波数)の電磁ノイズが生じ易い装置にも対応することが可能である。

## [0039]

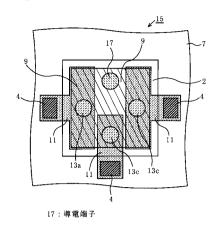

なお、図8及び図9では、導電端子13bから配線層11及びパッド電極4を介して半導体基板2及び容量電極9に所定の電圧(通常は接地電圧)を供給する構成になっていたが、図10に示すように、半導体基板2の裏面上に容量電極9と直接接続される導電端子17を形成し、導電端子17から容量電極9及び半導体基板2に所定の電圧を直接供給する構成にしてもよい。かかる構成によれば、導電端子17と容量電極9とが接触しているため、導電端子17から入ってくる電磁ノイズの影響を低減させることができるメリットがある。導電端子17は、保護層12に容量電極9に至る開口部を形成し、上記導電端子13a,13b,13cの形成と同様の工程(スクリーン印刷法やメッキ法等)で形成することができる。

10

20

30

20

30

40

50

#### [0040]

次に、本発明の第2の実施形態について図面を参照しながら説明する。なお、第1の実施形態と同様の構成については、同一符号を示してその説明を省略する。

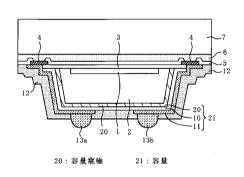

#### [0041]

第1の実施形態における容量電極9は、半導体基板2の裏面上にのみ形成されていた。これに対して第2の実施形態では、図11に示すように、半導体基板2の側面及び裏面の全体が容量電極20で被覆され、容量電極20,第2の絶縁膜10及び配線層11で容量21が形成されている。かかる構成によれば、半導体基板2の裏面上だけでなく側面側で形成された面積の分、容量21の静電容量を大きくすることができる。そして、電磁ノイズの除去の効果を第1の実施形態に係る構成に比べて更に向上させることができる。

## [0042]

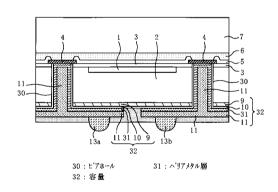

次に、本発明の第3の実施形態について図面を参照しながら説明する。なお、上記実施形態と同様の構成については同一符号を示してその説明を省略するか簡略する。

#### [0043]

第3の実施形態に係る半導体装置では、図12に示すように、半導体基板2の裏面からパッド電極4に至るビアホール30が形成され、当該ビアホール30内及び半導体基板2の裏面上にはバリアメタル層31が形成され、当該バリアメタル層31上にアルミニウムや銅等の金属からなる配線層11が形成されている。バリアメタル層31は、例えばチタン(Ti)層,チタンナイトライド(TiN)層,タンタル(Ta)層,タンタルナイトライド(TaN),チタンタングステン(TiW)層等の金属材料から成り、ビアホール30の底部(半導体基板2の表面に近い部分)でパッド電極4と接続されている。

#### [0044]

そして、半導体基板2の裏面と第2の絶縁膜10の間には、半導体基板2の裏面と接触した容量電極9が形成され、容量電極9,第2の絶縁膜10,バリアメタル層31,配線層11とから成る容量32が形成されている。このように、いわゆる貫通電極型の半導体装置に本発明を適用して容量32を形成することも可能である。

#### [0045]

当該貫通電極型の半導体装置は例えば、半導体集積回路1及び第1の絶縁膜3を介してパッド電極4が形成された半導体基板2を準備し、パッド電極4に対応する位置に半導体基板2を貫通するビアホール30を形成する工程と、半導体基板2の裏面上に容量電極9を形成する工程と、当該ビアホール30の内壁及び半導体基板2の裏面を被覆する第2の絶縁膜10を形成する工程と、ビアホール30底部の第2の絶縁膜10を除去する工程と、その後ビアホール30内にバリアメタル層31を形成する工程と、ビアホール30内及び半導体基板2の裏面上に例えば電解メッキ法などでアルミニウムや銅等の金属から成る配線層11を形成する工程と、保護層12及び導電端子13a,13bを形成する工程を経て製造される。なお、上記工程は本実施形態に係る貫通電極型の半導体装置の製造工程の一例の概略を説明するものであって、その製造工程は限定されず、例えばビアホール30を形成する前に容量電極9を形成することもできる。

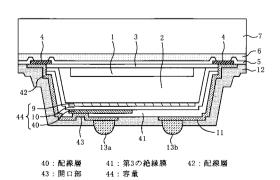

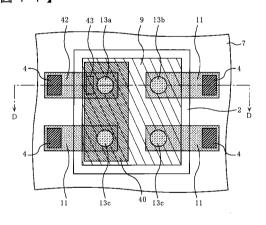

#### [0046]

次に、本発明の第4の実施形態について図13及び図14を参照しながら説明する。図14は第4の実施形態に係る半導体装置を半導体基板2側から見た平面図の概略であり、図13は図14のD-D線に沿った断面図に相当する。なお、上記実施形態と同様の構成については、同一符号を示してその説明を省略する。

## [0047]

第4の実施形態に係る半導体装置は、半導体基板2の裏面上において第2の絶縁膜10上に配線層40が、容量電極9と重畳するようにして形成されている。また、配線層40及び第2の絶縁膜10を被覆するようにしてシリコン酸化膜やシリコン窒化膜等から成る第3の絶縁膜41が形成され、第3の絶縁膜41上にはパッド電極4と接続された配線層42,11が半導体基板2の側面及び裏面に沿って形成されている。第3の絶縁膜41の一部には、配線層40に至る開口部43が形成されており、当該開口部43を介して配線

層40と配線層42とが接続されている。

### [0048]

第4の実施形態に係る半導体装置では、半導体基板2の裏面上に容量電極9、第2の絶縁膜10、配線層40がこの順に積層しているため、これらで容量44が形成されることになる。従って例えば、導電端子13aを電源電圧VDDの供給端子と接続し、導電端子13bを接地電圧GNDの供給端子と接続すると、導電端子13a,13b,13cから内部に浸入する電磁ノイズや,トランジスタのスイッチング動作等によって半導体集積回路1の内部から生じる電磁ノイズは容量44の充放電作用によって除去され、半導体集積回路1の誤動作が防止される。このように、半導体基板2の裏面上の容量の構成には様々なバリエーションが考えられる。

[0049]

なお、本発明は上記実施形態に限定されることはなく、その要旨を逸脱しない範囲で変更が可能であることは言うまでもない。例えば、上記実施形態では、ボール状の導電端子を有する B G A (Ball Grid Array)型の半導体装置について説明したが、本発明は L G A (Land Grid Array)型や、その他の C S P (Chip Size Package)型の半導体装置に適用するものであっても構わない。本発明は、容量素子を有する半導体装置として広く適用できるものである。

#### 【図面の簡単な説明】

[0050]

【図1】本発明の第1の実施形態に係る半導体装置の製造方法を説明する断面図である。

【図2】本発明の第1の実施形態に係る半導体装置の製造方法を説明する断面図である。

【図3】本発明の第1の実施形態に係る半導体装置の製造方法を説明する平面図である。

【図4】本発明の第1の実施形態に係る半導体装置の製造方法を説明する断面図である。

【図5】本発明の第1の実施形態に係る半導体装置の製造方法を説明する平面図である。

【図6】本発明の第1の実施形態に係る半導体装置の製造方法を説明する断面図である。

【図7】本発明の第1の実施形態に係る半導体装置の製造方法を説明する断面図である。

【図8】本発明の第1の実施形態に係る半導体装置の製造方法を説明する断面図である。

【図9】本発明の第1の実施形態に係る半導体装置の製造方法を説明する平面図である。

【図10】本発明の第1の実施形態に係る半導体装置の変更例を説明する平面図である。

【図11】本発明の第2の実施形態に係る半導体装置を説明する断面図である。

【図12】本発明の第3の実施形態に係る半導体装置を説明する断面図である。

【図13】本発明の第4の実施形態に係る半導体装置を説明する断面図である。

【図14】本発明の第4の実施形態に係る半導体装置を説明する平面図である。

## 【符号の説明】

[0051]

1 半導体集積回路 2 半導体基板 3 第1の絶縁膜 4 パッド電極

5 パッシベーション膜 6 接着層 7 支持体 8 開口部

9 容量電極 10 第2の絶縁膜 11 配線層 12 保護膜

13a,13b,13c 導電端子 15 半導体装置 16 容量

17 導電端子 20 容量電極 21 容量 30 ビアホール

3 1 バリアメタル層 3 2 容量 4 0 配線層 4 1 第 3 の 絶縁膜

4 2 配線層 4 3 開口部 4 4 容量 DL ダイシングライン

10

20

30

## 【図1】

## 【図2】

## 【図3】

【図4】

【図6】

【図5】

【図7】

## 【図8】

# 【図9】

【図12】

# 【図13】

# 【図10】

【図11】

【図14】

### フロントページの続き

(72)発明者 野間 崇

群馬県邑楽郡大泉町坂田一丁目1番1号 三洋半導体株式会社内

(72)発明者 関 嘉則

群馬県邑楽郡大泉町坂田一丁目1番1号 三洋半導体株式会社内

(72)発明者 山田 紘士

群馬県邑楽郡大泉町坂田一丁目1番1号 三洋半導体株式会社内

(72)発明者 石部 眞三

群馬県邑楽郡大泉町坂田一丁目1番1号 三洋半導体株式会社内

(72)発明者 篠木 裕之

群馬県邑楽郡大泉町坂田一丁目1番1号 三洋半導体株式会社内

## 審査官 今井 聖和

(56)参考文献 特開平01-105568(JP,A)

特開平03-227046(JP,A)

特開平07-106515(JP,A)

国際公開第2005/022631(WO,A1)

特開2006-253631(JP,A)

(58)調査した分野(Int.CI., DB名)

H01L 21/822

H01L 23/12

H01L 27/04

H01L 21/3205

H01L 21/768

H01L 23/522