(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第6607369号

(P6607369)

(45) 発行日 令和1年11月20日(2019.11.20)

(24) 登録日 令和1年11月1日(2019.11.1)

(51) Int.Cl.

F 1

G 1 O H 7/00 (2006.01)

G 1 O H 1/00 (2006.01)G 1 O H 7/00

G 1 O H 1/00

C

請求項の数 11 (全 15 頁)

(21) 出願番号 特願2015-59116 (P2015-59116)

(22) 出願日 平成27年3月23日 (2015.3.23)

(65) 公開番号 特開2016-177226 (P2016-177226A)

(43) 公開日 平成28年10月6日 (2016.10.6)

審査請求日 平成30年3月20日 (2018.3.20)

(73) 特許権者 000001443

カシオ計算機株式会社

東京都渋谷区本町1丁目6番2号

(74) 代理人 100096699

弁理士 鹿嶋 英實

(72) 発明者 坂田 吾朗

東京都羽村市栄町3丁目2番1号

カシオ計算機株式会

社 羽村技術センター内

審査官 大野 弘

(56) 参考文献 特開2007-219942 (JP, A )

最終頁に続く

(54) 【発明の名称】信号処理装置、信号処理方法、プログラムおよび電子楽器

## (57) 【特許請求の範囲】

## 【請求項1】

各サンプリング周期において順番に処理すべき複数のデータが離散的なアドレスの順番で記憶された第1のメモリ内から、複数サンプリング周期分のデータであって、前記第1のメモリ内の連続する複数のアドレスに記憶されている複数のデータをまとめて読み出すとともに、前記読み出された前記複数サンプリング周期分のデータを第2のメモリに書き込む第1のメモリコントローラと、

前記第2のメモリに書き込まれている前記複数サンプリング周期分のデータを、各サンプリング周期において処理すべき順番で処理する処理部と、

を備えた信号処理装置。

10

## 【請求項2】

前記第1のメモリコントローラは、前記処理部による前記複数サンプリング周期分のデータに対する処理を開始する前に、前記複数サンプリング周期分のデータをまとめて読み出すとともに、前記読み出された前記複数サンプリング周期分のデータを第2のメモリに書き込み、

前記処理部による前記複数サンプリング周期分のデータに対する処理が終了した後に、前記第2のメモリ内の前記処理された複数サンプル周期分のデータを読み出すとともに、前記読み出されたデータを前記第1のメモリ内の元のアドレスに書き込む第2のメモリコントローラを更に備える、

請求項1に記載の信号処理装置。

20

**【請求項 3】**

前記処理部は、各サンプリング周期において、前記第1のメモリ内の離散的なアドレスの順番で記憶されている複数のデータを離散的なアドレスの順番に処理することで遅延処理を実行する、請求項1または2に記載の信号処理装置。

**【請求項 4】**

前記第1のメモリには、各サンプリング周期において順番に処理すべき複数のデータが離散的なアドレスの順番で記憶されており、かつ、各サンプリング周期に対応するデータが他のサンプリング周期に対応するデータに対してシフトされたアドレスに記憶されており、

前記処理部は、前記第1のメモリに記憶されたデータのアドレスを、サンプリング周期でシフトしながら、各サンプリング周期に対応して離散的に記憶されている複数のデータに対する読み込み及び書き込みを行うことで、各サンプリング周期に対応する遅延処理を実行する、請求項1乃至3のいずれか一項に記載の信号処理装置。 10

**【請求項 5】**

前記第1のメモリは、リングバッファ形状に構成され、複数サンプリング周期それぞれに対応する複数のデータが記憶されている、請求項1乃至4のいずれか一項に記載の信号処理装置。

**【請求項 6】**

前記第2のメモリは、前記複数サンプリング周期分のデータを、サンプリング周期毎に分割して記憶する複数のページエリアを備えた、請求項1乃至5のいずれか一項に記載の信号処理装置。 20

**【請求項 7】**

前記処理部は、サンプリング周期毎に、前記第2のメモリ内の前記サンプリング周期に対応するページエリアにあるデータを読み出して処理し、前記処理されたデータを前記読み出したページエリアに書き込む、請求項6に記載の信号処理装置。

**【請求項 8】**

前記信号処理装置は、前記第1のメモリを外付けとし、前記第2のメモリを内蔵した請求項1乃至7に記載の信号処理装置。

**【請求項 9】**

演奏データを入力する演奏操作子と、

前記第1のメモリおよび前記第2のメモリと、

前記演奏データに応じて楽音を形成する、前記請求項1乃至8のいずれかに記載の信号処理装置と、

を備える電子楽器。 30

**【請求項 10】**

装置が、

各サンプリング周期において順番に処理すべき複数のデータが離散的なアドレスの順番で記憶された第1のメモリ内から、複数サンプリング周期分のデータであって、前記第1のメモリ内の連続する複数のアドレスに記憶されている複数のデータをまとめて読み出すとともに、前記読み出された前記複数サンプリング周期分のデータを第2のメモリに書き込み。 40

前記第2のメモリに書き込まれている前記複数サンプリング周期分のデータを、各サンプリング周期において処理すべき順番で処理する、信号処理方法。

**【請求項 11】**

コンピュータに、

各サンプリング周期において順番に処理すべき複数のデータが離散的なアドレスの順番で記憶された第1のメモリ内から、複数サンプリング周期分のデータであって、前記第1のメモリ内の連続する複数のアドレスに記憶されている複数のデータをまとめて読み出すとともに、前記読み出された前記複数サンプリング周期分のデータを第2のメモリに書き込むステップと、 50

前記第2のメモリに書き込まれている前記複数サンプリング周期分のデータを、各サンプリング周期において処理すべき順番で処理するステップと、

を実行させるプログラム。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、音源に用いて好適な信号処理装置、信号処理方法、プログラムおよび電子楽器に関する。 10

【背景技術】

【0002】

電子楽器では、音源にDSP（デジタル・シグナル・プロセッサ）と呼ばれる信号処理装置を備えることが多い。DSP（信号処理装置）は、外部メモリに記憶される波形データを所定のサンプリング周期毎に順次読み出し、読み出した波形データについて、遅延フィードバック演算やフィルタ演算を施して楽音波形を形成したり、その形成した楽音波形にリバーブ等のエフェクト（効果音）を付与するよう構成されている。

【0003】

この種の信号処理装置では、外部メモリへのアクセスタイムが内部メモリのそれより遅くなるのが一般的である。したがって、頻繁に外部メモリにアクセスしてデータを読み出し／書き込みする場合には、外部メモリにアクセスする際のレイテンシ（遅延）に起因して装置全体の処理速度低下を招く。 20

【0004】

その為、従来では、例えば特許文献1に開示の技術のように、第1の処理手段が内部メモリを占有していないタイムスロットに同期して、第2の処理手段が外部メモリから読み出したデータを内部メモリに書き込み、あるいは内部メモリから読み出したデータを外部メモリに書き込むようにし、これにより第1の処理手段から見ると、外部メモリがあたかも内部メモリの一部として動作するようにして装置全体の処理速度向上を図っている。

【先行技術文献】

【特許文献】

【0005】

【特許文献1】特許第3629693号公報 30

【発明の概要】

【発明が解決しようとする課題】

【0006】

ところで、近年の電子楽器では、コーラスやリバーブ等の信号遅延に基づく標準的なエフェクトを複数の音楽パート（発音チャンネル）に付与しながら、他の音楽パート（発音チャンネル）について各々異なる種類のエフェクトを時分割に付与する等、信号処理装置の高機能化を進める一方、その信号処理装置においては信号遅延に供する外部メモリに比較的低速な汎用デバイスを用いるようにし、さらに当該外部メモリを装置各部で共有可能として製品コスト低減を図ることが求められる。

【0007】

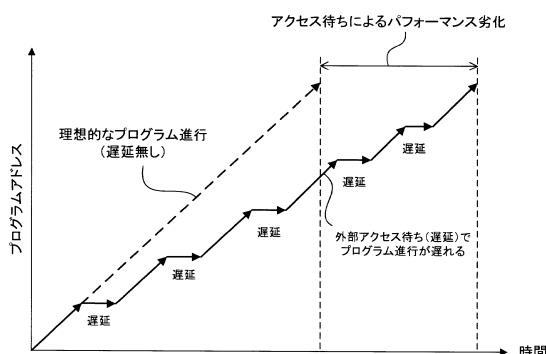

信号処理装置では、一般的に1クロック1命令でプログラムが進行する。したがって、プログラムカウンタにより計数されるプログラムアドレスは、停止やフォルト等の阻害要因が無い理想的な進行であれば、図10に図示するように、アドレスが直線的に変化する。しかしながら、比較的低速な汎用デバイスによる外部メモリを用いてエフェクトに必要な信号遅延処理を行う場合には、図10に図示する通り、当該外部メモリにアクセスする毎に生じるレイテンシ（遅延）によりパフォーマンス劣化を招くという問題がある。

さらにNAND FLSH、DDR-SDRAM等、大容量でも比較的安価なメモリは、連続するアドレスに記憶されているデータをアクセスする場合と比べて、ランダムアクセスする場合はレイテンシ（遅延）が大きくなることが知られている。

【0008】 50

本発明は、このような事情に鑑みてなされたもので、外部メモリを用いて信号遅延処理を行う場合でもアクセス待ちによるパフォーマンス劣化を回避することが出来る信号処理装置、信号処理方法、プログラムおよび電子楽器を提供することを目的としている。

**【課題を解決するための手段】**

**【0009】**

上記目的を達成するため、本発明の信号処理装置は、

各サンプリング周期において順番に処理すべき複数のデータが離散的なアドレスの順番で記憶された第1のメモリ内から、複数サンプリング周期分のデータであって、前記第1のメモリ内の連続する複数のアドレスに記憶されている複数のデータをまとめて読み出すとともに、前記読み出された前記複数サンプリング周期分のデータを第2のメモリに書き込む第1のメモリコントローラと、 10

前記第2のメモリに書き込まれている前記複数サンプリング周期分のデータを、各サンプリング周期において処理すべき順番で処理する処理部と、

を具備することを特徴とする。

**【0010】**

また、本発明の信号処理方法は、

装置が、

各サンプリング周期において順番に処理すべき複数のデータが離散的なアドレスの順番で記憶された第1のメモリ内から、複数サンプリング周期分のデータであって、前記第1のメモリ内の連続する複数のアドレスに記憶されている複数のデータをまとめて読み出すとともに、前記読み出された前記複数サンプリング周期分のデータを第2のメモリに書き込み、 20

前記第2のメモリに書き込まれている前記複数サンプリング周期分のデータを、各サンプリング周期において処理すべき順番で処理する、

ことを特徴とする。

**【0011】**

本発明のプログラムは、

コンピュータに、

各サンプリング周期において順番に処理すべき複数のデータが離散的なアドレスの順番で記憶された第1のメモリ内から、複数サンプリング周期分のデータであって、前記第1のメモリ内の連続する複数のアドレスに記憶されている複数のデータをまとめて読み出すとともに、前記読み出された前記複数サンプリング周期分のデータを第2のメモリに書き込むステップと、 30

前記第2のメモリに書き込まれている前記複数サンプリング周期分のデータを、各サンプリング周期において処理すべき順番で処理するステップと、

を実行させることを特徴とする。

**【発明の効果】**

**【0012】**

本発明では、外部メモリを用いて信号遅延処理を行う場合でもアクセス待ちによるパフォーマンス劣化を回避することが出来る。 40

**【図面の簡単な説明】**

**【0013】**

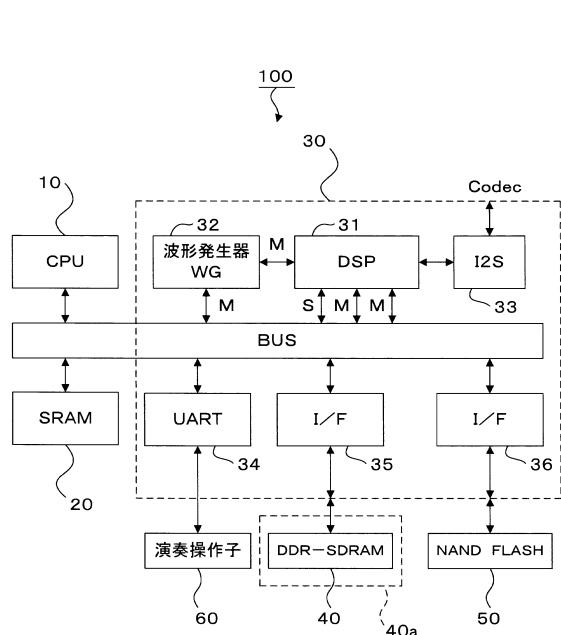

【図1】本発明の一実施形態である楽器システム100の構成を示すブロック図である。

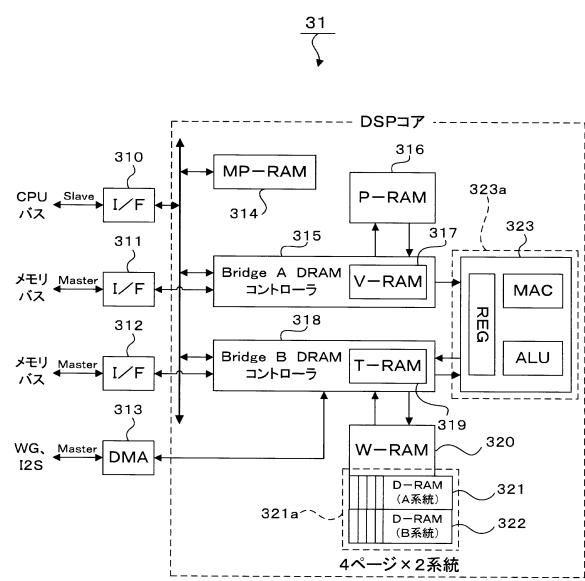

【図2】DSP31の構成を示すブロック図である。

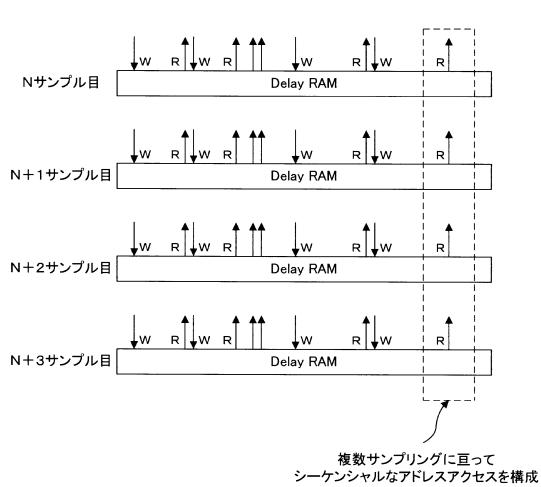

【図3】リングバッファとして機能する外部メモリ(DDR-SDRAM40)のアドレス変化を概略的に示す図である。

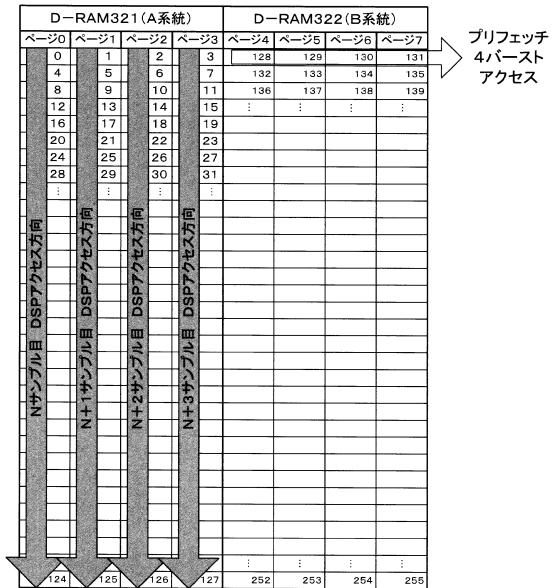

【図4】D-RAM(A系統)321およびD-RAM(B系統)322におけるページとバーストアクセスの関係を示す図である。

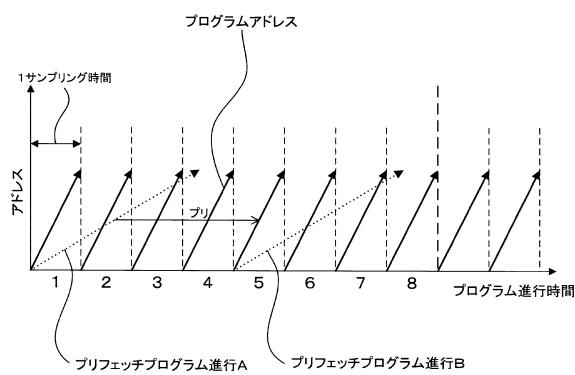

【図5】DSPプログラム進行とプリフェッチプログラム進行との関係を示す図である。

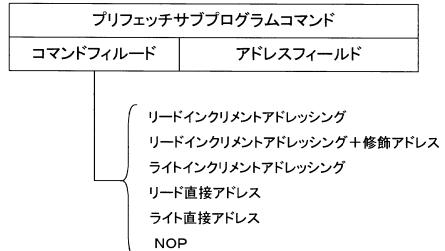

【図6】プリフェッチサブプログラムコマンドの構成を示す図である。 50

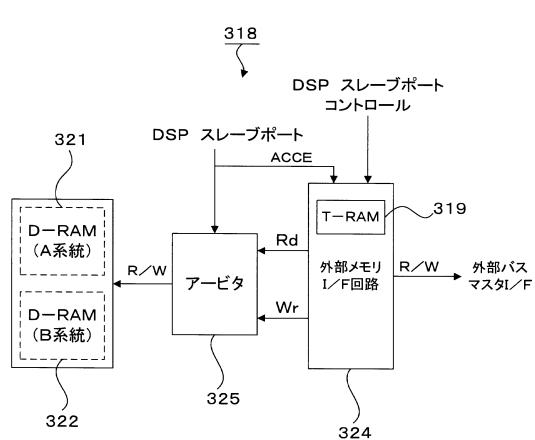

【図7】Bridge B DRAMコントローラ318の構成を示すブロック図である。

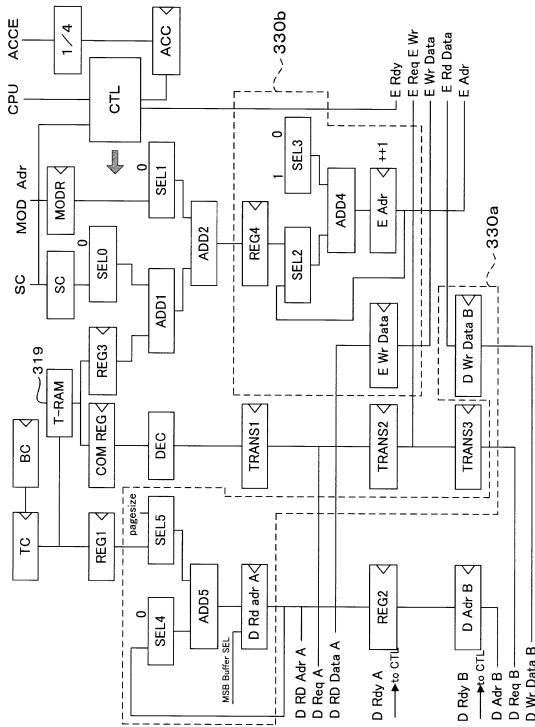

【図8】外部メモリインターフェース部324の構成を示すブロック図である。

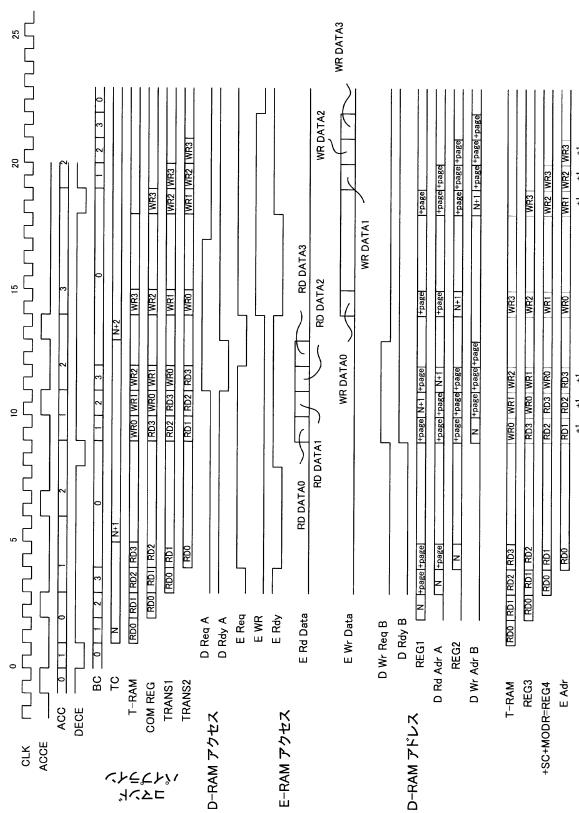

【図9】外部メモリインターフェース部324の動作を示すタイミングチャートである。

【図10】従来例を説明するための図である。

【発明を実施するための形態】

【0014】

以下、図面を参照して本発明の実施形態について説明する。

[全体構成]

図1は、本発明の一実施形態である電子楽器100の全体構成を示すブロック図である。この図に示す電子楽器100は、CPU10、SRAM20、音源部30、第1のメモリ40aとしてのDDR-SDRAM40およびNAND FLASH50から構成される。CPU10は、SRAM20に格納される各種プログラムに従って音源部30を制御する。具体的には、CPU10が音源部30のUART(Universal Asynchronous Receiver Transmitter)34を介して受信した演奏情報であるノートオン・ノートオフイベント等を表わすMIDIデータに従い、音源部30のDSP31に対して楽音波形の発生やエフェクト付与を指示する。このUARTには、例えば鍵盤などの演奏操作子60が接続される。

10

【0015】

音源部30は、起動時又は必要に応じて、NAND FLASHメモリ50から波形テーブルデータを読み出してDDR-SDRAM40に転送する。なお、DDR-SDRAM40とは、クロックの立ち上がり時と立ち下がり時の両方でデータの読み出し・書き込みを可能とするDDR(ダブルデータレート)モードを備えたSDRAMである。音源部30では、DDR-SDRAM40に格納された波形テーブルデータを参照して各種音色の波形データに基づく楽音波形を発生させた後、当該楽音波形に対してコーラスやリバーブ等のエフェクトを附加して出力する。

20

【0016】

音源部30は、DSP31、波形発生器32、I2S(I2C間サウンド)33、UART34、DDR-SDRAMインターフェース部35およびNAND FLASHインターフェース部36およびを備える。波形発生器32は、公知の波形メモリ読み出し方式で構成され、DDR-SDRAM40に格納された波形テーブルデータを参照して読み出した各種音色の波形データに基づき同時発音する複数の発音チャンネル毎の楽音波形データを生成する。

30

【0017】

DSP31では、CPU10からの指示がスレーブポートSから供給されると共に、波形発生器32が出力する各発音チャンネル毎の楽音波形データをマスターポートMを介して受信する。また、DSP31では、受信した各発音チャンネル毎の楽音波形データの内、リバーブ等の信号遅延に係るエフェクトを付与すべき発音チャンネルの楽音波形データをマスターポートM経由でDDR-SDRAM40に送る。このDDR-SDRAM40における書き込み/読み出しで信号遅延された楽音波形データは、再びマスターポートM経由でDSP31に戻る。

40

【0018】

DSP31は、各発音チャンネル毎の楽音波形データをI2S(I2C間サウンド)33に出力する。I2S33は、DSP31から供給された各発音チャンネル毎の楽音波形データを、I2Sフォーマットで外部出力する。具体的には、図示されていないサウンドシステムのD/A変換部に入力されてアナログ形式の楽音波形に変換される。

【0019】

[DSP31の構成]

次に、図2を参照してDSP31の構成について説明する。図2は、DSP31の構成を示すブロック図である。この図において、インターフェース部310は、CPUバスのス

50

レープポートSとしてI/O制御する。インターフェース部311は、Bridge A DRAMコントローラ315のメモリバス用のマスタポートMとしてI/O制御する。

#### 【0020】

インターフェース部312は、Bridge B DRAMコントローラ318のメモリバス用のマスタポートMとしてI/O制御する。DMAコントローラ313は、波形発生器32(図1参照)で発生した楽音波形データをBridge B DRAMコントローラ318側へDMA転送したり、Bridge B DRAMコントローラ318側で遅延付加した楽音波形データをI2S33(図1参照)にDMA転送する。

#### 【0021】

MP-RAM314は、上記インターフェース部310を介してCPU10から供給されるDSPプログラムを記憶する。このDSPプログラムに従って、後述する演算器323が波形信号処理を実行し、さらに後述のBridge A DRAMコントローラ315やBridge B DRAMコントローラ318が、波形信号処理に必要な各種パラメータおよび楽音波形データを演算器323に供給する。10

#### 【0022】

Bridge A DRAMコントローラ315は、P-RAM316に格納される波形信号処理用パラメータや、V-RAM317に格納される補間処理用パラメータを演算器323に供給する。Bridge B DRAMコントローラ318は、T-RAM319に格納される遅延信号処理用のプリフェッチサブプログラムに従い、DMAコントローラ313からDMA転送されて来る楽音波形データを、リングバッファとして機能する外部メモリ(DDR-SDRAM40)に対して書き込み/読み出しを行って遅延付加する。20

#### 【0023】

W-RAM320は、後述する演算器323のワークエリアとして用いられる。本願発明の第2のメモリ321aであるD-RAM(A系統)321およびD-RAM(B系統)322は、DDR-SDRAM40のミラーリング用バッファとして機能する。本実施形態では、4ページ×2系統のD-RAM(A系統)321およびD-RAM(B系統)322を用い、かつ複数サンプリング期間内に複数サンプリング分のプリフェッチ(先読み出し)を行ってDSPプログラム進行との衝突を避ける。具体的には、DSPプログラム用バッファとプリフェッチプログラム用バッファとのダブルバッファ(4ページ×2系統)を設け、プリフェッチプログラム用バッファから4サンプリング分をまとめてバーストアクセスすることで外部メモリにアクセスする毎に生じるレイテンシ(遅延)によるパフォーマンス劣化を回避する。30

#### 【0024】

本願発明の処理部323aとしての演算部323は、算術論理演算器ALU、乗累算器MACおよびレジスタREGを備え、W-RAM320をワークエリアとして、サンプリング周期毎の波形データについて、遅延フィードバック演算やフィルタ演算を施して楽音波形データを形成し、形成した楽音波形データに遅延信号処理を施してリバーブ等のエフェクトを付与する。演算部323でエフェクト付与された楽音波形データは、Bridge B DRAMコントローラ318からDMAコントローラ313を経由してI2S33(図1参照)にDMA転送される。40

#### 【0025】

##### [DDR-SDRAM40のメモリ構成]

次に、図3を参照してDDR-SDRAM40のメモリ構成について説明する。図3は、リングバッファとして機能するDDR-SDRAM40のアドレス変化を概略的に示す図である。この図は、実際のリングバッファの巡回アドレス空間を1次元のアドレス空間を備えた遅延メモリ(Delay RAM)として表現し、これを時系列(サンプリングタイミング順)に並べた様子を図示している。

#### 【0026】

こうした遅延メモリ(Delay RAM)において、Nサンプル目のデータは付与す50

べき遅延時間に対応した複数アドレスでライトW(書き込み) / リードR(読み出し)が行われる。この複数アドレスでのアクセスは、付与すべき遅延時間に対応するために離散的で連続しない。サンプリングタイミングN+1、N+2、N+3と見えていくと、Nサンプル目と同じアクセスパターンを繰り返すが、リングバッファの場合、各アドレスがサンプリング毎に増加する。1サンプリング単位で見れば比較的離散的なアドレスだが、複数サンプリングで見ると、シーケンシャルなアドレス変化として捉えることが出来る。そこで、本発明では、この複数サンプリングに亘ってシーケンシャルなアドレスについてまとめてバーストアクセスすることを特徴とする。

#### 【0027】

[D-RAM(A系統)321およびD-RAM(B系統)322のメモリ構成]

10

次に、図4は、D-RAM(A系統)321およびD-RAM(B系統)322におけるページとバーストアクセスの関係を示す図である。上述したバーストアクセスを具現する為、本実施形態では、図4に図示する通り、D-RAM(A系統)321をDSPプログラム用バッファ、D-RAM(B系統)322をプリフェッチプログラム用バッファとし、プリフェッチプログラム用バッファから4サンプリング分をまとめてバーストアクセスする。具体的には、例えば図4においてD-RAM(A系統)321のページ0～ページ3を逐次読み出ししている最中に、D-RAM(B系統)322のページ4～ページ7を一括読み出し(プリフェッチ4バーストアクセス)するようになっている。

#### 【0028】

次に、図5を参照してDSPプログラム進行とプリフェッチプログラム進行との関係を説明する。上述したように、DSPプログラム進行では、D-RAM(A系統)321から4サンプルデータを逐次読み出す。これが図5中のプログラム進行時間「1」～「4」に該当する。そして、このプログラム進行時間「1」～「4」が進行中に、プリフェッチプログラム進行AによりD-RAM(B系統)322から次の4サンプリング分「5」～「8」をプリフェッチ4バーストアクセスする。そして、DSPプログラム進行が「5」～「8」になると、次のプリフェッチプログラム進行Bがプリフェッチ4バーストアクセスする。以後、これを繰り返すことにより外部メモリにアクセスする毎に生じるレイテンシ(遅延)を回避してパフォーマンスの低下を防止する。

20

#### 【0029】

次に、図6を参照してプリフェッチプログラム進行を規定するプリフェッチサブプログラムコマンドについて説明する。前述したように、プリフェッチサブプログラムコマンドは、Bridge\_B\_DRAMコントローラ318内部のT-RAM319(図2参照)に格納され、順次実行される。プリフェッチサブプログラムコマンドは、コマンドフィールドおよびアドレスフィールドから構成される。

30

#### 【0030】

コマンドフィールドには、「リードインクリメントアドレッシング」、「リードインクリメントアドレッシング+修飾アドレス」、「ライトインクリメントアドレッシング」、「リード直接アドレス」、「ライト直接アドレス」および「NOP(no operation)」の何れかがセットされる。アドレスフィールドには、遅延する時間に関連したアドレス値がセットされる。

40

#### 【0031】

[Bridge\_B\_DRAMコントローラ318の構成]

次に、図7を参照してBridge\_B\_DRAMコントローラ318の構成について説明する。Bridge\_B\_DRAMコントローラ318は、外部メモリインタフェース部324およびアービタ325から構成される。外部メモリインタフェース部324は、DSPスレーブポートコントロール信号およびアクセスカウンタインクリメントイネーブルACCCEに応じて、外部バスマスタインタフェースを介して外部メモリ(E-RAM:DDR-SDRAM40)にリード/ライトを指示したり、アービタ325に対してリード/ライトを指示したりする。

#### 【0032】

50

アービタ325は、外部メモリインターフェース部324からのアクセス要求（リード／ライト）に応じて、D-RAM（A系統）321およびD-RAM（B系統）322が互いに干渉を起こすことなく独立してリード／ライト動作するよう調停する。具体的には、DSPスレーブポートを介したD-RAMへのアクセス要求を最優先させ、空タイミングで外部メモリ（E-RAM：DDR-SDRAM40）からプリフェッチデータを読み出したり、D-RAMから読み出したデータを外部メモリ（DDR-SDRAM40）に書き込む。

#### 【0033】

##### [外部メモリインターフェース部324の構成]

次に、図8を参照して外部メモリインターフェース部324の構成について説明する。図8において、カウンタTCは、T-RAM319のアドレス値を指定する。カウンタBCは、バーストアクセス回数を計数するカウンタであり、カウンタTCの下位を形成する。カウンタBCがバーストカウントする毎にカウンタTCがインクリメントされる。

#### 【0034】

レジスタREG1には、D-RAM（A系統）321又はD-RAM（B系統）322のアドレス（以下、D-RAMアドレスと記す）がフェッチされる。すなわち、T-RAM319（カウンタTCのアドレス値）で指定されるプリフェッチサブプログラムコマンド中のアドレスがレジスタREG1にストアされる。

#### 【0035】

セレクタSEL5は、レジスタREG1のD-RAMアドレス又は「pagesize」の何れかを選択して出力する。セレクタSEL4は、加算器ADD5の出力又は「0」の何れかを選択して出力する。加算器ADD5は、上記セレクタSEL4, SEL5の各出力を加算して得たD-RAMアドレスを発生する。つまり、レジスタREG1のD-RAMアドレスに対して「0」あるいは「pagesize」を加算し、逐次アクセスするアドレス又はバーストアクセスするアドレスを算出する。レジスタDRdadrAは、加算器ADD5の出力をフェッチする。

#### 【0036】

なお、レジスタDRdadrAに設けられたMSB\_Buffer\_SELは、前述したD-RAM（A系統）321又はD-RAM（B系統）322を選択する。D-RAM（A系統）321を選択した場合には、逐次アクセスするアドレスが用いられ、一方、D-RAM（B系統）322を選択した場合には、バーストアクセスするアドレスが用いられる。

#### 【0037】

レジスタREG2は、コントローラCTLから供給される信号DRdy\_Aを保持する。レジスタDRdadrAのアドレスに応じて読み出されるデータDRdDataは、レジスタEWrDataを介してデータEWrDataとして外部メモリ（DDR-SDRAM40）に書き込まれる。

#### 【0038】

コマンドレジスタCOM\_REGは、T-RAM319のプリフェッチサブプログラムコマンドをフェッチする。レジスタREG3は、T-RAM319のプリフェッチサブプログラムコマンド中のアドレスをフェッチする。デコーダDECは、コマンドレジスタCOM\_REGにフェッチされたプリフェッチサブプログラムコマンドをデコードし、これにより得られたアクセスコマンドをレジスタTRANS1～TRANS3に保持する。

#### 【0039】

サンプリングカウンタSCは、サンプリング数を計数して出力する。レジスタMODRは、アドレスモジュレーション値を保持する。セレクタSEL0は、「0」又はサンプリング数の何れかを選択して出力する。加算器ADD1は、レジスタREG3のプリフェッチサブプログラムコマンド中のアドレスに、セレクタSEL0の出力を加算する。セレクタSEL1は、「0」又はアドレスモジュレーション値の何れかを選択して出力する。加算器ADD2は、加算器ADD1の出力又はセレクタSEL1の出力の何れかを選択して

10

20

30

40

50

出力する。

#### 【0040】

このように、サンプリングカウンタ S C 乃至加算器 A D D 2 では、コントローラ C T L のセレクタ制御に従い、レジスタ R E G 3 のプリフェッчサブプログラムコマンド中のアドレスにサンプリング数を加算して歩進させるか、あるいはアドレスモジュレーション値を更に加算して歩進させるようになっている。歩進されたプリフェッчサブプログラムコマンド中のアドレスは、レジスタ R E G 4 に保持される。

#### 【0041】

セレクタ S E L 3 は、「1」又は「0」の何れかを選択して出力する。セレクタ S E L 2 は、レジスタ E A d r の出力又はレジスタ R E G 4 のアドレスの何れかを選択して出力する。加算器 A D D 4 は、上記セレクタ S E L 2 , S E L 3 の各出力を加算したアドレスを発生する。レジスタ E A d r は、加算器 A D D 4 が算出するアドレスをインクリメントして外部メモリ ( D D R - S D R A M 4 0 ) のアドレス E A d r を発生する。10

#### 【0042】

アドレス E A d r に応じて外部メモリから読み出されるデータ E R d D a t a は、レジスタ D W r D a t a B を介してデータ D W r D a t a B として D - R A M に書き込まれる。その書き込みアドレスは、コントローラ C T R からレジスタ D A d r B にセットされる。

#### 【0043】

1 / 4 回路は、アクセスカウンタインクリメントイネーブル A C C E のアクセス回数を 1 / 4 に減らし、4回のサンプリングアクセス巡回毎に1回のアクセスイネーブルを発生する。アクセスカウンタ A C C は、1 / 4 回路が発生するアクセスイネーブルに応じてアクセス回数をインクリメントする一方、コントローラ C T L 側から供給されるデクリメントイネーブル D E C E に応じてアクセス回数をデクリメントする。20

#### 【0044】

##### [外部メモリインターフェース部 324 の動作 ]

次に、図 9 に図示する外部メモリインターフェース部 324 のタイミングチャートを参照して動作説明する。以下では、クロック C L K のフェーズに対応して外部メモリインターフェース部 324 の動作を説明する。外部メモリインターフェース部 324 では、アクセスカウンタ A C C が「0」でないこと、レジスタ C O M R E G にコマンドが無いことを起点としてアクセス動作を開始する。30

#### 【0045】

先ず、クロック「1」フェーズでは、アクセスカウンタ A C C が「0」でないことに応じて、カウンタ B C がインクリメントを開始すると、T - R A M 319 の先頭コマンド R D 0 がパイプラインに流れる。その後、カウンタ B C のインクリメントに従い、T - R A M 319 のコマンド R D 1 、 R D 2 、 R D 3 がバースト用として発行される。

#### 【0046】

一方、D - R A M アドレスパイプラインの方は、カウンタ T C のアドレス値 N がコピーされ、続いてページアドレス + p a g e が加算されたアドレスが発行されてレジスタ D R d A D R A に保持される。40

#### 【0047】

T - R A M アドレスフィールドは、レジスタ R E G 3 からパイplineで + S C + M O D R が加算され、これにより外部メモリ ( D D R - S D R A M 4 0 ) のアドレスが算出される。外部メモリに対しては、レジスタ T R A N S 2 でアクセスリクエストがアサートされるが、外部から信号 E R d y がディアサートされる。この為、クロック「5」～「9」ではウェイト (待ち) が発生している。

#### 【0048】

そして、信号 E R d y がアサートされて再び実行を開始すると、外部メモリ ( D D R - S D R A M 4 0 : E - R A M ) からのリードデータ E R d D a t a ( R D D A T A 0 , R D D A T A 1 , R D D A T A 2 および R D D A T A 3 ) がレジスタ D W

r Data B に格納され、D - RAM に書き込むデータ ( RD DATA 0 , RD DATA 1 , RD DATA 2 および RD DATA 3 ) となる。

#### 【 0 0 4 9 】

次に、クロック「 1 0 」フェーズからは D - RAM から外部メモリへの書き込みが行われる。外部メモリへの書き込みを行う場合には、書き込むべきデータを D - RAM 側から読み出す必要が生じる。この為、クロック「 1 2 」において信号 D Req A がアサートされるが、このタイミング（クロック「 1 2 」の立ち上がり）では、先ほどの D - RAM への書き込みとコンフリクトするので、信号 D Rdy A がディアサートされてクロック「 1 2 」、「 1 3 」でウェイト（待ち）が発生する。

#### 【 0 0 5 0 】

そして、信号 D Rdy A がアサートされ次第、D - RAM からのリードデータ D RD Data ( WR DATA 0 , WR DATA 1 , WR DATA 2 および WR DATA 3 ) がレジスタ E Wr Data に格納され、順次外部メモリ ( E - RAM : DDR - SDRAM 40 ) に書き込まれる。

#### 【 0 0 5 1 】

ところで、この外部メモリへの書き込みの過程で、クロック「 1 5 」～「 1 8 」では、信号 E Rdy がディアサートされている為にウェイト状態が発生している。こうした書き込み過程でのウェイトが DSP プログラム進行において発生した場合には、そのまま処理低下の原因になるが、前述したプリフェッチプログラム進行ではプリフェッチ 4 バーストアクセスするので、その影響を回避出来る。

#### 【 0 0 5 2 】

図 8 における SEL 4 、 SEL 5 、 ADD 5 、 D Rd adr A 、及び D Wr Data B により本願発明の第 1 のメモリコントローラ 330a を構成し、 REG 4 、 SEL 2 、 SEL 3 、 ADD 4 、 E Adr 、及び E Wr Data により第 2 のメモリコントローラ 330b を構成する。

#### 【 0 0 5 3 】

以上説明したように、本実施形態では、 DSP プログラム用バッファとプリフェッチプログラム用バッファとのダブルバッファ ( 4 ページ × 2 系統 ) を設け、プリフェッチプログラム用バッファから 4 サンプリング分をまとめてバーストアクセスすることで外部メモリにアクセスする毎に生じるレイテンシ（遅延）によるパフォーマンス劣化を回避することが出来る。また、外部メモリにアクセスする毎に生じるレイテンシ（遅延）の影響を除去することで DSP 自体の処理能力が向上し、同時に処理できるエフェクトの数を増やすことも可能になる。加えて、 DSP の処理能力の向上によりバス占有率が下がる結果、楽器システム全体の処理能力の向上も期待できる。

#### 【 0 0 5 4 】

また、本願発明に係る信号処理装置の機能を、ソフトウェアプログラムによりコンピュータの処理に実現することも可能である。

#### 【 0 0 5 5 】

以上、本発明の実施形態について説明したが、本発明はそれに限定されるものではなく、本願出願の特許請求の範囲に記載された発明とその均等の範囲に含まれる。

#### 【 0 0 5 6 】

以下では、本願出願当初の特許請求の範囲に記載された各発明について付記する。

( 付記 )

##### [ 請求項 1 ]

第 1 のメモリ内の連続する複数のアドレスに記憶されている複数サンプリング周期分のデータを読み出すとともに、当該読み出された複数サンプリング周期分のデータを第 2 のメモリに書き込む第 1 のメモリコントローラと、

前記第 2 のメモリに書き込まれている複数サンプリング周期分のデータを、これら各サンプリング周期に対応するデータ毎に読み出して処理し、当該処理されたデータを前記第 2 のメモリに書き込む処理部と、

10

20

30

40

50

前記第2のメモリに書き込まれている複数サンプル周期分のデータを読み出すとともに、当該読み出されたデータを前記第1のメモリの連続するアドレスに書き込む第2のメモリコントローラと、

を備えた信号処理装置。

【0057】

[請求項2]

前記第1のメモリは、リングバッファ形状に構成され、前記第1のメモリに記憶されたデータのアドレスを、サンプリング周期でシフトすることにより、遅延処理を実行する遅延処理部をさらに有する請求項1に記載の信号処理装置。

【0058】

10

[請求項3]

前記第2のメモリは、前記複数サンプリング周期分のデータを、サンプリング周期毎に分割して記憶する複数のページエリアを備えた請求項1または請求項2に記載の信号処理装置。

【0059】

[請求項4]

前記処理装置は、サンプリング周期毎に、当該サンプリング周期に対応するページエリアにあるデータを読み出して処理し、当該処理されたデータを前記読み出しページエリアに書き込む処理部と、請求項1乃至請求項3のいずれかに記載の信号処理装置。

【0060】

20

[請求項5]

前記信号処理装置は、前記第1のメモリを外付けとし、前記第2のメモリを内蔵した請求項1乃至4に記載の信号処理装置。

【0061】

[請求項6]

信号処理装置に用いられる信号処理方法であって、前記信号処理装置は、

第1のメモリ内の連続する複数のアドレスに記憶されている複数サンプリング周期分のデータを読み出すとともに、当該読み出された複数サンプリング周期分のデータを第2のメモリに書き込み、

前記第2のメモリに書き込まれている複数サンプリング周期分のデータを、これら各サンプリング周期に対応するデータ毎に読み出して処理し、当該処理されたデータを前記第2のメモリに書き込み、

前記第2のメモリに書き込まれている複数サンプル周期分のデータを読み出すとともに、当該読み出されたデータを前記第1のメモリの連続するアドレスに書き込む、信号処理方法。

【0062】

[請求項7]

信号処理装置として用いられるコンピュータに、

第1のメモリ内の連続する複数のアドレスに記憶されている複数サンプリング周期分のデータを読み出すとともに、当該読み出された複数サンプリング周期分のデータを第2のメモリに書き込むステップと、

前記第2のメモリに書き込まれている複数サンプリング周期分のデータを、これら各サンプリング周期に対応するデータ毎に読み出して処理し、当該処理されたデータを前記第2のメモリに書き込むステップと、

前記第2のメモリに書き込まれている複数サンプル周期分のデータを読み出すとともに、当該読み出されたデータを前記第1のメモリの連続するアドレスに書き込むステップと、

、

を実行させるプログラム。

【0063】

[請求項8]

40

50

演奏データを入力する演奏操作子と、

第1および第2のメモリと、

前記演奏データに応じて楽音を形成する、前記請求項1乃至3のいずれかに記載の信号

処理装置と、

を備える電子楽器。

## 【符号の説明】

## 【0 0 6 4】

1 0 ... C P U

2 0 ... S R A M

3 0 ... 音源

10

3 1 ... D S P

3 2 ... 波形発生器

3 3 ... I 2 S

3 4 ... U A R T

3 5 ... I / F

3 6 ... I / F

4 0 ... D D R - S D R A M

5 0 ... N A N D F L A S H

1 0 0 ... 楽器システム

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

---

フロントページの続き

(58)調査した分野(Int.Cl., DB名)

G 10 H 7 / 0 0

G 10 H 1 / 0 0