(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第5624463号

(P5624463)

(45) 発行日 平成26年11月12日(2014.11.12)

(24) 登録日 平成26年10月3日(2014.10.3)

|                         |                    |

|-------------------------|--------------------|

| (51) Int.Cl.            | F 1                |

| HO 1 L 27/105 (2006.01) | HO 1 L 27/10 4 4 8 |

| HO 1 L 45/00 (2006.01)  | HO 1 L 45/00 Z     |

| HO 1 L 49/00 (2006.01)  | HO 1 L 49/00 Z     |

請求項の数 13 (全 21 頁)

|               |                               |

|---------------|-------------------------------|

| (21) 出願番号     | 特願2010-514824 (P2010-514824)  |

| (86) (22) 出願日 | 平成20年6月27日 (2008.6.27)        |

| (65) 公表番号     | 特表2010-532569 (P2010-532569A) |

| (43) 公表日      | 平成22年10月7日 (2010.10.7)        |

| (86) 国際出願番号   | PCT/US2008/007986             |

| (87) 国際公開番号   | W02009/005700                 |

| (87) 国際公開日    | 平成21年1月8日 (2009.1.8)          |

| 審査請求日         | 平成23年5月20日 (2011.5.20)        |

| (31) 優先権主張番号  | 11/772,084                    |

| (32) 優先日      | 平成19年6月29日 (2007.6.29)        |

| (33) 優先権主張国   | 米国(US)                        |

| (31) 優先権主張番号  | 11/772,090                    |

| (32) 優先日      | 平成19年6月29日 (2007.6.29)        |

| (33) 優先権主張国   | 米国(US)                        |

|           |                                                                            |

|-----------|----------------------------------------------------------------------------|

| (73) 特許権者 | 507318624<br>サンディスク スリーディー、エルエルシ<br>ー                                      |

|           | アメリカ合衆国、95035、カリフォル<br>ニア州、ミルピタス、マッカシー ブルバ<br>ード 601                       |

| (74) 代理人  | 100075144<br>弁理士 井ノ口 寿                                                     |

| (72) 発明者  | シェリッカー、エイプリル<br>アメリカ合衆国、94538、カリフォル<br>ニア州、フリーモント、モーリー アベニ<br>ュー 4875、#315 |

最終頁に続く

(54) 【発明の名称】選択付着による可逆的抵抗スイッチング素子を使用するメモリセルおよびその形成方法

## (57) 【特許請求の範囲】

## 【請求項 1】

メモリセルを形成する方法であって、

基板上にステアリング素子を形成するステップと、

前記ステアリング素子に接続される可逆的抵抗スイッチング素子をエッチングすることなく、

- a ) 導電層を形成し、

- b ) 前記導電層をエッチングして、エッチングされた表面を形成し、かつ

- c ) そのエッチングされた表面上の前記可逆的抵抗スイッチング素子を無電解に付着するか、あるいは電気メッキすることにより、選択付着プロセスを使用して前記可逆的抵抗スイッチング素子を形成するステップと、

- を含む方法。

## 【請求項 2】

請求項 1 記載の方法において、

前記ステアリング素子を形成するステップが、垂直多結晶ダイオードを形成するステップを含む方法。

## 【請求項 3】

請求項 1 記載の方法において、

前記ステアリング素子を形成するステップが、p - n ダイオードまたは p - i - n ダイオードを形成するステップを含む方法。

**【請求項 4】**

請求項 1 記載の方法において、

前記可逆的抵抗スイッチング素子を形成するステップが、 $\text{NiO}$ 、 $\text{NiO}_x$  および $\text{NiO}_x \text{P}_y$  のうちの少なくとも 1 つを形成するステップを含む方法。

**【請求項 5】**

請求項 4 記載の方法において、

前記可逆的抵抗スイッチング素子を形成するステップが、約 1,000 オングストローム以下の酸化層厚を有する可逆的抵抗スイッチング素子を形成するステップを含む方法。

**【請求項 6】**

請求項 1 記載の方法において、

前記可逆的抵抗スイッチング素子を形成するステップが、ニッケル含有層を選択的に形成するステップを含む方法。

**【請求項 7】**

請求項 6 記載の方法において、

前記ニッケル含有層を形成するステップが、 $\text{NiO}$ 、 $\text{NiO}_x$  または $\text{NiO}_x \text{P}_y$  含有層を選択的に形成するステップを含む方法。

**【請求項 8】**

請求項 7 記載の方法において、

前記ニッケル含有層を形成するステップが、前記ニッケル含有層を無電解に付着するステップを含む方法。

10

**【請求項 9】**

請求項 7 記載の方法において、

前記ニッケル含有層を形成するステップが、電気メッキを使用して前記ニッケル含有層を形成するステップを含む方法。

**【請求項 10】**

請求項 1 記載の方法において、

前記可逆的抵抗スイッチング素子を形成するステップが、 $\text{Ta}_2\text{O}_5$ 、 $\text{Nb}_2\text{O}_5$ 、 $\text{Al}_2\text{O}_3$ 、 $\text{V}_2\text{O}_5$ 、 $\text{CoO}$ 、 $(\text{Co}_x \text{Ni}_y)\text{O}_z$  および $\text{TiO}_2$  のうちの少なくとも 1 つを形成するステップを含む方法。

20

**【請求項 11】**

モノリシックな 3 次元メモリアレイを形成する方法であって、

基板上に形成される第 1 のメモリレベルを形成するステップであって、

ステアリング素子を形成し、かつ

前記ステアリング素子に接続される可逆的抵抗スイッチング素子をエッ칭することでなく、

a ) 導電層を形成し、

b ) 前記導電層をエッチングして、エッチングされた表面を形成し、かつ

c ) そのエッチングされた表面上の前記可逆的抵抗スイッチング素子を無電解に付着するか、あるいは電気メッキすることにより、選択付着プロセスを使用して前記可逆的抵抗スイッチング素子を形成することによって、複数のメモリセルの各メモリセルを形成することで、前記第 1 のメモリレベルを形成するステップと、

30

前記第 1 のメモリレベルの上にモノリシック的に形成される少なくとも第 2 のメモリレベルを形成するステップと、

を含む方法。

**【請求項 12】**

請求項 11 記載の方法において、

各ステアリング素子が、垂直多結晶ダイオードを含む方法。

**【請求項 13】**

請求項 11 記載の方法において、

各可逆的抵抗スイッチング素子が、 $\text{NiO}$ 、 $\text{NiO}_x$  および $\text{NiO}_x \text{P}_y$  のうちの少な

40

50

くとも 1 つを含む方法。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、不揮発性メモリに関し、さらに詳細には、選択付着による可逆的抵抗スイッチング素子を使用するメモリセルおよびその形成方法に関する。

【背景技術】

【0002】

関連出願の相互参照

本願は、2007年6月29日に出願された「MEMORY CELL THAT EMPLOYS A SELECTIVELY DEPOSITED REVERSIBLE RESISTANCE-SWITCHING ELEMENT AND METHODS OF FORMING THE SAME」という米国特許出願第11/772,090号（代理人整理番号：SD-MXD-0333X）（特許文献1）からの優先権を主張するとともに、2007年6月29日に出願された「MEMORY CELL THAT EMPLOYS A SELECTIVELY DEPOSITED REVERSIBLE RESISTANCE-SWITCHING ELEMENT AND METHODS OF FORMING THE SAME」という米国特許出願第11/772,084号（代理人整理番号：SD-MXD-0333Y）（特許文献2）からの優先権を主張し、どちらもその全体が本願明細書において参照により援用されている。10

本願は、以下の特許出願に関連し、各出願は、あらゆる点でその全体が本願明細書において参照により援用されている。以下の特許出願とは、2007年6月29日に出願された「METHOD TO FORM A REWRITABLE MEMORY CELL COMPRISING A DIODE AND A RESISTIVITY-SWITCHING GROWN OXIDE」という米国特許出願第11/772,081号（整理番号：MD-304X）（特許文献3）、2007年6月29日に出願された「MEMORY CELL THAT EMPLOYS A SELECTIVELY GROWN REVERSIBLE RESISTANCE-SWITCHING ELEMENT AND METHODS OF FORMING THE SAME」という米国特許出願第11/772,082号（整理番号：MD-335X）（特許文献4）、2007年6月29日に出願された「MEMORY CELL THAT EMPLOYS A SELECTIVELY GROWN REVERSIBLE RESISTANCE-SWITCHING ELEMENT AND METHODS OF FORMING THE SAME」という米国特許出願第11/772,088号（整理番号：MD-335Y）（特許文献5）である。20

【0003】

可逆的抵抗スイッチング素子から形成される不揮発性メモリが知られている。例えば、その全体が本願明細書において参照により援用されている、2005年5月9日に出願された「REWRITABLE MEMORY CELL COMPRISING A DIODE AND A RESISTANCE-SWITCHING MATERIAL」という米国特許出願第11/125,939号（特許文献6）には、金属酸化物または金属窒化物などの可逆的抵抗率スイッチング材料と直列に接続されるダイオードを含む書換可能不揮発性メモリセルが記載されている。30

しかし、書換可能抵抗率スイッチング材料からメモリデバイスを製造するのは困難であり、可逆的抵抗率スイッチング材料を使用するメモリデバイスの形成方法を改良することが望ましい。

【先行技術文献】

【特許文献】

【0004】

【特許文献1】米国特許出願第11/772,090号

【特許文献2】米国特許出願第11/772,084号

【特許文献3】米国特許出願第11/772,081号

【特許文献4】米国特許出願第11/772,082号

【特許文献5】米国特許出願第11/772,088号

【特許文献6】米国特許出願第11/125,939号

【特許文献7】米国特許出願第11/444,936号

【特許文献8】米国特許第6,952,030号

【特許文献9】米国特許出願第11/692,151号

40

50

【特許文献 10】米国特許第 5 , 915 , 167 号

【特許文献 11】米国特許出願第 11 / 298 , 331 号

【特許文献 12】米国特許第 7 , 176 , 064 号

【非特許文献】

【0005】

【非特許文献 1】N. Takano et al., "Mechanism of the Chemical Deposition of Nickel on Silicon Wafers in Aqueous Solution", Journal of Electrochemical Society, 146(4) pp. 1407-1411 (1999)

【発明の概要】

【0006】

本発明の第 1 の態様では、(1) 基板上にステアリング素子を形成するステップと、(2) 選択付着プロセスを使用してステアリング素子に接続される可逆的抵抗スイッチング素子を形成するステップと、を含むメモリセルを形成する方法が提供される。

【0007】

本発明の第 2 の態様では、(1) 基板上に第 1 の導体を形成するステップと、(2) 第 1 の導体の上にダイオードを形成するステップと、(3) 選択付着プロセスを使用して第 1 の導体の上に可逆的抵抗スイッチング素子を形成するステップと、(4) ダイオードおよび可逆的抵抗スイッチング素子の上に第 2 の導体を形成するステップと、を含むメモリセルを形成する方法が提供される。

【0008】

本発明の第 3 の態様では、(1) 基板上に第 1 の導体を形成するステップと、(2) 第 1 の導体の上に垂直多結晶ダイオードを形成するステップと、(3) 垂直多結晶ダイオードの上に、酸化ニッケル層を含む可逆的抵抗スイッチング素子を選択的に形成するステップと、(4) 垂直多結晶ダイオードの上に第 2 の導体を形成するステップと、を含むメモリセルを形成する方法が提供される。

【0009】

本発明の第 4 の態様では、(1) 基板上にソース領域およびドレイン領域を有する薄膜トランジスタを形成するステップと、(2) トランジスタのソース領域またはドレイン領域に接続される第 1 の導体を形成するステップと、(3) 第 1 の導体の上に酸化ニッケル層を含む可逆的抵抗スイッチング素子を選択的に形成するステップと、(4) 可逆的抵抗スイッチング素子の上に第 2 の導体を形成するステップと、を含むメモリセルを形成する方法が提供される。

【0010】

本発明の第 5 の態様では、(1) ステアリング素子と、(2) ステアリング素子に接続され、選択付着プロセスを使用して形成される可逆的抵抗スイッチング素子と、を含むメモリセルが提供される。

【0011】

本発明の第 6 の態様では、(1) 第 1 の導体と、(2) 第 1 の導体の上に形成される第 2 の導体と、(3) 第 1 の導体と第 2 の導体との間に形成されるダイオードと、(4) 選択付着プロセスを使用して第 1 の導体と第 2 の導体との間に形成される可逆的抵抗スイッチング素子と、を含むメモリセルが提供される。

【0012】

本発明の第 7 の態様では、(1) 第 1 の導体と、(2) 第 1 の導体の上に形成される垂直多結晶ダイオードと、(3) 垂直多結晶ダイオードの上に選択的に形成される酸化ニッケル層を含む可逆的抵抗スイッチング素子と、(4) 垂直多結晶ダイオードの上に形成される第 2 の導体と、を含むメモリセルが提供される。

【0013】

本発明の第 8 の態様では、(1) ソース領域およびドレイン領域を有する薄膜トランジスタと、(2) ソース領域またはドレイン領域に接続される第 1 の導体と、(3) 第 1 の導体の上に選択的に形成される酸化ニッケル層を含む可逆的抵抗スイッチング素子と、(4)

10

20

30

40

50

4 ) 可逆的抵抗スイッチング素子の上に形成される第 2 の導体と、を含むメモリセルが提供される。

【 0 0 1 4 】

本発明の第 9 の態様では、( 1 ) 第 1 の方向に延びる第 1 の複数の実質的に平行で実質的に共平面の導体と、( 2 ) 複数のダイオードと、( 3 ) 複数の可逆的抵抗スイッチング素子と、( 4 ) 第 1 の方向とは異なる第 2 の方向に延びる第 2 の複数の実質的に平行で実質的に共平面の導体と、を含む複数の不揮発性メモリセルが提供される。各メモリセルにおいて、ダイオードのうちの 1 つと可逆的抵抗スイッチング素子のうちの 1 つとが、直列に配列され、第 1 の導体のうちの 1 つと第 2 の導体のうちの 1 との間に配置される。さらに、各可逆的抵抗スイッチング素子は、選択付着プロセスを使用して形成される。 10

【 0 0 1 5 】

本発明の第 10 の態様では、基板上に形成される第 1 のメモリレベルを含むモノリシックな 3 次元メモリアレイが提供される。第 1 のメモリレベルは、( 1 ) ステアリング素子と、( 2 ) ステアリング素子に接続され、選択付着プロセスを使用して形成される可逆的抵抗スイッチング素子と、をそれぞれ有する複数のメモリセルを含む。さらに、モノリシックな 3 次元メモリアレイは、第 1 のメモリレベルの上にモノリシック的に形成される少なくとも第 2 のメモリレベルも含む。本発明のこれらの実施形態および他の実施形態による他の数多くの態様も提供される。

【 0 0 1 6 】

本発明の他の特徴および態様は、以下の詳細な説明、添付の特許請求の範囲、および添付の図面からさらに完全に明白になるであろう。 20

【 図面の簡単な説明 】

【 0 0 1 7 】

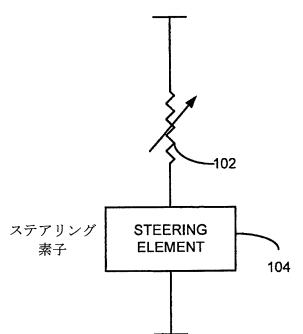

【 図 1 】 本発明に従って提供される例示的なメモリセルを示す概略図である。

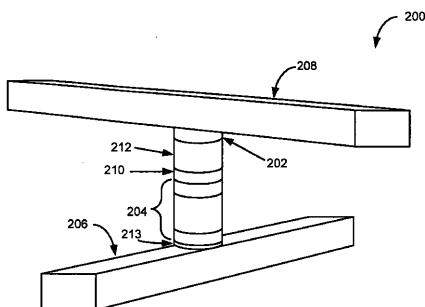

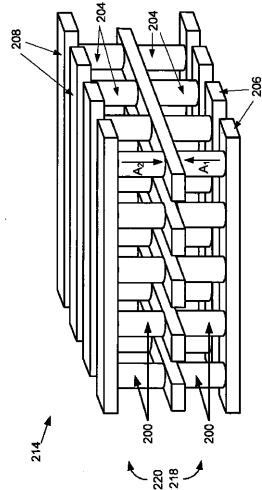

【 図 2 A 】 本発明に従って提供されるメモリセルの第 1 の実施形態を示す略斜視図である。

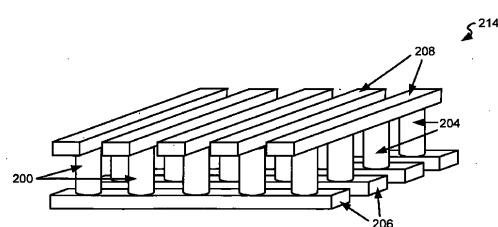

【 図 2 B 】 複数の図 2 A のメモリセルから形成される第 1 のメモリレベルの一部を示す略斜視図である。

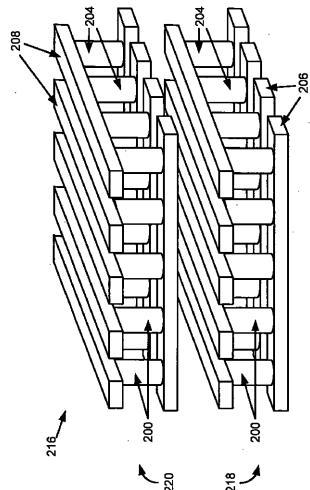

【 図 2 C 】 本発明に従って提供される第 1 の例示的な 3 次元メモリアレイの一部を示す略斜視図である。 30

【 図 2 D 】 本発明に従って提供される第 2 の例示的な 3 次元メモリアレイの一部を示す略斜視図である。

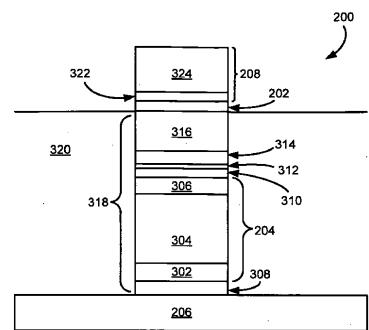

【 図 3 】 図 2 A のメモリセルの例示的な実施形態を示す断面図である。

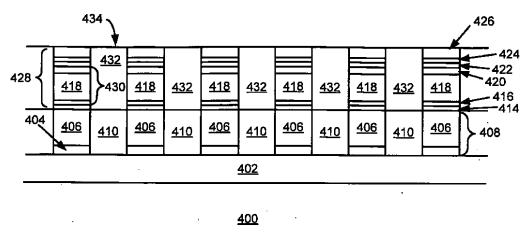

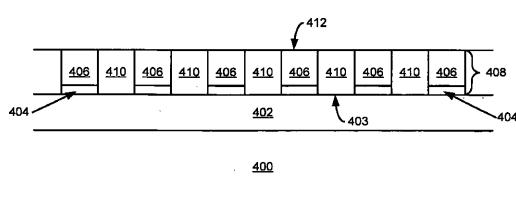

【 図 4 A 】 本発明に従って単一のメモリレベルを製造する過程の基板の一部を示す断面図である。

【 図 4 B 】 本発明に従って単一のメモリレベルを製造する過程の基板の一部を示す断面図である。

【 図 4 C 】 本発明に従って単一のメモリレベルを製造する過程の基板の一部を示す断面図である。

【 図 4 D 】 本発明に従って単一のメモリレベルを製造する過程の基板の一部を示す断面図である。 40

【 図 5 】 本発明に従って提供される代替のメモリセルを示す断面図である。

【 図 6 】 本発明に従って提供される第 2 の代替のメモリセルを示す断面図である。

【 発明を実施するための形態 】

【 0 0 1 8 】

前述したように、書換可能抵抗率スイッチング材料からメモリデバイスを製造するのは困難である。例えば、多くの書換可能抵抗率スイッチング材料は、化学的にエッティングするのが困難なため、集積回路にこれを使用することに関連する製造のコストや複雑さが増大する。

【 0 0 1 9 】

本発明によれば、化学的にエッティングするのが困難な書換可能抵抗率スイッチング材料は、メモリセル内でエッティングされることなく使用されてもよい。例えば、少なくとも1つの実施形態では、可逆的抵抗率スイッチング材料がメモリセル内でエッティングされることなく使用されるように、選択付着プロセスを使用して形成される可逆的抵抗率スイッチング材料を含むメモリセルが提供される。

#### 【0020】

1つ以上の例示的な実施形態では、可逆的抵抗スイッチング素子は、可逆的抵抗率スイッチング材料として酸化ニッケルを使用して形成されてもよい。酸化ニッケル膜は、例えば、前に援用されている特許文献6で説明されるように、メモリで使用するのに適していることが示されている。

10

#### 【0021】

Ni、Ni<sub>x</sub>P<sub>y</sub>、NiO、NiO<sub>x</sub>、NiO<sub>x</sub>P<sub>y</sub>などのニッケル含有膜は、化学的にエッティングするのが困難である。少なくとも1つの実施形態では、選択付着プロセスを使用することによって、酸化ニッケル層がエッティングされることなくメモリセルの可逆的抵抗スイッチング素子で酸化ニッケル層を使用することもできる。例えば、可逆的抵抗スイッチング素子は、電気メッキ、無電解付着、またはその類似方法などの付着プロセスを使用し、基板上に形成される導電面上のみにニッケル含有層を選択的に付着させることによって形成されてもよい。このように、(ニッケル含有層を付着させる前に)基板上の導電面のみがパターニングおよび/またはエッティングされ、ニッケル含有層には実施されない。

20

#### 【0022】

ある実施形態では、酸化ニッケルは、選択的に付着されてもよいが、他の実施形態では、ニッケルは選択的に付着され、次に酸化されて酸化ニッケルを形成してもよい。どちらの場合も、ニッケルおよび/または酸化ニッケル層をエッティングする必要がなくなり、メモリセルの製造を大幅に簡略化することもできる。

#### 【0023】

他の材料が本発明に従って選択的に付着され、次いで必要に応じてアニールおよび/または酸化されて、メモリセルで使用される可逆的または一度だけプログラム可能な抵抗率スイッチング材料を形成してもよい。例えば、Nb、Ta、V、Al、Ti、Co、コバルト-ニッケル合金などの層が、電気メッキなどによって選択的に付着され、酸化されて可逆的抵抗率スイッチング材料を形成してもよい。

30

#### 【0024】

##### 例示的な発明に関するメモリセル

図1は、本発明に従って提供される例示的なメモリセル100の概略図である。メモリセル100は、ステアリング素子104に接続される可逆的抵抗スイッチング素子102を含む。

#### 【0025】

可逆的抵抗スイッチング素子102は、2つ以上の状態の間を可逆的にスイッチングすることもできる抵抗率を有する可逆的抵抗率スイッチング材料(個別に図示せず)を含む。例えば、素子102の可逆的抵抗率スイッチング材料は、製造時には初期低抵抗率状態であってもよく、この状態は、第1の電圧および/または電流を印加すると高抵抗率状態にスイッチング可能である。第2の電圧および/または電流を印加すると、可逆的抵抗率スイッチング材料は低抵抗率状態に戻ってもよい。あるいは、可逆的抵抗スイッチング素子102は、製造時には初期高抵抗率状態であってもよく、この状態は、適切な電圧(单数または複数)および/または電流(单数または複数)を印加すると低抵抗率状態に可逆的にスイッチング可能である。メモリセルに使用される場合、1つの抵抗状態は、2進の「0」を表し、別の抵抗状態は2進の「1」を表してもよいけれども、3つ以上のデータ/抵抗状態が使用されてもよい。例えば、前に援用されている特許文献6には、多くの可逆的抵抗率スイッチング材料および可逆的抵抗スイッチング素子を使用するメモリセルの動作が記載されている。

40

50

## 【0026】

本発明の少なくとも1つの実施形態では、可逆的抵抗スイッチング素子102は、選択付着プロセスを使用して形成される。さらに以下に説明するように、選択付着プロセスを使用することによって、可逆的抵抗率スイッチング材料をエッ칭する必要なしに可逆的抵抗スイッチング素子102内に可逆的抵抗率スイッチング材料を提供することができる。これにより、可逆的抵抗スイッチング素子102の製造が簡略化される。

## 【0027】

ステアリング素子104は、薄膜トランジスタ、ダイオード、または可逆的抵抗スイッチング素子102によって電圧および/または電流を選択的に制限することによって非オーミック伝導を示す別の適切なステアリング素子を含んでもよい。このように、メモリセル100は、2次元または3次元メモリアレイの一部として使用されてもよく、アレイ内の他のメモリセルの状態に影響を及ぼすことなく、メモリセル100にデータを書き込んだり、および/またはそこからデータを読み出したりすることができる。10

## 【0028】

メモリセル100、可逆的抵抗スイッチング素子102およびステアリング素子104の例示的な実施形態は、図2A～図6を参照しながら以下に説明する。

## 【0029】

メモリセルの第1の例示的な実施形態

図2Aは、本発明に従って提供されるメモリセル200の第1の実施形態の略斜視図である。図2Aを参照して、メモリセル200は、第1の導体206と第2の導体208との間にダイオード204と直列に接続される可逆的抵抗スイッチング素子202を含む。ある実施形態では、可逆的抵抗スイッチング素子202とダイオード204との間に、バリア層210および/または導電層212が形成されてもよい。例えば、バリア層210は、窒化チタン、窒化タンタル、窒化タングステンなどを含んでもよく、導電層212は、タングステンまたは別の適切な金属層を含んでもよい。以下にさらに説明するように、バリア層210および/または導電層212は、ダイオード204を形成する過程でハードマスクとして働いてもよい。このようなハードマスクは、例えば、その全体が本願明細書において参照により援用されている、2006年5月13日に出願された「CONDUCTIVE HARD MASK TO PROTECT PATTERNED FEATURES DURING TRENCH ETCH」という米国特許出願第11/444,936号(特許文献7)に記載されている。ダイオード204と第1の導体206との間には、窒化チタン、窒化タンタル、窒化タングステンなどの追加のバリア層213も形成されてよい。2030

## 【0030】

以下にさらに説明するように、可逆的抵抗スイッチング素子202は、メモリセル200の製造を簡略化するように、選択的に形成される。少なくとも1つの実施形態では、可逆的抵抗スイッチング素子202は、ニッケルを選択的に付着させ、次いでニッケル層を酸化することによって形成される酸化ニッケル層の少なくとも一部を含む。例えば、Ni、Ni<sub>x</sub>P<sub>y</sub>またはニッケルの別の形態が、非電解析出、電気メッキまたは類似の選択プロセスを使用して選択的に付着され、次いで(例えば、急速熱酸化または他の酸化プロセスを使用して)酸化されて酸化ニッケルを形成してもよい。他の実施形態では、酸化ニッケル自体が選択的に付着されてもよい。例えば、NiO、NiO<sub>x</sub>またはNiO<sub>x</sub>P<sub>y</sub>含有層が、選択付着プロセスを使用してダイオード204の上に選択的に付着され、次いで(必要に応じて)アニールおよび/または酸化されてもよい。これらの実施形態および他の実施形態は、図3を参照しながら以下にさらに説明する。図2Aでは、可逆的抵抗スイッチング素子202は、ダイオード204の上に位置するように示されるが、当然ながら、代替の実施形態では、可逆的抵抗スイッチング素子202は、(例えば、図6を参照して以下に説明するように)ダイオード204の下に位置してもよい。ある実施形態では、可逆的抵抗スイッチング素子202の1つ以上のフィラメントなどの部分のみがスイッチングしても、および/またはスイッチング可能であってもよい。40

## 【0031】

ダイオード 204 は、ダイオードの p 領域の上に n 領域を有して上を向くか、ダイオードの n 領域の上に p 領域を有して下を向くかによらず、垂直多結晶 p - n または p - i - n ダイオードなどの何らかの適切なダイオードを含んでもよい。ダイオード 204 の例示的な実施形態は、図 3 を参照しながら以下に説明する。

#### 【0032】

第 1 および / または第 2 の導体 206、208 は、タンゲステン、何らかの適切な金属、高濃度にドープされた半導体材料、導電性シリサイド、導電性シリサイド - ゲルマニド、導電性ゲルマニドなどの何らかの適切な導電性材料を含んでもよい。図 2 A の実施形態では、第 1 および / または第 2 の導体 206、208 は、レール状で、( 例えれば、実質的に互いに直交して ) 異なる方向に延びる。他の導体形状および / または構造が使用されてもよい。ある実施形態では、第 1 および / または第 2 の導体 206、208 とともに、バリア層、接着層、反射防止コーティングおよび / またはその類似物 ( 図示せず ) が使用され、デバイス性能を改善し、および / またはデバイスの製造に役立てるこ<sup>10</sup>ともできる。

#### 【0033】

前述したように、他の材料を使用して、可逆的抵抗スイッチング素子 202 を形成してもよい。例えれば、Nb、Ta、V、Al、Ti、Co、コバルト - ニッケル合金などの材料が、同様に、( 図 2 A に示されるように、バリア層 210 の上および / または導電層 212 の上などの ) ダイオード 204 の上に選択的に付着され、必要に応じて酸化および / またはアニールされて、可逆的抵抗スイッチング素子 202 を形成してもよい。

#### 【0034】

図 2 B は、複数の図 2 A のメモリセル 200 から形成される第 1 のメモリレベル 214 の一部の略斜視図である。簡単にするため、可逆的抵抗スイッチング素子 202、ダイオード 204、バリア層 210 および 213、および導電層 212 は、個別に示されない。メモリアレイ 214 は、( 図に示されるように ) 複数のメモリセルが接続される複数のビット線 ( 第 2 の導体 208 ) およびワード線 ( 第 1 の導体 206 ) を含む「クロスポイント」アレイである。他のメモリアレイ構造が、マルチレベルのメモリとして使用されてもよい。例えれば、図 2 C は、第 2 のメモリレベル 220 の下に配置される第 1 のメモリレベル 218 を含むモノリシックな 3 次元アレイ 216 の一部の略斜視図である。図 2 C の実施形態では、各メモリレベル 218、220 は、クロスポイントアレイ内に複数のメモリセル 200 を含む。当然ながら、第 1 のメモリレベル 218 と第 2 のメモリレベル 220 との間に、追加の層 ( 例えれば、中間誘電体 ) が存在してもよいが、簡単にするために図 2 C では示されない。他のメモリアレイ構造が、メモリの追加レベルとして使用されてもよい。図 2 C の実施形態では、すべてのダイオードは、p 型領域を有する p - i - n ダイオードがダイオードの下部に使用されるか上部に使用されるかによって、上向きまたは下向きなどの同じ方向に「向く」ことで、ダイオードの製造を簡略化することもできる。<sup>20</sup>

#### 【0035】

ある実施形態では、メモリレベルは、例えれば、あらゆる点でその全体が本願明細書において参照により援用されている「High-density three-dimensional memory cell」という米国特許第 6,952,030 号 ( 特許文献 8 ) で説明されるように形成されてもよい。例えれば、図 2 D に示されるように、第 1 のメモリレベルの上部導体は、第 1 のメモリレベルの上に位置する第 2 のメモリレベルの下部導体として用いられてもよい。この実施形態では、あらゆる点でその全体が本願明細書において参照により援用されている、2007 年 3 月 27 日に出願された「LARGE ARRAY OF UPWARD POINTING P-I-N DIODES HAVING LARGE AND UNIFORM CURRENT」という米国特許出願第 11/692,151 号 ( 特許文献 9 ) で説明されるように、隣接するメモリレベル上のダイオードは、反対方向に向くのが好ましい。例えれば、第 1 のメモリレベル 218 のダイオードは、( 例えれば、ダイオードの下部に p 領域を有して ) 矢印 A<sub>1</sub> で示されるように上向きダイオードであってもよく、第 2 のメモリレベル 220 のダイオードは、( 例えれば、ダイオードの下部に n 領域を有して ) 矢印 A<sub>2</sub> で示されるように下向きダイオードであってもよく、あるいはその逆であってもよい。<sup>30</sup>

## 【0036】

モノリシックな3次元メモリアレイは、複数のメモリレベルが、中間基板を用いないでウェハなどの単一の基板上に形成されるアレイである。1つのメモリレベルを形成する層は、既存のレベル（単数または複数）の層の上に直接付着または成長される。これに対して、積層メモリは、Leedyによる「Three dimensional structure memory」という米国特許第5,915,167号（特許文献10）の場合のように、別々の基板上にメモリレベルを形成し、そのメモリレベルを互いに重ねて接着することによって構築されている。基板は、ボンディングの前に薄くされても、あるいはメモリレベルから取り除かれてもよいが、メモリレベルが個別の基板上に最初に形成されるので、このようなメモリは、本当のモノリシックな3次元メモリアレイではない。

10

## 【0037】

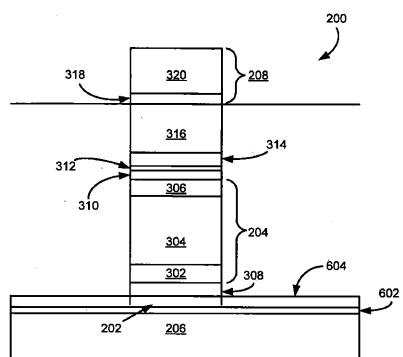

図3は、図2Aのメモリセル200の例示的な実施形態の断面図である。図3を参照して、メモリセル200は、可逆的抵抗スイッチング素子202と、ダイオード204と、第1および第2の導体206、208とを含む。

前述したように、ダイオード204は、垂直p-nまたはp-i-nダイオードであってもよく、このダイオードは上向きでも下向きでもよい。隣接するメモリレベルが導体を共有する図2Dの実施形態では、隣接するメモリレベルは、第1のメモリレベルには下向きのp-i-nダイオード、隣接する第2のメモリレベルには上向きのp-i-nダイオード（あるいは、その逆）のように反対方向を向くダイオードを有するのが好ましい。

20

## 【0038】

ある実施形態では、ダイオード204は、ポリシリコン、多結晶シリコン-ゲルマニウム合金、ポリゲルマニウム、または他の何らかの適切な材料などの多結晶半導体材料から形成されてもよい。例えば、ダイオード204は、高濃度にドープされたn+ポリシリコン領域302と、n+ポリシリコン領域302の上の低濃度にドープされたまたは真性（自然にドープされた）ポリシリコン領域304と、真性領域304の上の高濃度にドープされたp+ポリシリコン領域306とを含んでもよい。ある実施形態では、例えば、あらゆる点でその全体が本願明細書において参照により援用されている、2005年12月9日に出願された「DEPOSITED SEMICONDUCTOR STRUCTURE TO MINIMIZE N-TYPE DOPANT DIFFUSION AND METHOD OF MAKING」という米国特許出願第11/298,331号（特許文献11）で説明されるように、シリコン-ゲルマニウム合金層を使用する場合、約10at%（アトミックパーセント）以上のゲルマニウムを有する薄い（例えば、数百オングストローム以下の）ゲルマニウムおよび/またはシリコン-ゲルマニウム合金層（図示せず）をn+ポリシリコン領域302上に形成し、n+ポリシリコン領域302から真性領域304内へのドーパントの移動を防止および/または低減することもできる。当然ながら、n+およびp+領域の位置は逆であってもよい。（例えば、ポリシリコン領域内への金属原子の移動を防止および/または低減するために）第1の導体206とn+領域302との間に、窒化チタン、窒化タンタル、窒化タングステンなどのバリア層308が形成されてもよい。

30

## 【0039】

ダイオード204が、付着シリコン（例えば、非晶質または多結晶）から形成される場合、ダイオード204上にシリサイド層310を形成して、付着シリコンを製造時の低抵抗率状態に置いててもよい。この低抵抗率状態によって、付着シリコンを低抵抗率状態に切り換えるのに高い電圧は必要ないため、メモリセル200のプログラミングを容易にすることができます。例えば、p+ポリシリコン領域306上に、チタンまたはコバルトなどのシリサイド形成金属層312が付着されてもよい。ダイオード204を形成する付着シリコンを結晶化するのに使用される（以下に説明する）次のアニールステップの過程で、シリサイド形成金属層312とダイオード204の付着シリコンとが相互に作用してシリサイド層310を形成し、これがシリサイド形成金属層312のすべてまたは一部を占める。

40

## 【0040】

50

その全体が本願明細書において参照により援用されている「Memory Cell Comprising a Semiconductor Junction Diode Crystallized Adjacent to a Silicide」という米国特許第7,176,064号(特許文献12)に記載されるように、チタンおよび/またはコバルトなどのシリサイド形成材料は、アニール中に付着シリコンと反応してシリサイド層を形成する。チタンシリサイドおよびコバルトシリサイドの格子間隔は、シリコンの格子間隔に近く、このようなシリサイド層は、付着シリコンが結晶化する場合、隣接する付着シリコンの「結晶化テンプレート」または「シード」として働くことができる(例えば、シリサイド層310は、アニール中にシリコンダイオード204の結晶構造を強化する)ようである。これによって、低抵抗率シリコンが提供される。シリコン-ゲルマニウム合金および/またはゲルマニウムダイオードについても、同様な結果を得ることもできる。

10

#### 【0041】

図3の実施形態では、可逆的抵抗スイッチング素子202は、選択付着プロセスによって形成される。ある実施形態では、可逆的抵抗スイッチング素子202は、導電性シリサイド形成金属層312の上に(またはシリサイド形成金属層312の上に形成される導電性バリア層の上に)形成されてもよい。(図4A~図4Dを参照しながら以下に説明するように、このような層は、ダイオード204の形成中にパターニングされてもよい)。しかし、他の実施形態では、可逆的抵抗スイッチング素子202を形成する前に、シリサイド形成金属層312の上に金属ハードマスクが形成されてもよい。例えば、シリサイド形成金属層312の上に、バリア層314および/または導電層316が形成されてもよい。バリア層314は、窒化チタン、窒化タンタル、窒化タンゲステンなどを含んでもよく、導電層316は、タンゲステンまたは別の適切な金属層を含んでもよい。以下にさらに説明するように、バリア層314および/または導電層316は、ダイオード204の形成中にハードマスクとして働いてもよく、(前に援用されている特許文献7に記載されるように)上部導体208を形成する過程で発生し得るあらゆるオーバーエッ칭ングを軽減することもできる。例えば、バリア層314および導電層316は、パターニングおよびエッ칭ングされ、その後ダイオード204のエッ칭ング中にマスクとして働いてもよい。導電層316、バリア層314、シリサイド形成金属層312、ダイオード204(p+ポリシリコン層306、真性層304、n+ポリシリコン層302)およびバリア層308をエッ칭ングして、ピラー構造318が作られる。メモリセル200を含むメモリレベル上に製造される他のメモリセル(図示せず)の他の類似のピラー構造からピラー構造318を分離するように、ピラー構造318の上およびその周囲には、誘電材料320が付着される。次いで、CMPまたは誘電体エッチバックステップが実施され、誘電材料320を平坦化し、導電層316の上端部から誘電材料を取り除く。

20

#### 【0042】

誘電材料320の平坦化の後、パターニングされエッ칭ングされた導電層316の上に、選択付着プロセスによって可逆的抵抗スイッチング素子202が形成されてもよい。例えば、パターニングされエッ칭ングされた導電層316の上に、(1)NiO、NiO<sub>x</sub>、NiO<sub>x</sub>P<sub>y</sub>などの酸化ニッケルを選択的に付着させ、必要に応じて、酸化ニッケルをアニールおよび/または酸化し、および/または(2)ニッケルを選択的に付着させ、次いでニッケルを酸化することによって、酸化ニッケル層が選択的に形成されてもよい。どちらの場合も、酸化ニッケルは、パターニングされエッ칭ングされた導電層316の上面にのみ付着するため、ニッケルおよび/または酸化ニッケル層をエッ칭ングする必要がなくなり、メモリセルの製造を大幅に簡略化することもできる。さらに、所望のあらゆる厚さの酸化ニッケルを形成することもできる。ある実施形態では、可逆的抵抗スイッチング素子202に、約1,000オングストローム以下、さらに好ましくは、約500オングストローム以下の厚さの酸化ニッケル層が使用される(ただし、他の層厚範囲が使用されてもよい)。

30

#### 【0043】

一実施形態では、導電層316の形成、パターニングおよびエッ칭ングの後、無電解付

40

50

着プロセスが使用され、導電層 316 の上にニッケルまたは酸化ニッケルを選択的に付着させる。例えば、水溶液を使用し導電層 316 を水溶液に浸すことによって、導電層 316 の上にニッケルまたは酸化ニッケルを選択的に形成してもよい。水溶液は、例えば、溶液の pH を調整するための 1 つ以上の溶解塩 / 前駆物質、錯化剤および / または緩衝液を含んでもよい。ある実施形態では、水溶液は、硫酸ニッケル、亜硫酸ニッケル、リン酸ニッケル、亜リン酸ニッケル、水酸化ニッケル、リン酸アンモニア、またはその混合物などのニッケル塩および / または水酸化ニッケル塩を含んでもよい。さらに例示的な組成は、 $\text{NiSO}_4$ 、 $\text{NaH}_2\text{PO}_2$ 、クエン酸ナトリウム、 $(\text{NH}_4)_2\text{SO}_4$ 、またはその類似物を含んでもよい。当然ながら、水溶液および / または他のプロセス条件を形成するのに使用される正確な組成に応じて、導電層 316 の上にニッケルか酸化ニッケルのどちらか（またはその両方）が付着されてもよい。

#### 【0044】

例示的なプロセス条件は、ニッケル含有水溶液を約 20 から 85 の間の温度に維持しながら、導電層 316 をその水溶液中に約 1 秒から約 5 分間浸すステップを含む。あらゆる点でその全体が本願明細書において参照により援用されている、N. Takano et al., "Mechanism of the Chemical Deposition of Nickel on Silicon Wafers in Aqueous Solution", Journal of Electrochemical Society, 146(4) pp. 1407-1411 (1999)（非特許文献 1）には、ニッケルまたは酸化ニッケル層を選択的に形成するのに使用される追加の例示的な水溶液および / またはプロセス条件が記載されている。前述したように、付着ニッケルまたは酸化ニッケルは、 $\text{Ni}$ 、 $\text{Ni}_x\text{P}_y$ 、 $\text{NiO}$ 、 $\text{NiO}_x$ 、 $\text{NiO}_x\text{P}_y$ 、または他の類似の材料を含んでもよい。

#### 【0045】

ニッケルまたは酸化ニッケルの形成に続いて、熱酸化プロセスを使用して、選択付着ニッケルから酸化ニッケルを形成するか、あるいは選択付着酸化ニッケルの形態および / または電気的特性を改善するかのどちらかを行ってもよい。例示的な酸化条件は、約 400 から 800 の温度による約 20 秒から 10 分間の  $\text{O}_2$  などの酸素雰囲気中の急速熱酸化を含む。他の酸化またはアニールプロセス、酸素種、時間および / または温度が使用されてもよい。

#### 【0046】

パターニングおよびエッチングされた導電層 316 の上にニッケル含有層を形成するのに使用されてもよい別の適切な選択付着プロセスは、従来のニッケル電気メッキを含む。いかなる適切な電気メッキプロセスを使用して、導電層 316 の上にニッケルを選択的に付着させてもよい。その後、前述したように、電気メッキされたニッケルを酸化して酸化ニッケルを形成してもよい。

#### 【0047】

前述したように、他の材料を使用して可逆的抵抗スイッチング素子 202 を形成してもよい。例えば、Nb、Ta、V、Al、Ti、Co、コバルト - ニッケル合金などの材料が、同様に、（図 2A に示されるように、バリア層 210 の上および / または導電層 212 の上などの）ダイオード 204 の上に選択的に付着され、必要に応じて酸化および / またはアニールされてもよい。

#### 【0048】

可逆的抵抗スイッチング素子 202 の形成に続いて、上部導体 208 が形成される。ある実施形態では、導電層 324 を付着する前に 1 つ以上のバリア層および / または接着層 322 が、可逆的抵抗スイッチング素子 202 の上に形成されてもよい。導電層 324 とバリア層 322 とが、一緒にパターニングおよび / またはエッチングされて上部導体 208 を形成してもよい。ある実施形態では、図 4A ~ 図 4D を参照して以下に説明するように、ダマシンプロセスを使用して上部導体 208 が形成されてもよい。

#### 【0049】

上部導体 208 の形成に続いて、メモリセル 200 をアニールして、ダイオード 204 の付着半導体材料を結晶化（および / または、シリサイド層 310 を形成）してもよい。

10

20

30

40

50

少なくとも 1 つの実施形態では、アニールは、約 10 秒から約 2 分間、約 600 から 800 の温度、さらに好ましくは、約 650 から 750 の間の温度の窒素中で実施されてもよい。他のアニール時間、温度および / または雰囲気が使用されてもよい。前述したように、シリサイド層 310 は、アニール中に、ダイオード 204 を形成する下の付着半導体材料の「結晶化テンプレート」または「シード」として働くこともできる。これによって、低抵抗率ダイオード材料が提供される。

#### 【 0050 】

本発明に従ってメモリセルを製造する例示的なプロセスを図 4 A ~ 図 4 D を参照しながら以下に説明する。

#### 【 0051 】

10

#### メモリセルの例示的な製造プロセス

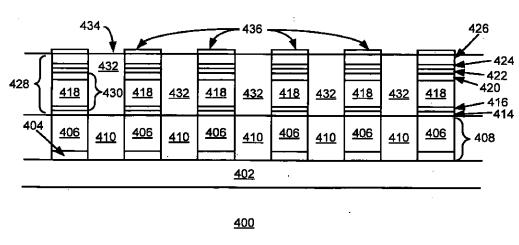

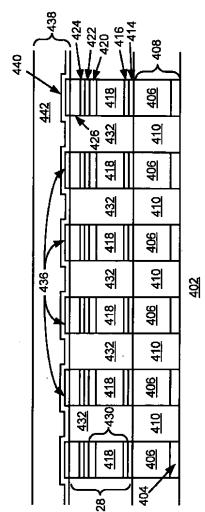

図 4 A ~ 図 4 D は、本発明に従って第 1 のメモリレベルを製造する過程の基板 400 の一部の断面図を示す。以下に説明するように、第 1 のメモリレベルは、選択付着プロセスを使用して形成される可逆的抵抗スイッチング素子をそれぞれ含む複数のメモリセルを含む。(図 2 C ~ 図 2 D を参照して前に説明したように) 第 1 のメモリレベルの上には追加のメモリレベルが製造されてもよい。

#### 【 0052 】

図 4 A を参照して、基板 400 は、幾つかの処理ステップが既に施されたものとして示される。基板 400 は、追加回路の有無にかかわらず、シリコン、ゲルマニウム、シリコン - ゲルマニウム、非ドープ、ドープ、バルク、シリコンオンインシュレータ (SOI) または他の基板などのどんな適切な基板でもよい。例えば、基板 400 は、1 つ以上の n ウェルまたは p ウェル領域(図示せず)を含んでもよい。

20

#### 【 0053 】

基板 400 の上には、絶縁層 402 が形成される。ある実施形態では、絶縁層 402 は、二酸化シリコン、窒化シリコン、酸窒化シリコン、または他の適切な絶縁層であってもよい。

#### 【 0054 】

絶縁層 402 の形成に続いて、(例えば、物理気相付着法または別の方法によって) 絶縁層 402 の上に接着層 404 が形成される。例えば、接着層 404 は、約 20 から約 500 オングストローム、好ましくは、約 100 オングストロームの窒化チタン、または窒化タンタル、窒化タンクス汀、1 つ以上の接着層の組み合わせ、またはその類似物などの別の適切な接着層であってもよい。他の接着層の材料および / または厚さが使用されてもよい。ある実施形態では、接着層 404 は任意であってもよい。

30

#### 【 0055 】

接着層 404 の形成に続いて、接着層 404 の上に導電層 406 が付着される。導電層 406 は、タンクス汀または別の適切な金属、高濃度にドープされた半導体材料、導電性シリサイド、導電性シリサイド - ゲルマニド、導電性ゲルマニド、または何らかの適切な方法(例えば、化学気相付着(CVD)、物理気相付着(PVD)など)によって付着される類似物などの何らかの適切な導電性材料を含んでもよい。少なくとも 1 つの実施形態では、導電層 406 は、約 200 から約 2,500 オングストロームのタンクス汀を含んでもよい。他の導電層の材料および / または厚さが使用されてもよい。

40

#### 【 0056 】

導電層 406 の形成に続いて、接着層 404 および導電層 406 がパターニングされエッティングされる。例えば、接着層 404 および導電層 406 は、ソフトまたはハードマスク、およびウェットまたはドライエッティングプロセスを用いる従来のリソグラフィ技術を使用してパターニングされエッティングされてもよい。少なくとも 1 つの実施形態では、接着層 404 および導電層 406 は、実質的に平行で実質的に共平面の導体 408 (図 4 A に示される) を形成するように、パターニングされエッティングされる。例示的な導体 408 の幅および / または導体 408 同士の間隔は、約 200 から約 2500 オングストロームの範囲であるが、他の導体の幅および / または間隔が使用されてもよい。

50

## 【0057】

導体408が形成された後、導体408間の隙間を充填するように、基板400の上に誘電層410が形成される。例えば、基板400上にほぼ3,000から7,000オングストロームの二酸化シリコンが付着され、化学的機械的研磨またはエッチバックプロセスを使用して平坦化されて平面412を形成してもよい。(図に示されるように)平面412は、誘電材料によって分離される導体408の露出された上面を含む。窒化シリコン、酸窒化シリコン、低誘電率(10wK)誘電体などの他の誘電材料、および/または他の誘電層厚が使用されてもよい。例示的な10wK誘電体は、炭素ドープ酸化物、シリコン炭素層、またはその類似物を含む。

## 【0058】

10

本発明の他の実施形態では、ダマシンプロセスを使用して導体408が形成されてもよいが、その場合、誘電層410が形成されパターニングされて導体408のための開口部または隙間が作られる。次いで、開口部または隙間は、接着層404および導電層406(および/または導電性シード、導電性フィルおよび/または必要に応じてバリア層)で充填されてもよい。次いで、接着層404および導電層406は、平坦化されて平面412を形成してもよい。この実施形態では、接着層404は、各開口部または隙間の底部および側壁を内張りする。

## 【0059】

20

平坦化に続いて、各メモリセルのダイオード構造が形成される。図4Bを参照して、基板400の平坦化された上面412の上にバリア層414が形成される。バリア層414は、約20から約500オングストローム、好ましくは、約100オングストロームの窒化チタン、あるいは、窒化タンタル、窒化タンゲステン、1つ以上のバリア層の組み合わせ、チタン/窒化チタン、タンタル/窒化タンタルまたはタンゲステン/窒化タンゲステンの積層などの他の層と組み合わせたバリア層、またはその類似物などの別の適切なバリア層であってもよい。他のバリア層の材料および/または厚さが使用されてもよい。

## 【0060】

30

バリア層414の付着の後で、各メモリセルのダイオード(例えば、図2A~図3のダイオード204)を形成するのに使用される半導体材料の付着が開始される。各ダイオードは、前に説明したように、垂直p-nまたはp-i-nダイオードであってもよい。ある実施形態では、各ダイオードは、ポリシリコン、多結晶シリコン-ゲルマニウム合金、ポリゲルマニウムまたは他の何らかの適切な材料などの多結晶半導体材料から形成される。便宜上、本願明細書では、ポリシリコンによる下向きのダイオードの形成について説明する。当然ながら、他の材料および/またはダイオード構造が使用されてもよい。

## 【0061】

図4Bを参照して、バリア層414の形成に続いて、バリア層414上に高濃度にドープされたn+シリコン層416が付着される。ある実施形態では、n+シリコン層416は、付着時に非晶質状態にある。他の実施形態では、n+シリコン層416は、付着時に多結晶状態にある。CVDまたは別の適切なプロセスを使用して、n+シリコン層416を付着してもよい。少なくとも1つの実施形態では、n+シリコン層416は、例えば、約 $10^{21} \text{ cm}^{-3}$ のドーピング濃度を有する約100から約1000オングストローム、好ましくは、約100オングストロームのリンまたはヒ素ドープシリコンから形成されてもよい。他の層厚、ドーピング型および/またはドーピング濃度が使用されてもよい。n+シリコン層416は、例えば、付着中にドナーガスを流すことによって、その場で(in situ)ドープされてもよい。他のドーピング方法が使用されてもよい(例えば、注入法)。

40

## 【0062】

n+シリコン層416の付着の後で、n+シリコン層416の上に低濃度にドープされた真性シリコン層および/または自然にドープされたシリコン層418が形成される。ある実施形態では、真性シリコン層418は、付着時に非晶質状態にある。他の実施形態では、真性シリコン層418は、付着時に多結晶状態にある。CVDまたは別の適切な付着方法を使用して、真性シリコン層418を付着してもよい。少なくとも1つの実施形態で

50

は、真性シリコン層418は、厚さが約500から約4,800オングストローム、好ましくは、約2,500オングストロームであってもよい。他の真性層厚が使用されてもよい。

#### 【0063】

(前に援用されている特許文献11に記載されるように)真性シリコン層418を付着する前に、n+シリコン層416の上に薄い(例えば、数百オングストローム以下の)ゲルマニウムおよび/またはシリコン-ゲルマニウム合金層(図示せず)を形成して、n+シリコン層416から真性シリコン層418内へのドーバントの移動を防止および/または低減してもよい。

#### 【0064】

高濃度にドープされたp型シリコンが付着されイオン注入によってドープされるか、あるいは付着中にその場でドープされてp+シリコン層420を形成する。例えば、プランケットp+注入を使用して、真性シリコン層418内に所定の深さでボロンを注入してもよい。例示的な注入可能分子イオンは、BF<sub>2</sub>、BF<sub>3</sub>、Bなどを含む。ある実施形態では、約1~5×10<sup>15</sup>イオン/cm<sup>2</sup>の注入ドーズ量が使用されてもよい。他の注入種および/またはドーズ量が使用されてもよい。さらに、ある実施形態では、拡散プロセスが使用されてもよい。少なくとも1つの実施形態では、その結果得られるP+シリコン領域420は、約100から700オングストロームの厚さを有するが、他のP+シリコン層サイズが使用されてもよい。

#### 【0065】

p+シリコン層420の形成に続いて、p+シリコン層420の上にシリサイド形成金属層422が付着される。例示的なシリサイド形成金属は、スパッタあるいは付着チタンまたはコバルトを含む。ある実施形態では、シリサイド形成金属層422は、約10から約200オングストローム、好ましくは、約20から約50オングストローム、さらに好ましくは、約20オングストロームの厚さを有する。他のシリサイド形成金属層の材料および/または厚さが使用されてもよい。

#### 【0066】

シリサイド形成金属層422の上に、バリア層424が付着される。バリア層424は、約20から約500オングストローム、好ましくは、約100オングストロームの窒化チタン、あるいは、窒化タンタル、窒化タンゲステン、1つ以上のバリア層の組み合わせ、チタン/窒化チタン、タンタル/窒化タンタルまたはタンゲステン/窒化タンゲステンの積層などの他の層と組み合わせたバリア層、またはその類似物などの別の適切なバリア層であってもよい。他のバリア層の材料および/または厚さが使用されてもよい。

#### 【0067】

バリア層424の形成に続いて、バリア層424の上に導電層426が形成される。導電層426は、約50から約1000オングストローム、好ましくは、約500オングストロームのタンゲステンなどの導電性材料または別の適切な金属であってもよい。

#### 【0068】

次いで、バリア層414、シリコン領域416、418および420、シリサイド形成金属層422、バリア層424ならびに導電層426は、パターニングされエッチングされてピラー428になる。例えば、最初に、導電層426およびバリア層424がエッチングされる。エッチングは続いて、シリサイド形成金属層422、シリコン領域420、418および416ならびにバリア層414をエッチングする。導電層426およびバリア層414は、シリコンのエッチング中にハードマスクとして働く。ハードマスクは、その下の層のエッチングをパターニングする働きをするエッチング層であり、導電層426上に存在するすべてのフォトレジストが使用された場合、その代わりにハードマスクはパターンを提供することができる。このように、ピラー428は、单一のフォトリソグラフィステップで形成される。従来のリソグラフィ技術およびウェットまたはドライエッチング処理を使用してピラー428を形成してもよい。各ピラー428は、p-i-n下向きダイオード430を含む。上向きp-i-nダイオードが同様に形成されてもよい。

10

20

30

40

50

## 【0069】

ピラー428が形成された後、ピラー428間の隙間を充填するためにピラー428の上に誘電層432が付着される。例えば、約200から7,000オングストロームの二酸化シリコンが付着され、化学的機械的研磨またはエッチバックプロセスを使用して平坦化され、平面434を形成してもよい。平面434は、(図に示されるように)誘電材料432によって分離されるピラー428の露出された上面を含む。窒化シリコン、酸窒化シリコン、10wK誘電体などの他の誘電材料、および/または他の誘電層厚が使用されてもよい。例示的な10wK誘電体は、炭素ドープ酸化物、シリコン炭素層、またはその類似物を含む。

## 【0070】

平面434の形成に続いて、各ピラー428の上に可逆的抵抗スイッチング素子436(図4C)が選択的に形成される。例えば、(1)酸化ニッケルを選択的に付着させる、および/または(2)ニッケルを選択的に付着させてからそのニッケルを酸化することによって、酸化ニッケル層が各導電性ピラー428の上に選択的に形成されてもよい。どちらの場合も、ニッケルおよび/または酸化ニッケル層をエッチングする必要がなくなり、メモリセルの製造を大幅に簡略化することもできる。前に説明したように、無電解付着、電気メッキまたはその類似の方法などのニッケルまたは酸化ニッケルを選択的に付着するためのいかなる適切な方法が使用されてもよい。少なくとも1つの実施形態では、各導電性ピラー428の上に形成される可逆的抵抗スイッチング素子436は、約1,000オングストローム以下の厚さ、より好ましくは、約500オングストローム以下の厚さを有する酸化ニッケル層を含む。他の酸化ニッケル層厚が使用されてもよい。酸化ニッケル層は、例えば、NiO、NiO<sub>x</sub>およびNiO<sub>x</sub>P<sub>y</sub>または他の類似の材料を含んでもよい。Nb、Ta、V、Al、Ti、Co、コバルト-ニッケル合金などの他の材料が、同様に、選択的に付着され、酸化および/またはアニールされて、各ピラー428の上に選択付着による可逆的抵抗スイッチング素子を形成してもよい。

## 【0071】

図4Dを参照して、可逆的抵抗スイッチング素子436の形成に続いて、第2の一連の導体438が、下部の一連の導体408の形成と同様な方法でピラー428の上に形成されてもよい。例えば、図4Dに示されるように、ある実施形態では、上部の第2の一連の導体438を形成するのに使用される導体層442を付着させる前に、可逆的抵抗スイッチング素子436の上に1つ以上のバリア層および/または接着層440が付着されてもよい。

## 【0072】

導電層442は、タンゲステン、別の適切な金属、高濃度にドープされた半導体材料、導電性シリサイド、導電性シリサイド-ゲルマニド、導電性ゲルマニド、または何らかの適切な方法(例えば、CVD、PVDなど)によって付着される類似物などの何らかの適切な導電性材料から形成されてもよい。他の導電層材料が使用されてもよい。バリア層および/または接着層440は、窒化チタン、あるいは窒化タンタル、窒化タンゲステン、1つ以上の層の組み合わせ、または他の何らかの適切な材料(単数または複数)などの別の適切な層を含んでもよい。付着された導電性層442およびバリアおよび/または接着層440は、パターニングおよびエッチングされて第2の一連の導体438を形成する。少なくとも1つの実施形態では、上部導体438は、下部導体408と異なる方向に延びる実質的に平行で実質的に共平面の導体である。

## 【0073】

本発明の他の実施形態では、ダマシンプロセスを使用して上部導体438が形成されてもよいが、その場合、誘電層が形成されパターニングされて導体438のための開口部または隙間が作られる。特許文献7に記載されるように、導電層426およびバリア層424は、上部導体438のための開口部または隙間を形成する過程でこの誘電層をオーバーエッチングする作用を軽減し、ダイオード430が誤って短絡するのを防ぐこともできる。

10

20

30

40

50

## 【0074】

開口部または隙間は、接着層440および導電層442（および／または導電性シード、導電性フィルおよび／または必要に応じてバリア層）で充填されてもよい。次いで、接着層440および導電層442は、平坦化されて平面を形成してもよい。

## 【0075】

上部導体438の形成に続いて、本構造をアニールして、ダイオード430の付着半導体材料を結晶化（および／またはシリサイド形成金属層422とp+領域420との反応によってシリサイド領域を形成）してもよい。少なくとも1つの実施形態では、アニールは、約600から800、さらに好ましくは、約650から750の間の温度の窒素中で、約10秒から約2分間実施されてもよい。他のアニール時間、温度および／または雰囲気が使用されてもよい。シリサイド形成金属層領域422とp+領域420とがそれぞれ反応して形成されるシリサイド領域は、アニール中にダイオード430を形成する下の付着半導体材料の「結晶化テンプレート」または「シード」として働くことができる（例えば、何らかの非晶質半導体材料を多結晶半導体材料に変化させる、および／またはダイオード430の全体的な結晶特性を改善させる）。これによって、低抵抗率ダイオード材料が提供される。10

## 【0076】

第1の代替の例示的なメモリセル

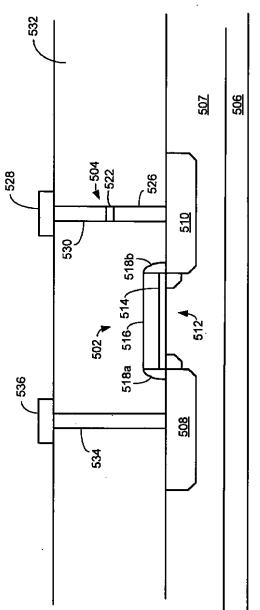

図5は、本発明に従って提供される例示的なメモリセル500の断面図である。メモリセル500は、基板505上に形成される可逆的抵抗スイッチング素子504に接続される薄膜金属酸化膜半導体電界効果トランジスタ（MOSFET）502などの薄膜トランジスタ（TFT）を含む。例えば、MOSFET502は、何らかの適切な基板上に形成されるnチャネルまたはpチャネル薄膜MOSFETであってもよい。図に示される実施形態では、二酸化シリコン、窒化シリコン、酸窒化物などの絶縁領域506が基板505上に形成され、絶縁領域506の上に、付着シリコン、ゲルマニウム、シリコン-ゲルマニウムなどの付着半導体領域507が形成される。付着半導体領域507内に薄膜MOSFET502が形成され、絶縁領域506によって基板505から分離される。20

## 【0077】

MOSFET502は、ソース／ドレイン領域508、510およびチャネル領域512、ならびにゲート誘電層514、ゲート電極516およびスペーサ518a、518bを含む。少なくとも1つの実施形態では、ソース／ドレイン領域508、510はp型にドープされ、チャネル領域512はn型にドープされてもよく、他の実施形態では、ソース／ドレイン領域508、510はn型にドープされ、チャネル領域512はp型にドープされてもよい。薄膜MOSFET502には、他の何らかのMOSFET構造または何らかの適切な製造技術が使用されてもよい。ある実施形態では、MOSFET502は、STI、LOCOSまたは他の類似プロセスを使用して形成される絶縁領域（図示せず）によって電気的に分離されてもよい。あるいは、MOSFET502のゲート、ソースおよび／またはドレイン領域は、基板505上に形成される他のトランジスタ（図示せず）と共有されてもよい。30

## 【0078】

可逆的抵抗スイッチング素子504は、導電性プラグ526の上に形成される可逆的抵抗率スイッチング材料522を含む。少なくとも1つの実施形態では、可逆的抵抗スイッチング素子522は、図1～図4Dの実施形態を参照しながら前に説明したように、選択付着プロセスを使用して形成される。例えば、（1）酸化ニッケルを選択的に付着させることによって、酸化ニッケル層が導電性プラグ526の上に選択的に形成されてもよい。例示的な選択付着プロセスは、無電解付着、電気メッキ、またはその類似プロセスを含む。他の材料が本発明に従って選択的に付着され、酸化され、および／またはアニールされてメモリセル500で使用される可逆的抵抗率スイッチング材料を形成してもよい（例えば、Nb、Ta、V、Al、Ti、Co、コバルト-ニッケル合金など）。4050

## 【0079】

図5に示されるように、可逆的抵抗スイッチング素子504は、第1の導電性プラグ526によってMOSFET502のソース／ドレイン領域510に、第2の導電性プラグ530によって第1の金属レベル(M1)線528に接続される(これにより誘電層532を貫通して延びる)。同様に、第3の導電性プラグ534は、MOSFET502のソース／ドレイン領域508をM1線536に接続する。導電性プラグおよび／または線は、(バリア層の有無にかかわらず)タンゲステン、別の金属、高濃度にドープされた半導体材料、導電性シリサイド、導電性シリサイド-ゲルマニド、導電性ゲルマニドまたはその類似物などの何らかの適切な材料から形成されてもよい。MOSFET502がnチャネルデバイスの場合には、領域508はMOSFET502のドレイン、領域510はMOSFET502のソースとして機能し、MOSFET502がpチャネルデバイスの場合には、領域508はMOSFET502のソース、領域510はMOSFET502のドレインとして機能することに留意すべきである。誘電層532は、二酸化シリコン、窒化シリコン、酸窒化シリコン、LOW-K誘電体などの何らかの適切な誘電体を含んでもよい。

## 【0080】

メモリセル500で、薄膜MOSFET502は、図2A～図4Dのメモリセルで使用されるダイオードのステアリング素子と同様な方法で、印加電圧および／または可逆的抵抗スイッチング素子504を通って流れる電流を選択的に制限するステアリング素子として動作する。

## 【0081】

少なくとも1つの実施形態では、可逆的抵抗スイッチング素子504は、約1,000オングストローム以下、さらに好ましくは、約500オングストローム以下の厚さを有する酸化ニッケル層を含む。他の酸化ニッケル層厚が使用されてもよい。

## 【0082】

第2の代替のメモリセル

図6は、本発明に従って提供される例示的なメモリセル600の断面図である。メモリセル600は、可逆的抵抗スイッチング素子202がダイオード204の下に形成される点を除けば、図3のメモリセル200と類似している。具体的には、図6に示されるように、可逆的抵抗スイッチング素子202は、パターニングされエッチングされた下部導体206の上に導電性材料602を選択的に付着させることによって形成される。次いで、導電性材料602は、本発明に従って、必要に応じてアニールおよび／または酸化されてメモリセル600で使用される可逆的抵抗率スイッチング材料604を形成してもよい。例えば、導電性材料602は、電気メッキなどによって選択的に付着され、酸化されて可逆的抵抗率スイッチング材料層604を形成するNi、Ni<sub>x</sub>P<sub>y</sub>、NiO、NiO<sub>x</sub>、NiO<sub>x</sub>P<sub>y</sub>、Nb、Ta、V、Al、Ti、Co、コバルト-ニッケル合金などの層を含んでもよい。ダイオード204と垂直方向に重なりおよび／またはこれと位置合わせされる可逆的抵抗率スイッチング材料層604の一部は、メモリセル600のダイオード204と第1の導体206との間の可逆的抵抗スイッチング素子202として働いてもよい。ある実施形態では、可逆的抵抗スイッチング素子202の1つ以上のフィラメントなどの部分のみがスイッチングしても、および／またはスイッチング可能であってもよい。層604は、既にパターニングされエッチングされた下部導体206の上に選択的に付着されるため、可逆的抵抗率スイッチング材料層604はエッチングを必要としない。

## 【0083】

前述した説明は、本発明の例示的な実施形態のみを開示している。本発明の範囲に含まれる上で開示された装置および方法についての変更は、当業者であれば容易に思い当たるであろう。例えば、本発明は、主にニッケルおよび酸化ニッケルの選択付着に関して説明したが、当然ながら、例えば、Ta<sub>2</sub>O<sub>5</sub>、Nb<sub>2</sub>O<sub>5</sub>、Al<sub>2</sub>O<sub>3</sub>、V<sub>2</sub>O<sub>5</sub>、CoO、(Co<sub>x</sub>Ni<sub>y</sub>)O<sub>z</sub>、およびTiO<sub>2</sub>を形成するTa、Nb、Al、V、Co、コバルト-ニッケル合金、Tiなどの他の材料が選択的に付着され、可逆的抵抗スイッチング

10

20

30

40

50

素子に使用されてもよい。

したがって、本発明は、その例示的な実施形態に関連して開示されたが、当然ながら、他の実施形態が、添付の特許請求の範囲によって定義される本発明の趣旨および範囲に含まれてもよい。

【図 1】

FIG. 1

【図 2 A】

Fig. 2A

【図 2 B】

Fig. 2B

【図2C】

Fig. 2C

【図2D】

Fig. 2D

【図3】

Fig. 3

【図4B】

Fig. 4B

【図4A】

Fig. 4A

【図4C】

Fig. 4C

【図4D】

**Fig. 4D**

【 四 5 】

FIG. 5

【図6】

*Fig. 6*

---

フロントページの続き

(72)発明者 ハーナー , エス . ブラッド

アメリカ合衆国、95125、カリフォルニア州、サンノゼ、マイルドレッド アベニュー 12

89

(72)発明者 コネベッキー ,マイケル

アメリカ合衆国、95126、カリフォルニア州、サンノゼ、サウスウェスト エクスプレスウェイ

2032、#73

審査官 外山 賀

(56)参考文献 特開2007-165873(JP,A)

特開2004-363604(JP,A)

国際公開第2006/075574(WO,A1)

国際公開第2006/121837(WO,A1)

特開2007-053199(JP,A)

韓国登録特許第10-0717286(KR,B1)

(58)調査した分野(Int.Cl., DB名)

H01L 27/105

H01L 45/00

H01L 49/00