(19) 日本国特許庁(JP)

## (12) 公開特許公報(A)

(11) 特許出願公開番号

特開2004-336772

(P2004-336772A)

(43) 公開日 平成16年11月25日(2004.11.25)

(51) Int.Cl.<sup>7</sup>

**H03M 1/08**

**H03K 17/00**

**H03K 17/60**

**H03M 1/70**

F 1

H03M 1/08

H03K 17/00

H03M 1/70

H03K 17/60

テーマコード(参考)

B 5J022

D 5J055

G

審査請求 未請求 請求項の数 10 O L (全 12 頁)

(21) 出願番号 特願2004-135316 (P2004-135316)

(22) 出願日 平成16年4月30日 (2004.4.30)

(31) 優先権主張番号 10/427578

(32) 優先日 平成15年4月30日 (2003.4.30)

(33) 優先権主張国 米国(US)

(71) 出願人 399117121

アジレント・テクノロジーズ・インク

A G I L E N T T E C H N O L O G I E

S, I N C.

アメリカ合衆国カリフォルニア州パロアル

ト ページ・ミル・ロード 395

395 Page Mill Road

Palo Alto, California

U. S. A.

(74) 代理人 100099623

弁理士 奥山 尚一

(74) 代理人 100096769

弁理士 有原 幸一

(74) 代理人 100107319

弁理士 松島 鉄男

最終頁に続く

(54) 【発明の名称】デジタル・アナログ・コンバータ用の素子単位のリサンプリング

## (57) 【要約】

【課題】スイッチの非線形性を出力信号に影響させることなく、デジタル入力をアナログ入力へと変換する。

【解決手段】デジタル入力に応答し、部分アナログ信号を選択的に生成するよう構成されたアナログ出力素子104A、104B、104C、104D、104E、304と、アナログ出力素子104A、104B、104C、104D、104E、304に接続され、前記部分アナログ信号を合わせてアナログ出力を生成するよう構成された加算回路108、208、208A、208Bと、アナログ出力素子104A、104B、104C、104D、104E、304と加算回路108、208、208A、208Bとの間に接続され、アナログ出力素子104A、104B、104C、104D、104E、304から加算回路108、208、208A、208Bへの前記部分アナログ信号の伝送を調節するよう構成されたスイッチ106、306とを含んでなるデジタル・アナログ・コンバータを提供する。

【選択図】 図1

**【特許請求の範囲】****【請求項 1】**

デジタル入力に応答し、部分アナログ信号を選択的に生成するよう構成されたアナログ出力素子と、

該アナログ出力素子に接続され、前記部分アナログ信号を合わせてアナログ出力を生成するよう構成された加算回路と、

前記アナログ出力素子と前記加算回路との間に接続され、前記アナログ出力素子から前記加算回路への前記部分アナログ信号の伝送を調節するよう構成されたスイッチとを含んでなるデジタル・アナログ・コンバータ。

**【請求項 2】**

前記アナログ出力素子のそれぞれは、前記スイッチ中の異なるスイッチを介して前記加算回路に接続されている請求項 1 に記載のデジタル・アナログ・コンバータ。

**【請求項 3】**

前記スイッチは、前記アナログ出力素子から前記加算回路へと前記部分アナログ信号を同時に伝送するためのクロック信号を受信するよう接続されている請求項 2 に記載のデジタル・アナログ・コンバータ。

**【請求項 4】**

前記アナログ出力素子は、等価な信号を生成するよう構成されている請求項 1 から 3 のいずれかに記載のデジタル・アナログ・コンバータ。

**【請求項 5】**

前記アナログ出力素子の中の少なくとも 1 つが、前記スイッチ中の 1 つの特定のスイッチと電圧端子とに直列に接続されている、トランジスタおよび電流源を含むものである請求項 1 から 4 のいずれかに記載のデジタル・アナログ・コンバータ。

**【請求項 6】**

デジタル入力を受信するステップと、

該デジタル入力に応答して部分アナログ信号を生成するステップと、

該部分アナログ信号の伝送を調節するステップと、

該部分アナログ信号を受信して合わせて、前記デジタル入力のアナログ表現であるアナログ出力を生成するステップと

を含んでなるデジタル・アナログ変換方法。

**【請求項 7】**

前記部分アナログ信号の伝送を調節するステップが、クロック信号を使用して前記部分アナログ信号を同時に伝送することを含む請求項 6 に記載の方法。

**【請求項 8】**

前記部分アナログ信号の伝送を調節するステップが、複数のスイッチを作動させて前記部分アナログ信号を伝送することを含むものである請求項 6 または 7 に記載の方法。

**【請求項 9】**

前記部分アナログ信号の伝送を調節するステップが、前記スイッチ中の 1 つを介して前記部分アナログ信号の中の少なくとも 2 つを送信する前に、前記部分アナログ信号の中の前記少なくとも 2 つを合わせることを含む請求項 8 に記載の方法。

**【請求項 10】**

前記複数のスイッチを作動させるステップが、前記複数のスイッチを同時に作動させて前記部分アナログ信号を同時に伝送することを含む請求項 8 または 9 に記載の方法。

**【発明の詳細な説明】****【技術分野】****【0001】**

本発明は、回路に関し、更に詳しくは、デジタル・アナログ・コンバータ (Digital-to-Analog Converter: 以下、「D/A」とよぶ) に関するものである。

**【背景技術】**

10

20

30

40

50

## 【0002】

DACは、デジタル入力を受信し、このデジタル入力のアナログ的な等価物であるアナログ出力を電流または電圧の形態で生成する回路である。代表的なDACは、エンコーダと、複数のアナログ出力素子と、加算回路とを含んでいる。エンコーダは、複数の2値データビットによって表現されたデジタル値であるデジタル入力を受信した後に、アナログ出力素子を選択的に作動させるための適切なドライブ信号にこれらの2値データビットデータをエンコードする。そして、これらのドライブ信号に応答し、アナログ出力素子が作動して部分アナログ信号を生成し、これらの部分アナログ信号が、加算回路によって合わせられ、デジタル入力のアナログ表現であるアナログ信号が生成されることになる。

## 【0003】

このDACの動作においてしばしば問題となるのが、「グリッチ(glitch)」と呼ばれる出力エラーの発生であり、これは、主に、DACの出力における部分アナログ信号のタイミング誤りによって発生するものである。このようなグリッチは、それぞれのデジタル入力に対応するアナログ出力が落ち着く最終的な値に影響を与えるものではなく、あるデジタル入力から次の入力に遷移する際にのみ発生するものである。この結果、グリッチによって、出力信号のスペクトルの内容が損なわれることになり、グリッチをアナログ出力として誤って解釈する可能性があることから、高速アプリケーションにおいては重要な懸念材料となる。

## 【0004】

タイミング誤りの原因の1つは、エンコーダ入力におけるデジタル入力のデータビットの到来時刻の違いである。しかしながら、この種のタイミング誤りの原因是、エンコーダの入力においてラッチを使用してデータビットを同期させることにより、簡単に極小化することができる。タイミング誤りの別の原因是、エンコーダの入力とエンコーダの出力との間における差動ロジック遅延である。但し、この場合にも、この種のタイミング誤りの原因是、エンコーダの出力にラッチを追加して慎重にクロックを制御することにより、極小化することができる。更なる別のタイミング誤りの原因是、エンコーダと出力アナログ素子との間の経路長の不一致、および/または、加算回路を介した出力アナログ素子とDACの出力との間における経路長の不一致である。このタイミング誤りの最後の原因是、加算回路とDACの出力との間にスイッチを追加することにより、極小化することができる。即ち、スイッチを使用し、信号が最終的な値に落ち着いた後にのみ、アナログ信号を出力に渡すようにするものである。この結果、スイッチを使用することにより、グリッチを有するアナログ信号の部分を遮断することができる。この技法は、問題となる期間の出力波形をゼロまたはなんらかの基準値に戻すというものであり、従って、一般に、RZ(Return to Zero)法と呼ばれている。

## 【0005】

このRZ法を使用すれば、DACの高速性能が加算ユニット以前の遅延の不一致の影響を受けなくなり、信号の完全性は、主に、スイッチの線形性とスイッチを動作させるのに使用するリサンプリングクロックの純度とによって制約されることになる。これら2つの制約要因の中でも、主要な制約要因はスイッチの線形性である。このスイッチの非線形性は、スイッチの通過電流に対して非線形の関数を有するスイッチの直列抵抗が原因となって発生するものである。また、スイッチの非線形性は、電流のレベルに伴って変化する静電容量などのその他の非線形性の寄生によっても引き起こされる。

## 【発明の開示】

## 【発明が解決しようとする課題】

## 【0006】

このような観点から、スイッチの非線形性を出力信号に持ち込むことなく、デジタル入力をアナログ入力へと変換し、この結果、出力信号におけるグリッチを削減または除去するDACおよび方法に対するニーズが存在する。

## 【課題を解決するための手段】

## 【0007】

10

20

30

40

50

デジタル入力をアナログ出力へと変換するD A Cおよび方法は、リサンプリングスイッチを利用してアナログ出力素子と加算回路との間の部分アナログ信号の伝送を調節して、出力信号における「グリッヂ」を削減または除去する。それぞれのアナログ出力素子によって生成される一定の部分アナログ信号（例えば、一定の電流）を処理するよう、それぞれのリサンプリングスイッチをアナログ出力素子に個々に接続可能である。この結果、リサンプリングスイッチを使用して部分アナログ信号を加算回路に同時に伝送することにより、スイッチの非線形性を出力信号へと伝えることなく、リサンプリングスイッチを使用して出力信号におけるグリッヂを削減または除去することができる。

#### 【0008】

本発明の実施例によるD A Cは、複数のアナログ出力素子と、複数のスイッチと、加算回路とを含んでいる。アナログ出力素子は、デジタル入力に応答して部分アナログ信号（複数）を選択的に生成するよう構成されている。加算回路は、これらの部分アナログ信号を合わせて、デジタル入力のアナログ表現であるアナログ出力を生成するよう構成されている。スイッチは、アナログ出力素子と加算回路との間に配置されており、アナログ出力素子と加算回路との間における部分アナログ信号の伝送を調節する。それぞれのアナログ出力素子によって生成される部分アナログ信号を加算回路に伝送するよう、それぞれのスイッチを個々のアナログ出力素子に接続可能である。

#### 【0009】

本発明の実施例に従ってデジタル入力をアナログ出力へと変換する方法は、デジタル入力を受信するステップと、このデジタル入力に応答して部分アナログ信号を生成するステップと、この部分アナログ信号の伝送を調節するステップと、部分アナログ信号を受信して合わせて、デジタル入力のアナログ表現であるアナログ出力を生成するステップとを含んでいる。

#### 【0010】

本発明のその他の態様および利点については、本発明の原理を一例として図示している添付図面との関連で本明細書の詳細な説明を参照することによって明らかになるであろう。

#### 【発明を実施するための最良の形態】

#### 【0011】

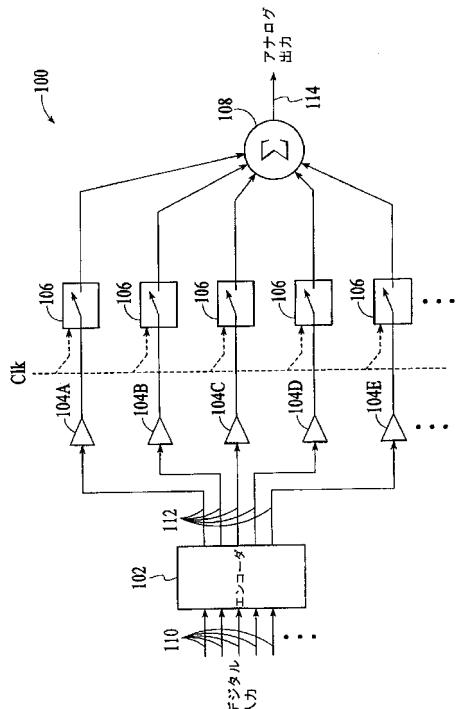

図1を参照すれば、本発明の模範的な実施例によるD A C 1 0 0が示されている。D A C 1 0 0は、受信したデジタル入力に応答してアナログ出力を生成するように動作する。これらアナログ出力の大きさは、個々のデジタル入力が表す値に対応している。従って、これらのアナログ出力は、デジタル入力のアナログ的な等価物になっている。D A C 1 0 0は、エンコーダ1 0 2と、（図1には、5つのアナログ出力素子1 0 4 A、1 0 4 B、1 0 4 C、1 0 4 D、1 0 4 Eのみが示されている）アナログ出力素子1 0 4と、リサンプリングスイッチ1 0 6と、加算回路1 0 8とを含んでいる。この図1に示されているように、リサンプリングスイッチ1 0 6は、アナログ出力素子1 0 4と加算回路1 0 8との間に位置している。後述するように、これらのリサンプリングスイッチ1 0 6を使用することにより、R Z法を使用する従来のD A Cにおいて通常懸念されるスイッチの非線形性が伝えられることなく、「グリッヂ」と呼ばれるD A C 1 0 0の出力信号における出力エラーが削減または除去されることになる。従って、これらのリサンプリングスイッチ1 0 6を使用してグリッヂを削減または除去することにより、出力信号の完全性が損なわれなくなる。

#### 【0012】

D A C 1 0 0のエンコーダ1 0 2は、受信したデジタル入力のN個の2値データビットを、M個のエンコードされた信号に変換するよう動作する（ここで、NおよびMは整数である）。エンコーダ1 0 2は、N個の2値データビットを受信するよう、N本の入力ライン1 1 0に接続されている。また、エンコーダ1 0 2は、アナログ出力要素1 0 4に個々に接続されたM個の制御ライン1 1 2にも接続されており、M個のエンコード信号は、エンコーダからM個の制御ラインを通じてアナログ出力素子に伝送される。これらのM個

10

20

30

40

50

のエンコード信号は、デジタル入力の値に従ってアナログ出力素子 104 を選択的に作動させるのに使用するドライブ信号であり、この結果、アナログ出力素子の作動によって生成されたアナログ信号を使用し、等価なアナログ出力を生成することができる。それぞれのエンコード信号は、アナログ出力素子を作動させるイネーブル信号であるか、または、アナログ出力素子の作動を停止させるディスエーブル信号である。エンコーダ 102 は、2 値データビットを D A C 内においてエンコード信号に変換するのに使用可能なエンコーダであればどのようなものであってもよい。一例として、エンコーダ 102 は、ルックアップテーブルを使用して 2 値データビットを温度計エンコード信号へと変換する標準的な温度計エンコーダであってもよい。

## 【0013】

10

D A C 100 のアナログ出力素子 104 は、エンコーダ 102 からのエンコード信号によって選択的に作動した際に、1つ以上のアナログ信号を生成するように動作する。これらのアナログ出力素子 104 によって生成されるアナログ信号は、部分的なアナログ信号であり、後からこれらの信号を合わせてアナログ出力を生成する。一例として、このアナログ出力素子 104 は、アナログ信号を電流の形態で生成するよう構成することができる。前述のように、アナログ出力素子 104 は、所与のデジタル入力のエンコード信号を受信するように、制御ライン 112 を介してエンコーダ 102 に個々に接続されている。即ち、それぞれのアナログ出力素子 104 は、所与のデジタル入力のエンコード信号の中の1つを受信するように別個の制御ライン 112 を介してエンコーダ 102 に接続されている。この結果、特定の制御ライン 112 上のエンコード信号に応じて、接続されているアナログ出力素子 104 は、部分アナログ信号を生成するように作動するか、または、信号を生成しないように作動を停止することになる。模範的な実施例においては、これらのアナログ出力素子 104 は同一のものになっているので、それぞれのアナログ出力素子は、イネーブルエンコード信号によって作動した際に、同一のアナログ信号（例えば、同一の電流）を生成することになる。それぞれのアナログ出力素子 104 の出力は、リサンプリングスイッチ 106 の中の1つによって加算回路 108 に接続されている。

20

## 【0014】

20

D A C 100 のリサンプリングスイッチ 106 は、リサンプリングクロック信号 C1k を使用して、アナログ出力素子 104 の作動によって生成された部分アナログ信号を加算回路 108 に同時に伝送するように動作する。それぞれのリサンプリングスイッチ 106 は、それぞれのアナログ出力素子によって生成される部分アナログ信号を伝送するように、個別のアナログ出力素子 104 に個々に接続されている。従って、この模範的な実施例においては、リサンプリングスイッチの数は、アナログ出力素子 104 の数と等しくなっている。C1k 信号は、リサンプリングスイッチ 106 の状態を制御し、所与の期間において、すべてのリサンプリングスイッチを同時に開閉する。このようにして、リサンプリングスイッチ 106 は、作動したアナログ出力素子 104 から加算回路 108 への部分アナログ信号の伝送を調節している。リサンプリングスイッチ 106 は、C1k 信号のタイミングを使用し、従来の RZスイッチに類似した機能を実行する。加算回路 108 に伝送される以前に、部分アナログ信号（例えば電流）を最終的な値に落ち着かせるように、リサンプリングスイッチ 106 を動作させることができる。この結果、リサンプリングスイッチ 106 を使用することにより、D A C 100 の最終的な出力信号においてグリッチの原因となるアナログ信号の部分が効果的に除去される。この模範的な実施例においては、これらのリサンプリングスイッチ 106 は、アナログ出力素子 104 の場合と同様に同一のものになっている。従って、閉じた際には、作動したアナログ出力素子 104 に接続されているそれぞれのリサンプリングスイッチ 106 は、そのアナログ出力素子によって生成されたアナログ信号を通過させる。それぞれのリサンプリングスイッチ 106 は、一定のアナログ信号（例えば、一定の電流）を処理しているため、従来の RZスイッチを使用する際に大きな懸念事項であるスイッチの非線形性に関する懸念が、これらのリサンプリングスイッチを使用してアナログ出力素子 104 から加算回路 108 に等価なアナログ信号を同時に伝送することによって解消される。

40

50

## 【0015】

その他の実施例においては、D A C 1 0 0 は、アナログ出力素子 1 0 4 よりも少ない数のリサンプリングスイッチ 1 0 6 を含みうる。これらの実施例においては、アナログ出力素子からの部分アナログ信号を合わせるように、複数のアナログ出力素子 1 0 4 の出力を相互に接続することができる。この結果として生成される出力もリサンプリングスイッチ 1 0 6 の中の 1 つの入力に接続される。即ち、複数のアナログ出力素子 1 0 4 からの合わせられたアナログ信号を伝送するように、それぞれのリサンプリングスイッチ 1 0 6 を接続することができる。D A C 1 0 0 に含まれるリサンプリングスイッチ 1 0 6 の数は、D A C に含まれているアナログ出力素子 1 0 4 の合計数を下回る数であれば、どのようなものであってもよい。

10

## 【0016】

D A C 1 0 0 の加算回路 1 0 8 は、リサンプリングスイッチ 1 0 6 を介して同時に伝送されるアナログ出力素子 1 0 4 からの部分アナログ信号を合わせて、受信したデジタル入力のアナログ的な等価物であるアナログ出力を出力端子 1 1 4 上に生成するように動作する。加算回路 1 0 8 は、アナログ出力素子 1 0 4 からのアナログ信号を線形加算する様々な信号合成方式の中の 1 つを使用してアナログ出力を生成するように構成することができる。一例として、この加算回路 1 0 8 は、アナログ出力素子 1 0 4 からの電流（即ち、部分アナログ信号）の中のいくつかを出力端子 1 1 4 に直接に印加してアナログ出力の最上位ビット信号を供給すると共に、アナログ出力素子からのその他の電流を、出力端子に印加する前に、まず、R - 2 R 構成を使用してスケーリングし、アナログ出力の 2 値スケーリングされた最下位ビット信号を供給する標準的なセグメント化された電流加算方式を使用可能である。加算回路 1 0 8 において使用可能なその他の電流加算方式は、ストレート 2 値加重 R - 2 R 方式と、アナログ出力素子 1 0 4 からの電流を单一の出力負荷抵抗に印加する单一出力負荷抵抗方式とを含む。アナログ出力を電流から電圧へと変換するように、D A C 1 0 0 の出力端子 1 1 4 を電流 / 電圧コンバータ（図示せず）に接続することができる。

20

## 【0017】

D A C 1 0 0 によって生成されるアナログ出力の線形性は、リサンプリングスイッチ 1 0 6 の基本的な直列線形性によって左右されることはない。例えば、それぞれのリサンプリングスイッチ 1 0 6 の出力電流が、 $I_{out} = I_{in} + A * I_{in}^2$  などの関数によって定義される入力電流との非線形関係を有していると仮定する（ここで、 $I_{out}$  は、リサンプリングスイッチの出力電流であり、 $I_{in}$  は、リサンプリングスイッチの入力電流であり、A は定数である）。この結果、それぞれのリサンプリングスイッチ 1 0 6 の出力電流において生成され得る値は、エンコード信号「0」（ディスエーブル）に対する $I_0$ 、またはエンコード信号「1」（イネーブル）に対する $I_1$  という 2 つのみである。制御ライン 1 1 2 に n 個の 1 が存在する場合には、信号は、加算回路 1 0 8 において合わせられた後に、 $n * I_1 + (M - n) * I_0$  となる。利得およびオフセットエラーを信号に含む可能性はあるものの、これは、n の線形関数である。

30

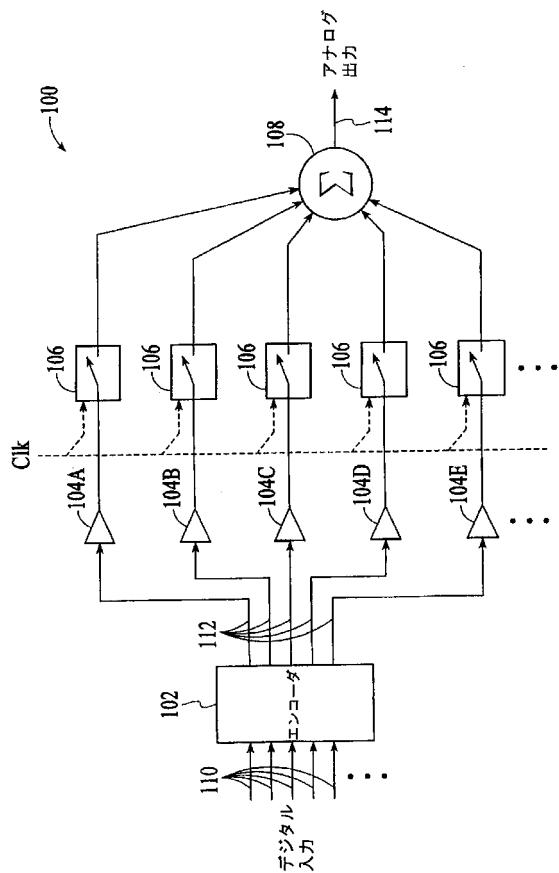

## 【0018】

次に、図 2 を参照すると、本発明の実施例による標準的なセグメント化された D A C アーキテクチャによって構成された D A C 2 0 0 の一部が示されている。この図 2 においては、図 1 と同一の参照符号を使用して類似の素子を識別している。この図 2 には、D A C 2 0 0 用のエンコーダは示されていない。D A C 2 0 0 は、R - 2 R 出力加算回路 2 0 8 を含んでおり、これは、リサンプリングスイッチ 1 0 6 を介してアナログ出力素子 1 0 4 A と 1 0 4 B と 1 0 4 C と 1 0 4 D と 1 0 4 E とに電気的に接続されている。この実施例においては、それぞれのアナログ出力素子は、同一のアナログ信号（例えば、同一の電流）を生成するものになっている。しかしながら、アナログ出力素子の R - 2 R 出力加算回路 2 0 8 への接続形態に応じて、特定のアナログ出力素子からのアナログ信号全体またはアナログ信号をスケーリングした一部を出力端子 1 1 4 に伝送し、最終的なアナログ出力を生成することができる。即ち、（例えば、アナログ出力素子 1 0 4 A と 1 0 4 B と 1 0

40

50

4 Cなどの)出力端子 114 に直接に接続されているアナログ出力素子の場合には、これらのアナログ出力素子が生成するアナログ信号の全体が出力端子 114 に伝送される。一方、(例えば、アナログ出力素子 104D および 104E などの)1つ以上のR抵抗器および2R抵抗器を介して出力端子 114 に接続されているアナログ出力素子の場合には、これらのアナログ出力素子が生成するアナログ信号を2値スケーリングした部分が出力端子 114 に伝送される。出力端子 114 に直接に接続されているアナログ出力素子は、(大きな固定アナログ信号である)アナログ信号の最上位ビット(MSB)信号を供給するものと考えることができ、1つ以上のR抵抗器および2R抵抗器を介して出力端子 114 に接続されているアナログ出力素子は、(小さなスケーリングされた信号である)アナログ出力の最下位ビット(LSB)信号を提供するものと考えることができる。そして、これらのMSB信号およびLSB信号が出力端子 114 において合わせられ、アナログ出力が生成される。図示を容易にするために、図2は、MSB信号を生成する3つのアナログ出力素子 104A と 104B と 104C と、LSB信号を生成する2つのアナログ出力素子 104D および 104E しか示していない。しかしながら、アナログ出力の生成に必要なMSBおよびLSB信号を生成するようにDAC200に含まれるアナログ出力素子の数を格段に大きなものにすることができる。一例として、DAC200は、14ビットのD/A変換のために、MSB信号を生成する32個のアナログ出力素子と、LSB信号を生成する9個のアナログ出力素子を含みうる。

## 【0019】

以上においては、説明を簡便にするべく、図1および図2のDAC100および200は、所与のデジタル入力に対して単一のアナログ出力を生成するよう構成されているものとして図示して説明している。しかしながら、DAC100および200は、所与のデジタル入力に対して差動アナログ出力の組を生成するよう変更することもできる(このことは、特定のアプリケーションにおいて望ましい)。

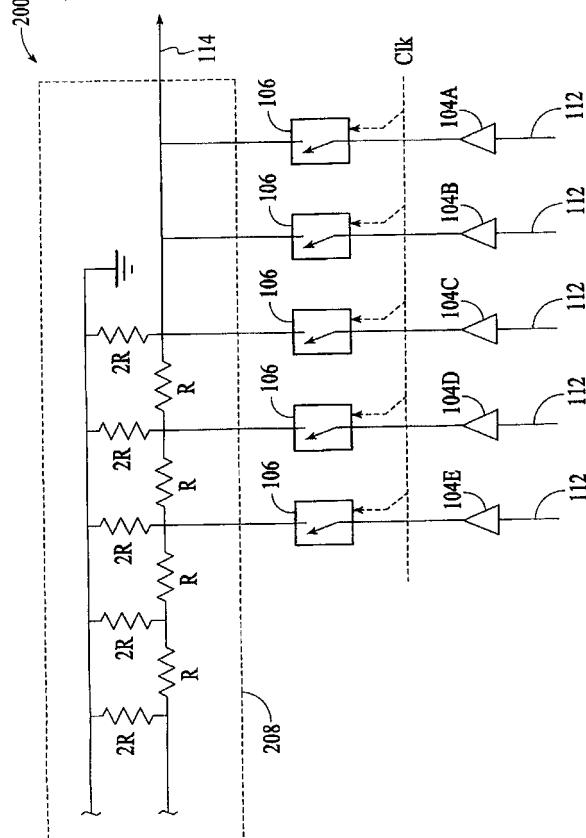

## 【0020】

図3には、模範的な差動実装によるアナログ出力素子304とリサンプリングスイッチ306とが示されている。これらのアナログ出力素子304およびリサンプリングスイッチ306は、図1のDAC100または図2のDAC200において使用可能である。アナログ出力素子304およびリサンプリングスイッチ306は、エンコード信号Dおよび

## 【0021】

## 【数1】

$\overline{D}$

## 【0022】

と、リサンプリングクロック信号Clkおよび

## 【0023】

## 【数2】

$\overline{Clk}$

## 【0024】

を使用し、差動アナログ信号 $I_{out}$ および

## 【0025】

## 【数3】

$\overline{I_{out}}$

## 【0026】

を生成するよう構成されている。アナログ出力素子304は、差動接続されたバイポーラトランジスタ316および318と、電流源320とを含んでいる。差動接続されたトランジスタ316および318のエミッタは、電流源320に接続されている。差動接続されたトランジスタ316のベースは、エンコード信号Dを受信するように接続されており

10

20

30

40

50

、差動接続されたトランジスタ 318 のベースは、エンコード信号

【0027】

【数4】

$\overline{D}$

【0028】

を受信するように接続されている。電流源 320 は、バイポーラトランジスタ 322 と抵抗器 324 を含んでおり、これらは、低電圧端子 326 (例: -3.3V) に直列に接続されている。バイポーラトランジスタ 322 のベースは、このトランジスタを流れる電流を制御するバイアス電圧  $V_{bias}$  を取得するように接続されている。この電流源 320 のバイポーラトランジスタ 322 および抵抗 324 は、 $I_{out}$  および

【0029】

【数5】

$\overline{\overline{I}_{out}}$

【0030】

の値を定義する一定電流  $I_{source}$  を流すように動作する。

【0031】

アナログ出力素子 304 の差動接続されたトランジスタ 316 および 318 は、リサンプリングスイッチ 306 に接続されており、これは、バイポーラリサンプリングトランジスタ 328 と 330 と 332 と 334 とを含んでいる。リサンプリングトランジスタ 328 および 330 のエミッタは、アナログ出力素子 304 の差動接続されたトランジスタ 316 のコレクタに接続されており、リサンプリングトランジスタ 332 および 334 のエミッタは、アナログ出力素子のもう一方の差動接続されたトランジスタ 318 のコレクタに接続されている。また、リサンプリングトランジスタ 328 のコレクタは、差動アナログ信号  $I_{out}$  を伝送するよう加算回路 208A (図示せず) に接続されている。同様に、リサンプリングトランジスタ 332 のコレクタは、差動アナログ信号

【0032】

【数6】

$\overline{\overline{I}_{out}}$

30

【0033】

を伝送するように、加算回路 208B (図示せず) に接続されている。これらの加算回路 208A および 208B は、図 2 の加算回路 208 と同一のものであってもよい。加算回路 208A および 208B は、アナログ出力素子から差動アナログ信号を受信し、差動アナログ出力を生成するよう構成されている。リサンプリングトランジスタ 328 および 332 は、トランジスタ 328 および 332 のベースに印加されるクロック信号  $C_{lk}$  によって制御されている。一方、リサンプリングトランジスタ 330 および 334 は、トランジスタ 330 および 334 のベースに印加されるクロック信号

【0034】

【数7】

$\overline{Clk}$

40

【0035】

によって制御されている。リサンプリングトランジスタ 330 および 334 のコレクタは、クロック信号

【0036】

【数8】

$\overline{Clk}$

50

## 【0037】

がハイの場合には、グリッチを有する遷移によって損なわれたリサンプリングトランジスタ330および334からの電流を処分するように、(例えば接地用の)電圧端子336に接続されている。

## 【0038】

なお、これらのアナログ出力素子304およびリサンプリングスイッチ306のトランジスタは、バイポーラトランジスタであるものとして図示して説明しているが、この代わりに、その他のタイプのトランジスタを使用することもできる。一例として、アナログ出力素子304およびリサンプリングスイッチ306のトランジスタは、MOSトランジスタであってもよい。あるいは、この代わりに、これらのトランジスタは、異なるタイプのトランジスタが混在したものであってもよい。

## 【0039】

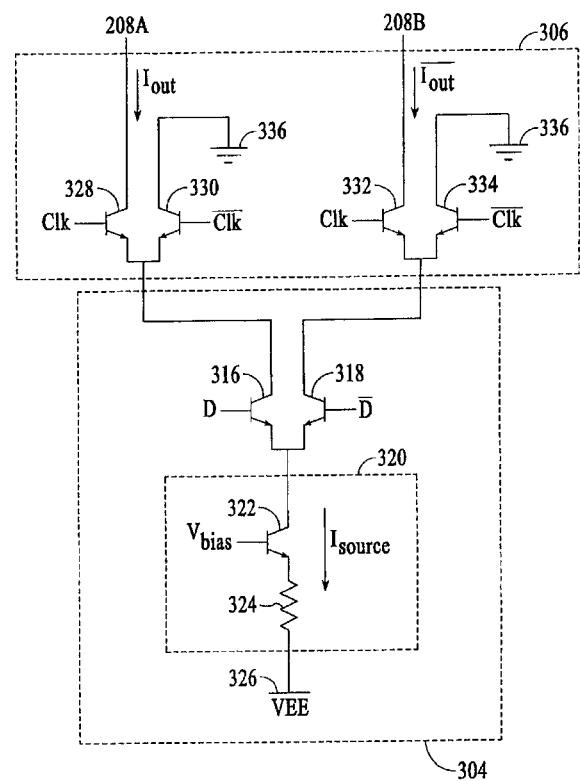

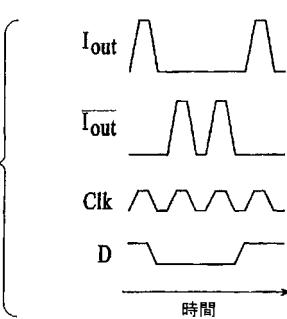

次に、図4を参照すると、信号 $I_{out}$ 、

## 【0040】

## 【数9】

$$\overline{I_{out}}$$

## 【0041】

、C1k、およびDのタイミングチャートが示されている。これらの信号は、アナログ出力素子304および対応するリサンプリングスイッチ306の動作を説明するための例である。このタイミングチャートに示されているように、クロック信号C1kとエンコード信号Dの両方がハイの場合には、ハイの差動信号 $I_{out}$ が生成され、クロック信号C1kがハイであり、エンコード信号Dがローの場合には、ハイの差動信号

## 【0042】

## 【数10】

$$\overline{I_{out}}$$

## 【0043】

が生成される。そして、タイミングチャートに更に示されているように、クロック信号C1kは、クロック信号C1kがローの場合にのみ、エンコード信号Dが変化するように、エンコード信号Dから時間的にずれている。従って、差動アナログ信号 $I_{out}$ および

## 【0044】

## 【数11】

$$\overline{I_{out}}$$

## 【0045】

は、クロック信号C1kが再度上昇する前に落ち着くことができるようになっており、この結果、クリーンな出力パルスが生成される。

## 【0046】

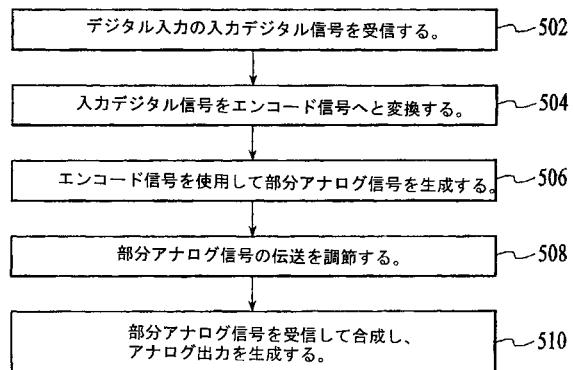

図5のフローチャートを参照し、模範的な実施例によってデジタル入力をアナログ出力へと変換する方法について説明する。まず、ブロック502において、デジタル入力の入力デジタル信号を受信する。このデジタル入力の入力デジタル信号は、1つの値を表している。次に、ブロック504において、この入力デジタル信号をエンコード信号へと変換する。一例として、このエンコード信号は、温度計エンコード信号でありうる。そして、ブロック506において、このエンコード信号を使用して部分アナログ信号を生成する。この部分アナログ信号は、エンコード信号をドライブ信号として使用してアナログ出力素子を選択的に作動させることによって生成することができる。次に、ブロック508において、この部分アナログ信号の伝送を調節する。一例として、いくつかのリサンプリングスイッチを使用し、クロック信号によってリサンプリングスイッチを同時に開閉して部分アナログ信号を同時に伝送することにより、部分アナログ信号の伝送を制御することがで

10

20

30

40

50

きるので、スイッチの非線形性を伝えることなく、最終的に生成される出力信号においてグリッチを削減または除去することができる。クロック信号は、スイッチが開いている際に関連する電気信号が落ち着くことができるよう、入力デジタル信号における遷移と時間的にずらしておく必要がある。そして、ブロック 510 において、部分アナログ信号を受信し、既定の方式を使用して合わせて、デジタル入力のアナログ表現であるアナログ出力を生成する。一例として、R - 2 R 構成を使用する標準的なセグメント化された合成方式を使用して、これらの部分アナログ信号を合成することができる。

#### 【0047】

以上、本発明の特定の実施例について説明して図示してきたが、本発明は、これらの説明および図示した特定の形態または部品の配列に限定されるものではない。本発明の範囲は、添付の特許請求の範囲とそれらの等価物とによって定義されている。10

#### 【図面の簡単な説明】

#### 【0048】

【図1】本発明の模範的な実施例によるD A Cを示す概略構成図である。

【図2】本発明の実施例による標準的なセグメント化されたD A Cアーキテクチャによって構成されたD A Cの部分図である。

【図3】模範的な実装による図1または図2のD A Cにおいて使用可能なアナログ出力素子およびリサンプリングスイッチの回路図である。

【図4】図3のアナログ出力素子およびリサンプリングスイッチのタイミングチャートである。20

【図5】本発明の模範的な実施例に従ってデジタル入力をアナログ出力に変換する方法のプロセスフローチャートである。

#### 【符号の説明】

#### 【0049】

104A、104B、104C、104D、104E、304 アナログ出力素子

106、306 スイッチ

108、208、208A、208B 加算回路

316、318 トランジスタ

320 電流源

326 電圧端子

20

30

【図1】

【図2】

【図3】

【図4】

【図5】

---

フロントページの続き

(72)発明者 ロバート・イー・ジェウェット

アメリカ合衆国カリフォルニア州94061, レッドウッド・シティ, ストーニー ヒル ロード

962

(72)発明者 ジャッキー・キン・チー・リュウ

アメリカ合衆国カリフォルニア州94086, サニーヴェイル, ヴィセンテ ドライヴ 1229

, アパートメント 26

F ターム(参考) 5J022 AB03 BA02 BA04 CB06 CD03 CE01 CF04

5J055 AX22 BX17 DX04 EX06 EY01 EY17 EZ24 FX04 GX01