(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第6769029号

(P6769029)

(45) 発行日 令和2年10月14日(2020.10.14)

(24) 登録日 令和2年9月28日(2020.9.28)

(51) Int.Cl.

F 1

H03M 1/74 (2006.01)

H03B 5/32 (2006.01)H03M 1/74

H03B 5/32

A

請求項の数 8 (全 39 頁)

(21) 出願番号 特願2015-242798 (P2015-242798)

(22) 出願日 平成27年12月14日 (2015.12.14)

(65) 公開番号 特開2017-112399 (P2017-112399A)

(43) 公開日 平成29年6月22日 (2017.6.22)

審査請求日 平成30年12月10日 (2018.12.10)

(73) 特許権者 000002369

セイコーエプソン株式会社

東京都新宿区新宿四丁目1番6号

(74) 代理人 100104710

弁理士 竹腰 昇

(74) 代理人 100090479

弁理士 井上 一

(74) 代理人 100124682

弁理士 黒田 泰

(72) 発明者 磯崎 繁紀

長野県諏訪市大和3丁目3番5号 セイコーエプソン株式会社内

審査官 渡井 高広

最終頁に続く

(54) 【発明の名称】 D／A変換器、回路装置、発振器、電子機器及び移動体

## (57) 【特許請求の範囲】

## 【請求項 1】

入力データのデコード処理を行って、制御信号を出力するデコーダーと、複数の電圧を生成して出力する電圧生成回路と、前記電圧生成回路からの前記複数の電圧と前記デコーダーからの前記制御信号に基づいて、前記複数の電圧の中から前記入力データに対応する電圧をD／A変換電圧として選択して出力する電圧選択回路と、

を含み、

前記電圧選択回路は、

前段のセレクターブロックが有するセレクターの出力が後段のセレクターブロックが有するセレクターに入力される複数段のセレクターブロックを含み、

前記複数段のセレクターブロックの1段目のセレクターブロックには、前記複数の電圧が入力され、前記複数段のセレクターブロックの最終段のセレクターブロックが、前記D／A変換電圧を出力し、

前記複数段のセレクターブロックの各々は、電源ノードから近い側の第1のトランジスター及び前記電源ノードから遠い側の第2のトランジスターを含む複数のトランジスターにより構成され、前記第2のトランジスターのしきい値電圧は、前記第1のトランジスターのしきい値電圧より低く、

前記第1のトランジスターとして、高電位側電源ノードから近い側の第1のP型トランジスターと、低電位側電源ノードから近い側の第1のN型トランジスターを含み、

10

20

前記第2のトランジスターとして、前記高電位側電源ノードから遠い側の第2のP型トランジスターと、前記低電位側電源ノードから遠い側の第2のN型トランジスターを含み、

前記第2のP型トランジスターのしきい値電圧は、前記第1のP型トランジスターのしきい値電圧より低く、

前記第2のN型トランジスターのしきい値電圧は、前記第1のN型トランジスターのしきい値電圧より低く、

前記第1のP型トランジスター及び前記第1のN型トランジスターは、高耐圧用の製造プロセスにより形成されるトランジスターであり、前記第2のP型トランジスター及び前記第2のN型トランジスターは、前記高耐圧用の製造プロセスよりトランジスター耐圧が低くなる低耐圧用の製造プロセスにより形成されるトランジスターであることを特徴とするD/A変換器。10

#### 【請求項2】

請求項1に記載のD/A変換器において、

前記最終段のセレクターブロックを構成する少なくとも1つのトランジスターは、基板電圧が制御されるトランジスターであることを特徴とするD/A変換器。

#### 【請求項3】

請求項1又は2に記載のD/A変換器において、

前記最終段のセレクターブロックのセレクターは、前段のセレクターブロックからI個(I=3)の電圧が入力され、1個の前記D/A変換電圧を出力するセレクターであることを特徴とするD/A変換器。20

#### 【請求項4】

請求項1乃至3のいずれか一項に記載のD/A変換器と、

前記D/A変換器に電源電圧を供給する電源回路と、

を含み、

前記電源回路は、

トランジスターの仕事関数差に基づき生成された基準電圧を生成する基準電圧生成回路を有し、前記基準電圧生成回路により生成された前記基準電圧を前記電源電圧として、前記D/A変換器に供給することを特徴とする回路装置。

#### 【請求項5】

請求項1乃至3のいずれか一項に記載のD/A変換器を含む回路装置であって、

温度センサー部からの温度検出電圧のA/D変換を行い、温度検出データを出力するA/D変換部と、

前記温度検出データに基づく周波数制御データを出力する処理部と、

前記処理部からの前記周波数制御データと振動子を用いて、前記周波数制御データにより設定される発振周波数の発振信号を生成する発振信号生成回路と、

を含み、

前記発振信号生成回路は、

前記D/A変換器を含み、前記処理部からの前記周波数制御データのD/A変換を行うD/A変換部と、40

前記D/A変換部の出力電圧と前記振動子を用いて、前記発振信号を生成する発振回路と、

を含むことを特徴とする回路装置。

#### 【請求項6】

請求項5に記載の回路装置と、

前記振動子と、

を含むことを特徴とする発振器。

#### 【請求項7】

請求項1乃至3のいずれか一項に記載のD/A変換器を含むことを特徴とする電子機器

。

**【請求項 8】**

請求項 1 乃至 3 のいずれか一項に記載の D / A 変換器を含むことを特徴とする移動体。

**【発明の詳細な説明】****【技術分野】****【0 0 0 1】**

本発明は、D / A 変換器、回路装置、発振器、電子機器及び移動体等に関する。

**【背景技術】****【0 0 0 2】**

従来より、温度補償型発振器等の発振器用の回路装置や、液晶パネルを駆動する表示ドライバーの回路装置などでは、デジタルデータをアナログ電圧に変換する D / A 変換器が用いられる。例えば温度補償型発振器用の回路装置では、周波数制御データの D / A 変換に D / A 変換器が用いられる。或いは、温度検出電圧を A / D 変換する A / D 変換部において D / A 変換器が用いられる。表示ドライバーの回路装置では、複数の階調電圧から表示データに対応する階調電圧を選択する回路として、D / A 変換器が用いられる。例えば特許文献 1 には、表示ドライバーの回路装置に用いられる D / A 変換器の構成例が開示されている。10

**【0 0 0 3】**

特許文献 1 に開示される D / A 変換器では、入力された複数の電圧の中から、入力データに対応する電圧を選択することで、入力データに対応する D / A 変換電圧を出力する。20

D / A 変換器が有する電圧選択回路は、複数のセレクターブロックを有し、これらの複数のセレクターブロックにより、いわゆるトーナメント方式で電圧を選択することで、入力電圧に対応する D / A 変換電圧を求める。

**【先行技術文献】****【特許文献】****【0 0 0 4】****【特許文献 1】特開 2009 - 118457 号公報****【発明の概要】****【発明が解決しようとする課題】****【0 0 0 5】**

このような D / A 変換器では、低消費電力化に対する要求がある。例えば D / A 変換器は、電圧生成回路を有しており、電圧生成回路は、直列接続された複数の抵抗により電源電圧を電圧分割することで、電圧選択回路に入力される複数の電圧を生成する。そして、この直列接続された複数の抵抗には常に電流が流れる。このため、D / A 変換器の低消費電力化を図るために、電圧生成回路に供給される電源電圧をなるべく低い電圧にすることが望ましい。また D / A 変換器以外の回路装置の他の回路の低消費電力化という意味でも、電源電圧をなるべく低い電圧にすることが望ましい。30

**【0 0 0 6】**

ところが、電圧選択回路を構成するセレクターは、P 型や N 型のトランジスターにより構成されており、電源電圧が低くなると、これらのトランジスターのオン条件やオフ条件などの種々の条件を満たすことが難しいということが判明した。40

**【0 0 0 7】**

本発明の幾つかの態様によれば、低消費電力化を図りながらも適正な電圧選択を行って D / A 変換電圧を出力できる D / A 変換器、回路装置、発振器、電子機器及び移動体等を提供できる。

**【課題を解決するための手段】****【0 0 0 8】**

本発明の一態様は、入力データのデコード処理を行って、制御信号を出力するデコーダーと、複数の電圧を生成して出力する電圧生成回路と、前記電圧生成回路からの前記複数の電圧と前記デコーダーからの前記制御信号に基づいて、前記複数の電圧の中から前記入力データに対応する電圧を D / A 変換電圧として選択して出力する電圧選択回路と、を含50

み、前記電圧選択回路は、前段のセレクターブロックが有するセレクターの出力が後段のセレクターブロックが有するセレクターに入力される複数段のセレクターブロックを含み、前記複数段のセレクターブロックの1段目のセレクターブロックには、前記複数の電圧が入力され、前記複数段のセレクターブロックの最終段のセレクターブロックが、前記D/A変換電圧を出力し、前記複数段のセレクターブロックの各々は複数のトランジスターにより構成され、セレクターブロックを構成する複数のトランジスターのうち、電源ノードから遠い側の第2のトランジスターは、前記電源ノードから近い側の第1のトランジスターに比べて、低いしきい値電圧に設定されているD/A変換器に関係する。

#### 【0009】

本発明の一態様によれば、電圧生成回路が生成した複数の電圧が、電圧選択回路の1段目のセレクターブロックに入力され、デコーダーからの制御信号に基づく電圧選択により、最終段のセレクターブロックから、入力データに対応するD/A変換電圧が出力される。そしてセレクターブロックを構成する複数のトランジスターのうち、電源ノードから遠い側の第2のトランジスターは、電源ノードから近い側の第1のトランジスターに比べて、低いしきい値電圧に設定されている。このようにすれば、例えば低消費電力化のために電源電圧を低い電圧にした場合にも、電源ノードから遠い側の第2のトランジスターが低いしきい値電圧に設定されていることで、電圧選択回路による適正な電圧選択を実現できる。従って、低消費電力化を図りながらも適正な電圧選択を行ってD/A変換電圧を出力できるD/A変換器の提供が可能になる。

#### 【0010】

また本発明の一態様では、前記セレクターブロックを構成する前記複数のトランジスターのうち、高電位側電源ノードから遠い側の第2のP型トランジスターは、前記高電位側電源ノードから近い側の第1のP型トランジスターに比べて、低いしきい値電圧に設定され、低電位側電源ノードから遠い側の第2のN型トランジスターは、前記低電位側電源ノードから近い側の第1のN型トランジスターのしきい値電圧に比べて、低いしきい値電圧に設定されていてもよい。

#### 【0011】

このようにすれば、P型トランジスターについては、高電位側電源ノードから遠い側の第2のP型トランジスターのしきい値電圧を低い電圧に設定し、N型トランジスターについては、低電位側電源ノードから遠い側の第2のN型トランジスターのしきい値電圧を低い電圧に設定することで、低消費電力化と適正な電圧選択とを両立できるようになる。

#### 【0012】

また本発明の一態様では、前記第1のトランジスターは、しきい値電圧のティピカル値が第1のしきい値電圧である第1の種類のトランジスターであり、前記第2のトランジスターは、前記しきい値電圧のティピカル値が前記第1のしきい値電圧よりも低い第2のしきい値電圧である第2の種類のトランジスターであってもよい。

#### 【0013】

このようにすれば、トランジスターの種類の設定により、第2のトランジスターのしきい値電圧を低い電圧に設定できるようになる。

#### 【0014】

また本発明の一態様では、前記第1のトランジスターと前記第2のトランジスターとは、ゲート長が異なっていてもよい。

#### 【0015】

このようにすれば、ゲート長の設定により、第2のトランジスター等のしきい値電圧の微調整が可能になる。

#### 【0016】

また本発明の一態様では、前記セレクターブロックを構成する前記複数のトランジスターのうち、前記第2のトランジスターよりも前記電源ノードから遠い側の第3のトランジスターは、前記第2のトランジスターに比べて、低いしきい値電圧に設定されていてもよい。

10

20

30

40

50

**【 0 0 1 7 】**

このようにすれば、第2のトランジスターよりも電源ノードから遠い側の第3のトランジスターのしきい値電圧を低い電圧に設定することで、電源電圧が更に低い電圧に設定された場合等にも、低消費電力化と適正な電圧選択とを両立できるようになる。

**【 0 0 1 8 】**

また本発明の一態様では、前記第1のトランジスターは、しきい値電圧のティピカル値が第1のしきい値電圧である第1の種類のトランジスターであり、前記第2のトランジスターは、前記しきい値電圧のティピカル値が前記第1のしきい値電圧よりも低い第2のしきい値電圧である第2の種類のトランジスターであり、前記第3のトランジスターは、前記しきい値電圧のティピカル値が前記第2のしきい値電圧よりも低い第3のしきい値電圧である第3の種類のトランジスターであってもよい。10

**【 0 0 1 9 】**

このようにすれば、トランジスターの種類の設定により、第2、第3のトランジスターのしきい値電圧を低い電圧に設定できるようになる。

**【 0 0 2 0 】**

また本発明の一態様では、前記第1、第2、第3のトランジスターのうちの少なくとも1つのトランジスターは、前記第1、第2、第3のトランジスターのうちの他のトランジスターとは、ゲート長が異なっていてもよい。

**【 0 0 2 1 】**

このようにすれば、ゲート長の設定により、第2、第3のトランジスター等のしきい値電圧の微調整等が可能になる。20

**【 0 0 2 2 】**

また本発明の一態様では、前記第1のトランジスターと前記第2のトランジスターとは、トランジスターの製造プロセスパラメーターが異なることで、異なるしきい値電圧に設定されていてもよい。

**【 0 0 2 3 】**

このようにすれば、トランジスターの製造プロセスパラメーターの設定により、第2のトランジスターのしきい値電圧を低い電圧に設定できるようになる。

**【 0 0 2 4 】**

また本発明の一態様では、前記最終段のセレクターブロックを構成する少なくとも1つのトランジスターのゲート長は、前記最終段のセレクターブロックを構成する他のトランジスターのゲート長よりも長くてもよい。30

**【 0 0 2 5 】**

このようにすれば、最終段のセレクターブロックを構成する複数のトランジスターにおいて、オン条件やオフ条件等の種々の条件を満たすためのしきい値電圧の微調整を実現できるようになる。

**【 0 0 2 6 】**

また本発明の一態様では、前記最終段のセレクターブロックを構成する少なくとも1つのトランジスターのゲート長は、前記1段目のセレクターブロックを構成するトランジスターのゲート長よりも長くてもよい。40

**【 0 0 2 7 】**

このようにすれば、1段目のセレクターブロックを構成するトランジスターに比べて、オン条件等を満たすことが厳しい最終段のセレクターブロックを構成するトランジスターのしきい値電圧を、ゲート長の設定により微調整することが可能になる。

**【 0 0 2 8 】**

また本発明の一態様では、前記最終段のセレクターブロックを構成する少なくとも1つのトランジスターは、基板電圧が制御されるトランジスターであってもよい。

**【 0 0 2 9 】**

このようにすれば、オン条件等を満たすことが厳しい最終段のセレクターブロックを構成するトランジスターのしきい値電圧を、基板電圧の制御により微調整することが可能に50

なる。

**【0030】**

また本発明の一態様では、前記最終段のセレクターブロックのセレクターは、前段のセレクターブロックから $I$ 個( $I \geq 3$ )の電圧が入力され、1個の前記D/A変換電圧を出力するセレクターであってもよい。

**【0031】**

このようにすれば、例えば2入力/1出力のセレクターを最終段のセレクターとして用いる場合に比べて、最終段のセレクターを構成するトランジスターの入力電圧範囲を狭くでき、トランジスターのオン条件等を満たすしきい値電圧の設定を容易化できる。

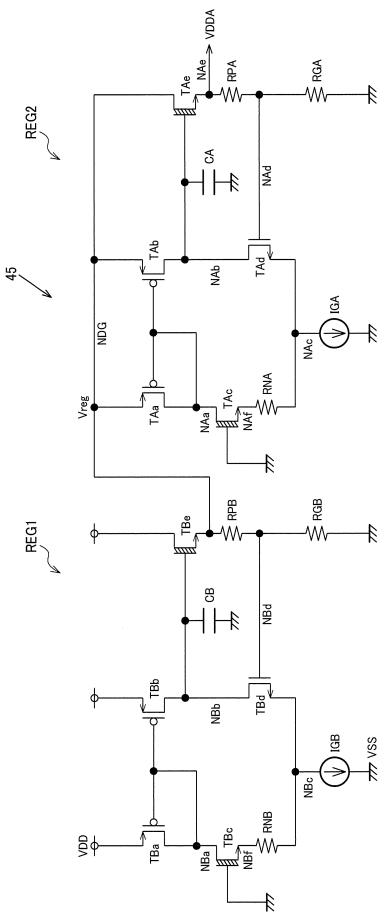

**【0032】**

また本発明の他の態様は、上記に記載のD/A変換器と、前記D/A変換器に電源電圧を供給する電源回路と、を含み、前記電源回路は、トランジスターの仕事関数差に基づき生成された基準電圧を生成する基準電圧生成回路を有し、前記基準電圧生成回路により生成された前記基準電圧を前記電源電圧として、前記D/A変換器に供給する回路装置に関係する。

**【0033】**

このように、基準電圧生成回路が仕事関数差に基づき生成した電源電圧を、D/A変換器に供給すれば、他の回路方式の基準電圧生成回路を用いる場合に比べて、低消費電力化を図れるようになる。そして、このような基準電圧生成回路により生成された電源電圧が、低い電圧である場合にも、D/A変換器は適正な電圧選択を行うことができるため、低消費電力化と適正な電圧選択とを両立できるようになる。

**【0034】**

また本発明の他の態様は、上記に記載のD/A変換器を含む回路装置であって、温度センサー部からの温度検出電圧のA/D変換を行い、温度検出データを出力するA/D変換部と、前記温度検出データに基づいて発振周波数の温度補償処理を行い、前記発振周波数の周波数制御データを出力する処理部と、前記処理部からの前記周波数制御データと振動子を用いて、前記周波数制御データにより設定される前記発振周波数の発振信号を生成する発振信号生成回路と、を含み、前記発振信号生成回路は、前記D/A変換器を含み、前記処理部からの前記周波数制御データのD/A変換を行うD/A変換部と、前記D/A変換部の出力電圧と前記振動子を用いて、前記発振信号を生成する発振回路と、を含む回路装置に関係する。

**【0035】**

このようにすれば、消費電力が低く適正な電圧選択が可能なD/A変換器を用いて、周波数制御データのD/A変換を行うことが可能になり、回路装置の低消費電力化と性能向上とを両立して実現できるようになる。

**【0036】**

また本発明の他の態様は、上記に記載の回路装置と、前記振動子と、を含む発振器に関係する。

**【0037】**

また本発明の他の態様は、上記に記載のD/A変換器を含む電子機器に関係する。

40

**【0038】**

また本発明の他の態様は、上記に記載のD/A変換器を含む移動体に関係する。

**【図面の簡単な説明】**

**【0039】**

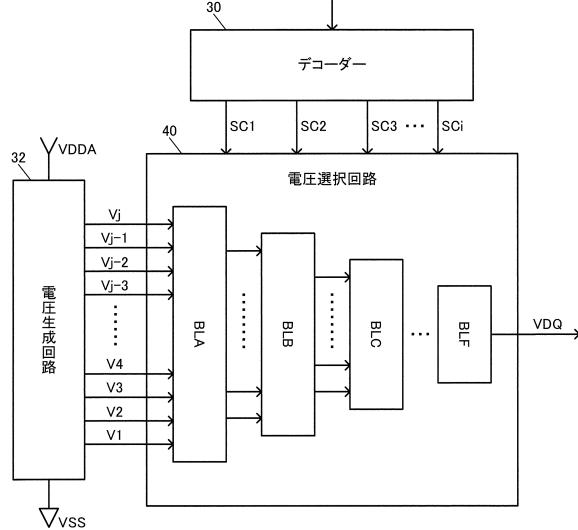

**【図1】**本実施形態のD/A変換器の構成例。

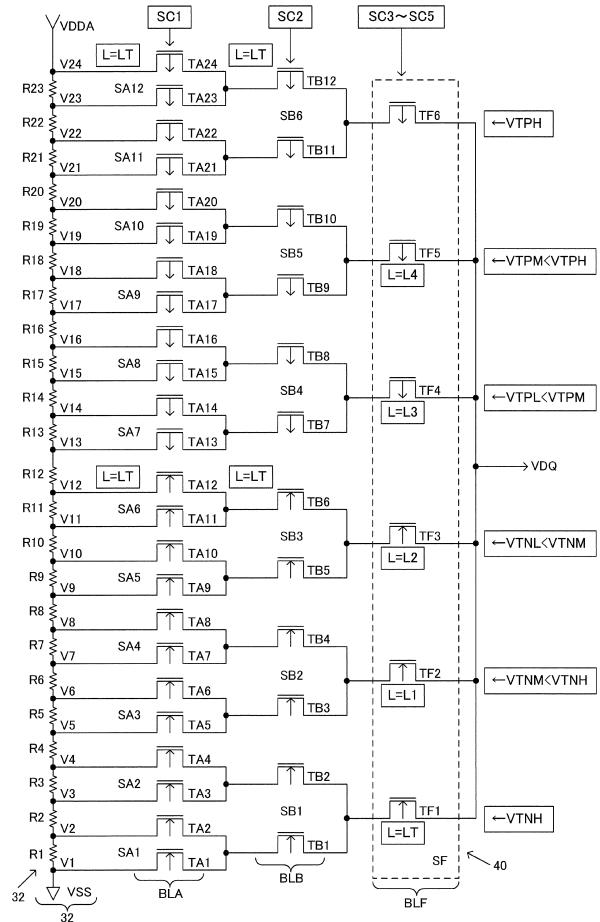

**【図2】**電圧選択回路、電圧生成回路の構成例。

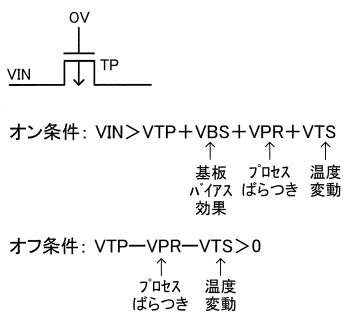

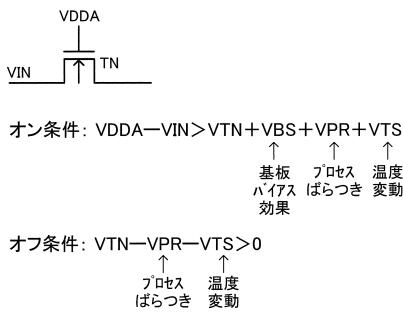

**【図3】**図3A、図3Bはトランジスターのオン条件、オフ条件の説明図。

**【図4】**図4A、図4Bは本実施形態のしきい値電圧設定手法の説明図。

**【図5】**オフリード電流により発生する問題点についての説明図。

**【図6】**図6A～図6Dはゲート長によりしきい値電圧を調整する手法の説明図。

50

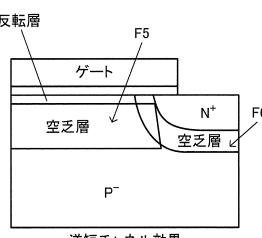

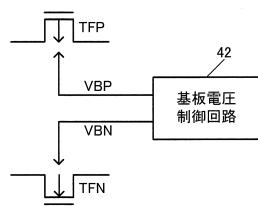

【図7】図7A～図7Cは基板電圧の制御によりしきい値電圧を調整する手法の説明図。

【図8】しきい値電圧の設定の具体例。

【図9】しきい値電圧の設定の他の具体例。

【図10】図10Aは回路装置、電子機器の構成例、図10Bは基準電圧生成回路の第1の構成例。

【図11】基準電圧生成回路の第2の構成例。

【図12】本実施形態の回路装置の構成例。

【図13】本実施形態の回路装置の詳細な構成例。

【図14】図14A、図14Bは温度補償処理の説明図。

【図15】D/A変換部の詳細な構成例。

【図16】D/A変換部の更に詳細な構成例。

【図17】図17A、図17B、図17CはPWM変調の説明図。

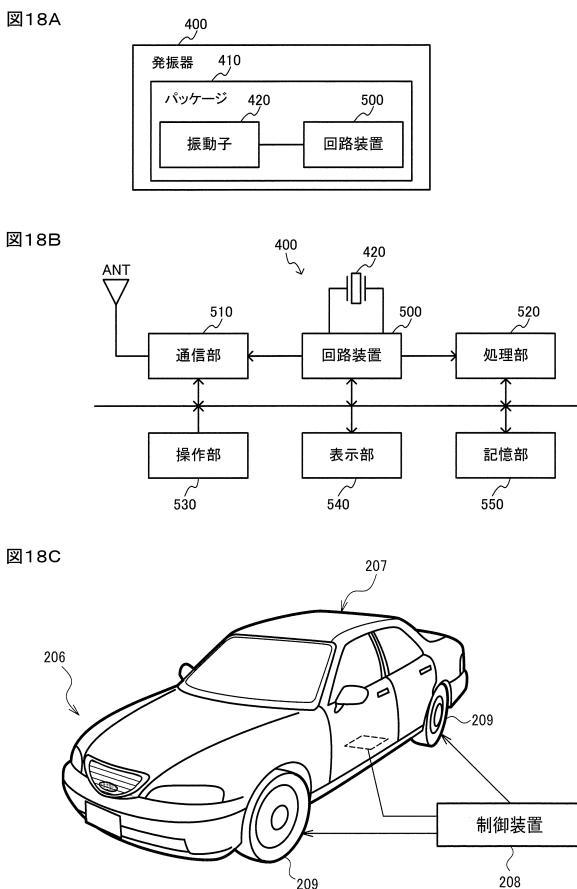

【図18】図18A、図18B、図18Cは発振器、電子機器、移動体の構成例。

【発明を実施するための形態】

【0040】

以下、本発明の好適な実施の形態について詳細に説明する。なお以下に説明する本実施形態は特許請求の範囲に記載された本発明の内容を不当に限定するものではなく、本実施形態で説明される構成の全てが本発明の解決手段として必須であるとは限らない。

【0041】

#### 1. D/A変換器の構成

図1に本実施形態のD/A変換器の構成例を示す。D/A変換器は、デコーダー30、電圧生成回路32、電圧選択回路40を含む。なおD/A変換器の構成は図1の構成には限定されず、その一部の構成要素を省略したり、他の構成要素を追加するなどの種々の変形実施が可能である。

【0042】

デコーダー30(スイッチング制御回路)は、入力データDIのデコード処理を行って、制御信号SC1～SCi(iは2以上の整数)を出力する。入力データDIはD/A変換の対象となるデータである。制御信号SC1～SCiは、電圧選択回路40が有するセレクターを構成するトランジスターをオン又はオフにする信号である。SC1～SCiの各制御信号の電圧レベルに応じて、各制御信号に対応するトランジスター(制御信号又はその反転信号がゲートに入力されるトランジスター)がオン又はオフになる。制御信号SC1は、入力データDIの下位ビットに対応し、制御信号SCiは、入力データDIの上位ビットに対応する。デコーダー30が行うデコード処理は公知の処理であるため、詳細な説明は省略する。

【0043】

電圧生成回路32は、複数の電圧V1～Vj(jは2以上の整数)を生成して出力する。例えば電圧生成回路32は、電源間(高電位側電源VDDAと低電位側電源VSSの間)に直列に接続された複数の抵抗を有し、これらの複数の抵抗により電圧分割された電圧を、複数の電圧V1～Vjとして出力する。これらの複数の電圧V1～Vjは電源間(VDDA、VSS間)の電圧を例えば等分割した電圧である。但し、複数の電圧V1～Vjは、液晶パネル等の表示パネルでの画像表示のための階調電圧であってもよい。この場合には、複数の電圧V1～Vjは表示パネルの階調特性に応じた電圧になる。

【0044】

電圧選択回路40は、複数の電圧V1～Vjに基づいて電圧選択を行い、D/A変換電圧VDQを出力する。具体的には電圧選択回路40は、電圧生成回路32からの複数の電圧V1～Vjと、デコーダー30からの制御信号SC1～SCiに基づいて、複数の電圧V1～Vjの中から入力データDIに対応する電圧をD/A変換電圧VDQとして選択して出力する。即ち、入力データDIをD/A変換した電圧を、D/A変換電圧VDQとして出力する。

【0045】

10

20

30

40

50

電圧選択回路 40 は、複数のセレクターブロック B L A、B L B、B L C・・・B L F を含む。セレクターブロックの段数は少なくとも 2 段以上である。B L A・・・B L F の各セレクターブロックは 1 又は複数のセレクターにより構成され、各セレクターは、例えば M O S 型のトランジスターにより構成される。そして前段のセレクターブロックが有するセレクターの出力が後段のセレクターブロックが有するセレクターに入力される。具体的には、1 段目（前段）のブロック B L A が有するセレクターの出力が、2 段目（後段）のセレクターブロック B L B に入力される。2 段目（前段）のセレクターブロック B L B が有するセレクターの出力が、3 段目（後段）のセレクターブロック B L C に入力される。最終段のセレクターブロック B L F は、その前段のセレクターブロックが有するセレクターの出力が入力され、電圧選択を行って D / A 変換電圧 V D Q を出力する。

10

#### 【 0 0 4 6 】

1 段目のセレクターブロック B L A には、電圧生成回路 32 からの複数の電圧 V 1 ~ V j が入力される。そして最終段のセレクターブロック B L F が、D / A 変換電圧 V D Q を出力する。具体的には、電圧選択回路 40 は、セレクターブロック B L A ~ B L F により、いわゆるトーナメント方式で電圧選択を行って、最終的な D / A 変換電圧 V D Q を出力する。トーナメント方式は、セレクターブロックの各セレクターが制御信号に基づき電圧選択を行うことで、セレクターに入力された複数の電圧の中から 1 つの電圧が選択され、これによりセレクターに対応するブロックの電圧が順次に勝ち残りで選択されて行く電圧選択方式である。

#### 【 0 0 4 7 】

20

複数段のセレクターブロック B L A ~ B L F の各々は複数のトランジスター（例えば P 型トランジスター、N 型トランジスター）により構成される。具体的には各セレクターブロック B L A ~ B L F は 1 又は複数のセレクターを有し、当該セレクターが複数のトランジスターにより構成される。

#### 【 0 0 4 8 】

そして本実施形態では、セレクターブロック（少なくとも最終段のセレクターブロック）を構成する複数のトランジスターのうち、電源ノード（V D D A、V S S）から遠い側の第 2 のトランジスターは、電源ノードから近い側の第 1 のトランジスターに比べて、低いしきい値電圧に設定されている。具体的には、セレクターブロック（B L A ~ B L F）を構成する複数のトランジスターのうち、高電位側電源ノード（V D D A）から遠い側の第 2 の P 型トランジスターは、高電位側電源ノードから近い側の第 1 の P 型トランジスターに比べて、低いしきい値電圧に設定されている。また低電位側電源ノード（V S S）から遠い側の第 2 の N 型トランジスターは、低電位側電源ノードから近い側の第 1 の N 型トランジスターのしきい値電圧に比べて、低いしきい値電圧に設定されている。

30

#### 【 0 0 4 9 】

ここで、電源ノードから遠い側のトランジスターとは、電源ノードから近い側のトランジスターに比べて、トランジスターの入力電圧（入力電圧範囲）が、電源電圧から離れた電圧（電源電圧との差が大きい電圧）となるトランジスターである。電源ノードから近い側の第 1 のトランジスターの入力電圧を V I N 1 とし、電源ノードから遠い側の第 2 のトランジスターを入力電圧 V I N 2 とし、電源電圧を V P W R とした場合に、例えば、| V P W R - V I N 2 | > | V P W R - V I N 1 | が成り立つ。

40

#### 【 0 0 5 0 】

具体的には、高電位側電源ノードから近い側の第 1 の P 型トランジスターの入力電圧を V I N P 1 とし、高電位側電源ノードから遠い側の第 2 の P 型トランジスターを入力電圧 V I N P 2 とし、高電位側電源電圧を V D D A とした場合に、例えば V D D A - V I N P 2 > V D D A - V I N P 1 が成り立つ。低電位側電源ノードから近い側の第 1 の N 型トランジスターの入力電圧を V I N N 1 とし、低電位側電源ノードから遠い側の第 2 の N 型トランジスターを入力電圧 V I N N 2 とし、低電位側電源電圧を V S S とした場合に、例えば V I N N 2 - V S S > V I N N 1 - V S S が成り立つ。なお本実施形態では、説明の簡素化のために V D D A、V S S を、適宜、電源を表す記号として用いたり、電源電圧を表

50

す記号として用いたりする。

#### 【0051】

例えば図1のセレクターブロックB L Aは、電圧V1、V2が入力されて、V1、V2のいずれかを出力する第1のセレクターと、電圧V3、V4が入力されて、V3、V4のいずれかを出力する第2のセレクターを含むことができる。この場合に第2のセレクター(V3、V4)を構成するトランジスター(N型)は、第1のセレクター(V1、V2)を構成するトランジスター(N型)に比べて、低電位側の電源VSSのノードから遠い側のトランジスターになる。

#### 【0052】

またセレクターブロックB L Aは、電圧Vj-2、Vj-3が入力されて、Vj-2、Vj-3のいずれかを出力する第3のセレクターと、電圧Vj、Vj-1が入力されて、Vj、Vj-1のいずれかを出力する第4のセレクターを含むことができる。この場合に第3のセレクター(Vj-2、Vj-3)を構成するトランジスター(P型)は、第4のセレクター(Vj、Vj-1)を構成するトランジスター(P型)に比べて、高電位側の電源VDDAのノードから遠い側のトランジスターになる。

#### 【0053】

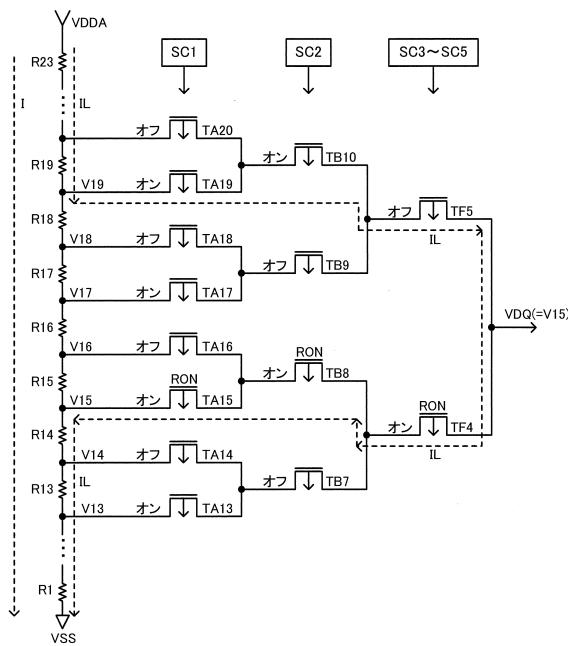

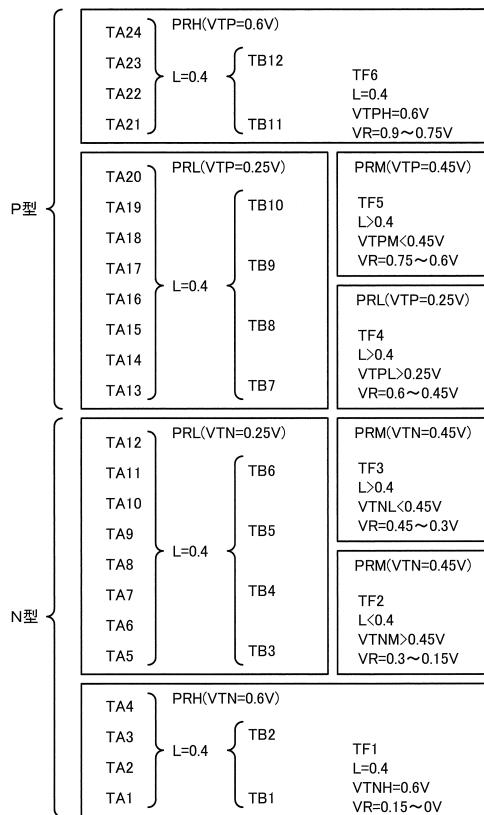

図2に電圧選択回路40、電圧生成回路32の詳細な構成例を示す。なお電圧選択回路40、電圧生成回路32の構成は図2の構成には限定されず、その一部の構成要素を省略したり、他の構成要素を追加するなどの種々の変形実施が可能である。例えば図2では電圧生成回路32が24個の電圧V1～V24を生成し、これらの電圧V1～V24が電圧選択回路40に入力される例を示しているが、生成及び入力される複数の電圧の個数はこれに限定されない。また図2では1段目のセレクターブロックB L Aを構成するセレクターが、2入力/1出力のセレクターである例を示しているが、例えば4入力/1出力のセレクターなどの他の構成のセレクターであってもよい。2段目、最終段のセレクターブロックB L B、B L Fも同様である。また図2ではセレクターブロックの段数が3段である場合を示しているが、セレクターブロックの段数は4段以上であってもよい。また電圧生成回路32は抵抗分割以外の手法により複数の電圧を生成してもよい。

#### 【0054】

図2では電圧生成回路32は、高電位側の電源VDDAのノードと低電位側の電源VSS(GND)のノードとの間に直列に接続された複数の抵抗R1～R23を有する。電圧生成回路32は、これらの抵抗R1～R23による電圧分割により、複数の電圧V1～V24を生成して出力する。

#### 【0055】

電圧選択回路40は、セレクターブロックB L A、B L B、B L Fを含む。B L A、B L B、B L Fは、各々、1段目(初段)、2段目、最終段のセレクターブロックである。

#### 【0056】

1段目のセレクターブロックB L AはセレクターSA1～SA12を含む。SA1～SA12の各セレクターは、2入力/1出力のセレクターであり、2つのトランジスターにより構成される。

#### 【0057】

具体的には、SA1～SA6の各セレクターは、2つのN型トランジスターにより構成される。例えばセレクターSA1はN型のトランジスターTA1、TA2により構成され、セレクターSA2はN型のトランジスターTA3、TA4により構成される。他のセレクターSA3～SA6も同様である。一方、SA7～SA12の各セレクターは、2つのP型のトランジスターにより構成される。例えばセレクターSA7はP型のトランジスターTA13、TA14により構成され、セレクターSA8はP型のトランジスターTA15、TA16により構成される。他のセレクターSA9～SA12も同様である。

#### 【0058】

そして、この1段目のセレクターブロックB L Aには、電圧生成回路32からの複数の電圧V1～V24が入力される。具体的にはセレクターSA1は、電圧V1、V2が入力

10

20

30

40

50

され、V1、V2のいずれかを選択して、後段のセレクターブロックBLL（セレクターSB1）に出力する。セレクターSA2は、電圧V3、V4が入力され、V3、V4のいずれかを選択して、後段のセレクターブロックBLL（セレクターSB2）に出力する。他のセレクターSA3～SA12も同様である。

#### 【0059】

2段目のセレクターブロックBLLはセレクターSB1～SB6を含む。SB1～SB6の各セレクターは、2入力/1出力のセレクターであり、2つのトランジスターにより構成される。具体的には、SB1～SB3の各セレクターは、2つのN型のトランジスターにより構成される。例えばセレクターSB1はN型のトランジスターTB1、TB2により構成される。他のセレクターSB2、SB3も同様である。一方、SB4～SB6の各セレクターは、2つのP型のトランジスターにより構成される。例えばセレクターSB4はP型のトランジスターTB7、TB8により構成される。他のセレクターSB5、SB6も同様である。

10

#### 【0060】

そして、この2段目のセレクターブロックBLLには、1段目（前段）のセレクターブロックBLAにより選択された複数の電圧が入力される。具体的にはセレクターSB1は、前段のセレクターSA1、SA2により選択された2つの電圧が入力され、これらの2つの電圧のいずれかを選択して、後段（最終段）のセレクターブロックBLFのセレクターSFに出力する。セレクターSB2は、前段のセレクターSA3、SA4により選択された2つの電圧が入力され、これらの2つの電圧のいずれかを選択して、後段のセレクターブロックBLFのセレクターSFに出力する。他のセレクターSB3～SB6も同様である。

20

#### 【0061】

最終段のセレクターブロックBLFは、6入力/1出力のセレクターSFにより構成される。このセレクターSFは、N型のトランジスターTF1～TF3と、P型のトランジスターTF4～TF6により構成される。そしてセレクターSFは、前段のセレクターブロックBLLのセレクターSB1～SB6により選択された6つの電圧が入力され、これらの6つの電圧のいずれかを選択して、D/A変換電圧VDQとして出力する。

#### 【0062】

1段目のセレクターブロックBLAを構成するトランジスターTA1～TA24は、図1のデコーダー30からの1ビットの制御信号SC1（スイッチ制御信号）によりオン、オフ制御される。制御信号SC1は入力データの下位の1ビットに対応する信号である。例えば制御信号SC1がLレベル（論理レベル「0」）である場合には、奇数番目のトランジスターTA1、TA3、TA5…TA23がオンになる。一方、制御信号SC1がHレベル（論理レベル「1」）である場合には、偶数番目のトランジスターTA2、TA4、TA6…TA24がオンになる。即ち、奇数番目のトランジスターと偶数番目のトランジスターとは、互いに排他的にオン又はオフになる。この排他的なオン、オフは、制御信号SC1とその反転信号を用いることで実現できる。

30

#### 【0063】

2段目のセレクターブロックBLLを構成するトランジスターTB1～TB12は、デコーダー30からの1ビットの制御信号SC2によりオン、オフ制御される。例えば制御信号SC2がLレベル（「0」）である場合には、奇数番目のトランジスターTB1、TB3…TB11がオンになる。一方、制御信号SC2がHレベル（「1」）である場合には、偶数番目のトランジスターTB2、TB4…TB12がオンになる。即ち、奇数番目のトランジスターと偶数番目のトランジスターとは、互いに排他的にオン又はオフになる。この排的なオン、オフは、制御信号SC2とその反転信号を用いることで実現できる。

40

#### 【0064】

最終段のセレクターブロックBLFを構成するトランジスターTF1～TF6は、デコーダー30からの例え3ビットの制御信号SC3～SC5によりオン、オフ制御される

50

。例えば制御信号 S C 3 ~ S C 5 により、6つのトランジスター T F 1 ~ T F 6 のいずれか1つのトランジスターがオンになり、他のトランジスターはオフになる。これにより6入力 / 1出力のセレクター S F が実現される。

#### 【 0 0 6 5 】

このように本実施形態では、複数段のセレクターブロック B L A、B L B、B L F では、前段のセレクターブロックが有するセレクターの出力が後段のセレクターブロックが有するセレクターに入力される。1段目(前段)のセレクターブロック B L A が有するセレクター S A 1 ~ S A 1 2 の出力が、2段目(後段)のセレクターブロック B L B が有するセレクター S B 1 ~ S B 6 に入力される。2段目(前段)のセレクターブロック B L B が有するセレクター S B 1 ~ S B 6 の出力が、最終段(後段)のセレクターブロック B L F が有するセレクター S F に入力される。そして1段目のセレクターブロック B L A には、複数の電圧 V 1 ~ V 2 4 が入力され、いわゆるトーナメント方式で電圧選択を行うことと、最終段のセレクターブロック B L F から、入力データ D I の D / A 変換電圧 V D Q が出力される。

#### 【 0 0 6 6 】

また複数段のセレクターブロック B L A、B L B、B L F の各々は複数のトランジスターにより構成される。例えばセレクターブロック B L A はトランジスター T A 1 ~ T A 2 4 により構成される。セレクターブロック B L B はトランジスター T B 1 ~ T B 1 2 により構成される。セレクターブロック B L F はトランジスター T F 1 ~ T F 6 により構成される。

10

#### 【 0 0 6 7 】

そして、これらの複数のトランジスターにおいて、電源ノード( V D D A、V S S )から遠い側のトランジスターは、電源ノード( V D D A、V S S )から近い側のトランジスターに比べて、低いしきい値電圧に設定されている。

20

#### 【 0 0 6 8 】

例えば最終段のブロック B L F において、P型のトランジスター T F 5 (第2のトランジスター)は、P型のトランジスター T F 6 (第1のトランジスター)に比べて、高電位側の電源 V D D A のノードから遠い側のトランジスターである。このため、T F 5 のしきい値電圧 V T P M は、T F 6 のしきい値電圧 V T P H よりも低い電圧に設定 ( V T P M < V T P H ) されている。P型のトランジスター T F 4 (第3のトランジスター)は、P型のトランジスター T F 5 (第2のトランジスター)に比べて、V D D A のノードから遠い側のトランジスターである。このため、T F 4 のしきい値電圧 V T P L は、T F 5 のしきい値電圧 V T P M よりも低い電圧に設定 ( V T P L < V T P M ) されている。前段のセレクターブロック B L A、B L B のP型のトランジスター T A 1 3 ~ T A 2 4 、T B 7 ~ T B 1 2 についても同様である。なおP型のトランジスターのしきい値電圧 V T P H 、V T P M 、V T P L はしきい値電圧の絶対値 ( | V T P H | 、| V T P M | 、| V T P L | ) を意味する。

30

#### 【 0 0 6 9 】

また最終段のブロック B L F において、N型のトランジスター T F 2 (第2のトランジスター)は、N型のトランジスター T F 1 (第1のトランジスター)に比べて、低電位側の電源 V S S のノードから遠い側のトランジスターである。このため、T F 2 のしきい値電圧 V T N M は、T F 1 のしきい値電圧 V T N H よりも低い電圧に設定 ( V T N M < V T N H ) されている。N型のトランジスター T F 3 (第3のトランジスター)は、N型のトランジスター T F 2 (第2のトランジスター)に比べて、V S S のノードから遠い側のトランジスターである。このため、T F 3 のしきい値電圧 V T N L は、T F 2 のしきい値電圧 V T N M よりも低い電圧に設定 ( V T N L < V T N M ) されている。前段のセレクターブロック B L A、B L B のN型のトランジスター T A 1 ~ T A 1 2 、T B 1 ~ T B 6 についても同様である。

40

#### 【 0 0 7 0 】

ここで、電源ノード( V D D A、V S S )に近い側の第1のトランジスター ( T F 1 、

50

TF6等)は、しきい値電圧のティピカル値が第1のしきい値電圧(例えば0.6V)である第1の種類(後述するPRH)のトランジスターである。電源ノードから遠い側の第2のトランジスター(TF2、TF5等)は、しきい値電圧のティピカル値が第1のしきい値電圧よりも低い第2のしきい値電圧(例えば0.45V)である第2の種類(後述するPRM)のトランジスターである。電源ノードから更に遠い側の第3のトランジスター(TF3、TF4等)は、しきい値電圧のティピカル値が第2のしきい値電圧よりも低い第3のしきい値電圧(例えば0.25V)である第3の種類(後述するPRL)のトランジスターである。

#### 【0071】

しきい値電圧のティピカル値は、例えば製造プロセス条件がティピカル条件(プロセスばらつきが無い場合の条件)であり、温度が基準温度(例えば25)である場合のしきい値電圧である。第1、第2、第3の種類のトランジスターは、例えば製造プロセスが異なるトランジスターである。第1の種類のトランジスター(TF1、TF6等)は、例えば高耐圧用(ハイボルテージ)の製造プロセスにより形成されるトランジスターである。第3の種類のトランジスター(TF3、TF4等)は、例えば低耐圧用(ローボルテージ)の製造プロセスにより形成されるトランジスターである。第2の種類のトランジスター(TF2、TF5等)は、例えば高耐圧用と低耐圧用の中耐圧用の製造プロセスにより形成されるトランジスターである。

#### 【0072】

例えば第1、第2の種類である第1、第2のトランジスターでは、トランジスターの製造プロセスパラメーターが異なることで、異なるしきい値電圧に設定されている。第3の種類である第3のトランジスターも、トランジスターの製造プロセスパラメーターが異なることで、第1、第2のトランジスターとは異なるしきい値電圧に設定されている。ここで、製造プロセスパラメーターは、トランジスターのチャネル領域等における不純物濃度やゲート酸化膜の厚さなどのパラメータである。例えば不純物濃度を高くしたり、低くすることで、トランジスターのしきい値電圧を設定する。或いは、ゲート酸化膜を薄くしたり、厚くすることで、トランジスターのしきい値電圧を設定する。或いは、製造プロセスパラメーターは、トランジスターの異極ゲートについてのパラメータであってもよい。即ち、トランジスターのゲート(ポリシリコン)について異種のゲート(例えばイオン注入される不純物の濃度や種類が異なるゲート)を用いることで、トランジスターのしきい値電圧を設定する。このようにトランジスターのしきい値電圧を設定する製造プロセスパラメーターとしては種々のパラメータを想定できる。

#### 【0073】

また本実施形態では、このようなトランジスターの種類(製造プロセス等)のみならず、トランジスターのゲート長L(チャネル長)の設定により、トランジスターのしきい値電圧を互いに異ならせている。具体的には、後述するようにトランジスターの短チャネル効果や、逆短チャネル効果を有効活用して、トランジスターのしきい値電圧を設定する。

#### 【0074】

例えば図2では、第1のトランジスター(TF1、TF6等)と、第2のトランジスター(TF2、TF5等)とは、ゲート長(チャネル長)が異なっている。また第3のトランジスター(TF3、TF4等)も、他のトランジスターとゲート長を異ならせてよい。即ち、第1、第2、第3のトランジスターのうちの少なくとも1つのトランジスターは、第1、第2、第3のトランジスターのうちの他のトランジスターとは、ゲート長が異なっている。

#### 【0075】

例えばトランジスターTF1、TF6(第1のトランジスター)のゲート長は $L = L_T$ に設定されている。ここで、 $L_T$ は、第1の種類のトランジスター(PRH)において標準的なゲート長(ティピカルのゲート長)であり、例えば $L_T = 0.4 \mu m$ である。

#### 【0076】

一方、トランジスターTF2、TF5(第2のトランジスター)のゲート長は $L = L_1$

10

20

30

40

50

、L<sub>4</sub>に設定されており、L<sub>1</sub>、L<sub>4</sub>は標準的なゲート長LTとは異なっている。例えばL<sub>1</sub>、L<sub>4</sub>をLTよりも長くしたり、短くする。なおL<sub>1</sub>又はL<sub>4</sub>を、LTと同じ長さに設定してもよい。またL<sub>1</sub>とL<sub>4</sub>は、異なる長さでもよいし、同じ長さでもよい。

#### 【0077】

またトランジスターTF3、TF4（第3のトランジスター）のゲート長はL=L<sub>2</sub>、L<sub>3</sub>に設定されており、L<sub>2</sub>、L<sub>3</sub>は標準的なゲート長LTとは異なっている。例えばL<sub>2</sub>、L<sub>3</sub>をLTよりも長くしたり、短くする。なおL<sub>2</sub>又はL<sub>3</sub>を、LTと同じ長さに設定してもよい。またL<sub>2</sub>とL<sub>3</sub>は、異なる長さでもよいし、同じ長さでもよい。またL<sub>2</sub>、L<sub>3</sub>と、前述のL<sub>1</sub>、L<sub>4</sub>は、異なる長さでもよいし、同じ長さでもよい。

#### 【0078】

また、最終段のセレクターブロックBLFを構成する少なくとも1つのトランジスターのゲート長は、最終段のセレクターブロックBLFを構成する他のトランジスターのゲート長よりも長くなっている。また最終段のセレクターブロックBLFを構成する少なくとも1つのトランジスターのゲート長は、1段目のセレクターブロックBLAを構成するトランジスターのゲート長よりも長くなっている。

#### 【0079】

例えばセレクターブロックBLFを構成するP型のトランジスターTF4又はTF5のゲート長L<sub>3</sub>、L<sub>4</sub>は、BLFを構成する他のP型のトランジスターTF6のゲート長LTよりも長くなっている。或いはトランジスターTF4又はTF5のゲート長L<sub>3</sub>、L<sub>4</sub>は、1段目のセレクターブロックBLAを構成するP型のトランジスターTA13～TA24のゲート長LTよりも例えれば長くなっている。

#### 【0080】

またセレクターブロックBLFを構成するN型のトランジスターTF3等のゲート長L<sub>2</sub>は、BLFを構成する他のN型のトランジスターTF1のゲート長LTよりも長くなっている。或いはトランジスターTF3等のゲート長L<sub>2</sub>は、1段目のセレクターブロックBLAを構成するN型のトランジスターTA1～TA12のゲート長LTよりも例えれば長くなっている。

#### 【0081】

このようにトランジスターの種類のみならず、ゲート長も用いて、トランジスターのしきい値電圧を設定すれば、より細かなしきい値電圧の調整が可能になる。これにより、電源電圧が低い場合等においても、例えばトランジスターのオン条件、オフ条件を満たすしきい値電圧の設定が容易になる。またトランジスターのオフリーケ電流（オフ時のリーケ電流）に起因するD/A変換器の非直線性誤差（DNL等）を抑制するしきい値電圧の設定も可能になる。

#### 【0082】

なお図2に示すように本実施形態では、最終段のセレクターブロックBLFのセレクタ-SFは、前段のセレクターブロックBLBから例えれば6個（広義にはI個。I=3）の電圧が入力され、1個のD/A変換電圧VDQを出力するセレクターになっている。即ち最終段のセレクターブロックBLFでは、例えれば1つのセレクタ-SFを用いて、例えれば6個の電圧（広義には3個以上の複数の電圧）から、電圧選択を行って、D/A変換電圧VDQを出力する。後述するように最終段のセレクターブロックBLFのトランジスターTF1～TF6では、その入力電圧が所与の電圧範囲で変化する。このため、トランジスターのオン条件及びオフ条件等を満たすしきい値電圧の設定が難しいという課題がある。この点、図2では、セレクターブロックBLFのセレクタ-SFは、2入力/1出力のセレクターではなく、6入力/1出力のセレクターになっている。従って、2入力/1出力のセレクターである場合に比べて、セレクタ-SFを構成するトランジスターTF1～TF6の入力電圧範囲（電圧変化範囲）を狭くできる。この結果、トランジスターのオン条件、オフ条件等を満たすしきい値電圧の設定を容易化できるという利点がある。

#### 【0083】

2. しきい値電圧設定手法

10

20

30

40

50

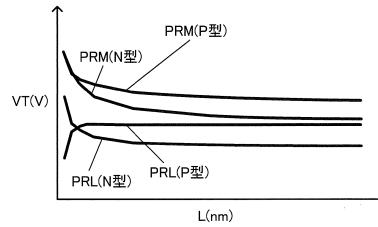

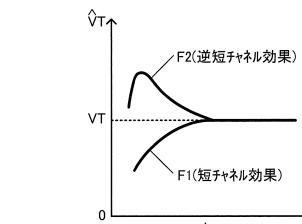

次に本実施形態のしきい値電圧設定手法について詳細に説明する。図3AはP型トランジスターTPのオン条件、オフ条件の説明図である。図3Aに示すようにP型トランジスターTPをオンさせる場合には、そのゲートに例えば $V_{SS} = 0\text{ V}$ が入力される。P型トランジスターTPがオンするためには、そのゲート・ソース間電圧（絶対値）をしきい値電圧（絶対値）よりも大きくする必要があり、下式(1)に示すオン条件が成立する必要がある。

#### 【0084】

$$V_{IN} > V_{TP} + V_{BS} + V_{PR} + V_{TS} \quad (1)$$

ここで $V_{IN}$ は、P型トランジスターTPの入力電圧（ソース・ドレインの入力電圧）である。 $V_{TP}$ はP型トランジスターTPの基本的なしきい値電圧であり、 $V_{BS}$ は基板バイアス効果によるしきい値電圧の増加分である。即ち、P型トランジスターTPでは、基板電圧が例えばVDDAの電圧となっており、入力電圧 $V_{IN}$ とは異なっているため、しきい値電圧 $V_{TP}$ が基板バイアス効果により電圧 $V_{BS}$ だけ増加する。また $V_{PR}$ はプロセスばらつきに起因するしきい値電圧の変動分（プラス方向への変動分）である。 $V_{TS}$ は温度変動に起因するしきい値電圧の変動分（プラス方向への変動分）である。即ち、半導体の製造プロセスにはばらつきあるため、このばらつきに起因して、しきい値電圧が高くなる場合がある。また温度変動があった場合にも、しきい値電圧が変動して、高くなる場合がある。従って、P型トランジスターTPがオンするためには、入力電圧 $V_{IN}$ が $V_{TP} + V_{BS} + V_{PR} + V_{TS}$ よりも高い電圧である必要がある。なお $V_{TP}$ はしきい値電圧の絶対値( $|V_{TP}|$ )を意味する。

10

20

#### 【0085】

またP型トランジスターTPが適正にオフするためには、下式(2)に示すオフ条件が成立する必要がある。

#### 【0086】

$$V_{TP} - V_{PR} - V_{TS} > 0 \quad (2)$$

ここで、 $V_{PR}$ はプロセスばらつきに起因するしきい値電圧の変動分（マイナス方向への変動分）である。 $V_{TS}$ は温度変動に起因するしきい値電圧の変動分（マイナス方向への変動分）である。即ち、半導体の製造プロセスにはばらつきあるため、このばらつきに起因して、しきい値電圧が低くなる場合がある。また温度変動があった場合にも、しきい値電圧が変動して、低くなる場合がある。これらのプロセスばらつきや温度変動に起因してしきい値電圧が変動した場合にも、P型トランジスターTPを適正にオフするためには、上式(2)のオフ条件が成立する必要がある。

30

#### 【0087】

図3BはN型トランジスターTNのオン条件、オフ条件の説明図である。図3Bに示すようにN型トランジスターTNをオンさせる場合には、そのゲートに例えばVDDAの電圧（例えば $0.9\text{ V}$ ）が入力される。N型トランジスターTNがオンするためには、そのゲート・ソース間電圧( $V_{DDA} - V_{IN}$ )をしきい値電圧よりも大きくする必要があり、下式(3)に示すオン条件が成立する必要がある。

#### 【0088】

$$V_{DDA} - V_{IN} > V_{TN} + V_{BS} + V_{PR} + V_{TS} \quad (3)$$

40

ここで、 $V_{TN}$ はN型トランジスターTNの基本的なしきい値電圧であり、 $V_{BS}$ は基板バイアス効果によるしきい値電圧の増加分である。 $V_{PR}$ 、 $V_{TS}$ は、上述と同様に、プロセスばらつき、温度変動に起因するしきい値電圧の変動分（プラス方向への変動分）である。

#### 【0089】

またN型トランジスターTNが適正にオフするためには、下式(4)に示すオフ条件が成立する必要がある。

#### 【0090】

$$V_{TN} - V_{PR} - V_{TS} > 0 \quad (4)$$

$V_{PR}$ 、 $V_{TS}$ は、上述と同様に、プロセスばらつき、温度変動に起因するしきい値電

50

圧の変動分（マイナス方向への変動分）である。

**【0091】**

さて、電源VDDAの電圧が、トランジスターのしきい値電圧に対して十分に高い場合には、図1、図2に示すような構成のD/A変換器において、上式(1)～(4)のようなオン条件、オフ条件を考慮する必要はほとんどない。

**【0092】**

しかしながら、電源VDDAの電圧が低くなり、トランジスターのしきい値電圧に近くなると、上式(1)～(4)のようなオン条件、オフ条件を考慮しないと、図1、図2のような構成のD/A変換器の適正な動作を実現できないことが判明した。

**【0093】**

例えば本実施形態では、後述するように、トランジスターの仕事関数差を利用した電源回路により、電源VDDAを生成している。このため、VDDAの電圧が例えば0.9Vというように非常に低い電圧になる。そしてVDDA = 0.9Vというように低い電圧になると、例えば図2に示すように電源間に多数のトランジスターが配列された電圧選択回路40において、適正な電圧選択を行うことが難しくなる。即ち、電源VDDAの電圧が低くなると、電圧選択回路40を構成するトランジスターのオン条件、オフ条件を満たすことが難しくなり、トーナメント方式による適正な電圧選択を行ってD/A変換電圧VDQを出力することが困難になる。

**【0094】**

例えば図4Aには、図2の最終段のP型のトランジスターTF4～TF6の入力電圧範囲VR（入力電圧VINの電圧範囲）が示されている。例えばVDDA = 0.9Vとした場合に、最終段のP型のトランジスターTF6の入力電圧範囲はVR = 0.9～0.75Vになる。即ち、トランジスターTF6には、電圧生成回路32により生成された電圧V24、V23、V22、V21のいずれかの電圧が、入力電圧VINとして入力される。従って、トランジスターTF6の入力電圧範囲は、電圧V24～V21に対応するVR = 0.9～0.75Vの範囲になる。

**【0095】**

また、P型のトランジスターTF5には、電圧生成回路32により生成された電圧V20、V19、V18、V17のいずれかの電圧が、入力電圧VINとして入力される。従って、トランジスターTF6の入力電圧範囲は、電圧V20～V17に対応するVR = 0.75～0.6Vの範囲になる。同様に、P型のトランジスターTF4の入力電圧範囲はVR = 0.6～0.45Vになる。

**【0096】**

図4Bには、図2のN型のトランジスターTF1～TF3の入力電圧範囲VRが示されている。例えばN型のトランジスターTF3には、電圧V12、V11、V10、V9のいずれかの電圧が、入力電圧VINとして入力される。従って、トランジスターTF3の入力電圧範囲は、電圧V12～V9に対応するVR = 0.45～0.3Vの範囲になる。同様に、N型のトランジスターTF2、TF1の入力電圧範囲は、各々、VR = 0.3～0.15V、VR = 0.15～0Vになる。

**【0097】**

そして図4Aにおいて、P型のトランジスターTF6の入力電圧範囲はVR = 0.9～0.75Vであり、この入力電圧範囲での入力電圧VINの最小電圧VINminは0.75Vである。そして図3Aに示すように、P型のトランジスターTF6のオン条件は、 $VIN > VTP + VBS + VPR + VTS$ である。従って、 $VIN_{min} = 0.75V$ である場合に、 $VIN - (VTP + VBS + VPR + VTS)$ で表されるマージンが最も小さくなり、トランジスターTF6のオン条件が最も厳しくなる。同様に、トランジスターTF5、TF4では、各々、 $VIN_{min} = 0.6V$ 、 $0.45V$ である場合に、オン条件が最も厳しくなる。

**【0098】**

また図4Bにおいて、N型のトランジスターTF3の入力電圧範囲はVR = 0.45～

10

20

30

40

50

0.3Vであり、この入力電圧範囲でのVDDA-VINの最小電圧(VDDA-VIN)<sub>min</sub>は0.45Vである。即ち、VDDA=0.9Vであるため、VIN=0.45Vである場合に、VDDA-VINは最小電圧(VDDA-VIN)<sub>min</sub>=0.9V-0.45V=0.45Vになる。そして図3Bに示すように、N型のトランジスターTF3のオン条件は、VDDA-VIN>VTN+VBS+VPR+VTSである。従って、(VDD-VIN)<sub>min</sub>=0.45Vである場合に、(VDDA-VIN)-(VTN+VBS+VPR+VTS)で表されるマージンが最も小さくなり、トランジスターTF3のオン条件が最も厳しくなる。同様に、トランジスターTF2、TF1では、各々、(VDD-VIN)<sub>min</sub>=0.6V、0.75Vである場合に、オン条件が最も厳しくなる。

10

#### 【0099】

このように図4AのP型のトランジスターTF6、TF5、TF4では、オン条件が最も厳しくなるVIN<sub>min</sub>=0.75V、0.6V、0.45Vの場合に、VIN>VTP+VBS+VPR+VTSのオン条件が満たされるように、しきい値電圧VTPを設定する必要がある。従って、トランジスターTF6、TF5、TF4のしきい値電圧VTPは、各々、少なくとも0.75V、0.6V、0.45Vよりも低い電圧に設定する必要がある。

#### 【0100】

また図4BのN型のトランジスターTF3、TF2、TF1では、オン条件が最も厳しくなる(VDDA-VIN)<sub>min</sub>=0.45V、0.6V、0.75Vの場合に、VDDA-VIN>VTN+VBS+VPR+VTSのオン条件が満たされるように、しきい値電圧VTNを設定する必要がある。従って、トランジスターTF3、TF2、TF1のしきい値電圧VTNは、各々、少なくとも0.45V、0.6V、0.75Vよりも低い電圧に設定する必要がある。

20

#### 【0101】

そして図4Aに示すように、例えば種類PRH、PRM、PRLのP型のトランジスターでは、しきい値電圧のティピカル値は、各々、0.6V、0.45V、0.25Vになっている。また図4Bに示すように、種類PRL、PRM、PRHのN型のトランジスターでは、しきい値電圧のティピカル値は、各々、0.25V、0.45V、0.6Vになっている。即ち、しきい値電圧(絶対値)は、種類PRHが最も高く、種類PRLが最も低い。

30

#### 【0102】

そこで、トランジスターの種類の設定により、しきい値電圧を設定する手法を採用する場合には、例えばTF6については種類PRHのトランジスターを用い、TF5については種類PRMのトランジスターを用い、TF4については種類PRLのトランジスターを用いることが望ましい。また、TF3については種類PRLのトランジスターを用い、TF2については種類PRMのトランジスターを用い、TF1については種類PRHのトランジスターを用いることが望ましい。こうすることで、少なくともトランジスターのオン条件については満たすことが可能になる。

#### 【0103】

40

一方、しきい値電圧VTP、VTNが低くなりすぎると、今度は図3A、図3Bのオフ条件が満たされなくなるという問題が生じる。即ち、しきい値電圧VTP、VTNが低くなりすぎると、VTP-VPR-VTS>0、VTN-VPR-VTS>0のオフ条件が成立しなくなるおそれがある。更に、トランジスターのオフリーケ電流に起因するD/A変換器の非直線性誤差(DNL)が許容値を超えてしまうという問題も考慮する必要がある。このため、例えばトランジスターTF6、TF5、TF4のしきい値電圧VTPは、各々、0.75V、0.6V、0.45Vよりも低く、且つ、これらの電圧に近い電圧にすることが望ましい。またトランジスターTF3、TF2、TF1のしきい値電圧VTNは、各々、0.45V、0.6V、0.75Vよりも低く、且つ、これらの電圧に近い電圧にすることが望ましい。

50

**【0104】**

図5は、トランジスターのオフリーク電流に起因する問題について説明する図である。1段目のトランジスターTA13～TA20は、制御信号SC1により排他的にオン又はオフになる。例えば図5では、奇数番目のトランジスターTA13、TA15…TA19がオンになっており、偶数番目のトランジスターTA14、TA16…TA20がオフになっている。また2段目のトランジスターTB7～TB10は、制御信号SC2により排他の的にオン又はオフになる。例えば図5では、奇数番目のトランジスターTB7、TB9がオフになっており、偶数番目のトランジスターTB8、TB10がオンになっている。そして最終段のトランジスターTF4、TF5では、TF4がオンになっており、TF5がオフになっている。これにより図5では、電圧V15が選択されて、D/A変換電圧VDQ = V15が出力されている。10

**【0105】**

この場合に、例えばオフになっているトランジスターTF5においても、オフリーク電流ILが流れる。このオフリーク電流ILは、電源VDDAから抵抗R23～R19及びオン状態のトランジスターTA19、TB10を介して、オフ状態のトランジスターTF5を流れ、オン状態のトランジスターTF4に流れ込む。そして、このオフリーク電流ILは、オン状態のトランジスターTB8、TA15を介して、電圧V15のノードに流れ込み、抵抗R14～R1を介して電源VSS側に流れる。

**【0106】**

このようなオフリーク電流ILが流れると、オン状態のトランジスターTF4、TB8、TA15のオン抵抗RONと、オフリーク電流との積に対応する電圧の分だけ、D/A変換電圧VDQが、電圧V15からずれてしまう。また、直列接続された抵抗R1～R23には、本来は、VDDA - VSSの電圧をR1～R23の総抵抗値で除算したものに相当する電流Iが流れると前提となっているが、オフリーク電流ILが流れると、この前提が崩れる。即ち電圧生成回路32では、電源VDDAからVSSに電流Iが流れることで、VDDA - VSSの電圧を等分割した電圧V1～V24が生成される前提となっている。しかしながら、オフリーク電流ILが存在すると、例えば抵抗R23～R19やR14～R1に流れる電流がI + ILになってしまなどの事態が発生し、上記前提が崩れ、D/A変換電圧VDQが電圧V15からずれた電圧になってしまう。そして、D/A変換電圧VDQが本来の電圧からずれた電圧になり、D/A変換器の非直線性誤差(DNL)が許容値(例えば1 LSBの電圧)を越えてしまうと、適正なD/A変換を実現できなくなってしまう。2030

**【0107】**

トランジスターのオン条件、オフ条件を満たしながら、図5のようなオフリーク電流の問題を回避するためには、図4A、図4Bで説明したトランジスターの種類の設定によるしきい値電圧の設定手法だけでは、不十分な場合がある。

**【0108】**

例えば図5において、オフリーク電流ILの電流値を小さくするためには、オフ状態のトランジスターTF5のしきい値電圧を高くする必要がある。トランジスターTF5のしきい値電圧を高くすることで、オフリーク電流ILが減り、オフリーク電流ILに起因する非直線性誤差を低減することが可能になる。40

**【0109】**

しかしながら、例えばオン状態のトランジスターTF4についても、しきい値電圧を高くしてしまうと、今度はオン抵抗RONが増加し、オン抵抗RONに起因する雑音が増加してしまう。このように雑音が増加すると、例えば後述する発振器用の回路装置にD/A変換器を用いた場合に、発振周波数の位相雑音が増加する問題が生じる。

**【0110】**

このようなトランジスターのオン条件、オフ条件、オフリーク電流に起因する性能低下(非直線性誤差の増加)の回避条件などの種々の条件を満たすためには、しきい値電圧の微調整が必要である。50

**【0111】**

ところが、図4A、図4Bに示すようなトランジスターの種類の設定によるしきい値電圧の設定手法では、しきい値電圧の粗調整は可能であるが、微調整は難しい。例えばトランジスターの種類（製造プロセス）を増やして、しきい値電圧の微調整を実現する手法も考えられるが、この手法では、製造プロセスの種類の増加によるコストの増加や、手間・作業の増加・複雑化などの問題を招く。

**【0112】**

そこで本実施形態では、図4A、図4Bに示すようなトランジスターの種類の設定によるしきい値電圧の設定に加えて、トランジスターのゲート長（チャネル長）の調整によるしきい値電圧の設定を行う。例えばトランジスターの種類の設定により、しきい値電圧の粗調整を行い、トランジスターのゲート長の調整により、しきい値電圧の微調整を実現する。こうすることで、トランジスターのオン条件、オフ条件、オフリーク電流に起因する性能低下の回避条件などを満たすことが可能なしきい値電圧の設定手法を実現できる。10

**【0113】**

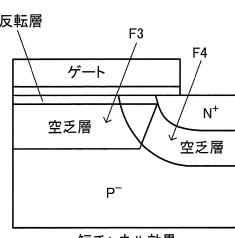

例えば図6Aは、種類P R M、P R LのP型、N型トランジスターにおけるゲート長Lとしきい値電圧V Tの関係の例を示す図である。例えば種類P R L（低耐圧）のP型トランジスターでは、図6BのF 1に示す短チャネル効果により、チャネル値Lが長くなった場合に、しきい値電圧V Tが増加する傾向にある。一方、種類P R M（中耐圧）のP型トランジスター、N型トランジスター、及び種類P R L（低耐圧）のN型トランジスターでは、図6BのF 2に示す逆短チャネル効果により、ゲート長が長くなった場合に（長チャネル領域において）、しきい値電圧V Tが減少する傾向にある。20

**【0114】**

例えば図6CのF 3、F 4は、短チャネル効果の場合の空乏層の様子を模式的に示す図である。F 3はゲートによる空乏層であり、F 4はソース・ドレイン（N型不純物領域）による空乏層である。短チャネル効果によるしきい値電圧の低下は、F 3、F 4の空乏層の影響により生じる。即ち空乏層中のアクセプターイオンが表面ポテンシャル（反転層）を低下させることで、しきい値電圧が低下してしまう。例えば図6Cではソース・ドレンによる空乏層がチャネル側に伸びることで、この部分でのアクセプターイオンが表面ポテンシャルを低下させ、しきい値電圧を低下させる。一方、図6DのF 5、F 6は、逆短チャネル効果の場合の空乏層の様子を模式的に示す図である。F 5はゲートによる空乏層であり、F 6はソース・ドレンによる空乏層である。図6DのF 6では、ソース・ドレンによる空乏層の形状が図6CのF 4とは異なっており、例えば空乏層中のアクセプターイオンの影響が少なくなる。30

**【0115】**

本実施形態では、これらの短チャネル効果、逆短チャネル効果を逆手にとって利用し、ゲート長Lによるしきい値電圧の微調整を実現する。例えば種類P R LのP型トランジスターでは、ゲート長Lを長くすることで、短チャネル効果により、しきい値電圧をそのティピカル値から増加させることができる。一方、種類P R MのP型トランジスター、N型トランジスター、及び種類P R LのN型トランジスターでは、ゲート長Lを長くすることで、逆短チャネル効果により、しきい値電圧をそのティピカル値から減少させることができる。これにより、トランジスターのオン条件、オフ条件、オフリーク電流に起因する性能低下の回避条件などを満たすためのしきい値電圧の微調整が可能になる。40

**【0116】**

なお、本実施形態では基板バイアス効果を利用して、トランジスターのしきい値電圧を設定してもよい。例えば最終段のセレクターブロックB L Fを構成する少なくとも1つのトランジスター（T F 1～T F 6）を、基板電圧が制御されるトランジスターにすることで、これらのトランジスターのしきい値電圧の微調整を実現する。

**【0117】**

例えば図7Aでは、基板電圧制御回路4 2がD / A変換器（回路装置）に設けられ、この基板電圧制御回路4 2が、P型トランジスターT F Pの基板電圧として電圧V B Pを供50

給する。またN型トランジスターTFNの基板電圧として電圧VBNを供給する。P型トランジスターTFPは、図2の最終段のセレクターブロックBLFを構成するP型のトランジスターTF4～TF6の少なくとも1つである。N型トランジスターTFNは、最終段のセレクターブロックBLFを構成するN型のトランジスターTF1～TF3の少なくとも1つである。即ち、P型トランジスターTFPの基板電圧としては、通常は高電位側の電源VDDAの電圧(例えば0.9V)が供給されるが、基板電圧制御回路42は、この電圧とは異なる電圧VBPを供給する。またN型トランジスターTFNの基板電圧としては、通常は低電位側の電源VSSの電圧(例えば0V)が供給されるが、基板電圧制御回路42は、この電圧とは異なる電圧VBNを供給する。

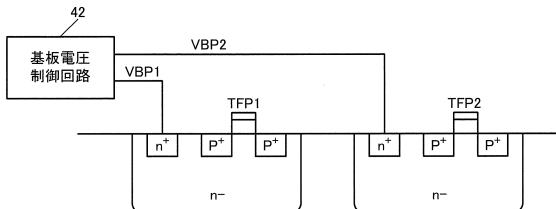

## 【0118】

10

例えは図7Bでは、P型トランジスターTFPとしてP型トランジスターTFP1、TFP2が設けられている。これらのP型トランジスターTFP1、TFP2は、互いに電気的に分離されたN型ウェルに形成されている。そして基板電圧制御回路42は、P型トランジスターTFP1のN型ウェルの電位を設定する基板電圧として、電圧VBP1を供給する。またP型トランジスターTFP2のN型ウェルの電位を設定する基板電圧として、電圧VBP2を供給する。こうすることで、P型トランジスターTFP1とTFP2のしきい値電圧を異なる電圧に設定できる。

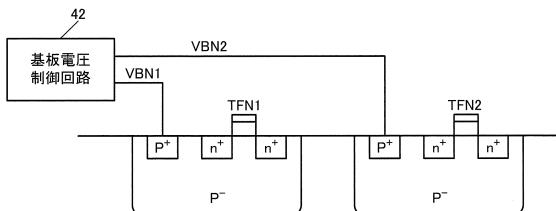

## 【0119】

また図7Cでは、N型トランジスターTFNとしてN型トランジスターTFN1、TFN2が設けられている。これらのN型トランジスターTFN1、TFN2は、互いに電気的に分離されたP型ウェルに形成されている。そして基板電圧制御回路42は、N型トランジスターTFN1のP型ウェルの電位を設定する基板電圧として、電圧VBN1を供給する。またN型トランジスターTFN2のP型ウェルの電位を設定する基板電圧として、電圧VBN2を供給する。こうすることで、N型トランジスターTFN1とTFN2のしきい値電圧を異なる電圧に設定できる。

20

## 【0120】

以上のように例えは最終段のセクレターを構成するトランジスター(TF1～TF6)の基板電圧を制御することで、これらのトランジスターのしきい値電圧を設定できる。これにより、トランジスターのオン条件、オフ条件、オフリーグ電流に起因する性能低下の回避条件などを満たすためのしきい値電圧の微調整が可能になる。

30

## 【0121】

但し、基板電圧を制御する手法では、図7B、図7Cに示すように、電気的に分離されたウェル(P型、N型)を形成する必要があるため、回路のレイアウト面積が増加してしまう。これに対してゲート長Lを設定する手法では、例えはゲート長を長くしても、回路のレイアウト面積は殆ど増加しない。従って、この点においてはゲート長Lを設定する手法の方が有利である。

## 【0122】

## 3. しきい値電圧の設定の具体例

図8にしきい値電圧の設定の具体例を示す。図8では、P型のトランジスターTA21～TA24、TB11、TB12、TF6として、種類PRH(高耐圧)のP型のトランジスターを用いている。これらのトランジスターのゲート長は $L = 0.4 \mu m$ に設定されている。この種類PRHのP型のトランジスターは、しきい値電圧のティピカル値が0.6Vになっている。例えは図4Aで説明したように最終段のトランジスターTF6の入力電圧範囲は0.9～0.75Vであり、 $V_{INmin} = 0.75V$ である。従って、トランジスターTF6のしきい値電圧VTPHが、種類PRHのしきい値電圧のティピカル値である0.6Vに設定されていても、トランジスターのオン条件、オフ条件等を満たすことができる。

40

## 【0123】

また図8では、P型のトランジスターTA13～TA20、TB7～TB10として、種類PRL(低耐圧)のトランジスターを用いている。これらのトランジスターのゲート

50

長は  $L = 0.4 \mu m$  に設定されている。この種類 P R L のトランジスターは、しきい値電圧のティピカル値が  $0.25 V$  になっている。

#### 【0124】

このように本実施形態では、電源 V D D A のノードから遠い側のトランジスター T A 1 3 ~ T A 2 0 、 T B 7 ~ T B 1 0 として、しきい値電圧が低い種類 P R L のトランジスターを用いている。これにより、これらのトランジスター T A 1 3 ~ T A 2 0 、 T B 7 ~ T B 1 0 のしきい値電圧を、電源 V D D A のノードから近い側のトランジスター T A 2 1 ~ T A 2 4 、 T B 1 1 、 T B 1 2 に比べて、低い電圧に設定できるようになる。

#### 【0125】

また図 8 では、N 型のトランジスター T A 1 ~ T A 4 、 T B 1 、 T B 2 、 T F 1 として 10 、種類 P R H (高耐圧) の N 型のトランジスターを用いている。これらのトランジスターのゲート長は  $L = 0.4 \mu m$  に設定されている。この種類 P R H の N 型トランジスターは、しきい値電圧のティピカル値が  $0.6 V$  になっている。例えば図 4 B で説明したように最終段のトランジスター T F 1 の入力電圧範囲は  $0.15 ~ 0 V$  であり、( V D D A - V I N ) min =  $0.75 V$  である。従って、トランジスター T F 1 のしきい値電圧 V TN H が、種類 P R H のしきい値電圧のティピカル値である  $0.6 V$  に設定されていても、トランジスターのオン条件、オフ条件等を満たすことができる。

#### 【0126】

また図 8 では、N 型のトランジスター T A 5 ~ T A 1 2 、 T B 3 ~ T B 6 として、種類 P R L (低耐圧) の N 型のトランジスターを用いている。これらのトランジスターのゲート長は  $L = 0.4 \mu m$  に設定されている。この種類 P R L の N 型のトランジスターは、しきい値電圧のティピカル値が  $0.25 V$  になっている。

#### 【0127】

このように本実施形態では、電源 V S S のノードから遠い側のトランジスター T A 5 ~ T A 1 2 、 T B 3 ~ T B 6 として、しきい値電圧が低い種類 P R L のトランジスターを用いている。これにより、これらのトランジスター T A 5 ~ T A 1 2 、 T B 3 ~ T B 6 のしきい値電圧を、電源 V S S のノードから近い側のトランジスター T A 1 ~ T A 4 、 T B 1 、 T B 2 に比べて、低い電圧に設定できるようになる。

#### 【0128】

また図 8 では、最終段の P 型のトランジスター T F 5 として、しきい値電圧のティピカル値が  $0.45 V$  である種類 P R M (中耐圧) のトランジスターを用いている。そして、このトランジスター T F 5 のゲート長 L は、標準のゲート長である  $0.4 \mu m$  よりも長くなっている。図 6 A に示すように、種類 P R M の P 型トランジスターは、逆短チャネル効果により、ゲート長を長くすることで、しきい値電圧が低くなる。これをを利用してトランジスター T F 5 のしきい値電圧を V TPM <  $0.45 V$  に設定する。例えばゲート長 L を  $2 \mu m$  以上に設定することで、しきい値電圧 V TPM をティピカル値である  $0.45 V$  から例えれば  $0.05 ~ 0.1 V$  程度、低い電圧にする。図 4 A で説明したようにトランジスター T F 5 の入力電圧範囲は  $0.75 ~ 0.6 V$  であり、V IN min =  $0.6 V$  である。従って、トランジスター T F 5 のしきい値電圧を V TPM <  $0.45 V$  に設定することで、トランジスターのオン条件、オフ条件、オフリーク電流に起因する性能低下の回避条件などを満たすことが可能になる。例えば、オン条件である V IN min =  $0.6 V$  > V TPM + V BS + V PR + V TS を満たすことができる。またオフ条件である V TPM - V PR - V TS > 0 も満たすことができる。またゲート長 L を長くすることによるしきい値電圧の微調整により、オフリーク電流に起因する性能低下の回避条件等も満たすことができる。

#### 【0129】

また図 8 では、最終段の P 型のトランジスター T F 4 として、しきい値電圧のティピカル値が  $0.25 V$  である種類 P R L (低耐圧) のトランジスターを用いている。そして、このトランジスター T F 4 のゲート長 L は、標準のゲート長である  $0.4 \mu m$  よりも長くなっている。図 6 A に示すように、種類 P R L の P 型のトランジスターは、短チャネル効

10

20

30

40

50

果により、ゲート長を長くすることで、しきい値電圧が高くなる。これを利用してトランジスターTF4のしきい値電圧V<sub>TPL</sub>を、ティピカル値である0.25Vよりも少しだけ高い電圧に設定する。トランジスターTF4の入力電圧範囲は0.6~0.45Vであり、V<sub>INmin</sub>=0.45Vである。従って、オン条件であるV<sub>INmin</sub>=0.45V > V<sub>TPL</sub>+V<sub>BS</sub>+V<sub>PR</sub>+V<sub>TS</sub>を満たすことができる。またオフ条件であるV<sub>TPL</sub>-V<sub>PR</sub>-V<sub>TS</sub>>0も満たすことができる。またゲート長Lを長くすることによるしきい値電圧の微調整により、オフリーク電流に起因する性能低下の回避条件等も満たすことができる。

#### 【0130】

また図8では、最終段のN型のトランジスターTF3として、しきい値電圧のティピカル値が0.45Vである種類PRM(中耐圧)のトランジスターを用いている。そして、このトランジスターTF3のゲート長Lは、標準のゲート長である0.4μmよりも長くなっている。図6Aに示すように、種類PRMのN型のトランジスターは、逆短チャネル効果により、ゲート長を長くすることで、しきい値電圧が低くなる。これをを利用してトランジスターTF3のしきい値電圧V<sub>TNL</sub>を、ティピカル値よりも低い電圧に設定する。例えばゲート長Lを2μm以上に設定することで、しきい値電圧V<sub>TNL</sub>をティピカル値である0.45Vから例えば0.1~0.15V程度、低い電圧にする。トランジスターTF3の入力電圧範囲は0.45~0.3Vであり、(VDDA-V<sub>IN</sub>)<sub>min</sub>=0.45Vである。従って、オン条件である(VDDA-V<sub>IN</sub>)<sub>min</sub>=0.45V > V<sub>TNL</sub>+V<sub>BS</sub>+V<sub>PR</sub>+V<sub>TS</sub>を満たすことができる。またオフ条件であるV<sub>TNL</sub>-V<sub>PR</sub>-V<sub>TS</sub>>0も満たすことができる。またゲート長Lを長くすることによるしきい値電圧の微調整により、オフリーク電流に起因する性能低下の回避条件等も満たすことができる。

#### 【0131】

また図8では、最終段のN型のトランジスターTF2として、しきい値電圧のティピカル値が0.45Vである種類PRM(中耐圧)のトランジスターを用いている。そして、このトランジスターTF2のゲート長Lは、標準のゲート長である0.4μmよりも少しだけ短くなっている。種類PRMのN型のトランジスターは逆短チャネル効果のトランジスターであるため、ゲート長Lを少しだけ短くすることで、トランジスターTF2のしきい値電圧V<sub>TNM</sub>を、ティピカル値である0.45Vよりも少しだけ高い電圧に設定できる。トランジスターTF2の入力電圧範囲は0.3~0.15Vであり、(VDDA-V<sub>IN</sub>)<sub>min</sub>=0.6Vである。従って、オン条件である(VDDA-V<sub>IN</sub>)<sub>min</sub>=0.6V > V<sub>TNM</sub>+V<sub>BS</sub>+V<sub>PR</sub>+V<sub>TS</sub>を満たすことができる。またオフ条件であるV<sub>TNM</sub>-V<sub>PR</sub>-V<sub>TS</sub>>0も満たすことができる。またゲート長Lを長くすることによるしきい値電圧の微調整により、オフリーク電流に起因する性能低下の回避条件等も満たすことができる。

#### 【0132】

例えば図8において、オフリーク電流に起因する性能低下の回避条件が厳しくなる場所は、P型トランジスターとN型トランジスターの境界である。即ち、図5のオフリーク電流I<sub>L</sub>が発生するトランジスターが、P型のトランジスターTF4であり、オン状態となってオフリーク電流I<sub>L</sub>が流れるトランジスターが、N型のトランジスターTF3である場合である。この場合にも、ゲート長Lによりしきい値電圧を微調整することで、オフリーク電流に起因する非直線性誤差の増加などの性能低下を回避できるようになる。

#### 【0133】

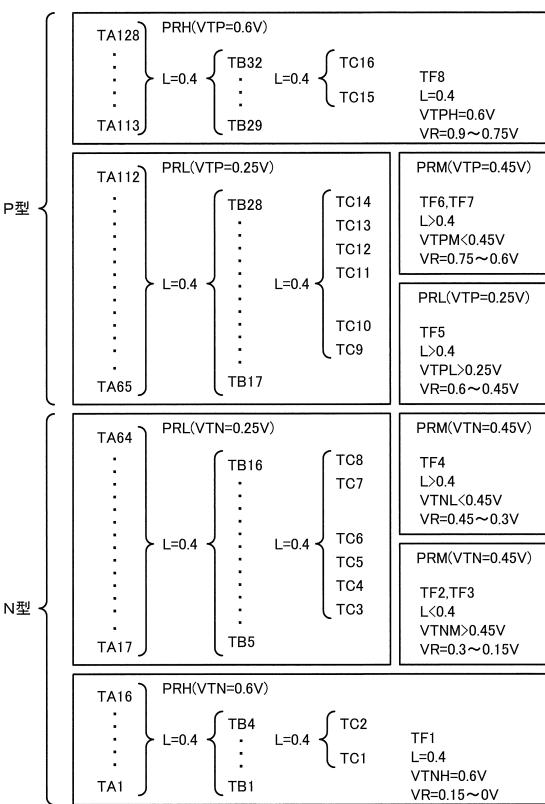

図9はしきい値電圧の設定の他の具体例である。図9では、1段目のセレクターブロック(BLA)は、128個のトランジスターTA1~TA128により構成され、2段目のセレクターブロック(BLB)は、32個のトランジスターTB1~TB32により構成される。即ち、1段目のセレクターブロックは、32個の4入力/1出力のセレクターにより構成され、2段目のセレクターブロックは、16個の2入力/1出力のセレクターにより構成される。また3段目のセレクターブロックは、16個のトランジスターTC1

10

20

30

40

50

～T C 1 6 により構成され、最終段のセレクターブロックは、8個のトランジスターT F 1～T F 8 により構成される。即ち、3段目のセレクターブロックは、8個の2入力/1出力のセレクターにより構成され、最終段目のセレクターブロックは、1個の8入力/1出力のセレクターにより構成される。なお、これらのトランジスターに対する種類P R H、P R M、P R Lの設定や、ゲート長Lの設定は、図8と同様であるため、詳細な説明は省略する。

#### 【0134】

##### 4. 電源回路

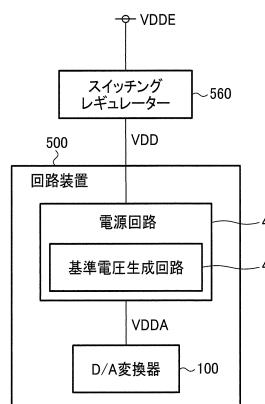

図10Aに本実施形態の回路装置500と、回路装置500を含む電子機器の構成例を示す。なお電子機器や回路装置500は他の構成要素を含むことができるが、ここでは図示を省略している。10

#### 【0135】

回路装置500は、図1～図9で説明した本実施形態のD/A変換器100と、D/A変換器100に電源電圧(VDDA)を供給する電源回路44を含む。そして電源回路44は、トランジスターの仕事関数差に基づき生成された基準電圧を生成する基準電圧生成回路45を有し、基準電圧生成回路45により生成された基準電圧を電源電圧(VDDA)として、D/A変換器100に供給する。

#### 【0136】

図10Aの電子機器は、スイッチングレギュレーター560(広義には外部電源回路)と、回路装置500を含む。回路装置500の電源回路44には、スイッチングレギュレーター560から外部電源(VDD)が供給される。20

#### 【0137】

スイッチングレギュレーター560は、例えばトランジスター等のスイッチ素子とインダクター、キャパシター、ダイオード等で構成される。そして、スイッチ素子がオンになるオン期間では、電源(VDDE)とインダクターの一端がスイッチ素子を介して接続されてインダクターが駆動されると共にキャパシターに電荷が供給される。スイッチ素子がオフになるオフ期間では、電源とインダクターの一端が遮断され、インダクターに蓄えられたエネルギーが放電されてダイオードを介したキャパシターに電荷が供給される。スイッチングレギュレーター560の出力電圧をフィードバックすることにより、オン期間とオフ期間のデューティーが制御され、出力電圧が一定に保たれる。30

#### 【0138】

なお、スイッチングレギュレーター560の構成はこれに限定されず、スイッチ素子のオンオフにより断続的に電源を接続及び遮断するDC-DCコンバーターであればよい。

#### 【0139】

このようなスイッチングレギュレーター560は、リニアレギュレーターのような抵抗による電力ロスがほとんどないため、リニアレギュレーターに比べて低消費電力である。一方、スイッチ素子によりショッピングを行うため、リニアレギュレーターに比べて、生成される電源電圧(VDD)のノイズが大きい。この点、図10Aの構成では、仕事関数差に基づき電源電圧(VDDA)を生成することで、電源回路44の消費電力を抑えつつ、高いPSRR(Power Supply Rejection Ratio)を実現することが可能であり、スイッチングレギュレーター560と電源回路44を含めた電源システム全体としての低消費電力化や低ノイズ化が可能になる。例えばPSRRが高ければ、スイッチングレギュレーター560が生成する電源電圧(VDD)のノイズを十分に低減できる。40

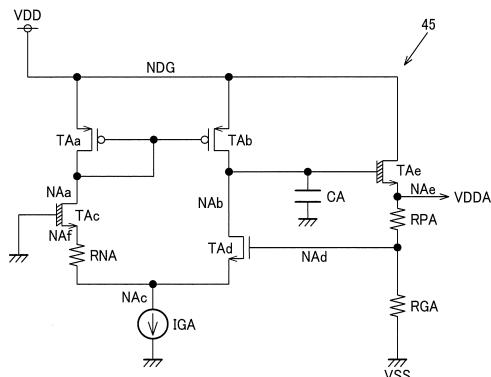

#### 【0140】

図10Bに、基準電圧生成回路45の第1の構成例を示す。図10Bの基準電圧生成回路45は、トランジスターT A a、T A b、T A c、T A d、T A e、抵抗R N A、R P A、R G A、キャパシターC A、電流源I G Aを含む。

#### 【0141】

トランジスターT A aとトランジスターT A bは、カレントミラー回路を構成し、トランジスターT A cとトランジスターT A dに電流を供給する。トランジスターT A cとト50

ランジスター T A d は差動対を構成する。電流源 I G A は、差動対にバイアス電流を供給する。トランジスター T A a、T A b は例えば P 型トランジスター（広義には第 1 導電型のトランジスター）であり、トランジスター T A c、T A d は N 型トランジスター（広義には第 2 導電型のトランジスター）である。またトランジスター T A a、T A b、T A d はエンハンスマント型のトランジスターであり、トランジスター T A c はデプレッション型のトランジスターである。

#### 【 0 1 4 2 】

トランジスター T A a、T A b のソースには V D D の電源電圧が供給され、トランジスター T A a、T A b のゲート電極はトランジスター T A c のドレインのノード N A a に接続される。

10

#### 【 0 1 4 3 】

トランジスター T A c、T A d は、ノード N A a、N A b とノード N A f、N A c との間に設けられる。またノード N A f とノード N A c との間には抵抗 R N A が設けられる。トランジスター T A c のゲート電極には、V S S の電源電圧が入力される。トランジスター T A d のゲート電極は、ノード N A d に接続される。電流源 I G A は、ノード N A c と V S S の電源ノードとの間に設けられる。

#### 【 0 1 4 4 】

トランジスター T A e はデプレッション型の N 型トランジスターである。トランジスター T A e は、V D D の電源ノード N D G と出力ノード N A e（抵抗 R P A の一端）との間に設けられ、そのゲート電極に差動対の出力ノード N A b が接続される。即ち、トランジスター T A e は、トランジスター T A d のドレイン電圧に基づきゲート電圧が制御される。キャパシター C A は、ノード N A b と V S S のノードとの間に設けられる。抵抗 R P A は、出力ノード N A e とノード N A d の間に設けられ、一端（ノード N A e）の電圧を、基準電圧である電源電圧 V D D A として出力する。抵抗 R G A は、ノード N A d と V S S のノードとの間に設けられる。

20

#### 【 0 1 4 5 】

トランジスター T A d は、トランジスター T A c とはゲート電極の導電性が異なるトランジスターになっている。例えばトランジスター T A c のゲート電極は N 型であり、トランジスター T A d のゲート電極は P 型となっている。例えばトランジスター T A c と T A d は、基板の不純物濃度やチャネルの不純物濃度は同じであるが、ゲート電極の導電性が異なっており、ゲート電極の不純物濃度が異なっている。

30

#### 【 0 1 4 6 】

例えば、MOSトランジスターのしきい値電圧は、 $V_{t h} = \frac{m_s - Q_{ss}}{C_{ox}} + 2\sqrt{F} + \frac{Q_D}{C_{ox}}$  と表すことができる。ここで  $m_s$  は、ゲート電極と基板の仕事関数差であり、 $Q_{ss}$  は酸化膜内の固定電荷であり、 $C_{ox}$  はゲート酸化膜の単位面積当たりの容量であり、 $F$  はフェルミ準位であり、 $Q_D$  は空乏層内の電荷である。トランジスター T A c の N 型ゲート電極の不純物濃度と、トランジスター T A d の P 型ゲート電極の不純物濃度の設定により、デプレッション型のトランジスター T A c のしきい値電圧  $V_{T 1}$  は例えば -0.52V に設定されており、エンハンスマント型のトランジスター T A d のしきい値電圧  $V_{T 2}$  は例えば 0.45V に設定されている。従って、基準電圧生成回路 45 の出力ノード N A e には、 $V_{T 2} - V_{T 1} = 0.97V$  の基準電圧が、電源電圧 V D D A として出力されるようになる。即ち、スイッチングレギュレーター 560 からの電源 V D D が変動した場合にも、一定電圧の電源電圧 V D D A を供給することが可能になる。

40

#### 【 0 1 4 7 】

図 1 1 に、基準電圧生成回路 45 の第 2 の構成例を示す。図 1 1 の基準電圧生成回路 45 は、第 1 の仕事関数差アンプ R E G 1、第 2 の仕事関数差アンプ R E G 2 を含む。第 1 の仕事関数差アンプ R E G 1 は、トランジスター T B a、T B b、T B c、T B d、T B e、抵抗 R N B、R P B、R G B、キャパシター C B、電流源 I G B を含む。第 2 の仕事関数差アンプ R E G 2 は、トランジスター T A a、T A b、T A c、T A d、T A e、抵抗 R N A、R P A、R G A、キャパシター C A、電流源 I G A を含む。

50

**【0148】**

第1、第2の仕事関数差アンプREG1、REG2の構成は、図10Bの回路の構成と同様である。即ち、図11では、図10Bの構成の回路が直列に接続された構成となっている。具体的には、第1の仕事関数差アンプREG1が、基準電圧である出力電圧Vregを生成し、この出力電圧Vregが、第2の仕事関数差アンプREG2の電源ノードNDGに対して供給される。即ち、同じ回路構成の仕事関数差アンプが2段積みとなる構成となっている。そして第2の仕事関数差アンプREG2により生成された基準電圧が、電源電圧VDDAとして出力される。具体的には、第1の仕事関数差アンプREG1が電圧Vreg = 0.97Vを出力し、第2の仕事関数差アンプREG2が電圧Vreg = 0.97Vを電源として電源電圧VDDA = 0.9Vを出力する。

10

**【0149】**

このように、第1の仕事関数差アンプREG1と第2の仕事関数差アンプREG2を直列に接続することによって、図10Bのような1段の仕事関数差アンプよりも、更にPSRRを向上できる。

**【0150】**

以上に説明した図10A～図11の構成によれば、トランジスターの仕事関数差に基づいて基準電圧が生成され、その基準電圧が電源電圧VDDAとして、D/A変換器100等の回路装置500の各回路に供給される。これにより、D/A変換器100や回路装置500の低消費電力化を実現できる。

**【0151】**

例えは本実施形態の比較例として、基準電圧生成回路45としてバンドギャップリファレンス回路を用いる手法が考えられる。しかしながら、バンドギャップリファレンス回路は、バンドギャップ電圧の温度依存性をキャンセルするために複数のバイポーラートランジスターを用いており、それらに流すバイアス電流等によって、消費電流が大きい回路となってしまう。そのため、高いPSRRを維持しつつ、消費電流を絞ることが難しいという課題がある。電源のノイズ特性は、例えば回路装置500を発振器に適用した場合には、発振器の発振信号の精度（例えは位相ノイズ特性）に影響する。このため、高いPSRRが必要であり、この点からバンドギャップリファレンス回路を用いた電源回路では低消費電力化に限界がある。

20

**【0152】**

この点、本実施形態の電源回路44ではトランジスターの仕事関数差に基づいて電源電圧VDDAを生成することで、バンドギャップリファレンス回路を用いる場合に比べて消費電流を低下させつつ、高いPSRRを維持できる。例えは、ゲート電極と基板の間の仕事関数が異なるトランジスターTAcとトランジスターTAdで差動対を構成し、その差動対の出力をトランジスターTAeにより差動対にフィードバックすることで、電源電圧VDDA（基準電圧）を生成できる。このように、仕事関数差を用いた場合には簡素な構成で電源回路44を構成できるので、バイアス電流を小さくすることが容易である。

30

**【0153】**

また本実施形態の電源回路44によれば、高いPSRRが得られることから、より上流側の外部電源として、図10Aに示すようにスイッチングレギュレーター560を用いることが可能となる。即ち、スイッチングレギュレーター560により発生するノイズを、高いPSSRの電源回路44により除去できる。

40

**【0154】**

また図10B、図11に示す基準電圧生成回路45は、バンドギャップリファレンス回路に比べて、回路規模が小さいという利点がある。このため、例えは回路装置の各回路ブロック毎に基準電圧生成回路45を設けるというような、電源回路44の構成が可能になる。例えはD/A変換器100を含むD/A変換部には、第1の基準電圧生成回路が電源電圧を供給し、後述するA/D変換部、処理部には、各々、第2、第3の基準電圧生成回路が電源電圧を供給するというような構成が可能になる。これにより基準電圧生成回路を用いた電源分離が可能になる。

50

**【0155】**

そして図10A～図11で説明したような電源回路44を用いた場合には、VDDAの電圧がトランジスターの仕事関数差を用いて生成されるため、VDDAが例えば0.9Vというように非常に低い電圧になる。従って、VDDAが供給されるD/A変換器100の適正なD/A変換（電圧選択）を実現できなくなるおそれがある。

**【0156】**

この点、図1～図9で説明した本実施形態のD/A変換器100では、前述したように、電源ノードから遠い側のトランジスターのしきい値電圧を、近い側のトランジスターに比べて低い電圧に設定する手法を採用している。また、しきい値電圧の設定を、トランジスターの種類による粗調整やゲート長による微調整により実現している。従って、VDDAの電圧が例えば0.9Vというように非常に低い電圧である場合にも、D/A変換器100の適正なD/A変換を実現することが可能になる。10

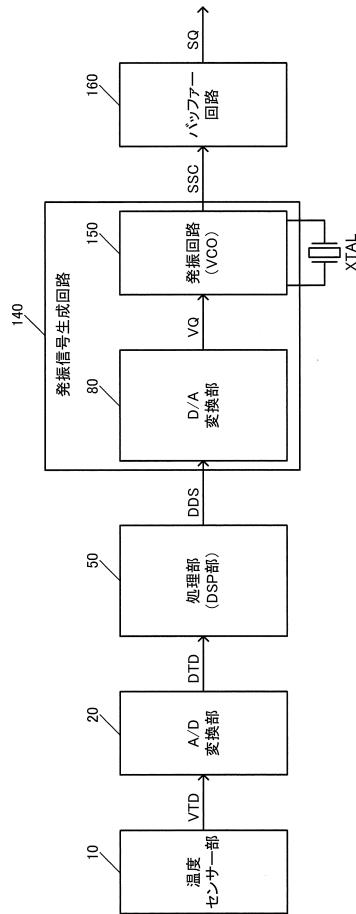

**【0157】****5. 回路装置**

次に本実施形態のD/A変換器100を有する回路装置の構成の一例について説明する。例えば図12の回路装置は、DTCXOやOCXO等のデジタル方式の発振器を実現する回路装置（半導体チップ）である。この回路装置と振動子XTALをパッケージに収納することで、デジタル方式の発振器が実現される。

**【0158】**

図12の回路装置は、A/D変換部20、処理部50、発振信号生成回路140を含む。また回路装置は温度センサー部10、バッファー回路160を含むことができる。なお回路装置の構成は図12の構成には限定されず、その一部の構成要素（例えば温度センサー部、バッファー回路、A/D変換部等）を省略したり、他の構成要素を追加するなどの種々の変形実施が可能である。20

**【0159】**

振動子XTALは、例えば水晶振動子等の圧電振動子である。振動子XTALは恒温槽内に設けられるオープン型振動子（OCXO）であってもよい。振動子XTALは共振器（電気機械的な共振子又は電気的な共振回路）であってもよい。振動子XTALとしては、圧電振動子、SAW（Surface Acoustic Wave）共振子、MEMS（Micro Electro Mechanical Systems）振動子等を採用できる。振動子XTALの基板材料としては、水晶、タンタル酸リチウム、ニオブ酸リチウム等の圧電単結晶や、ジルコン酸チタン酸鉛等の圧電セラミックス等の圧電材料、又はシリコン半導体材料等を用いることができる。振動子XTALの励振手段としては、圧電効果によるもの用いてもよいし、クーロン力による静電駆動を用いてもよい。30

**【0160】**

温度センサー部10は、温度検出電圧VTDを出力する。具体的には、環境（回路装置）の温度に応じて変化する温度依存電圧を、温度検出電圧VTDとして出力する。

**【0161】**

A/D変換部20は、温度センサー部10からの温度検出電圧VTDのA/D変換を行って、温度検出データDTDを出力する。例えば温度検出電圧VTDのA/D変換結果に対応するデジタルの温度検出データDTD（A/D結果データ）を出力する。A/D変換部20のA/D変換方式としては、例えば逐次比較方式や逐次比較方式に類似する方式などを採用できる。なおA/D変換方式はこのような方式には限定されず、種々の方式（計数型、並列比較型又は直並列型等）を採用できる。このA/D変換部20にも図1、図2等の本実施形態のD/A変換器を用いることができる。40

**【0162】**

処理部50（DSP部：デジタル信号処理部）は種々の信号処理を行う。例えば処理部50（温度補償部）は、温度検出データDTDに基づいて発振周波数（発振信号の周波数）の温度補償処理を行う。そして発振周波数の周波数制御データDDSを出力する。具体的には処理部50は、温度に応じて変化する温度検出データDTD（温度依存データ）と50

、温度補償処理用の係数データ（近似関数の係数のデータ）などに基づいて、温度変化があった場合にも発振周波数を一定にするための温度補償処理を行う。この処理部50は、ゲートアレイ等のASIC回路により実現してもよいし、プロセッサーとプロセッサー上で動作するプログラムにより実現してもよい。

#### 【0163】

発振信号生成回路140は発振信号SSCを生成する。例えば発振信号生成回路140は、処理部50からの周波数制御データDDSと振動子XTALを用いて、周波数制御データDDSにより設定される発振周波数の発振信号SSCを生成する。一例としては、発振信号生成回路140は、周波数制御データDDSにより設定される発振周波数で振動子XTALを発振させて、発振信号SSCを生成する。

10

#### 【0164】

なお発振信号生成回路140は、ダイレクト・デジタル・シンセサイザー方式で発振信号SSCを生成する回路であってもよい。例えば振動子XTAL（固定発振周波数の発振源）の発振信号をリファレンス信号として、周波数制御データDDSで設定される発振周波数の発振信号SSCをデジタル的に生成してもよい。

#### 【0165】

発振信号生成回路140は、D/A変換部80と発振回路150を含むことができる。但し発振信号生成回路140は、このような構成には限定されず、その一部の構成要素を省略したり、他の構成要素を追加するなどの種々の変形実施が可能である。

20

#### 【0166】

D/A変換部80は、処理部50からの周波数制御データDDS（処理部の出力データ）のD/A変換を行う。D/A変換部80に入力される周波数制御データDDSは、処理部50による温度補償処理後の周波数制御データ（周波数制御コード）である。

#### 【0167】

発振回路150は、D/A変換部80の出力電圧VQと振動子XTALを用いて、発振信号SSCを生成する。発振回路150は、第1、第2の振動子用端子（振動子用パッド）を介して振動子XTALに接続される。例えば発振回路150は、振動子XTAL（圧電振動子、共振子等）を発振させることで、発振信号SSCを生成する。具体的には発振回路150は、D/A変換部80の出力電圧VQを周波数制御電圧（発振制御電圧）とした発振周波数で、振動子XTALを発振させる。例えば発振回路150が、電圧制御により振動子XTALの発振を制御する回路（VCO）である場合には、発振回路150は、周波数制御電圧に応じて容量値が変化する可変容量キャパシター（バリキヤップ等）を含むことできる。

30

#### 【0168】

なお、前述のように発振回路150はダイレクト・デジタル・シンセサイザー方式により実現してもよく、この場合には振動子XTALの発振周波数はリファレンス周波数となり、発振信号SSCの発振周波数とは異なる周波数になる。

#### 【0169】

バッファー回路160は、発振信号生成回路140（発振回路150）で生成された発振信号SSCのバッファリングを行って、バッファリング後の信号SQを出力する。即ち、外部の負荷を十分に駆動できるようにするためのバッファリングを行う。信号SQは例えばクリップドサイン波信号である。但し信号SQは矩形波信号であってもよい。或いはバッファー回路160は、信号SQとしてクリップドサイン波信号と矩形波信号の両方の出力が可能な回路であってもよい。

40

#### 【0170】

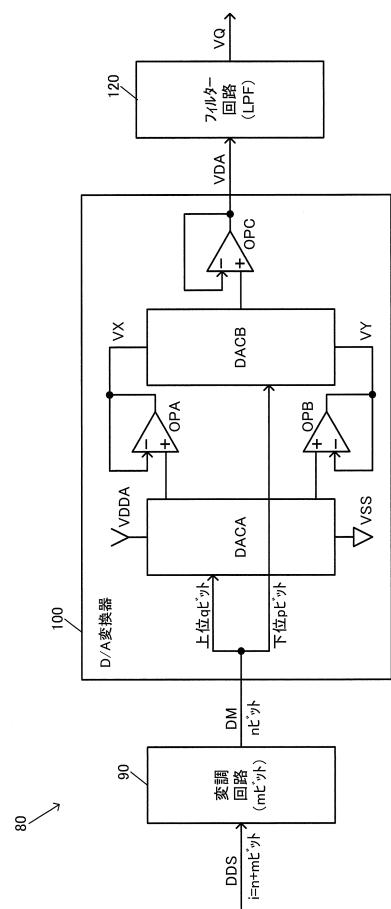

図13に本実施形態の回路装置の詳細な構成例を示す。図13ではD/A変換部80が、変調回路90とD/A変換器100とフィルター回路120を含む。

#### 【0171】

D/A変換部80の変調回路90は、処理部50から $i = (n + m)$ ビットの周波数制御データDDSを受ける（ $i$ 、 $n$ 、 $m$ は1以上の整数）。一例としては $i = 20$ 、 $n = 1$

50

6、 $m = 4$  である。そして変調回路 90 は、周波数制御データ DDS の  $m$  ビット（例えば 4 ビット）のデータに基づいて、周波数制御データ DDS の  $n$  ビット（例えば 16 ビット）のデータを変調する。具体的には変調回路 90 は、周波数制御データ DDS の PWM 变調を行う。なお変調回路 90 の変調方式は PWM 变調（パルス幅变調）には限定されず、例えば PDM 变調（パルス密度变調）等のパルス变調であってもよく、パルス变調以外の变調方式であってもよい。例えば周波数制御データ DDS の  $n$  ビットのデータに対して、 $m$  ビットのディザー処理（ディザーリング処理）を行うことでビット拡張（ $n$  ビットから  $i$  ビットへのビット拡張）を実現してもよい。

#### 【 0 1 7 2 】

D / A 变換器 100 は、変調回路 90 により变調された  $n$  ビットのデータの D / A 变換を行なう。例えば  $n = 16$  ビットのデータの D / A 变換を行なう。 10

#### 【 0 1 7 3 】

フィルター回路 120 は、D / A 变換器 100 の出力電圧 VDA を平滑化する。例えばローパスフィルター処理を行なって出力電圧 VDA を平滑化する。このようなフィルター回路 120 を設けることで、例えば PWM 变調された信号の PWM 復調が可能になる。このフィルター回路 120 のカットオフ周波数は、変調回路 90 の PWM 变調の周波数に応じて設定できる。即ち D / A 变換器 100 からの出力電圧 VDA の信号は、PWM 变調の基本周波数及び高調波成分のリップルを含むため、フィルター回路 120 により、このリップルを減衰させる。なおフィルター回路 120 としては、例えば抵抗又はキャパシター等の受動素子を用いたパッシブフィルターを採用できる。但しフィルター回路 120 として S 20 CF などのアクティブフィルターを用いることも可能である。

#### 【 0 1 7 4 】

例えば温度補償型発振器である TCXO では、周波数精度の向上と低消費電力化への要求がある。例えば GPS 内蔵の時計や脈波等の生体情報の測定機器などのウェアラブル機器では、バッテリーによる動作継続時間を長くする必要がある。このため、基準信号源となる TCXO に対しては、周波数精度を確保しながら、より低消費電力であることが要求される。 20

#### 【 0 1 7 5 】

また通信端末と基地局との通信方式としては種々の方式が提案されている。例えば TDD (Time Division Duplex) 方式では、各機器は割り当てられたタイムスロットにおいてデータを送信する。そしてタイムスロット（上がり回線スロット、下り回線スロット）の間にガードタイムが設定されることで、タイムスロットが重なるのが防止される。次世代の通信システムでは、例えば 1 つの周波数帯域（例えば 50 GHz）を用いて、TDD 方式でデータ通信することが提案されている。 30

#### 【 0 1 7 6 】

しかしながら、このような TDD 方式を採用した場合には、各機器において時刻同期を行う必要があり、正確な絶対時刻の計時が要求される。このような要求を実現するために、例えば各機器に、基準信号源として原子時計（原子発振器）を設ける手法も考えられるが、機器の高コスト化を招いたり、機器が大型化するなどの問題が生じる。 40

#### 【 0 1 7 7 】

また TCXO には、アナログ方式の温度補償型発振器である ATCXO と、デジタル方式の温度補償型発振器である DT CXO がある。 40

#### 【 0 1 7 8 】

そして基準信号源として ATCXO を用いた場合に、周波数精度を高精度化しようとすると、回路装置のチップサイズが増加してしまい、低コスト化や低消費電力化の実現が難しくなる。一方、DT CXO では、回路装置のチップサイズをそれほど大きくすることなく、周波数精度の高精度化を実現できるという利点がある。

#### 【 0 1 7 9 】

しかしながら、DT CXO 等のデジタル方式の発振器では、その発振周波数の周波数ドリフトが原因で、発振器が組み込まれた通信装置において通信エラー等が発生してしまう 50

という問題がある。例えばデジタル方式の発振器では、温度センサー部からの温度検出電圧をA/D変換し、得られた温度検出データに基づいて周波数制御データの温度補償処理を行い、当該周波数制御データに基づいて発振信号を生成する。この場合に、温度変化により周波数制御データの値が大きく変化すると、これが原因で周波数ホッピングの問題が生じることが判明した。このような周波数ホッピングが生じると、GPS関連の通信装置を例にとれば、GPSのロックが外れてしまうなどの問題が発生してしまう。

#### 【0180】

このような周波数ホッピングを原因とする通信エラーの発生を抑制し、周波数精度の向上を図るためにには、D/A変換部80の分解能をできる限り高くする必要がある。

#### 【0181】

しかしながら、例えば抵抗ストリング型等のD/A変換器100だけで、例えば*i*=20ビットというような高分解能のD/A変換を実現するのは困難である。またD/A変換部80の出力雑音が大きいと、当該雑音が原因となって、周波数精度の向上の実現が難しくなる。

#### 【0182】

そこで図13では、D/A変換部80に変調回路90を設ける。また処理部50は、D/A変換器100の分解能であるnビット(例えば16ビット)よりもビット数が多い*i*=*m*+*n*ビットの周波数制御データDDSを出力する。処理部50は、例えば温度補償処理等のデジタル信号処理を実現するために、浮動小数点演算等を行っているため、このような*n*ビット(例えば*n*=16ビット)よりもビット数が多い*i*=*m*+*n*ビットの周波数制御データDDSを出力することは容易である。

10

20

#### 【0183】

そして変調回路90は、*i*=*m*+*n*のうちの*m*ビットのデータに基づいて、*i*=*m*+*n*のうちの*n*ビットのデータの変調(PWM変調等)を行い、変調後の*n*ビットのデータDMをD/A変換器100に出力する。そしてD/A変換器100がデータDMのD/A変換を行い、得られた出力電圧VDAの平滑化処理をフィルター回路120が行うことで、*i*=*m*+*n*ビット(例えば20ビット)というような高分解能のD/A変換を実現できるようになる。

#### 【0184】

この構成によれば、D/A変換器100として例えば出力雑音が少ない抵抗ストリング型等を採用できるため、D/A変換部80の出力雑音を低減でき、周波数精度の劣化の抑制が容易になる。例えば変調回路90での変調により雑音が発生するが、当該雑音についても、フィルター回路120のカットオフ周波数の設定により十分に減衰することができ、当該雑音を原因とする周波数精度の劣化を抑制できる。

30

#### 【0185】

なおD/A変換部80の分解能は*i*=20ビットには限定されず、20ビットよりも高い分解能であってもよいし、低い分解能であってもよい。また変調回路90の変調のビット数も*m*=4ビットには限定されず、4ビットよりも大きくてよいし(例えば*m*=8ビット)、小さくてもよい。

#### 【0186】

また図13では、D/A変換部80の前段に、温度補償処理等のデジタル信号処理を行う処理部50が設けられていることを、有効活用している。即ち、処理部50は、例えば浮動小数点演算などにより、高精度で、温度補償処理等のデジタル信号処理を実行している。従って、例えば浮動小数点演算の結果の仮数部の下位ビットも有効なデータとして扱って、バイナリーデータに変換すれば、例えば*i*=*m*+*n*=20ビットというような高いビット数での周波数制御データDDSも、容易に出力できる。図13ではこの点に着目し、このような高いビット数である*i*=*m*+*n*ビットの周波数制御データDDSを、D/A変換部80に供給し、*m*ビットの変調回路90と*n*ビットのD/A変換器100を用いて、*i*=*m*+*n*ビットというような高分解能のD/A変換の実現に成功している。

40

#### 【0187】

50

このようにD/A変換部80の分解能を高分解能にすることで、上述した周波数ホッピングの発生を抑制できる。これにより周波数ホッピングを原因とする通信エラー等の発生を抑制することが可能になる。

#### 【0188】

また、このような周波数ホッピングの問題以外にも、DTCXOやOCXOなどのデジタル方式の発振器では、発振周波数に対して非常に高い周波数精度が要求される。例えば前述のTDD方式では、上がりと下りで同じ周波数を用いて時分割でデータが送受信され、各機器に割り当てられたタイムスロットの間にはガードタイムが設定されている。このため、適正な通信を実現するためには、各機器において時刻同期を行う必要があり、正確な絶対時刻の計時が要求される。例えば基準信号（GPS信号やインターネットを介した信号）が消失又は異常となるホールドオーバーが発生した場合には、基準信号が無い状態で発振器側が正確に絶対時刻を計時する必要がある。このため、このような機器（GPS関連機器、基地局等）に用いられる発振器には、非常に高い発振周波数精度が要求される。

#### 【0189】

このような要求を実現するために、例えば各機器に原子時計などを設ける手法を採用すると、機器の高コスト化や大規模化を招く。また、高い周波数精度の発振器を実現したとしても、発振器に用いられる回路装置が大規模化したり、消費電力が非常に大きくなってしまうのは望ましくない。

#### 【0190】

この点、図13の回路装置の構成によれば、D/A変換部80に、変調回路90やフィルター回路120を設けるだけで、例えば $i = 20$ ビットとなるような非常に高い分解能のD/A変換部80を実現でき、このように分解能が高くなることで、発振周波数の高精度化を実現できる。そして、このような変調回路90やフィルター回路120を設けることによる回路装置のチップサイズの増加や消費電力の増加は、それほど大きくない。更に処理部50では浮動点小数点演算などにより温度補償処理を実行しているため、例えば $i = 20$ ビットとなるような周波数制御データDDSをD/A変換部80に出力することも容易である。従って、図13の回路装置の構成は、発振周波数の高精度化と、回路装置の規模や消費電力の増加の抑制とを、両立して実現できるという利点がある。

#### 【0191】

なお図12、図13の回路装置は、基準信号（GPS信号やインターネットを介した信号）と発振信号に基づく入力信号を比較する位相比較回路を有するPLL回路における、発振用ICとしても用いることができる。この場合には、例えば当該位相比較回路からの周波数制御データに対して、処理部50が温度補償処理やエージング補正処理等を行って、発振信号生成回路140により発振信号を生成すればよい。

#### 【0192】

また処理部50は、第1の温度から第2の温度に温度が変化した場合に、第1の温度（第1の温度検出データ）に対応する第1のデータから、第2の温度（第2の温度検出データ）に対応する第2のデータへと、 $k \times LSB$ 単位で変化（ $k \times LSB$ ずつ変化）する周波数制御データDDSを出力する。ここで $k > 1$ であり、 $k$ は1以上の整数である。例えば周波数制御データDDSのビット数（D/A変換部の解像度）を $i$ とした場合に、 $k < 2^i$ であり、 $k$ は $2^i$ よりも十分に小さい整数である（例えば $k = 1 \sim 8$ ）。更に具体的には $k < 2^m$ である。例えば $k = 1$ の場合には、処理部50は、1 LSB単位（1ビット単位）で第1のデータから第2のデータに変化する周波数制御データDDSを出力する。即ち、第1のデータから第2のデータに向かって、1 LSB（1ビット）ずつシフトしながら変化するような周波数制御データDDSを出力する。なお周波数制御データDDSの変化ステップ幅は、1 LSBには限定されず、例えば $2 \times LSB$ 、 $3 \times LSB$ 、 $4 \times LSB$ ・・・というように $2 \times LSB$ 以上の変化ステップ幅であってもよい。

#### 【0193】

例えば処理部50は、演算部60と出力部70を含む。演算部60は、温度検出データ

10

20

30

40

50

D T D に基づいて発振周波数の温度補償処理の演算を行う。例えば浮動小数点演算等によるデジタル信号処理により温度補償処理を実現する。出力部 70 は、演算部 60 からの演算結果データ C Q を受け、周波数制御データ D D S を出力する。そして、この出力部 70 が、演算結果データ C Q が第 1 の温度に対応する第 1 のデータから、第 2 の温度に対応する第 2 のデータに変化した場合に、 $k \times L S B$  単位で第 1 のデータから第 2 のデータに変化する周波数制御データ D D S の出力処理を行う。

#### 【 0 1 9 4 】

このように、処理部 50 から出力される周波数制御データ D D S が、 $k \times L S B$  ずつ変化するようになれば、例えば温度が第 1 の温度から第 2 の温度に変化した場合に、D / A 変換部 80 の出力電圧 V Q に大きな電圧変化が生じ、この電圧変化が原因で周波数ホッピングが発生してしまう事態を抑制できる。これにより当該周波数ホッピングが原因で通信エラー等が生じるのを防止できるようになる。10

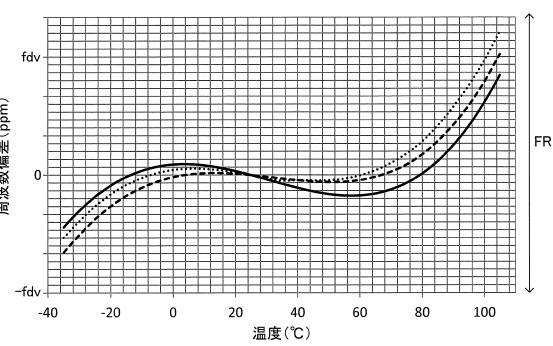

#### 【 0 1 9 5 】

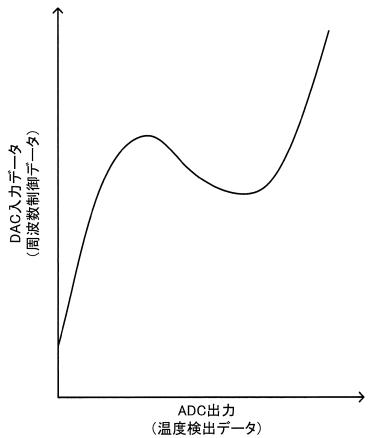

図 14 A は振動子 X T A L ( A T 振動子等 ) の温度による発振周波数の周波数偏差の一例を示す図である。処理部 50 は、図 14 A のような温度特性を有する振動子 X T A L の発振周波数を、温度に依存せずに一定にするための温度補償処理を行う。

#### 【 0 1 9 6 】

具体的には処理部 50 は、A / D 変換部 20 の出力データ ( 温度検出データ ) と D / A 変換部 80 の入力データ ( 周波数制御データ ) とが図 14 B に示すような対応関係になるような温度補償処理を実行する。図 14 B の対応関係 ( 周波数補正テーブル ) は、例えば回路装置が組み込まれた発振器を恒温槽に入れ、各温度での D / A 変換部 80 の入力データ ( D D S ) と A / D 変換部 20 の出力データ ( D T D ) をモニターするなどの手法により取得できる。20

#### 【 0 1 9 7 】

そして図 14 B の対応関係を実現するための温度補償用の近似関数の係数データを、回路装置のメモリー部 ( 不揮発性メモリー ) に記憶しておく。そして処理部 50 が、メモリー部から読み出された係数データと、A / D 変換部 20 からの温度検出データ D T D とに基づいて、演算処理を行うことで、振動子 X T A L の発振周波数を温度に依らずに一定にするための温度補償処理を実現する。なお温度センサー部 10 の温度検出電圧 V T D は、例えば負の温度特性を有している。従って、図 14 B のような温度補償特性で、図 14 A の振動子 X T A L の発振周波数の温度依存性を相殺して補償できるようになる。30

#### 【 0 1 9 8 】

##### 6 . D / A 変換部

図 15、図 16 は D / A 変換部 80 の詳細な構成例を示す図である。D / A 変換部 80 は、変調回路 90 と D / A 変換器 100 とフィルター回路 120 を含む。

#### 【 0 1 9 9 】

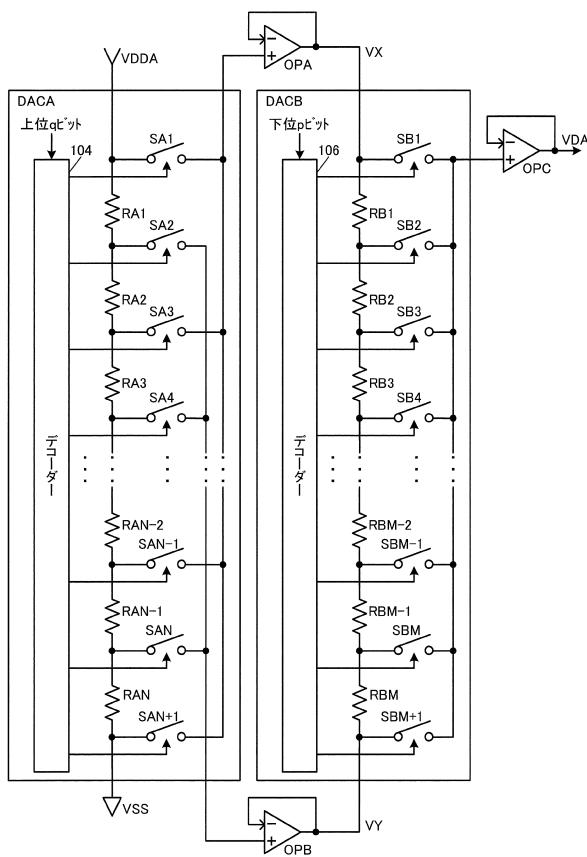

図 15 に示すように、D / A 変換器 100 は、上位側の D / A 変換器 D A C A と、下位側の D / A 変換器 D A C B と、ボルテージフォロワー接続されたオペアンプ ( 演算増幅器 ) O P A 、 O P B 、 O P C を含む。図 1 、図 2 等で説明した本実施形態の D / A 変換器は、例えば上位側の D / A 変換器 D A C A として用いられる。40

#### 【 0 2 0 0 】

上位側 D A C A には、変調回路 90 からの n ビット ( $n = q + p$ ) のデータ D M のうちの上位の q ビットのデータが入力され、下位側 D A C B には下位の p ビット ( 例えば  $p = q = 8$  ) のデータが入力される。これらの上位側 D A C A 、下位側 D A C B は、例えば直列接続された複数の抵抗により電圧分割された複数の分割電圧の中から、入力データに対応する電圧を選択する抵抗ストリング型の D / A 変換器である。

#### 【 0 2 0 1 】

図 16 に示すように上位側 D A C A は、高電位側電源 V D D A のノードと低電位側電源 V S S のノードとの間に直列接続された複数の抵抗 R A 1 ~ R A N を含む。また上位側 D A C A は、これらの抵抗 R A 1 ~ R A N による電圧分割ノードに一端が接続される複数の50

スイッチ素子 S A 1 ~ S A N + 1 と、データ D M の上位 q ビットのデータに基づいて、スイッチ素子 S A 1 ~ S A N + 1 をオン又オフにするスイッチ制御信号を生成するデコーダー 1 0 4 (スイッチ制御回路) を含む。

#### 【 0 2 0 2 】

なおこれらのスイッチ素子等の接続構成は、実際には図 2 のような接続構成になるが、ここでは簡略化して示している。例えば上位側 D A C A は、図 2 の構成の 2 組の第 1 、第 2 の電圧選択回路を有している。そして例えば第 1 の電圧選択回路を構成するセレクターのトランジスターが、スイッチ素子 S A 1 、 S A 3 、 S A 5 ・・・に相当し、第 2 の電圧選択回路を構成するセレクターのトランジスターが、スイッチ素子 S A 2 、 S A 4 、 S A 6 ・・・に相当する。

10

#### 【 0 2 0 3 】

上位側 D A C A は、複数の抵抗 R A 1 ~ R A N のうち上位 q ビットのデータにより特定される抵抗の両端の分割電圧のうち、一方の分割電圧をオペアンプ O P A の非反転入力端子に出力し、他方の分割電圧をオペアンプ O P B の非反転入力端子に出力する。これにより、当該一方の電圧が、ボルテージフォロワー接続されたオペアンプ O P A によりインピーダンス変換されて、電圧 V X として下位側 D A C B に供給される。また当該他方の電圧が、ボルテージフォロワー接続されたオペアンプ O P B によりインピーダンス変換されて、電圧 V Y として下位側 D A C B に供給される。

#### 【 0 2 0 4 】

例えば上位 q ビットのデータにより抵抗 R A 1 が特定された場合には、抵抗 R A 1 の両端の分割電圧のうち、高電位側の分割電圧が、オンになったスイッチ素子 S A 1 及びオペアンプ O P A を介して、電圧 V X として供給される。また低電位側の分割電圧が、オンになったスイッチ素子 S A 2 及びオペアンプ O P B を介して、電圧 V Y として供給される。また上位 q ビットのデータにより抵抗 R A 2 が特定された場合には、抵抗 R A 2 の両端の分割電圧のうち、低電位側の分割電圧が、オンになったスイッチ素子 S A 3 及びオペアンプ O P A を介して、電圧 V X として供給される。また高電位側の分割電圧が、オンになったスイッチ素子 S A 2 及びオペアンプ O P B を介して、電圧 V Y として供給される。

20

#### 【 0 2 0 5 】

下位側 D A C B は、電圧 V X のノードと電圧 V Y のノードとの間に直列接続された複数の抵抗 R B 1 ~ R B M を含む。また下位側 D A C B は、これらの抵抗 R B 1 ~ R B M による電圧分割ノードに一端が接続される複数のスイッチ素子 S B 1 ~ S B M + 1 と、データ D M の下位 p ビットのデータに基づいて、スイッチ素子 S B 1 ~ S B M + 1 をオン又オフにするスイッチ制御信号を生成するデコーダー 1 0 6 (スイッチ制御回路) を含む。

30

#### 【 0 2 0 6 】

そして下位側 D A C B は、抵抗 R B 1 ~ R B M による複数の分割電圧のうち、下位 p ビットのデータにより選択された 1 つの分割電圧を選択電圧として、オンになったスイッチ素子を介して、ボルテージフォロワー接続されたオペアンプ O P C の非反転入力端子に出力する。これにより、当該選択電圧が、D / A 変換器 1 0 0 の出力電圧 V D A として出力されるようになる。

#### 【 0 2 0 7 】

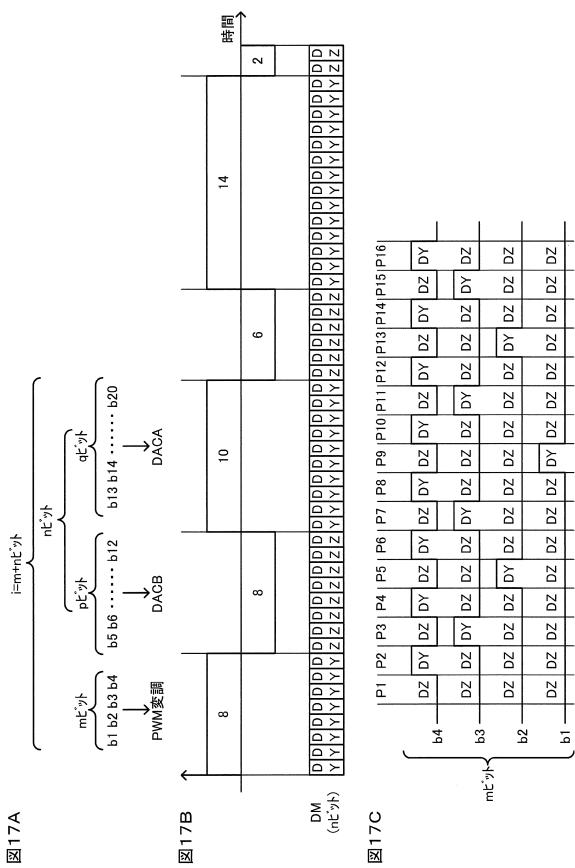

図 1 7 A 、図 1 7 B 、図 1 7 C は変調回路 9 0 の説明図である。図 1 7 A に示すように、変調回路 9 0 は、処理部 5 0 からの  $i = (n + m)$  ビットの周波数制御データ D D S を受ける。そして、この周波数制御データ D D S の下位の m ビットのデータ ( ビット b 1 ~ b 4 ) に基づいて、周波数制御データ D D S の上位の n ビット ( ビット b 5 ~ b 2 0 ) のデータの P W M 变調を行う。そして、当該 n ビットのデータのうち、上位の q ビットのデータ ( ビット b 1 3 ~ b 2 0 ) が、上位側 D A C A に入力され、下位の p ビットのデータ ( ビット b 5 ~ b 1 2 ) が、下位側 D A C B に入力される。

40

#### 【 0 2 0 8 】

図 1 7 B は P W M 变調の第 1 の方式の説明図である。D Y 、 D Z は、データ D M の上位の n ビットのデータであり、 n ビット表現において  $D Y = D Z + 1$  が成り立つデータであ

50

る。

#### 【0209】

PWM変調に用いられる下位の $m = 4$ ビットのデータで表されるデューティー比が、例えば8対8である場合には、図17Bに示すように、8個の16ビットのデータDYと8個の16ビットのデータDZが時分割で、変調回路90からD/A変換器100に出力される。

#### 【0210】

また下位の $m = 4$ ビットのデータで表されるデューティー比が10対6である場合には、10個のデータDYと6個のデータDZが時分割で、変調回路90からD/A変換器100に出力される。同様に、下位の $m = 4$ ビットのデータで表されるデューティー比が14対2である場合には、14個のデータDYと2個のデータDZが時分割で出力される。10

#### 【0211】

図17CはPWM変調の第2の方式の説明図である。PWM変調に用いられる $m = 4$ ビットの各ビット $b_4, b_3, b_2, b_1$ が、論理レベル「1」である場合に、図17Cにおいて各ビットに対応づけられた出力パターン（各ビットの右側に示される出力パターン）が選択される。

#### 【0212】

例えばビット $b_4 = 1$ で、 $b_3 = b_2 = b_1 = 0$ である場合には、ビット $b_4$ に対応づけられた出力パターンだけが期間P1～P16において出力される。即ち、 $n = 16$ ビットのデータがDZ、DY、DZ、DY……の順で時分割に、変調回路90からD/A変換器100に出力される。これにより、データDY、DZの出力回数は共に8回となり、図17Bにおいてデューティー比が8対8である場合と同様のPWM変調が実現される。20

#### 【0213】

またビット $b_4 = b_2 = 1$ で、 $b_3 = b_1 = 0$ である場合には、ビット $b_4$ と $b_2$ に対応づけられた出力パターンが期間P1～P16において出力される。これによりデータDY、DZの出力回数は、各々、10回、6回になり、デューティー比が10対6である場合と同様のPWM変調が実現される。同様に、ビット $b_4 = b_3 = b_2 = 1$ で、 $b_1 = 0$ である場合には、データDY、DZの出力回数は、各々、14回、2回になり、デューティー比が14対2である場合と同様のPWM変調が実現される。30

#### 【0214】

以上のように、本実施形態の変調回路90によれば、データDY、DZの出力回数等を制御するだけでPWM変調を実現でき、例えば16ビットの分解能のD/A変換器100を用いながらも、例えば20ビット以上のD/A変換の分解能を実現できるようになる。

#### 【0215】

例えば雑音が少なく抵抗ストリング型や抵抗ラダー型のD/A変換では、例えば16ビット程度の分解能が実質的な限界である。この点、本実施形態によれば、回路規模の小さな変調回路90とフィルター回路120を設けるだけで、D/A変換の分解能を例えば20ビット以上に向上できる。従って、回路規模の増加を最小限に抑えながら、D/A変換部80の分解能を向上することが可能になる。そしてD/A変換部80の分解能が向上することで、発振周波数精度の高精度化を実現でき、周波数ホッピングの抑制や、時刻同期に好適な発振器の提供を実現できるようになる。40

#### 【0216】

##### 7. 発振器、電子機器、移動体

図18Aに、本実施形態の回路装置500を含む発振器400の構成例を示す。図18Aに示すように、発振器400は、振動子420と回路装置500を含む。振動子420と回路装置500は、発振器400のパッケージ410内に実装される。そして振動子420の端子と、回路装置500（I C）の端子（パッド）は、パッケージ410の内部配線により電気的に接続される。

#### 【0217】

図18Bに、本実施形態の回路装置500（D/A変換器）を含む電子機器の構成例を示す。この電子機器は、本実施形態の回路装置500（D/A変換器）、水晶振動子等の振動子420、アンテナANT、通信部510、処理部520を含む。また操作部530、表示部540、記憶部550を含むことができる。振動子420と回路装置500により発振器400が構成される。なお電子機器は図18Bの構成に限定されず、これらの一部の構成要素を省略したり、他の構成要素を追加するなどの種々の変形実施が可能である。

#### 【0218】

図18Bの電子機器としては、例えばGPS内蔵時計、生体情報測定機器（脈波計、歩数計等）又は頭部装着型表示装置等のウェアラブル機器や、スマートフォン、携帯電話機、携帯型ゲーム装置、ノートPC又はタブレットPC等の携帯情報端末（移動端末）や、コンテンツを配信するコンテンツ提供端末や、デジタルカメラ又はビデオカメラ等の映像機器や、或いは基地局又はルーター等のネットワーク関連機器などの種々の機器を想定できる。

#### 【0219】

通信部510（無線回路）は、アンテナANTを介して外部からデータを受信したり、外部にデータを送信する処理を行う。処理部520は、電子機器の制御処理や、通信部510を介して送受信されるデータの種々のデジタル処理などを行う。この処理部520の機能は、例えばマイクロコンピューターなどのプロセッサーにより実現できる。

#### 【0220】

操作部530は、ユーザーが入力操作を行うためのものであり、操作ボタンやタッチパネルディスプレイをなどにより実現できる。表示部540は、各種の情報を表示するものであり、液晶や有機ELなどのディスプレイにより実現できる。なお操作部530としてタッチパネルディスプレイを用いる場合には、このタッチパネルディスプレイが操作部530及び表示部540の機能を兼ねることになる。記憶部550は、データを記憶するものであり、その機能はRAMやROMなどの半導体メモリーやHDD（ハードディスクドライブ）などにより実現できる。

#### 【0221】

図18Cに、本実施形態の回路装置を含む移動体の例を示す。本実施形態の回路装置（発振器）は、例えば、車、飛行機、バイク、自転車、或いは船舶等の種々の移動体に組み込むことができる。移動体は、例えばエンジンやモーター等の駆動機構、ハンドルや舵等の操舵機構、各種の電子機器（車載機器）を備えて、地上や空や海上を移動する機器・装置である。図18Cは移動体の具体例としての自動車206を概略的に示している。自動車206には、本実施形態の回路装置と振動子を有する発振器（不図示）が組み込まれる。制御装置208は、この発振器により生成されたクロック信号により動作する。制御装置208は、例えば車体207の姿勢に応じてサスペンションの硬軟を制御したり、個々の車輪209のブレーキを制御する。例えば制御装置208により、自動車206の自動運転を実現してもよい。なお本実施形態の回路装置や発振器が組み込まれる機器は、このような制御装置208には限定されず、自動車206等の移動体に設けられる種々の機器（車載機器）に組み込むことが可能である。

#### 【0222】

なお、上記のように本実施形態について詳細に説明したが、本発明の新規事項および効果から実体的に逸脱しない多くの変形が可能であることは当業者には容易に理解できるであろう。従って、このような変形例はすべて本発明の範囲に含まれるものとする。例えば、明細書又は図面において、少なくとも一度、より広義または同義な異なる用語と共に記載された用語は、明細書又は図面のいかなる箇所においても、その異なる用語に置き換えることができる。また本実施形態及び変形例の全ての組み合わせも、本発明の範囲に含まれる。またD/A変換器、回路装置、発振器、電子機器、移動体の構成・動作や、D/A変換手法、電圧選択手法、しきい値電圧の設定手法等も本実施形態で説明したものに限定されず、種々の変形実施が可能である。

10

20

30

40

50

## 【符号の説明】

## 【0223】

B L A ~ B L F ... セレクターブロック、R 1 ~ R 23 ... 抵抗、

S A 1 ~ S A 12、S B 1 ~ S B 6、S F ... セレクター、

T A 1 ~ T A 24、T B 1 ~ T B 12、T F 1 ~ T F 6 ... パワートランジスター、

10 ... 温度センサー部、20 ... A / D 変換部、30 ... デコーダー、

32 ... 電圧生成回路、40 ... 電圧選択回路、42 ... 基板電圧制御回路、

44 ... 電源回路、45 ... 基準電圧生成回路、50 ... 処理部、60 ... 演算部、

70 ... 出力部、80 ... D / A 変換部、90 ... 变調回路、100 ... D / A 変換器、

104、106 ... デコーダー、120 ... フィルター回路、

140 ... 発振信号生成回路、150 ... 発振回路、160 ... バッファーリード回路、

206 ... 自動車、207 ... 車体、208 ... 制御装置、209 ... 車輪、

400 ... 発振器、410 ... パッケージ、420 ... 振動子、500 ... 回路装置、

510 ... 通信部、520 ... 処理部、530 ... 操作部、540 ... 表示部、

550 ... 記憶部、560 ... スイッチングレギュレーター

10

【図1】

【図2】

【図3】

図3A

図3B

【図4】

| 種類  | しきい値電圧の<br>チビカル値 |

|-----|------------------|

| PRH | 0.6V             |

| PRM | 0.45V            |

| PRL | 0.25V            |

| 種類  | しきい値電圧の<br>チビカル値 |

|-----|------------------|

| PRL | 0.25V            |

| PRM | 0.45V            |

| PRH | 0.6V             |

| トランジスター | $V_R$     | $V_{INmin}$ |

|---------|-----------|-------------|

| TF6     | 0.9~0.75V | 0.75V       |

| TF5     | 0.75~0.6V | 0.6V        |

| TF4     | 0.6~0.45V | 0.45V       |

| トランジスター | $V_R$     | $(V_{DDA}-V_{IN})_{min}$ |

|---------|-----------|--------------------------|

| TF3     | 0.45~0.3V | 0.45V                    |

| TF2     | 0.3~0.15V | 0.6V                     |

| TF1     | 0.15~0V   | 0.75V                    |

図4B

【図5】

【図6】

図6A

図6B

図6C

短チャネル効果

図6D

逆短チャネル効果

【図7】

図7A

図7B

図7C

【図8】

【図9】

【図10】

図10A

図10B

【図11】

【図13】

【図12】

【図14】

図14A

図14B

【図15】

【図16】

【図17】

【図18】

---

フロントページの続き

(56)参考文献 特開2011-172100(JP,A)

特開平11-251914(JP,A)

特開平01-157127(JP,A)

特開平06-140212(JP,A)

特開昭55-115721(JP,A)

特開2009-187300(JP,A)

特開2012-108585(JP,A)

特開2002-198737(JP,A)

特開2000-250490(JP,A)

特開2007-037191(JP,A)

(58)調査した分野(Int.Cl., DB名)

H03M 1 / 74

H03B 5 / 32