### (19) **日本国特許庁(JP)**

# (12) 公 開 特 許 公 報(A)

(11)特許出願公開番号

特開2012-117144 (P2012-117144A)

(43) 公開日 平成24年6月21日(2012.6.21)

| (51) Int.Cl. |       |           | F I     |       |           | テーマコート   | : (参考) |

|--------------|-------|-----------|---------|-------|-----------|----------|--------|

| C25D         | 11/00 | (2006.01) | C 2 5 D | 11/00 | 308       | 5F058    |        |

| C25D         | 11/04 | (2006.01) | C 2 5 D | 11/04 | 3 1 1     |          |        |

| C25D         | 11/06 | (2006.01) | C 2 5 D | 11/06 | В         |          |        |

| C25D         | 11/24 | (2006.01) | C 2 5 D | 11/24 | 302       |          |        |

| C25D         | 11/26 | (2006.01) | C 2 5 D | 11/26 | 301       |          |        |

|              |       | 審査請求      | 未請求 請求項 | の数 18 | O L 外国語出願 | (全 53 頁) | 最終頁に続く |

(21) 出願番号 特願2011-90274 (P2011-90274) (22) 出願日 平成23年4月14日 (2011. 4. 14)

(31) 優先権主張番号 61/418, 194

(32) 優先日 平成22年11月30日 (2010.11.30)

(33) 優先権主張国 米国(US)

(71) 出願人 591060898 アイメック IMEC

ベルギー、ベー-3001ルーヴァン、カペルドリーフ75番

(71) 出願人 599098493

カトリーケ・ウニフェルジテイト・ルーベン・カー・イュー・ルーベン・アール・アンド・ディ

Katholieke Universiteit Leuven, K. U. Leuven R&D

ベルギー、ベーー3000ルーベン、ワー

イストラート6番、ボックス5105

最終頁に続く

### (54) 【発明の名称】正確に制御されたマスク陽極酸化のための方法

### (57)【要約】 (修正有)

【課題】基板上の陽極酸化可能な層、例えば犠牲層上に存在するアルミニウム層であって、該犠牲層は、マイクロ電気機械システム又はナノ電気機械システム(MEMS/NEMS)を備えたキャビティから除去する必要があるような層のマスク陽極酸化の方法を提供する。

【解決手段】A1層の陽極酸化は、細長い孔の形成につながり、該孔を通じて犠牲層を除去可能である。本発明の方法に従って、A1層の陽極酸化は、陽極酸化される領域21を規定する第1マスク20、及び陽極酸化される第2領域を規定する第2マスク22であって、前記第2領域は第1領域を包囲するようなマスクの補助がある状態で行う。第1マスク及び第2マスクが規定する領域の陽極酸化は、第1領域周囲の閉環形態における陽極酸化構造の形成につながり、第1領域内では不要な横方向陽極酸化に対するバリアを形成する。

【選択図】図3 a

#### 【特許請求の範囲】

### 【請求項1】

基板(10,11)を準備するステップと、

前記基板上に、陽極酸化可能な層(12)を設けるステップと、

前記陽極酸化可能な層上に、少なくとも、陽極酸化される1つ以上の第1構造(21)を規定する第1マスク(20)、及び陽極酸化される第2構造(23)を規定する追加の第2マスク(22)を設けるステップと、

第1マスク及び第2マスク(20,22)によって規定される領域内で、前記陽極酸化可能な層(12)を陽極酸化し、陽極酸化構造(21,23)を作成するステップと、

第1マスク及び第2マスク(20,22)を除去するステップとを含み、

前記第2構造は、前記1つ以上の第1構造(21)を包囲するようにした方法。

### 【請求項2】

前記陽極酸化可能な層(12)を陽極酸化するステップは、電解液中に基板を挿入し、前記基板に電圧(又は電流)を印加することによって実施される請求項1記載の方法。

### 【請求項3】

前記陽極酸化可能な層を陽極酸化するステップは、第1陽極酸化層を形成するための第 1陽極酸化ステップと、それに続く第1陽極酸化層をエッチング除去した後の第2陽極酸 化ステップとを含む、2ステップ陽極酸化プロセスを使用して実施される請求項1又は2 に記載の方法。

### 【請求項4】

陽極酸化するステップは、硫酸、リン酸、シュウ酸、フッ化水素酸、エタノール、イソプロピルアルコール及びこれらの化学物質の混合物から成る群から選択される電解液中に基板を挿入することにより実施される請求項1~3のいずれか1項に記載の方法。

#### 【請求項5】

前記陽極酸化するステップは、前記陽極酸化構造(21)において伸長した細孔(60)を製造し、前記細孔は、前記陽極酸化可能な層(12)の前面から後面まで延びる請求項1~4のいずれか1項に記載の方法。

#### 【請求項6】

陽極酸化可能な層(12)はA1層であり、陽極酸化するステップは、20 ~40の範囲にある温度の硫酸ベースの電解液中に基板を挿入し、約20Vの電圧を印加することによって実施される請求項5記載の方法。

### 【請求項7】

陽極酸化可能な層(12)は、陽極酸化されて金属酸化物層を形成する金属層であり、 前記陽極酸化浴は、前記酸化物をエッチングするのに好適なエッチング液を含み、

前記陽極酸化ステップは、前記電圧が印加される間の第1時間間隔と、前記第1時間間隔に続く第2時間間隔とを含み、

前記電圧は、前記第1時間間隔の終わりで取り除かれ、

前記第2時間間隔中、基板は前記浴に放置され、それにより、前記細孔(60)の底部でバリア層(61)が除去されるようにした請求項5記載の方法。

### 【請求項8】

前記金属はアルミニウムであり、前記エッチング液はリン酸である請求項7記載の方法

### 【請求項9】

前記基板を準備するステップは、犠牲層(40)をベース基板(10,11,50,5 1)上に堆積することを含み、

陽極酸化可能な層(41)は、前記犠牲層(40)上に設けられ、

前記第1マスク(42)は、陽極酸化構造(43)を規定し、

前記陽極酸化するステップは、前記陽極酸化構造において、伸長した細孔(60)を製造し、

前記細孔は、前記陽極酸化可能な層の前面から後面まで延び、

10

20

30

30

40

少なくとも犠牲層(40)の一部が、キャビティ(44)を形成するために、前記細孔 を通じて除去され、

封止層(45)が、前記陽極酸化構造(43)上に付加されて前記キャビティ(44)を封止する請求項2~8のいずれか1項に記載の方法。

### 【請求項10】

犠牲層(40)は、多結晶SiGe、酸化物ベース又は窒化物ベースの膜、ポリマー、 単結晶Si、多結晶Siから成る群から選択される材料から成る請求項9記載の方法。

### 【請求項11】

前記基板は、NEMS/MEMSデバイス(50)を含み、該デバイスは前記キャビティ(44)内に封入される請求項9又は10に記載の方法。

#### 【請求項12】

少なくとも犠牲材料(40)の一部を除去するステップは、封入されたNEMS/MEMSデバイス(50)を損なわない選択的ウェットエッチング又はドライエッチングを使用して実施される請求項11記載の方法。

### 【請求項13】

犠牲層(40)はシリコン酸化物であり、選択的エッチングは、減圧チャンバ内の他のガス、例えば窒素、エタノール蒸気又は水蒸気と混合した気相のフッ化水素(HF)酸を使用して実施される請求項9~12のいずれか1項に記載の方法。

#### 【請求項14】

犠牲層(40)はポリマーベースの材料であり、選択的エッチングは、酸素イオンが存在する低圧チャンバ内でのドライプラズマエッチングを使用して実施される請求項9~1 2のいずれか1項に記載の方法。

### 【請求項15】

封止層(45)は、

導電性層、例えばA1、Cu、Ni、多結晶Si若しくは多結晶SiGe層、

又は誘電体材料、例えば酸化物ベース若しくは窒化物ベースのシリコン化合物、

又はポリマー、

又は2つ以上の材料の組み合わせ若しくは積層体であり、

前記封止層は、低圧チャンバ内での蒸着技術、化学気相成長法(CVD)又は物理気相成長法(PVD)を使用して堆積される請求項9~14のいずれか1項に記載の方法。

### 【請求項16】

陽極酸化可能な層は、金属層又は半導体層である請求項 1 ~ 1 5 のいずれか 1 項に記載の方法。

### 【請求項17】

陽極酸化可能な層は、Al、Ta、Ti、Cu、Ni、多結晶Si、多結晶SiGeから成る群から選択される請求項16記載の方法。

### 【請求項18】

マスク構造は、感光性層のフォトリソグラフィックパターニングによって形成される請求項1~17のいずれか1項に記載の方法。

### 【発明の詳細な説明】

### 【技術分野】

### [0001]

本発明は、マスク陽極酸化(masked anodization)プロセスを正確に制御するための方法に関する。

### [0002]

本発明はさらに、半導体デバイスを製造すること、特に封入(encapsulation)の方法及びかかるデバイスに関する。より明確には、それは、半導体デバイスの、ゼロレベル又はウエハレベルパッケージングに関するであろう。

### [0003]

よ り 具 体 的 に は 、 本 発 明 は 、 ナ ノ 電 気 機 械 シ ス テ ム 及 び ノ 又 は マ イ ク ロ 電 気 機 械 シ ス テ

10

20

30

40

20

30

40

50

ム ( N E M S 及び / 又は M E M S ) 並びに前記システムを封入 ( 若 しくはパッケージング ) するプロセスに関する。

### 【背景技術】

### [0004]

マスク陽極酸化(ウェット電気化学酸化及び/又はエッチング)によって、導電性薄膜内に誘電体材料又は多孔質材料のパターンを作成することは、既在の薄膜堆積及びエッチング技術に対して種々の利点、例えば、製造プロセス及び該プロセスから生じる比較的平坦な(そして整列した)構造の単純化を有する。通常、マスク陽極酸化プロセスは、陽極酸化される層の上部にマスク構造を付加することによって実施する。該マスク構造は、既在のフォトリソグラフィによって(フォトレジストマスク)、又は陽極酸化プロセスに耐性を有する別の材料の堆積及びパターニングによって(ハードマスク)適用可能である。フォトレジストマスクは、ハードマスクに比べて実装するのがより単純であるが、通常、フォトレジストは、陽極酸化プロセス中に腐食され、陽極酸化パターンの横方向の広がりに対する制御が乏しくなる。

### [0005]

高精度のマスク陽極酸化のための単純な技術を見出すことが、導電性薄膜内で誘電体材料又は多孔質材料の平面パターンを製造するのに必要である。かかるパターンは、例えば相互接続ライン間のキャパシタが減少するという利点をもたらす低誘電率の多孔質誘電体材料によって、互いに絶縁した相互接続金属ライン(パターン)を作成するのに有用である。これにより、これらの相互接続部を通じて伝送可能な信号速度を増加させることができ、異なる相互接続部間での交差連結(cross-coupling)を減らすことができ、集積回路についてのより優れた性能をもたらす。

#### [0006]

高 精 度 の マ ス ク 陽 極 酸 化 を 要 求 す る 別 の 応 用 は 、 ナ ノ 電 気 機 械 シ ス テ ム 及 び / 又 は マ イ ク 口 電 気 機 械 シ ス テ ム ( N E M S / M E M S ) の パ ッ ケ ー ジ ン グ ( 封 入 ) で あ る 。 前 記 N E M S / M E M S システムは、ダイシング(dicing)及び組立て中に容易に損傷する可能性 がある、壊れやすく、及び/又は可動の自立(free-standing)パーツからしばしば構成さ れ て い る の で 、 プ ラ ス チ ッ ク 又 は セ ラ ミ ッ ク パ ッ ケ ー ジ 、 い わ ゆ る 第 1 レ ベ ル パ ッ ケ ー ジ では直接パッケージすることができない。かかる損傷を避けるために、ダイシングの前に 、NEMS/MEMSデバイスをウエハレベルで保護する必要がある。これは、いわゆる ゼロレベル又はウエハレベルパッケージング技術を用いて可能である。それゆえ、多くの NEMS/MEMSシステムは、真空下、又は制御された雰囲気及び圧力の下で封入し、 優れた性能又は許容できる動作期間のいずれかを保証することを要求する。該封入は、N EMS/MEMSデバイス上に封止材料を直接堆積することなく実施する必要がある。か かる堆積は、デバイスに損傷を与える可能性があるからである。それゆえに、真空及び/ 又 は 制 御 さ れ た 雰 囲 気 を 実 現 し 、 続 い て 封 止 層 を 堆 積 で き る ホ ー ル ( 細 孔 (pore) ) を 有 す る層から成る封入物を最初に堆積する必要がある。単純かつ安価なプロセスにより多孔質 薄膜を有するNEMS/MEMSデバイスを封入するアイデアに至った。薄膜の細孔を通 じてデバイスを除去することができるので、フォトリソグラフィを使用して薄膜にアクセ スホールを成形する必要を無くすことができ、デバイスの製造が容易になる。

### [ 0 0 0 7 ]

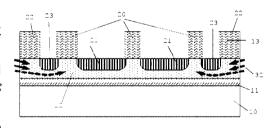

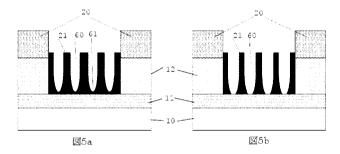

基板1(例えばSi)の概略図を表す図1に示すようなNEMS/MEMSデバイスの前記薄膜真空パッケージングにおいて、近年、多孔質皮膜(membrane)として使用するために、多孔質のアルミナ(A1〇 $_{\times}$ )皮膜が研究されている。基板1は、表面上でMEMSデバイス2を支持し、多孔質皮膜3によって封入される。該皮膜3は、封止層4に覆われる。多孔質皮膜3は、pHの低い電解液中でのアルミニウム薄膜(誘電体薄膜の上部に堆積した)の陽極酸化、及びマスクとしてパターニングしたフォトレジスト層を使用することによって得られる。陽極酸化プロセスは、フォトレジストマスクを使用して、マスクしたA1層上で実施してもよい(論文:ヘリンリコら J. Electrochem. Soc. Vol. 154, No. 9(2007)。細孔5(スケールどおり図示していない)は、皮膜の厚さ方向に貫通する

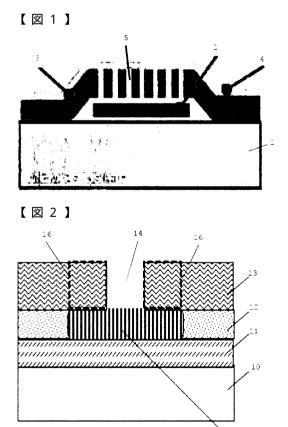

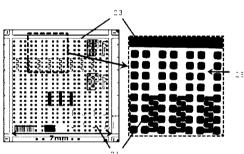

細長い開口部であり、該細孔を通じてMEMSデバイス2の放出(release)が生じ、それが皮膜層3の堆積の前にMEMSデバイス上で堆積した犠牲層を除去する。図2に示すように、フォトレジストを使用するこのマスク陽極酸化プロセスは、陽極酸化プロセスを所望の領域に適切には制限しないという欠点を有する。本図は基板1を示しており、基板表面上に薄膜11を有し、該薄膜11上に皮膜層12を有する。フォトレジストマスク13は、陽極酸化される皮膜領域を規定する部分14を除いて皮膜を覆う。さらに詳細に説明するように、通常、陽極酸化は、陽極酸化浴に基板を浸すことによって行う。基板を陽極酸化浴に必要以上に長い時間放置した場合、陽極酸化が続いて必要以上に広い陽極酸化領域15(境界16参照)が形成される。即ち、陽極酸化領域の不要な継続的成長が発生する。

[0008]

特に、陽極酸化される層を有するフルウエハ又は大面積基板に陽極酸化電圧を印加し、基板(ウエハ)を陽極酸化浴に放置した場合、フォトレジストマスクが規定する制限を越えて、前記陽極酸化領域の不要な継続的成長が発生する。フルウエハスケールでマスク陽極酸化プロセスを実施する場合の課題は、基板(ウエハ)のエッジ周辺に存在するマスクが規定する領域が既に完全に陽極酸化され、過陽極酸化(over-anodized)に至ることになる状態で、基板(ウエハ)表面の中心領域(中間)に存在するマスクが規定する領域は、未だ完全には陽極酸化されていないことである。不要な継続的成長という課題は、

- (1)酸性度の高い電解液による腐食、

- (2) A 1 O 、薄膜の拡張、

- ( 3 ) 陽 極 酸 化 プ ロ セ ス 中 に 発 生 す る ガ ス の 構 成

に起因するフォトレジストマスクのエッジ剥離(peeling)(「アンダーカット」(undercut)を生じる)によって生じる。

[0009]

従って、現在、フォトレジストマスクを使用して、正確に規定した陽極酸化パターンを 導電性層内に設けるために、信頼性の高い制御可能な方法を提供するための最先端の技術 、及び、例えばNEMS/MEMS用に薄膜真空パッケージングを提供するためのかかる 陽極酸化パターンの適用における課題が存在する。

【発明の概要】

【発明が解決しようとする課題】

[0010]

本発明の目的は、マスク陽極酸化によって、陽極酸化可能な(anodizable)層内で陽極酸化材料の正確なパターンを作成するための進んだ方法を提供することである。より明確には、マスク陽極酸化を使用して、導電性薄膜内で誘電体材料又は多孔質材料の正確なパターンを作成することである。具体的には、(フル)ウエハスケールで半導体デバイスを製造して、半導体デバイスの大きいスケールの製造に適用可能な陽極酸化プロセスを作成する際に用いるための、費用効率の高い、進んだマスク陽極酸化プロセスを提供することが目的である。

[0011]

本発明の実施形態の更なる目的は、陽極酸化可能な層、例えば導電性(金属)層を局所的に変形して陽極酸化(anodized)層、例えば誘電体層又は多孔質層にする、ウェット陽極酸化プロセスを実施するための、信頼性が高く制御可能な方法を提供することである。本発明の目標は、(フル)ウエハスケールで、均一に前記陽極酸化を実施することである。

[ 0 0 1 2 ]

更なる目的は、ナノ電気機械システム及びマイクロ電気機械システム(NEMS/MEMS)のためのマイクロ電気プロセス技術を提供して、前記NEMS/MEMSデバイスのための制御可能で均一な(フル)ウエハスケール封入又はパッケージングプロセスを達成することである。

【課題を解決するための手段】

[ 0 0 1 3 ]

10

20

30

40

上記目的は、本発明に係る方法及びデバイスによって達成される。本発明は、追加の包 囲マスク構造を有する一群の(複数の)マスク構造を包囲することによって、均一で制御 可能な陽極酸化を達成するという課題を解決する。換言すると、陽極酸化中のマスク層の 層間剥離又はアンダーカットにつながる過陽極酸化に至らないで、陽極酸化プロセスに選 択的に曝される表面上の小領域を規定する、高精度の追加の包囲フォトレジスト又は他の マスク構造を使用することによって該課題を解決する。前記追加のマスク構造の存在によ り、陽極酸化境界が前記境界内の陽極酸化領域と同時に陽極酸化(酸化)されるため、自 己制限が生じる。その結果、前記境界はさらに、陽極酸化電流がマスク構造の陽極酸化領 域に達するのを妨げ、不要な更なる陽極酸化を避ける。陽極酸化プロセスのために必要と される電流は基板のエッジ(周辺部)で供給されるため、追加の包囲マスク構造(陽極酸 化 材 料 の 境 界 線 を 規 定 す る ) を 有 す る 陽 極 酸 化 マ ス ク 上 の 全 て の 構 造 群 を 包 囲 す る こ と に より、陽極酸化プロセスの自己制限が生じる。これは、陽極酸化境界が同時に陽極酸化( 酸 化 ) さ れ た 状 態 に な り 、 更 な る 陽 極 酸 化 電 流 が 陽 極 酸 化 領 域 に 達 す る の を 妨 げ る か ら で ある。陽極酸化プロセスのためのマスクデザイン中に、さまざまな寸法の追加の包囲マス ク構造(境界線又は保護環を規定する)を付加してもよい(即ち、境界線は、小構造群又 は大構造群を包囲可能であり、又は基板(ウエハ)全体を包囲することができる)。追加 の包囲マスク構造及び包囲領域の幅を選択して(又は適合させて)封入された構造の完全 な 縦 方 向 陽 極 酸 化 を 保 障 す る こ と が で き 、 同 時 に 陽 極 酸 化 プ ロ セ ス の 横 方 向 の 大 き い 拡 張 からこれらの構造を保護することができる。

[0014]

本発明に係るマスク陽極酸化プロセスをNEMS/MEMSデバイスのためのパッケージングプロセスに付加することにより、追加の包囲マスク構造が、一群の個々のNEMS / MEMSデバイスを包囲し、陽極酸化プロセスの自己制限を生じることになる。これは、陽極酸化境界が同時に陽極酸化(酸化)された状態になり、更なる陽極酸化電流が陽極酸化領域に達するのを妨げ、更なる不要な陽極酸化を避けるからである。

[0015]

本発明に係る実施形態の利点は、包囲マスク構造を設けることは、別の加工ステップを必要としないことである。これは、前記追加のマスク構造を、第 1 マスク構造を設けるのと同時に設けるからである。

[0016]

本発明は、添付の請求項で開示する方法に関する。本発明の特定かつ好ましい態様は、添付する独立請求項及び従属請求項において詳説する。従属請求項の特徴は、独立請求項の特徴及び他の従属請求項の特徴と、適切及び単に請求項に明記されただけでないものとして組み合わせてもよい。

[0017]

このように、本発明は、マスク陽極酸化のための方法に関し、前記方法は、 基板を準備するステップと、

前記基板上に、陽極酸化可能な層を設けるステップと、

前記陽極酸化可能な層上に、少なくとも、陽極酸化される1つ以上の第1構造を規定する第1マスク、及び陽極酸化される第2構造を規定する追加の第2マスクを設けるステップと、

第1マスク及び第2マスクによって規定される領域内で、前記陽極酸化可能な層を陽極酸化し、陽極酸化構造を作成するステップと、

第1マスク及び第2マスクを除去するステップとを含み、

前記第2構造は、前記1つ以上の第1構造を包囲する。

ここで、「第1マスク及び第2マスクによって規定される領域内で、前記陽極酸化可能な層を陽極酸化する」という表現は、層が前記領域内で厚さ全体に渡って陽極酸化されるまで、陽極酸化が続くということを意味する。また、「包囲する(surrounding)」は、第2構造が第1構造の周囲に閉環構造を形成することを意味する。

[ 0 0 1 8 ]

10

20

30

40

好ましい実施形態に従って、前記陽極酸化可能な層を陽極酸化するステップは、基板を 電解液中に挿入し、前記基板に電圧(又は電流)を印加することによって実施する。

### [0019]

前記陽極酸化可能な層を陽極酸化するステップはまた、第1陽極酸化層を形成する第1 陽極酸化ステップと、それに続く第1陽極酸化層をエッチング除去した後の第2陽極酸化 ステップを含む、2ステップ陽極酸化プロセスを使用して実施してもよい。

#### [0020]

好ましい実施形態に従って、陽極酸化するステップは、硫酸、リン酸、シュウ酸、フッ化水素酸、エタノール、イソプロピルアルコール及びこれらの化学物質の混合物から成る群から選択した電解液中に基板を挿入することによって実施してもよい。

### [0021]

好ましい実施形態に従って、前記陽極酸化するステップは、前記陽極酸化構造に伸長した(elongate)細孔を作成する。前記細孔は、前記陽極酸化可能な層の前面から後面まで延びる。

### [0022]

実施形態に従って、陽極酸化可能な層はA1層であり、陽極酸化するステップは、基板を、20~40 の範囲にある温度の硫酸ベースの電解液中に基板を挿入することによって実施する。

### [0023]

実施形態に従って、陽極酸化可能な層は、陽極酸化されて金属酸化物層を形成する金属層であり、前記陽極酸化浴は前記酸化物をエッチングするのに好適なエッチング液を含み、前記陽極酸化ステップは、前記電圧が印加される間の第1時間間隔と、前記第1時間間隔に続く第2時間間隔とを含み、前記電圧は、前記第1時間間隔の終わりで取り除かれ、前記第2時間間隔中、基板は前記陽極酸化浴に放置され、それにより、前記細孔の底部でバリア層が除去される。この実施形態において、前記金属はアルミニウムでもよく、前記エッチング剤はリン酸でもよい。

### [0024]

実施形態に従って、前記基板を準備するステップは、犠牲層をベース基板上に堆積することを含み、

陽極酸化可能な層は、前記犠牲層上に設けられ、

前記第1マスクは、陽極酸化構造を規定し、

前記陽極酸化ステップは、前記陽極酸化構造において、伸長した細孔を製造し、前記細孔は、前記陽極酸化可能な層の前面から後面まで延び、

少なくとも犠牲層の一部が、キャビティ(cavity)を形成するために、前記細孔を通じて除去され、

封止層が、前記陽極酸化構造上に付加されて前記キャビティを封止する。

### [0025]

この実施形態において、犠牲層は、多結晶SiGe、酸化物ベース又は窒化物ベースの膜、ポリマー、単結晶Si、多結晶Siから成る群から選択された材料で構成することができる。この実施形態において、前記基板は、NEMS/MEMSデバイスを含み、該デバイスは前記キャビティ内に封入される。

#### [0026]

この場合、少なくとも犠牲材料の一部を除去するステップは、封入されたNEMS/MEMSデバイスを損なわない選択的ウェットエッチング又はドライエッチングを使用して実施される。

### [0027]

この実施形態において、犠牲層は、シリコン酸化物でもよく、選択的エッチングは、減圧チャンバ内の他のガス、例えば窒素、エタノール蒸気又は水蒸気と混合した気相のフッ化水素(HF)酸を使用して実施してもよい。

### [0028]

50

40

10

20

犠 牲 層 は ポ リ マ ー ベ ー ス の 材 料 で も よ く 、 選 択 的 エ ッ チ ン グ は 、 酸 素 イ オ ン が 存 在 す る 低圧チャンバ内でのドライプラズマエッチングを使用して実施してもよい。

### [0029]

この実施形態において、封止層は、

- ・導電性層、例えばA1、Cu、Ni、多結晶Si若しくは多結晶SiGe層、

- ・又は誘電体材料、例えば酸化物ベース若しくは窒化物ベースのシリコン化合物、

- ・又はポリマー、

- ・又は2つ以上の材料の組み合わせ若しくは積層体(stack)でもよく、

前記封止層は、低圧チャンバ内での蒸着技術、化学気相成長法(CVD)又は物理気相 成長法(PVD)を使用して堆積してもよい。

[0030]

本発明の方法において、陽極酸化可能な層は、金属層又は半導体層でもよい。前記陽極 酸化可能な層は、Al、Ta、Ti、Cu、Ni、多結晶Si、多結晶SiGeから成る 群から選択してもよい。

[0031]

本発明の方法において、マスク構造は、感光性層のフォトリソグラフパターニングによ って形成してもよい。

【図面の簡単な説明】

[ 0 0 3 2 ]

【図1】先行技術において既知の、多孔質皮膜を使用した薄膜MEMSパッケージングの 概念図を示す。

【 図 2 】フォトレジストマスクを使用したA1陽極酸化プロセスの横方向の大きな拡張( 本発明が解決する課題)を示す。

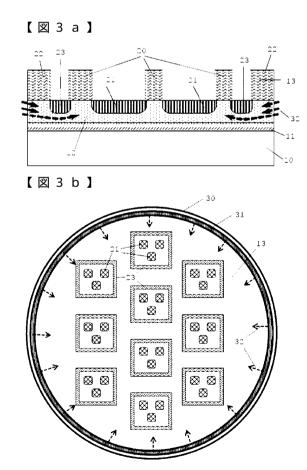

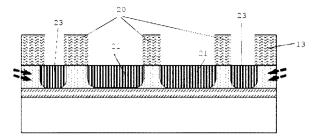

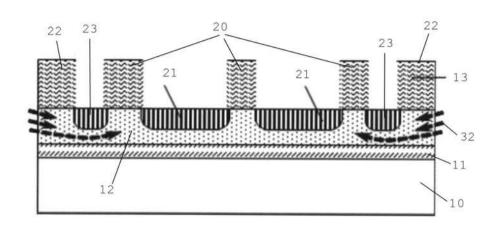

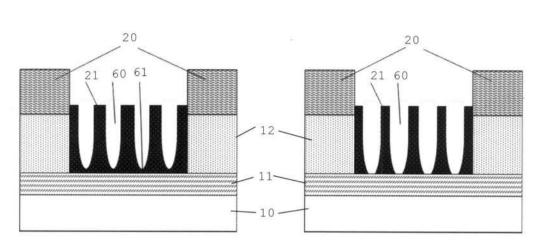

【図3a】本発明の陽極酸化プロセス中の中間段階を示しており、縦方向陽極酸化が終了 する前は、陽極酸化電流は、未だ陽極酸化領域に達する可能性がある。

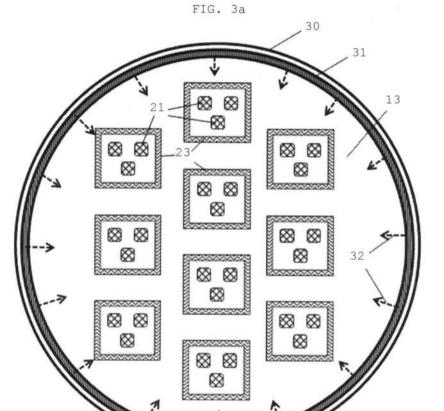

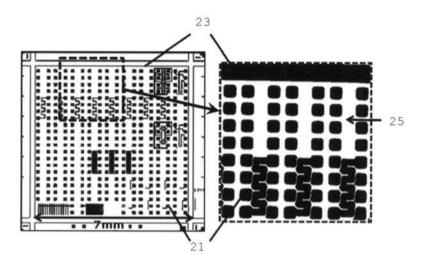

【図3b】いくつかのマスクを備え、ウエハの周囲に沿って配置された環状電極を設けた ウエハの上面である。

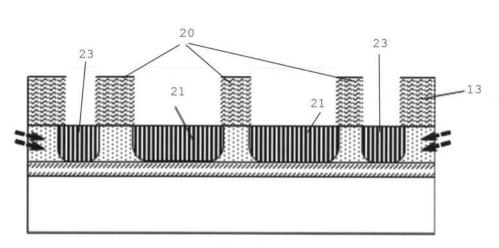

【図3c】本発明の陽極酸化プロセスの最終段階を示しており(縦方向陽極酸化は終了し ている)、境界線は完全に陽極酸化(酸化)されており、該陽極酸化領域周辺に、陽極酸 化に必要とされる電荷の更なる供給をブロックする誘電体の絶縁環を形成する

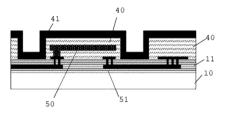

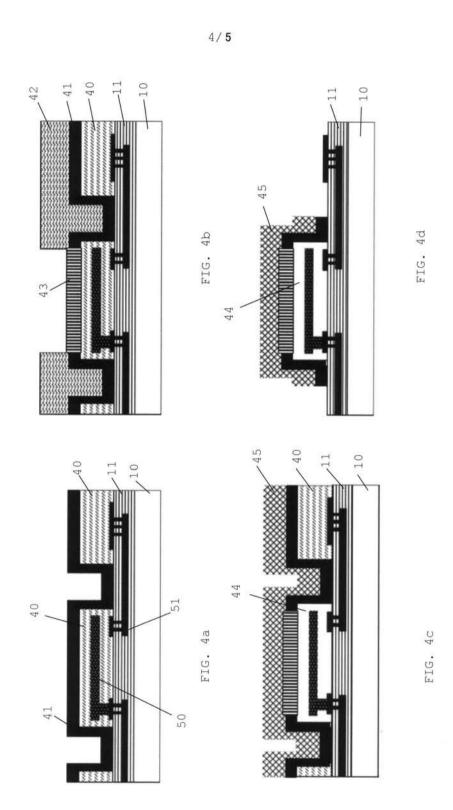

【 図 4 a 】 図 4 a ~ 図 4 d は、 本発明の実施形態に係るNEMS / MEMSデバイスの薄 膜 パ ッ ケ ー ジ ン グ に つ い て 、 マ ス ク 陽 極 酸 化 プ ロ セ ス を 使 用 す る た め の 好 適 な プ ロ セ ス フ ローにおけるさまざまなステップを示す。図4aは、NEMS/MEMS構造及び相互接 続部を覆う犠牲層の上部に金属層を堆積するステップを示す。

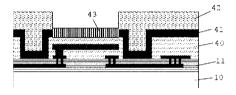

【図4b】マスク陽極酸化層及び薄いバリア酸化層を除去するステップを示す。

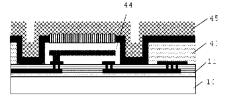

【図4c】犠牲層を除去し、封止層を堆積するステップを示す。

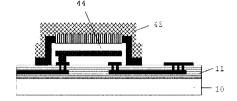

【 図 4 d 】 電 気 的 ア ク セ ス の た め の 金 属 パ ッ ド を 覆 う 層 を 除 去 す る ス テ ッ プ と 、 最 終 の N EMS/MEMSデバイスの封入を示す。

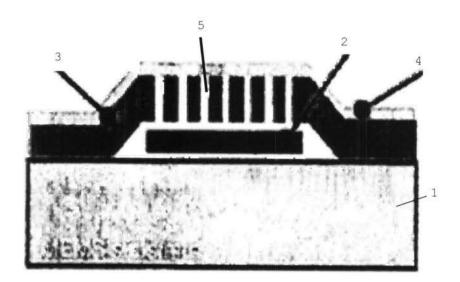

【図5】アルミニウム層の陽極酸化によって形成される細孔、及び該細孔の底部で形成さ れる酸化バリア層の形状を示す。

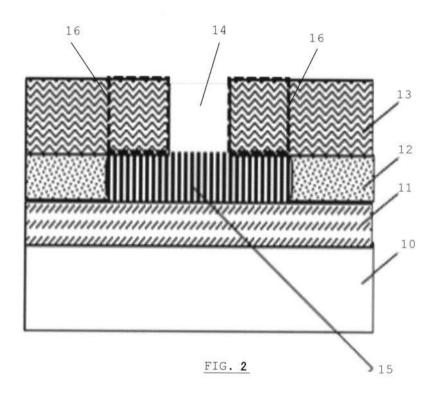

【 図 6 】 本 発 明 に 係 る 環 状 構 造 を 規 定 す る マ ス ク デ ザ イ ン の 例 を 示 す 。

[0033]

図面は概略的なものに過ぎず、限定的でない。図面において、いくつかのエレメントの 大きさは、説明目的のため、誇張し、及びスケールどおり描いていないことがある。請求 項中のどの参照符号も、範囲を限定するものと解釈すべきでない。異なる図面において、 同じ参照符号は同一又は類似のエレメントを参照する。

【発明を実施するための形態】

[ 0 0 3 4 ]

本 発 明 の 態 様 に 従 っ て 、 均 一 で 制 御 可 能 な 、 マ ス ク 陽 極 酸 化 を 提 供 す る た め の 方 法 で あ って、前記方法は少なくとも、

10

20

30

40

基板(10,11)を準備する(即ち、供給する、又は製造する)ステップと、

前記基板上に、陽極酸化可能な層(12)を設けるステップと、

前記陽極酸化可能な層(12)上に、陽極酸化される1つ以上の第1構造(21)の寸法を規定する少なくとも1つの第1マスク(20)、及び陽極酸化される第2構造(23)を規定する第2マスク(22)を設けるステップと、

第1マスク(20)及び第2マスク(22)によって規定される領域内で、前記陽極酸化可能な層を陽極酸化し、陽極酸化構造(21,23)を作成するステップと、

マスク構造(20,22)を除去するステップとを含み、

前記第2構造は、前記第1構造(21)を包囲する(図3を参照)。

### [0035]

図3aはまた、基板10を示す。本実施形態において(本発明の技術的範囲を限定するものではないが)、誘電体層11を基板上に堆積する。該誘電体層11は、例えば犠牲層でもよい。層12は皮膜層であり、層13はマスク層であり、好ましくはパターニングしたフォトレジスト層である。本発明に従って、マスク層は、少なくとも第1マスク20を有し、陽極酸化される領域21を規定する。マスク層はさらに、陽極酸化される前記1つ以上の第1領域21を包囲する領域23を規定する第2マスク22を有し、前記領域21の周囲に、閉環構造(必ずしも円形とは限らない)を形成する。図3bは、陽極酸化される領域21を規定する複数のマスク20を有するマスク層13を表面上で保持する半導体ウエハ30の上面図を示す。各マスク20の周囲で(従って、領域21の各群の周囲で)、マスク層は、マスク20を包囲する、陽極酸化される環構造23を規定する。従って、「第2マスク構造」22は、マスク層13全体からマスク構造20を除いたものに一致する。

### [0036]

ウエハのエッジ30に沿って電極31を配置する。該電極31は、陽極酸化される層12(好ましくは金属層、以下を参照)と電気的に接触する。電極31は、陽極酸化中、アノードの役割を果たすことになる。この集合体を、電解液で満ちた陽極酸化浴に浸す。第2電極(カソード)は、陽極酸化浴の一部(好ましくは、ウエハの前面、即ちマスク20,22を支持する面に対向し、陽極酸化浴に浸した、金属板)である。陽極酸化が開始すると、電荷は、図3a及び図3bに矢印32で示した方向に流れる。即ち、ウエハの外エッジ30及び各マスク20の外エッジから開始して、中央へ向かって流れる。

### [ 0 0 3 7 ]

図3 a は、本発明の陽極酸化プロセス中の中間段階を示しており、陽極酸化電流(電荷の流れ)は、縦方向の陽極酸化が終了する前に、さらに陽極酸化領域2 1 に達する可能性がある。図3 c は、本発明の陽極酸化プロセスの最終段階(縦方向の酸化が終了した時点)を示しており、環構造2 3 は、完全に陽極酸化(酸化)されて境界線として作用し、そして陽極酸化領域2 1 の周囲に誘電体絶縁環を形成する。該環構造2 3 は、陽極酸化に必要とされる電荷の更なる供給をブロックする。

### [0038]

実施形態に従って、陽極酸化層12として使用するための材料は、金属層、又はA1、Ta、Ti、Cu、Ni、多結晶Si、多結晶SiGeなどから選択される半導体層でもよい。例えば、低温で実施するスパッタリングプロセスを使用することによって堆積した、厚さ約0.5~10μmのアルミニウム層を使用してもよい。陽極酸化に先立って、脱イオン水の超音波浴内に置くことで、A1層を洗浄してもよい。

### [0039]

実施形態に従って、第1マスク構造20及び第2マスク構造22を、最先端の感光層(レジスト)のフォトリソグラフィックパターニングによって形成してもよい。フォトレジスト(感光層)を使用する利点は、別のマスク材料の堆積及びパターニング(化学エッチング又は物理エッチングによって)を含む他の技術と比較した場合の、マスク構造を形成する容易さである。

### [0040]

10

20

30

実施形態に従って、前記陽極酸化可能な層12を陽極酸化するステップは、多孔質(金属)層の形成につながるだろう。前記多孔質層における細孔(ホール)は、幅の10倍以上の長さを有してもよい。幅は、5~200nmの範囲にあって例えば20nmであり、又は20nm~200nmの範囲にあり、又は5~20nmの範囲にある。

### [0041]

実施形態に従って、前記陽極酸化可能な(金属)層12を陽極酸化するステップは、1ステップの陽極酸化プロセスによって実施してもよい。前述のように、前記1ステップ陽極酸化プロセスは、基板を電解液に挿入し、前記基板に電圧(又は電流)を印加することによって実施してもよい。前記電解液は、硫酸、リン酸、シュウ酸、フッ化水素酸、エタノール、イソプロピルアルコール若しくはこれらの化学物質の混合物又は他の化学物質でもよい。5~200Vの範囲の電圧を印加することによって、ランダムに、又は六角形配置で分布した、陽極酸化可能な(金属)層の表面上に細孔を形成する。細孔のよりよい六角形配置を達成するために、多孔質層について最大の体積膨張因子に達するように、最適化したプロセス条件(陽極酸化電圧、電解液及び温度)を選択するべきである。

### [0042]

実施形態に従って、前記陽極酸化可能な(金属)層12を陽極酸化するステップは、2ステップの陽極酸化プロセスによって実施してもよい。前記2ステップ陽極酸化プロセスは、最初、陽極酸化可能な(金属)層12の表面をパターン化する、短い陽極酸化ステップを適用することによって実施してもよい。次に、このパターン化した表面は、第2陽極酸化ステップのための自己集積化した標識(mark)として作用する[論文:メイら、"Formation mechanism of alumina nanotubes and nanowires from highly ordered porous anodic alumina template," Journal of Applied Physics, Vol. 97, 034305 (2005)]。第1陽極酸化層をエッチング除去した後の、広範囲の第2陽極酸化ステップは、セル(cell)配置の規則性を改善するだけでなく、欠陥及び転移の数を減少させる。第3陽極酸化ステップは、細孔の配列及び好適に配列した領域の大きさをあまり改善しない。

### [0043]

実施形態に従って、陽極酸化可能な(金属)層の陽極酸化を達成するために印加する電圧は、基板上の陽極酸化可能な(金属)層と、電解液又は該電解液中の参照電極との間に印加する。陽極酸化するために印加する電圧は、数ボルト~数百ボルトである。例えば、20~40の範囲内の温度の硫酸ベースの電解液中で陽極酸化を実施する場合、20Vの電圧が使用可能である。

### [0044]

実施形態に従って、追加構造23の陽極酸化(縦方向の陽極酸化)が終了する際に、前記追加構造は、陽極酸化に必要とされる電荷の更なる供給をプロックし、追加構造23に包囲された陽極酸化構造21の不要な拡張を避ける誘電体絶縁環として作用する保護構造23を形成する。

### [0045]

実施形態に従って、陽極酸化可能な(金属)層はアルミニウム層であり、陽極酸化プロセス条件、例えば陽極酸化電圧、陽極酸化温度及び酸濃度などを、所定の電極につりタ堆積の化してもよい。多孔質のアルミニウム酸化物(A1〇χ)皮膜の合成は、スパッタ堆積又は蒸着したA1膜から開始可能である。選択する主な陽極酸化パラメータは、電解液の種類は、細孔の直径、細孔間の距離、導電圧及びに陽極酸化ステップの順序に影響を与えるからである。陽極酸化は、導電性多に減少である。陽極酸化ステップの順序に影響を与えるからである。陽極酸化は、導電性多に調整を挿入する、ガラスベース以はテフロン(登録商標)ベースのチャンバ内で起こ又は配きである。陽極酸化電解液との接触から基板のエッジ及び後面を保護するテフロンベース又はでフロン(で起まする基板30を陽極酸化プロセスは、参照電極と基板上の陽極酸化が中ンバ内に挿入してもよい。陽極酸化プロセスは、参照電極と基板上の陽極酸化がの陽極酸化が一旦終了し、絶縁環23(境界線)が追加のマスク構造22内に形成されると、陽極酸化プロセスは、電荷が絶縁環を通って移動できないことに起因して

10

20

30

40

自動的にストップする。

### [0046]

本発明の更なる態様に従って、半導体デバイス内のキャビティを(密閉)封止し、先の 実 施 形 態 で 説 明 し た 、 均 一 で 制 御 可 能 な 、 マ ス ク 陽 極 酸 化 プ ロ セ ス を 使 用 す る た め の 方 法 を提供する。前記方法は、

基板上に犠牲層(40)を設けるステップと、

該犠牲層(40)の上部に、0.5ミクロンより大きい厚さを有する金属皮膜層(41 )を設けるステップと、

前記金属層(41)上に、陽極酸化される第1構造43の寸法を規定する第1マスク( (42)を設けるステップと、

前記金属層(41)を陽極酸化して、前記多孔質の金属酸化物層(43)の前面から前 記 多 孔 質 の 金 属 酸 化 物 層 ( 4 3 ) の 後 面 に 向 か っ て 延 び る 細 孔 ( ホ ー ル ) を 有 す る 多 孔 質 の金属酸化物層(43)を形成するステップと、

多孔質の金属酸化物層(43)を通じて、マスク構造及び少なくとも犠牲層(40)の 一部を除去し、マイクロキャビティ(44)を形成するステップと、

封止層45を用いて前記多孔質層の細孔を封止(閉鎖)して、(密閉)封止したキャビ ティ(44)を形成するステップとを含み、

前記マイクロキャビティは、前記犠牲層(40)に位置し、

前記基板は、ベース基板10と、誘電体層11と、MEMS又はNEMSデバイス50 とを備え、

前記犠牲層(40)には、前記デバイス50との電気接続構造51が設けられており、 前記寸法は、キャビティ及び前記第1構造(43)を包囲する、陽極酸化構造(不図示 )を規定する追加の第2マスクの寸法に対応する。

#### [0047]

図 4 a~図 4 d は、NEMS/MEMSデバイスの薄膜パッケージングに対してマスク 陽極酸化プロセスを使用するための、好適なプロセスフローにおけるさまざまなステップ を示している。

#### [0048]

実施形態に従って、基板(10,11,50,51)及び犠牲層(40)は、半導体加 工、より明確にはNEMS/MEMS加工と一緒に使用し、該加工に適合するいずれの基 板及び層でもよい。使用する基板の例は、例えば単結晶Si又は多結晶Si、単結晶Ge 又は多結晶Ge、ガラス、石英、ポリマーなどでもよい。

#### [0049]

図のように、壊れやすいデバイス50をキャビティ内に配置してもよい。前記壊れやす いデバイスは、真空又は制御された雰囲気及び圧力封入を必要とするいずれのNEMS/ MEMSデバイスでもよい。

### [0050]

実施形態に従って、犠牲層40は、多結晶SiGe、酸化物ベース又は窒化物ベースの 膜、ポリマー、単結晶Si又は多結晶Siなどから選択される材料でできていてもよい。 前記犠牲材料は、封入されたNEMS/MEMSデバイスを大きくは損なわないウェット エッチング又はドライエッチング技術(選択的エッチング)を使用して除去可能な材料で も よ い 。 例 え ば 、 シ リ コ ン 酸 化 物 犠 牲 層 4 0 は 、 減 圧 チ ャ ン バ 内 で 、 他 の ガ ス ( 例 え ば 窒 素 及 び エ タ ノ ー ル 蒸 気 又 は 水 蒸 気 ) と 混 合 し た 気 相 フ ッ 化 水 素 ( H F ) 酸 に よ っ て 除 去 可 能することができる。かかる希釈した気相HFの混合物は、NEMS/MEMSデバイス と反応しないで犠牲シリコン酸化物層を除去することができ、又はキャビティを包囲する 多孔質層を除去することができる。

### [0051]

実施形態に従って、犠牲材料40は、前記皮膜層41の下に存在するキャビティ44を 満たしている。さらに、キャビティは、NEMS/MEMSデバイス50を含むことがで き、その機能及び構造は、前記犠牲材料エッチング液に不活性である。それは、壊れやす 10

20

30

40

い物体を備えることができ、デバイスの適正な動作及び寿命を保証するための閉鎖プロセス中には、該物体上にいずれの材料も実質的に堆積することができない。特定の実施形態において、キャビティ44は、前記細孔、及び選択的に通気孔(不図示)を除いて閉鎖する。通気孔は、キャビティと外側とをつなぐ追加のホールである。

### [0052]

実施形態に従って、金属層41として使用するための材料は、A1、Ta、Ti、Cu、Ni、多結晶Si、多結晶SiGeなどから選択した金属層又は半導体層でもよい。例えば、厚さ約0.5~10μmのアルミニウム層を、低温で実施するスパッタリングプロセスによって堆積してもよい。陽極酸化の前に、脱イオン水の超音波浴内に置いて洗浄してもよい。

[0053]

実施形態に従って、前記金属層を陽極酸化して多孔質金属酸化物層を形成するステップにより、多孔質皮膜とも呼ばれる細孔(ホール)を有する層が得られるようにする。前記多孔質皮膜は、前記皮膜内に前主面及び後主面並びに細孔(ホール)を有し(ホールは、一組のサブ表面(sub-surface)相互接続細孔が可能である)、該細孔は、前主面から後主面まで延びる。

[0054]

実施形態に従って、前記多孔質層の細孔(ホール)は、幅の10倍大きい長さを有して もよく、幅は、5~200nmの範囲、例えば20nm、20nm~200nmの範囲、 又は5~200nmの範囲を有してもよい。

[0055]

本発明に従って、追加構造の陽極酸化(縦方向の陽極酸化)が終了する場合、陽極酸化に必要となる電荷の更なる供給をブロックし、追加構造が包囲する陽極酸化構造の不要な拡張を避けるNEMS/MEMSデバイスを包囲する誘電体絶縁環として作用するように保護構造を形成する。

[0056]

実施形態に従って、薄い酸化物バリア層は、陽極酸化の後、多孔質酸化物層43の細孔(ホール)の底部に存在してもよく、縦方向の陽極酸化の終了後(陽極酸化電流のらに存在してもよく、縦方向の陽極酸化の終了後(陽極酸化電流のにより長い時間ウエハを放置することによって除るとしてもよい。これに追して多孔質を限れ物層のスローであるリン酸化物のエッチングをを選択して多孔質を化物層のスローであるリン酸とができるので(例えば、アルミニウム酸化物のエッチングをととができるので(例えば、アルミニウム酸化物のエッナン酸によって)、多孔質層のほんの一部だけをする利点は、部をととがのきる。バリア酸化物層の除去を陽極酸化電解液中で実施する利点は、部へのエッテンがのの進入が容易になることである。代替として、酸化物バリア層は、陽極酸化ステップのの進入が容易になることである。代替として、酸化物バリア層はよいでのの進入が容易になることである。代替として、酸化物バリア層はよい。ここで酸化ウェット又はドライケミカルエッチングステップによって除去はい。ここで酸化物に達するのを妨げる可能性があるので、ウェットエッグ技術の使用を試みる場合は困難が予想される。

[ 0 0 5 7 ]

図5 a は、上述のバリア層を示す。本図は、図3 c に示す陽極酸化領域内の細孔60の伸長した形状を示す。バリア層は、細孔60の底部にある少量の酸化物61によって形成される。陽極酸化電流が停止した後、陽極酸化浴内に基板を所定の時間放置することにより、該浴内の追加のエッチング液が確実にバリア層を除去する(図5 b 参照)。

[0058]

実施形態に従って、多孔質 A 1 層(皮膜)の下の犠牲材料 4 0 を除去するステップは、前記多孔質層 4 3 の細孔 6 0 (ホール)を通じて前記犠牲材料を少なくとも部分的に除去(エッチング除去)するまでは、エッチング液を使用して実施してもよい。犠牲材料は、酸化物ベースの化合物(例えば S i O 2 )でもよく、この材料の除去は、犠牲材料のエッ

10

20

30

40

チング液(例えばフッ化水素酸)の蒸気、及び他のガス、例えばエタノール蒸気、窒素又は水蒸気を含むガスの混合物を含んだ減圧チャンバ内で実施してもよい。代替として、犠牲層40は、ポリマーベースの材料、例えばフォトレジストでもよく、酸素イオンの存在する減圧チャンバ内でのドライプラズマエッチングにより、前記多孔質層43の細孔を通じて除去することができる。犠牲材料の除去により、NEMS/MEMS構造を受入れる(host)のに使用可能なキャビティ44が得られる。

#### [0059]

実施形態に従って、低圧チャンバ内での蒸着技術又は化学気相成長法(CVD)若しくは物理気相成長法(PVD)を用いて封止層 4 5 を堆積してもよい。前記封止層 4 5 は、導電性層、例えば A 1、Cu、Ni、多結晶 Si又は多結晶 SiGeでもよい。代替として、封止層 4 5 は、誘電体材料、例えば酸化物若しくは窒化物ベースのシリコン化合物又はポリマーでもよい。代替として、封止層は2つ以上の材料の組み合わせ又は積層体でもよい。多孔質皮膜 4 3 の細孔 6 0 の非常に大きいアスペクト比が、NEMS/MEMS構造50上での封止層 4 5 の堆積を妨げ、その結果NEMS/MEMS構造の損傷又は改変を妨げる。封止層の堆積により、NEMS/MEMSデバイスを受入れ可能な封止キャビティ 4 4 が得られる。

### [0060]

実施形態に従って、封止層を堆積するのに使用するチャンバ内に存在するガス及び圧力を制御することによって、制御された雰囲気及び圧力下でキャビティ44を封止してもよい。封止層は細孔(ホール)60を順に閉鎖し、これが制御された雰囲気及び圧力を有する封止キャビティ44の形成につながる。

### [0061]

### (定義)

本発明の実施形態において、用語「制御された雰囲気」は、周囲ガスの制御された組成を意味する。「水平(horizontal)」という概念は、重量場、例えば地球の重量場の方向に実質的に垂直な方向と定義する。

### [0062]

本開示において、「原則として、どの材料も開口部を通過しない」という概念は、「開口部に入る、及び/又は開口部を通過する材料の量はゼロである、又は限られている」と理解するべきである。壊れやすいデバイスを備えたキャビティの封止との関連で、好適なデバイスの動作は、通過する限られた量の材料に影響を受けないようにする必要がある。

### [0063]

本開示において、用語「マイクロ電気機械システム」及び「ナノ電気機械システム」(NEMS/MEMS)は、電気的機能及び非電気的(例えば機械的)機能の両方を有する微小なシステムを指す。NEMS/MEMSデバイスの例は、インクジェットプリンタのヘッド、微小機械式スイッチ及び加速度計(例えば車のエアバッグのための)及びジャイロスコープ(例えば車のロールオーバ検出のための)を含む応用のためのセンサである

### [0064]

本開示において、用語「ゼロレベルパッケージング」は、個々のNEMS/MEMS構造をダイシングする前の、ウエハレベルでのNEMS/MEMS構造の封入を指す。NEMS/MEMS構造それ自体は、しばしば自立していて壊れやすいので、それらは、ウエハレベルで封入して、ウエハのダイシング及び使用中の損傷を避ける必要がある。加えて、多孔質薄膜(皮膜)は、前記封入物の一部でもよい。好ましくは、皮膜はNEMS/MEMSデバイスの上方に直接設ける。皮膜を通じて犠牲層(NEMS/MEMS構造を包囲する)を除去した後、皮膜を封止して所望のゼロレベル封入をもたらし、キャビティ中に所望の圧力の必要とされる雰囲気を封入する。本アプローチの一利点は、それが、既在のアプローチと比較して、パッケージしたデバイスの厚さ及び面積を減少させることである。

### 【実施例】

50

10

20

30

### [0065]

例として、いくつかの更なる実施例を以下で説明し、本発明に係る実施形態の特徴及び 利点を示す。但し、本発明の実施形態はそれに限定されることはない。

### [0066]

第1の実施例において、厚さ1μmのA1層(200mmのSiウエハ上にあるシリコン酸化層の上部にスパッタリングによって堆積した)の陽極酸化は、図2に示す160μm~800μmの陽極酸化領域幅の不要な大きい拡張をもたらす境界線構造を含まないった。陽極酸化プロセスは、硫酸ベースの電解液を管するテフロンベースのチャンバ内で実施する。ここで使用する陽極酸化温度及び陽極酸化電圧は、それぞれ20~30、10~20Vの範囲内である。図6に示すような他の複数の構造21を包囲する境界線23(環)を規定するフォトレジストマスクを使用した製の間じ陽極酸化プロセスを実施することによって、陽極酸化領域に制御されてきた。これは、領域25において、フォトレジストのアンダーカットが実質的に起こらないことを意味している。これは、陽極酸化プロセスの優れたコントロールの実例であり、また、本発明に係る実施形態の利点を示している。

#### [0067]

第2の実施例において、薄膜真空パッケージは、本発明の実施形態及び図4a~図4dのプロセスフローに従い、次のステップに従って構成した。

1 . 2 0 0 m m の S i ウエハ ( 1 0 + 1 1 ) の上部での、厚さ 3 μ m のシリコン酸化物層の堆積及びパターニング。

2. 図4aに示す、犠牲層の上部での、厚さ1.5µmのA1層41のスパッタ堆積。

3. 図4bに示す、定電圧20Vを印加することによる、30 の硫酸ベースの電解液中での、フォトレジストマスク42を使用したA1層のマスク陽極酸化。

4. 縦方向陽極酸化プロセスが終了し、陽極酸化電流が停止する際に、生じる多孔質 A 1 O  $_{\rm x}$  構造 4 3 を陽極酸化電解液中に 2 0 ~ 3 0 分放置することで、 A 1 O  $_{\rm x}$  層のわずか一部をウェットケミカルエッチングし、 細孔(ホール)底部に存在するバリア A 1 O  $_{\rm x}$  層 6 1 を(少なくとも部分的に)除去することができる(図 5 参照)。

5 . ウエハを低圧チャンバ内に配置し、 H F 蒸気、エタノール蒸気及び窒素の混合物に曝し、多孔質 A 1 O  $_{\rm x}$  構造 4 3 の下にある犠牲層 4 0 を除去する結果、図 4 c に示すようなキャビティ 4 4 が得られる。

6 . 図4cに示すように、PECVD技術を使用して、厚さ4μmのシリコン窒化物層4 5の堆積によって真空チャンバ内でキャビティ44を封止する結果、図4dに示すように 、薄膜真空パッケージが得られる。

### [0068]

本発明は、図面及び先の説明において、詳細に図示され、説明されているが、かかる図示及び説明は、説明目的又は例示的なものであり、限定的と考えるべきではない。本発明は、開示した実施形態に限定されない。開示した実施形態に対する他の変形が、図面、開示内容及び添付した請求項の研究から、請求項の発明を実施する際に、当業者によって理解され達成されるであろう。請求項において、「備える、含む」(comprising)は、他のエレメント又はステップを除外せず、不定冠詞「1つの」(a又はan)は複数を除外しない。単一の処理装置又は他のユニットは、請求項で記載した種々の項目の機能を達成するであろう。ある手段が異なる従属請求項に相互に記載されているという単なる事実は、これらの手段の組み合わせが有利に使用することができないことを言うものではない。請求項におけるどの参照符号も範囲を狭く限定するものと解釈すべきでない。

### [0069]

先の説明は、本発明の特定の実施形態を詳細に述べている。しかしながら、どれほど詳細に先の説明を明細書にて行っても、本発明は多くの方法で実施でき、また開示した実施形態に限定されないことが理解されるだろう。本発明のある特徴又は態様を述べる場合の

10

20

30

. .

40

特定の用語の使用は、その用語が関係する本発明の特徴又は態様のいかなる特定の特徴も含むように限定するように、その用語が本明細書で再定義されるということを暗示するように取られるべきではないことに注目すべきである。

### 【図3c】

### 【図4a】

【図4b】

### 【図4c】

### 【図4d】

## 【図5】

# 【図6】

### フロントページの続き

(51) Int.CI. F I テーマコード (参考)

**C 2 5 D 11/32 (2006.01)** C 2 5 D 11/26 3 0 2

**H01L 21/316 (2006.01)** C25D 11/32

H 0 1 L 21/316 T

(74)代理人 100101454

弁理士 山田 卓二

(74)代理人 100081422

弁理士 田中 光雄

(74)代理人 100100479

弁理士 竹内 三喜夫

(72)発明者 ジョゼフ・ゼクリー

ベルギー3001ルーヴァン、セレステイネンラーン21アー番、ブス0301

(72)発明者 ヘンドリクス・ティルマンス

ベルギー3630マースメヘレン、リングラーン19番

(72)発明者 クリス・ファン・ホーフ

ベルギー3001ルーヴァン、コニング・レオポルト・デルデ・ラーン23番

(72)発明者 ロベルト・プエルス

ベルギー3052ブランデン、ブライネストラート2番

F ターム(参考) 5F058 BC03 BD05 BF70 BJ02

### 【外国語明細書】

1

Tech IP Consulting

31/03/2011 11:32 AM

Imec ref. 2010/092 - Tech IP ref. IMEC073/EP

High precision Masked Anodization

5 draft 2

### A METHOD FOR PRECISELY CONTROLLED MASKED ANODIZATION

10

### Field of the Invention

[0001] The present invention is related to methods for precisely controlling a masked anodization process.

[0002] The present invention is further related to

15 manufacturing semiconductor devices, especially to methods

of encapsulation and to such devices. More specifically it

may relate to zero-Level or wafer level packaging of

semiconductor devices.

[0003] More particularly, the present invention relates to Nano- and/or Micro-Electro-Mechanical Systems (NEMS and /or MEMS) and to processes of encapsulating (or packaging) said systems.

### State of the art.

25 [0004] Creating patterns of a dielectric or porous material within a conductive thin film by means of masked anodization (wet electrochemical oxidation and/or etching) has several advantages over conventional thin film deposition and etching techniques, such as the simplicity of the fabrication process and the relatively planar (and aligned) structures that result from such process. Masking the anodization process is normally achieved by applying a masking structure on top of the layer to be anodized. The

masking structure can be applied by means of conventional photolithography (photoresist mask) or by means of deposition and patterning of another material that is resistant to the anodization process (hard mask). A photoresist mask is simpler to implement than a hard mask but photoresists are normally attacked during the anodization process resulting in poor control over the lateral extent of the anodized patterns.

[0005] Finding a simple technique for high-precision

masked anodization is necessary to fabricate planar patterns of a dielectric or porous material within a conductive thin film. Such patterns are for example useful to create interconnecting metal lines (patterns) which are isolated from each other by a porous dielectric material of low dielectric constant which provides the advantage of reduced capacitance between the interconnecting lines. Because of this, the speed of signals that can be transmitted through these interconnects can be increased and the cross-coupling between the different interconnects can be reduced, resulting in better performance for integrated circuits.

Another highapplication requiring [0006] anodization is the packaging masked precision (encapsulation) of Nano- and/or Micro-Electro-Mechanical 25 Systems (NEMS/MEMS). Said NEMS/MEMS systems cannot be directly packaged in a plastic or ceramic package, the socalled first level package, since NEMS/MEMS are often composed of fragile and/or mobile free-standing parts that can easily be damaged during dicing and assembly. To avoid 30 such damage, NEMS/MEMS devices have to be protected at the wafer level, before dicing. This is possible by the socalled zero-level packaging or wafer-level packaging techniques. Most NEMS/MEMS systems therefore require an encapsulation under vacuum or under a controlled atmosphere and pressure in order to ensure either a good performance or an acceptable lifetime of operation. The encapsulation has to be performed without the direct deposition of sealing material on the NEMS/MEMS device, as such 5 deposition can cause damage to the device. Therefore there is a need to deposit first an encapsulation made of a layer having holes (pores) through which a vacuum and/or controlled atmosphere can be realized and thereafter deposit a sealing layer. A simple and cheap process led to the idea of encapsulating NEMS/MEMS devices with a porous membrane. This facilitates the manufacturing of the device as it avoids the need to shape access holes in the membrane using photolithography since the device can be released through the pores of the membrane.

Porous alumina (AlOx) membranes are recently 15 [0007] being investigated for use as porous membranes in said thin film vacuum packaging of NEMS/MEMS devices as shown in figure 1, which shows a schematic image of a substrate 1 (e.g. Si), carrying on its surface a MEMS device 2, encapsulated by a porous membrane 3. The membrane 3 is covered by a sealing layer 4. The porous membrane 3 is obtained by anodization of an aluminum thin film (deposited on top of a dielectric thin film) in a low-pH electrolyte, and using a patterned photoresist layer as the mask. The anodization process may be performed on masked Al layers using a photoresist mask (Hellin Rico et Electrochem. Soc. Vol. 154, No. 9 (2007)). The pores 5 (not to scale), are elongate openings membrane's thickness, through which pores the release of 30 the MEMS device 2 takes place, which is the etching away of a sacrificial layer deposited onto the MEMS device prior to the deposition of the membrane layer 3. This masked anodization process using photoresist has the drawback that the openings in the photoresist do not appropriately limit

the anodization process to the desired area, as shown in figure 2. This figure shows the substrate 1, with a dielectric thin film 11 on the surface of the substrate, and a membrane layer 12 on the thin film 11. A photoresist 5 mask 13 covers the membrane film except for a portion 14 which defines the area of the membrane which is to be anodized. As described in more detail further, anodization generally takes place by submerging the substrate into an anodization bath. When the substrate is left too long in the anodization bath, anodization continues until an anodized region 15 is formed which is too wide (see borders 16), i.e. unwanted continuous growth of the anodized region occurs.

[8000] Especially when applying the anodization 15 voltage to a full wafer or large area substrate comprising the layer to be anodized and leaving the substrate (wafer) in the anodization bath results in said unwanted continuous growth of the anodized region beyond the limits defined by the photoresist mask. The problem of performing the masked anodization process on a full wafer scale is the fact that areas defined by the masks being present in the central areas (middle) of the substrate (wafer) surface are not yet completely anodized while the areas defined by the masks being present around the substrate (wafer) edges are 25 already completely anodized and will become over-anodized. The problem of unwanted continuous growth is caused by edge peeling (resulting in "undercut") of the photoresist mask due to:

- (1) Attack by the high-acidity level electrolyte,

- (2) Expansion of the AlOx thin film, and

30

(3) Gas formations occurring during the anodization process.

[0009] Hence there still exists a problem in state of the art techniques to provide a reliable and

controllable method for providing precisely-defined anodized patterns within a conductive layer using a photoresist mask, and the application of such anodized patterns to provide for example a thin film vacuum 5 packaging for NEMS/MEMS.

### Summary of the invention

[0010] It is an object of the invention to provide an improved method for creating precise patterns of anodized material within an anodizable layer by means of masked anodization. More specifically it is an object to create precise patterns of a dielectric or porous material within a conductive thin film using masked anodization. It is thereby in particular an object to provide an improved and cost-efficient masked anodization process for application in manufacturing of semiconductor devices on (full) wafer scale to make the anodization process applicable in large scale production of semiconductor devices.

20 [0011] It is further an object of embodiments of the present invention to provide a reliable and controllable method for performing wet anodization processes which locally transform an anodizable layer e.g. a conductive (metal) layer into an anodized layer e.g. a dielectric or porous layer. It is the goal of the invention to perform said anodization uniformly on a (full) wafer scale.

[0012] A further object is to provide a microelectronic process technology for Nano- and Micro Electro

Mechanical Systems (NEMS/MEMS) in order to achieve a

30 controllable and uniform (full) wafer scale encapsulation

or packaging process for said NEMS/MEMS devices.

[0013] The above objectives are accomplished by a method and device according to the present invention. The present invention solves the problem of achieving a uniform and

controllable anodization by surrounding a group (plurality) of mask structures with an additional surrounding mask structure. In other words the problem is solved by using additional surrounding photoresist or other mask 5 structure with high precision which defines small areas on the surface to be exposed selectively to the anodization process without causing over-anodization leading towards delamination or undercut of the mask layer during the anodization. The presence of said additional surrounding structure results in self-limitation of 10 mask anodization process as the anodized border becomes anodized (oxidized) simultaneously with the anodized areas within said border, so that said border prevents anodization current from reaching the anodized region of 15 the mask structures to avoid unwanted further anodization. Since the electrical current needed for the anodization process is supplied at the edge (perimeter) substrate, surrounding every group of structures on the anodization mask with an additional surrounding mask 20 structure (defining a borderline of anodized material) results in self-limitation of the anodization process as anodized border becomes simultaneously anodized (oxidized) and prevents further anodization current from reaching the anodized region. The additional surrounding 25 mask structure (defining the borderline or protection ring) may be applied at different scales during the mask design for the anodization process (i.e. the borderline can surround a small group or a large group of structures, or possibly surround the whole substrate (wafer). The width 30 of the additional surrounding mask structure and the surrounded area can be chosen (or adjusted) to guarantee a full vertical anodization of the enclosed structures, and at the same time protect these structures from large lateral extensions of the anodization process.

[0014] By applying the masked anodization process according to the invention in a packaging process for NEMS/MEMS devices, an additional surrounding mask structure is surrounding a group of individual NEMS/MEMS devices and will result in self-limitation of the anodization process as the anodized border becomes simultaneously anodized (oxidized) and prevents further anodization current from reaching the anodized region of the mask structures to avoid unwanted further anodization.

10 [0015] It is an advantage of embodiments according to the present invention that providing the additional surrounding mask structure does not need extra processing steps as said additional mask structure may be provided simultaneously with the provision of the first mask structure(s).

[0016] The invention is thus related to a method as disclosed in the appended claims. Particular and preferred aspects of the invention are set out in the accompanying independent and dependent claims. Features from the dependent claims may be combined with features of the independent claims and with features of other dependent claims as appropriate and not merely as explicitly set out in the claims.

[0017] As such, the invention is related to a method for masked anodization, said method comprising the steps of

- providing a substrate,

- providing an anodizable layer on said substrate,

- providing on said anodizable layer at least one first mask defining one or more first structures to be anodized and an additional second mask defining a second structure to be anodized, said second structure surrounding said one or more first structures,

- anodizing said anodizable layer in the regions defined by the first and second mask in order to create anodized structures,

- removing the first and second mask.

- 5 The expression 'anodizing said anodizable layer in the regions defined by the first and second mask' means that the anodization continues until the layer is anodized over the totality of its thickness in said regions.

- With 'surrounding' is meant that the second structure

10 forms a closed ring structure around the first

structure(s).

- [0018] According to the preferred embodiment, the step of anodizing said anodizable layer is performed by inserting the substrate in an electrolyte and applying a voltage (or electrical current) on said substrate.

- [0019] The step of anodizing said anodizable layer may also be performed using a two-step anodization process comprising a first anodizing step to form a first anodized layer, followed by a second anodizing step after etching away the first anodized layer.

- [0020] According to a preferred embodiment, the step(s) of anodizing is(are) performed by inserting the substrate in an electrolyte selected from the group consisting of sulphuric acid, phosphoric acid, oxalic acid,

- 25 hydrofluoric acid, ethanol, isopropyl alcohol, and mixtures of these chemicals.

- [0021] According to the preferred embodiment, said anodizing step(s) produce(s) elongate pores in said anodized structure(s), said pores extending from the front surface to the back surface of said anodizable layer.

- [0022] According to an embodiment, the anodizable layer is an Al layer and the step(s) of anodizing is(are) performed by inserting the substrate in a sulphuric-acid

based electrolyte at temperatures in the range of  $20-40\,^{\circ}\text{C}$  and applying a voltage of around 20V.

[0023] According to an embodiment, the anodizable layer is a metal layer which is to be anodized to form a 5 metal oxide layer, and said anodization bath comprises an etchant suitable for etching said oxide, and wherein said anodization step comprises a first time period during which said voltage is applied, said voltage being removed at the end of said first time interval, and a second time period following said first time period, during which second period the substrate is left in said bath, to thereby remove a barrier layer at the bottom of said pores.

In the latter embodiment, said metal may be aluminium and said etchant phosphoric acid.

- 15 [0024] According to an embodiment:

- said step of providing a substrate comprises depositing a sacrificial layer onto a base substrate,

- said anodizable layer is provided onto said sacrificial layer,

- 20 said first mask defines a structure to be a anodized,

- said anodizing step(s) produce(s) elongate pores in said anodized structure, said pores extending from the front surface to the back surface of said anodizable layer,

- at least a portion of the sacrificial layer is removed 25 through said pores, so as to form a cavity, and

- a sealing layer is applied onto said anodized structures in order to seal off said cavity.

[0025] In the latter embodiment, the sacrificial layer can be made of a material selected from the group consisting of polycrystalline SiGe, oxide-based or nitride-based films, polymer, single crystal or polycrystalline Si. In the latter embodiment, said substrate may comprise a NEMS/MEMS device, which is(are) encapsulated in said cavity.

[0026] In the latter case, the step of removing at least some of the sacrificial material is performed using a selective wet or dry etching that does not damage the enclosed NEMS/MEMS device.

- In the latter embodiment, the sacrificial layer may be silicon-oxide and the selective etching may be performed using a vapor-phase hydrofluoric (HF) acid mixed with other gases such as nitrogen and ethanol or water vapor in a reduced-pressure chamber.

- 10 [0028] In the latter embodiment, the sacrificial layer may be a polymer-based material and the selective etching may be performed using a dry plasma etching in a low-pressure chamber in the presence of oxygen ions.

[0029] In the latter embodiment, the sealing layer 15 may be:

- a conductive layer such as Al, Cu, Ni, polycrystalline Si or SiGe, or

- a dielectric material such as oxide- or nitride-based silicon compounds, or

- a polymer, or

- a combination or a stack of two or more materials, Said sealing layer may be deposited using an evaporation technique or a chemical (CVD) or physical vapour deposition (PVD) technique in a low-pressure chamber..

- 25 [0030] In the method of the invention, the anodizable layer may be a metal layer or semiconducting layer. Said anodizable layer may be selected from the group consisting of Al, Ta, Ti, Cu, Ni, polycrystalline Si, polycrystalline SiGe.

- 30 [0031] In the method of the invention, the mask structures may be formed by photolithographic patterning of a photosensitive layer.

### Brief description of the figures

[0032] Figure 1 illustrates the concept of thin film MEMS packaging using a porous membrane as known in the prior art.

5 [0033] Figure 2 illustrates the large lateral extension of the Al anodization process using a photoresist mask (problem to be solved by the invention).

[0034] Figure 3a illustrates an intermediate stage during the anodization process of the invention whereby the anodization current may still reach the anodization region before the vertical anodization is complete.

[0035] Figure 3b is a top view of a wafer comprising several masks and provided with a ring electrode arranged along the circumference of the wafer.

15 [0036] Figure 3c illustrates the final stage of the anodization process of the invention (when the vertical anodization is complete) whereby the borderline is completely anodized (oxidized) forming a dielectric isolation ring around the anodization region which blocks 20 further supply of the electric charges needed for anodization.

[0037] Figure 4a-4d illustrate different steps in a suitable process flow to use the masked anodization process for thin film packaging of a NEMS/MEMS device according to

25 embodiments of the invention.

[0038] Figure 4a illustrates the step of depositing a metal layer on top of the sacrificial layer covering the NEMS/MEMS structure and interconnects.

[0039] Figure 4b illustrates the step of masked anodization and thin barrier oxide layer removal.

[0040] Figure 4c illustrates the step of removing the sacrificial layer and depositing a sealing layer.

[0041] Figure 4d illustrates the step of removing the layers covering the metal pads for electrical access and illustrates the final NEMS/MEMS device encapsulation.

[0042] Figure 5 illustrates the form the pores 5 formed by anodization of an Aluminium layer, and the oxide barrier layer formed at the bottom of the pores.

[0043] Figure 6 illustrates an example of a mask design defining a ring structure in accordance with the invention.

10 [0044] The drawings are only schematic and are non-limiting. In the drawings, the size of some of the elements may be exaggerated and not drawn on scale for illustrative purposes. Any reference signs in the claims shall not be construed as limiting the scope. In the different drawings, the same reference signs refer to the same or analogous

# Detailed description of the invention

elements.

30

[0045] According to an aspect of the invention a 20 method is provided for uniform and controllable masked anodization, said method comprising at least the steps of (with reference to figure 3):

- providing (i.e. supplying or producing) a substrate (10,11), and then

- 25 providing an anodizable layer (12) on said substrate, and then

- providing on said anodizable layer (12) at least one first mask (20) defining the dimensions of one or more first structures (21) to be anodized and an additional second mask (22) defining a second structure (23) to be anodized, said second structure surrounding said first structure(s), and then

- anodizing said anodizable layer (12) in the regions defined by the first (20) and second (22) mask in order to create anodized structures (21,23), and then

- removing the mask structures (20,22).

[0046] Figure 3a shows again a substrate 10. In this embodiment (but not limiting to the scope of the invention), a dielectric layer 11 is deposited on the substrate, which may for example be a sacrificial layer.

10 Layer 12 is a membrane layer and layer 13 is a mask layer, preferably a patterned photoresist layer. According to the invention, the mask layer comprises at least one first mask 20, which defines the areas 21 which are to be anodized. The mask layer further comprises a second mask 22 which

defines an area 23 which surrounds said one or more first areas 21 to be anodized, forming a closed ring structure (not necessarily a circular-shaped ring) around said areas 21. Figure 3b shows a top view of a semiconductor wafer 30 carrying on its surface the mask layer 13 which comprises a

20 plurality of masks 20 which define areas 21 to be anodized. Around each mask 20 (and thus around each group of areas 21), the mask layer defines a ring structure 23 to be anodized which encircles the masks 20. The 'second mask structure' 22 thus corresponds to the totality of the mask

25 layer 13 minus the mask structures 20.

[0047] Along the edge of the wafer 30, an electrode 31 is placed, which is in electrical contact with the layer 12 to be anodized (preferably a metal layer, see further). The electrode 31 will play the role of the anode during the anodization. This assembly is submerged in an anodization bath, filled with an electrolyte. The second electrode (the cathode) is part of the anodization bath, facing the

front side of the wafer, i.e. the side carrying the masks 20/22). When anodization starts, the charge flows in the direction shown by the arrows 32 in figures 3a and 3b, i.e. starting from the outer edge of the wafer 30, and from the outer edge of each mask 20 towards the centre.

[0048] The drawing in figure 3a illustrates an intermediate stage during the anodization process of the invention whereby the anodization current (charge flow) may still reach the anodization regions 21 before the vertical anodization is complete. Figure 3c illustrates the final stage of the anodization process of the invention (when the vertical anodization is complete) whereby the ring structure 23 is completely anodized (oxidized), thereby acting as borderline and hence forming a dielectric isolation ring around the anodization regions 21, which blocks further supply of the electric charges needed for anodization.

[0049] According to embodiments, the material for use as anodizable layer 12 may be a metal or semiconducting layer which is selected from Al, Ta, Ti, Cu, Ni, polycrystalline Si, polycrystalline SiGe, etc... For example Aluminum layers may be used of around 0.5-10µm thick which may be deposited e.g. by using a sputtering process performed at low temperature. Prior to anodizing, the Al layers may be cleaned by placing them in an ultrasonic bath of deionized water.

[0050] According to embodiments, the first and second mask structures 20,22 may be formed by state of the art photolithographic patterning of a photosensitive layer 30 (resist). The advantage of using a photoresist (photosensitive layer) is the simplicity of forming the mask structures compared to other techniques involving deposition and patterning (by chemical or physical etching) of another mask material.

[0051] According to embodiments, the step of anodizing said anodizable layer 12 may lead to the formation of a porous (metal) layer. The pores (holes) in said porous layer may have a length greater than ten times their width, and a width in the range 5-200 nm, e.g. 20 nm or between 20nm and 200 nm, or between 5 and 20 nm.

According to embodiments, the step [0052] anodizing said anodizable (metal) layer 12 may be performed by means of a one-step anodization process. As already said one step-anodization process may be mentioned, performed by inserting the substrate in an electrolyte and applying a voltage (or electrical current) Said electrolyte may be sulphuric acid, substrate. phosphoric acid, oxalic acid, hydrofluoric acid, ethanol, 15 isopropyl alcohol, or a mixture of these or other chemicals. By applying a voltage in the range of 5-200V, pores are formed on the surface of the anodizable (metal) layer which are distributed randomly or in a hexagonal order. achieve better hexagonal order of the pores, optimized process conditions (anodization voltage, electrolyte, and temperature) should be chosen to reach the best volume

[0053] According to embodiments, the step of anodizing said anodizable (metal) layer 12 may be performed by means of a two-step anodization process. Said two step-anodization process may be performed by first applying a short anodizing step which patterns the surface of the anodizable (metal) layer 12. Later, this patterned surface acts as self-assembled marks for the second anodizing step [Mei et al., "Formation mechanism of alumina nanotubes and nanowires from highly ordered porous anodic alumina template," Journal of Applied Physics, Vol. 97, 034305 (2005)]. An extended second anodizing step, after etching away the first anodized layer not only improves the

expansion factor for the porous layer.

regularity of the cell arrangement but also reduces the number of defects and dislocations. A third anodizing step does not significantly improve the ordering of the pores and the size of the well-ordered domains.

the 5 [0054] According to embodiments, voltage (current) applied to achieve anodization of the anodizable (metal) layer is applied between the anodizable (metal) layer on the substrate and the electrolyte or a reference electrode therein. The voltage applied for anodizing lies 10 in the range between a few volts and a few hundreds of volts. A voltage of 20V can be used for example when sulphuric-acid anodization in а performing electrolyte at temperatures in the range of 20-40°C.

According to embodiments, when the [0055] 15 anodization of the additional structure 23 (vertical anodization) is complete, said additional structure forms a protective structure 23 acting as a dielectric isolation ring which blocks further supply of the electric charges for anodization needed and thereby avoids unwanted 20 extension of the anodized structures 21 surrounded by the additional structure 23.

[0056] According to embodiments, the anodizable (metal) layer may be an Aluminum layer and the anodization process conditions may be optimized for a given electrolyte, such as anodizing voltage and temperature, and acid concentration. Synthesis of porous aluminium oxide (AlO<sub>x</sub>) membranes can start from a sputter-deposited or evaporated Al film. The main anodizing parameters to be selected are dependent on the type of the electrolyte since this affects the diameter of the pores and the inter-pore distance, voltage and temperature, and the sequence of anodizing steps. The anodization may occur within a glass- or Teflon-based chamber in which a conductive reference electrode is inserted. The substrate 30 carrying the metal layer 12 to

be anodized may be inserted into the anodization chamber by means of a Teflon- or polymer-based holder which protects the edges and backside of the substrate from contacting the anodization electrolyte. The anodization process may be 5 performed by applying the anodization voltage (or current) between the reference electrode and the anodizable (metal) layer 12 on the substrate. Once the vertical anodization is dielectric isolation rings and the complete are formed within the additional (borderlines) structure 22, the anodization process is automatically stopped because of the impossibility of electric charges to travel through the isolation rings 23.

[0057] According to a further aspect of the invention a method is provided for (hermetically) sealing

15 a cavity in a semiconductor device thereby using the uniform and controllable masked anodization process described in previous embodiments, said method comprising at least the steps of (with reference to figure 4):

20

25

- providing a sacrificial layer (40) on a substrate wherein a micro cavity is to be located in said sacrificial layer (40), and wherein said substrate comprises a base substrate 10, a dielectric layer 11 and a MEMS or NEMS device 50, provided with electrical connections structures 51 to said device 50, and then

- providing a metal membrane layer (41) having a thickness greater than 0.5 micron on top of the sacrificial layer (40), and then

- providing on said metal layer (41) a first mask (42) defining the dimensions of a first structure 43 to be anodized, said dimensions corresponding to the dimensions of the cavity and an additional second mask defining a structure (not shown) to

10

be anodized surrounding said first structure (43), and then

- anodizing said metal layer (41) to form a porous metal oxide layer (43) having pores (holes) extending from the front surface of said porous metal oxide layer (43) towards the back surface of said porous metal oxide layer (43),

- removing the mask structures and at least some of the sacrificial layer (40) through the porous metal oxide layer (43), to form the micro cavity (44), and

- sealing (closing) with a sealing layer 45 the pores of said porous layer (43) in order to form a (hermetically) sealed cavity (44).

- 15 [0058] Figure 4a-4d illustrate different steps in a suitable process flow to use the masked anodization process for thin film packaging of a NEMS/MEMS device.

- [0059] According to embodiments, the substrate (10,11,50,51) and the sacrificial layer (40) may be any substrate and layer used and compatible with semiconductor processing, more particular NEMS/MEMS processing. Examples of substrates, which may be used are, for example, single crystal or polycrystalline Si, single crystal or polycrystalline Ge, glass, quartz, polymer, etc.

- 25 [0060] As shown, fragile devices 50 may be located in the cavity, said fragile device may be any NEMS/MEMS device requiring a vacuum or controlled atmosphere and pressure encapsulation.

- [0061] According to embodiments, the sacrificial layer 40 may be made of a material selected from polycrystalline SiGe, oxide-based or nitride-based films, polymer, single crystal or polycrystalline Si, etc. Said sacrificial material may be a material which can be removed

using a wet or dry etching technique that does not extensively damage the enclosed NEMS/MEMS device (selective etching). For example a silicon oxide sacrificial layer 40 can be removed by vapor-phase hydrofluoric (HF) acid mixed with other gases (such as nitrogen and ethanol or water vapor) in a reduced-pressure chamber. Such diluted vapor-phase HF mixture can remove the sacrificial silicon oxide layer without reacting with the NEMS/MEMS device or the porous layer surrounding the cavity.

10 [0062] According to embodiments, the sacrificial material 40 is filling a cavity 44 which is present under said membrane layer 41. The cavity can further comprise a NEMS/MEMS device 50, the functioning and structure of which is inert to said sacrificial material etchant. It can comprise a fragile object, on which substantially no material may be deposited during the closure process to guarantee the proper working and lifetime of the device. In certain embodiments the cavity 44 is closed except for said pores and optionally a vent hole (not shown). A vent hole is an additional hole which connects the cavity with the outside.

[0063] According to embodiments, the material for use as metal layer 41 may be a metal or semiconducting layer which is selected from Al, Ta, Ti, Cu, Ni, polycrystalline Si, polycrystalline SiGe, etc... For example Aluminum layers of around 0.5-10µm thick may be deposited by a sputtering process performed at low temperature. Prior to anodizing, the Al layers may be cleaned by placing them in an ultrasonic bath of deionized water.

[0064] According to embodiments, the step of anodizing said metal layer in order to form a porous metal oxide layer is such that a layer with pores (holes) is achieved, also referred to as porous membrane. Said porous

membrane has a front main surface and a back main surface and the pores (holes) in said membrane (holes can be a set of sub-surface interconnected pores) extend from the front main surface towards the back main surface.

5 [0065] According to embodiments the pores (holes) in said porous layer may have a length greater than ten times their width, and a width in the range 5-200 nm, e.g. 20 nm or between 20nm and 200 nm, or between 5 and 20 nm.

to the invention, when the According [0066] additional structure (vertical of the anodization 10 anodization) is complete, a protective structure is formed acting as a dielectric isolation ring surrounding the NEMS/MEMS devices which blocks further supply of the electric charges needed for anodization and thereby avoids 15 unwanted extension of the anodized structures surrounded by the additional structure.

According to 1700671 embodiments, thin barrier layer may be present after anodization at the bottom of the pores (holes) of the porous oxide layer 43 20 and may be removed by leaving the wafer for longer time in the anodization electrolyte after the completion of the vertical anodization process (after the end of the anodization current) and by further adding a small amount of an etching chemical to the anodization electrolyte. 25 This allows for chemical etching of a very small portion of the porous layer because the anodization electrolyte (mixture) and temperature can be chosen to provide slow etching of the porous oxide layer (for example by adding a small amount of phosphoric acid which is an etchant of 30 aluminium oxide). The advantage of performing the barrier oxide layer removal in the anodization electrolyte is that the inner surface of the pores (holes) is already wet upon completion of the anodization process which facilitates the access of the etching chemicals to the bottom of the pores.

The oxide barrier layer may alternatively be removed by a separate wet or dry chemical etching step after the anodization step, although difficulties are expected when attempting to use wet etching techniques because porous aluminium oxide may have hydrophobic properties that prevent the etching chemicals from penetrating the narrow pores to reach the barrier oxide layer.

[0068] Figure 5a illustrates the above described barrier layer. The figure illustrates the elongate shape of the pores 60 in the anodized region 21 shown in figure 3c. The barrier layer is formed by the small amount 61 of oxide at the bottom of the pores 60. By leaving the substrate in the anodization bath for a given time after the anodization current has been stopped, the additional etchant in the bath ensures the removal of the barrier layer (see figure 5b).

embodiments, the step [0069] According to removing the sacrificial material 40 under the porous Al layer (membrane) may be performed using an etchant 20 said sacrificial material is at least partially removed (etched away) through the pores 60 (holes) in said porous layer 43. The sacrificial material may be an oxide-based compound (such as SiO<sub>2</sub>) and the removal of this material may be performed in a reduced-pressure chamber containing a 25 mixture of gases including an etchant of the sacrificial material (such as hydrofluoric acid) in a vapor form in addition to other gases such as ethanol vapor, nitrogen, or water vapor. Alternatively the sacrificial layer 40 may be a polymer-based material such as photoresist, which can be 30 removed through the pores of said porous 43 layer by dry plasma etching in a low-pressure chamber in the presence of The removal of the sacrificial material oxygen ions. results in a cavity 44 that may be used to host a NEMS/MEMS structure.

[00701 According to embodiments, the sealing layer 45 may be deposited by an evaporation technique or a chemical (CVD) or physical vapour deposition (PVD) technique in a low-pressure chamber. Said sealing layer 45 a conductive layer such as Al, Cu, polycrystalline Si or SiGe. Alternatively, the sealing layer 45 may be a dielectric material such as oxide- or nitride-based silicon compounds, or a polymer. Alternatively, the sealing layer may be a combination or a 10 stack of two or more materials. The very high aspect ratio of the pores 60 of the porous membrane 43 prevents the deposition of the sealing layer 45 onto the NEMS/MEMS structure 50 and thus prevents damage or alteration of the NEMS/MEMS structure. Deposition of the sealing layer 15 results in a sealed cavity 44 that may host a NEMS/MEMS device.

[0071] According to embodiments, the cavity 44 may be sealed under controlled atmosphere and pressure by controlling the gases and pressure present in a chamber used to deposit the sealing layer which in turn closes the pores (holes) 60 leading to the formation of a sealed cavity 44 with controlled atmosphere and pressure.

25

# **DEFINITIONS**

[0072] Where reference is made in embodiments of the present invention to the term 'a controlled atmosphere', a controlled constitution of ambient gas is meant. The notion of 'horizontal' is defined as substantially orthogonal to the direction of a gravitational field, for example the earth's gravitational field.

[0073] For the purpose of this disclosure, the notion of 'essentially no material passing through the

openings' should be understood as 'no or only a limited amount of material passing in and/or through the openings'. In the context of sealing of a cavity that comprises a fragile device, it should be such that the proper working of the device is not affected by the limited amount of material that may pass.

[0074] For the purpose of this disclosure, the term Nano- and Micro-Electro-Mechanical Systems (NEMS/MEMS) refers to miniature systems with both electrical and non-electrical (e.g. mechanical) functionalities. Examples of NEMS/MEMS devices are inkjet printer heads, miniature mechanical switches, and sensors for applications that include accelerometers (e.g. for air bags in cars) and gyroscopes (e.g. for roll-over detection in cars).

For the purpose of this disclosure, the term "zero-level packaging" refers to the encapsulation of NEMS/MEMS structures at the wafer level before dicing the individual NEMS/MEMS devices. Because the NEMS/MEMS structures themselves are often freestanding and fragile 20 they must be encapsulated at the wafer level to avoid damage during wafer dicing and in use. Additionally a porous thin film (membrane) be part of said may encapsulation. The membrane is preferably provided directly above the NEMS/MEMS device. After removing the 25 sacrificial layer (surrounding the NEMS/MEMS structure) through the membrane, the membrane is sealed in order to provide the desired zero level encapsulation and to enclose the required atmosphere at a desired pressure in the cavity. One advantage of this approach is that it reduces the 30 thickness and area of the packaged device compared to the traditional approach.

## EXAMPLES

[0076] By way of illustration, embodiments of the present invention not being limited thereto, a number of further particular examples are discussed below, illustrating features and advantages of embodiments according to the present invention.

[0077] In a first particular example, anodization of a lum-thick Al layer (deposited by sputtering on top of a silicon oxide layer on 200mm Si wafer) has been performed using a photoresist mask not including the border line 10 structure resulting in a large unwanted extension of the anodization region width from 160 µm up to 800 µm as shown in figure 2. The anodization process is performed in a Teflonbased chamber housing a sulfuric-acid-based electrolyte. The anodization temperature and voltage used here are 15 within the range of 20-30°C and 10-20V respectively. By performing the same anodization process of an Al layer using a photoresist mask defining a border line 23 (ring) surrounding a plurality of other structures 21 as shown in figure 6, the anodization region width has been well 20 controlled by the photoresist mask resulting in only approximately 6µm lateral extension of the edges of the anodized regions 21. This means that in the areas 25, substantially no undercut of the photoresist occurs. latter is illustrative for the good control of the 25 anodization process using a simple photoresist mask comprising a borderline (ring) which surrounds the anodized region and illustrates advantages of embodiments according to the present invention.

[0078] In a second particular example, a thin film vacuum package has been constructed according to embodiments of the invention and the process flow of Figures 4a-4d by following the subsequent steps:

1. Deposition and patterning of a 3 $\mu$ m-thick silicon oxide layer 40 on top of a 200mm Si wafer 10+11.

- 2. Sputter-deposition of a 1.5µm-thick Al layer 41 on top of the sacrificial layer 40 as shown in Figure 4a.

- 3. Masked anodization of the Al layer using a photoresist mask 42 in a sulphuric-acid-based electrolyte at 30°C by applying a constant voltage of 20V as shown in Figure 4b.

5

10

- 4. Upon completion of the vertical anodization process and termination of the anodization current, the resulting porous AlOx structures 43 are left in the anodization electrolyte for a period of 20-30 minutes to allow for wet chemical etching of a small portion of the AlOx layer to (at least partially) remove the barrier AlOx layer 61 present at the bottom of the pores (holes) see figure 5.

- 5. The wafer is placed in a low-pressure chamber and exposed to a mixture of HF vapor, ethanol vapor and nitrogen to remove the sacrificial layer 40 below the porous AlOx structures 43 resulting in cavities 44 as shown in Figure 4c.

- 6. The cavities 44 are sealed by deposition of a 4μm-thick silicon nitride layer 45 in a vacuum chamber using a PECVD technique as shown in Figure 4c, resulting in thin film vacuum packages as shown in Figure 4d.

- 25 [0079] While the invention has been illustrated and described in detail in the drawings and foregoing description, such illustration and description are to be considered illustrative or exemplary and not restrictive. The invention is not limited to the disclosed embodiments.

- 30 Other variations to the disclosed embodiments can be understood and effected by those skilled in the art in practicing the claimed invention, from a study of the drawings, the disclosure and the appended claims. In the claims, the word "comprising" does not exclude other

elements or steps, and the indefinite article "a" or "an" does not exclude a plurality. A single processor or other unit may fulfill the functions of several items recited in the claims. The mere fact that certain measures are recited in mutually different dependent claims does not indicate that a combination of these measures cannot be used to advantage. Any reference signs in the claims should not be construed as limiting the scope.

[0080] The foregoing description details certain embodiments of the invention. It will be appreciated, however, that no matter how detailed the foregoing appears in text, the invention may be practiced in many ways, and is therefore not limited to the embodiments disclosed. It should be noted that the use of particular terminology when describing certain features or aspects of the invention should not be taken to imply that the terminology is being re-defined herein to be restricted to include any specific characteristics of the features or aspects of the invention with which that terminology is associated.

27

#### CLAIMS

- 1. A method for masked anodization, said method comprising the steps of

- providing a substrate (10,11),

10

- 5 providing an anodizable layer (12) on said substrate,

- providing on said anodizable layer at least one first mask (20) defining one or more first structures (21) to be anodized and an additional second mask (22) defining a second structure (23) to be anodized, said second structure surrounding said one or more first structures (21),

- anodizing said anodizable layer (12) in the regions defined by the first and second mask (20,22) in order to create anodized structures (21,23),

- 15 removing the first and second mask (20,22).

- 2. Method according to claim 1, wherein the step of anodizing said anodizable layer (12) is performed by inserting the substrate in an electrolyte and applying a voltage (or electrical current) on said substrate.

- 3. Method according to claim 1 or 2, wherein the step of anodizing said anodizable layer is performed using a two-step anodization process comprising a first anodizing step to form a first anodized layer, followed by a second anodizing step after etching away the first anodized layer.

- 4. Method according to any one of claims 1 to 3, wherein the step(s) of anodizing is(are) performed by inserting the substrate in an electrolyte selected from the group consisting of sulphuric acid, phosphoric acid, oxalic 30 acid, hydrofluoric acid, ethanol, isopropyl alcohol, and mixtures of these chemicals.

- 5. Method according to any one of clams 1 to 4, wherein said anodizing step(s) produce(s) elongate pores

- (60) in said anodized structure(s) (21), said pores extending from the front surface to the back surface of said anodizable layer (12).

- 6. Method according to claim 5, wherein the sanodizable layer (12) is an Al layer and wherein the step(s) of anodizing is(are) performed by inserting the substrate in a sulphuric-acid based electrolyte at temperatures in the range of 20-40°C and applying a voltage of around 20V.

- 7. Method according to claim 5, wherein the anodizable layer (12) is a metal layer which is to be anodized to form a metal oxide layer, and wherein said anodization bath comprises an etchant suitable for etching said oxide, and wherein said anodization step comprises a first time period during which said voltage is applied, said voltage being removed at the end of said first time period, and a second time period following said first time period, during which second period the substrate is left in said bath, to thereby remove a barrier layer (61) at the bottom of said pores (60).

- 8. Method according to claim 7, wherein said metal is aluminium and said etchant is phosphoric acid.

- $\begin{tabular}{ll} \bf 9. \ Method \ according \ to \ any \ one \ of \ claims \ 2 \ to \\ \bf 8, \ wherein \ : \end{tabular}$

- 25 said step of providing a substrate comprises depositing a sacrificial layer (40) onto a base substrate (10,11,50,51),

- said anodizable layer (41) is provided onto said sacrificial layer (40),

- 30 said first mask (42) defines a structure (43) to be a anodized,

- said anodizing step(s) produce(s) elongate pores (60) in said anodized structure, said pores extending from the

front surface to the back surface of said anodizable layer,

- at least a portion of the sacrificial layer (40) is removed through said pores, so as to form a cavity (44), and

5

- a sealing layer (45) is applied onto said anodized structure (43) in order to seal off said cavity (44).

- 10. Method according to claim 9 wherein the sacrificial layer (40) is made of a material selected from the group consisting of polycrystalline SiGe, oxide-based or nitride-based films, polymer, single crystal or polycrystalline Si.

- 11. Method according to claim 9 or 10,

wherein said substrate comprises a NEMS/MEMS device (50),

15 which is (are) encapsulated in said cavity (44).

- 12. Method according to claim 11, wherein the step of removing at least some of the sacrificial material (40) is performed using a selective wet or dry etching that does not damage the enclosed NEMS/MEMS device (50).

- 13. Method according to any one of claim 9 to 12 wherein the sacrificial layer (40) is silicon-oxide and the selective etching is performed using a vapor-phase hydrofluoric (HF) acid mixed with other gases such as nitrogen and ethanol or water vapor in a reduced-pressure chamber.

- 14. Method according to any one of claim 9 to 12 wherein the sacrificial layer (40) is a polymer-based material and the selective etching is performed using a dry plasma etching in a low-pressure chamber in the presence of 30 oxygen ions.

- ${\tt 15.}$  Method according to any one of claim 9 to 14 wherein the sealing layer (45) is

- a conductive layer such as Al, Cu, Ni, polycrystalline Si or SiGe, or

- a dielectric material such as oxide- or nitride-based silicon compounds, or

- 5 a polymer or

- a combination or a stack of two or more materials, and wherein said sealing layer is deposited using an evaporation technique or a chemical (CVD) or physical vapour deposition (PVD) technique in a low-pressure chamber.

- 16. Method according to any one of claims 1 to 15, wherein the anodizable layer is a metal layer or semiconducting layer.

- 17. Method according to claim 16, wherein the anodizable layer is selected from the group consisting of 15 Al, Ta, Ti, Cu, Ni, polycrystalline Si, polycrystalline SiGe.

- 18. Method according to any one of the preceding claims, wherein the mask structures are formed by photolithographic patterning of a photosensitive layer.

31

### ABSTRACT

## A METHOD FOR PRECISELY CONTROLLED MASKED ANODIZATION

5

The present invention is related to a method for masked anodization of an anodizable layer on a substrate, for example an aluminium layer present on a sacrificial layer, wherein the sacrificial layer needs to 10 be removed from a cavity comprising a Micro or Nano Electromechanical System (MEMS or NEMS). Anodization of an Al layer leads to the formation of elongate pores, through which the sacrificial layer can be removed. According to the method of the invention, the anodization of the Al 15 layer is done with the help of a first mask which defines the area to be anodized, and a second mask which defines a second area to be anodized, said second area surrounding the first area. Anodization of the areas defined by the first and second mask leads to the formation of an anodized 20 structure in the form of a closed ring around the first area, which forms a barrier against unwanted lateral anodization in the first area.

(Fig. 3a)

FIG. 1

FIG. 3b

FIG. 3c

FIG. 5a FIG. 5b

FIG. 6